Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

HARDWARE MANUAL

MN702-00009-1v0-E

8-BIT MICROCONTROLLER

New 8FX

MB95630H Series

Page 2

Page 3

8-BIT MICROCONTROLLER

New 8FX

MB95630H Series

HARDWARE MANUAL

For the information for microcontroller supports, see the following website.

http://edevice.fujitsu.com/micom/en-support/

FUJITSU SEMICONDUCTOR LIMITED

Page 4

Page 5

PREFACE

■ The Purpose and Intended Readership of This Manual

Thank you very much for your continued special support for Fujitsu Semiconductor products.

The MB95630H Series is a line of products developed as general-purpose products in the New

8FX family of proprietary 8-bit single-chip microcontrollers applicable as application-specific

integrated circuits (ASICs). The MB95630H Series can be used for a wide range of

applications from consumer products including portable devices to industrial equipment.

Intended for engineers who actually develop products using the MB95630H Series of

microcontrollers, this manual describes its functions, features, and operations. You should read

through the manual.

This manual is written to explain the respective configurations and operations of peripheral

functions, but not to provide specifications of a device.

For detailed specifications of a device, refer to its data sheet.

2

MC-8FX Programming Manual".

■ Trademark

For details on individual instructions, refer to "F

2

Note: F

The company names and brand names in this document are the trademarks or registered

trademarks of their respective owners.

MC is the abbreviation of FUJITSU Flexible Microcontroller.

■ Sample Programs

Fujitsu Semiconductor provides sample programs free of charge to operate the peripheral

resources of the New 8FX family of microcontrollers. Feel free to use such sample programs to

check the operational specifications and usages of Fujitsu microcontrollers.

Note that sample programs are subject to change without notice. As these pieces of software

are offered to show standard operations and usages, evaluate them sufficiently before use with

your system. Fujitsu Semiconductor assumes no liability for any damages whatsoever arising

out of the use of sample programs.

i

Page 6

How to Use This Manual

■ Finding a Function

The following methods can be used to search for details of a function in this manual:

• Searching from CONTENTS

CONTENTS lists the contents in this manual in the order of description.

• Searching from registers

The address at which a register is located is not mentioned in this manual. To check the

address of a register, refer to "■ I/O MAP" in the device data sheet.

■ Chapters

This manual explains one peripheral function in one chapter.

■ Terminology

This manual uses the following terminology.

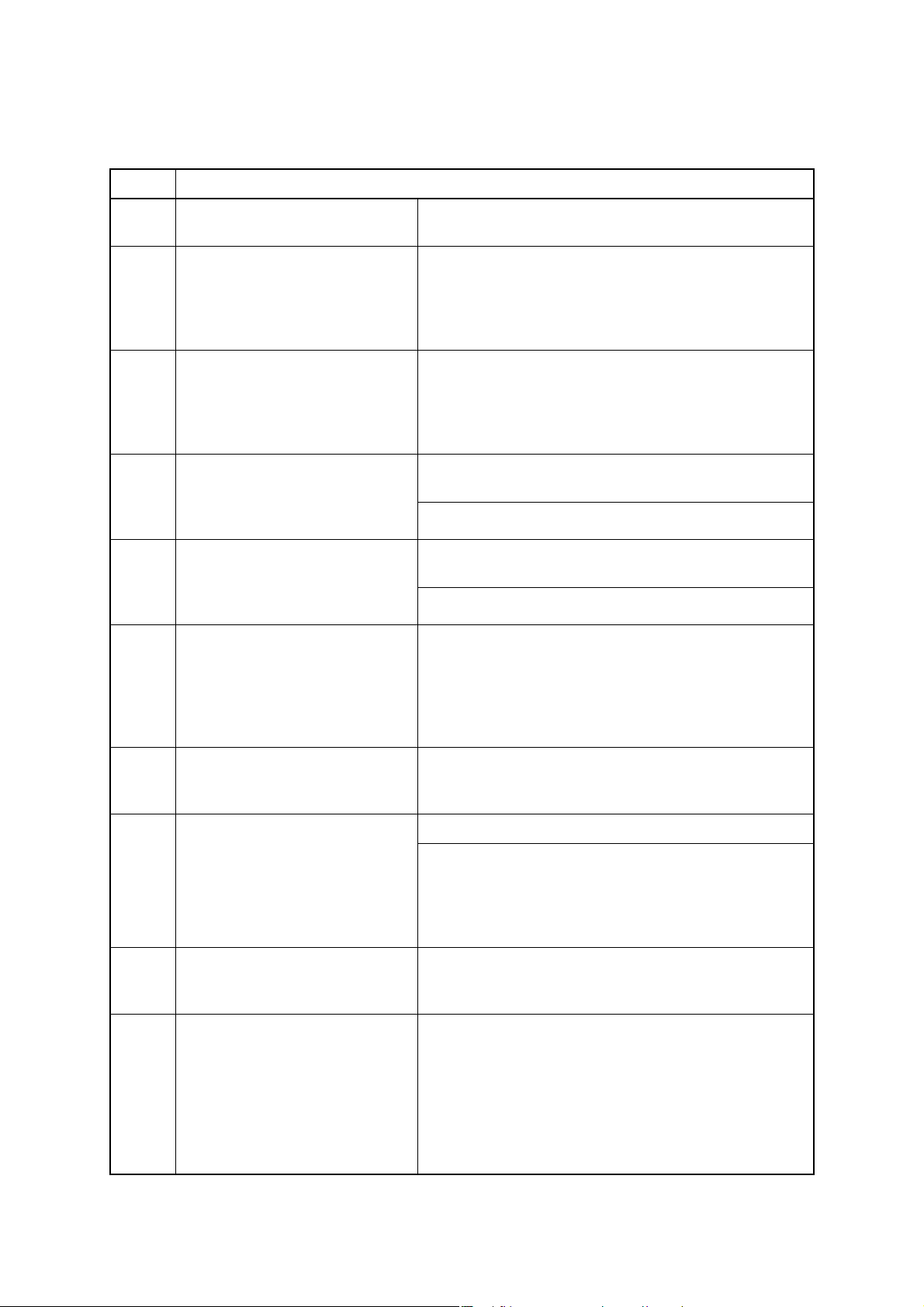

Te r m Explanation

Wor d Indicates an access in unit of 16 bits.

Byte Indicates an access in unit of 8 bits.

■ Notations

The notations in "■ Register Configuration" in this manual are explained below:

• bit: bit number

• Field: bit field name

• Attribute: Attributes for read access and write access of each bit

- R: Read-only

- W: Write-only

- R/W: Readable/Writable

- —: Undefined

• Initial value: Initial value of a bit after a reset

- 0: The initial value is "0".

- 1: The initial value is "1".

- X: The initial value is undefined.

Multiple bits are indicated in this manual in the following way.

- Example 1: bit7:0 represents bit7 to bit0.

- Example 2: SCM[2:0] represents SCM2 to SCM0.

The values such as those indicating addresses are written in this manual in the following ways:

- Hexadecimal number: The prefix "0x" is attached to the beginning of a value (e.g.:

0xFFFF).

- Binary number: The prefix "0b" is attached to the beginning of a value (e.g.: 0b1111).

- Decimal number: Only the number is used (e.g.: 1234).

In this manual, "n" in a pin name and a register abbreviation represents the channel number.

ii

Page 7

• The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

• The information, such as descriptions of function and application circuit examples, in this document are presented

solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR

device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based

on such information. When you develop equipment incorporating the device based on such information, you must

assume any responsibility arising out of such use of the information. FUJITSU SEMICONDUCTOR assumes no

liability for any damages whatsoever arising out of the use of the information.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be

construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or

any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR

warrant non-infringement of any third-party's intellectual property right or other right by using such information.

FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other

rights of third parties which would result from the use of information contained herein.

• The products described in this document are designed, developed and manufactured as contemplated for general

use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but

are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers

that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to

death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility,

aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control

in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial

satellite). Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for

any claims or damages arising in connection with above-mentioned uses of the products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss

from such failures by incorporating safety design measures into your facility and equipment such as redundancy,

fire protection, and prevention of over-current levels and other abnormal operating conditions.

• Exportation/release of any products described in this document may require necessary procedures in accordance

with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control

laws.

• The company names and brand names herein are the trademarks or registered trademarks of their respective

owners.

Copyright © 2011-2012 FUJITSU SEMICONDUCTOR LIMITED All rights reserved.

iii

Page 8

iv

Page 9

CONTENTS

CHAPTER 1 MEMORY ACCESS MODE .............................................................. 1

1.1 Memory Access Mode ......................................................................................................... 2

CHAPTER 2 CPU .................................................................................................. 3

2.1 Dedicated Registers ............................................................................................................ 4

2.1.1 Register Bank Pointer (RP) ............................................................................................ 6

2.1.2 Direct Bank Pointer (DP) ................................................................................................ 7

2.1.3 Condition Code Register (CCR) ..................................................................................... 9

2.2 General-purpose Register ................................................................................................. 11

2.3 Placement of 16-bit Data in Memory ................................................................................. 13

CHAPTER 3 CLOCK CONTROLLER ................................................................. 15

3.1 Overview ............................................................................................................................ 16

3.2 Oscillation Stabilization Wait Time .................................................................................... 24

3.3 Registers ........................................................................................................................... 27

3.3.1 System Clock Control Register (SYCC) ....................................................................... 28

3.3.2 PLL Control Register (PLLC) ........................................................................................ 29

3.3.3 Oscillation Stabilization Wait Time Setting Register (WATR) ....................................... 30

3.3.4 Standby Control Register (STBC) ................................................................................ 32

3.3.5 System Clock Control Register 2 (SYCC2) .................................................................. 34

3.3.6 Standby Control Register 2 (STBC2) ........................................................................... 36

3.4 Clock Modes ...................................................................................................................... 37

3.5 Operations in Low Power Consumption Mode (Standby Mode) ........................................ 41

3.5.1 Notes on Using Standby Mode ..................................................................................... 42

3.5.2 Sleep Mode .................................................................................................................. 48

3.5.3 Stop Mode .................................................................................................................... 49

3.5.4 Time-base Timer Mode ................................................................................................ 51

3.5.5 Watch Mode ................................................................................................................. 53

3.6 Clock Oscillator Circuit ...................................................................................................... 54

3.7 Overview of Prescaler ....................................................................................................... 55

3.8 Configuration of Prescaler ................................................................................................. 56

3.9 Operation of Prescaler ....................................................................................................... 57

3.10 Notes on Using Prescaler .................................................................................................. 59

CHAPTER 4 RESET ............................................................................................ 61

4.1 Reset Operation ................................................................................................................ 62

4.2 Register ............................................................................................................................. 66

4.2.1 Reset Source Register (RSRR) .................................................................................... 67

4.3 Notes on Using Reset ........................................................................................................ 70

CHAPTER 5 INTERRUPTS ................................................................................. 71

5.1 Interrupts ........................................................................................................................... 72

5.1.1 Interrupt Level Setting Registers (ILR0 to ILR5) ........................................................... 73

5.1.2 Interrupt Processing ..................................................................................................... 75

v

Page 10

5.1.3 Nested Interrupts .......................................................................................................... 77

5.1.4 Interrupt Processing Time ............................................................................................ 78

5.1.5 Stack Operation During Interrupt Processing ............................................................... 79

5.1.6 Interrupt Processing Stack Area ................................................................................... 80

CHAPTER 6 I/O PORT ....................................................................................... 81

6.1 Overview ............................................................................................................................ 82

6.2 Configuration and Operations ............................................................................................ 83

CHAPTER 7 TIME-BASE TIMER ........................................................................ 87

7.1 Overview ............................................................................................................................ 88

7.2 Configuration ..................................................................................................................... 89

7.3 Interrupt ............................................................................................................................. 91

7.4 Operations and Setting Procedure Example ..................................................................... 92

7.5 Register ............................................................................................................................. 95

7.5.1 Time-base Timer Control Register (TBTC) ................................................................... 96

7.6 Notes on Using Time-base Timer ...................................................................................... 98

CHAPTER 8 HARDWARE/SOFTWARE WATCHDOG TIMER .......................... 99

8.1 Overview .......................................................................................................................... 100

8.2 Configuration ................................................................................................................... 101

8.3 Operations and Setting Procedure Example ................................................................... 103

8.4 Register ........................................................................................................................... 106

8.4.1 Watchdog Timer Control Register (WDTC) ................................................................ 107

8.5 Notes on Using Watchdog Timer ..................................................................................... 109

CHAPTER 9 WATCH PRESCALER ................................................................. 111

9.1 Overview .......................................................................................................................... 112

9.2 Configuration ................................................................................................................... 113

9.3 Interrupt ........................................................................................................................... 115

9.4 Operations and Setting Procedure Example ................................................................... 116

9.5 Register ........................................................................................................................... 119

9.5.1 Watch Prescaler Control Register (WPCR) ................................................................ 120

9.6 Notes on Using Watch Prescaler ..................................................................................... 122

CHAPTER 10 WILD REGISTER FUNCTION ...................................................... 123

10.1 Overview .......................................................................................................................... 124

10.2 Configuration ................................................................................................................... 125

10.3 Operations ....................................................................................................................... 127

10.4 Registers ......................................................................................................................... 128

10.4.1 Wild Register Data Setting Registers (WRDR0 to WRDR2) ...................................... 129

10.4.2 Wild Register Address Setting Registers (WRAR0 to WRAR2) ................................. 130

10.4.3 Wild Register Address Compare Enable Register (WREN) ....................................... 131

10.4.4 Wild Register Data Test Setting Register (WROR) .................................................... 132

10.5 Typical Hardware Connection Example .......................................................................... 133

CHAPTER 11 8/16-BIT COMPOSITE TIMER ..................................................... 135

11.1 Overview .......................................................................................................................... 136

11.2 Configuration ................................................................................................................... 138

vi

Page 11

11.3 Channel ........................................................................................................................... 141

11.4 Pins .................................................................................................................................. 142

11.5 Interrupts ......................................................................................................................... 143

11.6 Operation of Interval Timer Function (One-shot Mode) ................................................... 144

11.7 Operation of Interval Timer Function (Continuous Mode) ............................................... 146

11.8 Operation of Interval Timer Function (Free-run Mode) .................................................... 148

11.9 Operation of PWM Timer Function (Fixed-cycle mode) .................................................. 150

11.10 Operation of PWM Timer Function (Variable-cycle Mode) .............................................. 152

11.11 Operation of PWC Timer Function .................................................................................. 154

11.12 Operation of Input Capture Function ............................................................................... 156

11.13 Operation of Noise Filter .................................................................................................. 158

11.14 Registers ......................................................................................................................... 159

11.14.1 8/16-bit Composite Timer Status Control Register 0 (Tn0CR0/Tn1CR0) ................... 160

11.14.2 8/16-bit Composite Timer Status Control Register 1 (Tn0CR1/Tn1CR1) ................... 163

11.14.3 8/16-bit Composite Timer Timer Mode Control Register (TMCRn) ............................ 167

11.14.4 8/16-bit Composite Timer Data Register (Tn0DR/Tn1DR) ......................................... 170

11.15 Notes on Using 8/16-bit Composite Timer ....................................................................... 173

CHAPTER 12 EXTERNAL INTERRUPT CIRCUIT ............................................. 175

12.1 Overview .......................................................................................................................... 176

12.2 Configuration ................................................................................................................... 177

12.3 Channels ......................................................................................................................... 178

12.4 Pin ................................................................................................................................... 179

12.5 Interrupt ........................................................................................................................... 180

12.6 Operations and Setting Procedure Example ................................................................... 181

12.7 Register ........................................................................................................................... 183

12.7.1 External Interrupt Control Register (EIC) .................................................................... 184

12.8 Notes on Using External Interrupt Circuit ........................................................................ 186

CHAPTER 13 INTERRUPT PIN SELECTION CIRCUIT ..................................... 187

13.1 Overview .......................................................................................................................... 188

13.2 Configuration ................................................................................................................... 189

13.3 Pins .................................................................................................................................. 190

13.4 Operation ......................................................................................................................... 191

13.5 Register ........................................................................................................................... 192

13.5.1 Interrupt Pin Selection Circuit Control Register (WICR) ............................................. 193

13.6 Notes on Using Interrupt Pin Selection Circuit ................................................................ 196

CHAPTER 14 LIN-UART .................................................................................... 197

14.1 Overview .......................................................................................................................... 198

14.2 Configuration ................................................................................................................... 200

14.3 Pins .................................................................................................................................. 205

14.4 Interrupts ......................................................................................................................... 206

14.4.1 Timing of Receive Interrupt Generation and Flag Set ................................................ 209

14.4.2 Timing of Transmit Interrupt Generation and Flag Set ............................................... 211

14.5 LIN-UART Baud Rate ...................................................................................................... 213

14.5.1 Baud Rate Setting ...................................................................................................... 215

14.5.2 Reload Counter .......................................................................................................... 219

14.6 Operations of LIN-UART and LIN-UART Setting Procedure Example ............................ 221

vii

Page 12

14.6.1 Operations in Asynchronous Mode (Operating Mode 0, 1) ........................................ 223

14.6.2 Operations in Synchronous Mode (Operating Mode 2) .............................................. 227

14.6.3 Operations of LIN function (Operating Mode 3) .......................................................... 231

14.6.4 Serial Pin Direct Access ............................................................................................. 234

14.6.5 Bidirectional Communication Function (Normal Mode) .............................................. 235

14.6.6 Master/Slave Mode Communication Function (Multiprocessor Mode) ....................... 237

14.6.7 LIN Communication Function ..................................................................................... 240

14.6.8 Examples of LIN-UART LIN Communication Flow Chart (Operating Mode 3) ........... 241

14.7 Registers ......................................................................................................................... 243

14.7.1 LIN-UART Serial Control Register (SCR) ................................................................... 244

14.7.2 LIN-UART Serial Mode Register (SMR) ..................................................................... 246

14.7.3 LIN-UART Serial Status Register (SSR) .................................................................... 248

14.7.4 LIN-UART Receive Data Register/LIN-UART Transmit Data Register (RDR/TDR) ... 250

14.7.5 LIN-UART Extended Status Control Register (ESCR) ............................................... 252

14.7.6 LIN-UART Extended Communication Control Register (ECCR) ................................ 255

14.7.7 LIN-UART Baud Rate Generator Registers 1, 0 (BGR1, BGR0) ................................ 257

14.8 Notes on Using LIN-UART .............................................................................................. 258

CHAPTER 15 8/10-BIT A/D CONVERTER ......................................................... 263

15.1 Overview .......................................................................................................................... 264

15.2 Configuration ................................................................................................................... 265

15.3 Pin ................................................................................................................................... 267

15.4 Interrupt ........................................................................................................................... 268

15.5 Operations and Setting Procedure Example ................................................................... 269

15.6 Registers ......................................................................................................................... 272

15.6.1 8/10-bit A/D Converter Control Register 1 (ADC1) ..................................................... 273

15.6.2 8/10-bit A/D Converter Control Register 2 (ADC2) ..................................................... 275

15.6.3 8/10-bit A/D Converter Data Register (Upper/Lower) (ADDH/ADDL) ......................... 277

15.7 Notes on Using 8/10-bit A/D Converter ........................................................................... 278

CHAPTER 16 LOW-VOLTAGE DETECTION RESET CIRCUIT ........................ 281

16.1 Overview .......................................................................................................................... 282

16.2 Configuration ................................................................................................................... 283

16.3 Pins .................................................................................................................................. 284

16.4 Operation ......................................................................................................................... 285

16.5 Register ........................................................................................................................... 286

16.5.1 LVD Reset Voltage Selection ID Register (LVDR) ..................................................... 287

CHAPTER 17 CLOCK SUPERVISOR COUNTER .............................................. 289

17.1 Overview .......................................................................................................................... 290

17.2 Configuration ................................................................................................................... 291

17.3 Operations ....................................................................................................................... 293

17.4 Registers ......................................................................................................................... 298

17.4.1 Clock Monitoring Data Register (CMDR) .................................................................... 299

17.4.2 Clock Monitoring Control Register (CMCR) ................................................................ 300

17.5 Notes on Using Clock Supervisor Counter ...................................................................... 302

CHAPTER 18 8/16-BIT PPG ............................................................................... 305

18.1 Overview .......................................................................................................................... 306

viii

Page 13

18.2 Configuration ................................................................................................................... 307

18.3 Channel ........................................................................................................................... 309

18.4 Pins .................................................................................................................................. 310

18.5 Interrupt ........................................................................................................................... 311

18.6 Operations and Setting Procedure Example ................................................................... 312

18.6.1 8-bit PPG Independent Mode ..................................................................................... 313

18.6.2 8-bit Prescaler + 8-bit PPG Mode ............................................................................... 315

18.6.3 16-bit PPG Mode ........................................................................................................ 317

18.7 Registers ......................................................................................................................... 320

18.7.1 8/16-bit PPG timer n1 Control Register (PCn1) .......................................................... 321

18.7.2 8/16-bit PPG timer n0 Control Register (PCn0) .......................................................... 323

18.7.3 8/16-bit PPG timer n1/n0 Cycle Setup Buffer Register (PPSn1/PPSn0) .................... 325

18.7.4 8/16-bit PPG timer n1/n0 Duty Setup Buffer Register (PDSn1/PDSn0) ..................... 326

18.7.5 8/16-bit PPG Start Register (PPGS) ........................................................................... 327

18.7.6 8/16-bit PPG Output Reverse Register (REVC) ......................................................... 329

18.8 Notes on Using 8/16-bit PPG .......................................................................................... 331

CHAPTER 19 16-BIT PPG TIMER ...................................................................... 333

19.1 Overview .......................................................................................................................... 334

19.2 Configuration ................................................................................................................... 335

19.3 Channel ........................................................................................................................... 337

19.4 Pins .................................................................................................................................. 338

19.5 Interrupts ......................................................................................................................... 339

19.6 Operations and Setting Procedure Example ................................................................... 340

19.7 Registers ......................................................................................................................... 344

19.7.1 16-bit PPG Downcounter Register (Upper/Lower) (PDCRHn/PDCRLn) .................... 345

19.7.2 16-bit PPG Cycle Setting Buffer Register (Upper/ Lower) (PCSRHn/PCSRLn) ......... 346

19.7.3 16-bit PPG Duty Setting Buffer Register (Upper/Lower) (PDUTHn/PDUTLn) ............ 347

19.7.4 16-bit PPG Status Control Register (Upper) (PCNTHn) ............................................. 348

19.7.5 16-bit PPG Status Control Register (Lower) (PCNTLn) ............................................. 350

19.8 Notes on Using 16-bit PPG Timer ................................................................................... 352

CHAPTER 20 16-BIT RELOAD TIMER .............................................................. 353

20.1 Overview .......................................................................................................................... 354

20.2 Configuration ................................................................................................................... 356

20.3 Channel ........................................................................................................................... 358

20.4 Pins .................................................................................................................................. 359

20.5 Interrupt ........................................................................................................................... 360

20.6 Operations and Setting Procedure Example ................................................................... 361

20.6.1 Internal Clock Mode .................................................................................................... 363

20.6.2 Event Count Mode ...................................................................................................... 367

20.7 Registers ......................................................................................................................... 369

20.7.1 16-bit Reload Timer Control Status Register (Upper) (TMCSRHn) ............................ 370

20.7.2 16-bit Reload Timer Control Status Register (Lower) (TMCSRLn) ............................ 372

20.7.3 16-bit Reload Timer Timer Register (Upper/Lower) (TMRHn/TMRLn) ....................... 374

20.7.4 16-bit Reload Timer Reload Register (Upper/Lower) (TMRLRHn/TMRLRLn) ........... 375

20.8 Notes on Using 16-bit Reload Timer ............................................................................... 376

ix

Page 14

CHAPTER 21 MULTI-PULSE GENERATOR ...................................................... 377

21.1 Overview .......................................................................................................................... 378

21.2 Block Diagram ................................................................................................................. 381

21.3 Pins .................................................................................................................................. 389

21.4 Interrupts ......................................................................................................................... 390

21.5 Operations ....................................................................................................................... 392

21.5.1 Operation of Position Detection .................................................................................. 394

21.5.2 Operation of Data Write Control Unit .......................................................................... 396

21.5.3 Operation of 16-bit MPG Output Data Buffer Register (Upper/Lower)

(OPDBRHx/OPDBRLx) .............................................................................................. 400

21.5.4 Operation of Data Transfer of 16-bit MPG Output Data Register (Upper/Lower) ....... 402

21.5.4.1 At OPDBRH0 and OPDBRL0 Write ......................................................................... 404

21.5.4.2 At 16-bit Reload Timer Underflow ........................................................................... 405

21.5.4.3 At Position Detection ............................................................................................... 407

21.5.4.4 At Position Detection and Timer Underflow ............................................................. 409

21.5.4.5 At Position Detection or Timer Underflow ................................................................ 412

21.5.4.6 At One-shot Position Detection ............................................................................... 414

21.5.4.7 When One-shot Position Detection and Reload Timer Underflow ........................... 415

21.5.4.8 When One-shot Position Detection or Reload Timer Underflow ............................. 416

21.5.5 Operation of DTTI Input Control ................................................................................. 417

21.5.6 Operation of Noise Cancellation Function .................................................................. 420

21.5.7 Operation of 16-bit Timer ............................................................................................ 421

21.6 Registers ......................................................................................................................... 426

21.6.1 16-bit MPG Output Control Register (Upper) (OPCUR) ............................................. 427

21.6.2 16-bit MPG Output Control Register (Lower) (OPCLR) .............................................. 429

21.6.3 16-bit MPG Output Data Register (Upper/Lower) (OPDUR/OPDLR) ......................... 431

21.6.3.1 16-bit MPG Output Data Register (Upper) (OPDUR) .............................................. 432

21.6.3.2 16-bit MPG Output Data Register (Lower) (OPDLR) ............................................... 434

21.6.4 16-bit MPG Output Data Buffer Register (Upper/Lower) (OPDBRHx/OPDBRLx) ...... 435

21.6.4.1 16-bit MPG Output Data Buffer Register (Upper) (OPDBRHx) ............................... 436

21.6.4.2 16-bit MPG Output Data Buffer Register (Lower) (OPDBRLx) ................................ 438

21.6.5 16-bit MPG Input Control Register (Upper/Lower) (IPCUR/IPCLR) ........................... 440

21.6.5.1 16-bit MPG Input Control Register (Upper) (IPCUR) ............................................... 441

21.6.5.2 16-bit MPG Input Control Register (Lower) (IPCLR) ............................................... 443

21.6.6 16-bit MPG Compare Clear Register (Upper/Lower) (CPCUR/CPCLR) .................... 445

21.6.7 16-bit MPG Timer Buffer Register (Upper/Lower) (TMBUR/TMBLR) ......................... 446

21.6.8 16-bit MPG Timer Control Status Register (TCSR) .................................................... 447

21.6.9 16-bit MPG Noise Cancellation Control Register (NCCR) .......................................... 449

21.7 Notes on Using Multi-pulse Generator ............................................................................ 450

21.8 Sample Program for Multi-pulse Generator ..................................................................... 452

CHAPTER 22 UART/SIO ..................................................................................... 455

22.1 Overview .......................................................................................................................... 456

22.2 Configuration ................................................................................................................... 457

22.3 Channel ........................................................................................................................... 459

22.4 Pins .................................................................................................................................. 460

22.5 Interrupts ......................................................................................................................... 461

22.6 Operations and Setting Procedure Example ................................................................... 462

22.6.1 Operations in Operation Mode 0 ................................................................................ 463

x

Page 15

22.6.2 Operations in Operation Mode 1 ................................................................................ 470

22.7 Registers ......................................................................................................................... 476

22.7.1 UART/SIO Serial Mode Control Register 1 (SMC1n) ................................................. 477

22.7.2 UART/SIO Serial Mode Control Register 2 (SMC2n) ................................................. 479

22.7.3 UART/SIO Serial Status and Data Register (SSRn) .................................................. 481

22.7.4 UART/SIO Serial Input Data Register (RDRn) ........................................................... 483

22.7.5 UART/SIO Serial Output Data Register (TDRn) ......................................................... 484

CHAPTER 23 UART/SIO DEDICATED BAUD RATE GENERATOR ................ 485

23.1 Overview .......................................................................................................................... 486

23.2 Channel ........................................................................................................................... 487

23.3 Operations ....................................................................................................................... 488

23.4 Registers ......................................................................................................................... 489

23.4.1 UART/SIO Dedicated Baud Rate Generator Prescaler Select Register (PSSRn) ..... 490

23.4.2 UART/SIO Dedicated Baud Rate Generator Baud Rate Setting Register (BRSRn) .. 491

CHAPTER 24 I2C BUS INTERFACE .................................................................. 493

24.1 Overview .......................................................................................................................... 494

24.2 Configuration ................................................................................................................... 495

24.3 Channel ........................................................................................................................... 498

24.4 Pins .................................................................................................................................. 499

24.5 Interrupts ......................................................................................................................... 500

24.6 Operations and Setting Procedure Example ................................................................... 502

24.6.1 l

24.6.2 Function to Wake up the MCU from Standby Mode ................................................... 511

24.7 Registers ......................................................................................................................... 513

24.7.1 I

24.7.2 I

24.7.3 I

24.7.4 I

24.7.5 I

24.7.6 I

24.8 Notes on Using I

2

C Bus Interface ........................................................................................................ 503

2

C Bus Control Register 0 (IBCR0n) ......................................................................... 514

2

C Bus Control Register 1 (IBCR1n) ......................................................................... 517

2

C Bus Status Register (IBSRn) ................................................................................ 521

2

C Data Register (IDDRn) ......................................................................................... 524

2

C Address Register (IAARn) .................................................................................... 525

2

C Clock Control Register (ICCRn) ........................................................................... 526

2

C Bus Interface .................................................................................... 528

CHAPTER 25 DUAL OPERATION FLASH MEMORY ....................................... 531

25.1 Overview .......................................................................................................................... 532

25.2 Sector/Bank Configuration ............................................................................................... 534

25.3 Invoking Flash Memory Automatic Algorithm .................................................................. 535

25.4 Checking Automatic Algorithm Execution Status ............................................................ 537

25.4.1 Data Polling Flag (DQ7) ............................................................................................. 539

25.4.2 Toggle Bit Flag (DQ6) ................................................................................................. 541

25.4.3 Execution Timeout Flag (DQ5) ................................................................................... 542

25.4.4 Sector Erase Timer Flag (DQ3) .................................................................................. 543

25.4.5 Toggle Bit2 Flag (DQ2) ............................................................................................... 544

25.5 Programming/Erasing Flash Memory .............................................................................. 545

25.5.1 Placing Flash Memory in Read/Reset State ............................................................... 546

25.5.2 Programming Data to Flash Memory .......................................................................... 547

25.5.3 Erasing All Data from Flash Memory (Chip Erase) ..................................................... 549

25.5.4 Erasing Specific Data from Flash Memory (Sector Erase) ......................................... 550

xi

Page 16

25.5.5 Suspending Sector Erase from Flash Memory ........................................................... 552

25.5.6 Resuming Sector Erase of Flash Memory .................................................................. 553

25.5.7 Unlock Bypass Program ............................................................................................. 554

25.6 Operations ....................................................................................................................... 555

25.7 Flash Security .................................................................................................................. 557

25.8 Registers ......................................................................................................................... 558

25.8.1 Flash Memory Status Register 2 (FSR2) .................................................................... 559

25.8.2 Flash Memory Status Register (FSR) ......................................................................... 562

25.8.3 Flash Memory Sector Write Control Register 0 (SWRE0) .......................................... 565

25.8.4 Flash Memory Status Register 3 (FSR3) .................................................................... 567

25.8.5 Flash Memory Status Register 4 (FSR4) .................................................................... 568

25.9 Notes on Using Dual Operation Flash Memory ............................................................... 576

CHAPTER 26 NON-VOLATILE REGISTER (NVR) INTERFACE ....................... 577

26.1 Overview .......................................................................................................................... 578

26.2 Configuration ................................................................................................................... 579

26.3 Registers ......................................................................................................................... 580

26.3.1 Main CR Clock Trimming Register (Upper) (CRTH) ................................................... 581

26.3.2 Main CR Clock Trimming Register (Lower) (CRTL) ................................................... 582

26.3.3 Main CR Clock Temperature Dependent Adjustment Register (CRTDA) .................. 583

26.3.4 Watchdog Timer Selection ID Register (Upper/Lower) (WDTH/WDTL) ..................... 584

26.4 Notes on Main CR Clock Trimming ................................................................................. 585

26.5 Notes on Using NVR Interface ........................................................................................ 587

CHAPTER 27 COMPARATOR ............................................................................ 589

27.1 Overview .......................................................................................................................... 590

27.2 Configuration ................................................................................................................... 591

27.3 Pins .................................................................................................................................. 593

27.4 Interrupt ........................................................................................................................... 594

27.5 Operations and Setting Procedure Example ................................................................... 595

27.6 Register ........................................................................................................................... 596

27.6.1 Comparator Control Register (CMR0C) ..................................................................... 597

CHAPTER 28 SYSTEM CONFIGURATION CONTROLLER .............................. 599

28.1 Overview .......................................................................................................................... 600

28.2 Register ........................................................................................................................... 601

28.2.1 System Configuration Register (SYSC) ...................................................................... 602

28.3 Notes on Using Controller ............................................................................................... 604

APPENDIX ............................................................................................................. 605

APPENDIX A Instruction Overview ............................................................................................. 606

A.1 Addressing ...................................................................................................................... 609

A.2 Special Instruction ........................................................................................................... 613

A.3 Bit Manipulation Instructions (SETB, CLRB) ................................................................... 617

A.4 F

A.5 Instruction Map ................................................................................................................ 621

2

MC-8FX Instructions .................................................................................................... 618

xii

Page 17

Major revisions in this edition

A change on a page is indicated by a vertical line drawn on the left of that page.

Page Revisions (For details, see their respective pages.)

ii How to Use This Manual

■ Finding a Function

— CHAPTER 1 NOTES ON DEVICE

HANDLING

21 CHAPTER 3 CLOCK

CONTROLLER

3.1 Overview

■ Standby Mode

22 3.1 Overview

■ Combinations of Clock Mode

and Standby Mode

Table 3.1-3

23 3.1 Overview

■ Combinations of Clock Mode

and Standby Mode

Table 3.1-4

33 3.3.4 Standby Control Register

(STBC)

■ Register Functions

Added the following section.

• Searching from registers

Deleted the entire chapter from the hardware manual.

For details of device handling, refer to "■ PRECAUTIONS

FOR DEVICE HANDLING", "■ NOTES ON DEVICE

HANDLING" and "■ PIN CONNECTION" in the device

data sheet.

Added the following statement.

In every standby mode, two further operating mode options,

normal standby mode and deep standby mode, can be

selected by the deep standby mode control bit in the standby

control register 2 (STBC2:DSTBYX).

Revised the internal operating states of the Flash memory

and RAM.

Added note *6.

Revised the internal operating states of the Flash memory

and RAM.

Added note *6.

Corrected the following heading in the bit function table of

the TMD bit.

In main clock mode or main CR clock mode

→

In main clock mode, main CR clock mode or main CR PLL

clock mode

53 3.5.5 Watch Mode

■ Operations in Watch Mode

● Release from Watch Mode

82 CHAPTER 6 I/O PORT

6.1 Overview

■ Overview

Table 6.1-1

83 6.2 Configuration and Operations of

I/O Port

■ Configuration of I/O Port

84 6.2 Configuration and Operations of

I/O Port

■ Operations of I/O Port

● Operation as an input port

Added the following statement at the end of the section.

However, if a program is being executed on the RAM, no

Flash recovery wait time occurs.

Added details of the A/D input disable register (upper).

Added the following note for the A/D input disable register

(upper) and the A/D input disable register (lower).

Refer to "■ I/O MAP" in the device data sheet for the

availability of the A/D input disable register (upper) and A/D

input disable register (lower).

Added A/D input disable register (upper) (AIDRH).

Revised the following statement.

When using an analog input shared pin as an input port, set

the corresponding bit in the A/D input disable register

(lower) (AIDRL) to "1".

→

When using an analog input shared pin as an input port, set

the corresponding bit in the A/D input disable register

(upper/lower) (AIDRH/AIDRL) to "1".

xiii

Page 18

Page Revisions (For details, see their respective pages.)

85 6.2 Configuration and Operations of

I/O Port

■ Operations of I/O Port

● Operation as an analog input pin

108 CHAPTER 8 HARDWARE/

SOFTWARE WATCHDOG

TIMER

8.4.1 Watchdog Timer Control

Register (WDTC)

■ Register Functions

152 CHAPTER 11 8/16-BIT

COMPOSITE TIMER

11.10 Operation of PWM Timer

Function (Variable-cycle

Mode)

■ Operation of PWM Timer Func-

tion (Variable-cycle Mode)

Figure 11.10-1

162 11.14.1 8/16-bit Composite Timer

Status Control Register 0

(Tn0CR0/Tn1CR0)

■ Register Functions

Revised the following statement.

Set the bit in the DDRx register corresponding to the analog

input pin to "0" and the bit corresponding to that pin in the

AIDRL register to "0".

→

Set the bit in the DDRx register corresponding to the analog

input pin to "0" and the bit corresponding to that pin in the

AIDRH/AIDRL register to "0".

Revised details of "Writing "0101"" of the WTE[3:0] bits in

the bit function table.

Corrected the following register names.

T00DR → Tn0DR

T01DR → Tn1DR

Corrected the bit number in the title of details of the F[3:0]

bits.

[bit3] → [bit3:0]

299 CHAPTER 17 CLOCK

SUPERVISOR COUNTER

17.4.1 Clock Monitoring Data Register (CMDR)

■ Register Functions

323 CHAPTER 18 8/16-BIT PPG

18.7.2 8/16-bit PPG Timer n0 Control Register (PCn0)

■ Register Functions

345 CHAPTER 19 16-BIT PPG TIMER

19.7.1 16-bit PPG Downcounter

Register (Upper/Lower)

(PDCRHn/PDCRLn)

■ Register Functions

362 CHAPTER 20 16-BIT RELOAD

TIMER

20.6 Operations and Setting Procedure Example

■ Setting Procedure Example

448 CHAPTER 21 MULTI-PULSE

GENERATOR

21.6.8 16-bit MPG Timer Control

Status Register (TCSR)

■ Register Functions

Corrected the name of the CMDR[7:0] bits.

Analog input pin select bits → Clock monitoring data bits

Added the following statement to details of the PIE0 bit.

In 16-bit PPG mode, use this bit to control the interrupt

request of the 8/16-bit PPG.

Revised the initial value of the DC06 bit.

1 → 0

Corrected the following register abbreviation.

TMR1 → TMRHn/TMRLn

Corrected the abbreviation of the compare clear interrupt

request flag bit.

PDIF → ICLR

xiv

Page 19

Page Revisions (For details, see their respective pages.)

481 CHAPTER 22 UART/SIO

22.7 UART/SIO Serial Status and

Data Register (SSRn)

■ Register Functions

514

CHAPTER 24 I

2

C BUS

INTERFACE

2

24.7.1 I

C Bus Control Register 0

(IBCR0n)

517

CHAPTER 24 I

2

C BUS

INTERFACE

24.7.2 I

2

C Bus Control Register 1

(IBCR1n)

597 CHAPTER 27 COMPARATOR

27.6.1 Comparator Control Register (CMR0C)

■ Register Functions

Corrected the following register abbreviation in the

respective details of the PER bit, the OVE bit and the FER

bit.

SMR2n → SMC2n

Revised the summary of this section.

Revised the summary of this section.

Revised the initial value of the IF bit.

X → 0

xv

Page 20

xvi

Page 21

CHAPTER 1

MEMORY ACCESS MODE

This chapter describes the memory access

mode.

1.1 Memory Access Mode

MN702-00009-1v0-E FUJITSU SEMICONDUCTOR LIMITED 1

Page 22

CHAPTER 1 MEMORY ACCESS MODE

Address

0xFFFD

Data

0x00

Other than 0x00 Reserved. Do not set mode data to any value other than 0x00.

Selects single-chip mode.

Operation

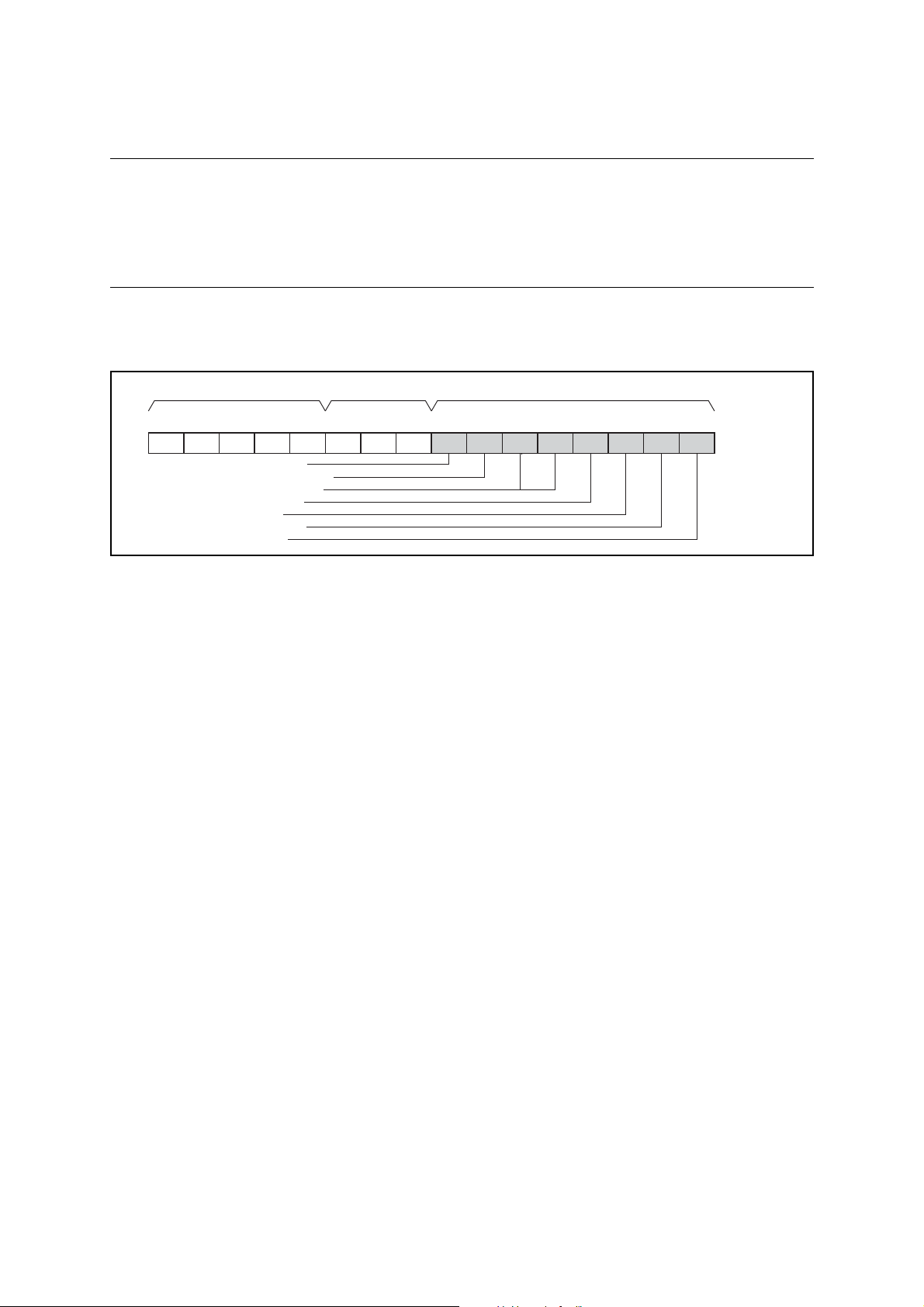

bit7 bit6 bit5 bit4 bit3bit2 bit1 bit0

1.1 Memory Access Mode

MB95630H Series

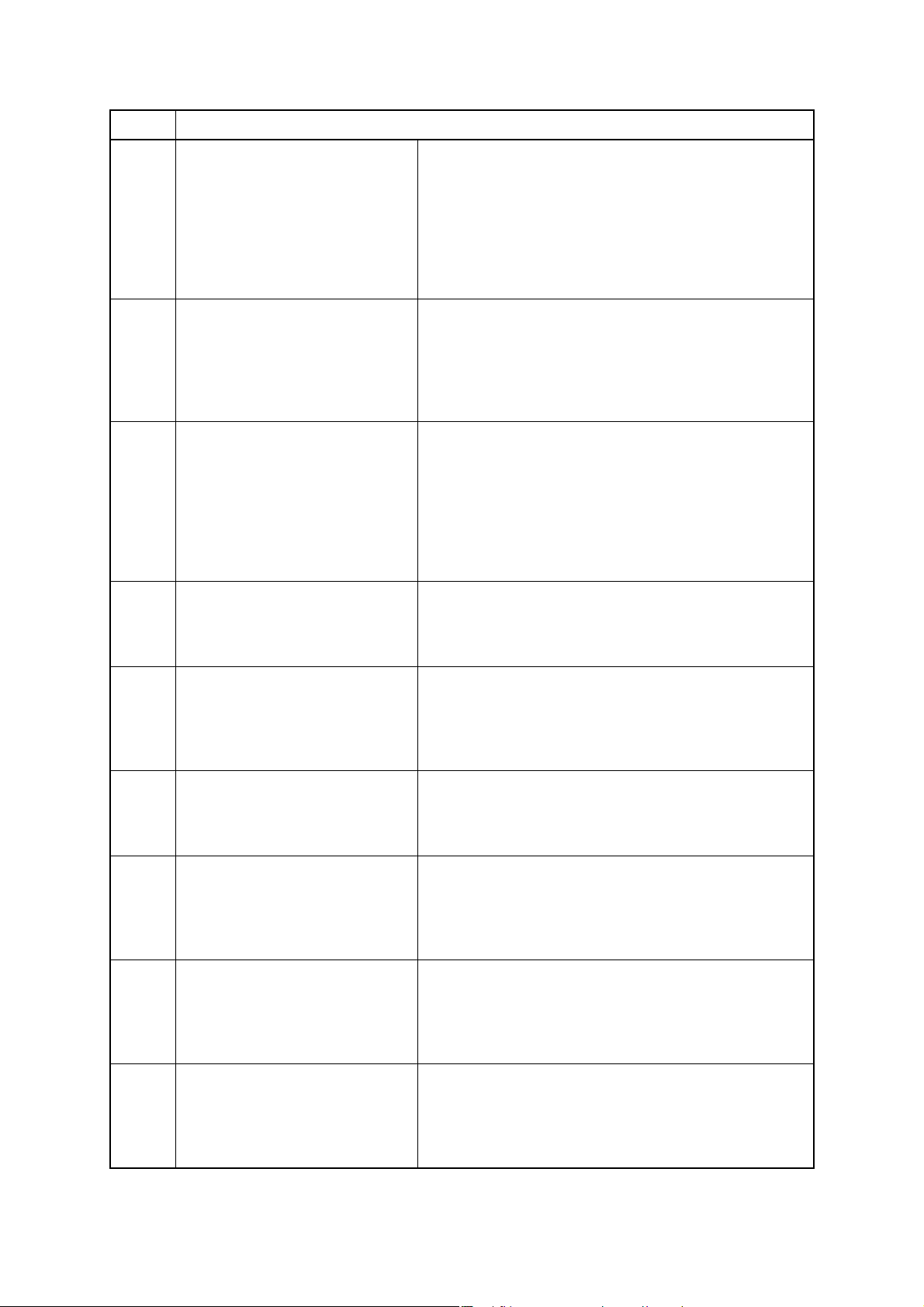

1.1 Memory Access Mode

The MB95630H Series supports only one memory access mode: single-chip

mode.

■ Single-chip Mode

In single-chip mode, only the internal RAM and the Flash memory are used, and no external

bus access is executed.

● Mode data

Mode data is the data used to determine the memory access mode of the CPU.

The mode data address is fixed at "0xFFFD". Always set the mode data of the Flash memory to

"0x00" to select the single-chip mode.

Figure 1.1-1 Mode Data Settings

After a reset is released, the CPU fetches mode data first.

The CPU then fetches the reset vector after the mode data. It starts executing instructions from

the address set in the reset vector.

2 FUJITSU SEMICONDUCTOR LIMITED MN702-00009-1v0-E

Page 23

CHAPTER 2

CPU

This chapter describes the functions and

operations of the CPU.

2.1 Dedicated Registers

2.2 General-purpose Register

2.3 Placement of 16-bit Data in Memory

MN702-00009-1v0-E FUJITSU SEMICONDUCTOR LIMITED 3

Page 24

CHAPTER 2 CPU

Initial value

0xFFFD

Program counter

Indicates the address of the current instruction.

0x0000 Accumulator (A)

Temporary storage register for arithmetic operation and transfer

0x0000

Te mp or ary accumulator (T)

Performs arithmetic operations with the accumulator.

0x0000

Index register

Indicates an index address.

0x0000 Extra pointer

Indicates a memory address.

0x0000 Stack pointer

Indicates the current stack location.

0x0030Program status

Stores a register bank pointer,

a direct bank pointer, and a condition code.

16 bits

PS

SP

EP

IX

PC

TH TL

AH AL

RP DP CCR

:

:

:

:

:

:

:

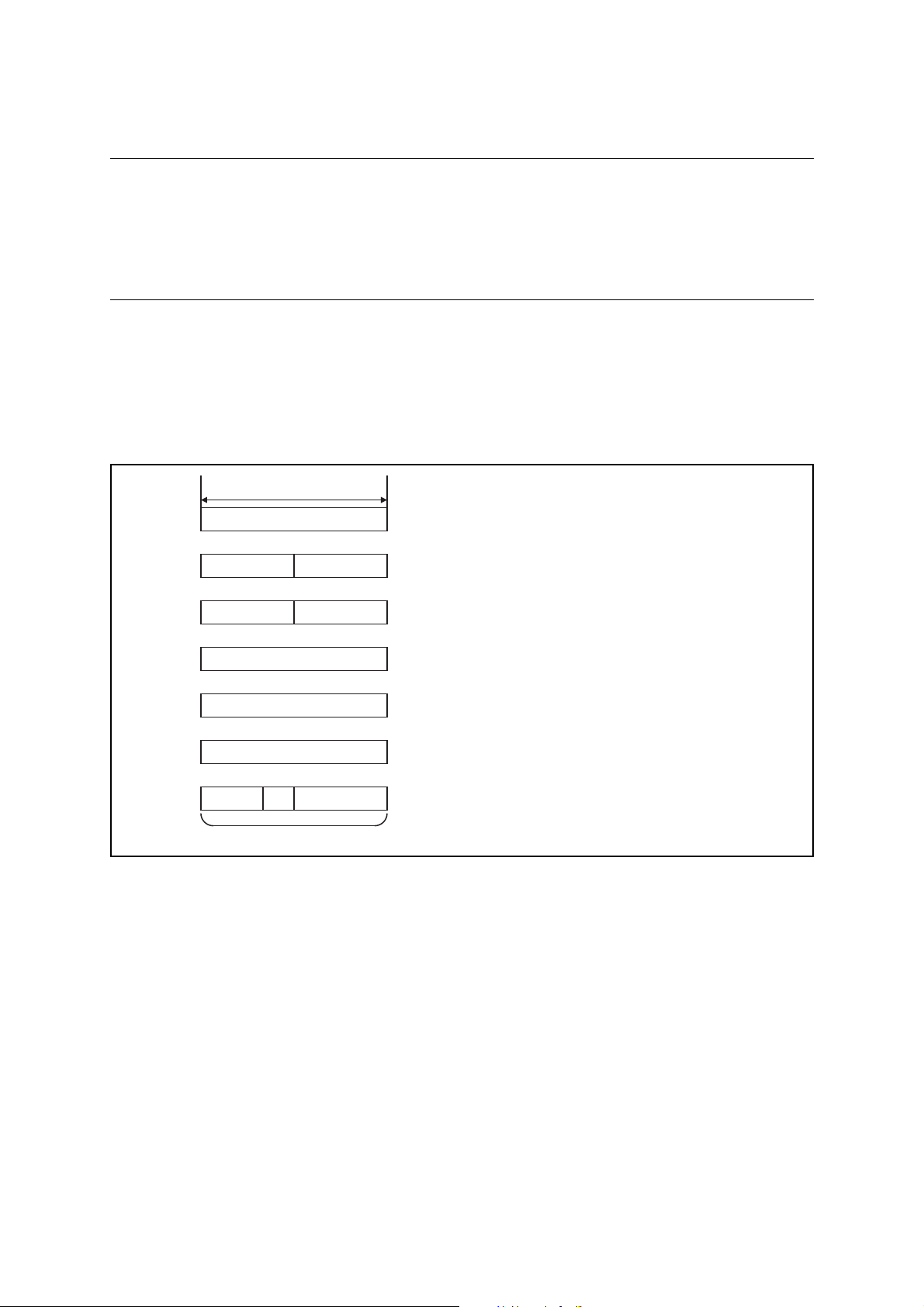

2.1 Dedicated Registers

MB95630H Series

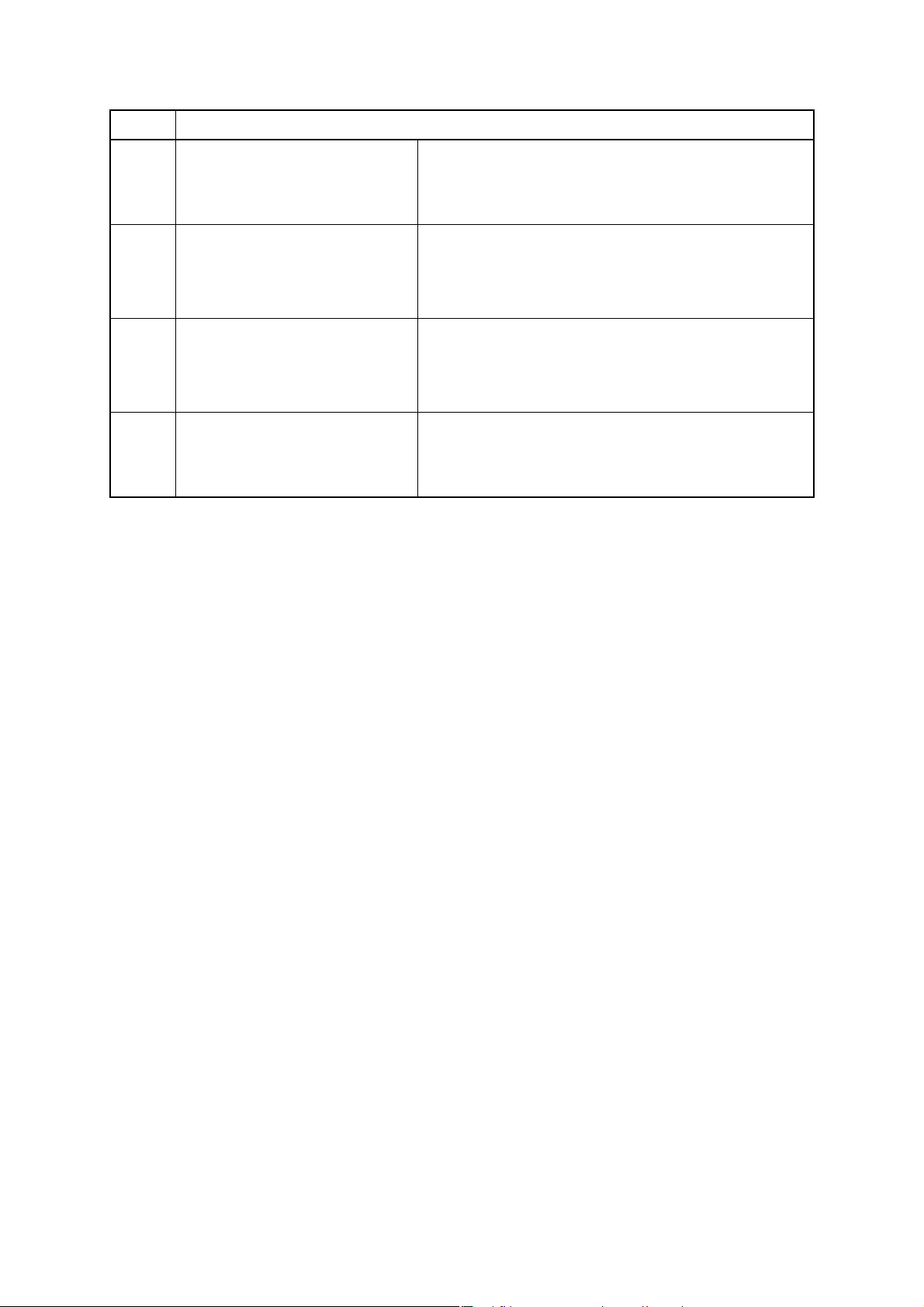

2.1 Dedicated Registers

The CPU has dedicated registers: a program counter (PC), two registers for

arithmetic operations (A and T), three address pointers (IX, EP, and SP), and the

program status (PS) register. Each of the registers is 16 bits long. The PS

register consists of the register bank pointer (RP), direct bank pointer (DP), and

condition code register (CCR).

■ Configuration of Dedicated Registers

The dedicated registers in the CPU consist of seven 16-bit registers. As for the accumulator (A)

and the temporary accumulator (T), using only the lower eight bits of the respective registers is

also supported.

Figure 2.1-1 shows the configuration of the dedicated registers.

Figure 2.1-1 Configuration of Dedicated Registers

■ Functions of Dedicated Registers

Program counter (PC)

●

● Accumulator (A)

4 FUJITSU SEMICONDUCTOR LIMITED MN702-00009-1v0-E

The program counter is a 16-bit counter which contains the memory address of the instruction

currently executed by the CPU. The program counter is updated whenever an instruction is

executed or an interrupt or a reset occurs. The initial value set immediately after a reset is the

mode data read address (0xFFFD).

The accumulator is a 16-bit register for arithmetic operation. It is used for a variety of

arithmetic and transfer operations of data in memory or data in other registers such as the

temporary accumulator (T). The data in the accumulator can be handled either as word (16-bit)

data or byte (8-bit) data. For byte-length arithmetic and transfer operations, only the lower

eight bits (AL) of the accumulator are used with the upper eight bits (AH) left unchanged. The

initial value set immediately after a reset is "0x0000".

Page 25

MB95630H Series

● Temporary accumulator (T)

The temporary accumulator is an auxiliary 16-bit register for arithmetic operation. It is used to

perform arithmetic operations with the data in the accumulator (A). The data in the temporary

accumulator is handled as word data for word-length (16-bit) operations with the accumulator

(A) and as byte data for byte-length (8-bit) operations. For byte-length operations, only the

lower eight bits (TL) of the temporary accumulator are used and the upper eight bits (TH) are

not used.

When a MOV instruction is used to transfer data to the accumulator (A), the previous contents

of the accumulator are automatically transferred to the temporary accumulator. When

transferring byte-length data, the upper eight bits (TH) of the temporary accumulator remain

unchanged. The initial value after a reset is "0x0000".

● Index register (IX)

The index register is a 16-bit register used to hold the index address. The index register is used

with a single-byte offset (-128 to +127). The offset value is added to the index address to

generate the memory address for data access. The initial value after a reset is "0x0000".

● Extra pointer (EP)

CHAPTER 2 CPU

2.1 Dedicated Registers

The extra pointer is a 16-bit register which contains the value indicating the memory address

for data access. The initial value after a reset is "0x0000".

● Stack pointer (SP)

The stack pointer is a 16-bit register which holds the address referenced when an interrupt or a

sub-routine call occurs and by the stack push and pop instructions. During program execution,

the value of the stack pointer indicates the address of the most recent data pushed onto the

stack. The initial value after a reset is "0x0000".

● Program status (PS)

The program status is a 16-bit control register. The upper eight bits consists of the register bank

pointer (RP) and direct bank pointer (DP); the lower eight bits consists of the condition code

register (CCR).

In the upper eight bits, the upper five bits consists of the register bank pointer used to contain

the address of the general-purpose register bank. The lower three bits consists of the direct

bank pointer which locates the area to be accessed at high-speed by direct addressing.

The lower eight bits consists of the condition code register (CCR) which consists of flags that

represent the state of the CPU.

The instructions that can access the program status are "MOVW A,PS" and "MOVW PS,A".

The register bank pointer (RP) and direct bank pointer (DP) in the program status register can

also be read from and written to by accessing the mirror address (0x0078).

Note that the condition code register (CCR) is a part of the program status register and cannot

be accessed independently.

Refer to the "F

2

MC-8FX Programming Manual" for details on using the dedicated registers.

MN702-00009-1v0-E FUJITSU SEMICONDUCTOR LIMITED 5

Page 26

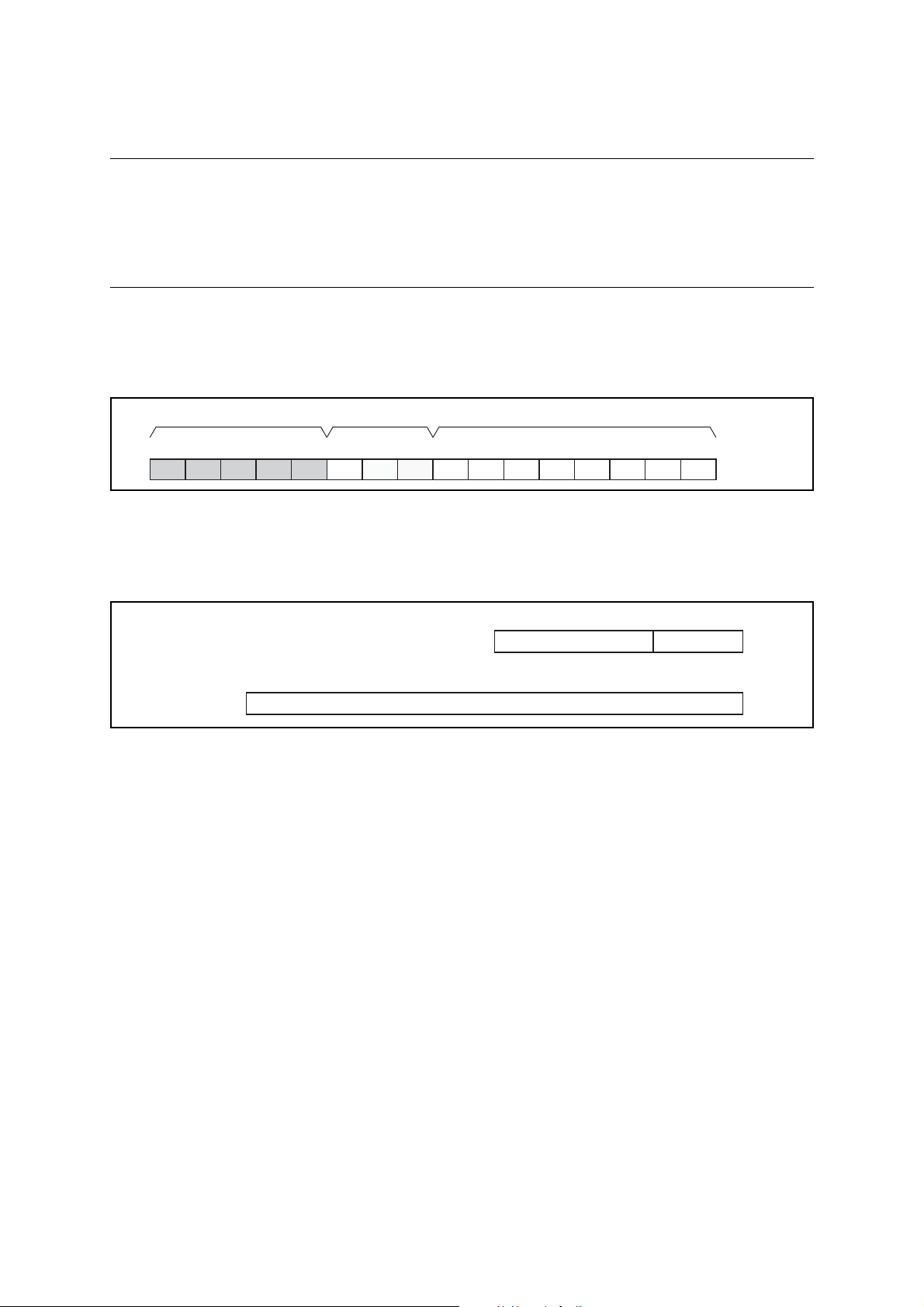

CHAPTER 2 CPU

CCRDPRP

PS 0b00000

RP

initial value

R4 R3 R2 R1 R0 DP2 DP1 DP0 H I IL1 IL0 N Z V C

bit15 bit14 bit13bit12 bit11 bit10 bit9 bit8bit7 bit6 bit5 bit4 bit3bit2 bit1 bit0

2.1 Dedicated Registers

MB95630H Series

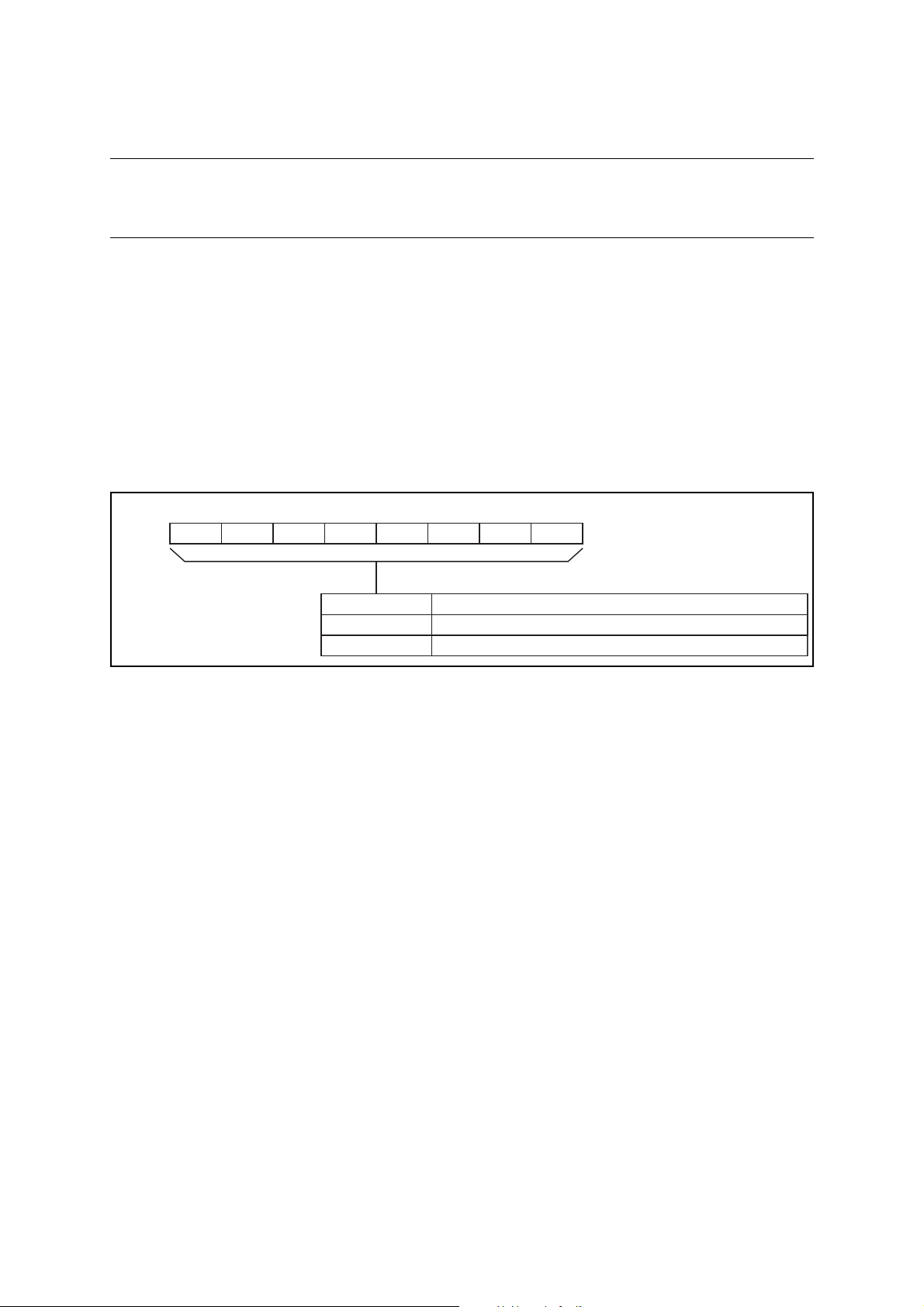

2.1.1 Register Bank Pointer (RP)

The register bank pointer (RP) in bit15 to bit11 of the program status (PS)

register contains the address of the general-purpose register bank that is

currently in use and is translated into a real address when general-purpose

register addressing is used.

■ Configuration of Register Bank Pointer (RP)

Figure 2.1-2 shows the configuration of the register bank pointer.

Figure 2.1-2 Configuration of Register Bank Pointer

The register bank pointer contains the address of the register bank currently in use. The content

of the register bank pointer is translated into a real address according to the rule shown in

Figure 2.1-3.

Figure 2.1-3 Rule for Translation into Real Addresses in General-purpose Register Area

Fixed value RP: Upper Op-code: Lower

Generated

address

“0” “0”

↓↓↓↓↓↓↓↓↓↓↓↓↓↓↓↓

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

“0” “0” “0” “0” “0” “1” R4 R3 R2 R1 R0 b2 b1 b0

The register bank pointer specifies the register bank used as general-purpose registers in the

RAM area. There are a total of 32 register banks, which are specified by setting a value

between 0 and 31 in the upper five bits of the register bank pointer. Each register bank has

eight 8-bit general-purpose registers which are selected by the lower three bits of the op-code.

The register bank pointer allows the space from "0x0100" to "0x01FF"(max) to be used as a

general-purpose register area. However, certain products have restrictions on the size of the

area available for the general-purpose register area. The initial value of the register bank

pointer after a reset is "0x0000".

■ Mirror Address for Register Bank and Direct Bank Pointer

Values can be written to the register bank pointer (RP) and the direct bank pointer (DP) by

accessing the program status (PS) register with the "MOVW PS,A" instruction; the two

pointers can be read by accessing PS with the "MOVW A,PS" instruction. Values can also be

directly written to and read from the two pointers by accessing "0x0078", the mirror address of

the register bank pointer.

6 FUJITSU SEMICONDUCTOR LIMITED MN702-00009-1v0-E

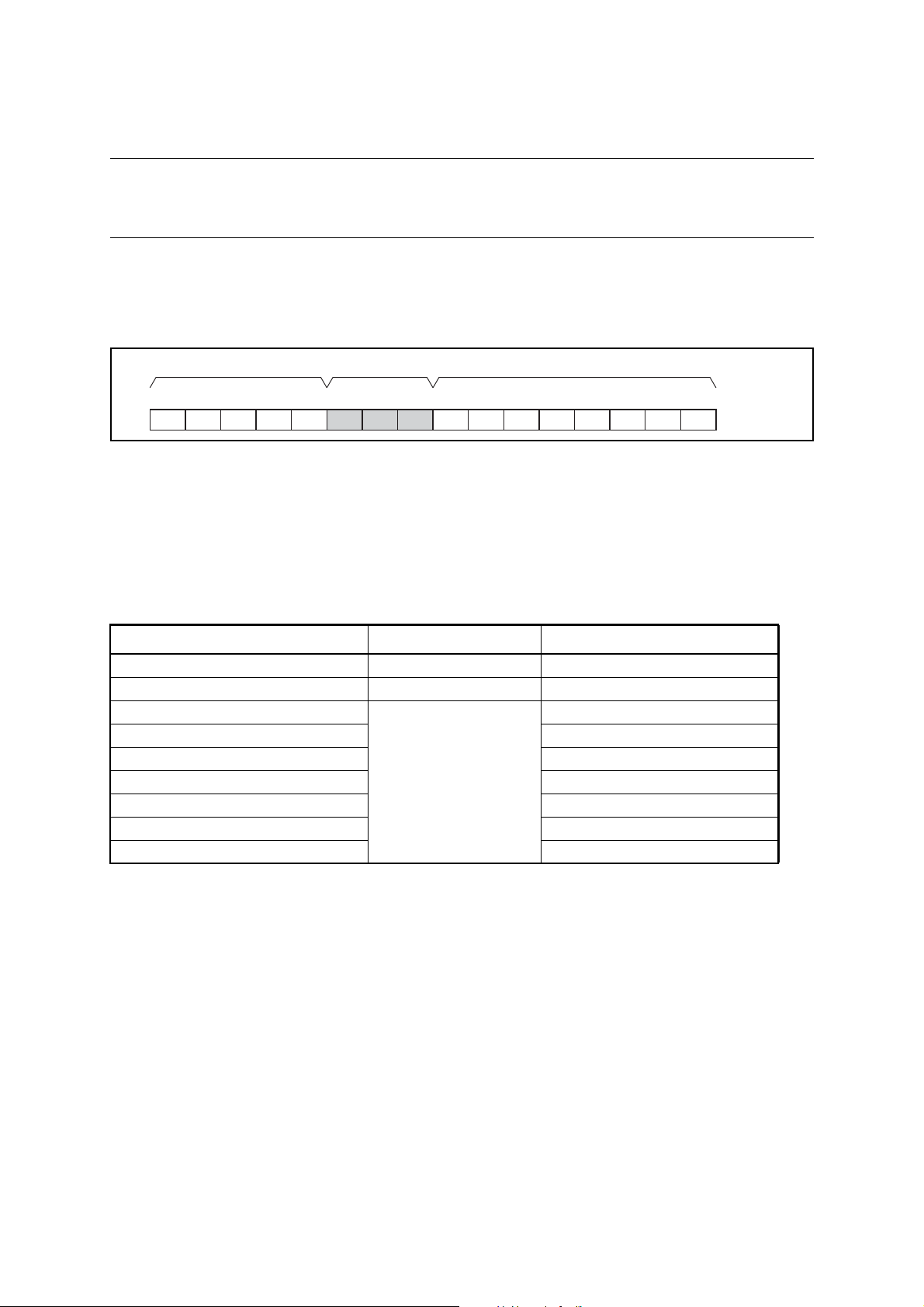

Page 27

CHAPTER 2 CPU

CCRDPRP

PS 0b000

DP

initial value

R4 R3 R2 R1 R0 DP2 DP1 DP0 H I IL1 IL0 N Z V C

bit15 bit14 bit13bit12 bit11 bit10 bit9 bit8bit7 bit6 bit5 bit4 bit3bit2 bit1 bit0

MB95630H Series

2.1 Dedicated Registers

2.1.2 Direct Bank Pointer (DP)

The direct bank pointer (DP) in bit10 to bit8 of the program status (PS) register

specifies the area to be accessed by direct addressing.

■ Configuration of Direct Bank Pointer (DP)

Figure 2.1-4 shows the configuration of the direct bank pointer.

Figure 2.1-4 Configuration of Direct Bank Pointer

The area of "0x0000 to 0x007F" and that of "0x0090 to 0x047F" can be accessed by direct

addressing. Access to 0x0000 to 0x007F is specified by an operand regardless of the value in

the direct bank pointer. Access to 0x0090 to 0x047F is specified by the value of the direct bank

pointer and the operand.

Table 2.1-1 shows the relationship between the direct bank pointer (DP) and the access area;

Table 2.1-2 lists the direct addressing instructions.

Table 2.1-1 Direct Bank Pointer and Access Area

Direct bank pointer (DP[2:0]) Operand-specified dir Access area*

0bXXX (It does not affect mapping.) 0x0000 to 0x007F 0x0000 to 0x007F

0b000 (Initial value) 0x0090 to 0x00FF 0x0090 to 0x00FF

0b001

0b010 0x0180 to 0x01FF

0b011 0x0200 to 0x027F

0b100 0x0280 to 0x02FF

0b101 0x0300 to 0x037F

0b110 0x0380 to 0x03FF

0b111 0x0400 to 0x047F

*: The available access area varies among products. For details, refer to the device data sheet.

0x0080 to 0x00FF

0x0100 to 0x017F

MN702-00009-1v0-E FUJITSU SEMICONDUCTOR LIMITED 7

Page 28

CHAPTER 2 CPU

2.1 Dedicated Registers

Table 2.1-2 Direct Address Instruction List

MB95630H Series

Applicable instructions

CLRB dir:bit

SETB dir:bit

BBC dir:bit,rel

BBS dir:bit,rel

MOV A,dir

CMP A,dir

ADDC A,dir

SUBC A,dir

MOV dir,A

XOR A,dir

AND A,dir

OR A,dir

MOV dir,#imm

CMP dir,#imm

MOVW A,dir

MOVW dir,A

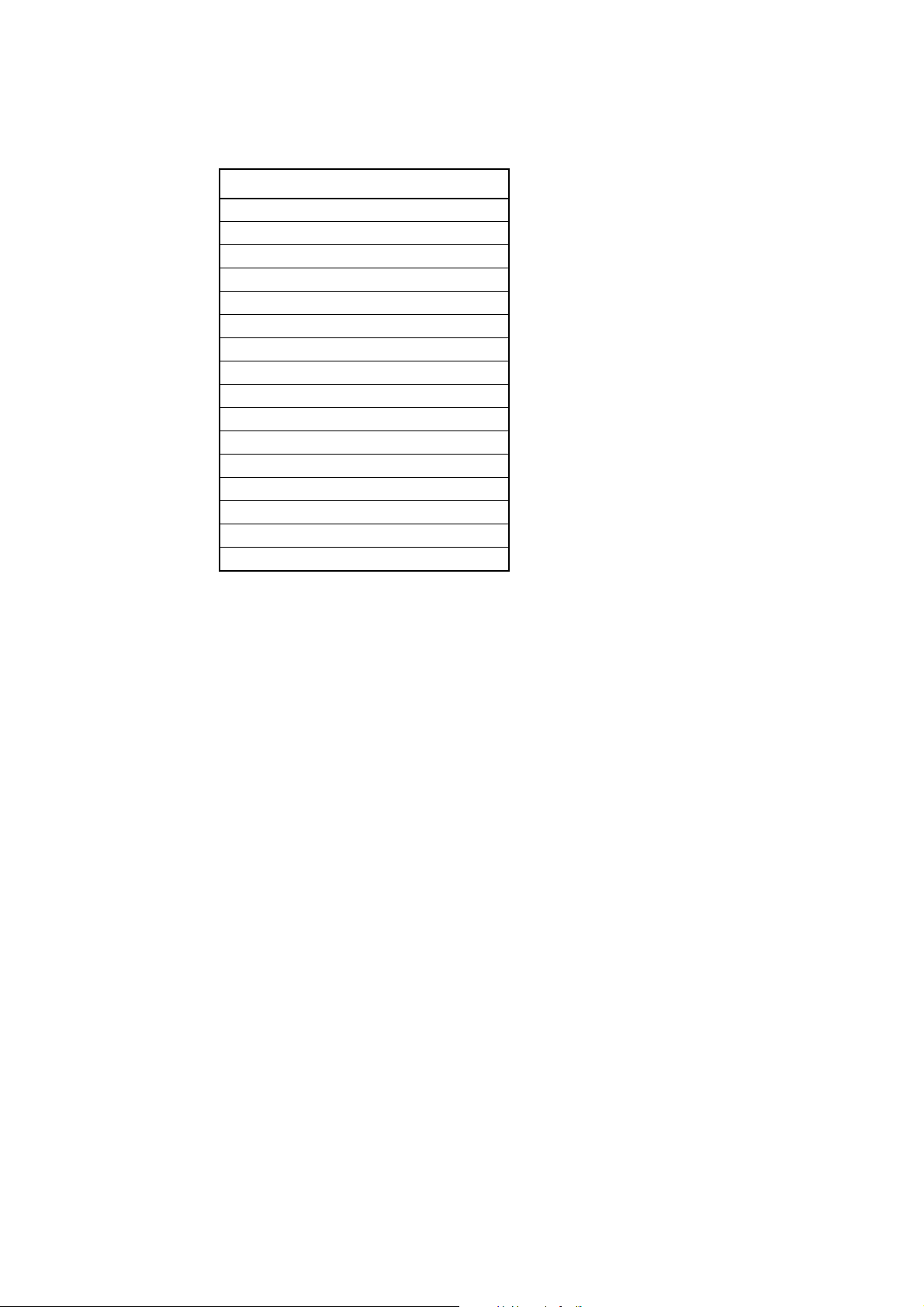

8 FUJITSU SEMICONDUCTOR LIMITED MN702-00009-1v0-E

Page 29

CHAPTER 2 CPU

MB95630H Series

2.1 Dedicated Registers

2.1.3 Condition Code Register (CCR)

The condition code register (CCR) in the lower eight bits of the program status

(PS) register consists of the bits (H, N, Z, V, and C) containing information

about the arithmetic result or transfer data and the bits (I, IL1, and IL0) used to

control the acceptance of interrupt requests.

■ Configuration of Condition Code Register (CCR)

Figure 2.1-5 Configuration of Condition Code Register (CCR)

CCRDPRP

bit15 bit14 bit13bit12 bit11 bit10 bit9 bit8bit7 bit6 bit5 bit4 bit3bit2 bit1 bit0

R4 R3 R2 R1 R0 DP2 DP1 DP0 H I IL1 IL0 N Z V C

PS 0b00110000

Half carry flag

Interrupt enable flag

Interrupt level bits

Negative flag

Zero flag

OVerflow flag

Carry flag

CCR

initial value

The condition code register is a part of the program status (PS) register and therefore cannot be

accessed independently.

■ Bits Showing Operation Results

● Half carry flag (H)

This flag is set to "1" when a carry from bit3 to bit4 or a borrow from bit4 to bit3 occurs due to

the result of an operation. Otherwise, the flag is set to "0". Do not use this flag for any

operation other than addition and subtraction as the flag is intended for decimal-adjusted

instructions.

● Negative flag (N)

This flag is set to "1" when the value of the most significant bit is "1" due to the result of an

operation, and is set to "0" when the value of the most significant bit is "0".

● Zero flag (Z)

This flag is set to "1" when the result of an operation is "0", and is set to "0" when the result of

an operation is a value other than "0".

● Overflow flag (V)

This flag indicates whether the result of an operation has caused an overflow, with the operand

used in the operation being regarded as an integer expressed as a complement of two. If an

overflow occurs, the overflow flag is set to "1"; otherwise, it is set to "0".

MN702-00009-1v0-E FUJITSU SEMICONDUCTOR LIMITED 9

Page 30

CHAPTER 2 CPU

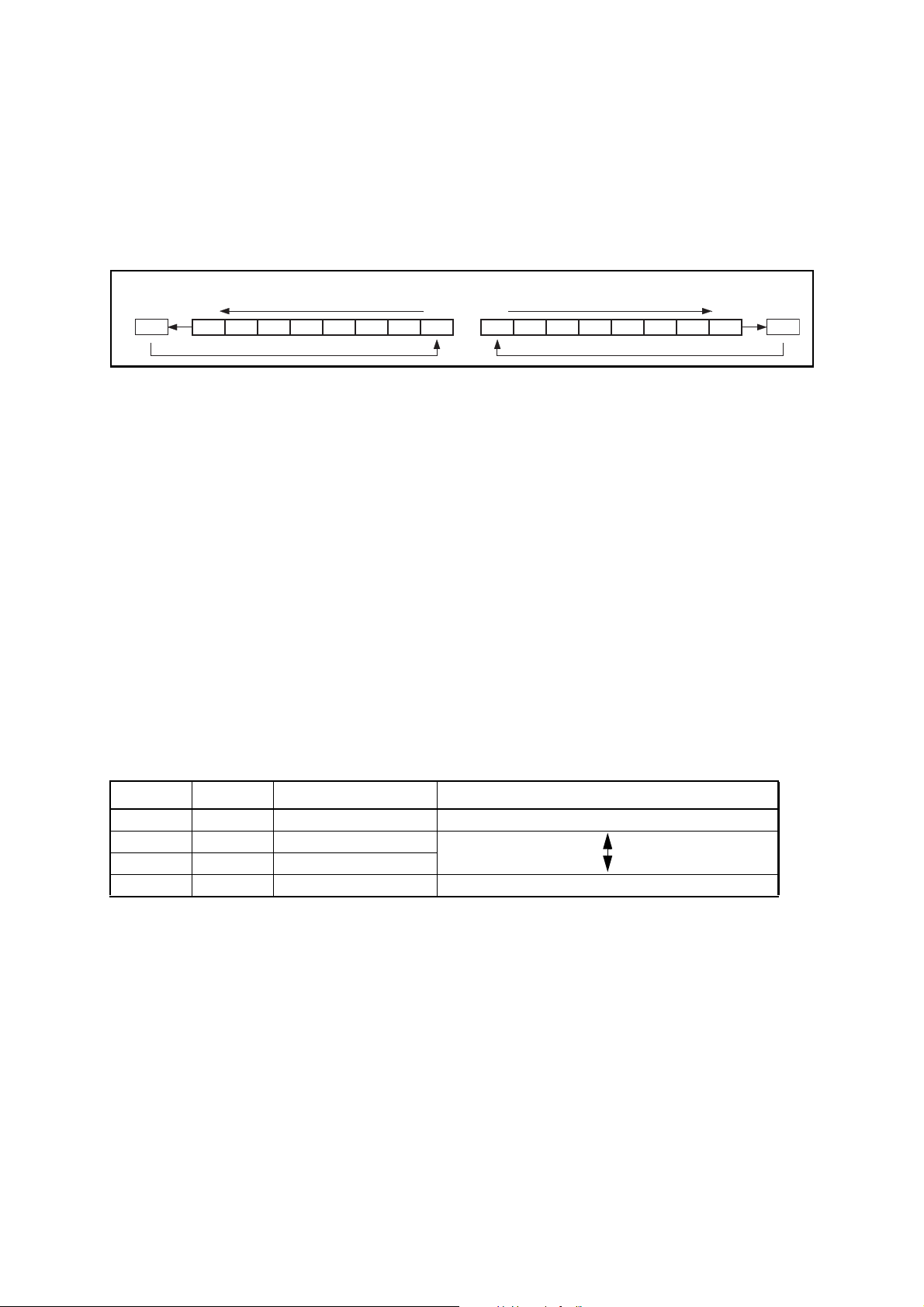

Right-shift (RORC)•Left-shift (ROLC)•

bit0bit7

C

bit0bit7

C

2.1 Dedicated Registers

● Carry flag (C)

This flag is set to "1" when a carry from bit7 or a borrow to bit7 occurs due to the result of an

operation. Otherwise, the flag is set to "0". When a shift instruction is executed, the flag is set

to the shift-out value.

Figure 2.1-6 shows how the carry flag is updated by a shift instruction.

Figure 2.1-6 Carry Flag Updated by Shift Instruction

■ Interrupt Acceptance Control Bits

● Interrupt enable flag (I)

When this flag is set to "1", interrupts are enabled and accepted by the CPU. When this flag is

set to "0", interrupts are disabled and rejected by the CPU.

The initial value after a reset is "0".

The SETI and CLRI instructions set and clear the flag to "1" and "0", respectively.

MB95630H Series

● Interrupt level bits (IL[1:0])

These bits indicate the level of the interrupt currently accepted by the CPU.

The interrupt level is compared with the value of the interrupt level setting register (ILR0 to

ILR5) that corresponds to the interrupt request (IRQ00 to IRQ23) of each peripheral function.

The CPU services an interrupt request only when its interrupt level is smaller than the value of

these bits with the interrupt enable flag set (CCR:I = 1). Table 2.1-3 lists interrupt level

priorities. The initial value after a reset is "0b11".

Table 2.1-3 Interrupt Levels

IL1 IL0 Interrupt level Priority

00 0 High

01 1

10 2

1 1 3 Low (No interrupt)

The interrupt level bits (IL[1:0]) are usually "0b11" when the CPU does not service an interrupt

(with the main program running).

For details of interrupts, see "5.1 Interrupts".

10 FUJITSU SEMICONDUCTOR LIMITED MN702-00009-1v0-E

Page 31

CHAPTER 2 CPU

MB95630H Series

2.2 General-purpose Register

2.2 General-purpose Register

The general-purpose registers are a memory block in which each bank consists

of eight 8-bit registers. Up to 32 register banks can be used in total. The

register bank pointer (RP) is used to specify a register bank.

Register banks are useful for interrupt handling, vector call processing, and

sub-routine calls.

■ Configuration of General-purpose Register

• The general-purpose register is an 8-bit register and is located in a register bank in the

general-purpose register area (in RAM).

• Up to 32 banks can be used, each of which consists of eight registers (R0 to R7).

• The register bank pointer (RP) specifies the register bank currently being used and the lower

three bits of the op-code specify the general-purpose register 0 (R0) to the general-purpose

register 7 (R7).

Figure 2.2-1 shows the configuration of the register banks.

Figure 2.2-1 Configuration of Register Banks

This address = 0x0100 + 8 × (RP)

Address 0x100

For information on the general-purpose register area available on each product, see "■ AREAS

FOR SPECIFIC APPLICATIONS" in the device data sheet.

0x107

R0

R1

R2

R3

R4

R5

R6

R7

Bank 0

Memory area

R0

R1

R2

R3

R4

R5

R6

R7

8 bits

R0

R1

R2

R3

R4

R5

R6

R7

0x1F8

0x1FF

Bank 31

32 banks

The number of banks

available is restricted by

the available RAM size.

MN702-00009-1v0-E FUJITSU SEMICONDUCTOR LIMITED 11

Page 32

CHAPTER 2 CPU

2.2 General-purpose Register

■ Features of General-purpose Registers

The general-purpose register has the following features.

• High-speed access to RAM with short instructions (general-purpose register addressing).

• Grouping registers into a block of register banks facilitates data protection and division of

registers in terms of functions.

A general-purpose register bank can be allocated exclusively to an interrupt service routine or a

vector call (CALLV #0 to #7) processing routine. For instance, the fourth register bank is

always assigned to the second interrupt.

Data of a general-purpose register before an interrupt can be saved to a dedicated register bank

by just specifying that register bank at the beginning of an interrupt service routine. This

therefore eliminates the need to save data of a general-purpose register in a stack, thereby

enabling the CPU to receive interrupts at high speed.

Note:

In an interrupt service routine, include one of the following in a program to ensure that

values of the interrupt level bits (CCR:IL[1:0]) of the condition code register are not

modified when modifying a register bank pointer (RP) to specify a register bank.