Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

F2MC-8FX

8-BIT MICROCONTROLLER

MB95170J Series

HARDWARE MANUAL

Version 1.0

Page 2

Page 3

FUJITSU LIMITED

F2MC-8FX

8-BIT MICROCONTROLLER

MB95170J Series

HARDWARE MANUAL

“Check Sheet” is seen at the following support page

URL : http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

“Check Sheet” lists the minimal requirement items to be checked to prevent problems beforehand in system

development.

Be sure to refer to the “Check Sheet” for the latest cautions on development.

Page 4

Page 5

i

PREFACE

■ The Purpose and Intended Readership of This Manual

Thank you very much for your continued special support for Fujitsu semiconductor products .

The MB95170J series is a line of products developed as general-purpose products in the F2MC-FX series

of proprietary 8-bit single-chip microcontrollers applicable as application-specific integrated circuits

(ASICs). The MB95170J series can be used for a wide range of applications from consumer products

including portable devices to industrial equipment.

Intended for engineers who actually develop products using the MB95170J series of microcontrollers, this

manual describes its functions, features, and operations. You should read through the manual.

For details o n individual instru ctions, refer to the "F

2

MC-8FX Programming Manua l" .

Note: F2MC is the abbreviation of FUJITSU Flexible Microcontroller.

■ License

Purchase of Fujitsu I2C components conveys a license under the Philips I2C Patent Rights to use, these

components in an I

2

C system provided that the system conforms to the I2C Standard Specification as

defined by Philips.

■ Sample Programs

Fujitsu provides sample programs free of charge to operate the peripheral resources of the F2MC-8FX

family of microcontrollers. Feel free to use such sample programs to check the operational specifications

and usages of Fujits u mi crocontrollers.

Microcontroller support information:

http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

* Note that sample programs are subject to change without notice. As these pieces of software are offered

to show standard operations and usages, evaluate them sufficiently before use with your system. Fujitsu

assumes no liability for any damages whatsoeve r arising out of the use of sample progra ms.

Page 6

ii

Copyright©2006 FU JITSU LIMITED All rights reserved

• The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales

representatives before ordering.

• The information, such as descriptions of function and application circuit examples, in this document are presented solely

for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not

warrant proper operation of the device with respect to use based on such information. When you develop equipment

incorporating the device based on such information, you must assume any responsibility arising out of such use of the

inform at ion. Fuji ts u as su m e s n o lia b i l ity fo r an y dam a g es wh a ts oever ari si ng out of the us e of the info rm a ti o n.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as

license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of

Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other

right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other

rights of third partie s which would result from the use of information contained herein.

• The products described in this document are designed, developed and manufactured as contemplated for general use,

including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not

designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless

extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury,

severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic

control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use

requiring extremely high reliability (i.e., submersible repeater and artificial satellite). Please note that Fujitsu will not be

liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the

products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such

failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and

prevention of over-current levels an d other abnormal operating conditions.

• If any products described in this document represent goods or technologies subject to certain restrictions on export under

the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for

export of those products from Japan.

Page 7

iii

CONTENTS

CHAPTER 1 DESCRIPTION ............................................................................................. 1

1.1 Feature of MB95170J Series .............................................................................................................. 2

1.2 Product Lineup of MB95170J Series .................................................................................................. 4

1.3 Difference Among Products and Notes on Selecting Products ......................................................... 7

1.4 Block Diagram of MB95170J Series ................................................................................................... 9

1.5 Pin Assignment ................................................................................................................................. 10

1.6 Package Dimension .......................................................................................................................... 11

1.7 Pin Description .................................................................................................................................. 13

1.8 I/O Circuit Type ................................................................................................................................. 17

CHAPTER 2 HANDLING DEVICES ................................................................................ 21

2.1 Device Handling Precautions ............................................................................................................ 22

CHAPTER 3 MEMORY SPACE ...................................................................................... 25

3.1 Memory Space .................................................................................................................................. 26

3.2 Memory Map ..................................................................................................................................... 28

CHAPTER 4 MEMORY ACCESS MODE ........................................................................ 29

4.1 Memory Access Mode ...................................................................................................................... 30

CHAPTER 5 CPU ............................................................................................................ 31

5.1 Dedicated Registers ......................................................................................................................... 32

5.1.1 Register Bank Pointer (RP) ......................................................................................................... 34

5.1.2 Direct Bank Pointer (DP) ............................................................................................................. 35

5.1.3 Condition Code Register (CCR) .................................................................................................. 37

5.2 General-purpose Registers ............................................................................................................... 39

5.3 Placement of 16-bit Data in Memory ................................................................................................ 41

CHAPTER 6 CLOCK CONTROLLER ............................................................................. 43

6.1 Overview of Clock Controller ............................................................................................................ 44

6.2 Oscillation Stabilization Wait Time .................................................................................................... 50

6.3 System Clock Control Register (SYCC) ........................................................................................... 52

6.4 PLL Control Register (PLLC) ............................................................................................................ 54

6.5 Oscillation Stabilization Wait Time Setting Register (WATR) ........................................................... 56

6.6 Standby Control Register (STBC) ..................................................................................................... 60

6.7 Clock Modes ..................................................................................................................................... 63

6.8 Operations in Low-power Consumption Modes (Standby Modes) ................................................... 67

6.8.1 Notes on Using Standby Mode .................................................................................................... 68

6.8.2 Sleep Mode ................................................................................................................................. 72

6.8.3 Stop Mode ................................................................................................................................... 73

6.8.4 Timebase Timer Mode ................................................................................................................. 74

6.8.5 Watch Mode ................................................................................................................................ 75

Page 8

iv

6.9 Clock Oscillator Circuits .................................................................................................................... 76

6.10 Overview of Prescaler ....................................................................................................................... 78

6.11 Configuration of Prescaler ................................................................................................................ 79

6.12 Operating Explanation of Prescaler .................................................................................................. 80

6.13 Notes on Use of Prescaler ................................................................................................................ 81

CHAPTER 7 RESET ........................................................................................................ 83

7.1 Reset Operation ................................................................................................................................ 84

7.2 Reset Source Register (RSRR) ........................................................................................................ 88

CHAPTER 8 INTERRUPTS ............................................................................................. 91

8.1 Interrupts ........................................................................................................................................... 92

8.1.1 Interrupt Level Setting Registers (ILR0 to ILR5) .......................................................................... 94

8.1.2 Interrupt Processing .................................................................................................................... 95

8.1.3 Nested Interrupts ......................................................................................................................... 97

8.1.4 Interrupt Processing Time ........................................................................................................... 98

8.1.5 Stack Operations During Interrupt Processing ............................................................................ 99

8.1.6 Interrupt Processing Stack Area ................................................................................................ 100

CHAPTER 9 I/O PORT .................................................................................................. 101

9.1 Overview of I/O Ports ...................................................................................................................... 102

9.2 Port 0 .............................................................................................................................................. 104

9.2.1 Port 0 Registers ......................................................................................................................... 106

9.2.2 Operations of Port 0 .................................................................................................................. 107

9.3 Port 1 .............................................................................................................................................. 109

9.3.1 Port 1 Registers ......................................................................................................................... 112

9.3.2 Operations of Port 1 .................................................................................................................. 113

9.4 Port 4 .............................................................................................................................................. 115

9.4.1 Port 4 Registers ......................................................................................................................... 117

9.4.2 Operations of Port 4 .................................................................................................................. 118

9.5 Port 5 .............................................................................................................................................. 120

9.5.1 Port 5 Registers ......................................................................................................................... 122

9.5.2 Operations of Port 5 .................................................................................................................. 123

9.6 Port 6 .............................................................................................................................................. 125

9.6.1 Port 6 Registers ......................................................................................................................... 127

9.6.2 Operations of Port 6 .................................................................................................................. 128

9.7 Port 9 .............................................................................................................................................. 130

9.7.1 Port 9 Registers ......................................................................................................................... 132

9.7.2 Operations of Port 9 .................................................................................................................. 133

9.8 Port A .............................................................................................................................................. 135

9.8.1 Port A Registers ........................................................................................................................ 137

9.8.2 Operations of Port A .................................................................................................................. 138

9.9 Port B .............................................................................................................................................. 140

9.9.1 Port B Registers ........................................................................................................................ 142

9.9.2 Operations of Port B .................................................................................................................. 143

9.10 Port C .............................................................................................................................................. 145

9.10.1 Port C Registers ........................................................................................................................ 147

Page 9

v

9.10.2 Operations of Port C .................................................................................................................. 148

9.11 Port E .............................................................................................................................................. 150

9.11.1 Port E Registers ........................................................................................................................ 152

9.11.2 Operations of Port E .................................................................................................................. 153

CHAPTER 10 TIMEBASE TIMER ................................................................................... 155

10.1 Overview of Timebase Timer .......................................................................................................... 156

10.2 Configuration of Timebase Timer ................................................................................................... 158

10.3 Registers of the Timebase Timer .................................................................................................... 161

10.3.1 Timebase Timer Control Register (TBTC) ................................................................................. 162

10.4 Interrupts of Timebase Timer .......................................................................................................... 164

10.5 Explanation of Timebase Timer Operations and Setup Procedure Example ................................. 166

10.6 Precautions when Using Timebase Timer ...................................................................................... 169

CHAPTER 11 WATCHDOG TIMER ................................................................................ 171

11.1 Overview of Watchdog Timer ......................................................................................................... 172

11.2 Configuration of Watchdog Timer ................................................................................................... 173

11.3 Registers of the Watchdog Timer ................................................................................................... 175

11.3.1 Watchdog Timer Control Register (WDTC) ............................................................................... 176

11.4 Explanation of Watchdog Timer Operations and Setup Procedure Example ................................. 178

11.5 Precautions when Using Watchdog Timer ...................................................................................... 180

CHAPTER 12 HARDWARE WATCHDOG TIMER .......................................................... 181

12.1 Overview of Hardware Watchdog Timer ......................................................................................... 182

12.2 Configuration of Hardware Watchdog Timer .................................................................................. 183

12.3 Registers of the Hardware Watchdog Timer ................................................................................... 185

12.3.1 Hardware Watchdog Timer Control Register (HWDC) .............................................................. 186

12.4 Explanation of Hardware Watchdog Timer Operations and Setup Procedure Example ................ 188

12.5 Precautions when Using Hardware Watchdog Timer ..................................................................... 190

CHAPTER 13 WATCH PRESCALER ............................................................................. 191

13.1 Overview of Watch Prescaler ......................................................................................................... 192

13.2 Configuration of Watch Prescaler ................................................................................................... 193

13.3 Registers of the Watch Prescaler ................................................................................................... 195

13.3.1 Watch Prescaler Control Register (WPCR) ............................................................................... 196

13.4 Interrupts of Watch Prescaler ......................................................................................................... 198

13.5 Explanation of Watch Prescaler Operations and Setup Procedure Example ................................. 200

13.6 Precautions when Using Watch Prescaler ...................................................................................... 202

13.7 Sample Programs for Watch Prescaler .......................................................................................... 203

CHAPTER 14 WATCH COUNTER .................................................................................. 205

14.1 Overview of Watch Counter ............................................................................................................ 206

14.2 Configuration of Watch Counter ..................................................................................................... 207

14.3 Registers of Watch Counter ............................................................................................................ 209

14.3.1 Watch Counter Data Register (WCDR) ..................................................................................... 210

14.3.2 Watch Counter Control Register (WCSR) ................................................................................. 212

14.4 Interrupts of Watch Counter ............................................................................................................ 214

Page 10

vi

14.5 Explanation of Watch Counter Operations and Setup Procedure Example ................................... 215

14.6 Precautions when Using Watch Counter ........................................................................................ 217

14.7 Sample Programs for Watch Counter ............................................................................................. 218

CHAPTER 15 WILD REGISTER ..................................................................................... 219

15.1 Overview of Wild Register .............................................................................................................. 220

15.2 Configuration of Wild Register ........................................................................................................ 221

15.3 Registers of Wild Register .............................................................................................................. 223

15.3.1 Wild Register Data Setup Registers (WRDR0 to WRDR2) ....................................................... 225

15.3.2 Wild Register Address Setup Registers (WRAR0 to WRAR2) .................................................. 226

15.3.3 Wild Register Address Compare Enable Register (WREN) ...................................................... 227

15.3.4 Wild Register Data Test Setup Register (WROR) ..................................................................... 228

15.4 Operating Description of Wild Register ........................................................................................... 229

15.5 Typical Hardware Connection Example .......................................................................................... 230

CHAPTER 16 8/16-BIT COMPOSITE TIMER ................................................................. 231

16.1 Overview of 8/16-bit Composite Timer ........................................................................................... 232

16.2 Configuration of 8/16-bit Composite Timer ..................................................................................... 234

16.3 Channels of 8/16-bit Composite Timer ........................................................................................... 237

16.4 Pins of 8/16-bit Composite Timer ................................................................................................... 238

16.5 Registers of 8/16-bit Composite Timer ........................................................................................... 239

16.5.1 8/16-bit Composite Timer 00/01 Control Status Register 0 (T00CR0/T01CR0) ........................ 240

16.5.2 8/16-bit Composite Timer 00/01 Control Status Register 1 (T00CR1/T01CR1) ........................ 244

16.5.3 8/16-bit Composite Timer 00/01 Timer Mode Control Register (TMCR0) ................................. 248

16.5.4 8/16-bit Composite Timer 00/01 Data Register (T00DR/T01DR) .............................................. 251

16.6 Interrupts of 8/16-bit Composite Timer ........................................................................................... 254

16.7 Operating Description of Interval Timer Function (One-shot Mode) ............................................... 256

16.8 Operating Description of Interval Timer Function (Continuous Mode) ............................................ 258

16.9 Operating Description of Interval Timer Function (Free-run Mode) ................................................ 260

16.10 Operating Description of PWM Timer Function (Fixed-cycle mode) ............................................... 262

16.11 Operating Description of PWM Timer Function (Variable-cycle Mode) .......................................... 264

16.12 Operating Description of PWC Timer Function ............................................................................... 266

16.13 Operating Description of Input Capture Function ........................................................................... 268

16.14 Operating Description of Noise Filter .............................................................................................. 270

16.15 States in Each Mode during Operation ........................................................................................... 271

16.16 Precautions when Using 8/16-bit Composite Timer ........................................................................ 273

CHAPTER 17 16-BIT PPG TIMER .................................................................................. 275

17.1 Overview of 16-bit PPG Timer ........................................................................................................ 276

17.2 Configuration of 16-bit PPG Timer .................................................................................................. 277

17.3 Channels of 16-bit PPG Timer ........................................................................................................ 278

17.4 Pins of 16-bit PPG Timer ................................................................................................................ 279

17.5 Registers of 16-bit PPG Timer ........................................................................................................ 282

17.5.1 16- bit PPG Down Counter Registers (PDCRH0, PDCRL0) ...................................................... 284

17.5.2 16-bit PPG Cycle Setting Buffer Registers (PCSRH0, PCSRL0) .............................................. 285

17.5.3 16-bit PPG Duty Setting Buffer Registers (PDUTH0, PDUTL0) ................................................ 286

17.5.4 16-bit PPG Status Control Register (PCNTH0, PCNTL0) ......................................................... 288

Page 11

vii

17.6 Interrupts of 16-bit PPG Timer ........................................................................................................ 292

17.7 Explanation of 16-bit PPG Timer Operations and Setup Procedure Example ................................ 293

17.8 Precautions when Using 16-bit PPG Timer .................................................................................... 297

17.9 Sample Programs for 16-bit PPG Timer ......................................................................................... 298

CHAPTER 18 EXTERNAL INTERRUPT CIRCUIT ......................................................... 303

18.1 Overview of External Interrupt Circuit ............................................................................................. 304

18.2 Configuration of External Interrupt Circuit ....................................................................................... 305

18.3 Channels of External Interrupt Circuit ............................................................................................. 306

18.4 Registers of External Interrupt Circuit ............................................................................................. 307

18.4.1 External Interrupt Control Register (EIC00) ............................................................................... 308

18.5 Interrupts of External Interrupt Circuit ............................................................................................. 310

18.6 Explanation of External Interrupt Circuit Operations and Setup Procedure Example ..................... 311

18.7 Precautions when Using External Interrupt Circuit ......................................................................... 313

18.8 Sample Programs for External Interrupt Circuit .............................................................................. 314

CHAPTER 19 INTERRUPT PIN SELECTION CIRCUIT ................................................. 317

19.1 Overview of Interrupt Pin Selection Circuit ..................................................................................... 318

19.2 Configuration of Interrupt Pin Selection Circuit ............................................................................... 319

19.3 Pins of Interrupt Pin Selection Circuit ............................................................................................. 320

19.4 Registers of Interrupt Pin Selection Circuit ..................................................................................... 321

19.4.1 Interrupt Pin Selection Circuit Control Register (WICR) ............................................................ 322

19.5 Operating Description of Interrupt Pin Selection Circuit ................................................................. 325

19.6 Precautions when Using Interrupt Pin Selection Circuit ................................................................. 326

CHAPTER 20 UART/SIO ................................................................................................. 327

20.1 Overview of UART/SIO ................................................................................................................... 328

20.2 Configuration of UART/SIO ............................................................................................................ 329

20.3 Channels of UART/SIO ................................................................................................................... 331

20.4 Pins of UART/SIO ........................................................................................................................... 332

20.5 Registers of UART/SIO ................................................................................................................... 333

20.5.1 UART/SIO Serial Mode Control Register 1 (SMC10) ................................................................ 334

20.5.2 UART/SIO Serial Mode Control Register 2 (SMC20) ................................................................ 336

20.5.3 UART/SIO Serial Status and Data Register (SSR0) ................................................................. 338

20.5.4 UART/SIO Serial Input Data Register (RDR0) .......................................................................... 340

20.5.5 UART/SIO Serial Output Data Register (TDR0) ........................................................................ 341

20.6 Interrupts of UART/SIO ................................................................................................................... 342

20.7 Explanation of UART/SIO Operations and Setup Procedure Example .......................................... 343

20.7.1 Operating Description of Operation Mode 0 .............................................................................. 344

20.7.2 Operating Description of Operation Mode 1 .............................................................................. 351

20.8 Sample Programs for UART/SIO .................................................................................................... 357

CHAPTER 21 UART/SIO DEDICATED BAUD RATE GENERATOR ............................. 361

21.1 Overview of UART/SIO Dedicated Baud Rate Generator .............................................................. 362

21.2 Channels of UART/SIO Dedicated Baud Rate Generator .............................................................. 363

21.3 Registers of UART/SIO Dedicated Baud Rate Generator .............................................................. 364

21.3.1 UART/SIO Dedicated Baud Rate Generator Prescaler Selection Register (PSSR) .................. 365

Page 12

viii

21.3.2 UART/SIO Dedicated Baud Rate Generator Baud Rate Setting Register (BRSR) ................... 366

21.4 Operating Description of UART/SIO Dedicated Baud Rate Generator ........................................... 367

CHAPTER 22 I2C ............................................................................................................. 369

22.1 Overview of I2C ............................................................................................................................... 370

22.2 I

2

C Configuration ............................................................................................................................ 371

22.3 I

2

C Channels .................................................................................................................................. 374

22.4 I

2

C Bus Interface Pins .................................................................................................................... 375

22.5 I

2

C Registers .................................................................................................................................. 377

22.5.1 I

2

C Bus Control Registers (IBCR00, IBCR10) ........................................................................... 378

22.5.2 I

2

C Bus Status Register (IBSR0) ............................................................................................... 386

22.5.3 I

2

C Data Register (IDDR0) ........................................................................................................ 388

22.5.4 I

2

C Address Register (IAAR0) ................................................................................................... 389

22.5.5 I

2

C Clock Control Register (ICCR0) .......................................................................................... 390

22.6 I

2

C Interrupts .................................................................................................................................. 392

22.7 I

2

C Operations and Setup Procedure Examples ............................................................................ 395

22.7.1 l

2

C Interface ............................................................................................................................... 396

22.7.2 Function to Wake up the MCU from Standby Mode .................................................................. 403

22.8 Notes on Use of I

2

C ........................................................................................................................ 405

22.9 Sample Programs for I

2

C ................................................................................................................ 407

CHAPTER 23 10-BIT A/D CONVERTER ........................................................................ 411

23.1 Overview of 10-bit A/D Converter ................................................................................................... 412

23.2 Configuration of 10-bit A/D Converter ............................................................................................. 413

23.3 Pins of 10-bit A/D Converter ........................................................................................................... 415

23.4 Registers of 10-bit A/D Converter ................................................................................................... 417

23.4.1 A/D Control Register 1 (ADC1) .................................................................................................. 418

23.4.2 A/D Control Register 2 (ADC2) .................................................................................................. 420

23.4.3 A/D Data Registers (ADDH, ADDL) ........................................................................................... 422

23.5 Interrupts of 10-bit A/D Converter ................................................................................................... 423

23.6 Operations of 10-bit A/D Converter and Its Setup Procedure Examples ........................................ 424

23.7 Notes on Use of 10-bit A/D Converter ............................................................................................ 427

23.8 Sample Programs for 10-bit A/D Converter .................................................................................... 428

CHAPTER 24 LCD CONTROLLER ................................................................................. 431

24.1 Overview of LCD Controller ............................................................................................................ 432

24.2 Configuration of LCD Controller ...................................................................................................... 433

24.2.1 Internal Driver Resistors for LCD Controller .............................................................................. 435

24.2.2 External Divider Resistors for LCD Controller ........................................................................... 437

24.3 Pins of LCD Controller .................................................................................................................... 439

24.4 Registers of LCD Controller ............................................................................................................ 445

24.4.1 LCDC Control Register (LCDCC) .............................................................................................. 446

24.4.2 LCDC Enable Register 1 (LCDCE1) .......................................................................................... 448

24.4.3 LCD Enable Registers 2 to 5 (LCDCE2 to 5) ............................................................................ 450

24.4.4 LCDC Blinking Setting Registers 1/2 (LCDCB1/2) .................................................................... 451

24.5 LCD Controller Display RAM .......................................................................................................... 452

24.6 Operations of LCD Controller ......................................................................................................... 453

Page 13

ix

24.6.1 Output Waveform during LCD Controller Operation (1/2 Duty) ................................................. 455

24.6.2 Output Waveform during LCD Controller Operation (1/3 Duty) ................................................. 457

24.6.3 Output Waveform during LCD Controller Operation (1/4 Duty) ................................................. 459

24.7 Notes on Use of LCD Controller ..................................................................................................... 461

CHAPTER 25 LOW-VOLTAGE DETECTION RESET CIRCUIT ..................................... 463

25.1 Overview of Low-voltage Detection Reset Circuit ........................................................................... 464

25.2 Configuration of Low-voltage Detection Reset Circuit .................................................................... 465

25.3 Pins of Low-voltage Detection Reset Circuit ................................................................................... 466

25.4 Operations of Low-voltage Detection Reset Circuit ........................................................................ 467

CHAPTER 26 CLOCK SUPERVISOR ............................................................................. 469

26.1 Overview of Clock Supervisor ......................................................................................................... 470

26.2 Configuration of Clock Supervisor .................................................................................................. 471

26.3 Registers of Clock Supervisor ........................................................................................................ 473

26.3.1 Clock Supervisor Control Register (CSVCR) ............................................................................ 474

26.4 Operations of Clock Supervisor ...................................................................................................... 476

26.5 Precautions when Using Clock Supervisor ..................................................................................... 479

CHAPTER 27 REAL TIME CLOCK ................................................................................. 481

27.1 Overview of Real time clock ........................................................................................................... 482

27.2 Configuration of Real Time Clock ................................................................................................... 483

27.3 Registers of Real Time Clock ......................................................................................................... 487

27.3.1 Real Time Clock Control Register Upper (RTCCRH) ................................................................ 489

27.3.2 Real Time Clock Control Register Lower (RTCCRL) ................................................................. 494

27.3.3 Minute Compare Register (MICR) ............................................................................................. 496

27.3.4 Hour Compare Register (HRCR) ............................................................................................... 497

27.3.5 Day Compare Register (DYCR) ................................................................................................ 498

27.3.6 Month Compare Register (MOCR) ............................................................................................ 499

27.3.7 Second register (SECR) ............................................................................................................ 500

27.3.8 Minute Register (MINR) ............................................................................................................. 501

27.3.9 Hour Register (HOUR) .............................................................................................................. 502

27.3.10 Day of the Week Register (DOWR) ........................................................................................... 503

27.3.11 Day Register (DAYR) ................................................................................................................ 504

27.3.12 Month Register (MONR) ............................................................................................................ 505

27.3.13 Year Register (YEAR) ............................................................................................................... 506

27.3.14 Frequency Fine-tuning Register (FFTR) .................................................................................... 507

27.3.15 Auto-Calibration Control Register (CALCR) .............................................................................. 510

27.4 Real Time Clock Interrupt ............................................................................................................... 512

27.5 Operation of the Real Time Clock ................................................................................................... 513

27.6 Notes on using RTC ....................................................................................................................... 517

CHAPTER 28 256-KBIT FLASH MEMORY .................................................................... 519

28.1 Overview of 256-Kbit Flash Memory ............................................................................................... 520

28.2 Sector Configuration of Flash Memory ........................................................................................... 521

28.3 Register of Flash Memory ............................................................................................................... 523

28.3.1 Flash Memory Status Register (FSR) ........................................................................................ 524

Page 14

x

28.4 Starting the Flash Memory Automatic Algorithm ............................................................................ 526

28.5 Checking the Automatic Algorithm Execution Status ...................................................................... 528

28.5.1 Data Polling Flag (DQ7) ............................................................................................................ 530

28.5.2 Toggle Bit Flag (DQ6) ................................................................................................................ 531

28.5.3 Execution Time-out Flag (DQ5) ................................................................................................. 532

28.5.4 Toggle Bit 2 Flag (DQ2) ............................................................................................................. 533

28.6 Details of Programming/Erasing Flash Memory ............................................................................. 534

28.6.1 Placing Flash Memory in the Read/Reset State ........................................................................ 535

28.6.2 Programming Data into Flash Memory ...................................................................................... 536

28.6.3 Erasing All Data from Flash Memory (Chip Erase) .................................................................... 538

28.7 Features of Flash Security .............................................................................................................. 539

CHAPTER 29 EXAMPLE OF SERIAL PROGRAMMING CONNECTION ...................... 541

29.1 Basic Configuration of MB95170J Serial Programming Connection ............................................. 542

29.2 Example of Serial Programming Connection .................................................................................. 545

29.3 Example of Minimum Connection to Flash Microcomputer Programmer ....................................... 547

APPENDIX ......................................................................................................................... 551

APPENDIX A I/O Map ................................................................................................................................ 552

APPENDIX B Table of Interrupt Causes .................................................................................................... 558

APPENDIX C Instruction Overview ............................................................................................................ 559

APPENDIX D Mask Option ........................................................................................................................ 575

APPENDIX E Writing to Flash Microcontroller Using Parallel Writer .......................................................... 576

Page 15

1

CHAPTER 1

DESCRIPTION

This chapter explains a feature and a basic specification

of the MB95170J series.

1.1 Feature of MB95170J Series

1.2 Product Lineup of MB95170J Series

1.3 Difference Among Products and Notes on Selecting Products

1.4 Block Diagram of MB95170J Series

1.5 Pin Assignment

1.6 Package Dimension

1.7 Pin Description

1.8 I/O Circuit Type

Page 16

2

CHAPTER 1 DESCRIPTION

1.1 Feature of MB95170J Series

In addition to a compact instruction set, the MB95170J series is a general-purpose

single-chip microcontroller built-in abundant peripheral functions.

■ Feature of MB95170J Series

●

F2MC-8FX CPU core

Instruction system opt imized for controllers

• Multiplication and division instructions

• 16-bit arithmetic operation

• Bit test branc h in st r u ct ion

• Bit operation instructions etc.

● Clock

•Main clock

• Main PLL clock

• Subclock

● Timer

• 8/16-bit compound timer x 2 channels

• 16-bit PPG x 8 channel s

• Timeb a s e ti mer

• Watch pr e scaler

● UART/SIO

• With full-du plex double buffer

• An asynchronous (UART) clock or a synchronous(SIO) serial data transfer capable

● I

2

C

• Built-in wake up function

● External interrupt

• Interrupt by the edge detection (Select rising edge/falling edge/both edges)

• Can be used to recover from low-power consumption (standby) mode

● 10-bit A/D converter

• 10-bit resolutions x 8 channels

● LCD controller (LCDC)

• 28 SEG x 4 COM

• built-in Resistor Ladder

Page 17

3

CHAPTER 1 DESCRIPTION

● Low-power consumption (standby) mode

• Stop mode

•Sleep mode

• Watch mo d e

• Timeb a s e ti mer mode

● Real Time Clock(RTC)

• Time with inf ormation of second, minute, hour, day of the week, day, month and year

• Automatic leap - y ea r adj u stment

• Two differe nt calibraion methods

● I/O port: Max 54

• General-purpose I/O ports (N-ch open drain) : 2

• General-purpose I/O ports (CMOS) : 52

● Programmable input voltage levels of port

Automotive input level / CMOS input level / Hysteresis input level

● Flash memory security function

Protects the content of Flash memory(Flash memory device only)

* : Purchase of Fujitsu I

2

C components conveys a license under the Philips I2C Patent Rights to use, these components in an

I

2

C system provided tha t the system conforms to the I2C Standard Specification as defined by Philips.

Page 18

4

CHAPTER 1 DESCRIPTION

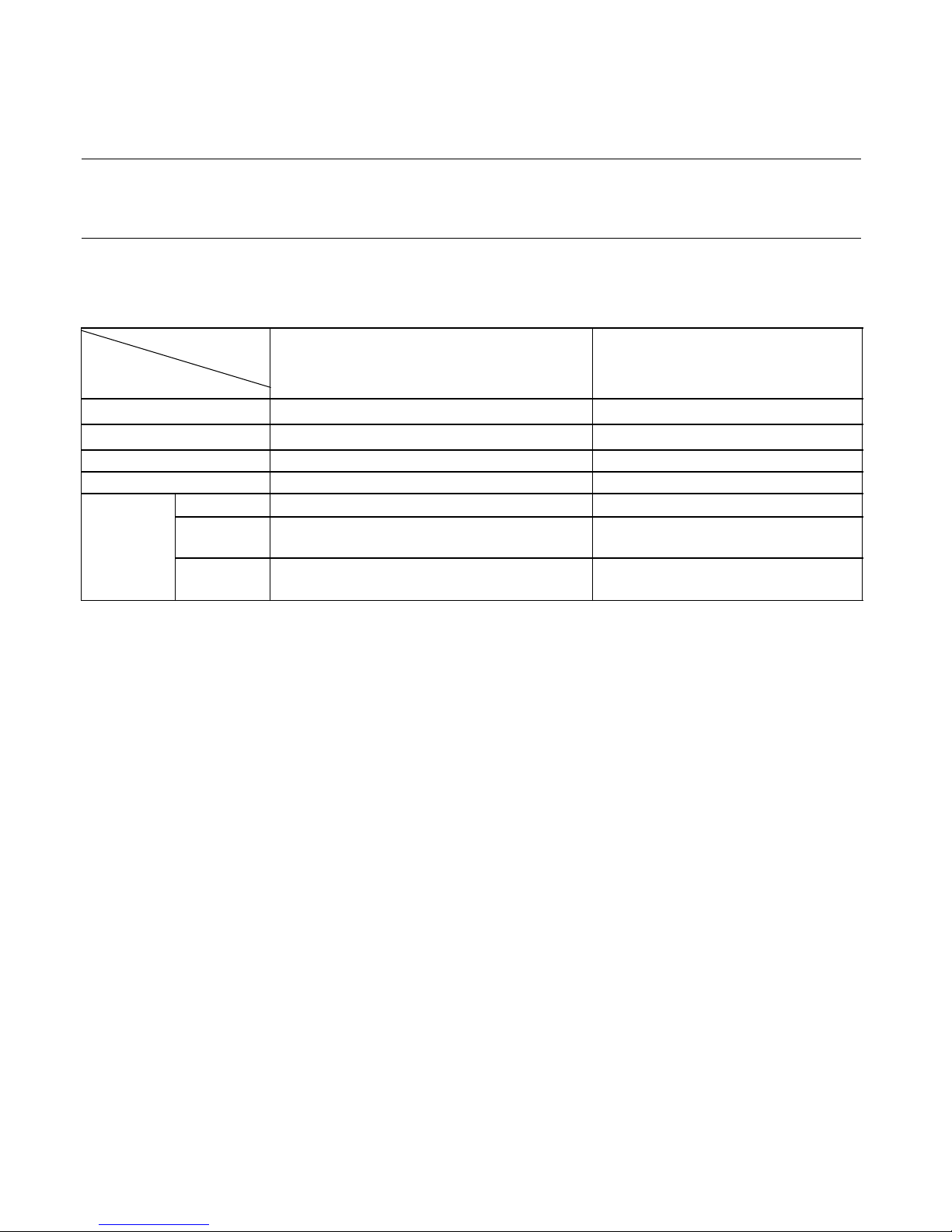

1.2 Product Lineup of MB95170J Series

MB95170J series is available in two types. Table 1.2-1 lists the product lineup and Table

1.2-2 lists the CPUs and peripheral functions.

■ Product Lineup of MB95170J Series

Table 1.2-1 Product Lineup of MB95170J Series

Part Number

Parameter

MB95F176JS MB95F176JW

Type

Flash memory pr oduct Flash memory product

ROM capacity

32K(MAX) 32K(MAX)

RAM capacity 1K (MAX) 1K (MAX)

Reset outpu t No No

Option

Clock syst em

Single Clock Dual Clock

Low voltag e

detection reset

Yes Yes

Clock

superv isor

Yes Yes

Page 19

5

CHAPTER 1 DESCRIPTION

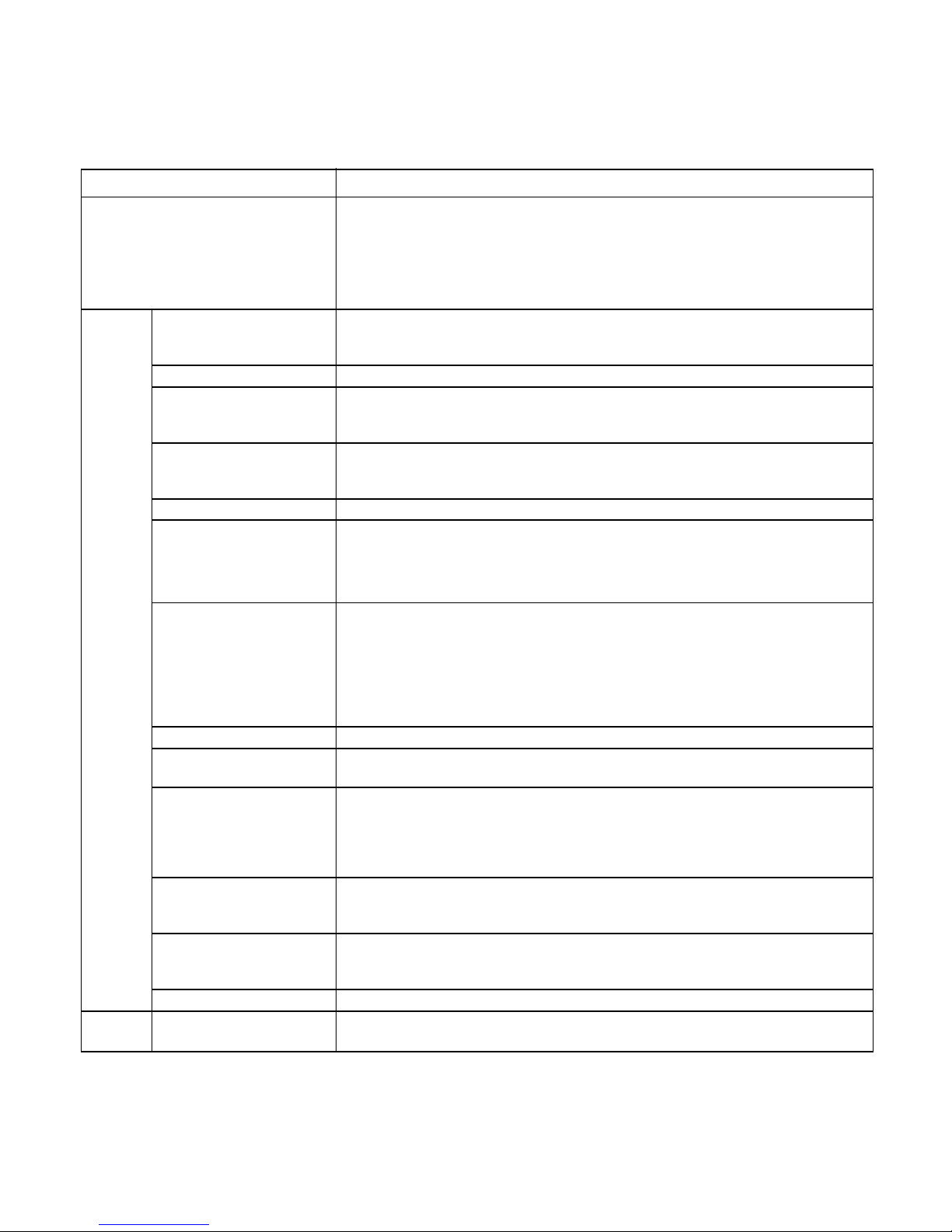

Table 1.2-2 CPU and Peripheral Function of MB95170J Series

Item Specification

CPU function

Number of basic instructions: 136 instructions

Instruction bit length: 8 bits

Instruction length: 1 to 3 bytes

Data bit length: 1, 8, and 16 bits

Minimum instruction exe cution time: 0.1μs (at machine clock 10 MHz)

Interrupt processing time: 0.9μs (at machine clock 10 MHz)

Peripheral

function

Port

General-purpose I/O ports (N-ch open drain): 2

General-purpose I/O ports (CMOS) : 52

To tal : 54 (M ax)

Timebase timer Interrupt cycle: 0.5 ms, 2.1 ms, 8. 2 m s, 32.8 ms (at main oscillation clock 4 MHz)

Watchdog timer

Reset generation cycle

At main oscillation clock at 10 MHz : 105 ms (Min)

At sub osci llation clock at 32.768 kHz : 250 ms (Min)

Hardware watchdog timer

Reset generation cycle

At RC oscillation clock 200 kHz : Min 327.68 ms

At RC oscillation clock 50 kHz : Max 2.62 s

Wild r egisters Capable of replacing three bytes of ROM data

I

2

C bus

Master/ slave sending/receiving

Bus error function, Arbit ration function, Forwarding dir ection detect ion function

Generating repeatedly and detecting function of the start condition

Built-in wake up function

UART/SIO

Data transfer is enabled at UART/SIO

Built-in full-duplex double buffer, Changeable data length (5/6/7/8-bit), Built-in baud rate

generator

NRZ method transfer for mat, Error detected function

LSB-first or MSB-first can be selected

Serial data transfer is available for clock synchronous (SIO) and clock asynchron ous (UART)

10-bit A/ D converter 8 channel s 10-bit resolution can be selected

LCD control ler

(LCDC)

MAX. 28 SEG x 4 CO M

Blinking function*2

8/16-bit compound timer

2ch.Each channel of the timer can be used as "2 cha nnels x 8-bit time r" or "1 channel x 16-bit

timer"

Built-in timer function, PWC function, PWM function and capture function

Count clock: available f rom internal clocks (7 types) or ex ternal clocks

With square wave output

16-bit PPG

8ch.PWM mode or one-shot mode ca n be selected

Counter operation clock: available from eight selectable clock sources

Support for external trigger activation

Watch counter

Count clock: available f rom four selectable clock source s (125 ms, 250 ms, 500 ms, or 1 s)

Counter value can be set within the range of 0 to 63 (When one second is se lected as for the

clock so urce and the counter value is set to 60 , it is possible to count for one minute.)

Watch prescale r Available from four selectab le interval time s (125 ms, 250 ms, 500 ms, 1 s)

Peripheral

function

Exter na l in te rrupt

12 channel s Interrupt by edge detection (Select rising edge/fallin g edge/both edges)

Can be used to recover from standby modes

Page 20

6

CHAPTER 1 DESCRIPTION

*1: Embedded Algorithm is a trade mark of Advanced Mic ro D evices Inc.

*2: Blinking f unction

is only for two-system clock product.

*3: Watch mode is only for two-s ystem clock product.

Flash memory

Support s automatic programming, Embedded Algorithm

TM

*1

Write/Erase/Erase-Suspend/Resume commands

A flag indicating completion of the algorithm

Number o f write/earse cycles (Minim um ) : 10000 times

Data rete n tio n tim e : 20 yea rs

Block protection with external programming voltage

Flash Sec urity Feature for protecting the content of the Flash

Standby Mode Sleep, stop, watch*3 and timebase timer

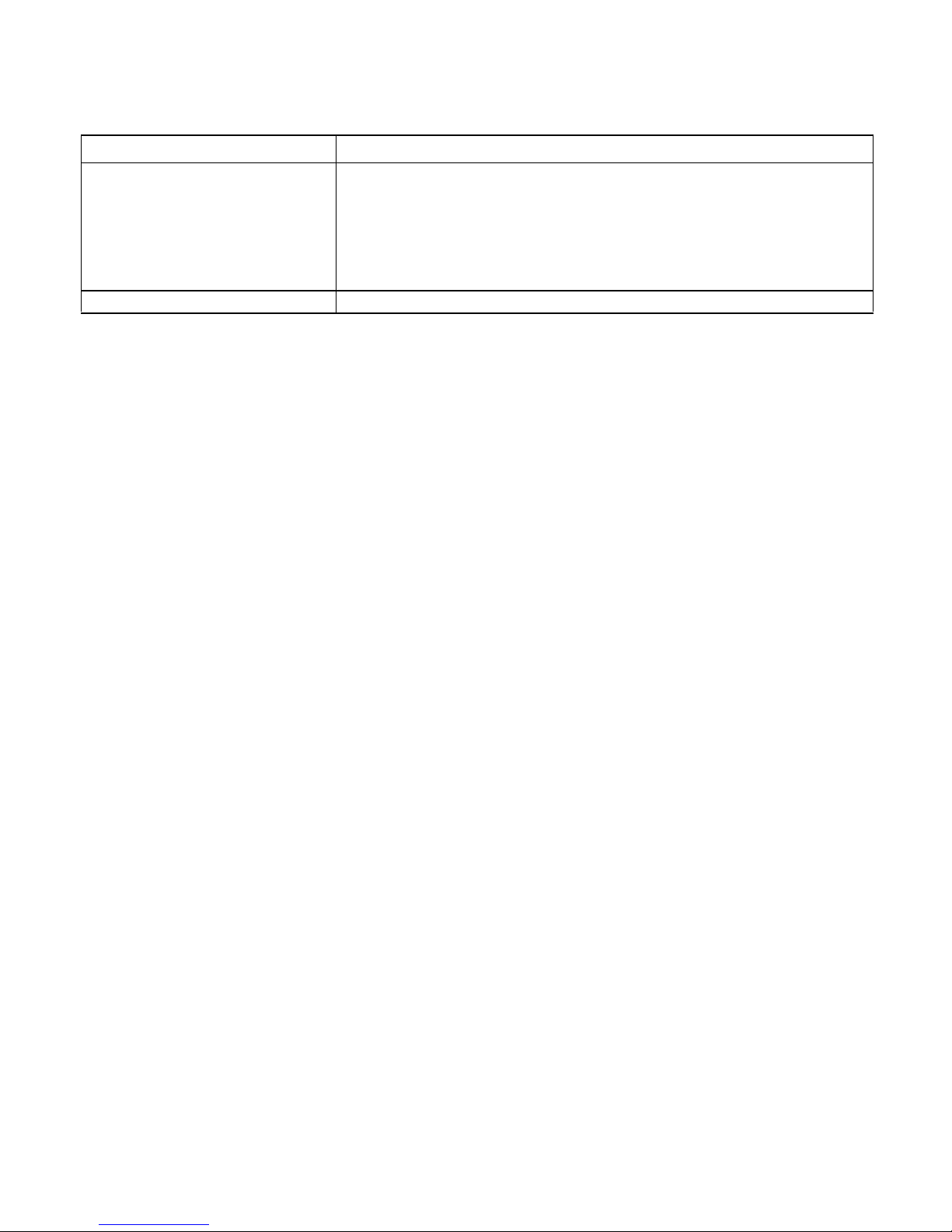

Table 1.2-2 CPU and Peripheral Function of MB95170J Series

Item Specification

Page 21

7

CHAPTER 1 DESCRIPTION

1.3 Difference Among Products and Notes on Selecting

Products

■ Difference Points among Products and Notes on Selecting a Product

●

Notes on using evaluation products

The Evaluation product has not only the functions of the MB95170J series but also those of other products

to support software development for multiple series and models of the F

2

MC-8FX family. The I/O

addresses for peripheral resources not used by the MB95170J series are therefore access-barred. Read/write

access to these access-barred addresses may cause peripheral resources supposed to be unused to operate,

resulting in unexpecte d malfunctions of hardware or software.

Particularly, do not use word access to odd numbered byte address in the prohibited areas (If these access

are used, the address may be read or writ ten unexpectedly).

Also, as the read values of prohibited addresses on the evaluation product are different to the values on the

flash memory and mask ROM products, do not use these values in the program.

The Evaluation product do not support the functions of some bits in single-byte registers. Read/write access

to these bits does not cause hardware malfunctions. The Evaluation, and Flash memory product are

designed to behave completely the same way in terms of hardware and software.

● Difference of memory space

If the amount of memory on the Evaluation product is different from that of the Flash memory product,

carefully check the difference in the amount of memory from the model to be actually used when

developing software.

For details of memory space, refer to “3.1 Memory Space”.

● Current consumption

For details of current consumption, refer to “ n ELE CTRICAL CHARACTERISTICS” in data sheet.

● Package

For detailed information on each package, see "n Package and Its Corresponding Product" and "1.6

Package Dimension".

● Operating voltage

The operating voltage are different between the Eva luation and Flash memory products .

For details of operating voltage, refer to “n ELECTRICAL CHARACTERISTICS” in data sheet.

Page 22

8

CHAPTER 1 DESCRIPTION

■ Package and Its Corresponding Product

❍: usable

× : unusable

MB95F176JS MB95F176JW

FPT-64P-M23 ❍❍

FPT-64P-M24 ❍❍

Package

Product

Page 23

9

CHAPTER 1 DESCRIPTION

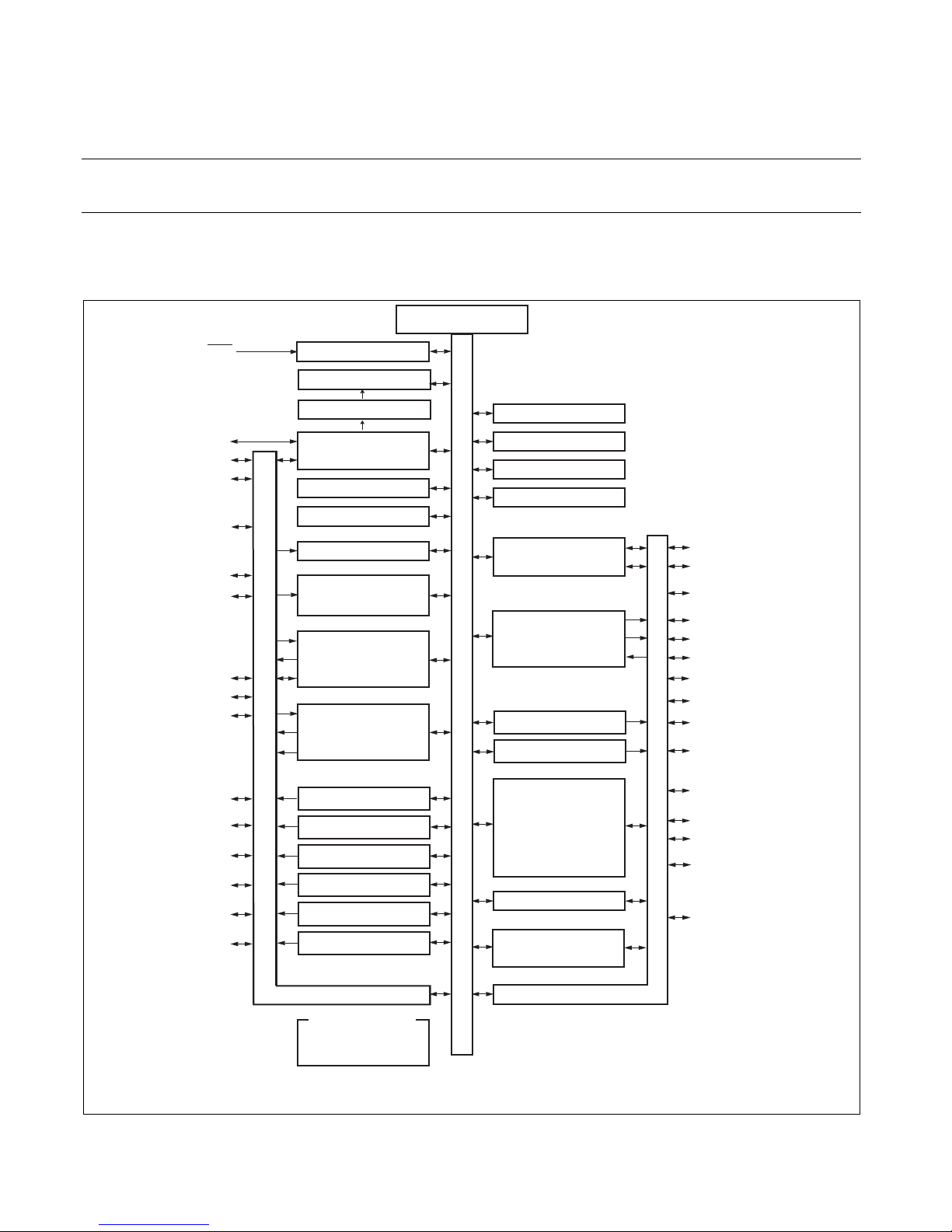

1.4 Block Diagram of MB95170J Series

Figure 1.4-1 shows the block diagram of all MB95170J series.

■ Block Diagram of All MB95170J Series

Figure 1.4-1 Block Diagram of All MB95170J Series

*

PE4/INT10/SEG28

to

PE7/INT13/SEG31

PA0/COM0 to PA3/COM3

PB0/SEG00/TPCLK/CALPL

PC0/TRG0/SEG08

to

PC7/TRG7/SEG15

P60/SEG16 to P61/SEG17

P42/PPG4

P43/PPG5

P14/PPG1

P40/PPG2

P41/PPG3

P13/PPG0/ADTG

P62/TO10/SEG18

P51/SDA0

P50/SCL0

P92/V1/PPG6

P91/V2/PPG7

P90/V3

P63/TO11/SEG19

P00/AN00/INT00

to

P05/AN05/INT05

P10/UI0/EC0

P64/EC1/SEG20

P65/SEG21

RST

X0,X1

P95/X1A*

P94/X0A*

MOD, V

CC, VSS, C

DVcc, DVss x 2

P11/UO0/TO01

P12/UCK0/TO00

I

2

C

F

2

MC-8FX CPU

UART/SIO

10-bit A/D

converter

C

LCDC

16-bit PPG 0

RTC

ROM

RAM

Port Port

External interrupt ch8 to ch11

Interrupt control

Wild register

Reset control

Clock control

Watch prescaler

Watch counter

External interrupt ch0 to ch7

Internal bus

Other pins

* : It is general-purpose port in single clock product, and it is sub clock oscillation pin in dual clock product.

P06/AN06/INT06/SEG22

P07/AN07/INT07/SEG23

8/16-bit compound

timer ch0

8/16-bit compound

timer ch1

RC oscillator

Hardware watchdog

16-bit PPG 1

16-bit PPG 2

16-bit PPG 3

16-bit PPG 4

16-bit PPG 5

16-bit PPG 7

16-bit PPG 6

PB1/SEG01 to PB7/SEG07

Page 24

10

CHAPTER 1 DESCRIPTION

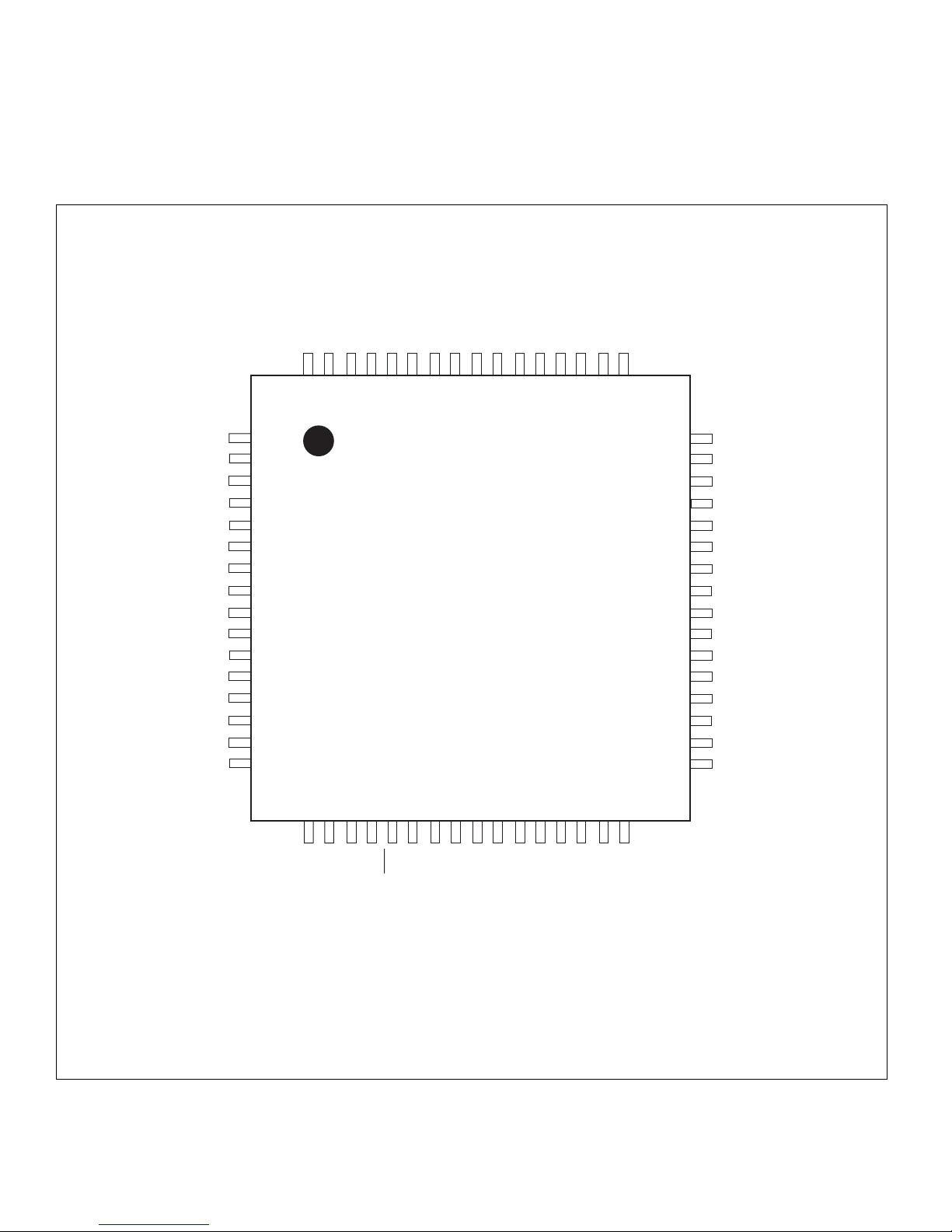

1.5 Pin Assignment

■ Pin Assignment of MB95170J Series

Figure 1.5-1 Pin Assignment of MB95170J Series

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

DVss

P12/UCK0/TO00

P11/UO0/TO01

P10/UI0/EC0

P07/INT07/AN07/SEG23

P06/INT06/AN06/SEG22

P05/INT05/AN05

P04/INT04/AN04

P03/INT03/AN03

P02/INT02/AN02

P01/INT01/AN01

P00/INT00/AN00

MOD

X0

X1

Vss

P64/SEG20/EC1

P63/SEG19/TO11

P62/SEG18/TO10

P61/SEG17

P60/SEG16

PC7/SEG15/TRG7

PC6/SEG14/TRG6

PC5/SEG13/TRG5

PC4/SEG12/TRG4

PC3/SEG11/TRG3

PC2/SEG10/TRG2

PC1/SEG09/TRG1

PC0/SEG08/TRG0

PB7/SEG07

PB6/SEG06

PB5/SEG05

Vcc

PB4/SEG04

PB3/SEG03

PB2/SEG02

PB1/SEG01

PB0/SEG00/TPCLK/CALPL

PA3/COM3

P50/SCL0

RST

P94/X0A

P95/X1A

C

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P51/SDA0

PA0/COM0

PA1/COM1

PA2/COM2

P13/ADTG/PPG

0

P65/SEG21

PE4/SEG28/INT

1

PE5/SEG29/INT

1

PE6/SEG30/INT

1

PE7/SEG31/INT

1

P90/V3

P42/PPG4

DVcc

P41/PPG3

P40/PPG2

P14/PPG1

P43/PPG5

P92/V1/PPG6

P91/V2/PPG7

DVss

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

(FPT-64P-M23/FPT-64P-M24)

Page 25

11

CHAPTER 1 DESCRIPTION

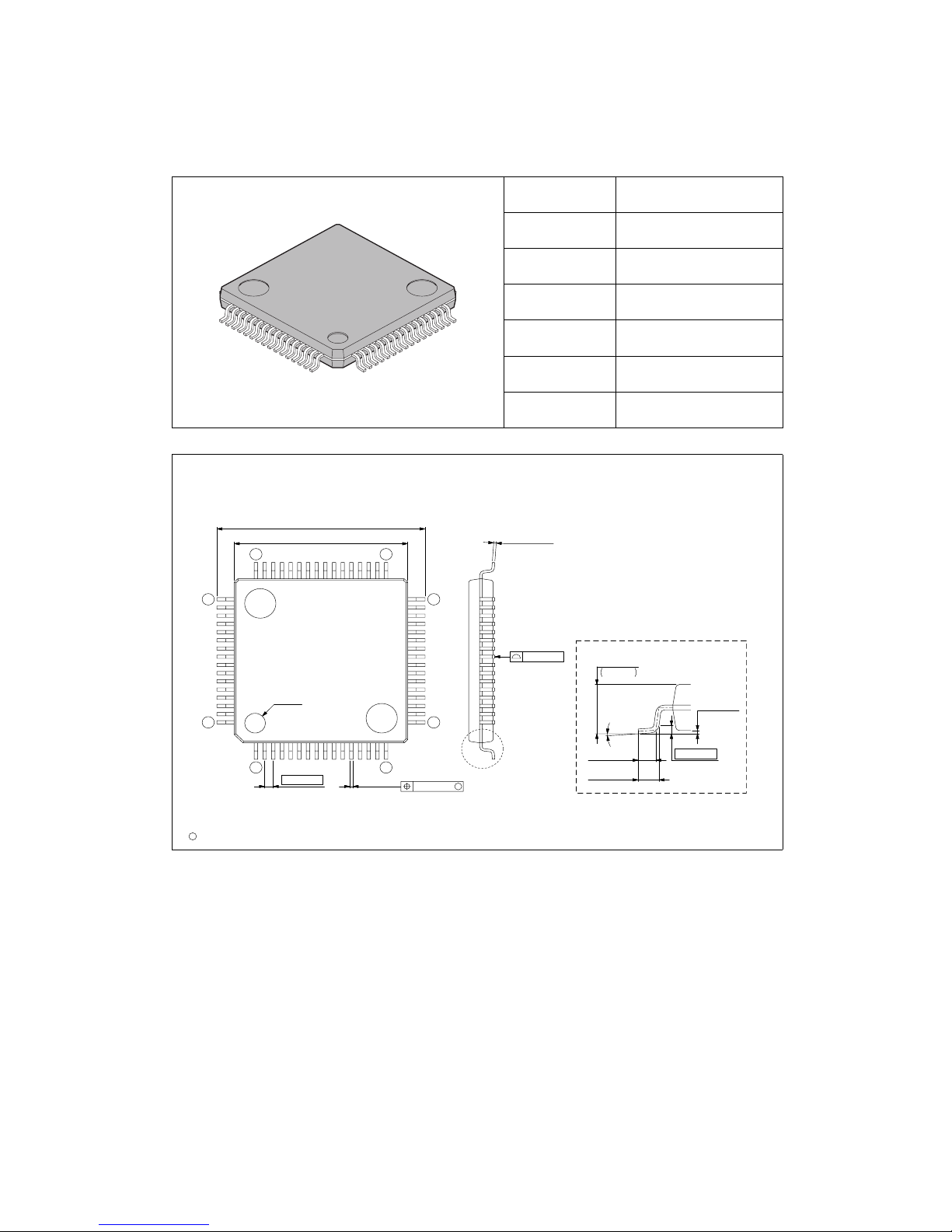

1.6 Package Dimension

MB95170J series is available in two types of package.

■ Package Dimension of FPT-64P-M23

Figure 1.6-1 Package Dimension of FPT-64P-M23

Please confirm the latest Package dimension by following URL.

http://edevice.fujitsu.com/fj/DATASHEET/ef-ovpklv.html

64-pin plastic LQFP Lead pitch 0.65 mm

Package width ×

package length

12.0 × 12.0 mm

Lead shape Gullwing

Sealing method Plastic mold

Mounting height

1.70 mm MAX

Code

(Reference)

P-LFQFP64-12×12-0.65

64-pin plastic LQFP

(FPT-64P-M23)

(FPT-64P-M23)

C

2003 FUJITSU LIMITED F64034S-c-1-1

0.65(.026)

0.10(.004)

1

16

17

32

49

64

3348

*12.00±0.10(.472±.004)SQ

14.00±0.20(.551±.008)SQ

INDEX

0.32±0.05

(.013

±.002)

M

0.13(.005)

0.145±0.055

(.0057

±.0022)

"A"

.059

–.004

+.008

–0.10

+0.20

1.50

0~8˚

0.25(.010)

(Mounting height)

0.50±0.20

(.020

±.008)

0.60±0.15

(.024

±.006)

0.10±0.10

(.004±.004)

Details of "A" part

(Stand off)

Dimensions in mm (inches).

Note: The values in parentheses are reference values

Note 1)* : These dimensions do not include resin protrusion.

Note 2) Pins width and pins thickness include plating thickness.

Note 3) Pins width do not include tie bar cutting remainder.

Page 26

12

CHAPTER 1 DESCRIPTION

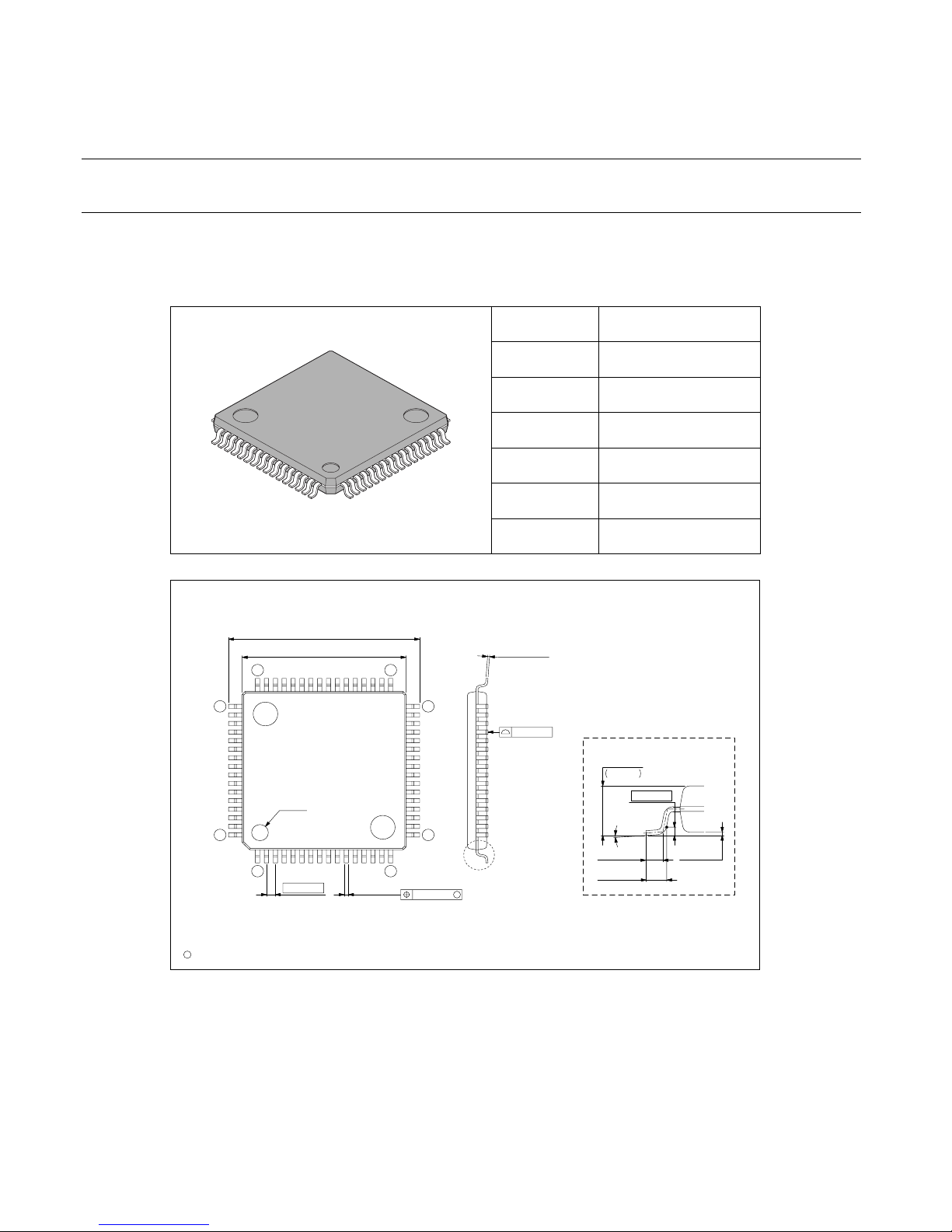

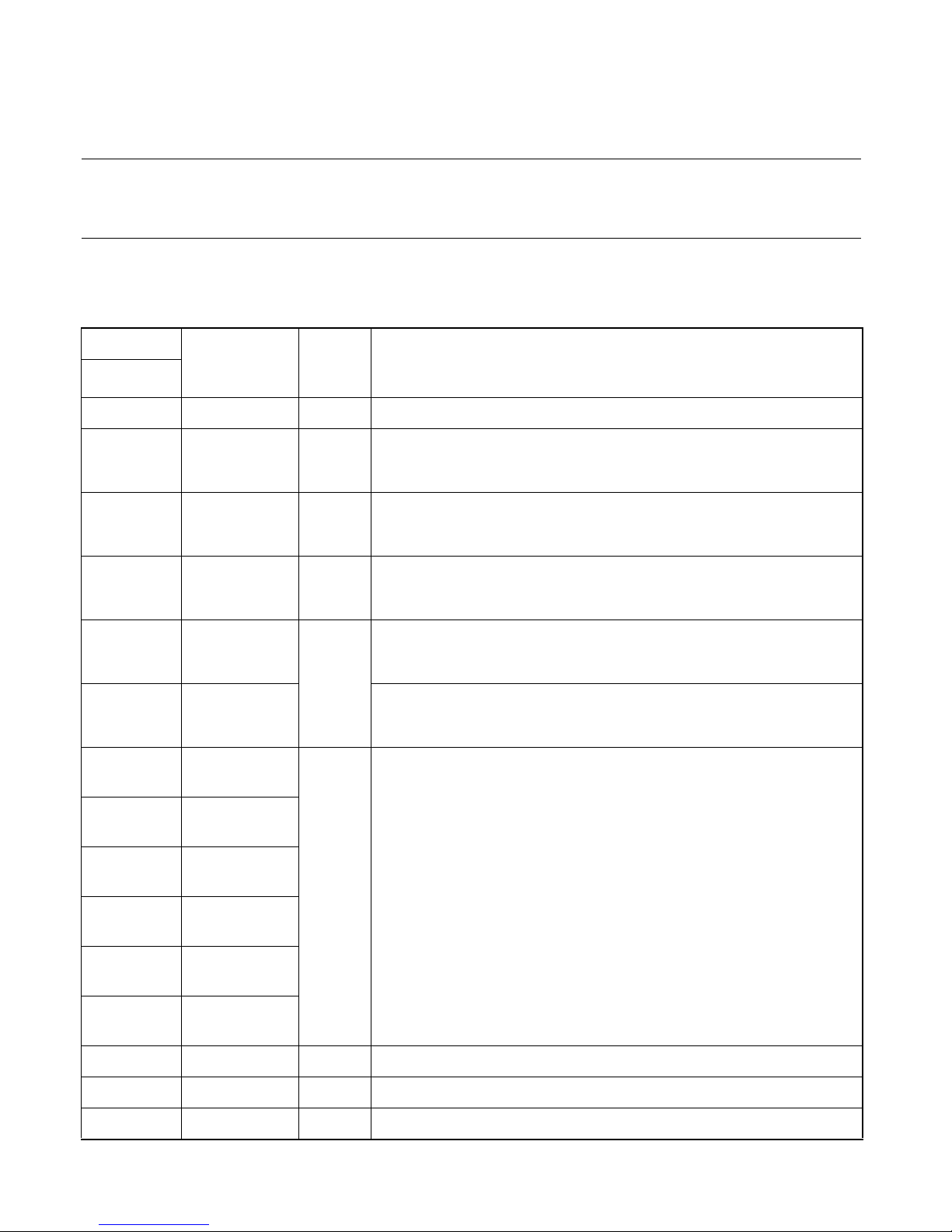

■ Package Dimension of FPT-64P-M24

Figure 1.6-2 Package Dimension of FPT-64P-M24

Please confirm the latest Package dimension by following URL.

http://edevice.fujitsu.com/fj/DATASHEET/ef-ovpklv.html

64-pin plastic LQFP Lead pitch 0.50 mm

Package width ×

package length

10.0 × 10.0 mm

Lead shape Gullwing

Sealing method Plastic mold

Mounting height

1.70 mm MAX

Weight 0.32g

Code

(Reference)

P-LFQFP64-10×10-0.50

64-pin plastic LQFP

(FPT-64P-M24)

(FPT-64P-M24)

LEAD No.

Details of "A" part

0.25(.010)

(Stand off)

(.004±.004)

0.10±0.10

(.024±.006)

0.60±0.15

(.020±.008)

0.50±0.20

1.50

+0.20

–0.10

+.008

–.004

.059

0˚~8˚

"A"

0.08(.003)

(.006±.002)

0.145±0.055

0.08(.003)

M

(.008±.002)

0.20±0.05

0.50(.020)

12.00±0.20(.472±.008)SQ

10.00±0.10(.394±.004)SQ

INDEX

49

64

3348

17

32

161

2005 FUJITSU LIMITED F64036S-c-1-1

C

(Mounting height)

*

Dimensions in mm (inches).

Note: The values in parentheses are reference values

Note 1) * : These dimensions do not include resin protrusion.

Note 2) Pins width and pins thickness include plating thickness.

Note 3) Pins width do not include tie bar cutting remainder.

Page 27

13

CHAPTER 1 DESCRIPTION

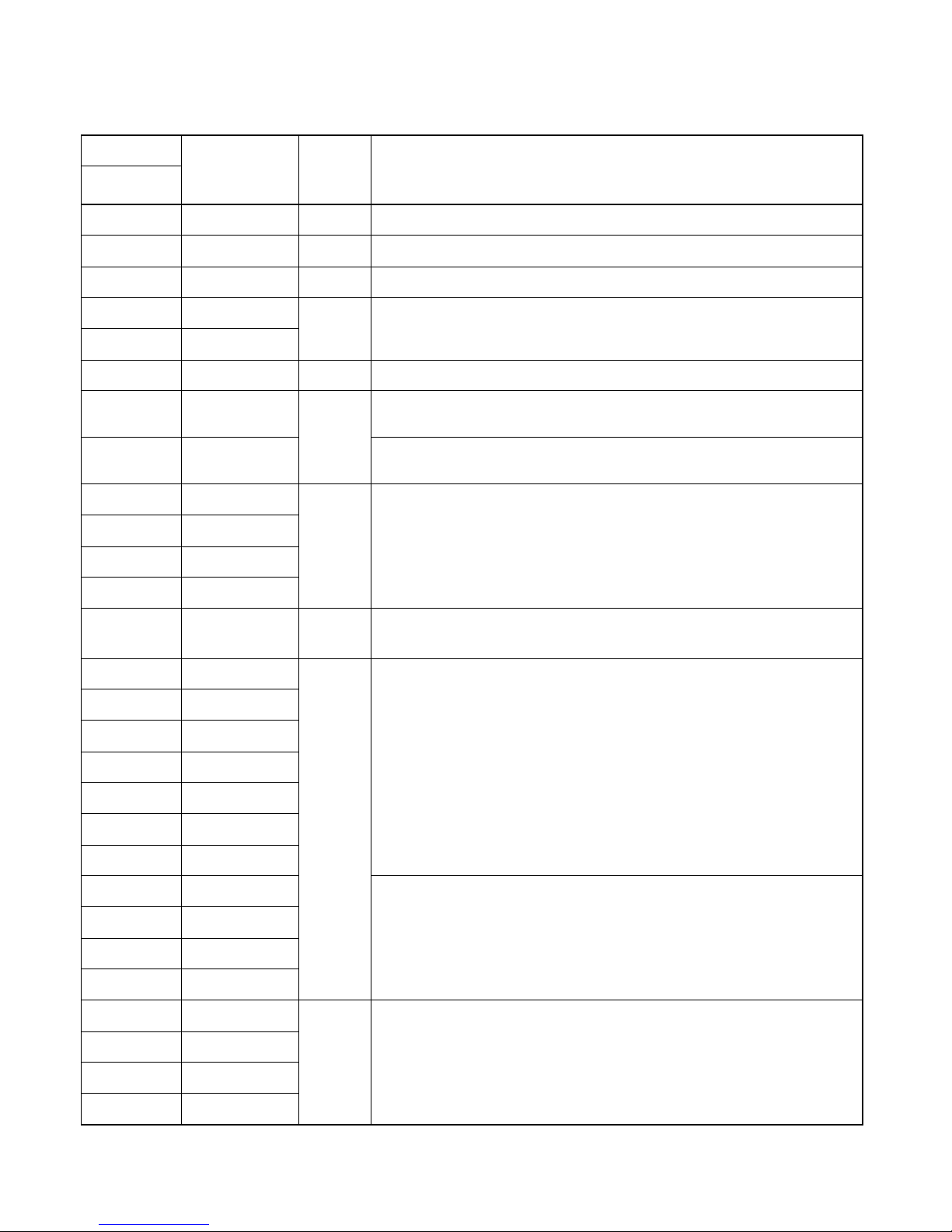

1.7 Pin Description

Table 1.7-1 shows pin description. The alphabet in the "Circuit Type" column of Table

1.7-1 corresponds to the one in the "Classification" column of Table 1.8-1.

■ Pin Description

Table 1.7-1 Pin Description (1 / 3)

Pin no.

Pin name

I/O

circuit

type*

2

Function

LQFP*

1

1DVSS⎯

Power supply pin (GND)

2

P12/UCK0/

TO00

H

General -purpose I/O port

The pin is shared with 8/16-bi t compound timer ch.0 output and UART/SIO ch.0

clock I/O .

3

P11/UO0/

TO01

H

General -purpose I/O port

The pin is share d with 8/16-b it compo und timer ch. 0 output and UART/SIO ch .0 data

output.

4 P10/UI0/EC0 G

General -purpose I/O port

The pin is share d with 8/16-b it compo und timer ch.0 clock input and UART/ SIO ch.0

data input.

5

P07/S23/

INT07/AN07

S

General -purpose I/O port

The pins are shared with LCDC SEG output (SEG23) , external interrupt input and

A/D converter analog input.

6

P06/S22/

INT06/AN06

General -purpose I/O port

The pins are shared with LCDC SEG output (SEG22) , external interrupt input and

A/D converter analog input.

7

P05/INT05/

AN05

J

General -purpose I/O port

The pins are shared with external interrupt input and A/D converter analog input.

8

P04/INT04/

AN04

9

P03/INT03/

AN03

10

P02/INT02/

AN02

11

P01/INT01/

AN01

12

P00/INT00/

AN00

13 MOD B

An operati ng m ode designation pin

14 X0 A

Main clock oscillation pi n

15 X1 A

Main clock oscillation pin

Page 28

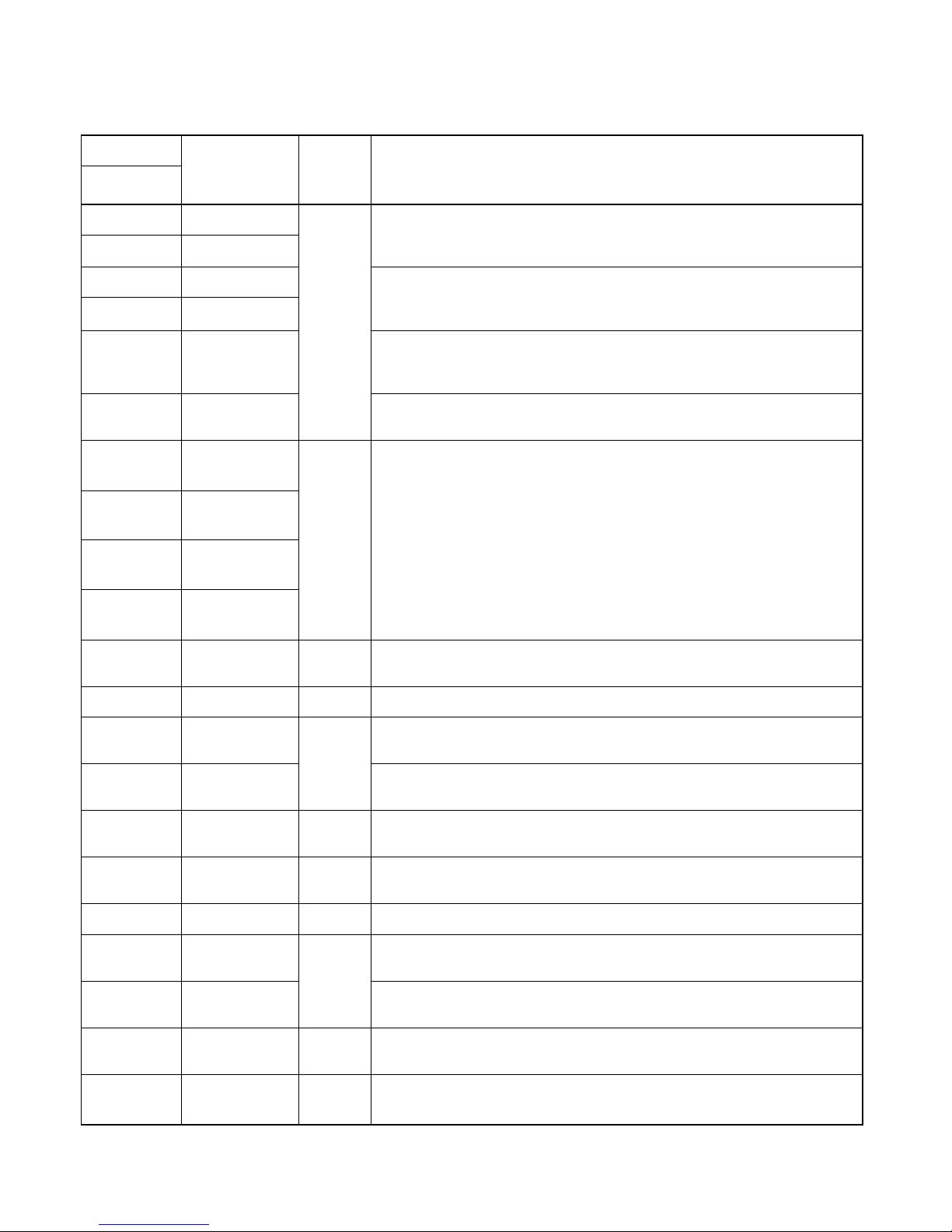

14

CHAPTER 1 DESCRIPTION

16 V

SS

⎯

Power supply pin (GND)

17 V

CC

⎯

Power supply pin

18 C ⎯ Capacitor connection pin

19 P95/X1A

A/H

General -purpose I/O port

The pins are shared with sub clock oscillation pin

20 P94/X0A

21 RST B’

Rese t pi n

22 P50/SCL0

I

General -purpose I/O port

The pin is shared with I

2

C ch.0 clock I/O.

23 P51/SDA0

General -purpose I/O port

The pin is shared with I

2

C ch.0 data I/O.

24 PA0/COM0

M

General -purpose I/O port

The pins are shared with LCDC COM output.

25 PA1/COM1

26 PA2/COM2

27 PA3/COM3

28

PB0/S00/TP-

CLK/CALPL

M

General -purpose I/O port

The pins are shared with LCDC SEG output and RTC I/O.

29 PB1/S01

M

General -purpose I/O port

The pi ns are sh ared with LC D C S EG o utput.

30 PB2/S02

31 PB3/S03

32 PB4/S04

33 PB5/S05

34 PB6/S06

35 PB7/S07

36 PC0/S08/TRG0

General -purpose I/O port

The pins are shared with LCDC SEG output and PPG trigger input.

37 PC1/S09/TRG1

38 PC2/S10/TRG2

39 PC3/S11/TRG3

40 PC4/S12/TRG4

M

General -purpose I/O port

The pins are shared with LCDC SEG output and PPG trigger input.

41 PC5/S13/TRG5

42 PC6/S14/TRG6

43 PC7/S15/TRG7

Table 1.7-1 Pin Description (2 / 3)

Pin no.

Pin name

I/O

circuit

type*

2

Function

LQFP*

1

Page 29

15

CHAPTER 1 DESCRIPTION

44 P60/S16

M

General -purpose I/O port

The pi ns are sh ared with LC D C S EG o utput.

45 P61/S17

46 P62/S18/TO10

General -purpose I/O port

The pins are sh ared wi th LCDC SEG outp ut and 8/16 -bit compound timer ch.1 ou tput

(TO10, TO11)

47 P63/S19/TO11

48 P64/S20/EC1

General -purpose I/O port

The pins are sh ar ed with LCD C SEG ou tpu t and 8/ 16- bit co mpoun d tim er ch. 1 cl ock

input

49 P65/S21

General -purpose I/O port

The pi ns are sh ared with LC D C S EG o utput

50

PE4/S28/

INT10

Q

General -purpose I/O port

The pins are shared with external interrupt input (INT10 to INT13) and LCDC SEG

output (SEG 28 to SEG31)

51

PE5/S29/

INT11

52

PE6/S30/

INT12

53

PE7/S31/

INT13

54 P90/V3 R

General -purpose I/O port

The pins are shared with power supply pins for LCDC drive

55 DV

SS

⎯

Power supply pin (GND)

56 P91/V2/PPG7

R

General -purpose I/O port

The pins are shared with power sup ply pins for LCDC drive and 16-bit PPG 7 output

57 P92/V1/PPG6

General -purpose I/O port

The pins are shared with power sup ply pins for LCDC drive and 16-bit PPG 6 output

58 P43/PPG5 H’

General -purpose I/O port

The pins are shared with and 16-bit PPG 5 output

59 P42//PPG4 H’

General -purpose I/O port

The pins are shared with and 16-bit PPG 4 output

60 DV

CC

⎯

Power supply pin

61 P41/PPG3

H’

General -purpose I/O port

The pins are shared with and 16-bit PPG 3 output

62 P40/PPG2

General -purpose I/O port

The pins are shared with and 16-bit PPG 2 output

63 P14/PPG1 H’

General -purpose I/O port

The pins are shared with and 16-bit PPG 1 output

64

P13/ADTG/

PPG0

H’

General -purpose I/O port

The pins are shared with and 16-bit PPG 0 output and A/D trigger input

Table 1.7-1 Pin Description (3 / 3)

Pin no.

Pin name

I/O

circuit

type*

2

Function

LQFP*

1

Page 30

16

CHAPTER 1 DESCRIPTION

*1 : FPT-64P-M23 , FPT-64P-M24

*2 : For the I/O circuit type, refer to “1.8 I/ O Ci rcuit Type”.

Page 31

17

CHAPTER 1 DESCRIPTION

1.8 I/O Circuit Type

Table 1.8-1 lists the I/O circuit types. Also, the alphabet in the "Type" column of Table

1.8-1 corresponds to the one in the "I/O circuit type" column of Table 1.7-1.

■ I/O Circuit Type

Table 1.8-1 I/O Circuit Type (1 / 3)

Type Circuit Remarks

A

• Oscillation circuit

• High-speed side

Feedback resistance: appro x 1 MΩ

• Low-speed side

Feedback resistance: appro x 10 MΩ

B

• Only for input

• Hysteresis input

B’

• Hysteresis input

G

• CMOS output

• CMOS input

• Hysteresis input

• With pull-up control

• Automotive input

H

• CMOS output

• Hysteresis input

• With pull-up control

• Automotive input

X0 (X0A)

X1 (X1A)

N-ch

Standby control

Clock input

Mode input

Reset input

R

P-ch

N-ch

P-ch

Pull-up control

Standby control

Digital output

Digital output

Hysteresis input

CMOS input

Automotive input

P-ch

P-ch

N-ch

R

Pull-up control

Standby control

Digital output

Digital output

Hysteresis input

Automotive input

Page 32

18

CHAPTER 1 DESCRIPTION

H’

• CMOS output

• Hysteresis input

• Automotive input

I

• N-ch open drain output

• CMOS input

• Hysteresis input

• Automotive input

J

• CMOS output

• Hysteresis input

• Analog input

• With pull-up control

• Automotive input

M

• CMOS output

• LCD output

• Hysteresis input

• Automotive input

Table 1.8-1 I/O Circuit Type (2 / 3)

Type Circuit Remarks

P-ch

N-ch

Standby con-

Digital output

Digital output

Hysteresis input

Automotive input

N-ch

Standby control

Digital output

CMOS input

Hysteresis input

Automotive input

R

P-ch

P-ch

N-ch

Pull-up control

A/D control

Standby control

Analog input

Digital output

Hysteresis input

Digital output

Automotive input

P-ch

N-ch

Standby control

Hysteresis input

Digital output

Digital output

LCD control

LCD output

Automotive input

Page 33

19

CHAPTER 1 DESCRIPTION

N

• CMOS output

• LCD output

• CMOS input

• Hysteresis input

• Automotive input

Q

• CMOS output

• LCD output

• Hysteresis input

• Automotive input

R

• CMOS output

• LCD power supply

• Hysteresis input

• Automotive input

S

• CMOS output

• LCD output

• Hysteresis input

• Analog input

• Automotive input

Table 1.8-1 I/O Circuit Type (3 / 3)

Type Circuit Remarks

P-ch

N-ch

LCD control

Digital output

Hysteresis input

CMOS input

Digital output

Standby control

LCD output

Automotive input

P-ch

N-ch

Standby control

Digital output

Hysteresis input

LCD control

Digital output

External

interrupt control

LCD output

Automotive input

P-ch

N-ch

LCD control

Standby control

LCD built-in division

resistance I/O

Hysteresis input

Digital output

Digital output

Automotive input

P-ch

N-ch

A/D control

Standby control

Analog input

Digital output

Hysteresis input

Digital output

Automotive input

LCD output

Page 34

20

CHAPTER 1 DESCRIPTION

Page 35

21

CHAPTER 2

HANDLING DEVICES

This chapter gives notes on using.

2.1 Device Handling Precautions

Page 36

22

CHAPTER 2 HANDLING DEVICES

2.1 Device Handling Precautions

This section summarizes the precautions on the device's power supply voltage and pin

treatment.

■ Device Handling Precautions

●

Preventing Latch-up

Care must be taken to ensure that maximum voltage ratings are not exceeded when they are used.

Latch-up may occur on CMOS ICs if voltage higher than V

CC

or lower than VSS is applied to input and

output pins other than medium- and high-withstand voltage pins or if higher than the rating voltage is

applied betwee n V

CC

pin and VSS pin.

When latch-up occurs, power s upply current increases rapidly and might thermally damage el ements.

● Stable Supply Voltage

Supply voltage should be stabilized.

A sudden change in power-supply voltage may cause a malfunction even within the guaranteed operating

range of the Vcc power-supply volt age.

For stabilizatio n , in principle, keep the variation in V cc ripple (p-p v alue) in a comm ercial freq u ency range

(50/60 Hz) not to exceed 10% of the standard Vcc value and suppress the voltage variation so that the

transient variation rate does not exceed 0.1 V/ms during a momentary change such as when the power

supply is switched.

● Precautions for Use of External Clock

Even when an external clock is used, oscillation stabilization wait time is required for power-on reset,

wake-up from subclock mode or stop mode.

Page 37

23

CHAPTER 2 HANDLING DEVICES

■ Pin Connection

● Treatment of Unused Pin