FUJITSU SEMICONDUCTOR

DATA SHEET

32-bit Proprietary Microcontroller

CMOS

FR60Lite MB91270/280 Series

MB91F272/F272S/V280

DESCRIPTION

■

The MB91270/280 series is single chip microcontroller that builds various I/O resources and the bus control

mechanisms into by using 32-bit efficient RISC CPU for the built-in control being demanded for CPU processing

high performance/high-speed. Because the vast address space that 32-bit CPU accesses is supported, the external

bus access is basically. To speed up CPU instruction execution, MB91270/280 has built-in RAM of 16 Kbytes (for

data) .

DS07-16801-1E

It is best specification for the built-in usage in which efficient CPU processing power such as the digital video

camera, navigation systems, and DVD players is demanded.

The MB91270/280 series power-up the bus access based on FR30/40 family CPU, and is FR60 Lite family

corresponding to use at high speed.

FEATURES

■

• FR CPU characteristics

• 32-bit RISC, load/store architecture with a five-stage pipeline

• Maximum operating frequency: 32 MHz (using the PLL at an oscillation frequency of 4 MHz)

• 16-bit fixed length instructions (basic instructions), 1 instruction per cycle

(Continued)

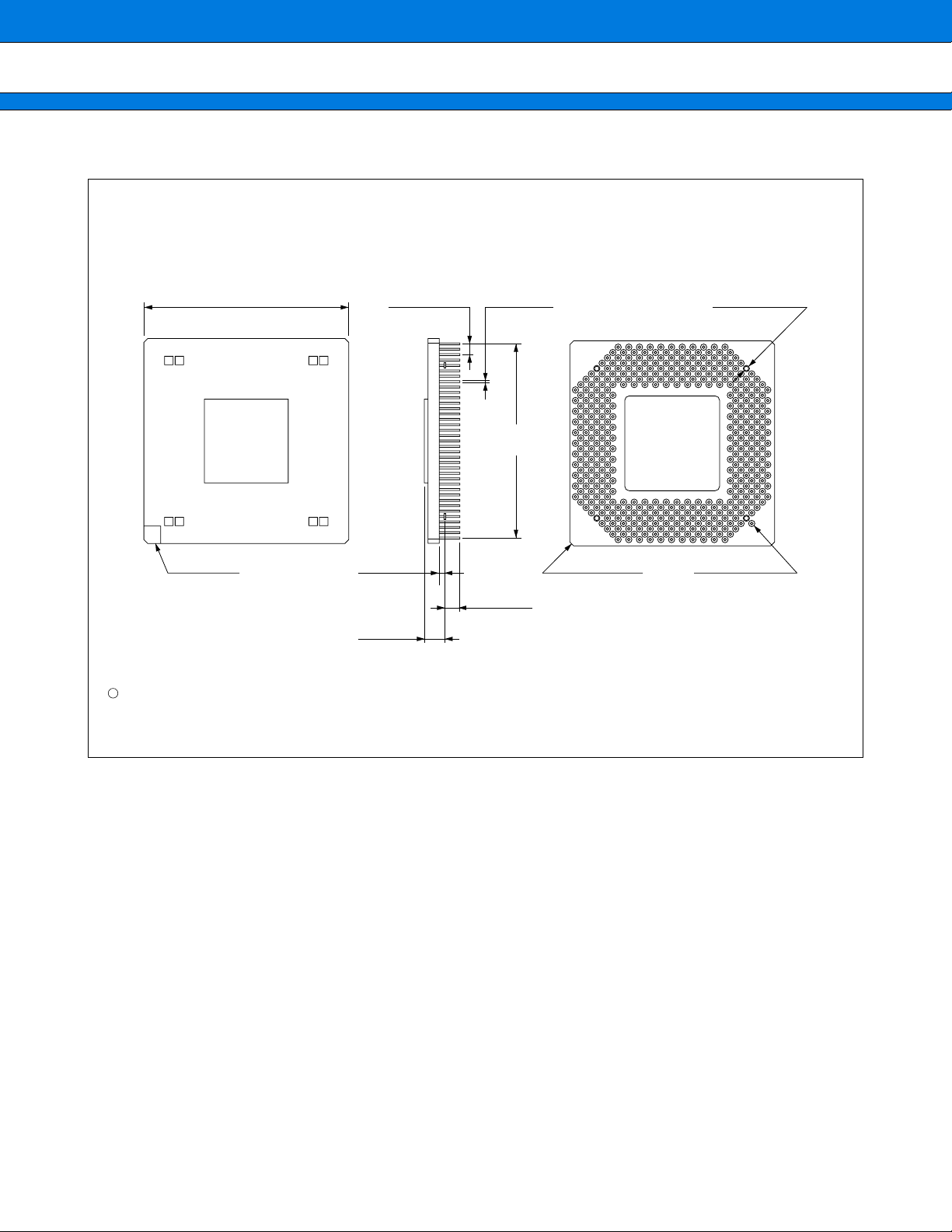

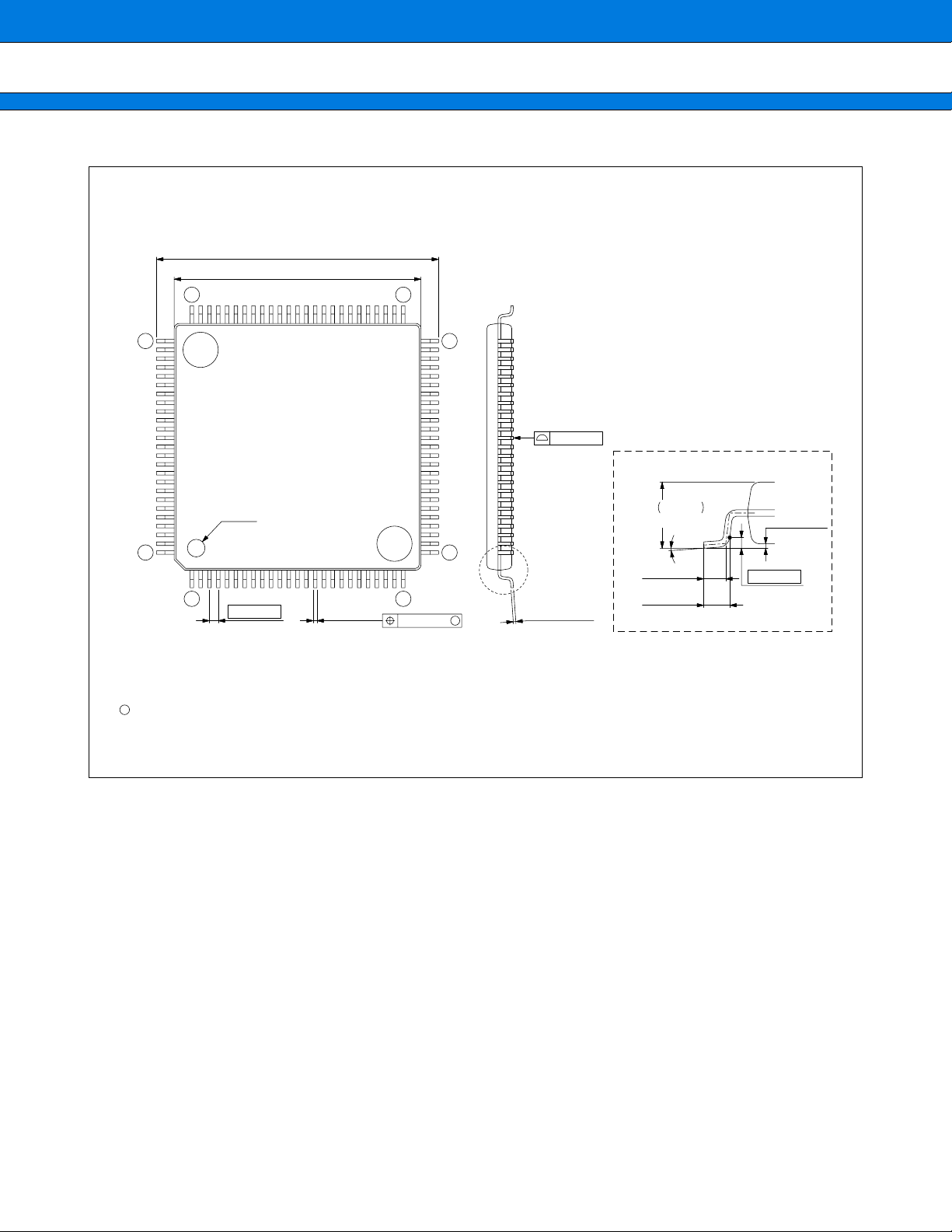

PACKAGES

■

401-pin ceramic PGA 100-pin plastic LQFP

(PGA-401C-A02) (FPT-100P-M05)

MB91270/280 Series

• Instruction optimized for embedded applications:

Memory-to-memory transfer, bit manipulation, barrel shift instruction etc.

• Instructions adapted for high - level languages:

Function entry/exit instructions, multiple - register load/store instructions

• Register interlock functions:

Facilitating coding in assemblers

• Built-in multiplier supported at the instruction level.

Signed 32-bit multiplication: 5 cycles.

Signed 16-bit multiplication: 3 cycles.

• Interrupt (PC, PS save): 6 cycles, 16 priority levels

• Harvard architecture allowing program access and data access to be executed simultaneously

• Instruction compatible with FR family

• External bus interface

• Maximum operating frequency: 16 MHz

• Can output full 24-bit address range (16 Mbyte space)

• 8,16-bit data output

• Unused data/address pin can be used as general-purpose I/O ports.

• Capable of chip select output for completely independent four areas settable in 64 Kbytes minimum.

• Supports the following memory interfaces

SRAM, ROM/Flash

• Basic bus cycle: 2 cycles

• Programmable automatic wait cycle generation function capable of inserting wait cycles for each area

• RDY input for external wait cycles

• Built-in memory

MB91V280 MB91F272 (S)

ROM/Flash External SRAM Flash 256 Kbytes

F-bus RAM 48 Kbytes 10 Kbytes

The peripheral circuits are described below.

See “■PRODUCT LINEUP” for the number of available channels on each model.

• DMAC (DMA Controller)

• Capable of simultaneous operation of up to five channels

• Two forwarding factors (internal peripheral/software)

• Bit search module (for REALOS)

Search for the position of the bit “1”/“0”-changed first in one word from the MSB

• LIN UARTs (LIN-UART) : Up to 7 channels

• Asynchronous (start-stop synchronous) communications, clock synchronous communications

• Synch-Break detection

• Built-in baud rate generator on each channel

• Supports SPI (mode 2: Clock synchronous communication mode)

• CAN CONTROLLERS : 3 channels (Max)

• High-speed transfer : 1 Mbps

• 32 message buffer (128 message buffer on the MB91V280)

(Continued)

2

MB91270/280 Series

• Various timers

• 16-bit reload timer : 3 channels (including one channel for use by REALOS)

The internal clock can be divided by 2, 8, or 32

• 16-bit free-running timer: 4 channels

Output compare module: 8 channels

Input capture module: 8 channels

• 8/16-bit PPG timer: 8-bit x 16 channels or 16-bit x 8 channels

• Interrupt controller

• Interrupt from internal peripheral

• Software-selectable priority level (16 levels)

• D/A converter : 2 channels

8-bit or 10-bit resolution, R-2R type

• A/D converter: 24 channels (MB91V280 has an additional module with eight more channels)

• 10-bit resolution

• Successive approximation conversion type

Conversion time : 3 µs

• Conversion mode (single conversion mode, continuous conversion mode)

• Activation source (software, external trigger, peripheral interrupt)

• Other interval timer/counter

• 8/16-bit up down counter :

8 bits × 4 channels or 16 bits × 2 channels

• 16-bit timebase timer / watchdog timer

2

C bus interface* (400 Kbps): 3 channels

• I

• Master/slave sending and receiving

• Arbitration and clock synchronization

• Hardware watchdog

Interval time: 569 ms (Min), 771 ms (Max)

(Using a self-oscillation circuit (100 kHz) with a trimming function.)

• I/O port

• Pull-up/pull-down can be controlled independently for each pin.

• The input level for each pin can be set to either CMOS Schmitt trigger levels or CMOS automotive Schmitt

trigger levels.

• The pin level can be read directly.

• Max 120 ports

• Other features

• Internal oscillator circuit as clock source, allowing PLL multiplication to be selected

• INITX is prepared as a reset pin.

• Watchdog timer reset, software reset

• Available low-power consumption modes are stop mode, sleep mode, and real time clock mode.

Supports low-power consumption operation with CPU operating at 32 kHz (MB91F272 only).

• Gear function

• Built-in timebase timer

• Output clock (clock monitor)

(Continued)

3

MB91270/280 Series

(Continued)

• Clock Modulator

• Clock monitor function

Uses an internal self-oscillation circuit to monitor whether the main clock halts.

• Package PGA-401, LQFP-100

• CMOS technology (0.35 µm)

• Power supply voltage: 3.5 V to 5.5 V

The 3.3 V supply to internal circuits is generated by an internal step-down circuit.

2

* : I

C license

Purchase of Fujitsu I

components in an I

by Philips.

2

C components conveys a license under the Philips I2C Patent Rights to use, these

2

C system provided that the system conforms to the I2C Standard Specification as defined

4

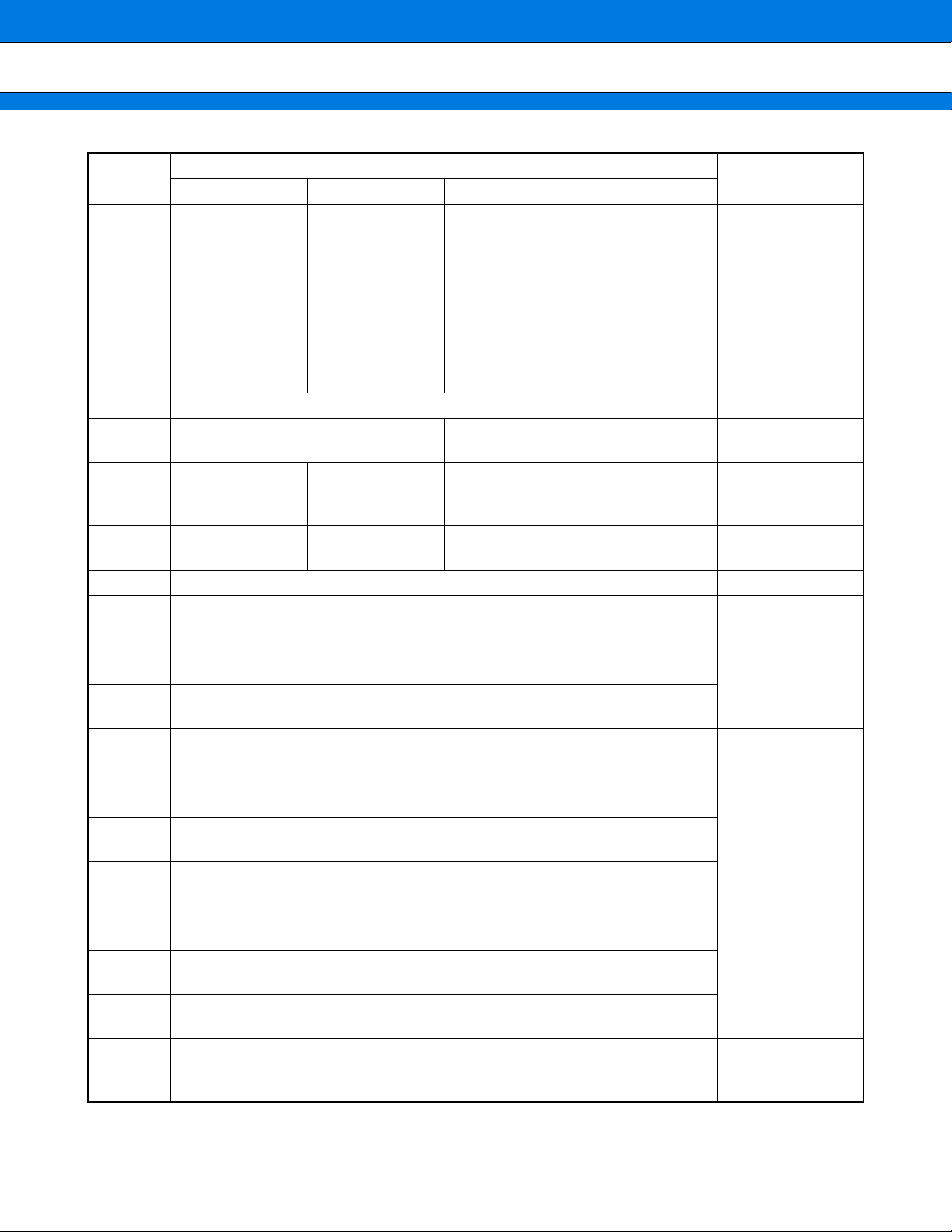

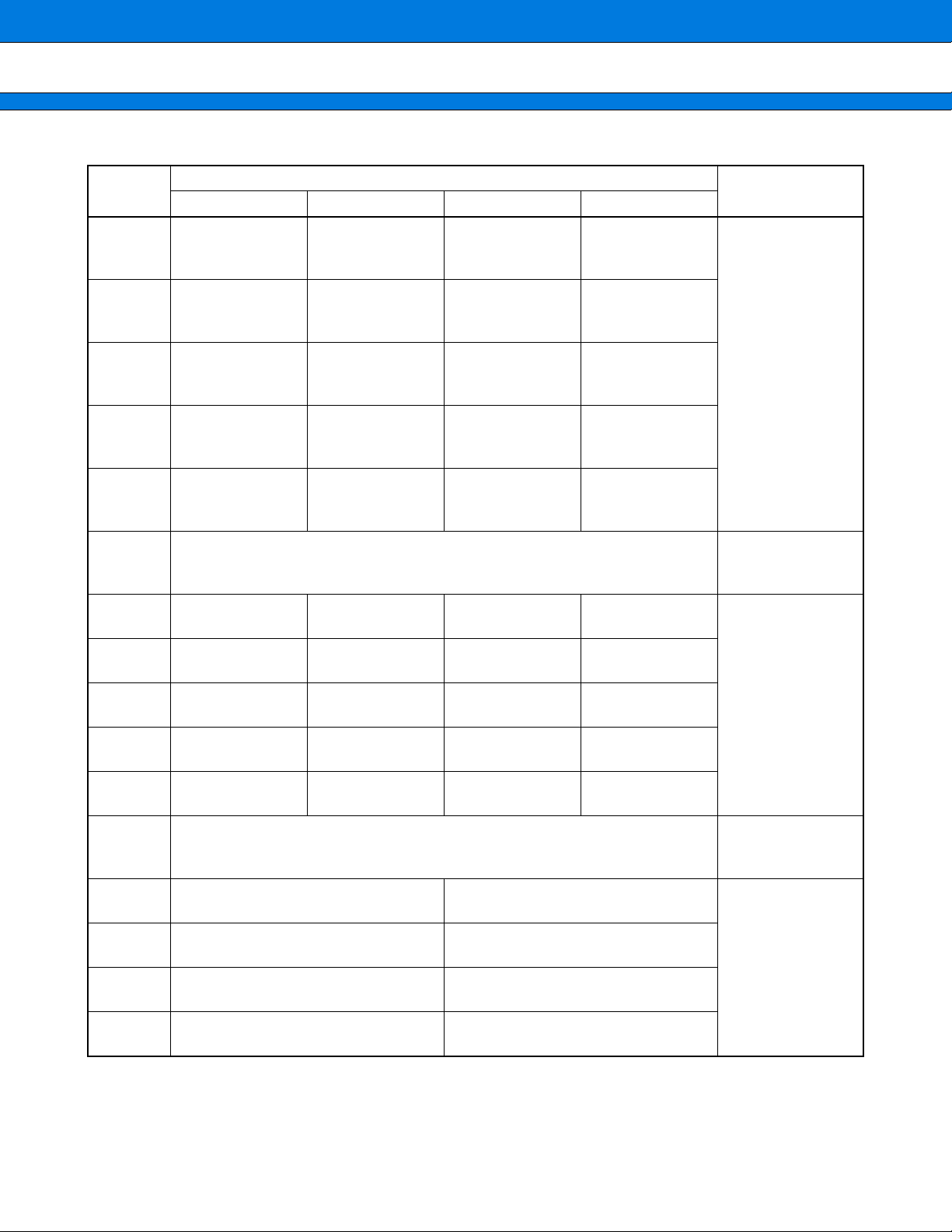

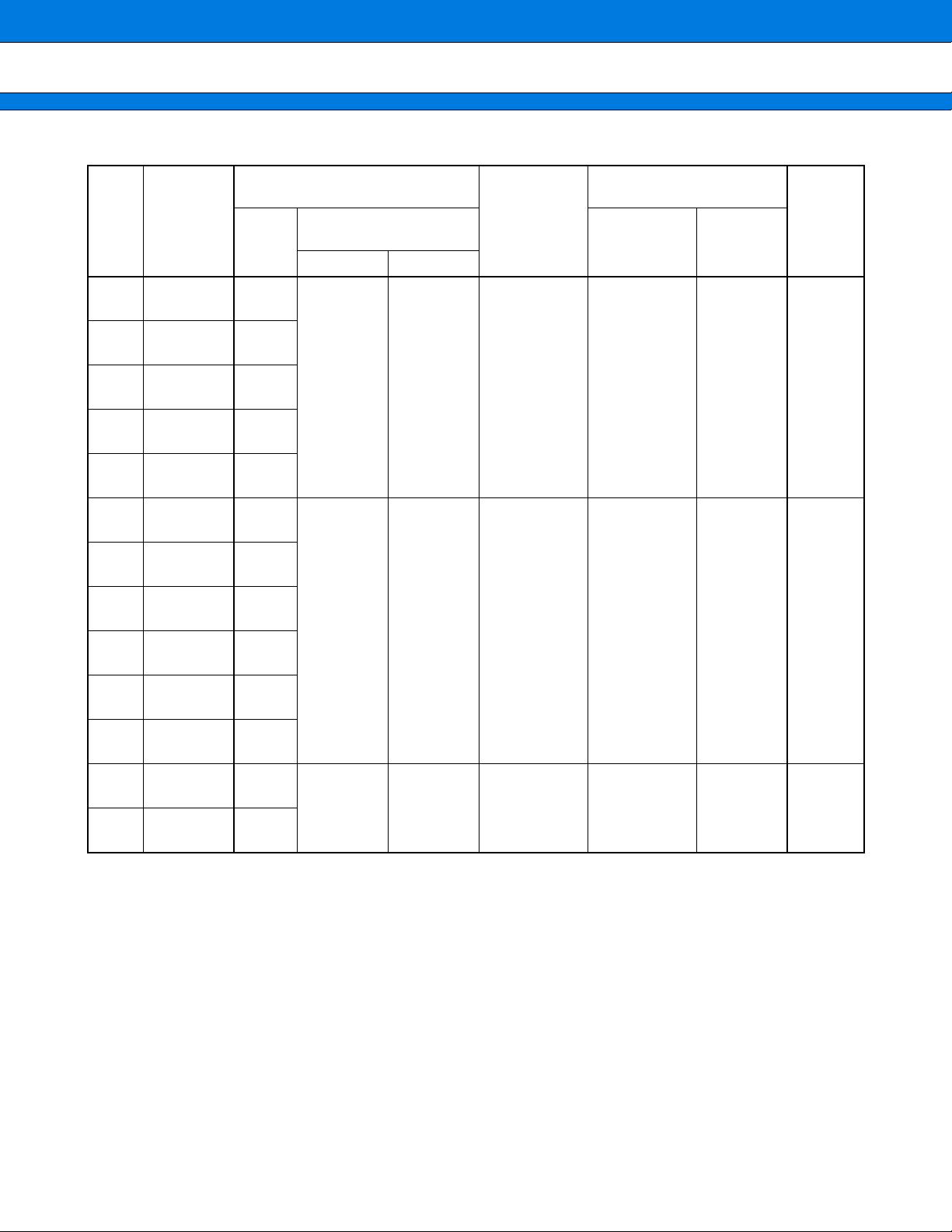

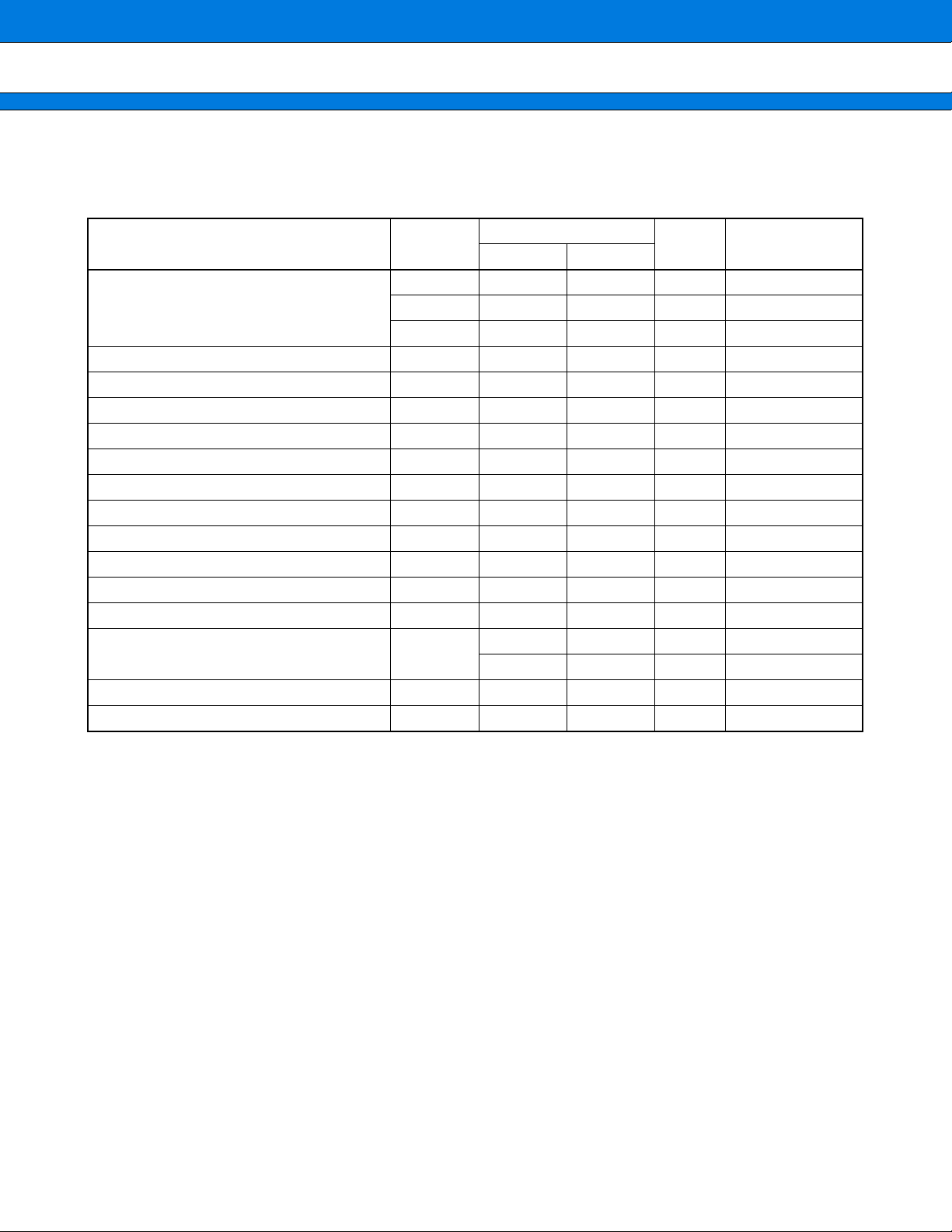

PRODUCT LINEUP

■

MB91270/280 Series

Kind

Parameter

Package LQFP-100 PGA-401

Built - in ROM/Flash Flash 256 Kbytes External SRAM

RAM 10 Kbytes 48 Kbytes

External bus

External interrupt 16 channels 40 channels

DMAC (DMA Controller) 5 channels 5 channels

Clock modulator Yes Yes

Clock monitor function Yes Yes

Clock monitor Yes Yes

32 kHz sub-clock

Real time clock Yes Yes

CAN controllers 1 channel (32 message buffer) 3 channels (128 message buffer)

LIN UARTs (LIN-UART) 7 channels 7 channels

2

C interface 3 channels 3 channels

I

16 - bit reload timer 3 channels 3 channels

8/16-bit up down counter 2 channels 2 channels

16 - bit free - run timer 4 channels 4 channels

Input capture 8 channels 8 channels

Output compare 8 channels 8 channels

8/16-bit PPG

10-bit A/D converter 24 channels 24 channels + 8 channels

8/10-bit D/A converter No 2 channels

Pin pull-up/down See “■PIN FUNCTION” All pins

Input level selector See “■PIN FUNCTION” All pins

Debugging support Wild register DSU4

MB91F272 (S) MB91V280

Address : 24 bits

Data : 16 bits

(Multiplex only)

Option

(MB91F272 only)

16-bit x 8 channels

8-bit x 16 channels

Address : 24 bits

Data : 16 bits

Yes

16-bit x 8 channels

8-bit x 16 channels

5

MB91270/280 Series

R

P

T

P

P

P

P

P

P

P

P

P

P

P

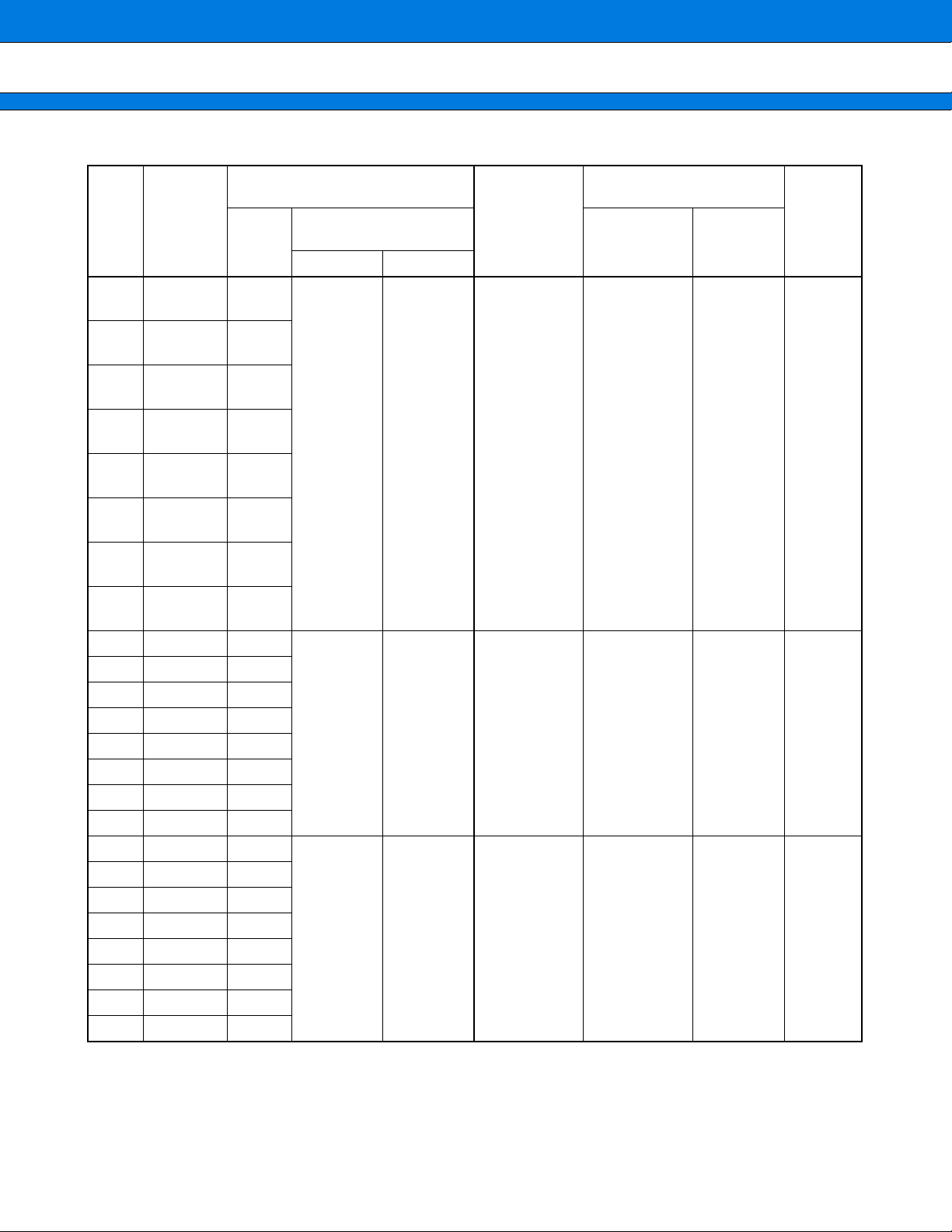

PIN ASSIGNMENT

■

P25/A21/IN1

P24/A20/IN0

P23/A19/PPGF

P22/A18/PPGD

P21/A17/PPGB

P20/A16/PPG9

9998979695949392919089888786858483828180797877

100

(TOP VIEW)

P17/AD15/SCK4

P16/AD14/SOT4

P15/AD13/SIN4

X0X1VSSVCCP14/AD12/SCK3

P13/AD11/SOT3

P12/AD10/SIN3/INT11

P11/AD09/TOT1

P10/AD08/TIN1

P07/AD07/INT15

P06/AD06/INT14

P05/AD05/SCK6/INT13

P04/AD04/SOT6/INT12

P03/AD03/SIN6/INT11

P02/AD02/SCK5/INT10

P01/AD01/SOT5/INT9

76

P26/A22/IN2

P27/A23/IN3

P30/ASX/IN4

32/WR0X/RX2/INT10R

P45/AIN2/SCL0/FRCK1

P31/RDX/IN5

P33/WR1X/TX2

P34/BRQ/OUT4

P35/BGRNTX/OUT5

P36/RDY/OUT6

P37/SYSCLK/OUT7

P40/(X0A)

P41/(X1A)

P42/IN6/RX1/INT9R

P43/IN7/TX1

P44/SDA0/FRCK0

P46/BIN2/SDA1

P47/ZIN2/SCL1

P50/AN8/SIN2

P51/AN9/SOT2

P52/AN10/SCK2

P53/AN11/BIN1

1

2

3

4

5

6

7

8

9

10

11

12

CC

V

13

V

SS

14

C

15

16

17

18

19

20

21

22

23

24

25

26272829303132333435363738394041424344454647484950

CC

AV

P56/AN14

P57/AN15

55/AN13/ZIN1

54/AN12/AIN1

AVRL

AVRH

SS

AV

LQFP-100

P60/AN0/PPG0

P61/AN1/PPG2

P62/AN2/PPG4

P63/AN3/PPG6

P64/AN4/PPG8

SS

V

65/AN5/PPGA

70/AN16/INT0

67/AN7/PPGE

66/AN6/PPGC

71/AN17/INT1

72/AN18/INT2

73/AN19/INT3

74/AN20/INT4

75/AN21/INT5

MD2

75

P00/AD00/SIN5/INT8

74

PA1/TX0

73

PA0/RX0/INT8R

72

P97/OUT3

71

P96/OUT2/ZIN0

70

P95/OUT1/BIN0

69

P94/OUT0/AIN0

68

P93/PPG7/ZIN3/CS3X

67

P92/PPG5/BIN3/CS2X

66

P91/PPG3/AIN3/CS1X

65

P90/PPG1/CS0X

SS

64

V

V

CC

63

P87/SCK1

62

P86/SOT1

61

P85/SIN1

60

P84/SCK0/INT15R

59

P83/TOT2/SOT0

58

P82/TIN2/SIN0/INT14R

57

P81/TOT0/INT13R/CKO

56

P80/TIN0/INT12R/ADTG

55

P77/AN23/INT7/SCL2

54

P76/AN22/INT6/SDA2

53

INITX

52

MD0

51

MD1

(FPT-100P-M05)

6

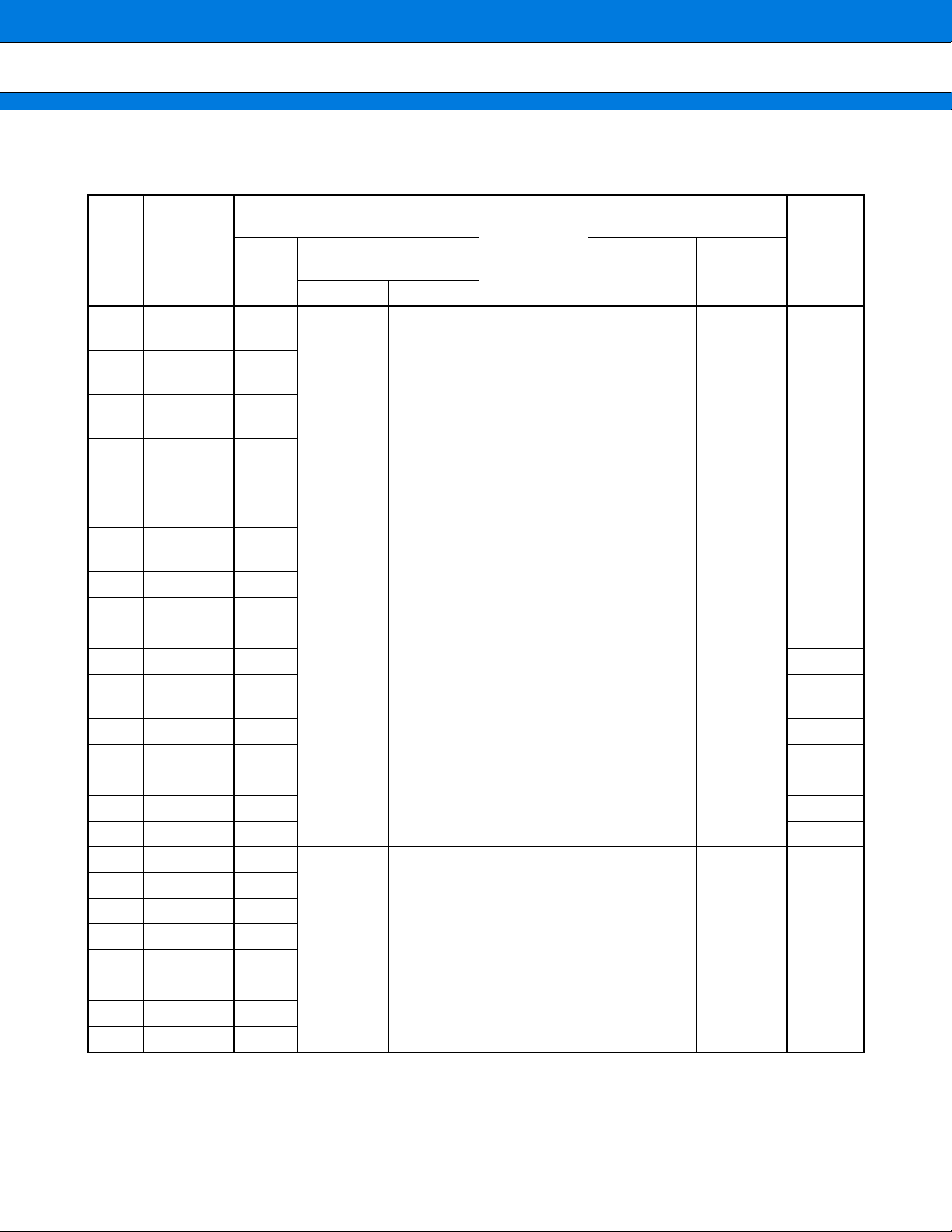

PIN FUNCTION

■

MB91270/280 Series

Pin No. Pin name

90 X1 X1 OB Oscillator output pin

91 X0 X0 OA Oscillator input pin

52 INITX INITX N Reset input pin (“L” active)

49 to 51 MD2 to MD0 MD2 to MD0 J

75

76

77

78

79

P00/AD00/

SIN5/INT8

P01/AD01/

SOT5/INT9

P02/AD02/

SCK5/INT10

P03/AD03/

SIN6/INT11

P04/AD04/

SOT6/INT12

Function

name

P00

AD00

INT8 External interrupt request 8 input pin

SIN5 Serial data input pin for LIN-UART5

P01

AD01

INT9 External interrupt request 9 input pin

SOT5 Serial data output pin for LIN-UART5

P02

AD02

INT10 External interrupt request 10 input pin

SCK5 Clock I/O pin for LIN-UART5

P03

AD03

INT11 External interrupt request 11 input pin

SIN6 Serial data input pin for LIN-UART6

P04

AD04

INT12 External interrupt request 12 input pin

SOT6 Serial data output pin for LIN-UART6

I/O circuit

type*

T

T

T

T

T

Operation mode select input pin.

Connect to V

Port 0

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 0

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 1

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 2

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 3

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 4

This function is enabled when the external bus is enabled.

or VSS directly.

CC

Function

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

(Continued)

7

MB91270/280 Series

Pin No. Pin name

80

81

82

83

84

85

86

P05/AD05/

SCK6/INT13

P06/AD06/

INT14

P07/AD07/

INT15

P10/AD08/

TIN1

P11/AD09/

TOT1

P12/AD10/

SIN3/

INT11R

P13/AD11/

SOT3

Function

name

P05

AD05

INT13 External interrupt request 13 input pin

SCK6 Clock I/O pin for LIN-UART6

P06

AD06

INT14 External interrupt request 14 input pin

P07

AD07

INT15 External interrupt request 15 input pin

P10

AD08

TIN1 Event input pin for reload timer 1

P11

AD09

TOT1 Output pin for reload timer 1

P12

AD10

SIN3 Serial data input pin for LIN-UART3

INT11R External interrupt request 11 input pin (Set by EISSR)

P13

AD11

SOT3 Serial data output pin for LIN-UART3

I/O circuit

type*

T

T

T

T

T

T

T

Function

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 5

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 6

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 7

This function is enabled when the external bus is enabled.

Port 1

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 8

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 9

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 10

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 11

This function is enabled when the external bus is enabled.

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

8

(Continued)

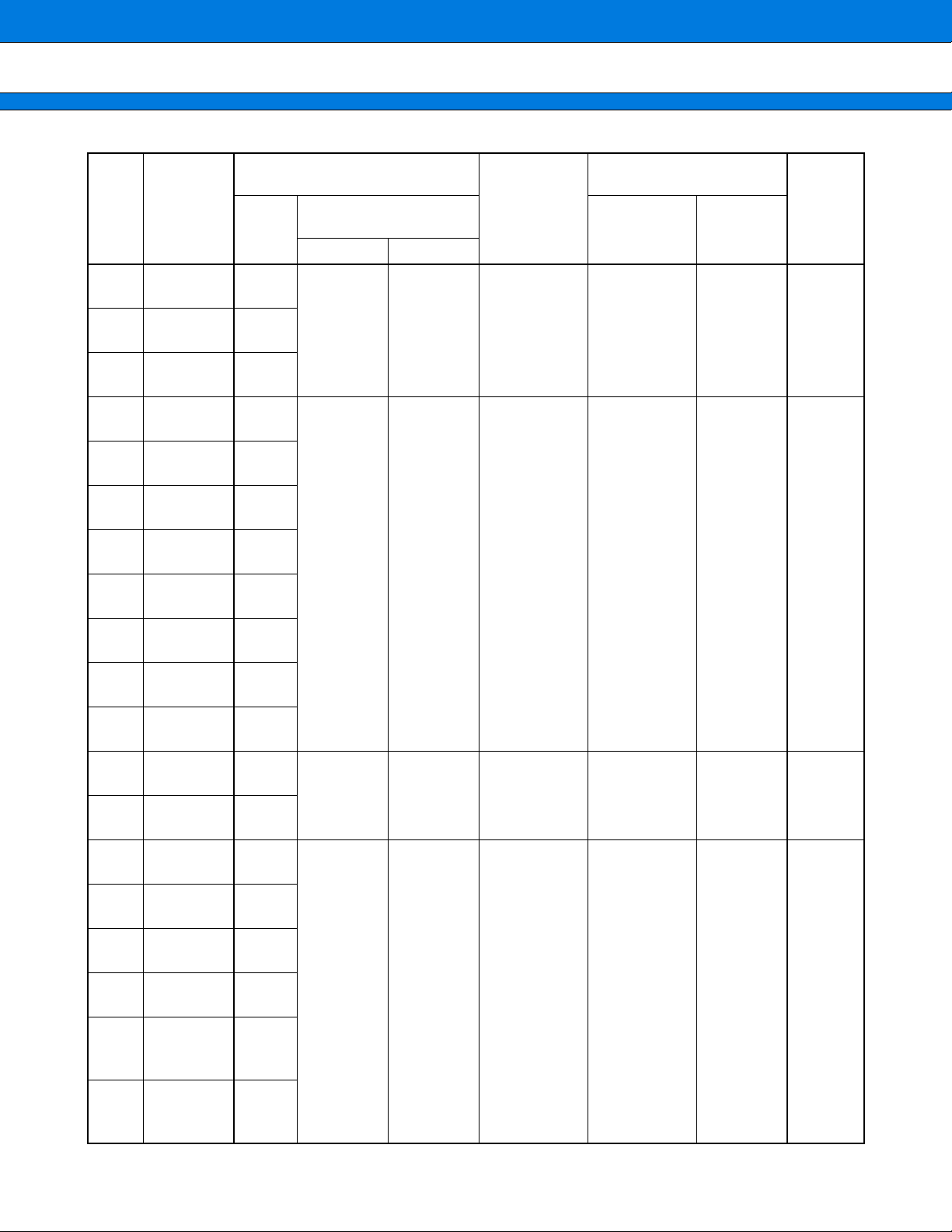

MB91270/280 Series

Pin No. Pin name

87

92

93

94

95

96

97

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

P14/AD12/

SCK3

P15/AD13/

SIN4

P16/AD14/

SOT4

P17/AD15/

SCK4

P20/A16/

PPG9

P21/A17/

PPGB

P22/A18/

PPGD

Function

name

P14

AD12

SCK3 Clock I/O pin for LIN-UART3

P15

AD13

SIN4 Serial data input pin for LIN-UART4

P16

AD14

SOT4 Serial data output pin for LIN-UART4

P17

AD15

SCK4 Clock I/O pin for LIN-UART4

P20

A16

PPG9 Output pin for PPG9

P21

A17

PPGB Output pin for PPGB

P22

A18

PPGD Output pin for PPGD

I/O circuit

type*

T

T

T

T

A

A

A

Function

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 12

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 13

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 14

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address/data bus I/O pin bit 15

This function is enabled when the external bus is enabled.

Port 2

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address bus output pin bit 16

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address bus output pin bit 17

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address bus output pin bit 18

This function is enabled when the external bus is enabled.

(Continued)

9

MB91270/280 Series

Pin No. Pin name

98

99, 100,

1, 2

3

4

5

6

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

P23/A19/

PPGF

P24/A20/IN0

to

P27/A23/IN3

P30/ASX/

IN4

P31/RDX/

IN5

P32/WR0X/

RX2/

INT10R

P33/WR1X/

TX2

Function

name

P23

A19

PPGF Output pin for PPGF

P24 to P27

A20 to A23

IN0 to IN3 Data sample input pins for input capture ICU0 to ICU3

P30

ASX

IN4 Data sample input pin for input capture ICU4

P31

RDX

IN5 Data sample input pin for input capture ICU5

P32

WR0X

RX2 CAN2 RX input pin (MB91V280 only)

INT10R External interrupt request 10 input pin (Set by EISSR)

P33

WR1X

TX2 CAN2 TX output pin (MB91V280 only)

I/O circuit

type*

A

A

A

A

A

A

Function

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address bus output pin bit 19

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address bus output pin bits 20 to 23

This function is enabled when the external bus is enabled.

Port 3

General-purpose I/O ports.

This function is enabled in single-chip mode.

External address strobe output pin

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External read strobe output pin

This function is enabled when the external bus is enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External data bus write strobe output pin. Enabled when the

external bus is enabled.

WR0X is used as the data write strobe for 8-bit access and

as the upper 8 bits of the data in 16-bit access.

General-purpose I/O ports.

This function is enabled in single-chip mode.

Write strobe output pin for lower 8 bits in external data bus

Enabled when the external bus is enabled and external bus

16-bit mode is selected.

(Continued)

10

MB91270/280 Series

Pin No. Pin name

7

8

9

10

11, 12

16

17

18

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

P34/BRQ/

OUT4

P35/

BGRNTX/

OUT5

P36/RDY/

OUT6

P37/

SYSCLK/

OUT7

P40/ (X0A) ,

P41/ (X1A)

P42/IN6/

RX1/INT9R

P43/IN7/

TX1

P44/SDA0/

FRCK0

Function

name

P34

BRQ

OUT4 Waveform output pin for output compare OCU4.

P35

BGRNTX

OUT5 Waveform output pin for output compare OCU5.

P36

RDY

OUT6 Waveform output pin for output compare OCU6.

P37

SYSCLK

OUT7 Waveform output pin for output compare OCU7.

P40, P41 A

X0A, X1A

P42

IN6 Data sample input pin for input capture ICU6

RX1 CAN1 RX input pin (MB91V280 only)

INT9R External interrupt request 9 input pin (Set by EISSR)

P43

IN7 Data sample input pin for input capture ICU7

TX1 CAN1 TX output pin (MB91V280 only)

P44

SDA0 Serial data I/O pin for I

FRCK0 16-bit input/output timer 0 input pin

I/O circuit

type*

T

(A)

A

T

A

WA

WB

A

A

C

Function

General-purpose I/O ports.

This function is enabled in single-chip mode.

External bus request input pin

Enabled when the external bus and the bus request functions are enabled.

(MB91V280 only)

General-purpose I/O ports.

This function is enabled in single-chip mode.

External bus acknowledge output pin

Enabled when the external bus and the bus request

functions are enabled.

(MB91V280 only)

General-purpose I/O ports.

This function is enabled in single-chip mode.

External ready input pin

Enabled when the external bus and the bus request functions are enabled.

General-purpose I/O ports.

This function is enabled in single-chip mode.

External clock output pin

This function is enabled when the external bus is enabled.

Port 4

General-purpose I/O ports

(S-suffix models)

sub-clock oscillator input pin

(without S-suffix models)

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

2

C0

(Continued)

11

MB91270/280 Series

Pin No. Pin name

Function

name

I/O circuit

type*

P45

19

P45/AIN2/

SCL0/

FRCK1

SCL0 Serial clock I/O pin for I

C

FRCK1 16-bit input/output timer 1 input pin

AIN2 16/8-bit up-count input pin for up down counter 2/3

P46

20

P46/BIN2/

SDA1

SDA1 Serial clock I/O pin for I

C

BIN2 16/8-bit down-count input pin for up down counter 2/3

P47

21

P47/ZIN2/

SCL1

SCL1 Serial clock I/O pin for I

C

ZIN2 16/8-bit reset input pin for up down counter 2/3

P50

22

P50/AN8/

SIN2

AN8 Analog input pin of A/D converter

D

SIN2 Serial data input pin for LIN-UART2

P51

23

P51/AN9/

SOT2

AN9 Analog input pin of A/D converter

D

SOT2 Serial data output pin for LIN-UART2

P52

24

P52/AN10/

SCK2

AN10 Analog input pin of A/D converter

D

SCK2 Clock I/O pin for LIN-UART2

P53

25

P53/AN11/

BIN1

AN11 Analog input pin of A/D converter

D

BIN1 8-bit down-count input pin for 16-bit up down counter 1

P54

26

P54/AN12/

AIN1

AN12 Analog input pin of A/D converter

D

AIN1 8-bit up-count input pin for 16-bit up down counter 1

P55

27

P55/AN13/

ZIN1

AN13 Analog input pin of A/D converter

D

ZIN1 8-bit reset input pin for 16-bit up down counter 1

P56

AN14 Analog input pin of A/D converter

E

28

P56/AN14/

DAO0

DAO0 Analog output pin 0 for D/A converter (MB91V280 only)

P57

29

P57/AN15/

DAO1

AN15 Analog input pin of A/D converter

E

DAO1 Analog output pin 1 for D/A converter (MB91V280 only)

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

General-purpose I/O ports

2

C0

General-purpose I/O ports

2

C1

General-purpose I/O ports

2

C1

Port 5

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

Function

(Continued)

12

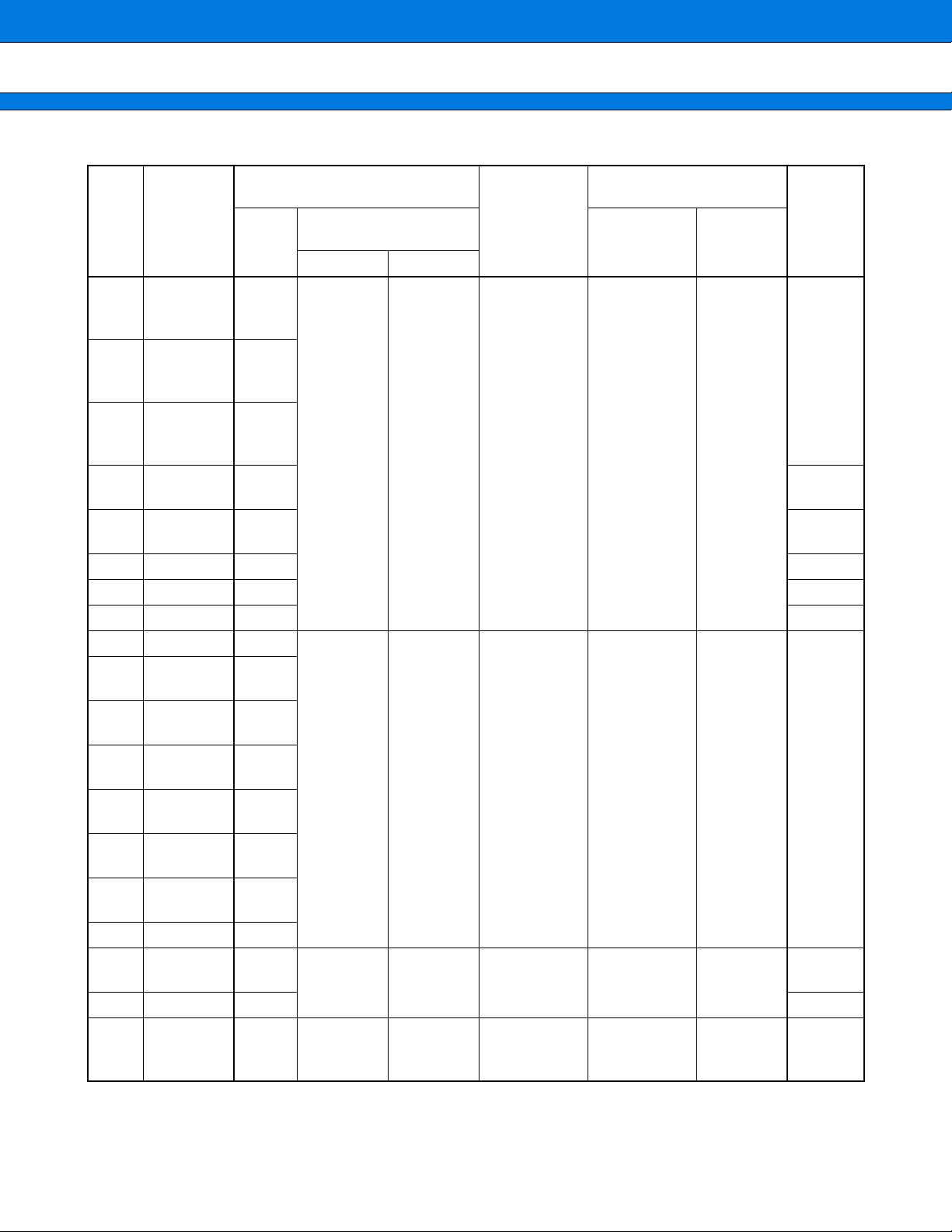

MB91270/280 Series

Pin No. Pin name

P60/AN0/

PPG0

34 to 41

43 to 48

53

54

55

56

57

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

to

P67/AN7/

PPGE

P70/AN16/

INT0

to

P75/AN21/

INT5

P76/AN22/

INT6/SDA2

P77/AN23/

INT7/SCL2

P80/TIN0/

INT12R/

ADTG

P81/TOT0/

INT13R/

CKOT

P82/TIN2/

SIN0/INT14R

Function

name

P60 to P67

AN0 to AN7 Analog input pin of A/D converter

PPG0

PPG2

PPG4

PPG6

PPG8

PPGA

PPGC

PPGE

P70 to P75

AN16 to

AN21

INT0 to INT5 External interrupt request 0 to 5 input pin

P76

AN22 Analog input pin of A/D converter

INT6 External interrupt request 6 input pin

SDA2 Serial clock I/O pin for I

P77

AN23 Analog input pin of A/D converter

INT7 External interrupt request 7 input pin

SCL2 Serial clock I/O pin for I

P80

TIN0 Event input pin for reload timer 0

ADTG Trigger input pin for A/D converter

INT12R External interrupt request 12 input pin (Set by EISSR)

P81

TOT0 Output pin for reload timer 0

CKOT Output pin for clock monitor

INT13R External interrupt request 13 input pin (Set by EISSR)

P82

SIN0 Serial data input pin for LIN-UART0

TIN2 Event input pin for reload timer 2

INT14R External interrupt request 14 input pin (Set by EISSR)

I/O circuit

type*

D

D

CA

CA

A

A

A

Function

Port 6

General-purpose I/O ports

Output pin for PPG

Port 7

General-purpose I/O ports

Analog input pin of A/D converter

General-purpose I/O ports

2

C2

General-purpose I/O ports

2

C2

Port 8

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

(Continued)

13

MB91270/280 Series

Pin No. Pin name

58

59

60 P85/SIN1

61 P86/SOT1

62 P87/SCK1

65

66

67

68

69

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

P83/TOT2/

SOT0

P84/SCK0/

INT15R

P90/PPG1/

CS0X

P91/PPG3/

AIN3/CS1X

P92/PPG5/

BIN3/CS2X

P93/PPG7/

ZIN3/CS3X

P94/OUT0/

AIN0

Function

name

P83

SOT0 Serial data output pin for LIN-UART0

TOT2 Output pin for reload timer 2

P84

SCK0 Clock I/O pin for LIN-UART0

INT15R External interrupt request 15 input pin (Set by EISSR)

P85

SIN1 Serial data input pin for LIN-UART1

P86

SOT1 Serial data output pin for LIN-UART1

P87

SCK1 Clock I/O pin for LIN-UART1

P90

CS0X

PPG1 Output pin for PPG1

P91

CS1X

PPG3 Output pin for PPG3

AIN3 8-bit up-count input pin for up down counter 3

P92

CS2X

PPG5 Output pin for PPG5

BIN3 8-bit down-count input pin for up down counter 3

P93

CS3X

PPG7 Output pin for PPG7

ZIN3 8-bit reset input pin for up down counter 3

P94

OUT0 Waveform output pin for output compare OCU0

AIN0 16/8-bit up-count input pin for up down counter 0/1

I/O circuit

type*

A

A

A

A

A

A

A

A

A

A

Function

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

Port 9

General-purpose I/O ports

External chip select 0

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External chip select 1

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External chip select 2

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External chip select 3

This function is enabled when the external bus is enabled.

General-purpose I/O ports

(Continued)

14

MB91270/280 Series

Pin No. Pin name

70

71

72 P97/OUT3

73

74 PA1/TX0

⎯ PB0

⎯ PB1

⎯ PB2

⎯ PB3

⎯ PB4

⎯ PB5

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

P95/OUT1/

BIN0

P96/OUT2/

ZIN0

PA0/RX0/

INT8R

Function

name

P95

OUT1 Waveform output pin for output compare OCU1

BIN0 16/8-bit down-count input pin for up down counter 0/1

P96

OUT2 Waveform output pin for output compare OCU2

ZIN0 16/8-bit reset input pin for up down counter 0/1

P97

OUT3 Waveform output pin for output compare OCU3

PA0

RX0 RX input pin for CAN0

INT8R External interrupt request 8 input pin (Set by EISSR)

PA1

TX0 TX output pin for CAN0

PB0

INT8-2 External interrupt request 8 input pin (Set by EPFRB)

SIN5-2 Serial data input pin for LIN-UART5 (Set by PFRB)

PB1

INT9-2 External interrupt request 9 input pin (Set by EPFRB)

SOT5-2 Serial data output pin for LIN-UART5

PB2

INT10-2 External interrupt request 10 input pin (Set by EPFRB)

SCK5-2 Clock I/O pin for LIN-UART5 (set by PFRB)

PB3

INT11-2 External interrupt request 11 input pin (Set by EPFEB)

SIN6-2 Serial data input pin for LIN-UART6 (Set by PFRB)

PB4

INT12-2 External interrupt request 12 input pin (Set by EPFRB)

SOT6-2 Serial data output pin for LIN-UART6

PB5

INT13-2 External interrupt request 13 input pin (Set by EPFRB)

SCK6-2 Clock I/O pin for LIN-UART6 (set by PFRB)

I/O circuit

type*

A

A

A

A

A

Port B (MB91V280 only)

A

A

A

A

A

A

Port C (MB91V280 only)

Function

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

Port A

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

(Continued)

15

MB91270/280 Series

Pin No. Pin name

⎯ PC0

⎯ PC1

⎯ PC2

⎯ PC3

⎯ PC4

⎯ PC5

⎯ PC6

⎯ PC7

⎯ PD0

⎯ PD1

⎯ PD2

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

Function

name

PC0

OUT4-2 Output pin for output compare 4

INT0R External interrupt request 0 input pin (Set by EISSR)

PC1

OUT5-2 Output pin for output compare 5

INT1R External interrupt request 1 input pin (Set by EISSR)

PC2

SIN3-2 Serial data input pin for LIN-UART3 (Set by PFRC)

INT2R External interrupt request 2 input pin (Set by EISSR)

PC3

SOT3-2 Serial data output pin for LIN-UART3

INT3R External interrupt request 3 input pin (Set by EISSR)

PC4

SCK3-2 Clock I/O pin for LIN-UART3 (set by PFRC)

INT4R External interrupt request 4 input pin (Set by EISSR)

PC5

SIN4-2 Serial data input pin for LIN-UART4 (Set by PFRC)

INT5R External interrupt request 5 input pin (Set by EISSR)

PC6

SOT4-2 Serial data output pin for LIN-UART4

INT6R External interrupt request 6 input pin (Set by EISSR)

PC7

SCK4-2 Clock I/O pin for LIN-UART4 (set by PFRC)

INT7R External interrupt request 7 input pin (Set by EISSR)

PD0

INT16 External interrupt request 16 input pin

PPG9-2 Output pin for PPG9 (8)

PD1

INT17 External interrupt request 17 input pin

PPGB-2 Output pin for PPGB (A)

PD2

INT18 External interrupt request 18 input pin

PPGD-2 Output pin for PPGD (C)

I/O circuit

type*

A

A

A

A

A

A

A

A

Port D (MB91V280 only)

A

A

A

Function

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

(Continued)

16

MB91270/280 Series

Pin No. Pin name

⎯ PD3

⎯ PD4

⎯ PD5

⎯ PD6

⎯ PD7

⎯ PE0

⎯ PE1

⎯ PE2

⎯ PE3

⎯ PE4

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

Function

name

PD3

INT19 External interrupt request 19 input pin

PPGF-2 Output pin for PPGF (E)

PD4

INT20 External interrupt request 20 input pin

IN0-2 Input pin for input capture ICU0 (set by PFRD)

PD5

INT21 External interrupt request 21 input pin

IN1-2 Input pin for input capture ICU1 (set by PFRD)

PD6

INT22 External interrupt request 22 input pin

IN2-2 Input pin for input capture ICU2 (set by PFRD)

PD7

INT23 External interrupt request 23 input pin

IN3-2 Input pin for input capture ICU3 (set by PFRD)

PE0

A00

INT24 External interrupt request 24 input pin

PE1

A01

INT25 External interrupt request 25 input pin

PE2

A02

INT26 External interrupt request 26 input pin

PE3

A03

INT27 External interrupt request 27 input pin

PE4

A04

INT28 External interrupt request 28 input pin

I/O circuit

type*

A

A

A

A

A

Port E (MB91V280 only)

A

A

A

A

A

Function

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

General-purpose I/O ports

External address bus output pin bit 0

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 1

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 2

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 3

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 4

This function is enabled when the external bus is enabled.

(Continued)

17

MB91270/280 Series

Pin No. Pin name

⎯ PE5

⎯ PE6

⎯ PE7

⎯ PF0

⎯ PF1

⎯ PF2

⎯ PF3

⎯ PF4

⎯ PF5

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

Function

name

PE5

A05

INT29 External interrupt request 29 input pin

PE6

A06

INT30 External interrupt request 30 input pin

PE7

A07

INT31 External interrupt request 31 input pin

PF0

A08

INT32 External interrupt request 32 input pin

PF1

A09

INT33 External interrupt request 33 input pin

PF2

A10

INT34 External interrupt request 34 input pin

PF3

A11

INT35 External interrupt request 35 input pin

PF4

A12

INT36 External interrupt request 36 input pin

PF5

A13

INT37 External interrupt request 37 input pin

I/O circuit

type*

A

A

A

Port F (MB91V280 only)

A

A

A

A

A

A

Function

General-purpose I/O ports

External address bus output pin bit 5

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 6

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 7

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 8

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 9

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 10

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 11

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 12

This function is enabled when the external bus is enabled.

General-purpose I/O ports

External address bus output pin bit 13

This function is enabled when the external bus is enabled.

(Continued)

18

MB91270/280 Series

(Continued)

Pin No. Pin name

Function

name

PF6

⎯ PF6

A14

INT38 External interrupt request 38 input pin

PF7

⎯ PF7

A15

INT39 External interrupt request 39 input pin

PG0

⎯ PG0

AN24 Analog input pin of A/D converter

PG1

⎯ PG1

AN25 Analog input pin of A/D converter

PG2

⎯ PG2

AN26 Analog input pin of A/D converter

PG3

⎯ PG3

AN27 Analog input pin of A/D converter

PG4

⎯ PG4

AN28 Analog input pin of A/D converter

PG5

⎯ PG5

AN29 Analog input pin of A/D converter

PG6

⎯ PG6

AN30 Analog input pin of A/D converter

PG7

⎯ PG7

AN31 Analog input pin of A/D converter

13, 63, 88 V

14, 42,

64, 89

CC

SS

V

⎯⎯Power supply (5 V) input pin

⎯⎯Power supply (0 V) input pin

15 C ⎯⎯Power stabilization capacitance pin

30 AV

CC

⎯⎯Analog power supply input pin

31 AVRH ⎯⎯

32 AVRL ⎯⎯Low reference voltage input pin for the A/D converter

33 AV

SS

⎯⎯Analog V

I/O circuit

type*

General-purpose I/O ports

A

External address bus output pin bit 14

This function is enabled when the external bus is enabled.

General-purpose I/O ports

A

External address bus output pin bit 15

This function is enabled when the external bus is enabled.

Port G (MB91V280 only)

General-purpose I/O ports

D

General-purpose I/O ports

D

General-purpose I/O ports

D

General-purpose I/O ports

D

General-purpose I/O ports

D

General-purpose I/O ports

D

General-purpose I/O ports

D

General-purpose I/O ports

D

Power supply pin

Reference voltage input pin for the A/D converter

Ensure that a voltage greater than AVRH is applied to AV

when turning this power supply on or off.

input pin

SS

Function

CC

* : See “■ I/O CIRCUIT TYPE” for the I/O circuit type.

19

MB91270/280 Series

ut

ut

ut

ut

ut

ut

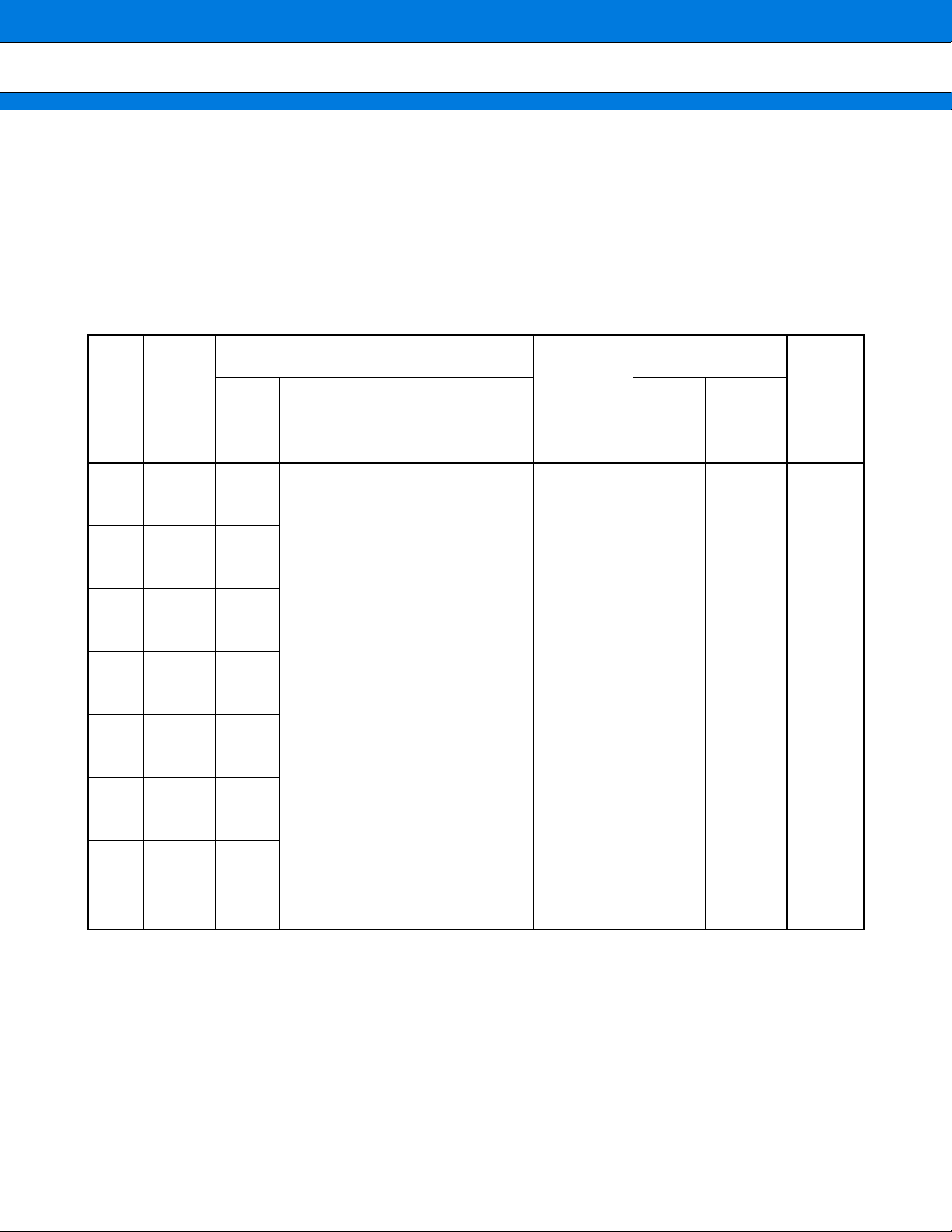

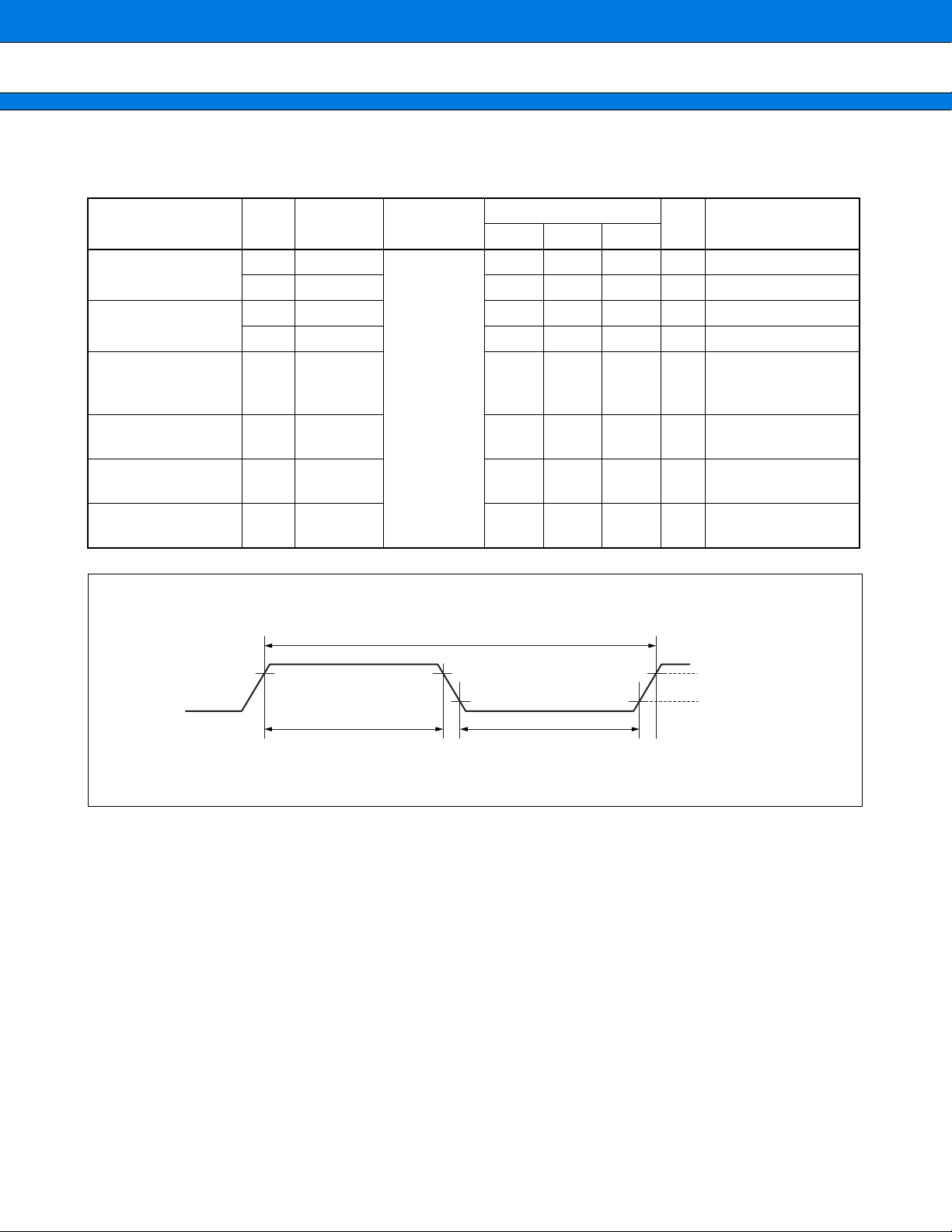

I/O CIRCUIT TYPE

■

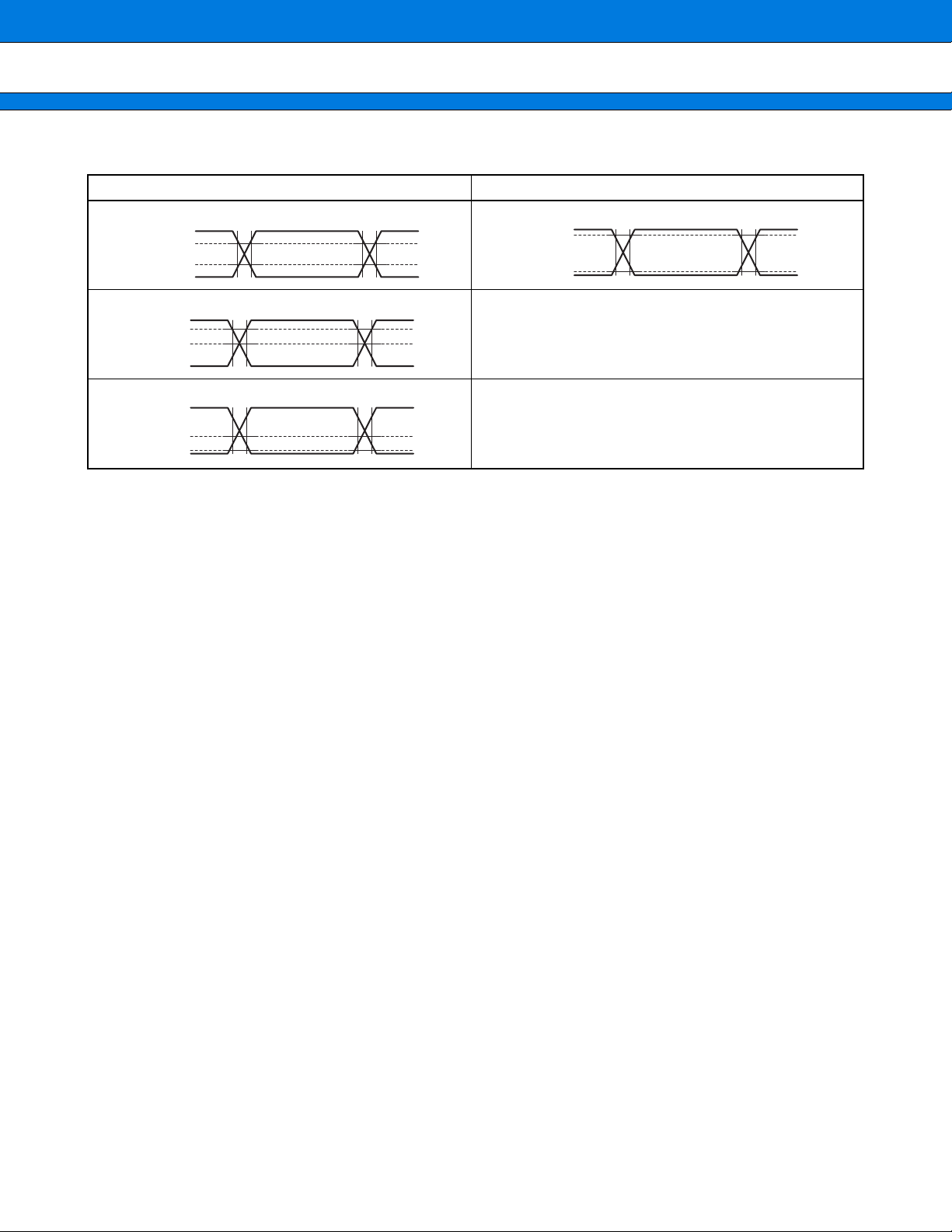

Type Circuit Remarks

Pull-up control

P-ch

N-ch

P-ch

N-ch

Po

No

A

Pull-down control

CMOS hysteresis input

Automotive input

Standby control for

disconnect input

P-ch

N-ch

Po

No

B

CMOS hysteresis input

• CMOS level output

(I

= 4 mA, IOH = −4 mA)

OL

• CMOS hysteresis input

(With function to disconnect

input during standby mode. )

• Automotive input

(With function to disconnect

input during standby mode. )

• Resistor that can be set

pull-up resistor : Approx. 50 Ω

• CMOS level output

(I

= 4 mA, IOH = −4 mA)

OL

• CMOS hysteresis input

(With function to disconnect

input during standby mode. )

• Automotive input

(With function to disconnect

input during standby mode. )

20

Automotive input

Standby control for

disconnect input

P-ch

Po

• CMOS level output

(I

= 3 mA, IOH = −3 mA)

OL

• CMOS hysteresis input

(With function to disconnect

N-ch

No

input during standby mode. )

• Automotive input

C

CMOS hysteresis input

Automotive input

Standby control for

(With function to disconnect

input during standby mode. )

disconnect input

(Continued)

MB91270/280 Series

ut

ut

ut

ut

Type Circuit Remarks

CA

P-ch

N-ch

Po

No

CMOS hysteresis input

Automotive input

Standby control for

disconnect input

Analog input

• CMOS level output

(I

= 3 mA, IOH = −3 mA)

OL

• CMOS hysteresis input

(With function to disconnect

input during standby mode. )

• Automotive input

(With function to disconnect

input during standby mode. )

• A/D analog input

Pull-up control

• CMOS level output

(I

= 4 mA, IOH = −4 mA)

OL

• CMOS hysteresis input

(With function to disconnect

P-ch

P-ch

Po

input during standby mode. )

• Automotive input

N-ch

N-ch

No

(With function to disconnect

input during standby mode. )

• Resistor that can be set

D

Pull-down control

pull-up resistor : Approx. 50 Ω

• A/D analog input

CMOS hysteresis input

Automotive input

Standby control for

disconnect input

Analog input

(Continued)

21

MB91270/280 Series

ut

ut

ut

ut

Type Circuit Remarks

P-ch

N-ch

Po

No

CMOS hysteresis input

E

Automotive input

Standby control for

disconnect input

Analog input

Analog output

• CMOS level output

(I

= 4 mA, IOH = −4 mA)

OL

• CMOS hysteresis input

(With function to disconnect

input during standby mode. )

• Automotive input

(With function to disconnect

input during standby mode. )

• A/D analog input

• D/A analog output

J

CMOS hysteresis input

CMOS hysteresis input

• CMOS hysteresis input

• Pull-up resistor value :

N

Pull-up resistor

Approx. 50 kΩ

CMOS hysteresis input

Pull-up control

• CMOS level output

(I

= 4 mA, IOH = −4 mA)

OL

• CMOS hysteresis input

(With function to disconnect

P-ch

P-ch

Po

input during standby mode. )

• Automotive input

N-ch

N-ch

No

(With function to disconnect

input during standby mode. )

T

Pull-down control

CMOS hysteresis input

•TTL

(With function to disconnect

input during standby mode. )

• Resistor that can be set

pull-up resistor : Approx. 50 kΩ

Automotive input

22

TTL input

Standby control for

disconnect input

(Continued)

MB91270/280 Series

utX

X

l

utX

X

l

(Continued)

Type Circuit Remarks

OA

OB

1

0

Xo

Standby control signa

Oscillation circuit

High speed oscillation feedback resistance =

Approx. 1 MΩ

WA

WB

1A

Xo

Oscillation circuit

Low speed oscillation feedback

resistance = Approx. 10 MΩ

0A

Standby control signa

23

MB91270/280 Series

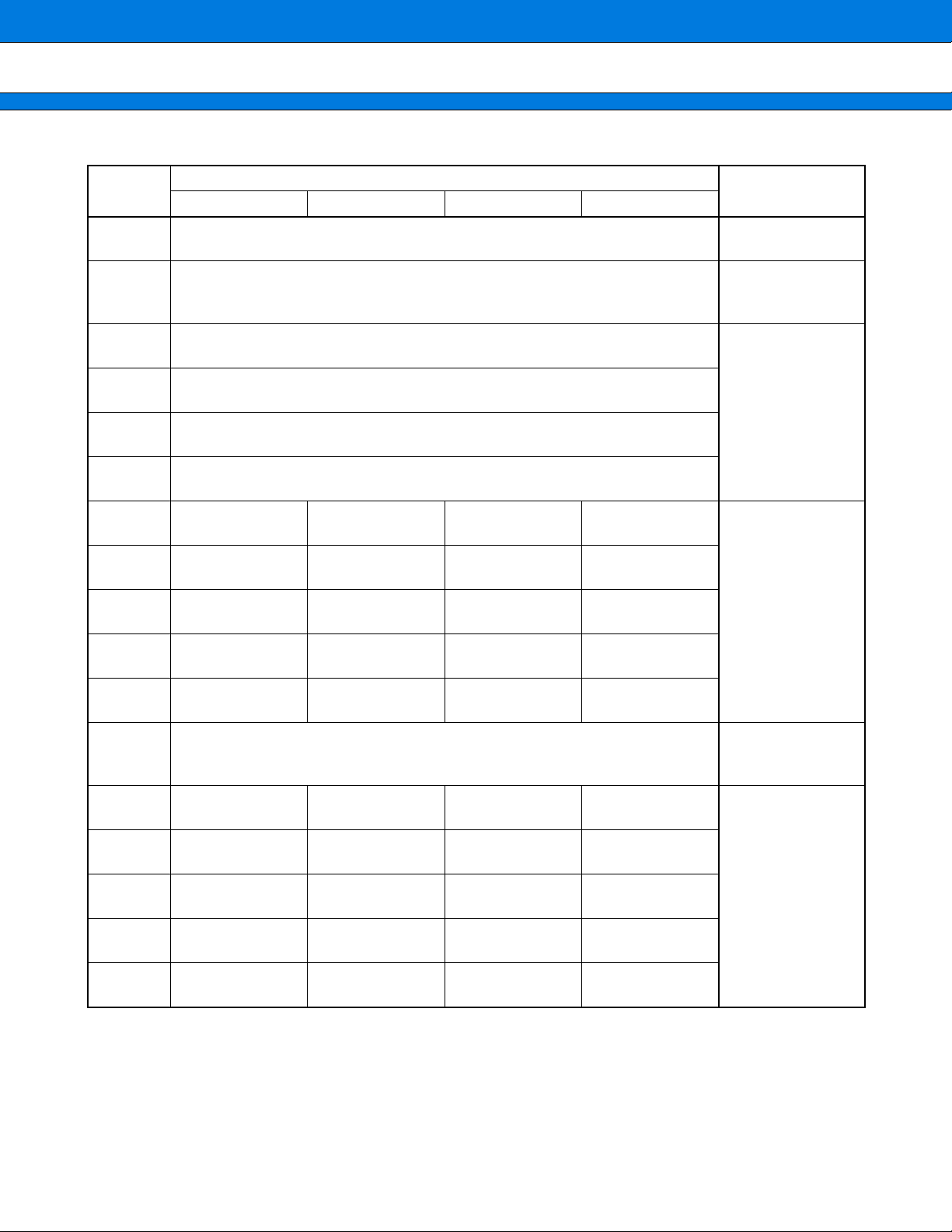

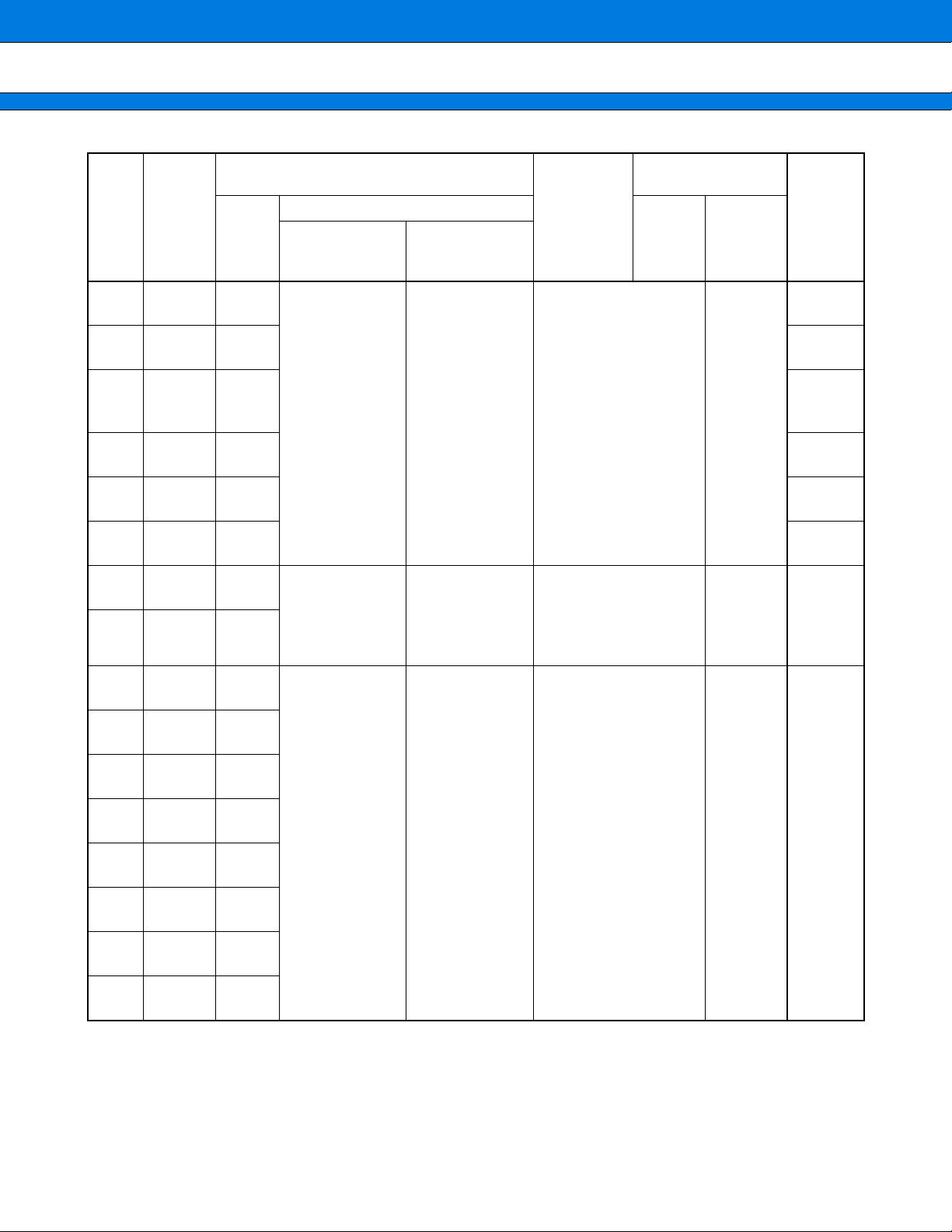

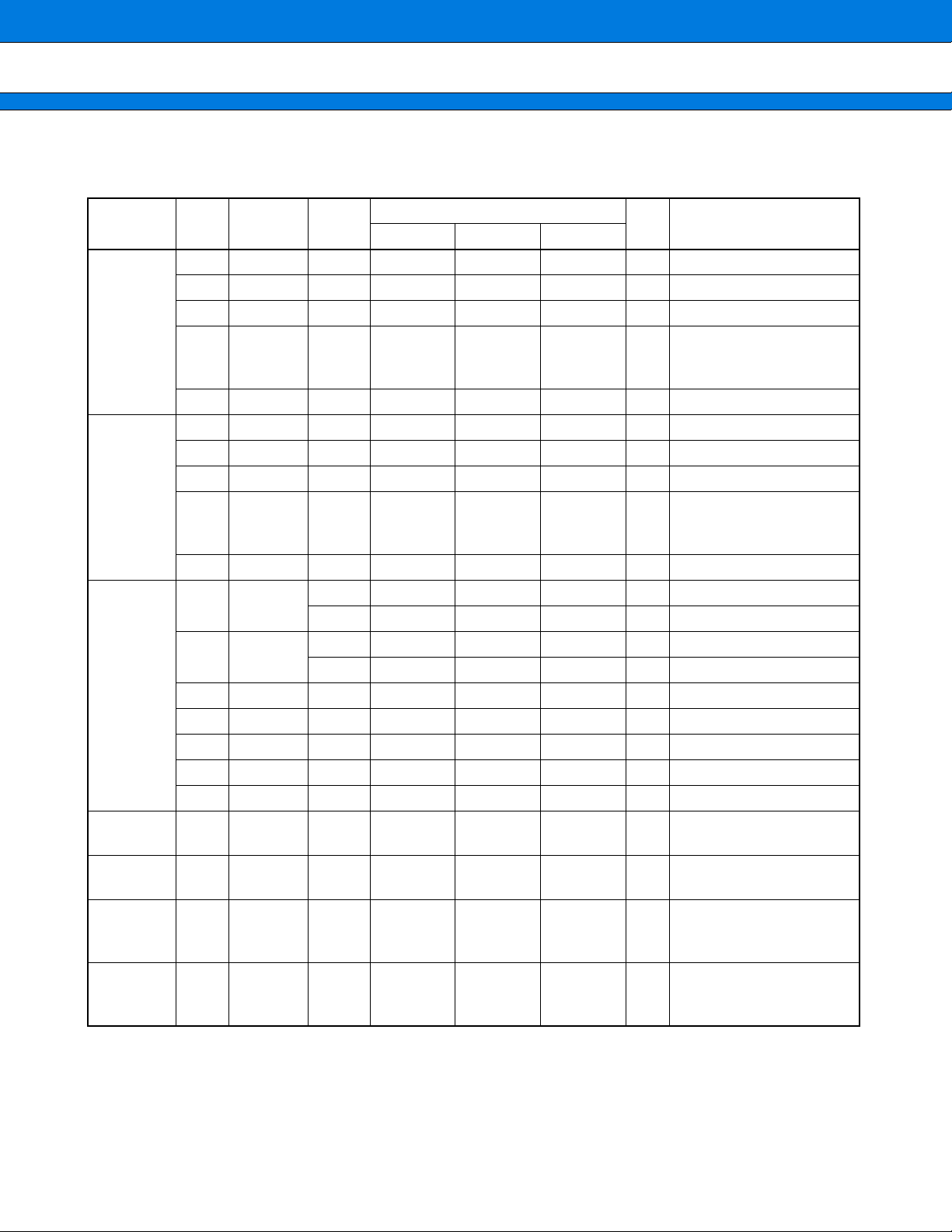

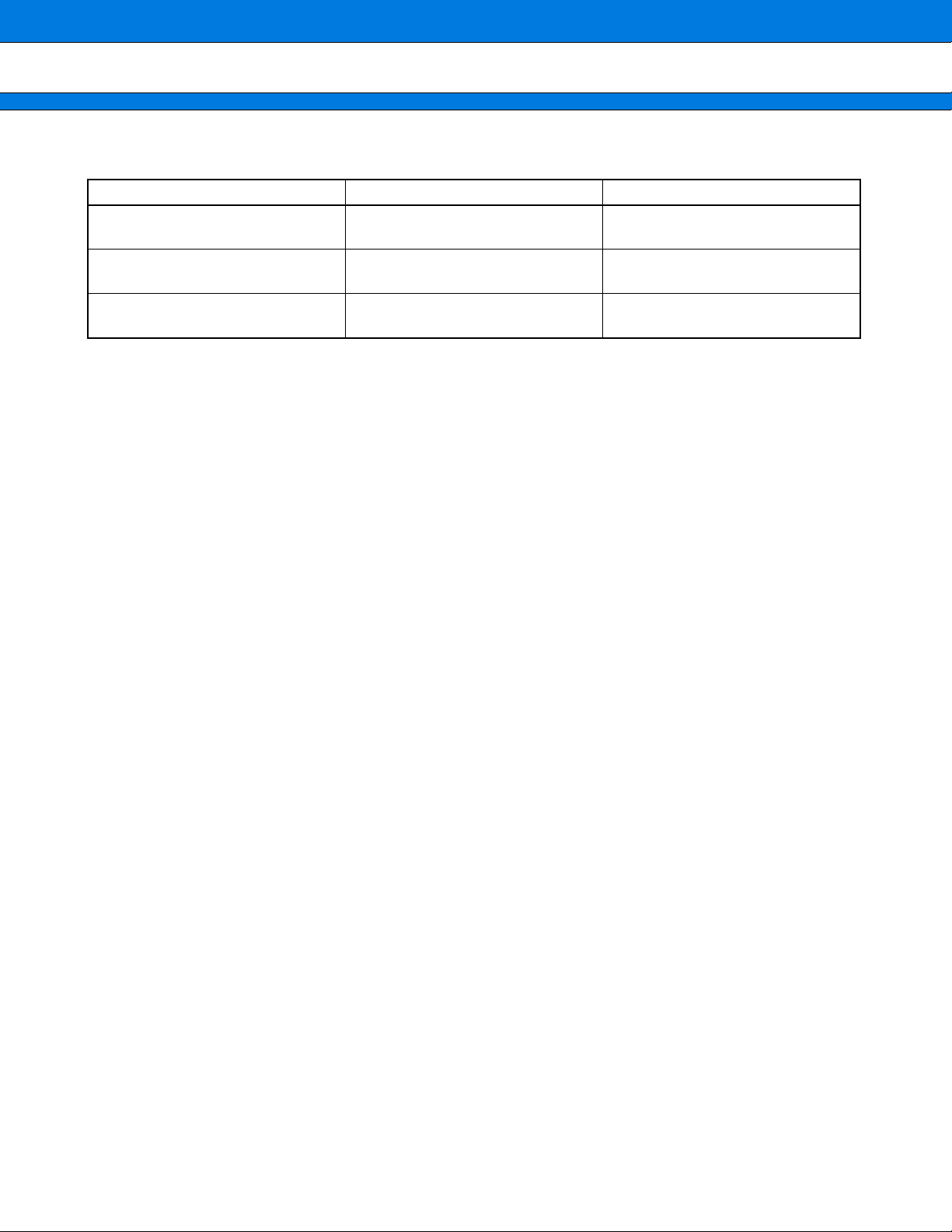

I/O CELL LIST

■

Input

Type

Pull Up/Down

(50 kΩ)

CMOS (C)

CMOS Schmitt (CS)

Automotive (A)

Input Stop

Analog Line

A Up/Down switch CS/A switch Stop ⎯ 4 mA

B ⎯ CS/A switch Stop ⎯ 4 mA

C* ⎯ CS/A switch Stop ⎯ 3 mA I

CA* ⎯ CS/A switch Stop Input 3 mA I

D Up/Down switch CS/A switch Stop Input 4 mA ADC

E ⎯ CS/A switch Stop I/O 4 mA ADC + DAC

J ⎯ C ⎯⎯⎯MD[2 : 0]

N Up CS (initx) ⎯⎯⎯INITX

T Up/Down switch CS/A/TTL switch Stop ⎯ 4 mA

OA

OB

WA

WB

⎯⎯Stop ⎯⎯

⎯⎯Stop ⎯⎯

Output Driv-

er

Remarks

2

Has TTL

Oscillator

Oscillator

2

C

C + ADC

input

4 MHz

32 kHz

* : When the C and CA ports are set for use as an I2C interface, the outputs are Nch open drain outputs.

Otherwise, functions as a CMOS output.

PIN INPUT VOLTAGE

■

Form Type V

IL

V

C CMOS input VSS + 0.3 V VCC − 0.3 V

CS (initx) CMOS Schmitt trigger input (for INITX pin) 0.2 × V

CS CMOS Schmitt trigger input 0.3 × V

A CMOS automotive Schmitt trigger input 0.5 × V

CC

CC

CC

0.8 × V

0.7 × V

0.8 × V

T TTL input 0.8 V 2.1 V

IH

CC

CC

CC

24

MB91270/280 Series

HANDLING DEVICES

■

• Preventing Latch-up

Latch-up may occur in a CMOS IC if a voltage greater than V

pin or if an above-rating voltage is applied between V

CC

increases the power supply current and may cause thermal destruction of an element. When you use a CMOS

IC, do not exceed the maximum rating.

• Treatment of Unused Pins

Do not leave an unused input pin open, since it may cause a malfunction. Handle by, for example, using a pull-

up or pull-down resistor.

• About Power Supply Pins

In products with multiple V

or VSS pins, the pins of the same potential are internally connected in the device

CC

to avoid abnormal operations including latch-up. However, you must connect the pins to external power supply

and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals

caused by the rise in the ground level, and to conform to the total output current rating.

or less than VSS is applied to an input or output

CC

pin and VSS pin. A latch-up, if it occurs, significantly

Moreover, connect the current supply source with the V

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1 µF between V

and VSS pins of this device at the low impedance.

CC

and VSS near

CC

this device.

• About Crystal Oscillator Circuit

Noise near the X0, X1, X0A and X1A pins may cause the device to malfunction. Design the printed circuit board

so that X0, X1, X0A and X1A the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground

are located as close to the device as possible.

It is strongly recommended to design the PC board artwork with the X0, X1, X0A and X1A pins surrounded by

ground plane because stable operation can be expected with such a layout.

Please ask the crystal maker to evaluate the oscillational characteristics of the crystal and this device.

• Notes on Using External Clock

When external clock is selected, supply it to X0 pin generally, and simultaneously the opposite phase clock to

X0 must be supplied to X1 pin. However, in this case the stop mode (oscillation stop mode) must not be used.

(This is because the X1 pin stops at High level output in STOP mode.)

Using an external clock (normal)

X0

Note : The STOP mode (oscillation stop mode) cannot be used.

• Notes when using no sub-clock

Use a single-clock model if not using the sub-clock.

X1

25

MB91270/280 Series

Always connect a resonator of 100 kHz or less on dual clock models.

• Treatment of N.C. or OPEN pins

Pins marked as N.C. and OPEN must be left open - circuit.

• About Mode pins (MD0 to MD2)

These pins should be connected directly to V

due to noise, design the printed circuit board such that the distance between the mode pins and V

as short as possible and the connection impedance is low.

• Operation at start-up

The INITX pin must be held at the “L”level when turning on the power.

• Source oscillation input at power on

When turning the power on, maintain clock input until the device is released from the oscillation stabilization

wait state.

or VSS. To prevent the device erroneously switching to test mode

CC

CC

or VSS is

• Caution on Operations during PLL Clock Mode

Even if the oscillator comes off or the clock input stops with the PLL clock selected for this microcontroller, the

microcontroller may continue to operate at the free-running frequency of the PLL’s internal self-oscillating oscillator circuit.

Performance of this operation, however, cannot be guaranteed.

• External bus setting

This device is guaranteed for use with a 16 MHz external bus.

If the base clock is set to 32 MHz with DIVR1 (external bus base clock division setting register) set to its initial

value, the external bus also operates at 32 MHz. When changing the base clock, first set the external bus so

that it will not exceed 16 MHz.

• Pull-up control

The AC characteristics cannot be guaranteed if pull-up resistors are used for pins used as external bus pins.

26

BLOCK DIAGRAM

■

MB91270/280 Series

Clock generator

Bit search

module

Debug

support

DMA

controller

External bus

24-bit address

16-bit data

Clock

supervisor

LIN-

UART0

32

D-bus

32

External bus I/F

FR 60 Lite

CPU CORE

Harvard bus

converter

32

Hardware

watchdog

R-bus

32

I-bus

Flash/

MASK ROM

32

R-bus

adapter

16

Watchdog

timer

F-bus

Voltage

regulator

F-bus-

RAM

CAN

DAC

ADC

sub-clock

LIN-

UART

I2C

400 kHz

External interrupt

Reload timer

ICU

16 bits

Clock

monitor

Free-run timer

Up down counter

8/16 bits

Real time

clock

Output Compare

16 bits

PPG

8/16 bits

27

MB91270/280 Series

0

0

0

0

0

0

0

0

0

F

0

0

0

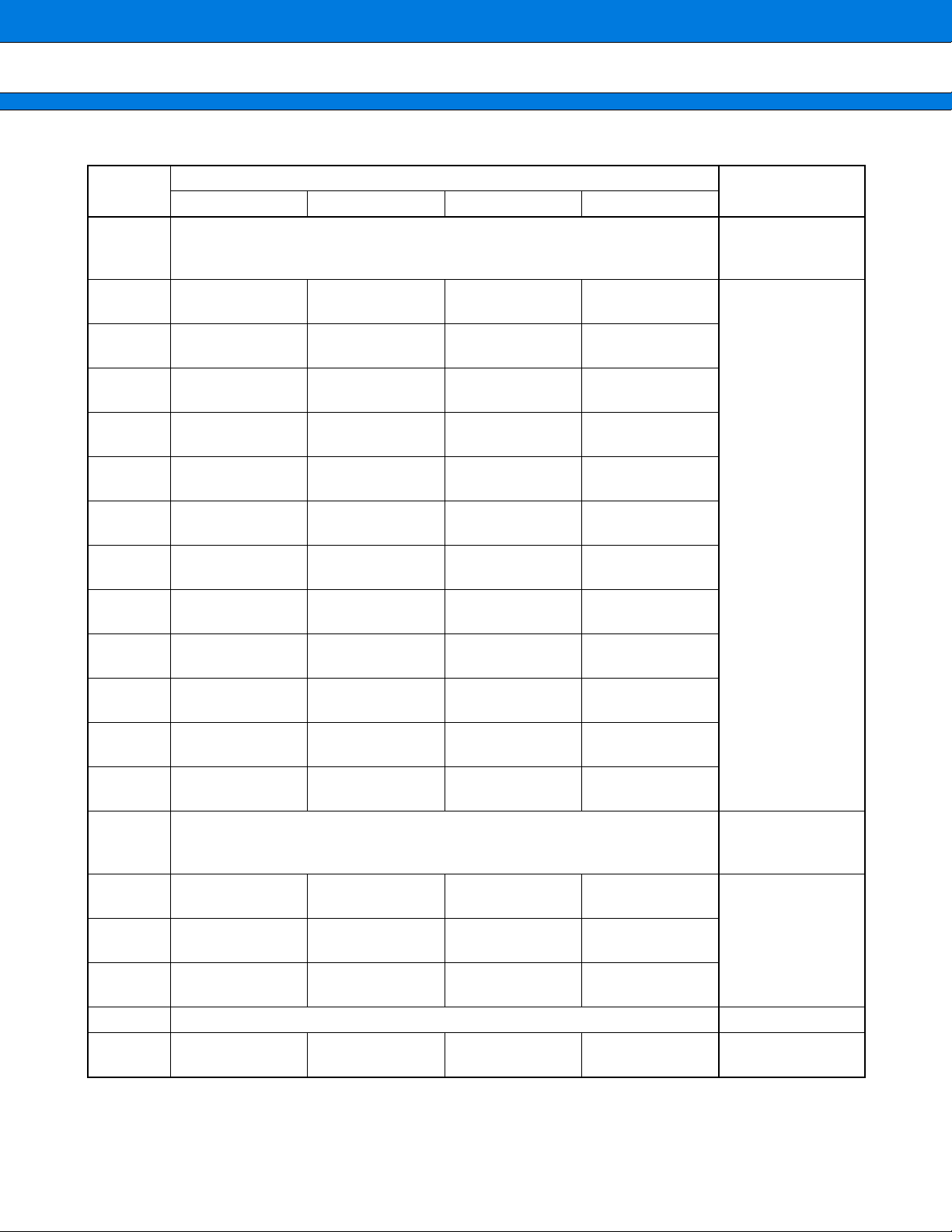

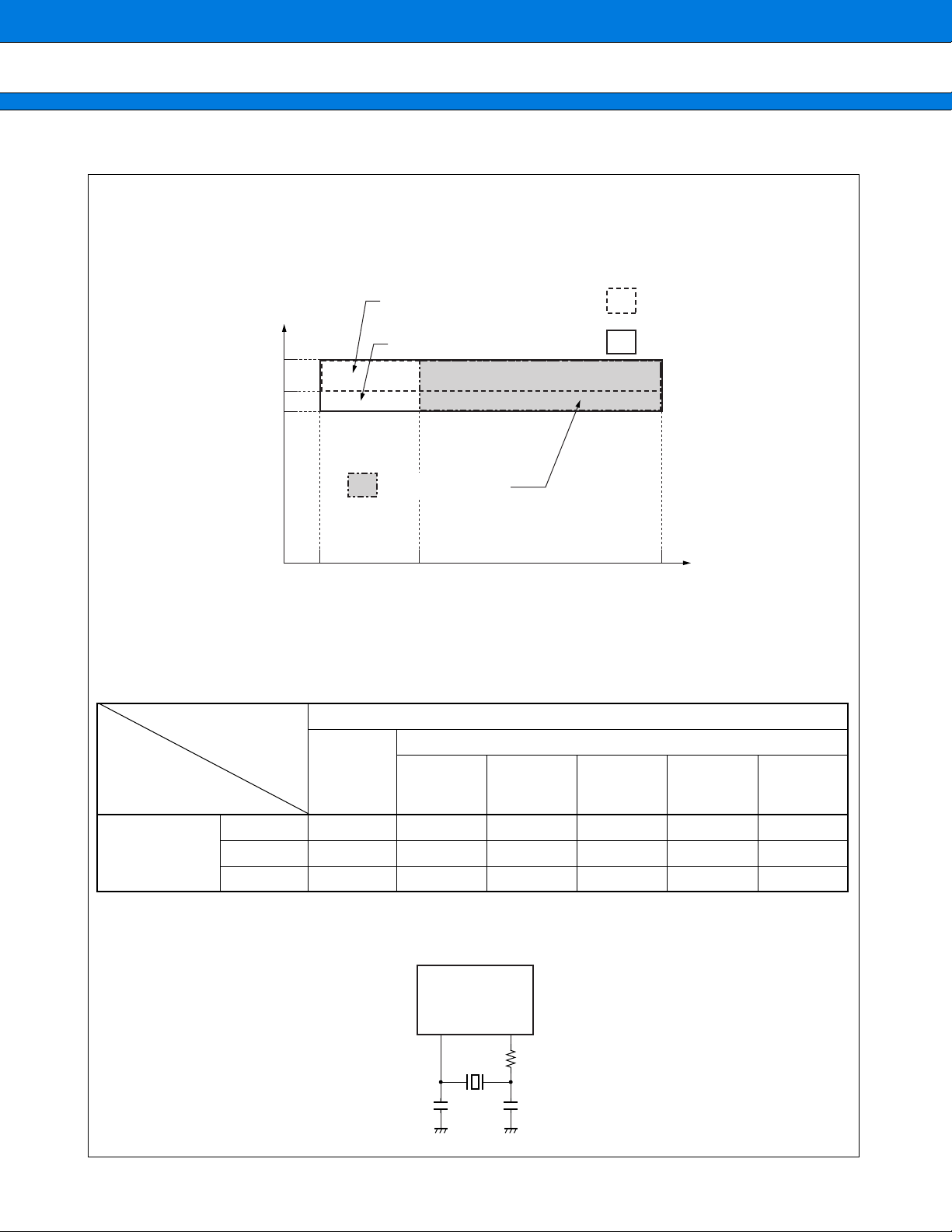

MEMORY MAP

■

MB91V280 MB91F272 (S)

000 0000

000 0400

001 0000

002 0000

002 0500

003 4000

003 8000

003 D800

004 0000

H

H

H

H

H

H

H

H

H

I/O

I/O

CAN

Access prohibited

Built-in RAM

48 Kbytes

I/O

I/O

Access prohibitedAccess prohibited

CAN

Access prohibited

Built-in RAM

10 Kbytes

Direct

addressing area

Refer to “■I/O Map”

H

Access prohibited

Emulation

SRAM area

External area

Access prohibited

Flash

256 Kbytes

External area

008 0000

00C 0000

010 0000

FFF FFFF

H

H

H

Note : The initial value for the emulation SRAM area on the MB91V280 is 512 Kbytes (0X080000H to 0X100000H).

An SRAM area of up to 1024 Kbytes is supported (0X050000

to 0X150000H)

H

28

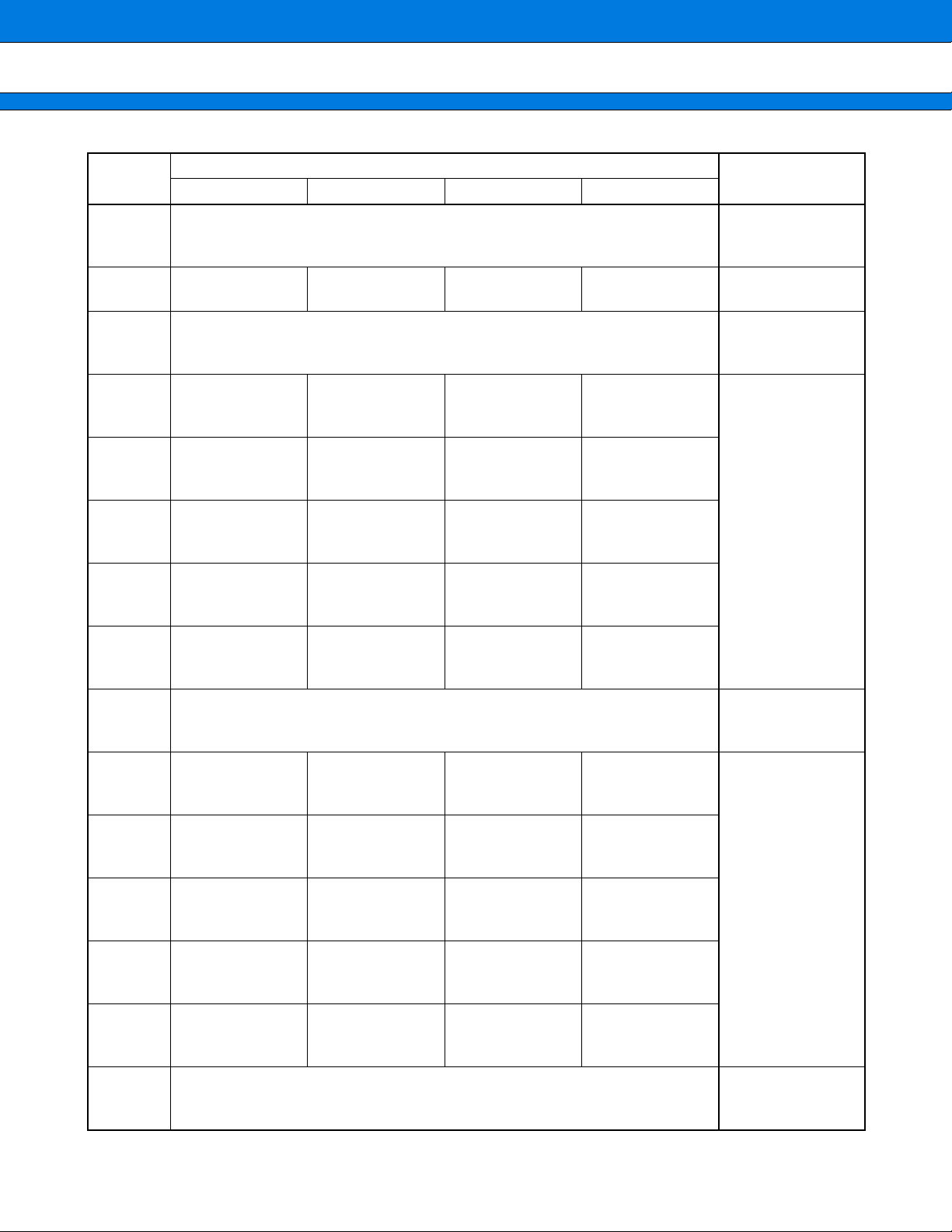

I/O MAP

r

■

How to read I/O map

Address

000000

Initial values of register bits are represented as follows

•“1” : Initial value“1”

H

+

0

PDR0 [R/W] B

XXXXXXXX

+

1

PDR1 [R/W] B

XXXXXXXX

Read/write attribute, Access unit

(B: Byte, H: Half word, W: Word)

Initial value of register after a reset

Register name (First-column register at address 4n; second-column registe

at address 4n + 1)

Address of left - most register (When using word access, the register

in column 1 is in the MSB side of the data.)

Register

PDR2 [R/W] B

MB91270/280 Series

+

2

XXXXXXXX

+

3

PDR3 [R/W] B

XXXXXXXX

Block

T-unit

Port data regis-

ter

•“0” : Initial value“0”

•“X” : Initial value“X”

• “-” : No physical register is present at the location (access prohibited) .

29

MB91270/280 Series

Address

000000

000004

000008

00000C

000010

000014

to

00003C

000040

000044

000048

00004C

000050

000054

000058

00005C

000060

000064

000068

00006C

+

PDR0 [R/W] B, H

H

XXXXXXXX

PDR4 [R/W] B, H

H

XXXXXXXX

PDR8 [R/W] B, H

H

XXXXXXXX

PDRC [R/W] B, H

H

XXXXXXXX

PDRG [R/W] B, H

H

XXXXXXXX

H

H

EIRR0 [R/W]

H

H

H

H

H

H

H

H

H

H

H

H

00000000

DICR [R/W]

-------0

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

⎯⎯

SCR0 [R, R/W]

00000000

ESCR0 [R/W]

00000100

SCR5 [R, R/W]

00000000

ESCR5 [R/W]

00000100

0

TMRLR0 [W]

TMRLR1 [W]

TMRLR2 [W]

+

1

PDR1 [R/W] B, H

XXXXXXXX

PDR5 [R/W] B, H

XXXXXXXX

PDR9 [R/W] B, H

XXXXXXXX

PDRD [R/W] B, H

XXXXXXXX

⎯⎯⎯

ENIR [R/W]

00000000

HRCL [R, R/W]

0--11111

⎯

⎯

SMR0 [W, R/W]

00000000

ECCR0

[R, W, R/W]

000000XX

SMR5 [W, R/W]

00000000

ECCR5

[R, W, R/W]

000000XX

Register

Block

+

2

PDR2 [R/W] B, H

XXXXXXXX

PDR6 [R/W] B, H

XXXXXXXX

PDRA [R/W] B, H

------XX

PDRE [R/W] B, H

XXXXXXXX

PDR3 [R/W] B, H

PDR7 [R/W] B, H

PDRB [R/W] B, H

PDRF [R/W] B, H

+

3

XXXXXXXX

XXXXXXXX

--XXXXXX

XXXXXXXX

Port Data

Registers

(PDRB to PDRG

are only available

on the MB91V280.)

⎯ System Reserved

ELVR0 [R/W]

00000000 00000000

Ext. INT 0-7

⎯⎯DLY / I-Unit

TMR0 [R]

XXXXXXXX XXXXXXXX

Reload Timer 0

TMCSR0 [R, RW]

00000000 00000000

TMR1 [R]

XXXXXXXX XXXXXXXX

Reload Timer 1

TMCSR1 [R, RW]

00000000 00000000

TMR2 [R]

XXXXXXXX XXXXXXXX

Reload Timer 2

TMCSR2 [R, RW]

00000000 00000000

SSR0 [R, R/W]

00001000

RDR0/TRD0

[R/W]

00000000

LIN-UART 0

BGR10 [R/W]

00000000

SSR5 [R, R/W]

00001000

BGR00 [R/W]

00000000

RDR5/TRD5

[R/W]

00000000

LIN-UART 5

BGR15 [R/W]

00000000

BGR05 [R/W]

00000000

30

(Continued)

MB91270/280 Series

Address

000070

000074

000078

to

0000AC

0000B0

0000B4

0000B8

0000BC

0000C0

0000C4

0000C8

0000CC

0000D0

0000D4

0000D8

0000DC

0000E0

SCR6 [R, R/W]

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

00000000

ESCR6 [R/W]

00000100

SCR1 [R, R/W]

00000000

ESCR1 [R/W]

00000100

SCR2 [R, R/W]

00000000

ESCR2 [R/W]

00000100

SCR3 [R, R/W]

00000000

ESCR3 [R/W]

00000100

SCR4 [R, R/W]

00000000

ESCR4 [R/W]

00000100

EIRR1 [R/W]

00000000

+

0

SMR6 [W, R/W]

00000000

ECCR6

[R, W, R/W]

000000XX

SMR1 [W, R/W]

00000000

ECCR1

[R, W, R/W]

000000XX

SMR2 [W, R/W]

00000000

ECCR2

[R, W, R/W]

000000XX

SMR3 [W, R/W]

00000000

ECCR3

[R, W, R/W]

000000XX

SMR4 [W, R/W]

00000000

ECCR4

[R, W, R/W]

000000XX

ENIR1 [R/W]

00000000

TCTDT0 [R/W] H

00000000 00000000

TCTDT1 [R/W] H

00000000 00000000

TCTDT2 [R/W] H

00000000 00000000

TCTDT3 [R/W] H

00000000 00000000

+

1

Register

Block

+

2

SSR6 [R, R/W]

00001000

+

3

RDR6/TRD6

[R/W]

00000000

LIN-UART 6

BGR16 [R/W]

00000000

BGR06 [R/W]

00000000

⎯ System Reserved

SSR1 [R, R/W]

00001000

RDR1/TRD1

[R/W]

00000000

LIN-UART 1

BGR11 [R/W]

00000000

SSR2 [R, R/W]

00001000

BGR01 [R/W]

00000000

RDR2/TRD2

[R/W]

00000000

LIN-UART 2

BGR12 [R/W]

00000000

SSR3 [R, R/W]

00001000

BGR02 [R/W]

00000000

RDR3/TRD3

[R/W]

00000000

LIN-UART 3

BGR13 [R/W]

00000000

SSR4 [R, R/W]

00001000

BGR03 [R/W]

00000000

RDR4/TRD4

[R/W]

00000000

LIN-UART 4

BGR14 [R/W]

00000000

ELVR1 [R/W]

00000000 00000000

⎯

⎯

⎯

⎯

BGR04 [R/W]

00000000

TCCS0 [R/W] B

00000000

TCCS1 [R/W] B

00000000

TCCS2 [R/W] B

00000000

TCCS3 [R/W] B

00000000

Ext. INT 8 to 15

Free-run Timer 0

Free-run Timer 1

Free-run Timer 2

Free Run Timer 3

(Continued)

31

MB91270/280 Series

Address

0000E4

0000E8

0000EC

0000F0

0000F4

0000F8

0000FC

000100

000104

000108

00010C

000110

000114

000118

000110

000120

to

00012C

000130

000134

000138

00013C

000140

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

Register

+

0

IPCP1 [R]

XXXXXXXX XXXXXXXX

+

1

+

2

IPCP0 [R]

XXXXXXXX XXXXXXXX

⎯⎯⎯

IPCP3 [R]

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

IPCP2 [R]

⎯⎯⎯

IPCP5 [R]

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

IPCP4 [R]

⎯⎯⎯

IPCP7 [R]

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

IPCP6 [R]

⎯⎯⎯

⎯ System Reserved

OCCP1 [R/W]

XXXXXXXX XXXXXXXX

OCCP3 [R/W]

XXXXXXXX XXXXXXXX

OCS23 [R/W]

11101100 00001100

OCCP5 [R/W]

XXXXXXXX XXXXXXXX

OCCP7 [R/W]

XXXXXXXX XXXXXXXX

OCS67 [R/W]

11101100 00001100

OCCP0 [R/W]

XXXXXXXX XXXXXXXX

OCCP2 [R/W]

XXXXXXXX XXXXXXXX

OCS01 [R/W]

11101100 00001100

OCCP4 [R/W]

XXXXXXXX XXXXXXXX

OCCP6 [R/W]

XXXXXXXX XXXXXXXX

OCS45 [R/W]

11101100 00001100

⎯ System Reserved

EIRR2 [R/W]

00000000

EIRR3 [R/W]

00000000

EIRR4 [R/W]

00000000

⎯

DADR1 [R/W]

------00 00000000

ENIR2 [R/W]

00000000

ENIR3 [R/W]

00000000

ENIR4 [R/W]

00000000

DACR [R/W]

-----000

ELVR2 [R/W]

00000000 00000000

ELVR3 [R/W]

00000000 00000000

ELVR4 [R/W]

00000000 00000000

DADR0 [R/W]

------00 00000000

⎯

+

3

ICS01 [R/W]

00000000

ICS23 [R/W]

00000000

ICS45 [R/W]

00000000

ICS67 [R/W]

00000000

DADBL [R/W]

-------0

Block

Input Capture Unit

0, 1

Input Capture Unit

2, 3

Input Capture Unit

4, 5

Input Capture Unit

6, 7

Output Compare

1/0

Output Compare

3/2

Output Compare

3 to 0 Ctrl.

Output Compare

5/4

Output Compare

7/6

Output Compare

7 to 4 Ctrl.

Ext. INT 16 to 23

Ext. INT 24 to 31

(MB91V280 only)

Ext. INT 32 to 39

(MB91V280 only)

D/A Converter

(MB91V280 only)

(Continued)

32

MB91270/280 Series

Address

000144

00014C

000150

000158

00015C

000160

000164

to

00016C

000170

000174

000178

00017C

000180

000184

000188

00018C

000190

000194

000198

+

0

H

H

WTHR [R/W] B, H

H

H

H

H

H

H

H

H

UDRC1 [W] B, H

H

⎯

⎯

XXXXXXXX

00000000 00000000

ADCS1 [R/W]

00000000

ADCT1 [R/W]

00010000

CUCR [R/W] B, H, W

CUTR1 [R] B, H, W

00000000

UDCCH0 [R/W] B,

H

H

00000000

UDCCH1 [R/W] B,

H

H

-0000000

H

UDRC3 [W] B, H

H

00000000

UDCCH2 [R/W] B,

H

H

00000000

UDCCH3 [R/W] B,

H

H

-0000000

H

H

AD2CS1 [R/W]

H

AD2CT1 [R/W]

H

00000000 00000000

00000000

00010000

WTDBL [R/W] B

------00

WTMR [R/W] B, H

XXXXXXXX

ADERH [R/W]

ADCS0 [R, R/W]

00000000

ADCT0 [R/W]

00101100

-------- ---00000

-------- 00000000

UDRC0 [W] B, H

00000000

UDCCL0 [R/W]

-0000000

UDCCL1 [R/W]

-0000000

UDRC2 [W] B, H

00000000

UDCCL2 [R/W]

-0000000

UDCCL3 [R/W]

-0000000

AD2ERH [R/W]

AD2CS0 [R, R/W]

00000000

AD2CT0 [R/W]

00101100

Register

+

1

+

2

WTCR [R/W] B, H

00000000 000-00-X

WTBR [R/W] B

---XXXXX XXXXXXXX XXXXXXXX

WTSR [R/W] B

--XXXXXXXX

ADERL [R/W]

00000000 00000000

ADCR1 [R]

------XX

ADSCH [R/W]

---00000

CUTD [R/W] B, H, W

10000000 00000000

CUTR2 [R] B, H, W

00000000 00000000

⎯ System Reserved

UDCR1 [R] B, H

00000000

B, H

B, H

⎯

⎯

⎯ System Reserved

UDCR3 [R] B, H

00000000

B, H

B, H

⎯

⎯

⎯ System Reserved

AD2ERL [R/W]

00000000 00000000

AD2CR1 [R]

------XX

AD2SCH [R/W]

---00000

+

3

⎯

ADCR0 [R]

XXXXXXXX

ADECH [R/W]

---00000

UDCR0 [R] B, H

00000000

UDCS0 [R/W] B

00000000

UDCS1 [R/W] B

00000000

UDCR2 [R] B, H

00000000

UDCS2 [R/W] B

00000000

UDCS2 [R/W] B

00000000

AD2CR0 [R]

XXXXXXXX

AD2ECH [R/W]

---00000

Block

Real Time Clock000148

A/D Converter000154

Clock Calibration

(MB91V280 and

without S-suffix

models only)

Up Down Counter

0/1

Up Down Counter

2/3

A/D Converter 2

(MB91V280 only)

(Continued)

33

MB91270/280 Series

Address

00019C

0001A0

0001A4

0001A8

0001AC

0001B0

0001B8

0001BC

0001C0

0001C8

0001CC

0001D0

0001D8

0001DC

H

H

H

H

H

PRLH0 [R/W]

H

XXXXXXXX

PRLH2 [R/W]

H

XXXXXXXX

PPGC0 [R/W]

H

H

PRLH4 [R/W]

H

XXXXXXXX

PRLH6 [R/W]

H

XXXXXXXX

PPGC4 [R/W]

H

H

PRLH8 [R/W]

H

XXXXXXXX

PRLHA [R/W]

H

XXXXXXXX

PPGC8 [R/W]

H

H

+

0

CMPR [R/W] B, H

--000010 11111101

CMT1 [R/W] B, H, W

00000000 10000000

CANPRE

[R, R/W]

00000000

B, H, W

B, H, W

B, H, W

0000000X

B, H, W

B, H, W

B, H, W

0000000X

B, H, W

B, H, W

B, H, W

0000000X

Register

+

1

⎯

PRLL0 [R/W]

B, H, W

XXXXXXXX

PRLL2 [R/W]

B, H, W

XXXXXXXX

PPGC1 [R/W]

B, H, W

0000000X

PRLL4 [R/W]

B, H, W

XXXXXXXX

PRLL6 [R/W]

B, H, W

XXXXXXXX

PPGC5 [R/W]

B, H, W

0000000X

PRLL8 [R/W]

B, H, W

XXXXXXXX

PRLLA [R/W]

B, H, W

XXXXXXXX

PPGC9 [R/W]

B, H, W

0000000X

+

2

+

3

⎯ System Reserved

Block

⎯

CMCR [R/W] B, H

-0010000

Clock Modulator

CMT2 [R/W] B, H, W

00000000 00000000

EISSR [R/W] B, H

00000000 00000000

CAN Clock Presc /

Ext. Int. Source Sel.

⎯ System Reserved

PRLH1 [R/W]

B, H, W

XXXXXXXX

PRLH3 [R/W]

B, H, W

XXXXXXXX

PPGC2 [R/W]

B, H, W

0000000X

PRLL1 [R/W]

B, H, W

XXXXXXXX

PRLL3 [R/W]

B, H, W

XXXXXXXX

PPGC3 [R/W]

B, H, W

0000000X

PPG0 to PPG30001B4

⎯ System Reserved

PRLH5 [R/W]

B, H, W

XXXXXXXX

PRLH7 [R/W]

B, H, W

XXXXXXXX

PPGC6 [R/W]

B, H, W

0000000X

PRLL5 [R/W]

B, H, W

XXXXXXXX

PRLL7 [R/W]

B, H, W

XXXXXXXX

PPGC7 [R/W]

B, H, W

0000000X

PPG4 to PPG70001C4

⎯ System Reserved

PRLH9 [R/W]

B, H, W

XXXXXXXX

PRLHB [R/W]

B, H, W

XXXXXXXX

PPGCA [R/W]

B, H, W

0000000X

PRLL9 [R/W]

B, H, W

XXXXXXXX

PRLLB [R/W]

B, H, W

XXXXXXXX

PPGCB [R/W]

B, H, W

0000000X

PPG8 to PPGB0001D4

⎯ System Reserved

34

(Continued)

MB91270/280 Series

Address

0001E0

0001E8

0001EC

0001F0

0001F4

0001F8

0001FC

000200

000208

00020C

000210

000214

000218

00021C

000220

000224

000228

to

00023C

+

PRLHC [R/W]

H

B, H, W

XXXXXXXX

PRLHE [R/W]

H

B, H, W

XXXXXXXX

PPGCC [R/W]

H

B, H, W

0000000X

H

H

PPGTRG [R/W] B, H, W

00000000 00000000

PPGSWAP [R/W]

H

B

00000000

CMCLKR [R/W] B

H

H

H

H

H

H

H

H

H

H

H

H

H

H

----0000

Register

Block

0

+

1

PRLLC [R/W]

B, H, W

XXXXXXXX

PRLLE [R/W]

B, H, W

XXXXXXXX

PPGCD [R/W]

B, H, W

0000000X

+

2

PRLHD [R/W]

B, H, W

XXXXXXXX

PRLHF [R/W]

B, H, W

XXXXXXXX

PPGCE [R/W]

B, H, W

0000000X

+

3

PRLLD [R/W]

B, H, W

XXXXXXXX

PRLLF [R/W]

B, H, W

XXXXXXXX

PPGCF [R/W]

B, H, W

0000000X

PPGC to PPGF0001E4

⎯ System Reserved

PPGREVC [R/W] B, H, W

00000000 00000000

⎯⎯⎯

PPG0 to PPGF

Enable / Reverse

PPG0 to PPGF

Output Swap

⎯⎯⎯Clock Monitor

⎯ System Reserved

DMACA0 [R/W]

00000000 00000000 00000000 00000000

DMACB0 [R/W]

00000000 00000000 00000000 00000000

DMAC000204

DMACA1 [R/W]

00000000 00000000 00000000 00000000

DMACB1 [R/W]

00000000 00000000 00000000 00000000

DMACA2 [R/W]

00000000 00000000 00000000 00000000

DMACB2 [R/W]

00000000 00000000 00000000 00000000

DMACA3 [R/W]

00000000 00000000 00000000 00000000

DMAC

DMACB3 [R/W]

00000000 00000000 00000000 00000000

DMACA4 [R/W]

00000000 00000000 00000000 00000000

DMACB4 [R/W]

00000000 00000000 00000000 00000000

⎯ System Reserved

(Continued)

35

MB91270/280 Series

Address

000240

000244

to

0003EC

0003F0

0003F4

0003F8

0003FC

000400

000404

000408

00040C

000410

000414

to

00041C0

000420

000424

000428

00042C

000430

+

H

H

H

H

H

H

H

DDR0 [R/W] B, H

H

H

H

H

H

H

H

H

H

H

H

00000000

DDR4 [R/W] B, H

00000000

DDR8 [R/W] B, H

00000000

DDRC [R/W] B, H

00000000

DDRG [R/W] B, H

00000000

H

PFR0 [R/W] B, H

00000000

PFR4 [R/W] B, H

00000000

PFR8 [R/W] B, H

00000000

PFRC [R/W] B, H

00000000

PFRG [R/W] B, H

00000000

Register

0

+

1

+

2

DMACR [R/W]

0XX00000 XXXXXXXX XXXXXXXX XXXXXXXX

⎯ System Reserved

BSD0 [W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

BSD1 [R/W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

BSDC [W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

BSRR [R]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

DDR1 [R/W] B, H

00000000

DDR5 [R/W] B, H

00000000

DDR9 [R/W] B, H

00000000

DDRD [R/W] B, H

00000000

DDR2 [R/W] B, H

00000000

DDR6 [R/W] B, H

00000000

DDRA [R/W] B, H

------00

DDRE [R/W] B, H

00000000

⎯⎯⎯

⎯ System Reserved

PFR1 [R/W] B, H

00000000

PFR5 [R/W] B, H

00000000

PFR9 [R/W] B, H

00000000

PFRD [R/W] B, H

00000000

PFR2 [R/W] B, H

00000000

PFR6 [R/W] B, H

00000000

PFRA [R/W] B, H

------00

PFRE [R/W] B, H

00000000

⎯⎯⎯

+

3

DDR3 [R/W] B, H

00000000

DDR7 [R/W] B, H

00000000

DDRB [R/W] B, H

--000000

DDRF [R/W] B, H

00000000

PFR3 [R/W] B, H

00000000

PFR7 [R/W] B, H

00000000

PFRB [R/W] B, H

--000000

PFRF [R/W] B, H

00000000

Block

DMAC

Bit Search

Data Direction

Registers

(DDRB to DDRG

are only available

on the MB91V280)

Port Function

Registers

(PFRB to PFRG

are only available

on the MB91V280)

36

(Continued)

MB91270/280 Series

Address

000434

to

00043C

000440

000444

000448

00044C

000450

000454

000458

00045C

000460

000464

000468

00046C

000470

to

00047C

000480

000488

00048C

000490

H

H

ICR00 [R, R/W]

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

---11111

ICR04 [R, R/W]

---11111

ICR08 [R, R/W]

---11111

ICR12 [R, R/W]

---11111

ICR16 [R, R/W]

---11111

ICR20 [R, R/W]

---11111

ICR24 [R, R/W]

---11111

ICR28 [R, R/W]

---11111

ICR32 [R, R/W]

---11111

ICR36 [R, R/W]

---11111

ICR40 [R, R/W]

---11111

ICR44 [R, R/W]

---11111

RSRR [R, R/W]

10000000

CLKR [R/W]

00000000

OSCR [W, R/W]

00000000

Register

+

0

+

1

⎯ System Reserved

ICR01 [R, R/W]

---11111

ICR05 [R, R/W]

---11111

ICR09 [R, R/W]

---11111

ICR13 [R, R/W]

---11111

ICR17 [R, R/W]

---11111

ICR21 [R, R/W]

---11111

ICR25 [R, R/W]

---11111

ICR29 [R, R/W]

---11111

ICR33 [R, R/W]

---11111

ICR37 [R, R/W]

---11111

ICR41 [R, R/W]

---11111

ICR45 [R, R/W]

---11111

ICR02 [R, R/W]

---11111

ICR06 [R, R/W]

---11111

ICR10 [R, R/W]

---11111

ICR14 [R, R/W]

---11111

ICR18 [R, R/W]

---11111

ICR22 [R, R/W]

---11111

ICR26 [R, R/W]

---11111

ICR30 [R, R/W]

---11111

ICR34 [R, R/W]

---11111

ICR38 [R, R/W]

---11111

ICR42 [R, R/W]

---11111

ICR46 [R, R/W]

---11111

⎯ System Reserved

STCR [R/W]

00110011

WPR [W]

XXXXXXXX

⎯⎯

TBCR [R/W]

00XXXX00

DIVR0 [R/W]

00000011

OSCCR [R/W]

XXXXXXX0

⎯ System Reserved

⎯⎯⎯Stb. Wait Timer

+

2

+

3

ICR03 [R, R/W]

---11111

ICR07 [R, R/W]

---11111

ICR11 [R, R/W]

---11111

ICR15 [R, R/W]

---11111

ICR19 [R, R/W]

---11111

ICR23 [R, R/W]

Block

---11111

ICR27 [R, R/W]

Interrupt Control

Unit

---11111

ICR31 [R, R/W]

---11111

ICR35 [R, R/W]

---11111

ICR39 [R, R/W]

---11111

ICR43 [R, R/W]

---11111

ICR47 [R, R/W]

---11111

CTBR [W]

XXXXXXXX

DIVR1 [R/W]

00000000

Clock Control Unit000484

⎯

(Continued)

37

MB91270/280 Series

Address

000494

to

0004A8

0004AC

0004B0

to

0004FC

000500

000504

000508

00050C

000510

000514

to

00051C

000520

000524

000528

00052C

000530

000534

to

00053C

H

H

H

H

H

PPER0 [R/W]

H

00000000

PPER4 [R/W]

H

00000000

PPER8 [R/W]

H

00000000

PPERC [R/W]

H

00000000

PPERG [R/W]

H

00000000

H

H

PPCR0 [R/W]

H

00000000

PPCR4 [R/W]

H

00000000

PPCR8 [R/W]

H

00000000

PPCRC [R/W]

H

00000000

PPCRG [R/W]

H

00000000

H

H

+

0

⎯

B, H

B, H

B, H

B, H

B, H

B, H

B, H

B, H

B, H

B, H

Register

+

1

+

2

+

3

⎯ System Reserved

CSVCR [R/W]

0001XX00

⎯⎯Clock Supervisor

⎯ System Reserved

PPER1 [R/W]

B, H

00000000

PPER5 [R/W]

B, H

00000000

PPER9 [R/W]

B, H

00000000

PPERD [R/W]

B, H

00000000

PPER2 [R/W]

B, H

00000000

PPER6 [R/W]

B, H

00000000

PPERA [R/W]

B, H

------00

PPERE [R/W]

B, H

00000000

PPER3 [R/W]

B, H

00000000

PPER7 [R/W]

B, H

00000000

PPERB [R/W]

B, H

--000000

PPERF [R/W]

B, H

00000000

⎯⎯⎯

⎯ System Reserved

PPCR1 [R/W]

B, H

00000000

PPCR5 [R/W]

B, H

00000000

PPCR9 [R/W]

B, H

00000000

PPCRD [R/W]

B, H

00000000

PPCR2 [R/W]

B, H

00000000

PPCR6 [R/W]

B, H

00000000

PPCRA [R/W]

B, H

------00

PPCRE [R/W]

B, H

00000000

PPCR3 [R/W]

B, H

00000000

PPCR7 [R/W]

B, H

00000000

PPCRB [R/W]

B, H

--000000

PPCRF [R/W]

B, H

00000000

⎯⎯⎯

⎯ System Reserved

Block

Port Pull-up/down

Enable Registers

(PPERB to PPERG

are only available

on the MB91V280)

Port Pull-up/down

Control Registers

(PPCRB to PPCRG

are only available

on the MB91V280)