Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

CM71-xxxxx-1E

FR60

32-BIT MICROCONTROLLER

MB91460 Series

User’s Manual

- PRELIMINARY -

Version 1.00

2006-10-22

Page 2

FUJITSU LIMITED

Page 3

FR60

32-BIT MICROCONTROLLER

MB91460 Series

User’s Manual

Page 4

• The contents of this document are subject to change without notice.

Customers are advised to consult with FUJITSU sales representatives before ordering.

• The information, such as descriptions of function and application circuit examples, in this document are presented solely

for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not

warrant proper operation of the device with respect to use based on such information. When you develop equipment

incorporating the device based on such information, you must assume any responsibility arising out of such use of the

information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as

license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of

Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party' s intellectual property right or other

right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other

rights of third parties which would result from the use of information contained herein.

• The products described in this document are designed, developed and manufactured as contemplated for general use,

including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not

designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless

extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury,

severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic

control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use

requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection

with above-mentioned uses of the products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such

failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and

prevention of over-current levels and other abnormal operating conditions.

• If any products described in this document represent goods or technologies subject to certain restrictions on export under

the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required

for export of those products from Japan.

©2004 FUJITSU LIMITED Printed in Japan

-i

Page 5

TOC

Chapter 1 Introduction......................................................................................... 1

1. How to Handle the Device..................................................................................................... 1

2. Instruction for Users............................................................................................................... 3

3. Caution: debug-related matters............................................................................................. 6

4. How to Use This Document................................................................................................... 7

Chapter 2 MB91460 Rev.A/Rev.B Overview..................................................... 11

1. Overview.............................................................................................................................. 11

2. Features............................................................................................................................... 11

3. MB91460 Series Product Lineup......................................................................................... 19

4. Block Diagram ..................................................................................................................... 21

Chapter 3 MB91460 Series Basic Information ................................................. 23

1. Memory Map........................................................................................................................ 23

2. I/O Map................................................................................................................................ 24

3. Interrupt Vector Table.......................................................................................................... 73

4. Package............................................................................................................................... 78

5. Pin Assignment Diagram..................................................................................................... 79

6. Pin Definitions...................................................................................................................... 80

7. I/O Circuit Type.................................................................................................................... 94

8. Pin State Table.................................................................................................................... 96

Chapter 4 CPU Architecture ............................................................................ 105

1. Overview............................................................................................................................ 105

2. Features............................................................................................................................. 106

3. CPU................................................................................................................................... 107

4. 32-bit/16-bit Bus Converter................................................................................................ 107

5. Harvard/Princeton Bus Converter...................................................................................... 107

6. Instruction Overview.......................................................................................................... 108

7. Data Structure.................................................................................................................... 109

8. Word Alignment................................................................................................................. 110

9. Addressing......................................................................................................................... 111

Chapter 5 CPU Registers................................................................................. 113

1. General-purpose Registers................................................................................................ 113

2. Dedicated Registers .......................................................................................................... 113

Chapter 6 EIT: Exceptions, Interrupts and Traps.......................................... 121

1. Overview............................................................................................................................ 121

2. Features............................................................................................................................. 121

3. EIT Trigger......................................................................................................................... 121

4. Return from EIT................................................................................................................. 121

5. EIT Interrupt Level............................................................................................................. 122

i

Page 6

6. EIT Vector Table................................................................................................................ 122

7. Multiple EIT Processing..................................................................................................... 123

8. Operation........................................................................................................................... 125

9. Caution .............................................................................................................................. 128

Chapter 7 Branch Instruction.......................................................................... 129

1. Branch Instruction with Delay Slot..................................................................................... 129

2. Operation of Branch Instruction with Delay Slot................................................................ 129

3. Actual Example (with Delay Slot)....................................................................................... 130

4. Restrictions on Branch Instruction with Delay Slot............................................................ 131

5. Branch Instruction without Delay Slot................................................................................ 132

6. Operation of Branch Instruction without Delay Slot........................................................... 132

Chapter 8 Device State Transition .................................................................. 133

1. Overview............................................................................................................................ 133

2. Features............................................................................................................................. 133

3. State Transition Diagram................................................................................................... 134

Chapter 9 Reset ................................................................................................ 139

1. Overview............................................................................................................................ 139

2. Features............................................................................................................................. 139

3. Configuration ..................................................................................................................... 140

4. Registers............................................................................................................................ 141

5. INIT Pin Input (INIT: Settings Initialization Reset) ............................................................ 146

6. Watchdog Reset (INIT: Settings Initialization Reset)......................................................... 148

7. Software Reset (RST: Operation Initialization Reset)....................................................... 149

8. Reset Operation Modes..................................................................................................... 150

9. MCU Operation Mode........................................................................................................ 151

10. Caution .............................................................................................................................. 152

Chapter 10 Standby............................................................................................ 155

1. Overview............................................................................................................................ 155

2. Features............................................................................................................................. 155

3. Configuration ..................................................................................................................... 156

4. Registers............................................................................................................................ 157

5. Operation........................................................................................................................... 159

6. Settings.............................................................................................................................. 161

7. Q&A................................................................................................................................... 161

8. Caution .............................................................................................................................. 165

Chapter 11 Memory Controller.......................................................................... 167

1. Overview............................................................................................................................ 167

2. FLASH Interface................................................................................................................ 167

3. General Purpose RAM....................................................................................................... 167

4. Instruction Cache and Data Buffer..................................................................................... 167

5. Prefetch ............................................................................................................................. 167

6. Fixed Mode and Reset Vectors ......................................................................................... 167

7. Registers............................................................................................................................ 168

ii

Page 7

8. Explanations of Registers.................................................................................................. 169

Chapter 12 Instruction Cache............................................................................ 179

1. General description............................................................................................................ 179

2. Main body structure........................................................................................................... 179

3. Operating mode conditions................................................................................................ 185

4. Cacheable areas in the instruction cache.......................................................................... 186

5. Settings for handling the I-Cache ...................................................................................... 186

Chapter 13 Clock Control .................................................................................. 189

1. Overview............................................................................................................................ 189

2. Features............................................................................................................................. 189

3. Configuration ..................................................................................................................... 190

4. Registers............................................................................................................................ 191

5. Operation........................................................................................................................... 199

6. Settings.............................................................................................................................. 201

7. Q & A................................................................................................................................. 202

8. Caution .............................................................................................................................. 205

Chapter 14 PLL Interface ................................................................................... 207

1. Overview............................................................................................................................ 207

2. Features............................................................................................................................. 207

3. Frequency calculation........................................................................................................ 207

4. Registers............................................................................................................................ 208

5. Recommended Settings .................................................................................................... 212

6. Clock Auto Gear Up/Down................................................................................................. 213

7. Caution .............................................................................................................................. 215

Chapter 15 CAN Clock Prescaler ...................................................................... 217

1. Overview............................................................................................................................ 217

2. Features............................................................................................................................. 217

3. Registers............................................................................................................................ 218

Chapter 16 Clock Supervisor ............................................................................ 221

1. Overview Clock Supervisor................................................................................................ 221

2. Clock Supervisor Register................................................................................................. 222

3. Block Diagram Clock Supervisor....................................................................................... 224

4. Operation Modes............................................................................................................... 225

Chapter 17 Clock Modulator.............................................................................. 239

1. Overview............................................................................................................................ 239

2. Clock Modulator Registers................................................................................................. 240

3. Application Note................................................................................................................. 247

Chapter 18 Timebase Counter........................................................................... 249

1. Overview............................................................................................................................ 249

2. Features............................................................................................................................. 249

iii

Page 8

3. Configuration ..................................................................................................................... 250

4. Registers............................................................................................................................ 251

5. Operation........................................................................................................................... 253

6. Settings.............................................................................................................................. 259

7. Q&A................................................................................................................................... 260

8. Caution .............................................................................................................................. 262

Chapter 19 Timebase Timer............................................................................... 263

1. Overview............................................................................................................................ 263

2. Features............................................................................................................................. 263

3. Configuration ..................................................................................................................... 264

4. Register ............................................................................................................................. 265

5. Operation........................................................................................................................... 267

6. Setting................................................................................................................................ 268

7. Q & A................................................................................................................................. 269

8. Caution .............................................................................................................................. 271

Chapter 20 Software Watchdog Timer.............................................................. 273

1. Overview............................................................................................................................ 273

2. Features............................................................................................................................. 273

3. Configuration ..................................................................................................................... 274

4. Register ............................................................................................................................. 275

5. Operation........................................................................................................................... 278

6. Setting................................................................................................................................ 280

7. Q & A................................................................................................................................. 281

8. Caution .............................................................................................................................. 282

Chapter 21 Hardware Watchdog Timer ............................................................ 283

1. Overview............................................................................................................................ 283

2. Configuration ..................................................................................................................... 284

3. Register ............................................................................................................................. 285

4. Functions........................................................................................................................... 287

5. Caution .............................................................................................................................. 288

Chapter 22 Main Oscillation Stabilisation Timer ............................................. 289

1. Overview............................................................................................................................ 289

2. Features............................................................................................................................. 289

3. Configuration ..................................................................................................................... 290

4. Register ............................................................................................................................ 291

5. Operation........................................................................................................................... 292

6. Setting................................................................................................................................ 294

7. Q & A................................................................................................................................. 295

8. Caution .............................................................................................................................. 297

Chapter 23 Sub Oscillation Stabilisation Timer............................................... 299

1. Overview............................................................................................................................ 299

2. Features............................................................................................................................. 299

3. Configuration ..................................................................................................................... 300

iv

Page 9

4. Register ............................................................................................................................. 301

5. Operation........................................................................................................................... 303

6. Setting................................................................................................................................ 306

7. Q & A................................................................................................................................. 307

8. Caution .............................................................................................................................. 309

Chapter 24 Interrupt Control ............................................................................. 311

1. Overview............................................................................................................................ 311

2. Features............................................................................................................................. 311

3. Configuration ..................................................................................................................... 312

4. Registers............................................................................................................................ 313

5. Operation........................................................................................................................... 318

6. Setting................................................................................................................................ 319

7. Q & A................................................................................................................................. 319

8. Caution .............................................................................................................................. 320

Chapter 25 External Interrupt............................................................................ 321

1. Overview............................................................................................................................ 321

2. Features............................................................................................................................. 321

3. Configuration ..................................................................................................................... 322

4. Registers............................................................................................................................ 325

5. Operation........................................................................................................................... 327

6. Setting................................................................................................................................ 328

7. Q & A................................................................................................................................. 328

8. Caution .............................................................................................................................. 331

Chapter 26 DMA Controller................................................................................ 333

1. Overview of the DMA Controller (DMAC).......................................................................... 333

2. DMA Controller (DMAC) Registers.................................................................................... 335

3. DMA Controller (DMAC) Operation ................................................................................... 354

4. Operation Flowcharts......................................................................................................... 373

5. Data Bus............................................................................................................................ 376

6. DMA External Interface...................................................................................................... 379

Chapter 27 Delayed Interrupt ............................................................................ 383

1. Overview............................................................................................................................ 383

2. Features............................................................................................................................. 383

3. Configuration ..................................................................................................................... 383

4. Register ............................................................................................................................. 384

5. Operation........................................................................................................................... 384

6. Setting................................................................................................................................ 385

7. Q & A................................................................................................................................. 385

8. Caution .............................................................................................................................. 385

Chapter 28 Bit Search ........................................................................................ 387

1. Overview............................................................................................................................ 387

2. Features............................................................................................................................. 387

3. Configuration ..................................................................................................................... 388

v

Page 10

4. Register ............................................................................................................................. 389

5. Operation........................................................................................................................... 391

6. Setting................................................................................................................................ 393

7. Q & A................................................................................................................................. 394

8. Caution .............................................................................................................................. 395

Chapter 29 MPU / EDSU..................................................................................... 397

1. Overview............................................................................................................................ 397

2. Features............................................................................................................................. 398

3. Break Functions................................................................................................................. 399

4. Registers............................................................................................................................ 407

5. Quick Reference................................................................................................................ 429

Chapter 30 I/O Ports........................................................................................... 431

1. I/O Ports Functions............................................................................................................ 431

2. I/O Circuit Types................................................................................................................ 453

3. Port Register Settings........................................................................................................ 454

Chapter 31 External Bus.................................................................................... 507

1. Overview of the External Bus Interface ............................................................................. 507

2. External Bus Interface Registers....................................................................................... 512

3. Setting Example of the Chip Select Area........................................................................... 542

4. Endian and Bus Access..................................................................................................... 543

5. Operation of the Ordinary bus interface............................................................................. 562

6. Burst Access Operation..................................................................................................... 574

7. Address/data Multiplex Interface ....................................................................................... 576

8. Prefetch Operation............................................................................................................. 579

9. SDRAM/FCRAM Interface Operation................................................................................ 582

10. DMA Access Operation ..................................................................................................... 592

11. Bus Arbitration................................................................................................................... 608

12. Procedure for Setting a Register ....................................................................................... 610

13. Notes on Using the External Bus Interface........................................................................ 611

Chapter 32 USART (LIN / FIFO) ......................................................................... 613

1. Overview............................................................................................................................ 613

2. USART Configuration........................................................................................................ 616

3. USART Pins....................................................................................................................... 620

4. USART Registers .............................................................................................................. 621

5. USART Interrupts .............................................................................................................. 638

6. USART Baud Rates........................................................................................................... 642

7. USART Operation.............................................................................................................. 647

8. Notes on using USART...................................................................................................... 663

Chapter 33 I2C Controller .................................................................................. 665

1. Overview............................................................................................................................ 665

2. I2C Interface Registers...................................................................................................... 667

3. I2C Interface Operation ..................................................................................................... 685

4. Programming Flow Charts................................................................................................. 687

vi

Page 11

Chapter 34 CAN Controller................................................................................ 691

1. Overview............................................................................................................................ 691

2. Register Description .......................................................................................................... 692

3. Functional Description....................................................................................................... 720

4. CAN Application................................................................................................................. 724

Chapter 35 Free-Run Timer ............................................................................... 733

1. Overview............................................................................................................................ 733

2. Features............................................................................................................................. 733

3. Configuration Diagram....................................................................................................... 734

4. Registers............................................................................................................................ 735

5. Operation........................................................................................................................... 739

6. Setting................................................................................................................................ 741

7. Q & A................................................................................................................................. 742

8. Caution .............................................................................................................................. 745

Chapter 36 Input Capture................................................................................... 747

1. Overview............................................................................................................................ 747

2. Features............................................................................................................................. 747

3. Configuration ..................................................................................................................... 748

4. Register ............................................................................................................................. 749

5. Operation........................................................................................................................... 752

6. Settings.............................................................................................................................. 754

7. Q&A................................................................................................................................... 755

8. Caution .............................................................................................................................. 758

Chapter 37 Output Compare.............................................................................. 759

1. Overview............................................................................................................................ 759

2. Features............................................................................................................................. 759

3. Configuration Diagram....................................................................................................... 760

4. Registers............................................................................................................................ 761

5. Operation........................................................................................................................... 765

6. Settings.............................................................................................................................. 767

7. Q & A................................................................................................................................. 768

8. Caution .............................................................................................................................. 773

Chapter 38 Reload Timer ................................................................................... 775

1. Overview............................................................................................................................ 775

2. Features............................................................................................................................. 775

3. Configuration ..................................................................................................................... 776

4. Registers............................................................................................................................ 778

5. Operation........................................................................................................................... 782

6. Setting................................................................................................................................ 787

7. Q & A................................................................................................................................. 789

8. Caution .............................................................................................................................. 794

Chapter 39 Programmable Pulse Generator.................................................... 795

1. Overview............................................................................................................................ 795

vii

Page 12

2. Features............................................................................................................................. 795

3. Configuration ..................................................................................................................... 797

4. Registers............................................................................................................................ 799

5. Operation........................................................................................................................... 808

6. Setting................................................................................................................................ 811

7. Q & A................................................................................................................................. 813

8. Caution .............................................................................................................................. 821

Chapter 40 Pulse Frequency Modulator........................................................... 823

1. PFM Overview................................................................................................................... 823

2. Reload Counter Registers ................................................................................................. 826

3. Reload Counter Operation................................................................................................. 830

4. PFM Operation and Setting............................................................................................... 833

Chapter 41 Up/Down Counter............................................................................ 835

1. Overview............................................................................................................................ 835

2. Feature .............................................................................................................................. 835

3. Configuration ..................................................................................................................... 836

4. Register ............................................................................................................................. 840

5. Operation........................................................................................................................... 848

6. Setting................................................................................................................................ 855

7. Q&A................................................................................................................................... 857

8. Caution .............................................................................................................................. 862

Chapter 42 Sound Generator............................................................................. 863

1. Overview............................................................................................................................ 863

2. Block Diagram ................................................................................................................... 864

3. Registers............................................................................................................................ 865

Chapter 43 Stepper Motor Controller ............................................................... 871

1. Overview............................................................................................................................ 871

2. Registers............................................................................................................................ 872

3. Operation........................................................................................................................... 881

4. Caution .............................................................................................................................. 883

Chapter 44 A/D Converter.................................................................................. 885

1. Overview of A/D Converter................................................................................................ 885

2. Block Diagram of A/D Converter........................................................................................ 886

3. Registers of A/D Converter................................................................................................ 887

4. Operation of A/D Converter............................................................................................... 896

5. Setting................................................................................................................................ 899

6. Q & A................................................................................................................................. 901

7. Caution .............................................................................................................................. 906

Chapter 45 D/A Converter.................................................................................. 909

1. Overview............................................................................................................................ 909

2. Features............................................................................................................................. 909

3. Configuration ..................................................................................................................... 910

viii

Page 13

4. Registers............................................................................................................................ 911

5. Operation........................................................................................................................... 913

6. Setting................................................................................................................................ 914

7. Q & A................................................................................................................................. 915

8. Caution .............................................................................................................................. 916

Chapter 46 Alarm Comparator .......................................................................... 917

1. Overview............................................................................................................................ 917

2. Block Diagram .................................................................................................................. 917

3. Alarm Comparator Control/Status Register (ACSR).......................................................... 918

4. Operation Modes............................................................................................................... 919

Chapter 47 LCD Controller ................................................................................ 921

1. Overview............................................................................................................................ 921

2. Features............................................................................................................................. 921

3. Configuration ..................................................................................................................... 922

4. Registers............................................................................................................................ 924

5. Operation........................................................................................................................... 929

6. Setting................................................................................................................................ 934

7. Q&A................................................................................................................................... 935

8. Caution .............................................................................................................................. 940

Chapter 48 Clock Monitor.................................................................................. 941

1. Overview............................................................................................................................ 941

2. Features............................................................................................................................. 941

3. Configuration ..................................................................................................................... 942

4. Register ............................................................................................................................. 943

5. Operation........................................................................................................................... 945

6. Settings.............................................................................................................................. 946

7. Q&A................................................................................................................................... 946

8. Caution .............................................................................................................................. 947

Chapter 49 Real-Time Clock.............................................................................. 949

1. Overview............................................................................................................................ 949

2. Features............................................................................................................................. 949

3. Configuration ..................................................................................................................... 950

4. Registers............................................................................................................................ 951

5. Operation........................................................................................................................... 956

6. Setting................................................................................................................................ 958

7. Q&A................................................................................................................................... 959

8. Caution .............................................................................................................................. 961

Chapter 50 Subclock Calibration Unit .............................................................. 963

1. Overview............................................................................................................................ 963

2. Block Diagram ................................................................................................................... 964

3. Timing................................................................................................................................ 965

4. Clocks................................................................................................................................ 966

5. Register Description .......................................................................................................... 967

ix

Page 14

6. Application Note................................................................................................................. 973

Chapter 51 Low Voltage Reset/Interrupt .......................................................... 975

1. Overview............................................................................................................................ 975

2. Features............................................................................................................................. 975

3. Registers............................................................................................................................ 976

Chapter 52 Regulator Control ........................................................................... 979

1. Overview............................................................................................................................ 979

2. Features............................................................................................................................. 979

3. Registers............................................................................................................................ 980

Chapter 53 Fixed Mode-Reset Vector / BOOT-ROM........................................ 983

1. Overview............................................................................................................................ 983

2. Check for Boot Conditions................................................................................................. 983

3. Registers modified by Boot ROM ...................................................................................... 988

4. Flash Access Mode Switching........................................................................................... 989

5. Bootloader Update Strategy .............................................................................................. 990

Chapter 54 Flash Memory.................................................................................. 993

1. Overview............................................................................................................................ 993

2. Features............................................................................................................................. 993

3. Configuration ..................................................................................................................... 994

4. Registers............................................................................................................................ 996

5. Access Modes ................................................................................................................... 996

6. Flash Access Mode Switching........................................................................................... 997

7. Auto Algorithms ................................................................................................................. 999

8. Caution ............................................................................................................................ 1007

Chapter 55 Flash Security ............................................................................... 1009

1. Overview.......................................................................................................................... 1009

2. Features........................................................................................................................... 1009

3. Flash Security Vectors..................................................................................................... 1010

4. Register ........................................................................................................................... 1013

Chapter 56 Electrical Specification................................................................. 1017

x

Page 15

xi

Page 16

xii

Page 17

Chapter 1 Introduction

1.How to Handle the Device

Chapter 1 Introduction

1. How to Handle the Device

■ Device Handling Instructions

This chapter describes latch-up prevention and pin termination.

● To set latch-up prevention

Latch up may occur on CMOS ICs when the applied voltage for input terminals or output terminals is higher than V

or lower than VSS, or a voltage higher than the maximum rating voltage is applied between VCCand VSS. Make sure

not to apply a voltage higher than the maximum rating voltage since latch up may surge electric current and result in

the thermal destruction of the device.

● Termination of unused pin

An unused pin must be terminated by a pull-up or pull-down resistor externally, or by switching on the internal pull-up

or pull-down resistor before enabling the pin inputs to avoid transverse current.

CC

● Power-supply pin

If multiple VCCand VSSexist, as a matter of device design, they are connected to each other to prevent an error when

their voltage should be identical in the device. In order to reduce unnecessary radiation, prevent an strobe signal error

due to upward ground level, and comply with total output current standard, be sure to externally connect them to power

supply and ground. Give consideration to connect V

Near the device, it is preferable to connect about 0.1uF ceramic capacitor as a bypass capacitor between V

.

V

SS

CC andVSS

of the device from power supply at low impedance.

● Crystal-oscillator circuit

Noise to X0 or X1 pin may cause an error. Make a design for printed board to closely allocate X0, X1, crystal oscillator

(or ceramic oscillator), bypass capacitor towards ground and the device.

It is recommended to make a printed board artwork which surrounds X0 and X1 pins using ground.

The above recommendations also apply to the subclock oscillator pins X0A and X1A.

● NC and OPEN pin termination

Do not terminate NC pin and OPEN pin to use.

● Mode pins (from MD0 to MD2)

Connect pins from MD0 to MOD2 directly to VCCor VSSto use. To avoid entering test mode due to noise, make a short

pattern length between each mode pin on printed board and V

or VSS to connect pins at low impedance.

CC

CC

and

● At the time of power-on

Immediately after power-on operation, be sure to reset INIT pin to initialize the setting (INIT). Immediately after poweron operation, to ensure the oscillation stabilization time required for oscillation circuit, hold “L”-level input to the pin

during the oscillation stabilization time required for oscillation circuit. (INIT operation on the pin initializes the setting for

oscillation stabilization time to minimum value.)

● Source oscillation input at the time of power-on

At the time of power-on, be sure to input the clock until the oscillation stabilization wait is over.

1

Page 18

Chapter 1 Introduction

1.How to Handle the Device

● Caution: during the PLL clock operation

Even if oscillator is disconnected or input is stopped while selecting PLL clock, self-excited oscillation circuit in the PLL

may continue running at self-running frequency. This self-running operation is not covered by guarantee.

● For more specification about operating voltage, see the latest data sheet.

2

Page 19

Chapter 1 Introduction

2.Instruction for Users

2. Instruction for Users

■ Clock Controls

By inputting “L” to INIT, ensure clock oscillation stabilization time.

■ Switching of dual-purpose port

Use PFR (Port function register) to switch between PORT and dual-purpose port.

■ Low-power-consumption mode

• For standby mode, enable synchronous standby (TBCR.SYNCS=“1”) and then use the following sequences.

(LDI

(LDI

STB

LDUB

LDUB

NOP

NOP

NOP

NOP

NOP

In addition, after returning from standby, set I flag, ILM and ICR in order to branch to interrupt handler which

triggered the return.

• If you use monitor debugger, you should avoid the following.

• Do not set breakpoints for command sequence above.

• Do not conduct stepwise execution for command sequence above.

#_STCR, R12

R0, @R12

@R12, R0

@R12, R0

value_of_standby is a write data to STCR#value_of_standby, R0

_STCR is the STCR address. (481H)

Write to Standby Control Register (STCR).

STCR read for synchronous standby.

Dammy read STCR again.

NOP x 5 for timing adjustment.

■ Power-on sequence

Power-on and power-off sequence valid for MB91V460 Rev.A. Please review the datasheets of the flash

devices for a valid power-on and power-off sequence on those devices.

Power-on sequence: (1) VDD5 , VDD35, HVDD5, VDD5R (2) AVCC, AVRH, V0-V3

Power-off sequence: (1) AVCC, AVRH, V0-V3 (2) VDD5 , VDD35, HVDD5, VDD5R

The power supply V3 for LCD must not exceed VDD5. The power-on of V3 should be carried out after poweron of VDD5R and VDD5. To power on analogue power supply AVCC and analogue signal, power VDD5R and

VDD5 on before.

■ Power supply operating conditions

Power supply recommendation valid for MB91V460 Rev.A. Please review the datasheets of the flash devices

for a recommendation of the power supply conditions on those devices.

[VDD5 = HVDD5 = AVCC] >= VDD35. This is the recommended condition.

3

Page 20

Chapter 1 Introduction

2.Instruction for Users

■ Caution: PS register

Because some commands previously proceed PS register, interrupt processing routine may be broken during

the use of debugger or displayed data on PS flag may be updated due to the following excecptional operations

((1) and (2)).

In each case, it is designed to correctly re-proceed operations after the return, the operation before and after

EIT is carried out in accordance with the specification.

• In immediately preceding DIV0U or DIV0S command,

• If interrupted by user,

• If stepwise execution is carried out,

• If data event or emulator menu made a break,

The following operation may be generated.

1. D0 or D1 flag is updated ahead.

2. EIT processing routine (interruption by user or emulator) is carried out.

3. After the return from EIT, it executes DIV0U or DIV0S command and then D0 or D1 flag are updated

to the same value as 1.

• If you execute each command of ORCCR, STILM, MOV Ri or PS to enable interruption with

interruption by user generated, the following operation may be generated.

4. PS register is updated ahead.

5. EIT processing routine (interruption by user) is carried out.

6. After the return from EIT, it executes commands above, and then PS register is updated to the same

value as 1.

■ Watchdog timer function

Watchdog timer function equipped with FR60 monitors the progress to ensure that program executes reset

delay operation within a specified time and resets CPU if reset delay operation was not executed due to

runaway of program. Once you enable watchdog timer function, it continues running until it is reset.

By way of exception, reset delay is automatically conducted under the condition where CPU program

execution is stopped. For this exceptional condition, see “Chapter 20 Software Watchdog Timer (Page

No.273)“.

■ Register against read/modify/write command

SMR register within UART cannot use read/modify/write command. To write in SMR register, write by Byte/

Half-word/Word in consideration with write control bit (bit-5, 4, 2, 0) rather than accessing by bit-by-bit.

4

Page 21

Chapter 1 Introduction

2.Instruction for Users

■ Caution: writing to registers which include a status flag

Writing to a register including a status flag (in particular, interrupt request flag) in order to control the function,

note that you should not clear status flag unintentionally.

That is, take care not to clear the flag for status bit and make control bit to be the expected value during the

writing.

Especially, for control bits consisting of several bits, bit command is not available since single bit access is

only acceptable for bit command, you should write into the both of control bit and status flag at the same time

by Byte/Half-word/Word access. In this case, you should not clear other bits (bits of status flag) unintentionally.

The following shows registers which mostly include both of several bits and status flag.

• TBCR

• OSCR

•TWCR

• TCCS0, TCCS1

• ICS01

• TMCSR0, TMCSR1, TMCSR2, TMCSR3

• PCN00, PCN01, PCN02,...

• ADCSL0, ADCSL1

• CCR0, CCR1

Note: For bit command, you do not have to be careful since this matter has been already considered.

■ Caution: writing to registers which include a status flag

Writing to a register including a status flag (in particular, interrupt request flag) in order to control the function,

note that the actual writing to the registers may be delayed. This is because of using write buffers on the

busses to the resources which accept a write access from CPU immediately but can access the resource

registers delayed.

In this case it can happen that within an ISR the interrupt request flag is cleared by writing to the register and

the ISR is completed with RETI, but the interrupt request flag is still active and the ISR is executed again.

To synchronize the access to the resources on this architecture please follow this recommendation:

Use a read access (byte or halfword) to the RBSYNC address to synchronize the CPU operation (e.g. the

interrupt acceptance of the CPU) to a preceding write access to the resources on R-bus (e.g. to an interrupt

flag) on following addresses (0x0000-0x01FF, 0x0280-0x037F, 0x0400-0x063F and 0x0C00-0x0FFF).

Use a read access (byte or halfword) to the CBSYNC address to synchronize the CPU operation (e.g. the

interrupt acceptance of the CPU) to a preceding write access to the CANs on D-bus (e.g. to an interrupt flag)

on following addresses (0xC000-0xFFFF).

5

Page 22

Chapter 1 Introduction

3.Caution: debug-related matters

3. Caution: debug-related matters

■ Stepwise execution of RETI command

Under the circumstances where interruption is often generated when carrying out stepwise execution, only

relevant interrupt processing routine is repeatedly executed after the stepwise execution of RETI. Therefore,

main routine or low-level interruption program will not be executed.

To avoid this problem, do not proceed stepwise execution of RETI command.

Or, upon the time when no debug is needed for relevant interrupt routine, proceed the debug by prohibiting

relevant interruptions.

■ Operand break

Do not set the access for area including system stack pointer address as the target for data event break.

6

Page 23

4.How to Use This Document

4. How to Use This Document

■ Main terminology: This table shows main terminology used for FR60.

Term Meaning

32-bit-wide bus for internal instruction.

I-bus

D-bus

F-bus

R-bus

X-bus 32-bit-wide address and data bus. Via bus-converter for external bus, it accesses to external bus.

Main clock

(F

CL-MAIN

Subclock

(F

CL-SUB

Base clock

(Φ)

CPU clock

(CLKB)

Peripheral clock

(CLKP)

External bus clock

(CLKT)

CAN clock

(CLKCAN)

Main clock mode

Subclock mode

Main RUN Main RUN is the status which is in main clock mode and also all circuits are operable.

Sub RUN Sub RUN is the status which is in subclock mode and also all circuits are operable.

Oscillation

stabilization time

Main clock

oscillation

stabilization wait

)

)

Since FR60 series employ internal Harvard architecture, instruction and data are independent bus. For I-bus,

Harverd/Prinston-bus-converter is connected.

Internal 32-bit-wide data bus.

For D-bus, bit search module, Harverd/Prinston-bus-converter, R-bus interface (32-bit⇔16-bit Busconverter), and CAN modules are connected.

Internal 32-bit-wide bus.

F-bus is connected to embedded Flash/ROM and embedded RAM.

Internal 16-bit-wide data bus.

R-bus is connected to D-bus via R-bus-converter. For R-bus, peripheral function, I/O, clock generator and

interrupt controller are connected.

This a clock which acts as a benchmark for LSI operation triggered by high-speed-side oscillation.

This is connected to main clock oscillation stabilization timer and clock generator.

This a clock which acts as a benchmark for LSI operation triggered by low-speed-side oscillation.

This is connected to sub oscillation stabilisation timer, real-time clock and clock generator.

At the maximum speed, base clock has the same cycle as source oscillation. In PLL of the clock generator,

base clock has clock multiplied by 1, 2, 3, 4, 5, 6, 7 and 8 or clock divided by 2.

Base clock is basis clock which generates CLKB, CLKP and CKLT in the clock generator.

CPU clock is the clock which is referred by CPU, embedded ROM, embedded RAM, bit search module and

internal bus (I-bus, D-bus, F-bus and X-bus) operations. Generated from the base clock in the clock generator.

Peripheral clock is the clock which is referred by each peripheral function (peripheral functions other than bit

search module and CAN) connected to R-bus and R-bus, clock control, interrupt controller, I/O port and

external interrupt input d operations. Generated from the base clock in the clock generator.

External bus clock is the clock which is referred by external expansion bus interface connected to X-BUS and

external clock output operations. Generated from the base clock in the clock generator.

CAN clock is the clock which is referred by the CAN modules. Generated from the non modulated PLL

output clock to ensure operation within CAN network oscillation tolerances.

Mode which runs based on main clock. This main clock mode has status such as main RUN,main sleep, main

stop, oscillation stabilization wait RUN, oscillation stabilization wait reset and program reset.

Mode which runs based on subclock. This subclock mode has status such as sub RUN, sub sleep, sub stop,

subclock oscillation stabilization wait RUN and program reset.

Upon the reset (INITX, RST), return from stop, return from PLL abnormal operation, generation of watchdog

and during main clock stop, it takes oscillation stabilization time for main clock. Time base timer counts the

time.

Wait time until main clock oscillates after main clock stops in subclock mode.

Main clock oscillation stabilization timer counts the time.

Chapter 1 Introduction

7

Page 24

Chapter 1 Introduction

4.How to Use This Document

■ Access size and address position

Offset Register name Write-only Read-only

Address

Address offset value/Register name

Read/write

Block

Up/down counter

0, 1

Initial value

Byte access, Half-word access, and Word access are allowed.

There are three kinds of accesses such as Byte access, Half-word access and Word access. However, note

that some registers have restricted access. For more information, see “3.2. I/O Map (Page No.24)” or “Detail

Description of Register” in each chapter.

B,H,W : Byte access, Half-word access, and Wordaccess are allowed.

B : Byte access (Be sure to access by Byte.)

H : Half-word access (Be sure to access by Half-word.)

W : Word access (Be sure to access by Word.)

B, H : Byte access, Half-word access only (Word access is not allowed.)

H,W : Half-word access, Word access only (Byte access is not allowed.)

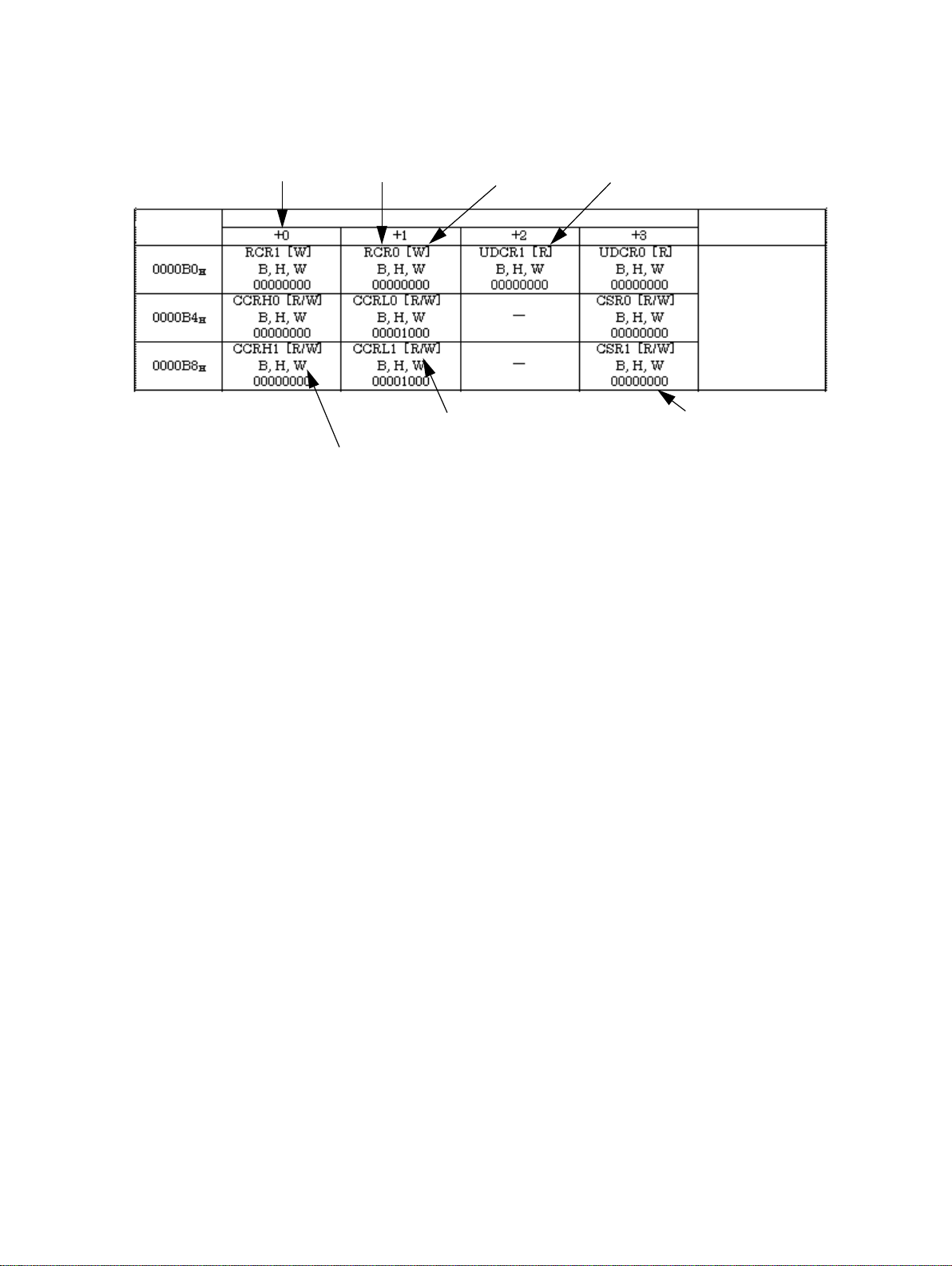

Reference

The following describes address position to access.

• In Word access, address becomes multiple of 4. (Lowest order 2 bits mandatorily become “00”.)

• In Half-word access, address becomes multiple of 2. (Lowest order 1 bit mandatorily becomes “0”.)

• In Byte access, address will not be changed.

Therefore, for example, make RCR0 register to use Half-word access,

For address 0B0H, RCR1+RCR0 register is accessed.

(When address offset is +1 and +2, (Example: RCR0+UDCR1) Half-word access is not allowed.)

8

Page 25

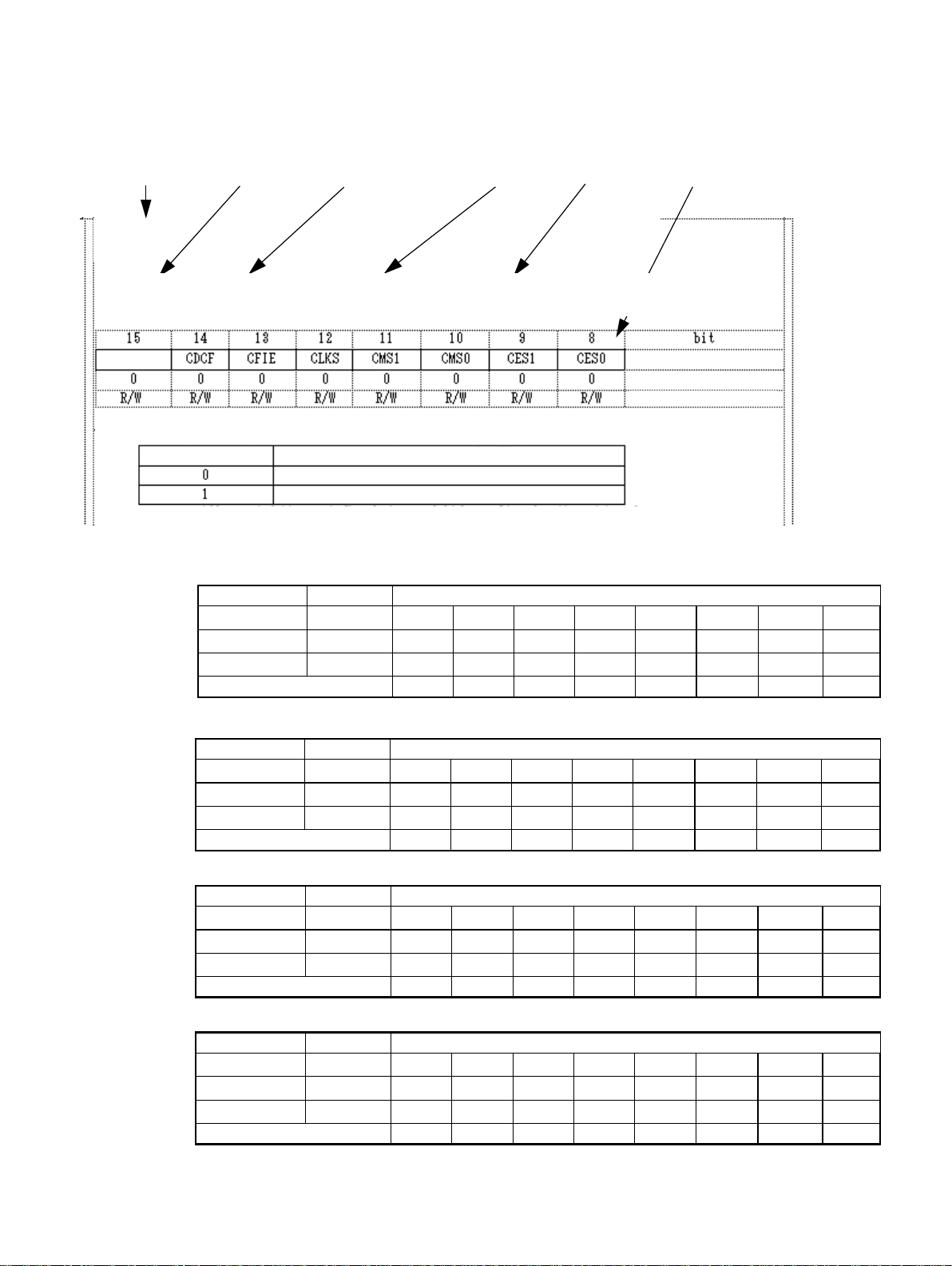

■ About access size and bit position

Register markRegister name Target peripheral device Address Access size Bit position

(1) Counter control register (Higher byte)

This is the register (higher byte) which controls up/down counter operation.

CCRH0 (Up/down counter 0): address 00B4h (Access: Byte, Half-word, Word)

CCRH1 (Up/down counter 1): address 00B8h (Access: Byte, Half-word, Word)

M16E/Reserved

*

bit15: Enable 16-bit mode

M16E (CCRH0 only) Enable 16-bit mode

8-bit x 2-channel mode (8-bit mode)

16-bit x 1-channel mode (16-bit mode)

*: CCRH1: ReservedAlways write 0 for writing. The read value is indeterminate.

Chapter 1 Introduction

4.How to Use This Document

Initial value

Attribute

When access size changes, bit position changes.

• In the case that address offset value is +0 (Example: CCRH0 register)

Access size Address Bit position

Byte

Half-word

Word

0B4

0B4

0B4

H+0H

H+0H

H+0H

07 06 05 04 03 02 01 00

15 14 13 12 11 10 09 08

31 30 29 28 27 26 25 24

Bit name M16E CDCF CFIE CLKS CMS1 CMS0 CES1 CES0

• In the case that address offset value is +1 (Example: CCRL0 register)

Access size Address Bit position

Byte

Half-word

Word

Bit name

0B4

0B4

0B4

H+1H

H+0H

H+0H

07 06 05 04 03 02 01 00

07 06 05 04 03 02 01 00

23 22 21 20 19 18 17 16

Reserved

CTUT UCRE RLDE UDCC CGSC CGE1 CGE0

• In the case that address offset value is +2 (Example: UDCR1 register)

Access size Address Bit position

Byte

Half-word

Word

0B0

0B0

0B0

H+2H

H+2H

H+0H

07 06 05 04 03 02 01 00

15 14 13 12 11 10 09 08

15 14 13 12 11 10 09 08

Bit name D15 D14 D13 D12 D11 D10 D9 D8

• In the case that address offset value is +3 (Example: UDCR 1 register)

Access size Address Bit position

Byte

Half-word

Word

0B0

0B0

0B0

H+3H

H+2H

H+0H

07 06 05 04 03 02 01 00

07 06 05 04 03 02 01 00

07 06 05 04 03 02 01 00

Bit name D7 D6 D5 D4 D3 D2 D1 D0

9

Page 26

Chapter 1 Introduction