Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

CM71-10121-3E

FR60

32-BIT MICROCONTROLLER

MB91350A Series

HARDWARE MANUAL

Page 2

Page 3

FR60

32-BIT MICROCONTROLLER

MB91350A Series

HARDWARE MANUAL

Be sure to refer to the “Check Sheet” for the latest cautions on development.

“Check Sheet” is seen at the following support page

URL : http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

“Check Sheet” lists the minimal requirement items to be checked to prevent problems beforehand in system development.

FUJITSU LIMITED

Page 4

Page 5

CONTENTS

■ Objectives and Intended Reader

The MB91350A series is one of the FR60 family of microcontrollers. The FR60 fam ily of microcontroll ers

is based on the FR30/40 family of CPUs, which u se a 32-b it high-performance RI SC CPU as the core CPU.

The FR60 family offers enhanced bus access. The MB91350A series is a single-chip microcontroller with

built-in peripheral resources. The MB91350A series is ideal for embedded control applications th at require

high-performance or high-speed CPU processing.

This manual is intended for engineers who will develop products using the MB91 350A seri es and describes

the functions and operations of the MB91350A series. Read this manual thoroughly.

For more information on instructions, see the "Instructions Manual".

Note : FR, which is an abbreviation of FUJITSU RISC controller, is a product of FUJITSU LIMITED.

■ Trademark

The company names and brand names herein are the trademarks or registered trademarks of their respective

owners.

■ License

Purchase of Fujitsu I2C components conveys a licence under the Philips I2C Patent Rights to use, these

2

components in an I

defined by Philips.

C system provided that the system conforms to the I2C Standard Specification as

■ Organization of This Manual

This manual consists of the following 19 chapters and an appendix.

CHAPTER 1 OVERVIEW

This chapter provides basic information required to u nderstand the MB91 350A series. It covers features

and dimensions, and presents a block diagram of the MB91350A series.

CHAPTER 2 HANDLING THE DEVICE

This chapter provides precautions on handling the device.

CHAPTER 3 CPU AND CONTROL UNITS

This chapter provides basic information required to understand the MB91350A series core CPU

functions. It covers architecture, specifications, and instructions.

CHAPTER 4 EXTERNAL BUS INTERFACE

This chapter describes basic items related to the external bus interface, register configuration/functions,

bus operation, bus timing, and procedures for setting the registers.

CHAPTER 5 I/O PORT

This chapter describes the I/O ports and the configuration and functions of registers.

i

Page 6

CHAPTER 6 8/16-bit Up/Down Counters/Timer and U-Timers

This chapter outlines the 8/16-bit up/down counter/timer an d U-TIMER and explains the configuration

and functions of the registers and timer operations.

CHAPTER 7 16-BIT FREE-RUNNING TIMER AND 16-BIT RELOAD TIMER

This chapter outlines the 16-bit free-running timer and 16-bit reload timer and explains the

configuration and functions of the registers and timer operations.

CHAPTER 8 PROGRAMMABLE PULSE GENERATOR (PPG) TIMER

This chapter gives an outline of the PPG (Programmable Pulse Generator) timer and explains the

register configuration and functions and the timer operations.

CHAPTER 9 INTERRUPT CONTROLLER

This chapter describes the overview of the interrupt controller, the configuration and functions of

registers, and interrupt controller operation.

CHAPTER 10 EXTERNAL INTERRUPT AND NMI CONTROLLER

This chapter outlines the external interrupt/NMI controller and explains the configuration and functions

of the registers and operations of the external interrupt/NMI controller.

CHAPTER 11 REALOS-RELATED HARDWARE

This chapter outlines the delayed interrupt module and bit search module, and explains the

configuration and functions of registers and operations.

CHAPTER 12 A/D CONVERTER

This chapter outlines the A/D converter and explains the configuration and functions of registers and

the A/D converter operations.

CHAPTER 13 8-BIT D/A CONVERTER

This chapter gives an overview of the 8-bit D/A converter, register configuration and functions, an d 8bit D/A converter operation.

CHAPTER 14 UART, SERIAL I/O INTERFACE (SIO), INPUT CAPTURE MODULE, AND

OUTPUT COMPARE MODULE

This chapter outlines the UART, SIO, input capture, and output compare, and expl ains the configuration

and functions of registers. It also explains UART, SIO, input capture, and output compare operations.

CHAPTER 15 I

This chapter describes the overview of the I

2

and I

C interface operation.

2

C INTERFACE

2

C interface, the configuration and functions of registers,

CHAPTER 16 DMA CONTROLLER (DMAC)

This chapter describes the overview of the DMAC, the configuration and functions of registers, and

DMAC operation.

CHAPTER 17 FLASH MEMORY

This chapter provides an outline of flash memory and explains its register configuration, register

functions, and operations.

CHAPTER 18 MB91F355A/F353A/F356B/F357B SERIAL PROGRAMMING CONNECTION

This chapter describes the serial onboard writing connection (Fujitsu standard) using the AF220/AF210 /

AF120/AF110 Flash Microcontroller Programmer by Yokogawa Digital Computer Corporation.

ii

Page 7

CHAPTER 19 DATA INTERNAL RAM/INSTRUCTION INTERNAL RAM ACCESS

RESTRICTION FUNCTIONS

This chapter outlines a function that restricts access to data internal RAM and instruction internal RAM.

It also explains the configuration and functions of reg isters and internal RAM operatio ns.

APPENDIX

This appendix consists of the following parts: I/O map, interrupt vectors, pin state for each CPU state,

and the instruction lists.

iii

Page 8

• The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

• The information, such as descriptions of function and application circuit examples, in this document are presented solely for the

purpose of reference to show examples of operations and uses of FUJITSU semiconductor device; FUJITSU does not warrant

proper operation of the device with respect to use based on such information. When you develop equipment incorporating the

device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU

assumes no liability for any damages whatsoever arising out of the use of the information.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license

of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU or any

third party or does FUJITSU warrant non-infringement of any third-party's intellectual property right or other right by using such

information. FUJITSU assumes no liability for any infringement of the intellectual property rights or other rights of third parties

which would result from the use of information contained herein.

• The products described in this document are designed, developed and manufactured as contemplated for general use, including

without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed

and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured,

could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss

(i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life

support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible

repeater and artificial satellite).

Please note that FUJITSU will not be liable against you and/or any third party for any claims or damages arising in connection

with above-mentioned uses of the products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such

failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and

prevention of over-current levels and other abnormal operating conditions.

• Exportation/release of any products described in this document may require necessary procedures in accordance with the

regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

• The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Copyright ©2003-2007 FUJITSU LIMITED All rights reserved

iv

Page 9

CONTENTS

CHAPTER 1 OVERVIEW ................................................................................................... 1

1.1 Features ........................ .......... .......... ......... .......... .......... ......... ....... ......... .......... .................................. 2

1.2 Block Diagram .................................................................................................................................... 7

1.3 Package Dimensions .......................................................................................................................... 9

1.4 Pin Layout ......................................................................................................................................... 11

1.5 List of Pin Functions ......................................... ... ... ... .... ...................................... .... ... ... ................... 13

1.6 Input-output Circuit Forms ................................................................................................................ 27

CHAPTER 2 HANDLING THE DEVICE .......................................................................... 31

2.1 Precautions on Handling the Device ................................................................................................. 32

2.2 Precautions on Using the Little-Endian Area .................................................................................... 37

2.2.1 C Compiler (fcc911) ................................. .... ... ....................................... ... ... ... .... ......................... 38

2.2.2 Assembler (fasm911) .................................................................................................................. 41

2.2.3 Linker (flnk911) ............................................................................................................................ 42

2.2.4 Debuggers (sim911, eml911, and mon911) ................................................................................ 43

CHAPTER 3 CPU AND CONTROL UNITS ..................................................................... 45

3.1 Memory Space .............. ... .... ... ... ....................................... ... ... .......................................................... 46

3.2 Internal Architecture ......... .... ... ... ....................................... ... ... .... ... ................................................... 49

3.2.1 Internal Architecture .................................................................................................................... 50

3.2.2 Overview of Instructions ........................................... ... ... ... .... ...................................... ... ............. 53

3.3 Programming Model ......................................................................................................................... 55

3.3.1 General-Purpose Registers .................. ... ....................................... ... .... ...................................... 56

3.3.2 Dedicated Registers .................................................................................................................... 57

3.4 Data Configuration ............................................................................................................................ 64

3.5 Memory Map ........................ ... ....................................... ... ... ....................................... ...................... 66

3.6 Branch Instructions ........................................................................................................................... 67

3.6.1 Operations with a Delay Slot ................................................. ... ... ... ... .... ...................................... 68

3.6.2 Operation without Delay Slot ....................................................................................................... 71

3.7 EIT (Exception, Interrupt, and Trap) ................................................................................................. 72

3.7.1 EIT Interrupt Levels .... ....................................... ... .... ... ... ....................................... ... ... ................ 73

3.7.2 ICR (Interrupt Control Register) ................................................................................................... 75

3.7.3 SSP (System Stack Pointer) ........................................................................................................ 77

3.7.4 Interrupt Stack ...... ... ....................................... ... ... ....................................... ... .... ......................... 78

3.7.5 TBR (Table Base Register) ......................................................................................................... 79

3.7.6 EIT Vector Table ...... ....................................... ... ... .... ... ....................................... ... ... .. ................. 80

3.7.7 Multiple EIT Processing ............................................................................................................... 84

3.7.8 Operations ................................................................................................................................... 86

3.8 Operating Modes ................. ... ... ....................................... ... ... ....................................... ................... 90

3.8.1 Bus Modes ................................................................................................................................... 91

3.8.2 Mode Settings .............................................................................................................................. 92

3.9 Reset (Device Initialization) .............................................................................................................. 94

3.9.1 Reset Levels ......... ... ... .... ...................................... .... ... ....................................... ... ...................... 95

v

Page 10

3.9.2 Reset Sources ................................... ... ... ....................................... ... .... ...................................... 96

3.9.3 Reset Sequence ................................ ... ... .... ... ... ....................................... ... ... ............................. 98

3.9.4 Oscillation Stabilization Wait Time .............................................................................................. 99

3.9.5 Reset Operation Modes ........................... ....................................... ... .... .................................... 102

3.10 Clock Generation Control ................................. ... ... ... ....................................... ... .... ... ... ................. 104

3.10.1 PLL Controls ................................................ ... ... ... .... ...................................... .... ... .................... 105

3.10.2 Oscillation Stabilization Wait Time and PLL Lock Wait Time .................................................... 106

3.10.3 Clock Distribution ....................................................................................................................... 108

3.10.4 Clock Division ............................................................................................................................ 110

3.10.5 Block Diagram of Clock Generation Controller ......................................... ... ... .... ... .................... 111

3.10.6 Register of Clock Generation Controller ............................................ .... ... ... ... .... ....................... 112

3.10.7 Peripheral Circuits of Clock Controller ....................................................................................... 129

3.11 Device State Control ....................................................................................................................... 133

3.11.1 Device States and State Transitions ......................................................................................... 134

3.11.2 Low-power Consumption Modes ............................................................................................... 138

3.12 Watch Timer ................................................................................................................................... 143

3.13 Main Clock Oscillation Stabilization Wait Timer .............................................................................. 149

3.14 Peripheral Stop Control .................................................................................................................. 155

CHAPTER 4 EXTERNAL BUS INTERFACE ................................................................ 161

4.1 Overview of the External Bus Interface .......................................................................................... 162

4.2 External Bus Interface Registers .................................................................................................... 167

4.2.1 ASR0 to ASR3 (Area Select Register) .............. ... .... ... ... ....................................... ... ... ... .... ... ... . 168

4.2.2 ACR0 to ACR7 (Area Configuration Registers) ......................................................................... 169

4.2.3 AWR0 to AWR3 (Area Wait Register) ....................................................................................... 175

4.2.4 IOWR0 to IOWR3 (I/O Wait Registers for DMAC) ..................................................................... 181

4.2.5 Chip Select Enable Register (CSER) ........................................................................................ 183

4.2.6 TCR (Terminal and Timing Control Register) ........... ... ... ... ....................................... ... ... .... ... .... 184

4.3 Setting Example of the Chip Select Area ........................................................................................ 186

4.4 Byte Ordering (Endian) and Bus Access ....................................... ... ... ... ........................................ 188

4.4.1 Relationship Between Data Bus Widths and Control Signals .................................................... 189

4.4.2 Big Endian Bus Access ............................................................................................................. 190

4.4.3 Little Endian Bus Access ........................................................................................................... 197

4.4.4 External Access ......................................................................................................................... 201

4.5 Ordinary Bus Interface .................................................................................................................... 205

4.6 Address/data Multiplex Interface .................. .... ...................................... .... ... ................................. 215

4.7 Prefetch Operation ............................................ ...................................... .... .................................... 218

4.8 DMA Access Operation .................................................................................................................. 222

4.9 Bus Arbitration ................................................................................................................................ 228

4.10 Procedure for Setting a Register .................................................................................................... 230

CHAPTER 5 I/O PORT .................................................................................................. 231

5.1 Overview of the I/O Port ................................................................................................................. 232

5.2 I/O Port Registers ........................................................................................................................... 234

CHAPTER 6 8/16-bit Up/Down Counters/Timer and U-Timers ................................. 245

6.1 8/16-bit Up/Down Counters/Timers ..................... ... ... .... ... ....................................... ... ... ... .............. 246

vi

Page 11

6.1.1 Overview of 8/16-bit Up/Down Counters/Tim er s ............................... .... ... ... ... .... ....................... 247

6.1.2 8/16-bit Up/Down Counters/Timer Registers ............................................................................. 252

6.1.3 Operation of the 8/16-bit Up/Down Counters/Timers ................................................................ 259

6.2 U-TIMER ....................... .......................................... .......................................... .............................. 268

6.2.1 Overview of the U-TIMER ............................... ... ... .... ... ....................................... ... ... ... .............. 269

6.2.2 U-TIMER Registers ................................................................................................................... 270

6.2.3 Operation of the U-TIMER ......................................................................................................... 275

CHAPTER 7 16-BIT FREE-RUNNING TIMER AND 16-BIT RELOAD TIMER ............. 277

7.1 16-bit Free-Running Timer ...... ... ... .... ...................................... .... ... ... ... ........................................... 278

7.1.1 Structure of the 16-bit Free-Running Timer ............................................................................... 279

7.1.2 16-bit Free-Running Timer Registers ................................ .... ... ... ....................................... ... .... 280

7.1.3 Operation of the 16-bit Free-Running Timer .............................................................................. 284

7.2 16-bit Reload Timer ................... ... .... ... ... ... ....................................... ... ... .... .................................... 286

7.2.1 Structure of the 16-bit Reload Timer ......................................................................................... 287

7.2.2 16-bit Reload Timer Register ..................................................................................................... 289

7.2.3 Operation of the 16-bit Reload Register .................................................................................... 292

CHAPTER 8 PROGRAMMABLE PULSE GENERATOR (PPG) TIMER ...................... 297

8.1 Overview of the PPG Timer ............................................................................................................ 298

8.2 PPG Timer Registers ...................................................................................................................... 302

8.2.1 Control Status Register ............................................................................................................. 303

8.2.2 PPG Cycle Setting Register (PCSR) ......................................................................................... 307

8.2.3 PPG Duty Setting Register (PDUT) ........................................................................................... 308

8.2.4 PPG Timer Register (PTMR) ..................................................................................................... 309

8.2.5 General Control Register 10 ...................................................................................................... 310

8.2.6 General Control Register 20 ...................................................................................................... 313

8.3 Operation of the PPG Timer ................ ... ... ... .... ... ....................................... ... ... ... .... ....................... 314

8.3.1 Timing Charts for PWM Operation ............................................................................................ 315

8.3.2 Timing Charts for One-Shot Operation ...................................................................................... 317

8.3.3 Interrupt Sources and Timing Chart (with PPG output set for ordinary polarity) ........................ 318

8.3.4 Examples of Methods of All-L and All-H PPG Output ................................................................ 319

8.3.5 Activation of Multiple Channels Using the General Control Register ........................................ 320

CHAPTER 9 INTERRUPT CONTROLLER ................................................................... 323

9.1 Overview of the Interrupt Controller ................................................................................................ 324

9.2 Interrupt Controller Registers ..................................... .... ... ... ... ....................................... ... .............. 328

9.2.1 Interrupt Control Register (ICR) ................................................................................................. 329

9.2.2 Hold request cancellation request register (HRCL) ................................................................... 331

9.3 Operation of the Interrupt Controller .......................... .... ... ....................................... ... ... ................. 332

CHAPTER 10 EXTERNAL INTERRUPT AND NMI CONTROLLER ............................... 341

10.1 Overview of the External Interrupt and NMI Controller ................................................................... 342

10.2 External Interrupt and NMI Controller Registers ............................................................................. 344

10.2.1 Enable Interrupt Request Register (ENIRn) .............................................................................. 345

10.2.2 External Interrupt Request Register (EIRRn) ............................................................................ 346

10.2.3 External Level Register (ELVRn) ............................................................................................... 347

vii

Page 12

10.3 Operation of the External Interrupt and NMI Con tr oller .................................................................. 348

CHAPTER 11 REALOS-RELATED HARDWARE .......................................................... 351

11.1 Delayed Interrupt Module ............................................................................................................... 352

11.1.1 Overview of the Delayed Interrupt Module .................................. ... ....................................... ... . 353

11.1.2 Delayed Interrupt Module Registers .......................................................................................... 354

11.1.3 Operation of the Delayed Interrupt Module ............................................................................... 355

11.2 Bit Search Module ............................................ ...................................... .... ... ... ... ........................... 356

11.2.1 Overview of the Bit Search Module ............................................. ... ... .... .................................... 357

11.2.2 Bit Search Module Registers ..................................................................................................... 358

11.2.3 Operation of the Bit Search Module .......................................................................................... 360

CHAPTER 12 A/D CONVERTER .................................................................................... 363

12.1 Overview of the A/D Converter ....................................................................................................... 364

12.2 A/D Converter Registers ................................................................................................................. 366

12.2.1 Control Status Register (ADCS1) .............................................................................................. 367

12.2.2 Control Status Register (ADCS2) .............................................................................................. 370

12.2.3 Conversion Time Setting Register (ADCT) ................................................................................ 373

12.2.4 Data Registers (ADTHx and ADTLx) ......................................................................................... 375

12.3 Operation of the A/D Converter ........ ... ... ... ... ....................................... ... .... .................................... 376

CHAPTER 13 8-BIT D/A CONVERTER .......................................................................... 379

13.1 Overview of the 8-bit D/A Converter ................................. ....................................... ... ... ................. 380

13.2 8-bit D/A Converter Register ........................................................................................................... 382

13.3 8-bit D/A Converter Operation ........................................................................................................ 384

CHAPTER 14 UART, SERIAL I/O INTERFACE (SIO), INPUT CAPTURE MODULE,

AND OUTPUT COMPARE MODULE ...................................................... 385

14.1 UART ................................... ....................................................................... .................................... 386

14.1.1 Features of the UART ................................................................................................................ 387

14.1.2 UART Registers ......................................................................................................................... 390

14.1.3 Operation of the UART .............................................................................................................. 399

14.1.4 Example of using the UART ...................................................................................................... 407

14.2 Serial I/O Interface (SIO) ................................................................................................................ 410

14.2.1 Overview of the Serial I/O Interface (SIO) ............ .... ... ... ... .... ...................................... ... .... ....... 411

14.2.2 Serial I/O Interface Registers .................................................................................................... 413

14.2.3 Operation of the Serial I/O Interface (SIO) ................................................................................ 419

14.3 Input Capture Module ............. ... ... .... ... ... ....................................... ... ... ........................................... 425

14.3.1 Overview of the Input Capture Module .............. ... .... ... ... ....................................... ... ... .............. 426

14.3.2 Input Capture Module Registers ................................................................................................ 428

14.3.3 Input Capture Operation ............................................................................................................ 430

14.4 Output Compare ............................................................................................................................. 431

14.4.1 Features of the Output Compare Module .................................................................................. 432

14.4.2 Output Compare Module Registers ........................................................................................... 434

14.4.3 Operation of the Output Compare Module ................................................................................ 437

viii

Page 13

CHAPTER 15 I2C INTERFACE ....................................................................................... 439

15.1 Overview of the I2C Interface .......................................................................................................... 440

15.2 I

15.3 Explanation of I

15.4 Operation Flowcharts .... ... .... ... ... ... ....................................... ... .... .................................... ................ 468

2

C Interface Registers ................................................................................................................... 444

15.2.1 Bus Status Register (IBSR) ....................................................................................................... 445

15.2.2 Bus Control Register (IBCR) ..................................................................................................... 448

15.2.3 Clock Control Register (ICCR) .................................................................................................. 455

15.2.4 10-bit Slave Address Register (ITBA) ........................................................................................ 457

15.2.5 10-bit Slave Address Mask Register (ITMK) ............................................................................. 458

15.2.6 7-bit Slave Address Register (ISBA) ......................................................................................... 460

15.2.7 7-bit Slave Address Mask Register (ISMK) ............................................................................... 461

15.2.8 Data Register (IDAR) ................................................................................................................. 462

15.2.9 Clock Disable Register (IDBL) ................................................................................................... 463

2

C Interface Operation ........................................................................................... 464

CHAPTER 16 DMA CONTROLLER (DMAC) .................................................................. 471

16.1 Overview .......................... ....................................... .......................................... .............................. 472

16.2 Detailed Explanation of Registers ................................................................................................... 475

16.2.1 DMAC ch0 to ch4 Control/Status Registers A ........................................................................... 476

16.2.2 DMAC ch0 to ch4 Control/Status Registers B ........................................................................... 482

16.2.3 DMAC ch0 to ch4 Transfer Source/Transfer Destination Add re ss Set tin g Regi st er s ............ ... . 488

16.2.4 DMAC ch0 to ch4 DMAC All-Channel Control Register ..................................... ... .................... 490

16.3 Explanation of Operation ........... ... .... ... ....................................... ... ... .............................................. 492

16.3.1 Overview of Operation ........................................................... ...................................... .. ............ 493

16.3.2 Setting a Transfer Request ........................................................................................................ 496

16.3.3 Transfer Sequence ............................... ... ....................................... ... .... .................................... 497

16.3.4 General Aspects of DMA Transfer ............................................................................................. 501

16.3.5 Addressing Mode .. ... ....................................... ... ... .... ...................................... .... ... ... ... .............. 503

16.3.6 Data Types ................................................................................................................................ 504

16.3.7 Transfer Count Control ............................ .... ... ... ... ....................................... ... .... ... ... ................. 505

16.3.8 CPU Control .............................................................................................................................. 506

16.3.9 Hold Arbitration .......................................................................................................................... 507

16.3.10 Operation from Starting to End/Stopping ................................................................................... 508

16.3.11 Transfer Request Acceptance and Transfer .............................................................................. 509

16.3.12 Clearing Peripheral Interrupts by DMA ...................................................................................... 510

16.3.13 Temporary Stopping .......................... ... ... .... ... ....................................... ... ... .............................. 511

16.3.14 Operation End/Stopping ............................................................................................................ 512

16.3.15 Stopping Due To an Error .......................................................................................................... 513

16.3.16 DMAC Interrupt Control ........................ ... .... ... ....................................... ... ... .............................. 514

16.3.17 DMA Transfer during Sleep ....................................................................................................... 515

16.3.18 Channel Selection and Control .................................................................................................. 516

16.3.19 Supplement on External Pin and Internal Operation Timing ..................................................... 518

16.4 Operation Flowcharts .... ... .... ... ... ... ....................................... ... .... .................................... ................ 522

16.5 Data Path ........................................................................................................................................ 525

16.6 DMA External Interface ................................................................................................................... 529

ix

Page 14

CHAPTER 17 FLASH MEMORY ..................................................................................... 533

17.1 Outline of Flash Memory ................................................................................................................. 534

17.2 Flash Memory Registers ................................................................................................................. 539

17.2.1 Flash Control/Status Register (FLCR) (CPU mode) .................................................................. 540

17.2.2 Flash Memory Wait Register (FLWC) ................... .... ...................................... .... ... ... ................. 543

17.3 Explanation of Flash Memory Operation .......................................................... ... .... ... ... ................. 545

17.4 Automatic Algorithm of Flash Memory ....... ....................................... ... ... .... ... ................................. 547

17.4.1 Command Sequence ......................................................... .... ... ... ... ... ........................................ 548

17.4.2 Checking the Automatic Algorithm Operating Status ................................................................ 552

17.5 Writing to and Erasing Flash Memory ............................................................................................. 557

17.5.1 Read/Reset Status .................................................................................................................... 558

17.5.2 Data Writing ............................................................................................................................... 559

17.5.3 Data Erasure (Chip Erasure) ..................................................................................................... 561

17.5.4 Data Erasure (Sector Erasure) .................................................................................................. 562

17.5.5 Temporary Sector Erase Stop ........................... ....................................... ... ... .... ... .................... 564

17.5.6 Sector Erase Restart ................................................................................................................. 565

CHAPTER 18 MB91F355A/F353A/F356B/F357B SERIAL PROGRAMMING CONNECTION

................................................................................................................... 567

18.1 Basic Configuration of MB91F355A/F353A/F356B/F357B Serial Programming Connection ......... 568

18.2 Pins Used for Fujitsu Standard Serial Onboard Writing .................................................................. 569

18.3 Examples of Serial Programming Connection ........................ .... ... ... ... ... ....................................... . 570

18.4 System Configuration of Flash Microcontrolle r Pro g ramm e r ...................... ... ... ... .... ....................... 572

18.5 Other Precautionary Information .................................................................... ... ... ........................... 573

CHAPTER 19 DATA INTERNAL RAM/INSTRUCTION INTERNAL RAM

ACCESS RESTRICTION FUNCTIONS .................................................... 575

19.1 Overview .......................... ....................................... .......................................... .............................. 576

19.2 Explanation of Registers ............... .... ... ... ....................................... ... ... ... ........................................ 577

19.3 Explanation of Operation ........... ... .... ... ....................................... ... ... .............................................. 579

APPENDIX ......................................................................................................................... 581

APPENDIX A I/O Map ................................................................................................................................ 582

APPENDIX B Interrupt Vector .................................................................................................................... 594

APPENDIX C Pin States in Each CPU State .............................................................................................. 597

APPENDIX D Instruction Lists .................................................................................................................... 603

INDEX...................................................................................................................................619

x

Page 15

Main changes in this edition

Page Changes (For details, refer to main body.)

- - Products were changed.

(MB91F353A/352A/353A → MB91F353A/351A/352A/353A)

(MB91F35 → MB91F353A/351A/352A/353A)

(MB91F35A → MB91F353A/351A/352A/353A)

(MB91F355A/353A → MB91F353A/F355A/F356B/F357B)

(MB91F355A/355A/354A → MB91F355A/355A/354A/F356B/ F3 57B)

- - "flash memories" were changed.

(256 KB flash memories → 256K bytes/128K bytes flash memories)

(512 KB flash memories → 512K bytes/256K bytes flash memories)

- - The following terms were unified.

(FR series → FR family)

(FR30 series → FR30 family)

3 1.1 Features "Table 1.1-1 Internal Memory Details" was changed.

(The column for MB91351A was added.)

(The columns for MB91F356B and MB91F357B were added.)

5 1.1 Features "■ Other Features" was changed.

(LQFP-176 (lead pitch 0.50 mm) → MB91F355A/F356B/F357B/355A/354A:

LQFP-176 (lead pitch 0.50 mm))

6 1.1 Features "Table 1.1-2 Comparison of Functions: Internal Memory (Products whose

Memory Capacity is to be Extended and the Configuration of Memory are Currently under Study.)" was changed.

(The column for MB91351A was added.)

7, 8 1.2 Block Diagram "Figure 1.2-1 MB91F353A/353A/352A/351A Block Diagram" was changed.

"Figure 1.2-2 MB91355A/354A/F355A/F356B/F357B Block Diagram" was

changed.

12 1.4 Pin Layout "■ Pin layout of the MB91352A and MB91F353A (LQFP-120)" was deleted.

46 3.1 Memory Space "Figure 3.1-1 MB91F355A, MB91355A, MB91F353A, MB91353A and

MB95F357B Memory Maps" was changed.

(Internal ROM → Internal RAM)

47 "Figure 3.1-2 MB91351A Memory Map " was added.

"Figure 3.1-3 MB91354A and MB91352A Memory Map" was changed.

(Internal ROM → Internal RAM)

48 "Figure 3.1-4 MB91F356B Memory Map" was added.

xi

Page 16

Page Changes (For details, refer to main body.)

48 3.1 Memory Space "■ Memory Map" was changed.

(For the MB91V350A, a 512K-byte internal ROM area is used as emulation

RAM for the MB91355A, F355A, 353A, and F353A memory map. In addi-

tion, the instruction internal RAM is extended from 8 KB to 16 KB. → For the

MB91V350A, with the memory map of the MB91355A/F355A/353A/F353A/

F357B, the 512K bytes area of the internal ROM, and with the memory map of

the MB91F356B, the 256K bytes area of the internal ROM, is the emulation

RAM. In addition, internal RAM(Instruction) is extended from 8K bytes to16K

bytes.)

174 4.2.2 ACR0 to ACR7

(Area Configuration Registers)

230 4.10 Procedure for Setting

a Register

238

to

244

246 6.1 8/16-bit Up/Down

271 6.2.2 U-TIMER Registers "■ Reload Register (UTIMR)" was changed.

275 6.2.3 Operation of the U-

348 10.3 Operation of the

5.2 I/O Port Registers "Table 5.2-1 Initial Values and Functions of the Port Function Registers

Counters/Timers

TIMER

External Interrupt and

NMI Controller

"Notes:" was changed.

"(Set both ASR and ACR at the same ti me us ing wo rd access. When acces sing

ASR and ACR using half word, please set ACR after setting ASR.)" was

added.

"■ Procedure for Setting the External Bus Interface" was changed.

(PFRs)" was changed.

("*2" was deleted.)

"■ Overview of the 8/16-bit Up/Down Counters/Timers" was changed.

(The MB91F355A/355A/354A/V350A→ The MB91F355A/355A/354A/

F356B/F357B)

("Note:" was added.)

"■ Calculation of Baud Rate" was changed.

("Note:" was added.)

"■ Operating Procedure for an External Interrupt" was changed.

("1. Terminal and general-purpose I/O port used as external interrupt input are

set to input port." was added.)

384 13.3 8-bit D/A Converter

Operation

413, 414 14.2.2 Serial I/O Interface

Registers

450 15.2.2 Bus Control Regis-

ter (IBCR)

451

to

454

479 16.2.1 DMAC ch0 to ch4

Control/Status Registers A

"Table 13.3-1 Logical Expressions for D/A Converter Output Voltage" was

changed.

(Values specified in DADR1 DADR2 DADR3 → Values specified in DADR0

DADR1 DADR2)

"[Bits 15, 14, and 13] Shift clock selection bits (SMD2, SMD1, SMD0: Serial

shift clock mode)" was changed.

"[Bit 12] MSS (Master Slave Select)" was changed.

("Note:" was changed.)

"■ Bus Control Register (IBCR)" was changed.

("Note:" was changed.)

"■ [Bits 28 to 24] IS4 to 0 (Input Select)*: Transfer Source Selection" was

changed.

xii

Page 17

Page Changes (For details, refer to main body.)

494 16.3.1 Overview of Opera-

tion

"● Fly-by transfer (I/O → memory)" was changed.

(Access areas used for MB91350A fly-by transfer must be external areas. →

Access areas used for MB91F355A/F356B/F357B/355A fly-by transfer must

be external areas.)

534 17.1 Outline of Flash

536 "Figure 17.1-3 Memory Map of MB91F356B Flash Memory" was added.

Memory

"Summary of 17.1 Outline of Flash Memory" was changed.

537, 538 "■ Sector Address Table of Flash Memory" was changed.

544 17.2.2 Flash Memory W ait

"[Bits 2 to 0] WTC2, WTC1, and WTC0 (wait cycle bits)" was changed.

Register (FLWC)

559 17.5.2 Data Writing "■ How to Specify Address" was changed.

568 18.1 Basic Configuration

of MB91F355A/F353A/

F356B/F357B

Serial Programming Con-

"■ Basic Configuration of MB91F355A/F353A/F356B/F357B Serial Programming Connection" was changed.

("Either a program operating in single-chip mode or a program operating in

internal ROM external bus mode is selected to write." was added.)

nection

569 18.2 Pins Used for Fujitsu

Standard Serial Onboard

"Table 18.2-1 Function of Pins Used for Fujitsu Standard Serial Onboard Writing" was changed.

Writing

573 18.5 Other Precautionary

Information

"● Oscillation Clock Frequency" was changed.

(4.0 MHz and 12.0 MHz → 10.0 MHz and 12.5 MHz)

"● Port State for Write Operations on Flash Memory" was changed.

(reset state except → initial state in the single-chip mode except)

584 APPENDIX A I/O Map "Address 00009C

of Table A-1 I/O Map" was changed.

H

("*1" was added.)

The vertical lines marked in the left side of the page show the changes.

xiii

Page 18

xiv

Page 19

CHAPTER 1

OVERVIEW

The FR family is a standard single-chip microcontroller

that has a 32-bit high-performance RISC CPU as well as

internal I/O resources and bus control configuration for

embedded controllers that require high-performance or

high-speed CPU processing.

This model is an FR60 family model that is based on the

FR30/40 family of CPUs, and offers enhanced bus

access. The FR family is a single-chip microcontroller

with built-in peripheral resources.

1.1 Features

1.2 Block Diagram

1.3 Package Dimensions

1.4 Pin Layout

1.5 List of Pin Functions

1.6 Input-output Circuit Forms

1

Page 20

CHAPTER 1 OVERVIEW

1.1 Features

This section describes the features of the FR60 family microcontrollers.

■ FR CPU Features

• 32-bit RISC, load/store architecture, five stages pipeline

• Maximum operating frequency of 50 MHz [PLL used: Oscillation at 12.5 MHz]

• 16-bit fixed-length instructions (basic instructions), one instruction per cycle

• Memory-to-memory transfer, bit processing, instructions including barrel shift, etc.--instructions

appropriate for embedded applications

• Function entry and exit instructions, multi load/store instructions of register content--instructions

compatible with high-level languages

• Register interlock function to facilitate assembly- language coding

• Built-in multiplier/instruction-level support

• Signed 32-bit multiplication: 5 cycles

• Interrupts (saving of PC and PS): 6 cycles, 16 priority lev els

• Harvard architecture enabling simultaneous execution of both program access and data access

• Instructions compatible with the FR family

■ Bus Interface

• Maximum operating frequency of 25 MHz

• 24-bit address full output (16M bytes space) capability

• 8/16-bit data output

• Prefetch buffer installed

• Use of unused data/address pins as general-purpose I/O ports

• Totally independent 4-area chip select outputs that can be configured in units as small as 64K bytes

• Supported interface for each type of memory

• Basic bus cycle (2 cycles)

• Automatic wait cycle generator that can be programmed for each area and can insert waits.

• External wait cycle using RDY input

• DMA support of fly-by transfer capable of wait control for independent I/O

• Signed 16-bit multiplication: 3 cycles

(21-bit address full output (2M bytes space) capability: MB91F353A/351A/35 2A/353A)

SRAM and ROM/FLASH

Page mode FLASHROM and page mode ROM interface

(The MB91F353A/351A/352A/353A does not support fly-by transfer.)

2

Page 21

■ Internal Memory

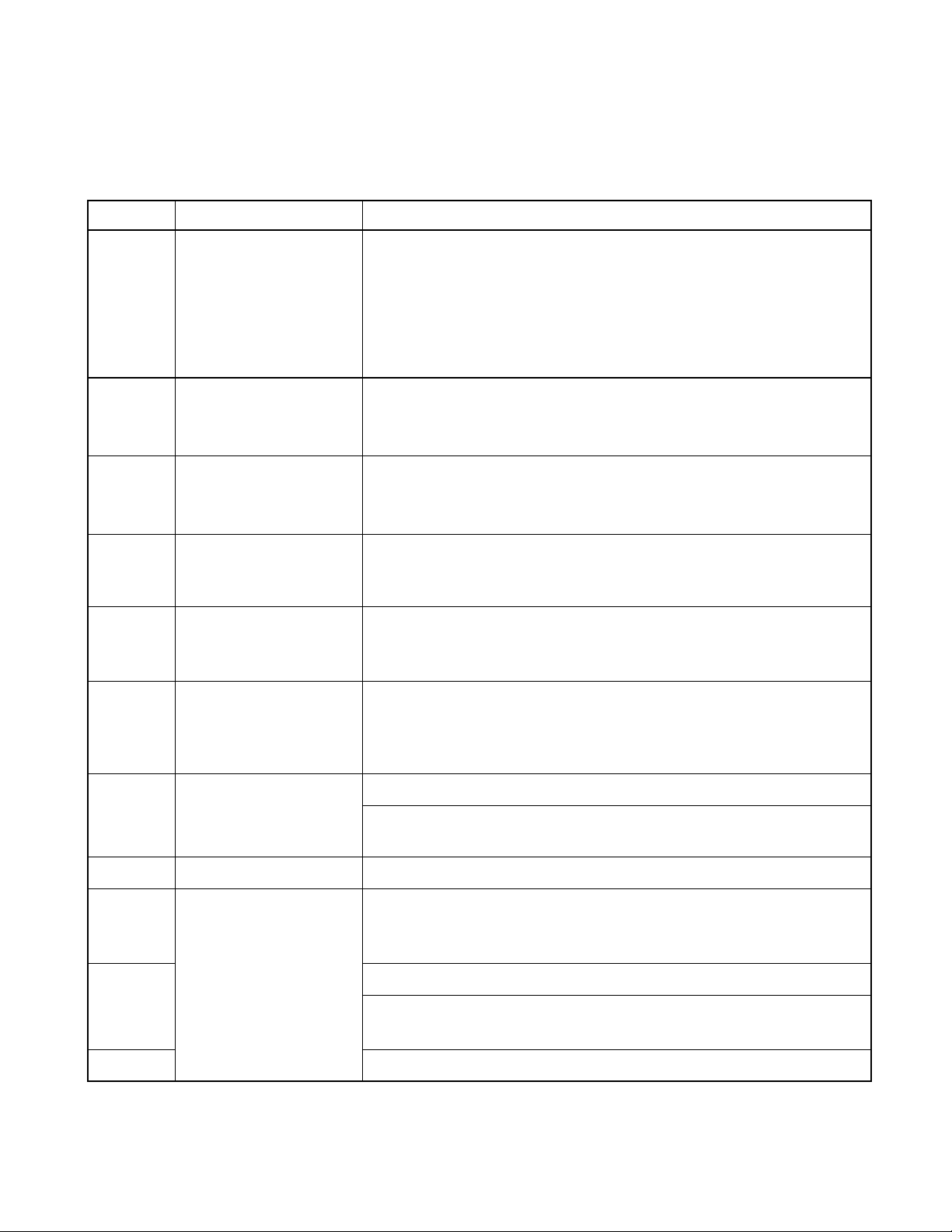

Table 1.1-1 provides details about internal memory.

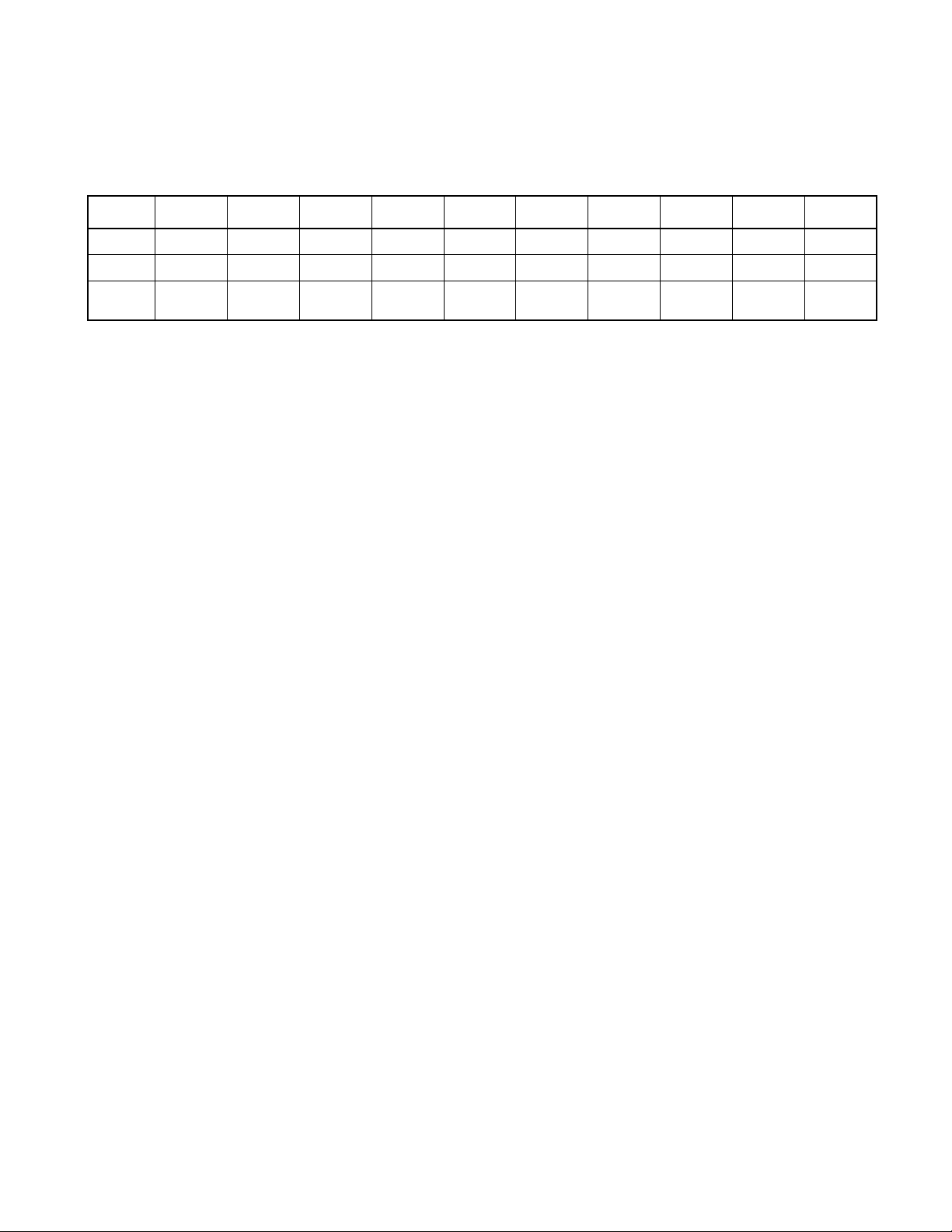

Table 1.1-1 Internal Memory Details

Memory MB91V350A MB91F355A MB91F356B MB91F357B MB91355A MB91354A MB91F353A MB91353A MB91352A MB91351A

ROM None 512K bytes 256K bytes 512K bytes 512K bytes 384K bytes 512K bytes 512K bytes 384K bytes 384K bytes

Stack RAM 16K bytes 16K bytes 16K bytes 16K bytes 16K bytes 8K bytes 16K bytes 16K bytes 8K bytes 16K bytes

Instruction

RAM

16K bytes 8K bytes 8K bytes 8K bytes 8K bytes 8K bytes 8K bytes 8K bytes 8K bytes 8K bytes

■ DMAC (DMA Controller)

• Up to 5 channels can operate simultaneously (3 channels for external → external)

• Three transfer sources (external pins, built-in peripherals, and software)

• Selectability of activation source using software (activation can be from UART0, UART1, and

UART2).

• Addressing mode with 32-bit full address specifications (increase, decrease, fixed)

• Transfer modes (demand transfer, burst transfer, step transfer, block transfer)

• Fly-by transfer supported between external I/O and memory

• Transfer data size that can be selected from 8, 16, and 32 bits

• Multibyte transfer supported (defined by software)

• DMAC descriptor I/O area (200 to 240

(The MB91F353A/351A/352A/353A does not have an external interface.)

External pin transfer is not supported. Demand transfer and fly-by transfer cannot be used.

■ Bit Search Module (Used by REALOS)

• Searches for the position of the first bit varying between 1 and 0 in the MSB of a word

■ Various Timers

• 16-bit reload timer; 4 channels (including 1 channel for REALOS)

The internal clock can be selected using divide by 2, 8, or 32.

(For ch3, divide by 64 or 128 can also be selected.)

• 16-bit free-running timer; 1 channel

Output compare: 8 channels (MB91F353A/351A/352A/353A: 2 channels)

Input capture: 4 channels

• 16-bit PPG timer: 6 channels (MB91F353A/351A/352A/353A: 3 channels)

and 1000H to 1024H)

H

3

Page 22

CHAPTER 1 OVERVIEW

■ UART

• UART full-duplex double buffer

• 5 channels, (MB91F353A/351A/352A/353A: 4 channels)

• Parity or no parity can be selected.

• Either asynchronous (start-stop synchronization) or CLK synchronous commu nicati on can be sel ected.

• Built-in timer for dedicated baud rates

• An external clock can be used as the transfer clock.

• Plentiful error detection functions (parity, frame, overrun)

• 115 kbps supported

■ SIO

• 8-bit data serial transfer

• 3 channels, (MB91F353A/351A/352A/353A: 2 channels)

• A shift clock can be selected from three internal types and one external type.

• The shift direction can be switched between LSB and MSB.

■ Interrupt Controller

• Total number of external interrupts: 17

(MB91F353A/351A/352A/353A: (9)) [One non-maskable interrupt pin and 16 (8) ordinary

interrupt pins that can be used for wakeup in stop mode.]

• Interrupts from internal peripherals

• Priority level can be defined as programmable (16 levels) except for the unmaskable pin

■ D/A Converter

• 8-bit resolution: 3 channels (MB91F353A/351A/352A/353A: 2 channels)

■ A/D Converter

• 10-bit resolution: 12 channels (MB91F353A/351A/352A/353A: 8 channels)

• Serial-parallel conversion type

Conversion time: About 1.48 µs

• Conversion modes (single conversion mode and continuous conversion mode)

• Activation sources (software, external trigger, and peripheral interrupt)

■ Other Interval Timers and Counters

• 8/16-bit up/down counter

Note: The MB91F353A/351A/352A/353A supports only an 8-bit up/down counter.

• 16-bit timer (U-TIMER), 5 channels, (MB91F353A/351A/352A/353A: 4 channels)

• Watchdog timer

4

Page 23

■ I2C* Bus Interface (400 kbps Supported)

• 1 channel master/slave send and receive

- Arbitration function and clock synchronization function

■ I/O Ports

• 3 V I/O ports

(5 V input is supported for those ports that are also used for external in terrupts (16 ports, MB9 1F353A/

351A/352A/353A: 8 ports).

• Up to 126 ports (MB91F353A/351A/352A/35 3A: Up to 84 ports)

■ Other Features

• Internal oscillation circuit as a clock source provided. PLL multiplication can also be selected.

•INIT

• Additionally, a watchdog timer reset and software resets are provided.

• Stop mode and sleep mode supported as low-power consumption modes

• Gear function

• Built-in timebase timer

• Package:

is provided as a reset pin.

(When the INIT

stabilize.)

Low-power consumption operation using 32 kHz CPU operation enabled

MB91F355A/F356B/F357B/355A/354A: LQFP-176 (lead pitch 0.50 mm)

pin is cleared, CPU operation starts immediately without waiting for oscillation to

MB91F353A/351A/352A/353A: LQFP-120 (lead pitch 0.50 mm)

• CMOS technology: 0.35 µm

• Supply voltage: 3.3 V (-0.3 V to +0.3 V)

2

*: I

C license

Purchase of Fujitsu I

components in an I

defined by Philips.

2

C components conveys a license under the Philips I2C Patent Rights to use, these

2

C system provided that the system conforms to the I2C Standard Specification as

5

Page 24

CHAPTER 1 OVERVIEW

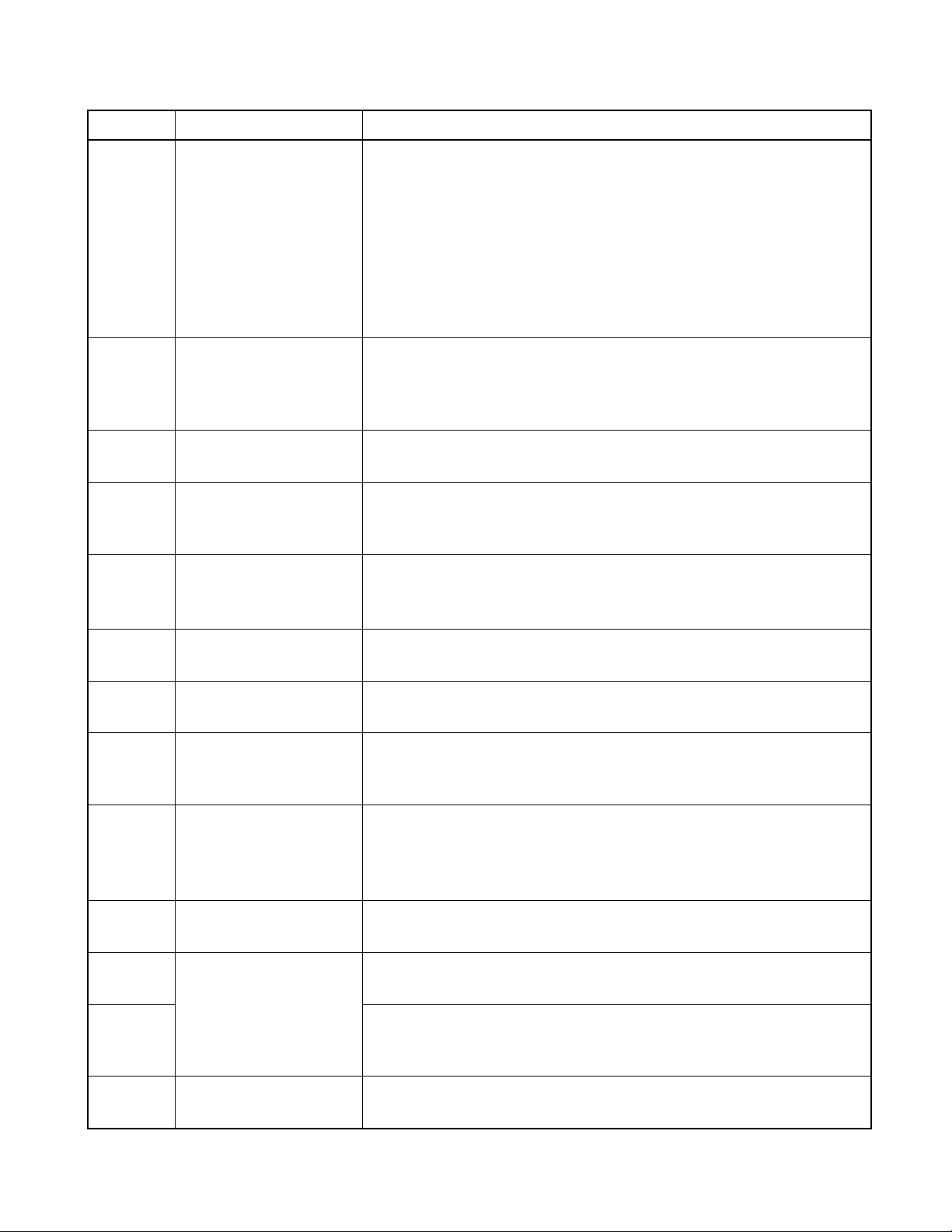

■ Comparison of Functions

Table 1.1-2 compares the functions of FR60 family microcontrollers.

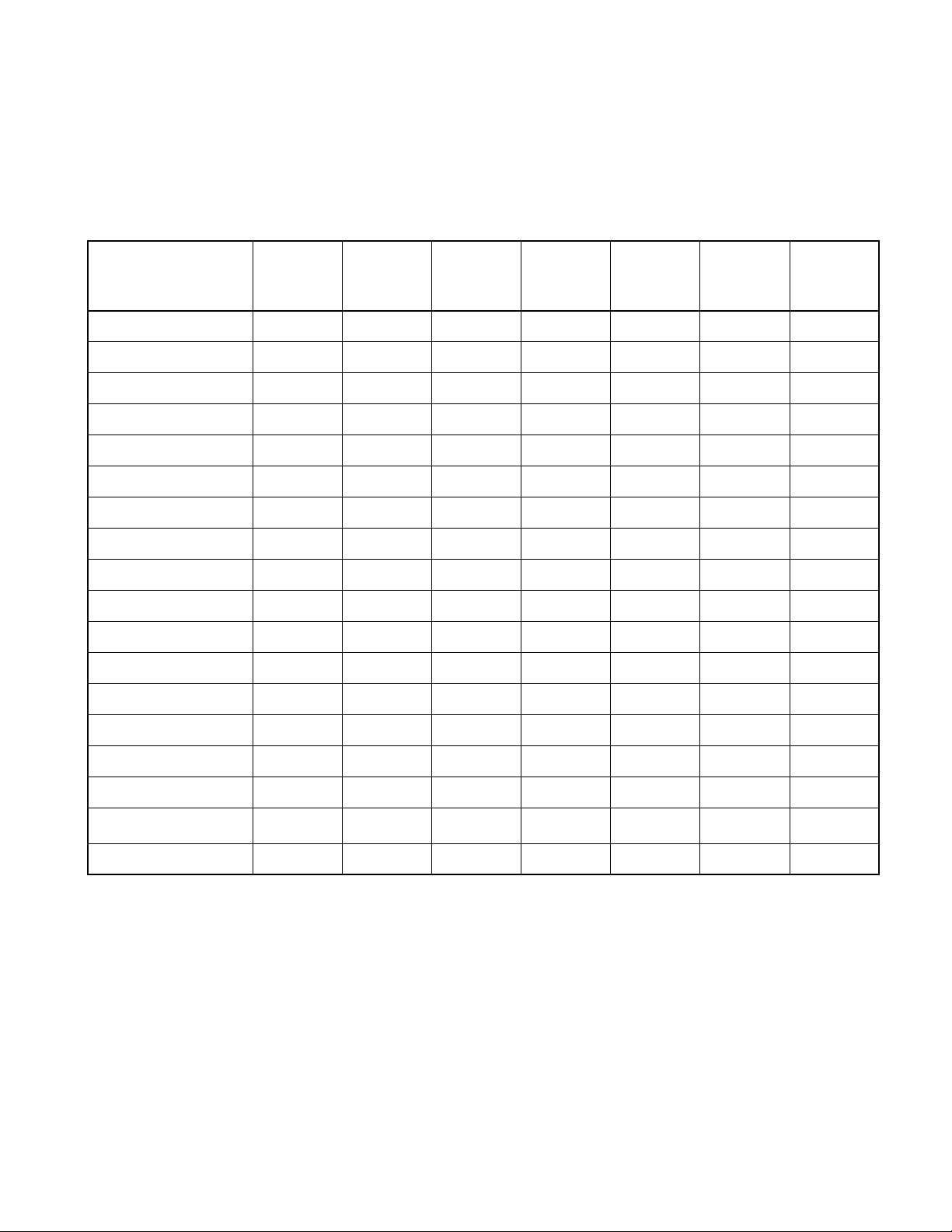

Table 1.1-2 Comparison of Functions: Internal Memory (Products whose Memory Capacity is to be

Extended and the Configuration of Memory are Currently under

Study.)

Function

MB91V350A

MB91F355A

MB91355A

MB91F357B

MB91F356B MB91354A

MB91F353A

MB91353A

MB91352A MB91351A

ROM None 512K bytes 256K bytes 384K bytes 512K bytes 384K bytes 384K bytes

Stack RAM 16K bytes 16K bytes 16K bytes 8K bytes 16K bytes 8K bytes 16K bytes

Instruction RAM 16K bytes 8K bytes 8K bytes 8K bytes 8K bytes 8K bytes 8K bytes

DMAC 5ch 5ch 5ch 5ch 5ch 5ch 5ch

A/D input 12ch 12ch 12ch 12ch 8ch 8ch 8ch

D/A input 3ch 3ch 3ch 3ch 2ch 2ch 2ch

UART 5ch 5ch 5ch 5ch 4ch 4ch 4ch

U-TIMER 5ch 5ch 5ch 5ch 4ch 4ch 4ch

SIO 3ch 3ch 3ch 3ch 2ch 2ch 2ch

External interrupt 16ch 16ch 16ch 16ch 8ch 8ch 8ch

Free-running timer 1ch 1ch 1ch 1ch 1ch 1ch 1ch

PPG 6ch 6ch 6ch 6ch 3ch 3ch 3ch

Reload timer 4ch 4ch 4ch 4ch 4ch 4ch 4ch

Input capture 4ch 4ch 4ch 4ch 4ch 4ch 4ch

Output compare 8ch 8ch 8ch 8ch 2ch 2ch 2ch

8-bit up/down counter 2ch 2ch 2ch 2ch 1ch 1ch 1ch

2

I

C

1ch 1ch 1ch 1ch 1ch 1ch 1ch

Number of pins 279 176 176 176 120 120 120

6

Page 25

1.2 Block Diagram

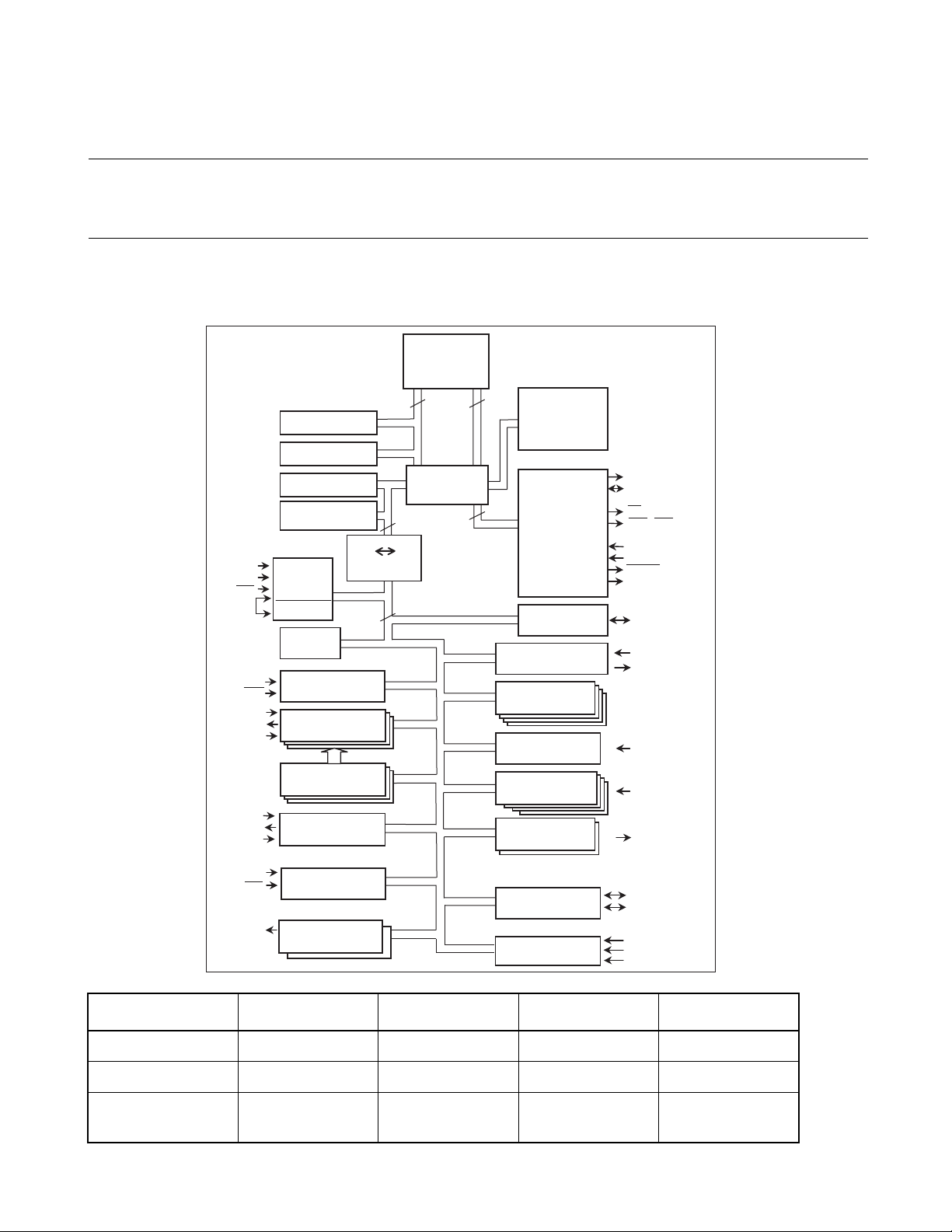

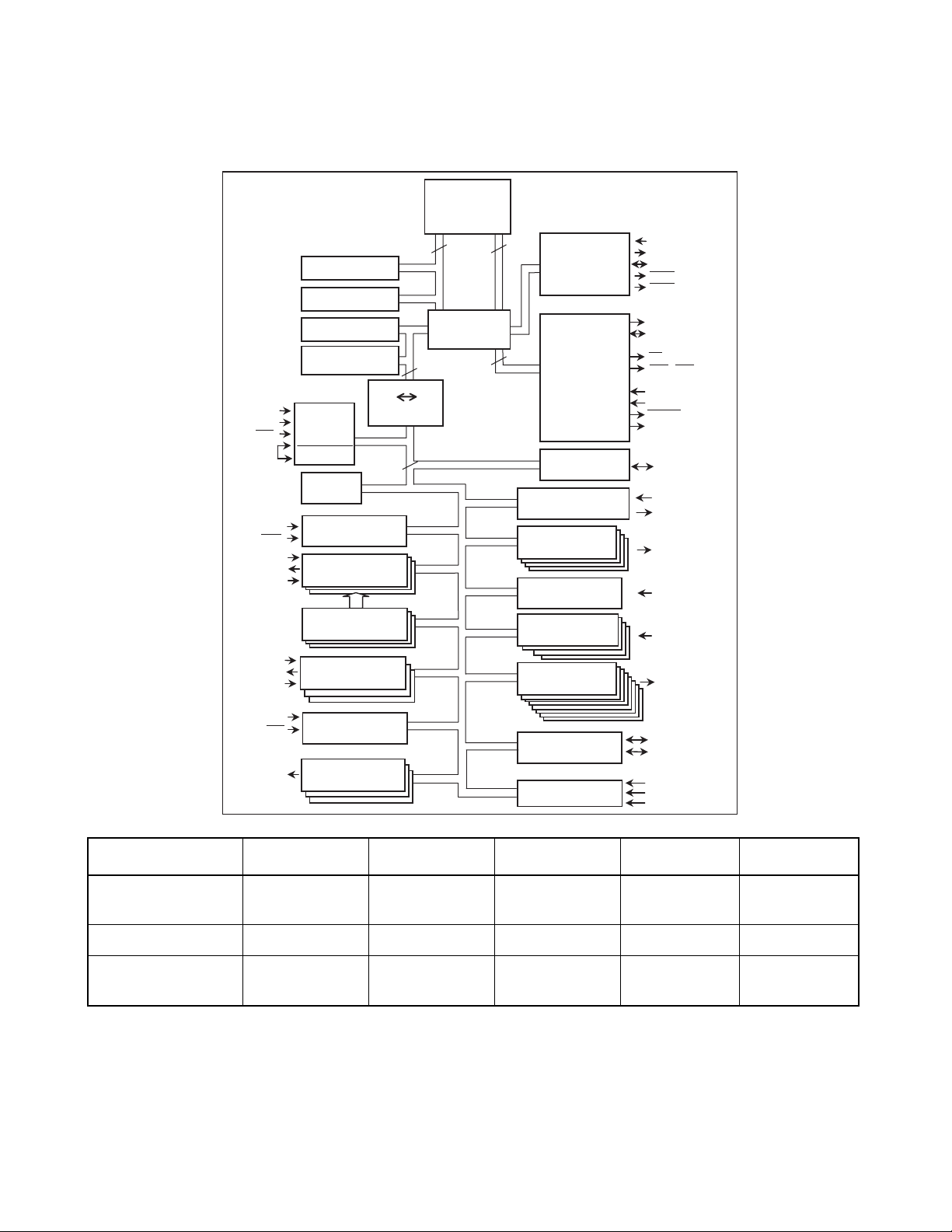

Figure 1.2-1 is a block diagram of the MB91F353A/353A/352A/351A.

Figure 1.2-2 is a block diagram of the MB91355A/354A/F355A/F356B/F357B.

■ MB91F353A/353A/352A/351A Block Diagram

Figure 1.2-1 MB91F353A/353A/352A/351A Block Diagram

FR CPU Core

X0,

MD0 to

X0A,

INT0 to

SI0 to

SO0 to

SCK0 to

SO6,

SCK6,

X1

INIT

X1A

SI6,

(Instruction execution

Clock

2

control

Watch timer

Interrupt

controller

External interrupt

7

(8 channels)

NMI

7

7

7

7

7

SIO (2 channels)

7

Bit search

Stack RAM

ROM/Flash

RAM

enabled)

UART

(4 channels)

U-TIMER

(4 channels)

32

32

32 16

adapter

16

32

Bus converter

32

DMAC

(5 channels)

External

memory

interface

PORT

16-bit PPG

(3 channels)

Reload timer

(4 channels)

Free-running timer

Input capture

(4 channels)

Output compare

(2 channels)

to 00

A20

D31

to 16

RD

WR1, WR0

RDY

BRQ

BGRNT

SYSCLK

PORT

TRG0

PPG0, 2,

FRCK

to 3

IN0

OC0, 2

to 4

4

AN0

to 7

A/D (8 channels)

ATG

AVRH, AVCC

AVSS, AVRL

DA0

DAVC, DAVS

to 1

D/A (2 channels)

2

C (1 channel)

I

Up/down counter

(1 channel)

SDA

SCL

AIN0

BIN0

ZIN0

MB91F353A MB91353A MB91352A MB91351A

ROM/Flash Flash 512K bytes 512K bytes 384K bytes 384K bytes

RAM (Stack) 16K bytes 16K bytes 8K bytes 16K bytes

RAM (Instruction

execution enabled)

8K bytes8K bytes8K bytes8K bytes

7

Page 26

CHAPTER 1 OVERVIEW

■ MB91355A/354A/F355A/F356B/F357B Block Diagram

Figure 1.2-2 MB91355A/354A/F355A/F356B/F357B Block Diagram

FR CPU Core

X0,

MD0 to

INIT

X0A,

INT0 to

SI0 to

SO0 to

SCK0 to

SI5 to

SO5 to

SCK5 to

X1

X1A

NMI

2

15

4

4

4

7

7

7

Clock

control

Watch timer

Bit search

Stack RAM

ROM/Flash 512KB

(F356B only : 256 KB)

RAM

(Instruction execution

enabled)

32 16

adapter

16

Interrupt

controller

External interrupt

(16 channels)

UART (5 channels)

U-TIMER

(5 channels)

SIO (3 channels)

32

32

32

Bus converter

32

DMAC

(5 channels)

16-bit PPG

(6 channels)

Reload timer

(4 channels)

Free-running timer

Input capture

(4 channels)

Output compare

(2 channels)

External

memory

interface

PORT

DREQ0

to 2

DACK0

to 2

EOP/DSTP to 2

IOWR

IORD

A23

to 00

D31

to 16

RD

WR1, WR0

RDY

BRQ

BGRNT

SYSCLK

PORT

TRG0

to 5

to 5

PPG0

TOT0

to 3

FRCK

IN0

to 3

OC0

to 7

to 11

AN0

AVRH, AVCC

AVSS, AVRL

DA0 to 2

DAVC, DAVS

ATG

A/D (12 channels)

D/A (3 channels)

2

I

C (1 channel)

Up/down counter

(1 channel)

SDA

SCL

AIN0, 1

BIN0, 1

ZIN0, 1

MB91F355A MB91F356B MB91F357B MB91355A MB91354A

ROM/Flash Flash

512K bytes

Flash

256K bytes

Flash

512K bytes

512K bytes 384K bytes

RAM (Stack) 16K bytes 16K bytes 16K bytes 16K bytes 8K bytes

RAM (Instruction

execution enabled)

8K bytes 8K bytes 8K bytes 8K bytes 8K bytes

8

Page 27

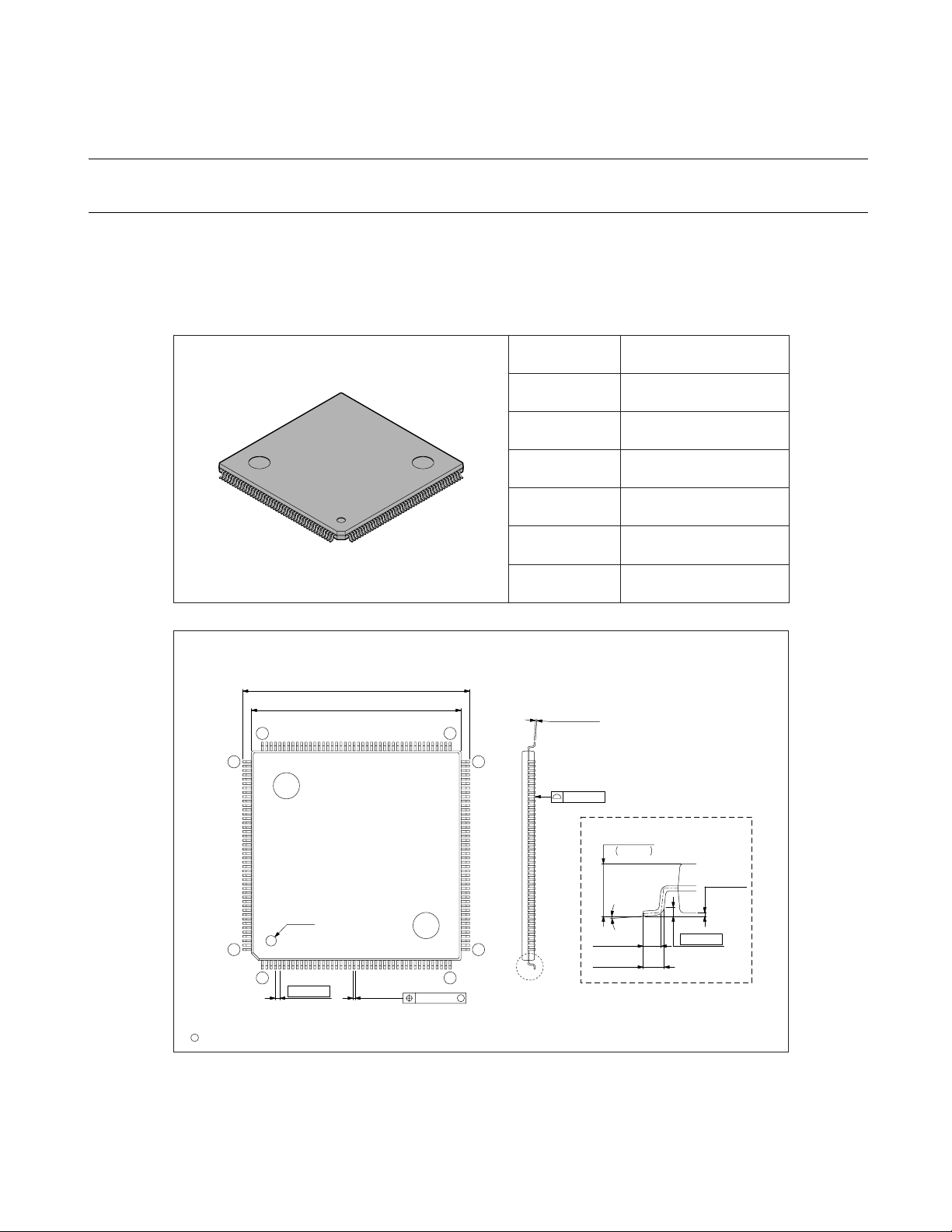

1.3 Package Dimensions

Figure 1.3-1 and show the package dimensions.

■ MB91F355/354A/355A/F356B/F357B Package Dimensions (Reference Diagram)

Consult your customer representative for the formal version.

Figure 1.3-1 MB91F355/354A/355A/F356B/F357B Package Dimensions

176-pin plastic LQFP Lead pitch 0.50 mm

(FPT-176P-M02)

176-pin plastic LQFP

(FPT-176P-M02)

26.00±0.20(1.024±.008)SQ

*

24.00±0.10(.945±.004)SQ

133

Package width ×

package length

24.0 × 24.0 mm

Lead shape Gullwing

Sealing method Plastic mold

Mounting height

1.70 mm MAX

Weight 1.86g

Code

(Reference)

Note 1)* : Values do not include resin protrusion.

Resin protrusion is +0.25(.010)Max(each side).

Note 2) Pins width and pins thickness include plating thickness

Note 3) Pins width do not include tie bar cutting remainder.

0.145±0.055

89132

88

(.006±.002)

0.08(.003)

Details of "A" part

P-LFQFP176-24×24-0.50

+0.20

–0.10

1.50

(Mounting height)

+.008

–.004

.059

INDEX

176

1

LEAD No.

C

2003 FUJITSU LIMITED F176006S-c-4-6

0.50(.020)

0.22±0.05

(.009±.002)

0.08(.003)

0.10±0.10

0˚~8˚

45

44

M

"A"

0.50±0.20

(.020±.008)

0.60±0.15

(.024±.006)

Dimensions in mm (inches).

Note: The values in parentheses are reference values.

(.004±.004)

0.25(.010)

(Stand off)

9

Page 28

CHAPTER 1 OVERVIEW

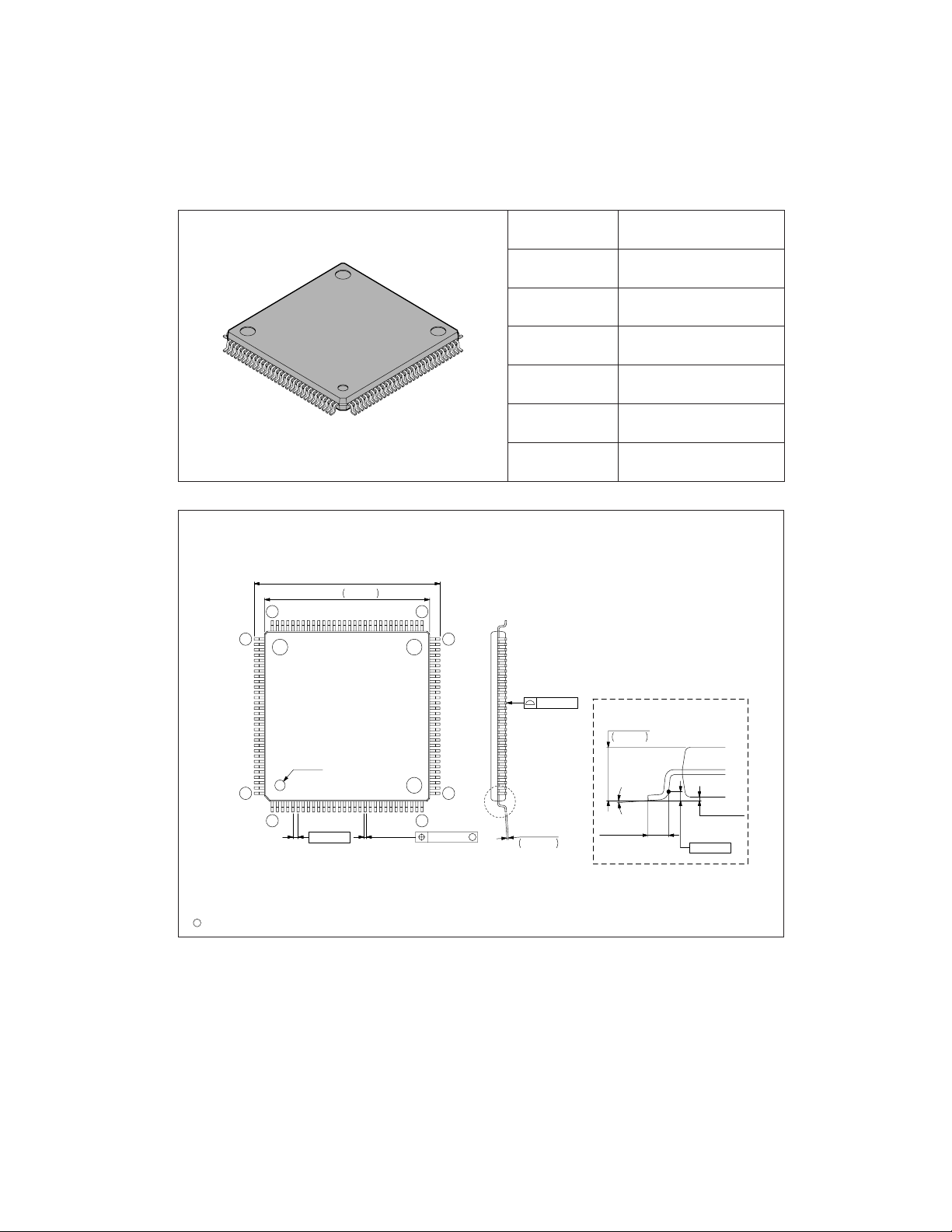

■ MB91F353A/351A/352A/353A Package Dimensions

Figure 1.3-2 MB91F353A/351A/352A/353A Package Dimensions

120-pin plastic LQFP Lead pitch 0.50 mm

(FPT-120P-M21)

120-pin plastic LQFP

(FPT-120P-M21)

18.00±0.20(.709±.008)SQ

+0.40

*

–0.10

16.00

90 61

91

.630 –.004

Package width ×

package length

16.0 × 16.0 mm

Lead shape Gullwing

Sealing method Plastic mold

Mounting height

1.70 mm MAX

Weight 0.88 g

Code

(Reference)

Note 1) * : These dimensions do not include resin protrusion.

Resin protrusion is +0.25(.010) MAX(each side).

Note 2) Pins width and pins thickness include plating thickness.

Note 3) Pins width do not include tie bar cutting remainder.

+.016

SQ

60

0.08(.003)

P-LFQFP120-16×16-0.50

Details of "A" part

+0.20

–0.10

1.50

(Mounting height)

+.008

.059 –.004

10

INDEX

120

1 30

LEAD No.

0.50(.020)

C

2002 FUJITSU LIMITED F120033S-c-4-4

0.22±0.05

(.009±.002)

31

0.08(.003)

0~8

"A"

+0.05

–0.03

M

0.145

.006

+.002

–.001

Dimensions in mm (inches).

Note: The values in parentheses are reference values.

˚

0.60±0.15

(.024±.006)

0.10±0.05

(.004±.002)

(Stand off)

0.25(.010)

Page 29

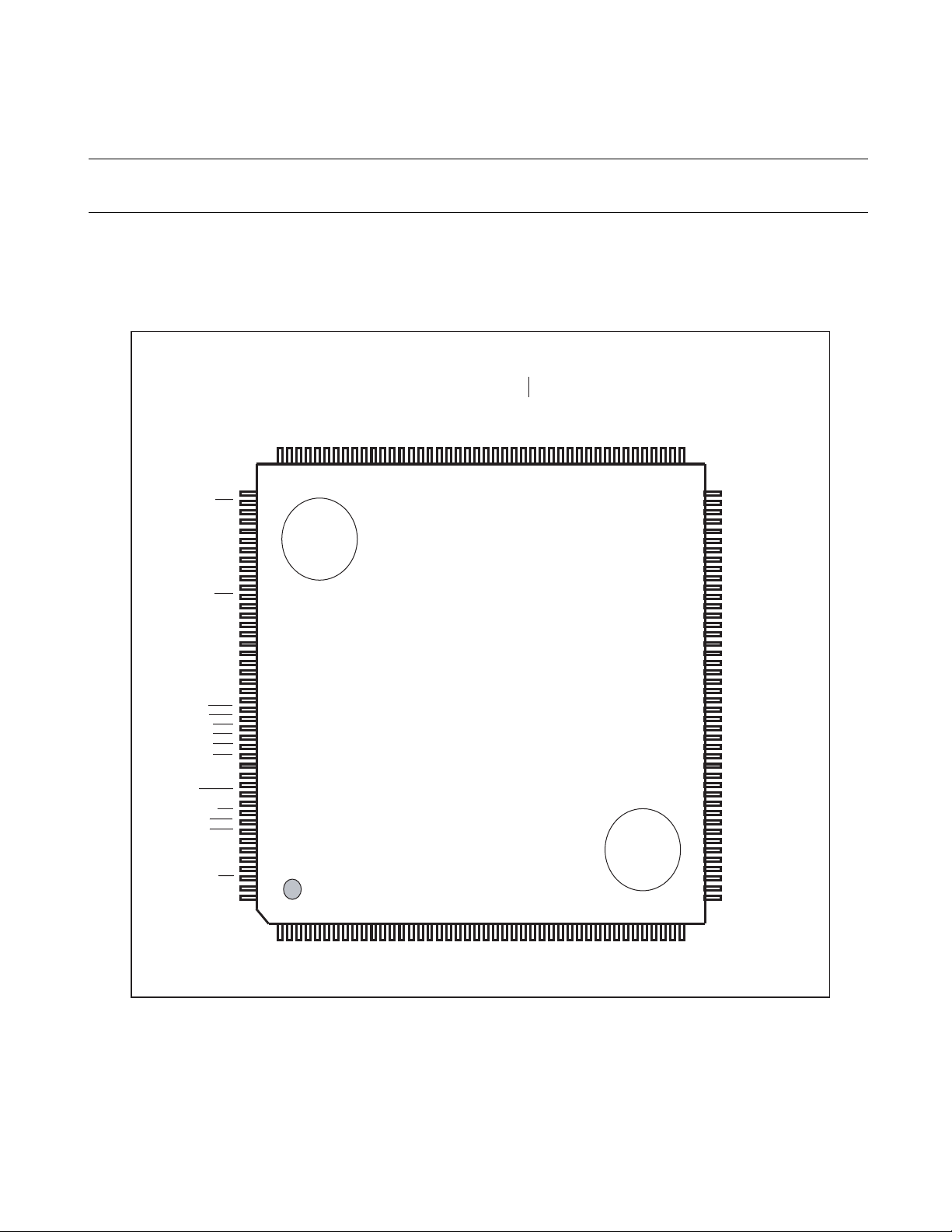

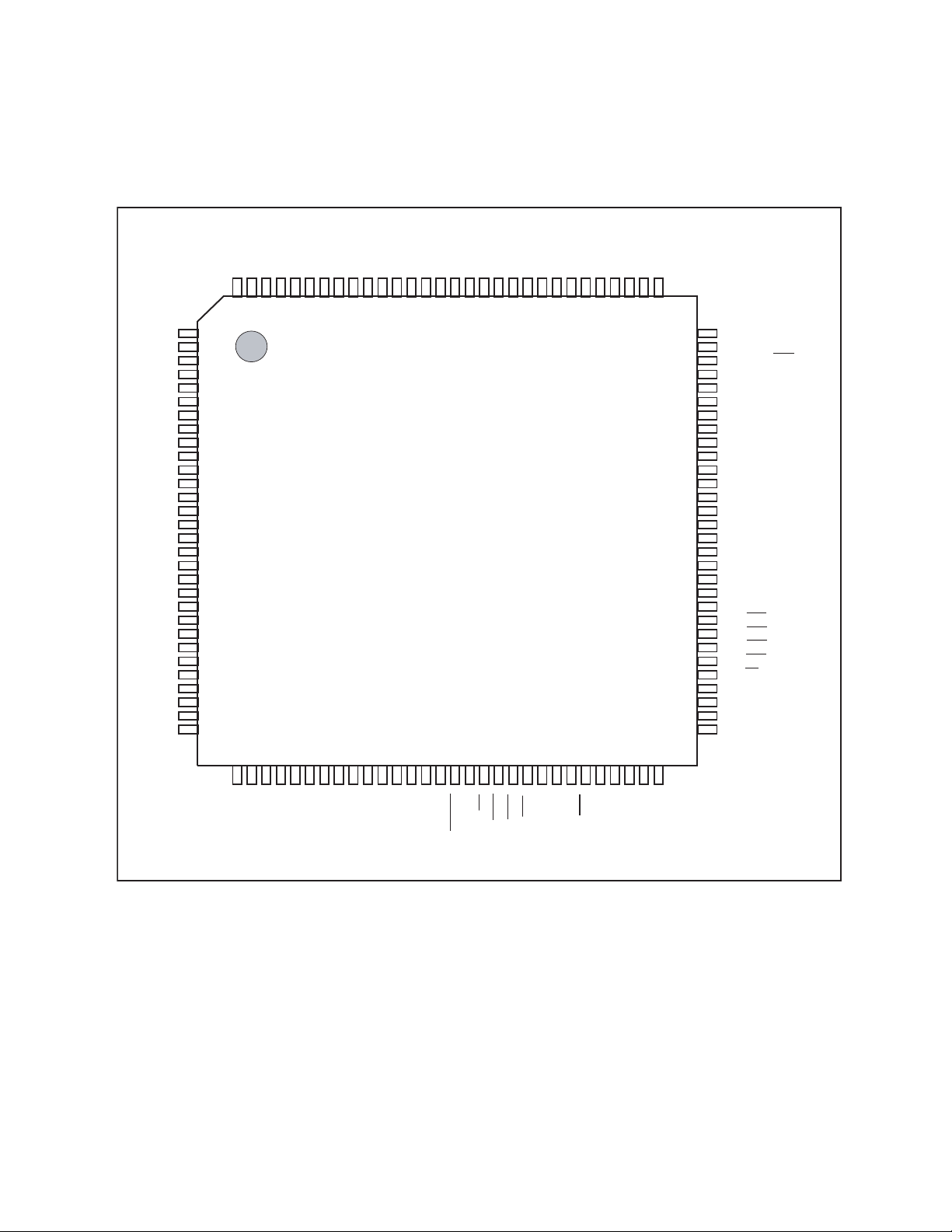

1.4 Pin Layout

88

Figure 1.4-1 , Figure 1.4-2 show the FR60 family pin layouts.

■ Pin Layout of the MB91F355A/354A/355A/F356B/F357B

The installed package is FPT-176P-M02.

Figure 1.4-1 Pin Layout of the MB91F355A/354A/355A/F356B/F357B

PG4/SO5

PG3/SI5

PG2/SCK4

PG1/SO4

PG0/SI4

PH5/SCK3

PH4/SO3

PH3/SI3

PH2/SCK2

PH1/SO2

PH0/SI2

PI5/SCK1

PI4/SO1

PI3/SI1

PI2/SCK0

PI1/SO0

PI0/SI0

VCCVSSPJ7/INT15

PJ6/INT14

PJ5/INT13

PJ4/INT12

PJ3/INT11

PJ2/INT10

PJ1/INT9

PJ0/INT8

PK7/INT7/ATG

PK6/INT6/FRCK

PK5/INT5

PK4/INT4

PK3/INT3

PK2/INT2

PK1/INT1

PK0/INT0

VCCVSSPL1/SCL

PL0/SDA

VSSPM5/SCK7/ZIN1/TRG5

PM4/SO7/BIN1/TRG4

PM3/SI7/AIN1/TRG3

PM2/SCK6/ZIN0/TRG2

PG5/SCK5

NMI

X1A

Vss

X0A

MD2

MD1

MD0

X0

Vcc

X1

INIT

Vss

Vcc

PC0/DREQ2

PC1/DACK2

PC2/DSTP2/DEOP2

PB0/DREQ0

PB1/DACK0

PB2/DSTP0/DEOP0

PB3/DREQ1

PB4/DACK1

PB5/DSTP1/DEOP1

PB6/IOWR

PB7/IORD

A0/CS0

PA1/CS1

PA2/CS2

PA3/CS3

V

V

P80/IN0/RDY

P81/IN1/BGRNT

P82/IN2/BRQ

P83/RD

P84/WR0

P85/IN3/WR1

P90/SYSCLK

P91

P92/MCLK

P93

P94/AS

V

V

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

MB91F355A/MB91355A/MB91354A/

150

151

152

153

154

155

156

157

158

159

160

161

162

SS

CC

163

164

165

166

167

168

169

170

171

172

173

174

175

SS

CC

176

12345678910111213141516171819202122232425262728293031323334353637383940414243

MB91F356B/MB91F357B

TOP VIEW

(LQFP176)

105

104

103

102

101

100

9998979695949392919089

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

PM1/SO6/BIN0/TRG1

PM0/SI6/AIN0/TRG0

PN5/PPG5

PN4/PPG4

PN3/PPG3

PN2/PPG2

PN1/PPG1

PN0/PPG0

CC

V

V

SS

PO7/OC7

PO6/OC6

PO5/OC5

PO4/OC4

PO3/OC3

PO2/OC2

PO1/OC1

PO0/OC0

PP3/TOT3

PP2/TOT2

PP1/TOT1

PP0/TOT0

CC

V

V

SS

AVSS/AVRL

AVRH

AV

CC

AN11

AN10

AN9

AN8

AN7

AN6

AN5

AN4

AN3

AN2

AN1

AN0

DA2

DA1

DA0

DAVC

DAVS

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

P30/D24

P31/D25

P32/D26

P33/D27

P34/D28

P35/D29

P36/D30

SS

CC

V

V

P40/A00

P41/A01

P42/A02

P43/A03

P44/A04

P45/A05

P46/A06

P47/A07

P50/A08

P51/A09

P37/D31

P52/A10

P53/A11

P54/A12

P55/A13

P56/A14

SS

CC

V

V

P57/A15

P60/A16

P62/A18

P61/A17

P63/A19

P64/A20

P65/A21

P66/A22

P67/A23

11

Page 30

CHAPTER 1 OVERVIEW

■ Pin Layout of the MB91F353A/351A/352A/353A

The installed package is FPT-120P-M21.

Figure 1.4-2 Pin Layout of the MB91F353A/351A/352A/353A

/AVRL

SS

AN7

AN6

AN5

AN4

AN3

AN2

AN1

AN0

VSSAV

CC

DAVC

DAVS

DA0

DA1

PH5/SCK3

PH4/SO3

AVRH

AV

PH3/SI3

PH2/SCK2

PH1/SO2

PH0/SI2

PO2/OC2

SSVCC

PO0/OC0

V

PI5/SCK1

PI4/SO1

PI3/SI1

PI2/SCK0

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

P30/D24

P31/D25

P32/D26

P33/D27

P34/D28

P35/D29

P36/D30

P37/D31

P40/A00

V

V

P41/A01

P42/A02

P43/A03

P44/A04

P45/A05

P46/A06

P47/A07

P50/A08

P51/A09

P52/A10

P53/A11

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

SS

19

CC

20

21

22

23

24

25

26

27

28

29

30

31

3233343536

MB91F353A/MB91351A/

MB91352A/MB91353A

TOP VIEW

(LQFP-120)

3738394041424344454647484950515253545556575859

999897969594939291

102

101

100

90

PI1/SO0

89

PI0/SI0

88

PK7/INT7/ATG

87

PK6/INT6/FRCK

86

PK5/INT5

85

PK4/INT4

84

PK3/INT3

83

PK2/INT2

82

PK1/INT1

81

PK0/INT0

80

PM5/SCK7

79

PM4/SO7/TRG4

78

PM3/SI7/TRG3

77

V

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

CC

V

SS

PM2/SCK6/ZIN0/TRG2

PM1/SO6/BIN0/TRG1

PM0/SI6/AIN0/TRG0

PN4/PPG4

PN2/PPG2

PN0/PPG0

PA3/CS3

PA2/CS2

PA1/CS1

PA0/CS0

P94/AS

P93

P91

P90/SYSCLK

X1A

12

P54/A12

P55/A13

P56/A14

P57/A15

P60/A16

P61/A17

SS

SS

PL1/SCL

PL0/SDA

CC

V

V

P80/IN0/RDY

P82/IN2/BRQ

P83/RD

NMI

P84/WR0

P85/IN3/WR1

MD2

MD1

MD0

INIT

V

P62/A18

P63/A19

P64/A20

SS

CC

X1

X0

V

V

X0A

P81/IN1/BGRNT

Page 31

1.5 List of Pin Functions

Table 1.5-1 lists the functions of the pins. Table 1.5-2 lists the power supply and GND

pins. See Figure 1.4-1 , Figure 1.4-2 for the pin layouts.

■ List of Pin Functions

Table 1.5-1 Pin Functions (1 / 13)

Pin number

176 pins 120 pins

1 to 8 1 to 8

9 to 16 9 to 16

19 to 26 17,20 to 26

27 to 34 27 to 34

37 to 41 35 to 39

I/O

Pin name

D16 to D23

P20 to P27 Can be used as a port in external bus 8-bit mode.

D24 to D31

P30 to P37 Can be used as a port in single-chip mode.

A00 to A07

P40 to P47 Can be used as a port in single-chip mode.

A08 to A15

P50 to P57 Can be used as a port in single-chip mode.

A16 to A20

P60 to P64

circuit

type

C

C

C

C

C

Function

Bits 16 to 23 of the external data bus.

Valid only in external bus mode.

Bits 24 to 31 of the external data bus.

Valid only in external bus mode.

Bits 0 to 7 of the external address bus.

Valid only in external bus mode.

Bits 8 to 15 of the external address bus.

Valid only in external bus mode.

Bits 16 to 20 of the external address bus.

Valid only in external bus mode.

Can be used as a port in single-chip mode or when an

external address bus is not used.

A21 to A23

42 to 44 -

P65 to P67

47, 48 106,105 DA0, DA1 - D/A converter output pin

49 - DA2 - D/A converter output pin

50 to 57 113 to 120 AN0 to AN 7 G Analog input pin

58 to 61 - AN8 to AN11 G Analog input pin

TOT0 to

TOT3

67 to 70 -

PP0 to PP3

C

D

Bits 21 to 23 of the external address bus.

Valid only in external bus mode.

Can be used as a port in single-chip mode or when an

external address bus is not used.

[TOT0 to TOT3] are reload timer output ports.

This function is valid when timer output is enabled.

[PP0 to PP3] are general-purpose I/O ports.

This function is valid when the timer output function is

disabled.

13

Page 32

CHAPTER 1 OVERVIEW

Table 1.5-1 Pin Functions (2 / 13)

Pin number

176 pins 120 pins

71 97

72 -

73 98

74 to 78 -

Pin name

OC0

PO0

OC1

PO1

OC2

PO2

OC3 to OC7

PO3 to PO7

PPG0

I/O

circuit

type

D

D

D

D

Function

[OC0] is an output compare output pin.

[PO0] is a general-purpose I/O port.

This function can be used as a port when output compare

output is not used.

[OC1] is an output compare output pin.

[PO1] is a general-purpose I/O port.

This function can be used as a port when output compare

output is not used.

[OC2] is an output compare output pin.

[PO2] is a general-purpose I/O port.

This function can be used as a port when output compare

output is not used.

[OC3 to OC7] are output compare output pins.