Page 1

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface

PCB Design Guideline

November, 2011

The 1.0 edition

Page 2

Page 3

i

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

FUJITSU SEMICONDUCTOR CONFIDENTIAL

Preface

This guideline describes PCB design restrictions related to MB86R12 DDR3 interface signal wiring.

· The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

· The information, such as descriptions of function and application circuit examples, in this document are

presented solely for the purpose of reference to show examples of operations and uses of FUJITSU

SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR

does not warrant proper operation of the device

with respect to use based on such information. When you develop equipment incorporating the device based

on such information, you must assume any responsibility arising out of such use of the information. FUJITSU

SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the

information.

· Any information in this document, including descriptions of function and schematic diagrams, shall not be

construed as license of the use or exercise of any intellectual property right, such as patent right or copyright,

or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU

SEMICONDUCTOR warrant no n -infringement of any third-party's intellectual property right or other right

by using such information. FUJITSU SEMICONDUCTOR assumes no liabilit y for any infringement of the

intellectual property rights or other rights of third parties which would res ult from the use of information

contained herein.

· The products described in this document are designed, developed and manufactured as contemplated for

general use, including without limitation, ordinary industrial use, general office use, personal use, and

household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying

fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public,

and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction

control in nuclear facility, aircraft flig ht control, air traffic control, mass transport control, medical life

support system, missile launch control in weapon sys t em), or (2) for use requiring extremely high r eliability

(i.e., submersible repeater and ar tificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/o r any third party for any

claims or damages arising in connectio n with above-mentioned uses of the products.

· Any semiconductor de vi ces have an inherent chance of failur e. You must protect against injury, damage or

loss from such failures by incorporating safety design measures into your facility and equipment such as

redundancy, fire protection, and p revention of over-current levels and other abnormal operating conditions.

· Exportation/release of any products described in this document may require necessary procedures in

accordance with the

regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US

export control laws.

· The company names and brand names herein are the trademarks or registered trademarks of their respective

owners.

All rights reserved, Copyright FUJITSU SEMICONDUCTOR LIMITED 2011

Page 4

ii

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

FUJITSU SEMICONDUCTOR CONFIDENTIAL

Revision History

Date

Ver.

Contents

2011/11/29

1.0

Newly issued

Page 5

iii

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

FUJITSU SEMICONDUCTOR CONFIDENTIAL

Contents

1. Floor plan ............................................................................................................ 1

2. PCB laminating ................................................................................................... 2

3. DDR3_SDRAM specifications ............................................................................ 3

4. Signal design restrictions (DDR3 interface part) ............................................. 4

4.1. Definition of signal li ne group ................................................................................................................ 4

4.2. General wiring restrictions ...................................................................................................................... 5

4.3. Resistance ................................................................................................................................................ 5

4.4. Terminal resistance/Damping resistance/Wire length ............................................................................. 6

4.5. Wiring gap/Crosstalk ............................................................................................................................... 7

4.6. ZQ/ODT setting ...................................................................................................................................... 8

4.7. Wiring topology ...................................................................................................................................... 9

4.7.1. Wiring topology diagram of MCK_Group ...................................................................................... 9

4.7.2. Wiring topology diagram of MDQSx_Group................................................................................ 10

4.7.3. Wiring topology diagram of MDQx_Group ................................................................................... 11

4.7.4. Wiring topology diagram of MCNTL_Group/MCMD_Group ..................................................... 12

5. Power system design restrictions .................................................................. 13

5.1. Number and capacity of bypass capacitor ............................................................................................. 13

5.2. Pull-out wiring condition ...................................................................................................................... 14

Page 6

Page 7

1

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

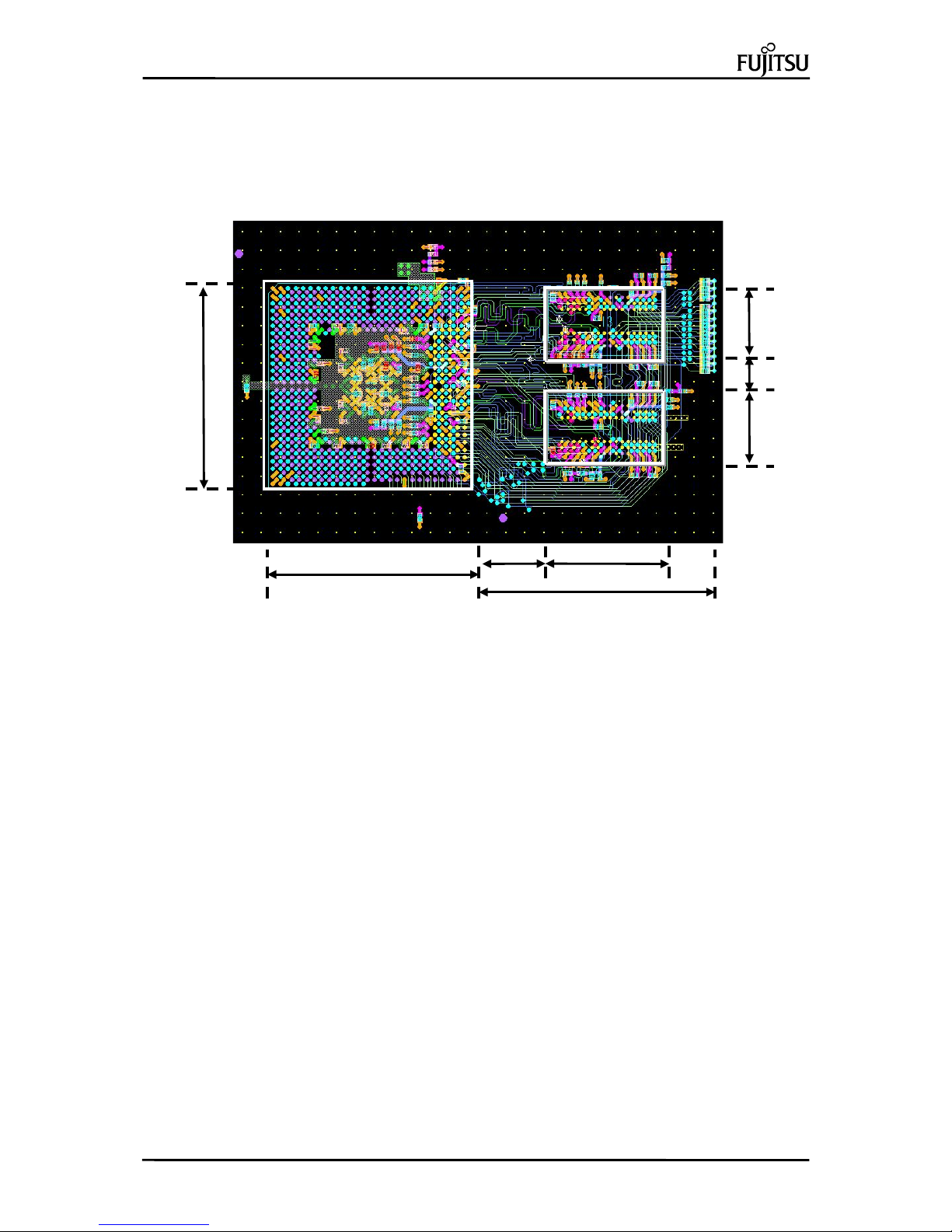

1. Floor plan

Figure 1-1 shows the reference example of t he floor plan of MB86R12 and connected DDR3 SDRAM

devices.

Figure 1-1 Reference example of the floor plan of MB86R12 and DDR3 SDRAM devices

27mm

9mm

27mm

32mm

6mm

9mm

MB86R12

10mm

15.5mm

SDRAM

SDRAM

Page 8

2

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

2. PCB laminating

This chapter shows the recommended laminating cond itions of the PCB.

Figure 2-1 PC B laminating

Specified condition of wiring layer

• L1 and L8 are used as wiring and pull-out wiring layer of CLK .

• L3 and L6 are used as wiring layer of DQS, DQ, and CMD/ADD.

• L2 and L5 are used as power layer.

• L4 and L7 are used as GND layer.

Conductor

thickness

Insulator thickness

L1 43μm SIG. (copper foil: 18mm, plating: 25mm)

L2 35μm Power

L3 35μm SIG.

L4 35μm GND

L5 35μm Power

L6 35μm SIG.

L7 35μm GND

L8 43μm SIG. (copper foil: 18mm, plating: 25mm)

Resist thickness

40μm

100μm

150μm

150μm

100μm

150μm

150μm

100μm

40μm

Insulation material: relative pe rmittivity=4.3 (only the resist part is 3.9)

Classification

Resist thickness

Page 9

3

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

3. DDR3_SDRAM specifications

This chapter shows DDR3_SDRAM that can be used for the DDR3 interface with MB86R12.

If an alternative device fulfills the same requirements, it can also used.

Please note however, that if you use an alternative device, there may be differences concerning I/O quality

which may require your attention. However, all I/O characteristics should be checked as could differ.

Even if you use the device(s) listed below, you must refer to the specifications provided by the DRAM

manufacturer for the confirmation of details (e.g. op e rating temperature conditions etc. ).

Table 3-1 Recommended DDR3_SDRAM

Manufacturer

Product name

IBIS model name

Driver strength

Remarks

Micron

Technology, Inc.

MT41J128M16HA-15E

(2Gb 1333Mbps)

v69a_at.ibs

34Ω

It has already been verified by

the transmission line analysis.

Page 10

4

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4. Signal design restrictions (DDR3 i nterface part)

This chapter describes the signal wiring design restrictions for the DDR3 interface part.

4.1. Definition of signal line group

In order to make t he re quir eme nts for wiri ng co nfig urat ion s de scrib ed further on in t his do cu ment ea sier t o

understand, the DDR3 interface signals are classified into the groups listed belo w.

Table 4-1 DDR3 interface signal grouping

Wiring

preferential

order

Group name Pin name of MB86R12

1

MCK_Group

MCK, MXCK

2

MDQS0_Group

MDQS0, MXDQS0

MDQS1_Group

MDQS1, MXDQS1

MDQS2_Group

MDQS2, MXDQS2

MDQS3_Group

MDQS3, MXDQS3

3

MDQ0_Group

MDQ0~MDQ7, MDM0

MDQ1_Group

MDQ8~MDQ15, MDM1

MDQ2_Group

MDQ16~MDQ23, MDM2

MDQ3_Group

MDQ24~MDQ31, MDM3

4

MCNTL_Group

MCKE, MXCS, MODT

5

MCMD_Group

MA0~MA14, MB A0~MBA2, MXCAS, MXRAS, MXWE

Page 11

5

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.2. General wiring restrictions

This section describes the general wiring restrictions.

• It is recommended that signal wiring be designed to have the following characteristic impedance.

Single impedance: 50Ω±10%

Differential impedance: 100Ω±10%

• Signal wiring on power layer and GND layer should be sufficient width to guarantee the flow of

return current. (Signal l ine should be wired on t he same power group or GND group. It must not cross

over other power and GND groups.)

• Please use parallel wiring for the positive and negative signals of the differential MCK_Group and

MDQSx_Group signals. In addition, also take care that the position and number of layer vias is the

same.

• The follo wing groups mu st wire the same layer respectively, and the number of layer transfer vias

must become the same, too.

MDQS0_Group and MDQ0_Group

MDQS1_Group and MDQ1_Group

MDQS2_Group and MDQ2_Group

MDQS3_Group and MDQ3_Group

There are no restrictions to the number of layer transfer vias for other signals, but use a minimum

possible.

• When using meander wiring layouts for signal delay, crosstalk may occur and the delay value reduced,

therefore ha ving wider spacing between wiri ngs is recommended. The recommended wire spacing is

about five times the wiring width.

Figure 4-1 Meander wiring

The recommended conditions and the simulation waveform which are described further on in this

document are valid under the above conditions.

If your design greatly differs from the above conditions, then please run a simulation on your wiring.

4.3. Resistance

• Resistors described in this guideline should be generally selected from the E12 series.

E12 series: 10, 12, 15, 18, 22, 27, 33, 39, 47, 56, 68, 82

• The following resistance tolerance values should be used (according to the resistance type):

Terminal resistance: under ±5%

Divider resistance for VREF: under ±1%

Bevelled corners used in order to reduce signal reflections

Wire spacing

Page 12

6

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.4. Terminal resistance/Damping resistance/Wire length

Table 4-2 shows the recommended resistance value and wire length for each group.

The wiring topology diagram relevant to this section is shown in "4.7. Wiring topology".

Table 4-2 Resistance value and wire length list

No.

Group name

External terminal

resistance value

(Rt)

Damping

resistance

value

(Rd)

Wire le ngth from

MB86R12 output to

SDRAM input

Internal group approved

wire length variation

1

MCK_Group

39Ω × 2

0.1μF capacitor × 1

(

Refer to "4.7.1.")

N/A

Refer to "4.7.1

."

Meet the conditions of

"4.7.1."

2

MDQSx_Group

N/A

N/A

Refer to "

4.7.2."

Meet the conditions of

"4.7.2."

3

MDQx_Group

N/A

N/A

Refer to "

4.7.3."

Meet the conditions of

"4.7.3."

4

MCNTL_Group

39Ω

N/A

Refer to "

4.7.4."

Meet the conditions of

"

4.7.4."

5

MCMD_Group

39Ω

N/A

Refer to "

4.7.4."

Meet the conditions of

"4.7.4."

Page 13

7

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.5. Wiring gap/Crosstalk

Please keep to the wiring configurations shown below in order to avoid malfunctions and deteriorated

signal integrity due to crosstalk.

(1) The recommended gap for wiring within MDQx_Group and MCMD_Group groups should be over

300µm.

Figure 4-2 Gap f or wiring within MDQx_Group and MCMD_Group

(2) The gap for wiring with other groups should be over 300µm.

Figure 4-3 Gap for wiring of other signal groups

(3) Differential wiring signals of MCK_Group and MDQSx_Group should use a wiring gap of over 500µm

to other signals.

If it is difficult to guarantee a gap above 500µm, separate the wire from other signals using a GND area.

However, please take the consequent decrease of the wiring impedance into consideration.

Figure 4-4 Gap f or wiring between signal in MCK_Group/MDQSx_Group and other signals

MA1

Over 300μm

MA0

Example:

MDQ1

Over 300μm

MDQ0

Example:

MDQ8

Over 300μm

MDQ0

Example:

MA0

Over 300μm

MDQ0

Example:

Other signals

Over 500μm

MDQS0

Example:

Other signals

Over 500μm

MCK

Example:

Page 14

8

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.6. ZQ/ODT setting

Table 4-3 shows the ZQ setting conditions.

Table 4-3 ZQ setting conditions

Group name

Output impedance of MB86R 12 I/O (RON)

ZQ setting of MB86R12

MCK_Group

40Ω

Perform the ZQ calibration, and set it

automatically.

MDQSx_Group

48Ω

MDQx_Group 48Ω

MCNTL_Group 60Ω

MCMD_Group

60Ω

Table 4-4 shows the recommended ODT setting conditions for MDQSx_Group and MDQx_Group signals.

Table 4-4 ODT setting conditions

Operating condition

MB86R12

DDR3_SDRAM

Write to DDR3_SDRAM

Off

60Ω

Read from DDR3_SDRAM 40Ω Off

Page 15

9

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.7. Wiring topology

This section illustrates the recommended wiring topology of each group.

4.7.1. Wiring topology diagram of MCK_Group

Figure 4-5 Wiring topology diagram of MCK_Group

DDR3_

SDRAM

For DQ[15:0]

MB86R12

DDR3_

SDRAM

For DQ[31:16]

L2

(15.5mm

~15.9mm)

No limit

3 9Ω

L1 (24.8mm~25.3mm)

RON: 40[Ω]

- In wiring, the L1/L8 layer is assumption.

- Wire length doesn't contain the length of the via.

Signal name Length of wiring "L1 + L2" [mm]

MCK/MXCK 40.7±1 (Differential and equal-length)

Wire length of each CLK signal

39Ω

VSS

0.1μF

Page 16

10

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.7.2. Wiring topology diagram of MDQSx_Group

Figure 4-6 Wiring topology diagram of MDQSx_Group

Signal name Length of wiring "L1" [mm]

MDQS0/MXDQS0 30.9±3 (Differential and equal-length)

MDQS1/MXDQS1 31.5±3 (Differential and equal-length)

MDQS2/MXDQS2 30.5±3 (Differential and equal-length)

MDQS3/MXDQS3 28.7±3 (Differential and equal-length)

DDR3_

SDRAM

MB86R12

RON: 48[Ω]

ODT: 40[Ω]

Driver strength: 34[Ω]

ODT: 60[Ω]

L1

Wire length of each DQS signal

- In wiring, the L3/L6 layer is assumption.

- Wire length doesn't contain the length of the via.

Page 17

11

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.7.3. Wiring topology diagram of MDQx_Group

Wire length of each DQ signal

Signal

name

Length of wiring "L1" [mm] Signal

name

Length of wiring "L1" [mm]

MDM0 Wire length of MDQS0_Group (Average value): +3.5±2 MDM2 Wire length of MDQS2_Group (Average value): +5.1±2

MDQ0 Wire lengt h of MDQS0_Group (Average value): +2.9±2 MDQ16 Wire length of MDQS2_Group (Average value): +2.0±2

MDQ1 Wire length of MDQS0_Group (Average value): +2.8±2 MDQ17 Wire length of MDQS2_Group (Average value): +0.9±2

MDQ2 Wire lengt h of MDQS0_Group (Average value): +2.2±2 MDQ18 Wire length of MDQS2_Group (Average value): +4.5±2

MDQ3 Wire lengt h of MDQS0_Group (Average value): +1.1±2 MDQ19 Wire length of MDQS2_Group (Average value): +2.7±2

MDQ4 Wire lengt h of MDQS0_Group (Average value): +2.7±2 MDQ20 Wire length of MDQS2_Group (Average value): +4.1±2

MDQ5 Wire lengt h of MDQS0_Group (Average value): +5.0±2 MDQ21 Wire length of MDQS2_Group (Average value): +4.8±2

MDQ6 Wire lengt h of MDQS0_Group (Average value): +3.6±2 MDQ22 Wire length of MDQS2_Group (Average value): +3.3±2

MDQ7 Wire lengt h of MDQS0_Group (Average value): +1.1±2 MDQ23 Wire length of MDQS2_Group (Average value): +2.5±2

MDM1 Wire length of MDQS1_Group (Average value): +2.5±2 MDM3 Wire length of MDQS3_Group (Average value): +4.7±2

MDQ8 Wire lengt h of MDQS1_Group (Average value): +4.4±2 MDQ24 Wire length of MDQS3_Group (Average value): +3.2±2

MDQ9 Wire length of MDQS1_Group (Average value): +3.1±2 MDQ25 Wire length of MDQS3_Group (Average value): +1.3±2

MDQ10 Wire length of MDQS1_Group (Average value): +1.4±2 MDQ26 Wire length of MDQS3_Group (Average value): +5.9±2

MDQ11 Wire length of MDQS1_Group (Average value): +3.3±2 MDQ27 Wire length of MDQS3_Group (Average value): +3.4±2

MDQ12 Wire length of MDQS1_Group (Average value): +2.2±2 MDQ28 Wire length of MDQS3_Group (Average value): +6.6±2

MDQ13 Wire length of MDQS1_Group (Average value): +2.9±2 MDQ29 Wire length of MDQS3_Group (Average value): +3.9±2

MDQ14 Wire length of MDQS1_Group (Average value): +4.2±2 MDQ30 Wire length of MDQS3_Group (Average value): +5.0±2

MDQ15 Wire length of MDQS1_Group (Average value): +2.1±2 MDQ31 Wire length of MDQS3_Group (Average value): +6.4±2

Note 1) The DQ signal can be shuffled in byte.

Figure 4-7 Wiring topology diagram of MDQx_Group

L1

DDR3_

SDRAM

MB86R12

RON: 48[Ω]

ODT: 40[Ω]

Driver strength: 34[Ω]

ODT: 60[Ω]

- In wiring, the L3/L6 layer is assumption.

- Wire length doesn't contain the length of the via.

Page 18

12

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

4.7.4. Wiring topology diagram of MCNTL_Group/MCMD_Group

Figure 4-8 Wiring topology diagram of MCNTL_Group/MCMD_Group

DDR3_

SDRAM

For DQ[15:0]

MB86R12

DDR3_

SDRAM

For DQ[31:16]

0.6mm or less

L1/L8 layer

L1 (31.0mm~44.7mm)

39Ω

RON: 60[Ω]

L2

(17.1mm

~17.4mm)

No limit

Wire length from MB86R12 to

SDRAM at the farthest position

(48.7mm

~62.7mm)

- In wiring, the L3/L6 layer is assumption.

- Wire length doesn't contain the length of the via.

0.6mm or less

VTT=DDRVDE/2

Page 19

13

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

5. Power system design restrictions

This chapter describes the power system design restrictions for the DDR3 interface part of MB86R12.

5.1. Number and capacity of bypass capacitor

Table 5-1 shows recommended number of bypass capacitors for the high frequency noise removal for

which mounting is necessary directly under MB86R12.

Table 5-1 Recommended number of bypass capacitors

Pin name of

MB86R12

Power supply

voltage

Recommended number of

bypass capacitors

Remarks

0.1µF

DDRVDE

1.5V

18

For DDR3 interface

VSS

0V

-

• If capacity is a value close to 0.1µF (0.22µF etc. for instance), the bypass capacitor can be used.

• Place the 0.1µF capacitor as close as possible to the power/GND pins of MB86R12 (refer to "5.2.

Pull-out wiring condition").

• For the 0.1µF capacitor, we recommend the use of ceramic capacitors of under size 1005

(1.0mm × 0.5mm).

In addition, use low ESL (Equivalent Series Inductance) value components where possible in order to

decrease noise.

• Mount a high-capacity capacitor for the low frequency if needed. One 100µF is recommended to be

used for the current variation of 1A only as a guide.

• Verify your board design by simulations and measure me nts if you can not mount capacitors of the

above number.

Page 20

14

FUJITSU SEMICONDUCTOR CONFIDENTIAL

MB86R12 Application Note

DDR3 Interface PCB Design Guideline

5.2. Pull-out wiring condition

This section shows the example of mounting the bypass capacitor for the high frequency noise removal.

Be sure to meet the following pull-out wiring conditions to reduce the inductance value by wiring and to

reduce the noise. If it doesn't meet these conditions, widen the wire width as much as possibl e, and shorte n

the wire length.

Note 1) There is no proble m even if the Chi p on Via method without the pull-out wiring is used.

Figure 5-1 Example of mounting a bypass ca pacitor

Pull

-

out

wiring

Pull

-

out

wiring

Pull-out

wiring

Pull-out

wiring

Power

PAD

GND

PAD

PAD

PAD PAD

PAD PAD PAD

1mm

GND

via

Power

via

Bypass capacitor

(mounted on

Ln layer)

L1 layer MB86R11 PAD

1mm

L1 layer pull-out wiring

L1 ~ Ln layer via

Ln layer pull-out wiring

Bypass capacitor PAD

[Pull-out wiring conditions]

Wire width (W): over 0.3mm

Wire length (L): under 0.71mm

* Average value of all pull-out

wiring

Wire width

(W)

Wire length (L)

Wire length (L)

PAD

L1 layer MB86R12 PAD

Page 21

Loading...

Loading...