Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

MB89202/F202RA Series

HARDWARE MANUAL

CM25-10153-2E

F2MC-8L

8-BIT MICROCONTROLLER

Page 2

Page 3

F2MC-8L

8-BIT MICROCONTROLLER

MB89202/F202RA Series

HARDWARE MANUAL

Be sure to refer to the “Check Sheet” for the latest cautions on development.

“Check Sheet” is seen at the following support page

URL:http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

“Check Sheet” lists the minimal requirement items to be checked to prevent problems beforehand in system development.

FUJITSU LIMITED

Page 4

Page 5

PREFACE

■ Purpose of This Manual and Intended Reader

The MB89202/F202RA series was developed as one of the general-purpose products of the

2

F

MC-8L family, which contains original 8-bit one-chip microcontrollers for use with ASICs

(application specific ICs). The MB89202/F202RA series can be used in a wide range of

products from consumer products to industrial products .

This manual explains the functions and operations of the MB89202/F202RA series for product

development.

2

The F

Note: F

■ Trademark

The company names and brand names herein are the trademarks or registered trademarks of

their respective owners.

■ Structure of This Manual

MC-8L Programming Manual contains details of the programming instructions.

2

MC, an abbreviation for FUJITSU Flexible Microcontroller, is a registered trademark of

FUJITSU LIMITED.

This manual consists of the following 17 chapters and appendix.

CHAPTER 1 OVERVIEW

This chapter describes the features and basic specification of the MB89202/F202RA series.

CHAPTER 2 HANDLING DEVICES

This chapter describes the precautions to be taken when handling the MB89202/F202RA

series.

CHAPTER 3 CPU

This chapter describes the functions and operation of the CPU.

CHAPTER 4 I/O PORTS

This chapter describes the functions and operation of the I/O ports.

CHAPTER 5 TIME-BASE TIMER

This chapter describes the functions an d operation of the time-base timer.

CHAPTER 6 WATCHDOG TIMER

This chapter describes the functions an d operation of the watchdog timer.

CHAPTER 7 8-BIT PWM TIMER

This chapter describes the functions an d operation of the 8-bit PWM timer.

CHAPTER 8 8/16-BIT CAPTURE TIMER/COUNTER

This chapter describes the functions and operation of the 8/16-bit capture timer/coun ter.

CHAPTER 9 12-BIT PPG TIMER

This chapter describes the functions and operation of the 12-bit PPG timer.

i

Page 6

CHAPTER 10 EXTERNAL INTERRUPT CIRCUIT 1 (EDGE)

This chapter describes the functions and operation of external interrupt circuit 1 (edge).

CHAPTER 11 EXTERNAL INTERRUPT CIRCUIT 2 (LEVEL)

This chapter describes the functions and operation of external interrupt circuit 2 (level).

CHAPTER 12 A/D CONVERTER

This chapter describes the functions and operation of the A/D converter.

CHAPTER 13 UART

This chapter describes the functions and operation of UART.

CHAPTER 14 8-BIT SERIAL I/O

This chapter describes the functions and operation of the 8-bit serial I/O.

CHAPTER 15 BUZZER OUTPUT

This chapter describes the functions and ope ration of the buzzer output.

CHAPTER 16 WILD REGISTER FUNCTIONS

This chapter describes the functions and operation of the wild registers.

CHAPTER 17 FLASH MEMORY

This chapter describes the functions and operation of the flash memory.

APPENDIX

This appendix shows the I/O map and instructions list.

ii

Page 7

• The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

• The information, such as descriptions of function and application circuit examples, in this document are presented

solely for the purpose of reference to show examples of operations and uses of FUJITSU semiconductor device;

FUJITSU does not warrant proper operation of the device with respect to use based on such information. When you

develop equipment incorporating the device based on such information, you must assume any responsibility arising out

of such use of the information. FUJITSU assumes no liability for any damages whatsoever arising out of the use of the

information.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be construed

as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right

of FUJITSU or any third party or does FUJITSU warrant non-infringement of any third-party's intellectual property

right or other right by using such information. FUJITSU assumes no liability for any infringement of the intellectual

property rights or other rights of third parties which would result from the use of information contained herein.

• The products described in this document are designed, developed and manufactured as contemplated for general use,

including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not

designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless

extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal

injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air

traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for

use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU will not be liable against you and/or any third party for any claims or damages arising in

connection with above-mentioned uses of the products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from

such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire

protection, and prevention of over-current levels and other abnormal operating conditions.

• Exportation/release of any products described in this document may require necessary procedures in accordance with

the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

• The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Copyright© 2005-2008 FUJITSU LIMITED All rights reserved

iii

Page 8

READING THIS MANUAL

■ Example Notation of Register Names and Pin Names

❍ Example notation of register names and bit names

By writing 1 into the sleep bit of the standby control register (STBC : SLP), ...

Bit name

Prohibit the output of interrupt request of the time-base timer (TBTC : TBIE = 0).

If interrupt enabled (CCR : I = 1) is specified, the interrupt is accepted.

Current state

Bit abbreviation

Register abbreviation

❍ Example notation of multi-use pins

P33/EC pin

Some pins can switch functions according to a setting made by a program or other method.

These pins are called multi-use pins. For multi-use pins, the names corresponding to

functions are listed and divided by /.

Register name

Register abbreviation

Bit abbreviation

Bit abbreviation

Register abbreviation

Setting data

iv

Page 9

CONTENTS

CHAPTER 1 OVERVIEW ................................................................................................... 1

1.1 Features of MB89202/F202RA Series ................................................................................................ 2

1.2 MB89202/F202RA Series Product Lineup .......................................................................................... 4

1.3 Differences between Models ............................ ... ... ... .... ...................................... .... ... ... ... .................. 6

1.4 Block Diagram of MB89202/F202RA Series ....................................................................................... 7

1.5 Pin Assignment ................................................................................................................................... 8

1.6 Package Dimensions ........................................................................................................................ 10

1.7 Pin Functions Description ................................................................................................................. 12

1.8 I/O Circuit Types ............................................................................................................................... 14

CHAPTER 2 HANDLING DEVICES ................................................................................ 17

2.1 Precautions on Handling Devices ..................................................................................................... 18

CHAPTER 3 CPU ............................................................................................................ 21

3.1 Memory Space .............. ... .... ... ... ....................................... ... ... .......................................................... 22

3.1.1 Specific-purpose Areas ............................................................................................................... 24

3.1.2 Location of 16-bit Data on Memory ............................................................................................. 26

3.2 Dedicated Register ........................................................................................................................... 27

3.2.1 Condition Code Register (CCR) .................................................................................................. 29

3.2.2 Register Bank Pointer (RP) ............................................... .... ... ... ................................................ 31

3.3 General-Purpose Registers . ... ... ... .... ... ....................................... ... ... ... ... .......................................... 32

3.4 Interrupts ....................... ............. ............. ............. ............. ............. ............. ............ .......................... 34

3.4.1 Interrupt Level Setting Registers (ILR1 to ILR4) .......................................................................... 36

3.4.2 Steps in the Interrupt Operation .................................................................................................. 37

3.4.3 Multiple Interrupts ........................................................................................................................ 39

3.4.4 Interrupt Processing Time ................. ... ... ....................................... ... .... ... ... ................................ 40

3.4.5 Stack Operation at Interrupt Processing ...................................................................................... 41

3.4.6 Stack Area for Interrupt Processing ............................................................................................. 42

3.5 Reset ................................................................................................................................................ 43

3.5.1 Reset Flag Register (RSFR) ........................................................................................................ 45

3.5.2 External Reset Pin ....................................................................................................................... 47

3.5.3 Reset Operation ................... ... .... ... ... ... ....................................... ... ... .... ...................................... 48

3.5.4 State of Each Pin at Reset .......................... ... ....................................... ... ... ... .... ... ...................... 50

3.6 Clock .................................... .......................................... ................................................................... 51

3.6.1 Clock Generator .......................................................................................................................... 53

3.6.2 Clock Controller ........................................................................................................................... 54

3.6.3 System Clock Control Register (SYCC) ......................................... ... ....................................... .. . 56

3.6.4 Clock Mode .................................................................................................................................. 58

3.6.5 Oscillation Stabilization Wait Time .............................................................................................. 60

3.7 Standby Mode (Low-Power Consumption Mode) ............................................................................. 62

3.7.1 Operations in Standby Mode ....................................................................................................... 63

3.7.2 Sleep Mode ................................................................................................................................. 64

3.7.3 Stop Mode ................................................................................................................................... 65

v

Page 10

3.7.4 Standby Control Register (STBC) ........... .... ...................................... .... ... ... ... ............................. 66

3.7.5 Diagram for State Transition in Standby Mode ............................................................................ 68

3.7.6 Notes on Standby Mode .......................... .... ...................................... .... ... ... ................................ 70

3.8 Memory Access Mode ............... ... .... ... ... ... ... ....................................... ... .... ... ... ................................ 72

CHAPTER 4 I/O PORTS .................................................................................................. 75

4.1 Overview of I/O Ports ........................................................................................................................ 76

4.2 Port 0 ............................... .... ...................................... .... ... ... ............................................................. 78

4.2.1 Registers of Port 0 (PDR0, DDR0, and PUL0) ............................................................................ 80

4.2.2 Operations of Port 0 Functions .................................................................................................... 82

4.3 Port 3 ............................... .... ...................................... .... ... ... ............................................................. 84

4.3.1 Registers of Port 3 (PDR3, DDR3, PUL3) ................................................................................... 86

4.3.2 Operations of Port 3 Functions .................................................................................................... 88

4.4 Port 4 ............................... .... ...................................... .... ... ... ............................................................. 90

4.4.1 Registers of Port 4 (PDR4) .......................................................................................................... 92

4.4.2 Operations of Port 4 Functions .................................................................................................... 93

4.5 Port 5 ............................... .... ...................................... .... ... ... ............................................................. 94

4.5.1 Registers of Port 5 (PDR5, DDR5, PUL5) ................................................................................... 96

4.5.2 Operations of Port 5 Functions .................................................................................................... 98

4.6 Port 6 ............................... .... ...................................... .... ... ... ........................................................... 100

4.6.1 Registers of Port 6 (PDR6, DDR6, PUL6) ................................................................................. 103

4.6.2 Operations of Port 6 Functions .................................................................................................. 105

4.7 Port 7 ............................... .... ...................................... .... ... ... ........................................................... 107

4.7.1 Registers of Port 7 (PDR7, DDR7, PUL7) ................................................................................. 109

4.7.2 Operations of Port 7 Functions .................................................................................................. 111

4.8 Programming Example of I/O Port .................................................................................................. 113

CHAPTER 5 TIME-BASE TIMER .................................................................................. 115

5.1 Overview of Time-base Timer . ... ... .... ... ....................................... ... ... .............................................. 116

5.2 Configuration of Time-base Timer .................................................................................................. 118

5.3 Time-base Timer Control Register (TBTC) ..................................................................................... 119

5.4 Interrupt of Time-base Timer ............ ... ....................................... ... ... ... ... ........................................ 121

5.5 Operations of Time-base Timer Functions ..................................................................................... 122

5.6 Notes on Using Time-base Timer ................................................................................................... 124

5.7 Program Example for Time-base Timer .......................................................................................... 125

CHAPTER 6 WATCHDOG TIMER ................................................................................ 127

6.1 Overview of Watchdog Timer ..................................................................... ... ... ... .... ... .................... 128

6.2 Configuration of Watchdog Timer ................................................................................................... 129

6.3 Watchdog Control Register (WDTC) .............................................................................................. 130

6.4 Operations of Watchdog Timer Functions ...................................................................................... 131

6.5 Notes on Using Watchdog Timer .................................................................................................... 132

6.6 Program Example for Watchdog Timer .......................................................................................... 133

vi

Page 11

CHAPTER 7 8-BIT PWM TIMER ................................................................................... 135

7.1 Overview of 8-bit PWM Timer ......................................................................................................... 136

7.2 Configuration of 8-bit PWM Timer .................................................................................................. 139

7.3 Pin of 8-bit PWM Timer ................................................................................................................... 141

7.4 Registers of 8-bit PWM Timer ......................................................................................................... 142

7.4.1 PWM Control Register (CNTR) ............... .... ... ... ... .... ... ... ....................................... ... ... ... .... ... . ... 143

7.4.2 PWM Compare Register (COMR) ..................................... .... ... ...................................... .... ... ... . 145

7.5 Interrupt of 8-bit PWM Timer .................................. ... .... ... ....................................... ... ... ... .............. 147

7.6 Operations of the Interval Timer Functions ..................................................................................... 148

7.7 Operations of the 8-bit PWM Timer Functions ................................................................................ 150

7.8 States in Each Mode During Operation .......................................................................................... 152

7.9 Notes on Using 8-bit PWM Timer ................................................................................................... 155

7.10 Program Example for PWM Timer .................................................................................................. 157

CHAPTER 8 8/16-BIT CAPTURE TIMER/COUNTER ................................................... 161

8.1 Overview of 8/16-bit Capture Timer/Counter .................................................................................. 162

8.2 Configuration of 8/16-bit Capture Timer/Counter ............................................................................ 166

8.3 Pins of 8/16-bit Capture Timer/Counter .......................................................................................... 168

8.4 Registers of 8/16-bit Capture Timer/Cou n te r ....................................................... .... ... ... ................. 170

8.4.1 Capture Control Register (TCCR) ............................................................................................. 171

8.4.2 Timer 0 Control Register (TCR0) ............................................................................................... 173

8.4.3 Timer 1 Control Register (TCR1) ............................................................................................... 175

8.4.4 Timer Output Control Register (TCR2) ...................................................................................... 177

8.4.5 Timer 0 Data Register (TDR0) ................................................................................................... 178

8.4.6 Timer 1 Data Register (TDR1) ................................................................................................... 180

8.4.7 Capture Data Registers H and L (TCPH and TCPL) ................................................................. 182

8.5 8/16-bit Capture Timer/Counter of Int er ru p ts ........................................................... ... .................... 183

8.6 Explanation of Operations of Interval Time r Fu n c tio ns .. ...................................... .... ... .................... 185

8.7 Operation of Counter Functions . ... ....................................... ... .... ... ...................................... ........... 189

8.8 Functions of Operations of Capture Fun c tio n s .................................... ....................................... ... . 193

8.9 8/16-bit Capture Timer/Counter Operation in Each Mode .............................................................. 197

8.10 Notes on Using 8/16-bit Capture Timer/Counter ............................................................................ 198

8.11 Program Example for 8/16-bit Capture Timer/Counter ................................................................... 200

CHAPTER 9 12-BIT PPG TIMER .................................................................................. 205

9.1 Overview of 12-bit PPG Timer ........................................................................................................ 206

9.2 Configuration of 12-bit PPG Timer Circuit ...................................................................................... 209

9.3 Pin of 12-bit PPG Timer .................................................................................................................. 211

9.4 Registers of 12-bit PPG Timer ................ ... ... .... ...................................... .... ... ... ... ........................... 213

9.4.1 12-bit PPG Control Register 1 (RCR21) .................................................................................... 214

9.4.2 12-bit PPG Control Register 2 (RCR22) .................................................................................... 215

9.4.3 12-bit PPG Control Register 3 (RCR23) .................................................................................... 216

9.4.4 12-bit PPG Control Register 4 (RCR24) .................................................................................... 218

9.5 Operations of 12-bit PPG Timer Functions ..................................................................................... 219

9.6 Notes on Using 12-bit PPG Timer .................................................................................................. 221

9.7 Program Example for 12-bit PPG Timer ......................................................................................... 223

vii

Page 12

CHAPTER 10 EXTERNAL INTERRUPT CIRCUIT 1 (EDGE) ......................................... 225

10.1 Overview of External Interrupt Circuit 1 ............................... ... ....................................... ... ... ........... 226

10.2 Configuration of External Interrupt Circuit 1 .................................................................................... 227

10.3 Pins of External Interrupt Circuit 1 .................................................................................................. 229

10.4 Registers of External Interrupt Circuit 1 .......................................................................................... 231

10.4.1 External Interrupt Control Register 1 (EIC1) .............................................................................. 232

10.4.2 External Interrupt Control Register 2 (EIC2) .............................................................................. 235

10.5 Interrupt of External Interrupt Circuit 1 ................................. ... .... ...................................... .............. 237

10.6 Operations of External Interrupt Circuit 1 ....................................................................................... 239

10.7 Program Example for External Interrupt Circuit 1 ........................................................................... 241

CHAPTER 11 EXTERNAL INTERRUPT CIRCUIT 2 (LEVEL) ....................................... 243

11.1 Overview of External Interrupt Circuit 2 ............................... ... ....................................... ... ... ........... 244

11.2 Configuration of External Interrupt Circuit 2 .................................................................................... 245

11.3 Pins of External Interrupt Circuit 2 .................................................................................................. 246

11.4 Registers of External Interrupt Circuit 2 .......................................................................................... 249

11.4.1 External Interrupt 2 Control Register (EIE2) .............................................................................. 250

11.4.2 External Interrupt 2 Flag Register (EIF2) ................................................................................... 252

11.5 Interrupt of External Interrupt Circuit 2 ................................. ... .... ...................................... .............. 253

11.6 Operations of External Interrupt Circuit 2 ....................................................................................... 254

11.7 Program Example for External Interrupt Circuit 2 ........................................................................... 256

CHAPTER 12 A/D CONVERTER .................................................................................... 259

12.1 Overview of A/D Converter ............................................ ... ... ... .... ...................................... .............. 260

12.2 Configuration of A/D Converter ....................................................................................................... 261

12.3 Pins of A/D Converter ..................................................................................................................... 263

12.4 Registers of A/D Converter ............................................................................................................. 265

12.4.1 A/D Control Register 1 (ADC1) .................................................................................................. 266

12.4.2 A/D Control Register 2 (ADC2) .................................................................................................. 268

12.4.3 A/D Data Register (ADDH and ADDL) ...................................................................................... 270

12.4.4 A/D Enable Register (ADEN) ..................................................................................................... 271

12.5 Interrupt of A/D Converter .......................................... .... ... ... ....................................... ... .. ............... 272

12.6 Operations of A/D Converter Functions .......................................................................................... 273

12.7 Notes on Using A/D Converter ....................................................................................................... 275

12.8 Program Example for A/D Converter .............................................................................................. 277

CHAPTER 13 UART ........................................................................................................ 279

13.1 Overview of UART .......................................................................................................................... 280

13.2 Configuration of UART .................................................................................................................... 284

13.3 Pins of UART .................................................................................................................................. 287

13.4 Registers of UART ........................ .... ...................................... .... ... ... ... ........................................... 289

13.4.1 Serial Mode Control Register (SMC) ......................................................................................... 290

13.4.2 Serial Rate Control Register (SRC) ........................................................................................... 292

13.4.3 Serial Status and Data Register (SSD) ..................................................................................... 294

13.4.4 Serial Input Data Register (SIDR) ............................................................................................. 297

13.4.5 Serial Output Data Register (SODR) ................................................. .... ... ................................. 298

13.4.6 Clock Divider Selection Register (UPC) .................................................................................... 299

viii

Page 13

13.4.7 Serial Switch Register (SSEL) ................................................................................................... 301

13.5 Interrupt of UART ....................................................... .... ... ... ... ........................................................ 303

13.6 Operations of UART Functions ....................................................................................................... 304

13.6.1 Transmission Operations (Operating Mode 0, 1, 2, and 3) ....................................................... 306

13.6.2 Reception Operations (Operating Mode 0, 1, or 3) ................................................................... 307

13.6.3 Reception Operations (Operating Mo d e 2 Only) ............................ ... .... ... ... .............................. 309

13.7 Program Example for UART ........................................................................................................... 311

CHAPTER 14 8-BIT SERIAL I/O ..................................................................................... 313

14.1 Overview of 8-Bit Serial I/O ............................................................................................................ 314

14.2 Configuration of 8-Bit Serial I/O ...................................................................................................... 315

14.3 Pins of 8-Bit Serial I/O .................................................................................................................... 317

14.4 Registers of 8-Bit Serial I/O .............. ...................................... .... ... ... ... ........................................... 319

14.4.1 Serial Mode Register (SMR) ...................................................................................................... 320

14.4.2 Serial Data Register (SDR) ....................................................................................................... 323

14.5 Interrupt of 8-Bit Serial I/O ............................................. ...................................... .... ... .................... 324

14.6 Operations of Serial Output Functions ............................................................................................ 325

14.7 Operations of Serial Input Functions .............................................................................................. 327

14.8 8-Bit Serial I/O Operation in Each Mode ......................................................................................... 329

14.9 Notes on Using 8-Bit Serial I/O ....................................................................................................... 333

14.10 Example of 8-Bit Serial I/O Connection .......................................................................................... 334

14.11 Program Example for 8-Bit Serial I/O ............................................................................................. 336

CHAPTER 15 BUZZER OUTPUT .................................................................................... 339

15.1 Overview of the Buzzer Output ....................................................................................................... 340

15.2 Configuration of the Buzzer Output ................................................................................................ 341

15.3 Pin of the Buzzer Output ................................................................................................................. 342

15.4 Buzzer Register (BZCR) ......................................... ... ....................................... ... .... ... .................... 343

15.5 Program Example for Buzzer Output .............................................................................................. 345

CHAPTER 16 WILD REGISTER FUNCTION .................................................................. 347

16.1 Overview of the Wild Register Function .......................................................................................... 348

16.2 Configuration of the Wild Register Function ................................................................................... 349

16.3 Registers of the Wild Register Function ......................................................................................... 350

16.3.1 Data Setting Registers (WRDR0 and WRDR1) ......................................................................... 351

16.3.2 Higher Address Set Registers (WRARH0 and WRARH1) ......................................................... 352

16.3.3 Lower Address Set Registers (WRARL0 and WRARL1) ........................................................... 353

16.3.4 Address Comparison EN Register (WREN) .............................................................................. 354

16.3.5 Data Test Set Register (WROR) ............................................................................................... 355

16.4 Operations of the Wild Register Functions ..................................................................................... 356

ix

Page 14

CHAPTER 17 FLASH MEMORY ..................................................................................... 357

17.1 Overview of Flash Memory ............................................................................................................. 358

17.2 Flash Memory Control Status Register (FMCS) ............................................................................. 359

17.3 Starting the Flash Memory Automatic Algorithm ............................................................................ 361

17.4 Confirming the Automatic Algorithm Execution State ..................................................................... 362

17.4.1 Data Polling Flag (DQ7) ............................................................................................................ 363

17.4.2 Toggle Bit Flag (DQ6) . .... ... ... ... ....................................... ... .... ... ... .............................................. 364

17.4.3 Timing Limit Exceeded Flag (DQ5) ........................................................................................... 365

17.4.4 Toggle Bit-2 Flag (DQ2) .................... ... ... .... ...................................... .... ... ... ... ........................... 366

17.5 Detailed Explanation of Writing to Erasing Flash Memory .............................................................. 367

17.5.1 Setting The Read/Reset State ................................................................................................... 368

17.5.2 Writing Data ............. ....................................... ... ... .... ... ....................................... ... .................... 369

17.5.3 Erasing All Data (Erasing Chips) ............................................................................................... 371

17.6 Flash Security Feature .................................................................................................................... 372

17.7 Notes on using Flash Memory ........................................................................................................ 373

APPENDIX ......................................................................................................................... 375

APPENDIX A I/O Map .......... ..................................................................................................................... 376

APPENDIX B Overview of the Instructions ............................................................................ .................... 380

B.1 Addressing ..................................................................................................................................... 383

B.2 Special Instructions ........................................................................................................................ 387

B.3 Bit Manipulation Instructions (SETB and CLRB) ............................................................................ 391

B.4 F

B.5 Instruction Map ............................................................................................................................... 399

APPENDIX C Mask Options ...................................................................................................................... 400

APPENDIX D Programming EPROM with Evaluation Chip ........................................................................ 401

APPENDIX E Pin State of the MB89202/F202RA Series .......................................................................... 402

2

MC-8L Instructions List ............................................................................................................... 392

INDEX...................................................................................................................................403

x

Page 15

Main changes in this edition

Page Changes (For details, refer to main body.)

-

6 1.3 Differences between

Models

12 1.7 Pin Functions RST

19 2.1 Precautions on

Handling Devices

24 3.1.1 Specific-purpose

Areas

-

The followings product name is changed.

(MB89202 → MB89202/F202RA)

The followings term is changed.

(source oscillation → oscillation frequency)

"Notes:" is changed.

(The followings sentence is deleted.

• At turning on the power, when the device is used without inputting the external

"

reset, select "reset output supported" and "power-on reset supported" by mask

option.")

The followings package is changed in Table 1.3-1.

(FPT-34P-M03 → FPT-32P-M03)

"● External pull-up for the External Reset Pin (RST

changed.

The summary is changed.

"■ General-purpose Register Area (address: 0100

"■ Vector Table Area (Address: FFC0

pin in Table 1.7-1 is changed.

) of MB89F202/F202RA" is

to 01FFH)" is changed.

H

to FFFFH)" is changed.

H

44 3.5 Reset "● Power-on reset" is changed.

"Note:" is deleted.

56 3.6.3 System Clock

57 Table 3.6-1 is changed.

130 6.3 Watchdog Control

186 8.6 Explanation of

264 12.3 Pins of A/D

308 13.6.2 Reception

Control Register (SYCC)

Register (WDTC)

Operations of Interval

Timer Functions

Converter

Operations (Operating

Mode 0, 1, or 3)

Figure 3.6-5 is changed.

Figure 6.3-1 is changed.

"● 8-bit mode"is changed.

(The followings sentence is deleted.

"The initial value of the square wave output is "L" level. The square wa ve output is

initialized by writing "0" to the TSTR bit of the timer control register (TCR).")

"■ Block Diagram of the Pins Related to the A/D Converter" is changed.

("Note:" is deleted.)

"■ Reception Operations (Operating Mode 0, 1, or 3)" is changed.

("Note:" is changed.)

xi

Page 16

Page Changes (For details, refer to main body.)

310 13.6.3 Reception

Operations (Operating

"■ Reception Operations (Operating Mode 2 Only)" is changed.

("Note:" is changed.)

Mode 2 Only)

358 17.1 Overview of Flash

"■ High voltage supply on RST

Memory

370 17.5.2 Writing Data Figure 17.5-1 is changed.

(F555 → F554)

394

2

MC-8L

B.4 F

Instructions List

Table B.4-2 is changed.

("No.22 DECW A" is changed.)

The vertical lines marked in the left side of the page show the changes.

pin (applicable to MB89F202RA only)" is added.

xii

Page 17

CHAPTER 1

OVERVIEW

This chapter describes the features and basic

specification of the MB89202/F202RA series.

1.1 Features of MB89202/F202RA Series

1.2 MB89202/F202RA Series Product Lineup

1.3 Differences between Models

1.4 Block Diagram of MB89202/F202RA Series

1.5 Pin Assignment

1.6 Package Dimensions

1.7 Pin Functions Description

1.8 I/O Circuit Types

1

Page 18

CHAPTER 1 OVERVIEW

1.1 Features of MB89202/F202RA Series

The MB89202/F202RA series contains general-purpose single-chip microcontroller s that

incorporate a full range of peripheral functions such as A/D converter, UART, PWM

timer, PPG, capture timer/counter and external interrupts as well as a compact

instruction set.

■ Features of MB89202/F202RA Series

● F2MC-8L CPU core

• Instruction set most suitable for controllers

• Multiplication and division instruction

• 16-bit operation

• Branch instruction by bit test

• Bit operation instruction, and others

● 4-system timers

• 8/16-bit capture timer/counter (8-bit capture timer/counter + 8-bit timer or 16-bit capture timer/counter)

• 8-bit PWM timer (also available as an interval timer)

• 21-bit time-base timer

• Watchdog timer

● 10-bit A/D converter

•10-bit A/D × 8 channels

• Activation by 8/16-bit capture timer/counter output is possible.

● Programmable pulse generator (PPG)

• Pulse width and cycle are software selectable (12-bit PPG).

● UART

• 6, 7, or 8 transfer data length

● 8-bit serial I/O

• Available when switched from UART

• LSB first/MSB first selectability

● External interrupts

• External interrupt 1 (edge detection × 3 pins) has three independent inputs and can be used for wake-up

from low-power consumption mode. (The edge detection can be sel ected from rising -edge, falli ng-edge,

and both-edge modes.)

2

Page 19

• External interrupt 2 (level d etection × 8 pins, 1 channel) has eight independent inputs and can be used

for wake-up from low-power consumption mode. (L level detection function is supported.)

● Low-power consumption modes (standby modes)

• Stop mode (The oscillation is stopped so that current cons umption is minimal.)

• Sleep mode (The CPU is stopped so that the current consumption is reduced by one-third of normal

consumption.)

● Up to 26 pins of I/O ports

• General-purpose I/O ports (CMOS): 26 pins (4 of which can be used as N-ch open-drain I/O ports.)

● Wild registers

• 2-byte data at two addresses are available.

• When a specific address or data is used on a wild register, the data in the ROM area is changed.

● 16 KB Flash with read protection

• Once the protection code is written in the specified address, the FLASH content cannot be read by

parallel/serial programmer.

CHAPTER 1 OVERVIEW

3

Page 20

CHAPTER 1 OVERVIEW

1.2 MB89202/F202RA Series Product Lineup

Four MB89202 series models are available. Table 1.2-1 shows the models and Table 1.22 shows the CPU and peripheral functions.

■ MB89202/F202RA Series Models

Table 1.2-1 MB89202/F202RA Series Models

MB89201 MB89F202/F202RA MB89V201

Classification

ROM size

RAM size 512 × 8 bits

Low-power consumption

(standby mode)

Process CMOS

Operating voltage

*1: The minimum operating voltage varies with conditions such as operating frequency, functions, and connecting

ICE.

*2: MBM27C256A is used as the external ROM.

*1

Evaluation product

(for development)

32K × 8 bits

(External EPROM

2.7V to 5.5V 3.5V to 5.5V 2.2V to 5.5V

*2

)

Flash memory product

(read protection)

16K × 8 bits

(Internal Flash)

Sleep mode and stop mode

Mask ROM product

16K × 8 bits

(Internal mask ROM)

4

Page 21

Table 1.2-2 CPU and Peripheral Functions of MB89202/F202RA Series

Item Specification

Number of basic instructions: 136 instructions

Instruction bit length: 8 bits

CPU function

Instruction length: 1 to 3 bytes

Data bit length: 1, 8, or 16 bits

Minimum instruction execution time: 0.32 to 5.1 µs (at 12.5 MHz)

Interrupt processing time: 2.88 to 46.1 µs (at 12.5 MHz)

CHAPTER 1 OVERVIEW

Periphera

l function

Port

21-bit

time-base

General-purpose I/O port: 26 pins (Also serve as peripherals. 4 of which can be used as N-ch

open-drain I/O ports.)

21 bits

Interrupt cycle: 0.66 ms, 2.64 ms, 21 ms, or 335.5 ms with 12.5MHz main clock

timer

Watchdog

Reset occurrence cycle: When the main clock is at 12.5 MHz (minimum 335.5 ms)

timer

8-bit

PWM

timer

8/16-bit

capture

timer/

8-bit interval timer operation (Square wave output is supported. Operating clock cycle:

1 t

INST

, 16 t

INST

, 64 t

, and 8/16-bit capture timer/counter output)

INST

8-bit resolution PWM operation (Conversion cycle:

256 t

INST

, 4096 t

INST

, 16384 t

8-bit capture timer/counter × 1 channel + 8-bit timer or 16-bit capture timer/counter × 1 channel

When timer 0 or a 16-bit counter is operating, event-counting operation by external clock input

and square wave output are supported.

counter

UART Transfer data length: 6, 7, or 8 bits

8-bit serial

I/O

12-bit

8 bits length, LSB first/MSB first selectability

One clock selectable from four operation clocks

(one external shift clock, three internal shift clocks: 2 t

Output frequency: Pulse width and cycle are selectable.

PPG timer

and 256 times 8/16-bit capture timer/counter output)

INST

INST

, 8 t

INST

, 32 t

INST

)

External

interrupt 1

(wake-up)

External

interrupt 2

3 channels (interrupt vector, request flag, and request output enable)

Edge selectability (selectable from rising edge, falling edge, and both-edge modes)

Also available for wake-up from stop or sleep (Edge detection is also available in stop mode.)

8 inputs 1 channel (L level interrupt and input enable are independent.)

Also available for wake-up from stop or sleep (Level detection is also available in stop mode.)

(wake-up)

10-bit A/D

converter

Wild

10-bit resolution × 8 channels

A/D conversion function (Conversion time: 38 t

INST

)

Continuous activation by 8/16-bit capture timer/counter output or time-base timer output.

8-bit × 2

register

Note:

The oscillation is 12.5 MHz unless another condition such as the main clock maximum speed, the clock

cycle value, or conversion time is stated.

5

Page 22

CHAPTER 1 OVERVIEW

1.3 Differences between Models

This section describes the precautions to be taken when selecting a MB89202/F202RA

series model.

■ Precautions when Selecting a Model

Table 1.3-1 Differences between Mod els

Package MB89201 MB89F202/F202RA MB89V202

DIP-32P-M06

FPT-32P-M03

FPT-64P-M03

● Current consumption

• When operated at a low speed, the current consumption of a model with a flash is greater than that of a

model with a mask ROM, though the current consumption in sleep or stop mode is the same.

Notes:

• For details on each package, see Section "1.6 Package Dimensions ".

• For details on current consumption and electrical characteristics of A/D converter, see the electrical

characteristics in the Data Sheet.

6

Page 23

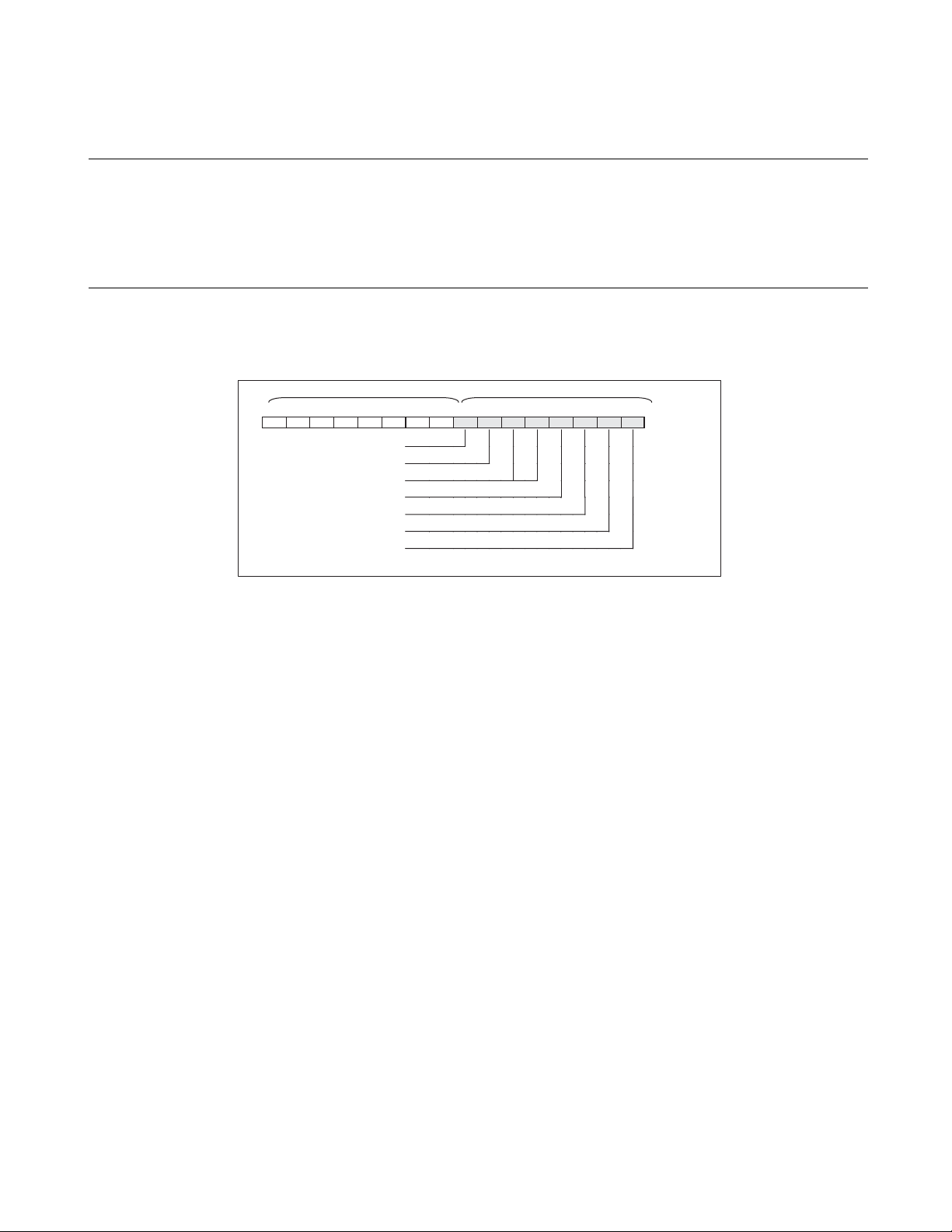

1.4 Block Diagram of MB89202/F202RA Series

Figure 1.4-1 shows the block diagram of the MB89202/F202RA series.

■ Block Diagram of MB89202/F202RA Series

Figure 1.4-1 Block Diagram of MB89202/F202RA Series

CHAPTER 1 OVERVIEW

RST

P60, P61

1

*

P70

to

1

*

P04 / INT24

to

P07 / INT27

P02 / INT22 / AN6,

P03 / INT23 / AN7

P00 / INT20 / AN4,

P01 / INT21 / AN5

*1P40 / AN0

to

1

P43 / AN3

*

P72

X0

X1

Main clock

oscillator

Clock controller

Reset circuit

Port 6

2

CMOS I/O port

3

4

2

2

4

CMOS I/O port

Port 7

CMOS I/O port

8

4

4

External

interrupt2

(wake-up)

10-bit A/D

converter

Port 4 Port 0

CMOS I/O port

(N-ch OD)

Time-base timer

UART prescaler

Internal bus

serial I/O

capture timer/

External interrupt1

CMOS I/O port

8-bit PWM

UART

8-bit

8/16-bit

counter

Serial function switching

3

Port 5Port 3

P50 / PWM

P30 / UCK / SCK

P31 / UO / SO

P32 / UI / SI

P33 / EC

P34 / TO / INT10

P35 / INT11

P36 / INT12

512 or 256 bytes RAM

Other pins

VCC, VSS, C

1

: Large-current drive type

*

2

*

: Check section "3.1 Memory Space"

F2MC - 8 L CPU

16K or 8K bytes ROM

Wild register

2

*

12-bit PPG

P37 / BZ / PPG

2

*

Buzzer output

CMOS I/O port

7

Page 24

CHAPTER 1 OVERVIEW

1.5 Pin Assignment

Figure 1.5-1 and Figure 1.5-2 show the pin assignment of the MB89202/F202RA series.

■ Pin Assignment of DIP-32P-M06

Figure 1.5-1 Pin Assignment of DIP-32P-M06

P04/INT24

P05/INT25

P06/INT26

P07/INT27

P60

P61

RST

X0

X1

SS

V

P37/BZ/PPG

P36/INT12

P35/INT11

P34/TO/INT10

P33/EC

C

* : Large-current drive type

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

CC

P03/INT23/AN7

P02/INT22/AN6

P01/INT21/AN5

P00/INT20/AN4

P43/AN3*

P42/AN2*

P41/AN1*

P40/AN0*

P72*

P71*

P70*

P50/PWM

P30/UCK/SCK

P31/UO/SO

P32/UI/SI

8

Page 25

■

Pin Assignment of FPT-34P-M03

Figure 1.5-2 Pin Assignment of FPT-34P-M03

P04/INT24

P05/INT25

P06/INT26

P07/INT27

P37/BZ/PPG

P36/INT12

P35/INT11

P34/TO/INT10

P33/EC

P60

P61

RST

X0

X1

SS

V

N.C.

CHAPTER 1 OVERVIEW

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

C

17

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

V

P03/INT23/AN7

P02/INT22/AN6

P01/INT21/AN5

P00/INT20/AN4

*

P43/AN3

*

P42/AN2

*

P41/AN1

*

P40/AN0

*

P72

*

P71

*

P70

N.C.

P50/PWM

P30/UCK/SCK

P31/UO/SO

P32/UI/SI

* : Large-current drive type

Note: N.C.: Do not use because it is connected internally.

9

Page 26

CHAPTER 1 OVERVIEW

1.6 Package Dimensions

Two different packages are available for MB89202/F202RA series.

Figure 1.6-1 and Figure 1.6-2 show package dimensions.

■ Package Dimension of DIP-32P-M06

Figure 1.6-1 Package Dimension of DIP-32P-M06

32-pin plastic SH-DIP Lead pitch 1.778 mm

Low space 10.16 mm

(DIP-32P-M06)

32-pin plastic SH-DIP

(DIP-32P-M06)

INDEX

+0.70

4.70

–0.20

+.028

.185

–.008

+0.20

3.30

–0.30

+.008

.130

–.012

1.27(.050)

MAX.

C

2003 FUJITSU LIMITED D32018S-c-1-1

*28.00

1.102

1.778(.070)

Sealing method

Note 1)* : These dimensions do not include resin protrusion.

+0.20

–0.30

+.008

–.012

0.48

.019

Note 2) Pins width and pins thickness include plating thickness.

±0.25

*8.89

(.350±.010)

+0.30

1.02

–0.20

+.012

–.008

.040

0.51(.020)

MIN.

+0.03

0.27

–0.07

+.001

.011

+0.08

–0.12

+.003

–.005

0.25(.010)

M

–.003

Dimensions in mm (inches).

Note: The values in parentheses are reference values

Plastic mold

10.16(.400)

0~15˚

10

Please confirm the latest Package dimension by following URL.

http://edevice.fujitsu.com/fj/DATASHEET/ef-ovpklv.html

Page 27

■

Package Dimension of FPT-34P-M03

Figure 1.6-2 Package Dimension of FPT-34P-M03

34-pin plastic SSOP Lead pitch 0.65 mm

CHAPTER 1 OVERVIEW

(FPT-34P-M03)

34-pin plastic SSOP

(FPT-34P-M03)

1

*

11.00±0.10(.433±.004)

34 18

INDEX

Note 1)*1 : Resin protrusion. (Each side : +0.15 (.006) Max).

Note 2)*2 : These dimensions do not include resin protrusion.

Note 3)Pins width and pins thickness include plating thickness.

Note 4) Pins width do not include tie bar cutting remainder.

2

*

6.10±0.10 8.10±0.20

(.240±.004) (.319±.008)

Package width

package length

Lead shape

Sealing method

×

6.10 × 11.00 mm

Gullwing

Plastic mold

Mounting height 1.45 mm MAX

Code

(Reference)

P-SSOP34-6.1×11-0.65

0.17±0.03

(.007±.001)

Details of "A" part

+0.20

–0.10

1.25

+.008

–.004

.049

0.25(.010)

(Mounting height)

1 17

0.65(.0265)

0.10(.004)0.10(.004)

C

2003 FUJITSU LIMITED F34003S-c-2-3

0.24

.009

+0.08

–0.07

0.10(.004)

+.003

–.003

"A"

M

Please confirm the latest Package dimension by following URL.

http://edevice.fujitsu.com/fj/DATASHEET/ef-ovpklv.html

0~8

˚

0.50±0.20

(.020±.008)

0.60±0.15

(.024±.006)

Dimensions in mm (inches).

Note: The values in parentheses are reference values

0.10±0.10

(.004±.004)

(Stand off)

11

Page 28

CHAPTER 1 OVERVIEW

1.7 Pin Functions Description

Table 1.7-1 describes the I/O pins and functions.

The letters in the circuit type column shown in Table 1.7-1 correspond to the letters in

the Circuit Type column shown in Table 1.8-1 .

■ Pin Functions Description

Table 1.7-1 Pin Functions Description (1/2)

SHDIP32

Pin No.

*1

SSOP34

Pin

name

*2

Circuit

type

Function

8 8 X0 A Pins for connecting the crystal for the main clock. To use an

99X1

5, 6 5, 6 P60,

H / E General-purpose CMOS input port.

external clock, input the signal to X0 and leave X1 open.

P61

77RST

C Reset I/O pin.

This pin serves as an N-ch open-drain reset output and a reset input

as well. The reset is a hysteresis input.

It outputs the "L" signal in response to an internal reset request.

Also, it initializes the internal circuit upon input of the "L" signal.

28, 29 30, 31 P00/

INT20

AN4,

P01/

INT21

G General-purpose CMOS I/O ports.

/

These pins also serve as an input (wake-up input) of external

interrupt 2 or as an 10-bit A/D converter analog input. The input of

external interrupt 2 is a hysteresis input.

/

AN5

30, 31 32, 33 P02/

INT22

AN6,

P03/

INT23

G General-purpose CMOS I/O ports.

/

These pins also serve as an input (wake-up input) of external

interrupt 2 or as an 10-bit A/D converter analog input. The input of

external interrupt 2 is a hysteresis input.

/

AN7

1 to 4 1 to 4 P04/

19 20 P30/

18 19 P31/

12

INT24

to

P07/

INT27

UCK/

SCK

UO/SO

D General-purpose CMOS I/O ports.

These pins also serve as an input (wake-up input) of external

interrupt 2. The input of external interrupt 2 is a hysteresis input.

B General-purpose CMOS I/O ports.

This pin also serves as the clock I/O pin for the UART or 8-bit

serial I/O. The resource is a hysteresis input.

E General-purpose CMOS I/O ports.

This pin also serves as the data output pin for the UART or 8-bit

serial I/O.

Page 29

Table 1.7-1 Pin Functions Description (2/2)

CHAPTER 1 OVERVIEW

SHDIP32

Pin No.

*1

SSOP34

Pin

name

*2

Circuit

type

Function

17 18 P32/UI/SIB General-purpose CMOS I/O ports.

This pin also serves as the data input pin for the UART or 8-b it

serial I/O. The resource is a hysteresis input.

15 15 P33/EC B General-purpose CMOS I/O ports.

This pin also serves as the external clock input pin for the 8/16-bit

capture timer/counter. The resource is a hysteresis input.

14 14 P34/

TO/

INT10

B General-purpose CMOS I/O ports.

This pin also serves as the output pin for the 8/16-bit capture timer/

counter or as the input pin for external interrupt 1. The resource is a

hysteresis input.

13 13 P35/

INT11

B General-purpose CMOS I/O ports.

These pins also serve as the input pin for external interrupt 1. The

resource is a hysteresis input.

12 12 P36/

INT12

B General-purpose CMOS I/O ports.

These pins also serve as the input pin for external interrupt 1. The

resource is a hysteresis input.

11 11 P37/

BZ/

PPG

E General-purpose CMOS I/O ports.

This pin also serves as the buzzer output pin or the 12-bit PPG

output pin.

20 21 P50/

PWM

24 to 27 26 to 29 P40/

AN0 to

P43/

E General-purpose CMOS I/O ports.

This pin also serves as the 8-bit PWM timer output pin.

F General-purpose CMOS I/O ports.

These pins can also be used as N-ch open-drain ports.

These pins also serve as 10-bit A/D converter analog input pins.

AN3

21 to 23 23 to 25 P70 to

E General-purpose CMOS I/O ports.

P72

32 34 V

10 10 V

CC

SS

-- Power supply pin

-- Power (GND) pin

16 17 C -- MB89F202/F202RA:

Capacitance pin for regulating the power supply.

Connect an external ceramic capacitor of about 0.1µF.

MB89202:

This pin is not internally connected. It is unnecessary to connect

a capacitor.

-- 16, 22 N.C. -- Internally connected pins

Be sure to leave it open.

*1 : DIP-32P-M06

*2 : FPT-34P-M03

13

Page 30

CHAPTER 1 OVERVIEW

1.8 I/O Circuit Types

Table 1.8-1 describes the I/O circuit types.

The letters in the circuit column shown in Table 1.8-1 correspond to the letters in the

circuit type column shown in Table 1.7-1 .

■ I/O Circuit Types

Table 1.8-1 I/O Circuit Types (1/2)

Types Circuit Remarks

A At an oscillation feedback resistance of

approximately 500 kΩ

X1

X0

Standby control signal

B CMOS output

Hysteresis input

Pull-up resistor optional

Input enable

P-ch

P-ch

N-ch

Port / Resource

C At an output pull-up resistor (P-ch) of

P-ch with pull-up, not

available for

MB89F202/F202RA

approximately 50 kΩ/5.0 V

(not available for MB89F202/F202RA)

N-ch open-drain reset output

Hysteresis input

High voltage input tolerable in MB90F202RA

N-ch

Reset

14

Page 31

Table 1.8-1 I/O Circuit Types (2/2)

Types Circuit Remarks

D CMOS output

P-ch

P-ch

N-ch

CMOS input

Hysteresis input (Resource input)

Pull-up resistor optional

CHAPTER 1 OVERVIEW

Input enable

Input enable

Port

Resource

E CMOS output

CMOS input

P-ch

Pull-up resistor optional

P70 to P72 are large current drive type

P-ch

N-ch

Input enable

Port

F CMOS output

CMOS input

P-ch

Open-drain control

Analog input

N-ch open-drain output available

P40 to P43 are large current drive type

Input enable

N-ch

Analog input

Port

A/D enable

G CMOS output

P-ch

CMOS input

Hysteresis input (Resource input)

Analog input

P-ch

N-ch

Input enable

Input enable

Analog input

A/D enable

Port

Resource

HCMOS input

Input enable

Port

15

Page 32

CHAPTER 1 OVERVIEW

16

Page 33

CHAPTER 2

HANDLING DEVICES

This chapter describes the precautions to be taken when

handling general-purpose one-chip microcontrollers.

2.1 Precautions on Handling Devices

17

Page 34

CHAPTER 2 HANDLING DEVICES

2.1 Precautions on Handling Devices

This section describes the precautions to be taken when handling the power supply

voltage, pins, and other device items.

■ Precautions on Handling Devices

● Ensure that the voltage does not exceed the maximum ratings. (Preventing latch-up)

A latch-up may occur if a voltage higher than Vcc or lower than Vss is applied to input or output pins other

than middle- or high-level resistant pins, or if voltage exceeding the rated value is applied between Vcc and

Vss.

When a latch-up occurs, the supply current increases rapidly, occasionally resulting in overheating.

Therefore, ensure that the voltage does not exceed the maximum ratings when using the microcontrollers.

● Stabilize the supply voltage as much as possible

Although the specified Vcc supply voltage operating range is assured, a sudden change in the supply

voltage within the specified range may result in a malfunction.

The following stabilization guidelines are recommended: The Vcc ripple (P-P value) at the supply

frequency (50 Hz to 60 Hz) should be less than 10% o f the typical Vcc value, and the transient fluctuation

rate should be less than 0.1 V/ms at the time of momentary fluctuation when switching the power supply.

● Handling unused input pins

Leaving unused input pins open may result in a malfunction or equipment damage due to a latch-up.

Therefore, set these pins to pull-up or pull-down via resistors of 2 kΩ or hi gher.

● Handling the N.C. pins

Ensure that the N.C. (internally connected) pins are opened before using.

● Precautions on using an external clock

When an external clock is used, the oscillation stabilization wait time is also provided for power-on reset

and stop mode release.

● Wild register function

Because wild registers cannot be debugged on MB89V201, check operation on an actual MB89F202/

F202RA.

18

● Program execution on RAM

When MB89V201 is used, a program cannot be executed on RAM.

Page 35

CHAPTER 2 HANDLING DEVICES

● Note to Noise in the External Reset Pin (RST

If the reset pulse applied to the external reset pin (RST

malfunctions. Use caution so that the reset pulse less than the specifications will not be f ed to the external

reset pin (RST

● External pull-up for the External Reset Pin (RST

Internal pull-up control for RST

control in MB89F202/F202RA, an external pull-up (recommend 100 kΩ) for RST

For MB89F202RA only, high voltage must be applied to RST

typical high voltage is 10 V.

● Step-down circuit stabilization time

The MB89202/F202RA series consists of the products listed in Table 2.1-1 "Pin Processing for the

Products with and without a Step-down Circuit". The operation characteristic depends on whether a product

contains a step-down circuit.

Table 2.1-1 Pin Processing for the Products with and without a Step-down Circuit

Product name Operating voltage Step-down circuit

).

is not available for MB89F202/F202RA. To ensure proper external reset

MB89V201 2.7 V to 5.5 V Not contained

)

) does not meet the specifications, it may cause

) of MB89F202/F202RA

pin must be required.

during flash memory program / erase. The

MB89202 2.2 V to 5.5 V Not contained

MB89F202/F202RA 3.5 V to 5.5 V Contained

These products use the same internal resources. However, the operation sequence after power-on reset

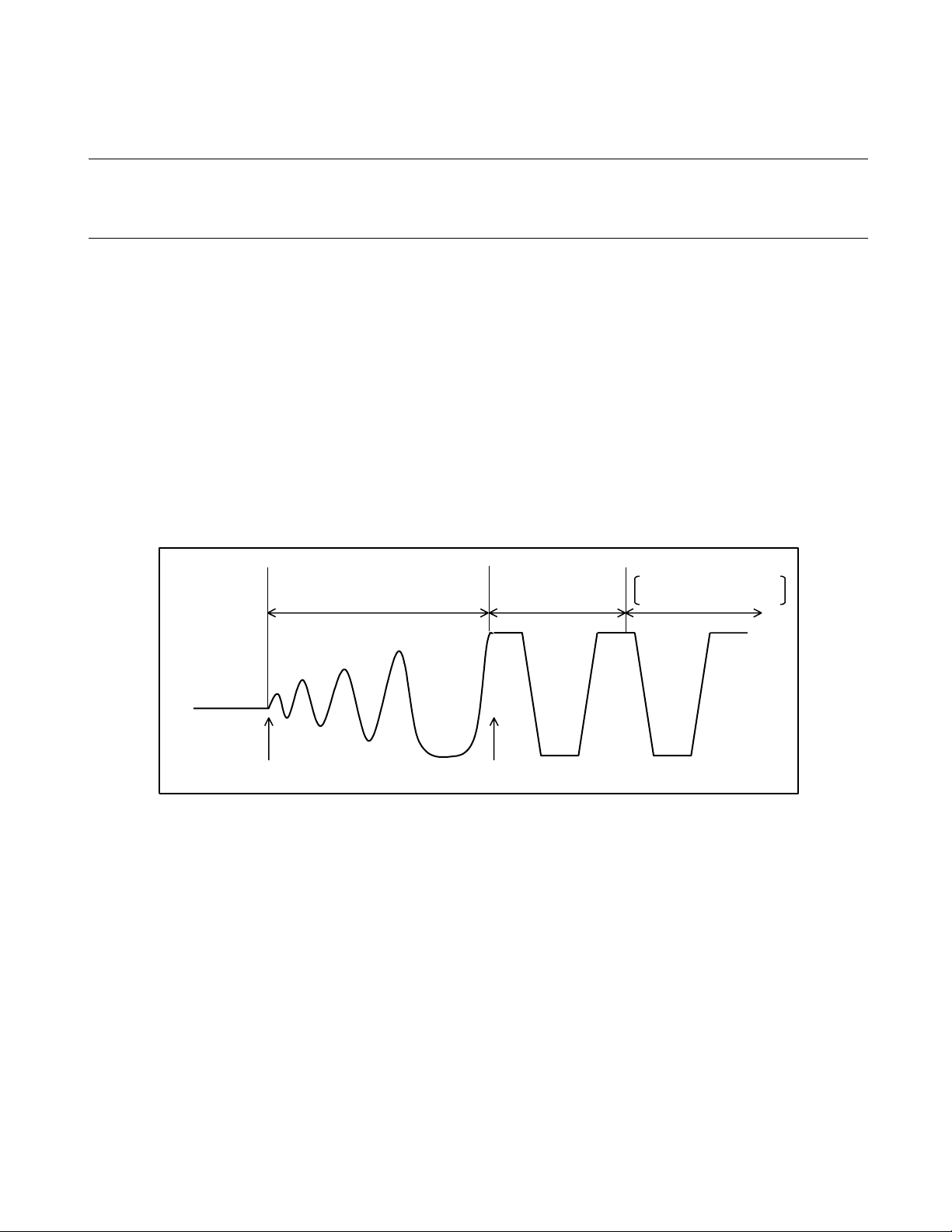

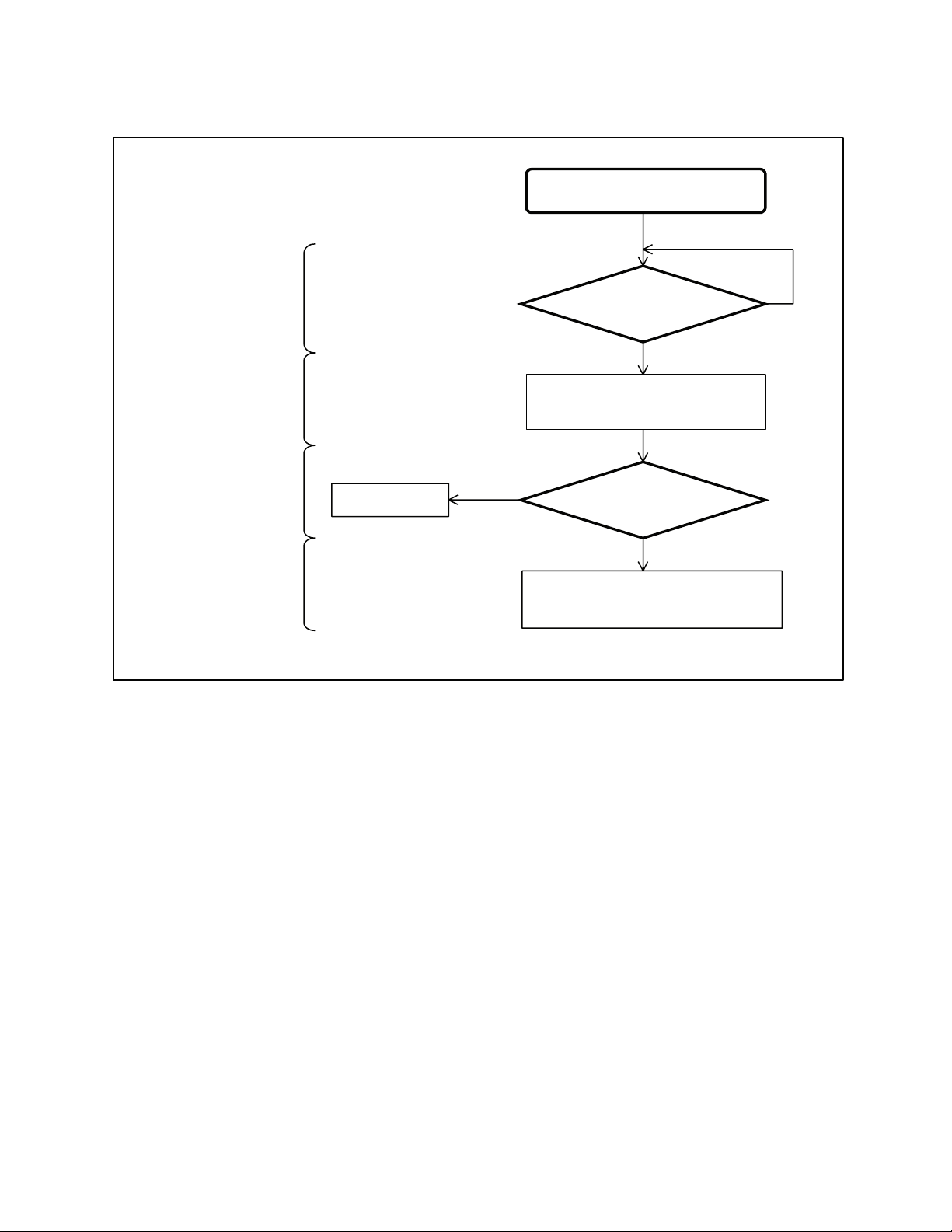

depends on whether a product contains a step-down circuit. Figure 2.1-1 shows the sequence of operations

after the power-on reset for each model.

19

Page 36

CHAPTER 2 HANDLING DEVICES

Figure 2.1-1 Operation Sequences after Power-on Reset between Product Types

Power supply (VCC)

CPU operation of

product with a step-down

circuit (MB89F202/F202RA)

CPU operation of

product without a

step-down circuit

(MB89202 and MB89V201)

F

: Main oscillation frequency

CH

As shown in Figure 2.1-1 , the start of CPU operation of a product with a step-down circuit is slower th an

that of the product without a step-down circuit. This is because time is required for the step-down circuit to

stabilize prior to normal operation of the step-down circuit.

Step-down circuit stabilization time (217/FCH) +

Oscillation stabilization wait time (2

Oscillation stabilization

wait time (2

18

/FCH)

Start of CPU operation of

product without a step-down

circuit (reset vector)

18

/FCH)

Start of the CPU operation of

product with a step-down

circuit (reset vector)

20

Page 37

CHAPTER 3

CPU

This chapter describes the functions and operations of

the CPU.

3.1 Memory Space

3.2 Dedicated Register

3.3 General-Purpose Registers

3.4 Interrupts

3.5 Reset

3.6 Clock

3.7 Standby Mode (Low-Power Consumption Mode)

3.8 Memory Access Mode

21

Page 38

CHAPTER 3 CPU

3.1 Memory Space

The MB89202/F202RA series has 64-KB memory space that consists of the I/O area,

RAM area, ROM area, and external area. P a rt of the memory space is applied for specific

use such as general-purpose registers or a vector table.

■ Configuration of Memory Space

● I/O area (address: 0000H to 007FH)

The control registers and data registers for built-in peripheral functions are assigned.

The I/O area is assigned as part of the memory space, thus access to the I/O area can be obtained in the

same manner as access to memory. Also, direct addressing provides high-speed access.

● RAM area

Static RAM is equipped as the internal data area.

The size of internal RAM depends on the model.

Direct addressing allows high-speed access to an area from 80

range of the area.)

100

H

If a reset occurs while data is being written into RAM, the data being written cannot be guaranteed.

● ROM area

ROM is equipped as the internal program area.

The size of internal ROM depends on the model.

FFC0

to 1FFH can be used as the general-purpose register area.

to FFFFH are usable as a vector table or another feature.

H

to FFH. (Some models restrict the usable

H

22

Page 39

■

Memory Map

0000

Figure 3.1-1 Memory Map

MB89V201 MB89202 MB89F202/F202RA

H

0000H

0000H

CHAPTER 3 CPU

0080H

0100H

0200H

0280H

8000H

FFFFH

I/O

0080H

RAM 512 bytes

0100H

Register

0200H

0280H

Not available Not available

C000H

External EPROM

32 KB

FFFFH

I/O I/O

RAM 512 bytes RAM 512 bytes

Register

ROM 16 KB Flash 16 KB

0080H

0100H

Register

0200H

0280H

Not available

C000H

FFFFH

23

Page 40

CHAPTER 3 CPU

3.1.1 Specific-purpose Areas

In addition to the I/O area, the general-purpose register area and vector table area are

available as areas for specific applications.

■ General-purpose Register Area (Address: 0100

• This area is used for 8-bit arithmetic operations and transfer. Supplementary registers are provided.

• Since this area is allocated to a part of the RAM area, it can also be used as normal RAM.

• When this area is used as a general-purpose register, it can be accessed faster using shorter instructions

by general-purpose register addressing.

For details, see Section "3.2.2 Register Bank Pointer (RP) " and Section "3.3 General-Purpose Registers ".

■

Vector Table Area (Address: FFC0H to FFFFH)

• This area is used as vector tables of the vector call instructions, interrupts, and reset.

• This area is allocated to the highest ranges of the ROM area, and the start address of the corresponding

processing routine is set to the address of each vector table.

Table 3.1-1 provides the reference addresses in the vector table that correspond to the vector instruct ions,

interrupts, and reset.

For details, see Section "3.4 Interrupts ", Section "3.5 Reset ", and "CALLV #vct" in APPENDIX "B.2

Special Instructions ".

Table 3.1-1 Vector Table (1/2)

Address in the vector table

Vector call instruction

Upper digits Lower digits

to 01FFH)

H

24

CALLV #0

CALLV #1

CALLV #2

CALLV #3

CALLV #4

CALLV #5

FFC0

FFC2

FFC4

FFC6

FFC8

FFCA

CALLV #6 FFCC

CALLV #7

FFCE

IRQF FFDC

IRQE FFDE

IRQD FFE0

IRQC FFE2

H

H

H

H

H

H

H

H

H

H

H

H

FFC1

FFC3

FFC5

FFC7

FFC9

FFCB

FFCD

FFCF

FFDD

FFDF

FFE1

FFE3

H

H

H

H

H

H

H

H

H

H

H

H

Page 41

Table 3.1-1 Vector Table (2/2)

Vector call instruction

CHAPTER 3 CPU

Address in the vector table

Upper digits Lower digits

IRQB FFE4

IRQA FFE6

IRQ9 FFE8

IRQ8 FFEA

IRQ7 FFEC

IRQ6 FFEE

IRQ5 FFF0

IRQ4 FFF2

IRQ3 FFF4

IRQ2 FFF6

IRQ1 FFF8

IRQ0 FFFA

H

H

H

H

H

H

H

H

H

H

H

H

FFE5

FFE7

FFE9

FFEB

FFED

FFEF

FFF1

FFF3

FFF5

FFF7

FFF9

FFFB

Mode data - * FFFD

Reset vector FFFE

H

FFFF

H

H

H

H

H

H

H

H

H

H

H

H

H

H

*: For MB89202 / MB89V201, FFFCH is prohibited. (Use "FFH".)

For MB89F202/F202RA, write "01

otherwise write "FF

".

H

" to FFFCH to activate read protection,

H

25

Page 42

CHAPTER 3 CPU

3.1.2 Location of 16-bit Data on Memory

Upper digits of 16-bit data and stack data are stored in lower addresses on memory.

■ 16-bit Data Storage State on RAM

When 16-bit data is written into RAM, the upper byte of the data is stored with a lower address and the

lower byte of the data is stored with the next address. 16-bit data is read in the same manner.

Figure 3.1-2 shows the location of 16-bit data on RAM.

Figure 3.1-2 Location of 16-bit Data on RAM

Before

written

1234

H

A

■

16-bit Operand Storage State

When 16 bits are specified for operands in instructions, upper bytes are also stored in addresses close to

operation codes (instructions) and lower bytes are stored in the following addresses.

Operands that indicate memory addresses and 16-bit immediate data are handled in the same manner as

stated above.

Figure 3.1-3 shows the locations of 16-bit data in instructions.

Figure 3.1-3 Location of 16-bit Data in Instructions

[Example] MOV A, 5678H

Memory

MOV W A, #1234H

XXX0HXX XX

XXX2

XXX5

XXX8

0080

H

0081

H

0082

H

0083

H

H

60

H

E4 12 34

H

XX

MOVW 0081H, A

Processed through assembler

.

.

.

78

56

.

.

.

After

written

A

1234

H

; Extend address

; 16-bit immediate data

; Extend address

; 16-bit immediate data

Memory

H

12

34

H

0080

0081

0082

0083

H

H

H

H

■

16-bit Data Storage State in Stack

The upper byte of data for a 16-bit register put in the stack due to an interrupt is also stored with a lower

address.

26

Page 43

CHAPTER 3 CPU

3.2 Dedicated Register

The dedicated register in the CPU consists of a program counter (PC), two arithmetic

operation registers (A and T), three address pointers (IX, EP, and SP), and program

status (PS) register. The size of each register is 16 bits.