Page 1

5

4

3

2

1

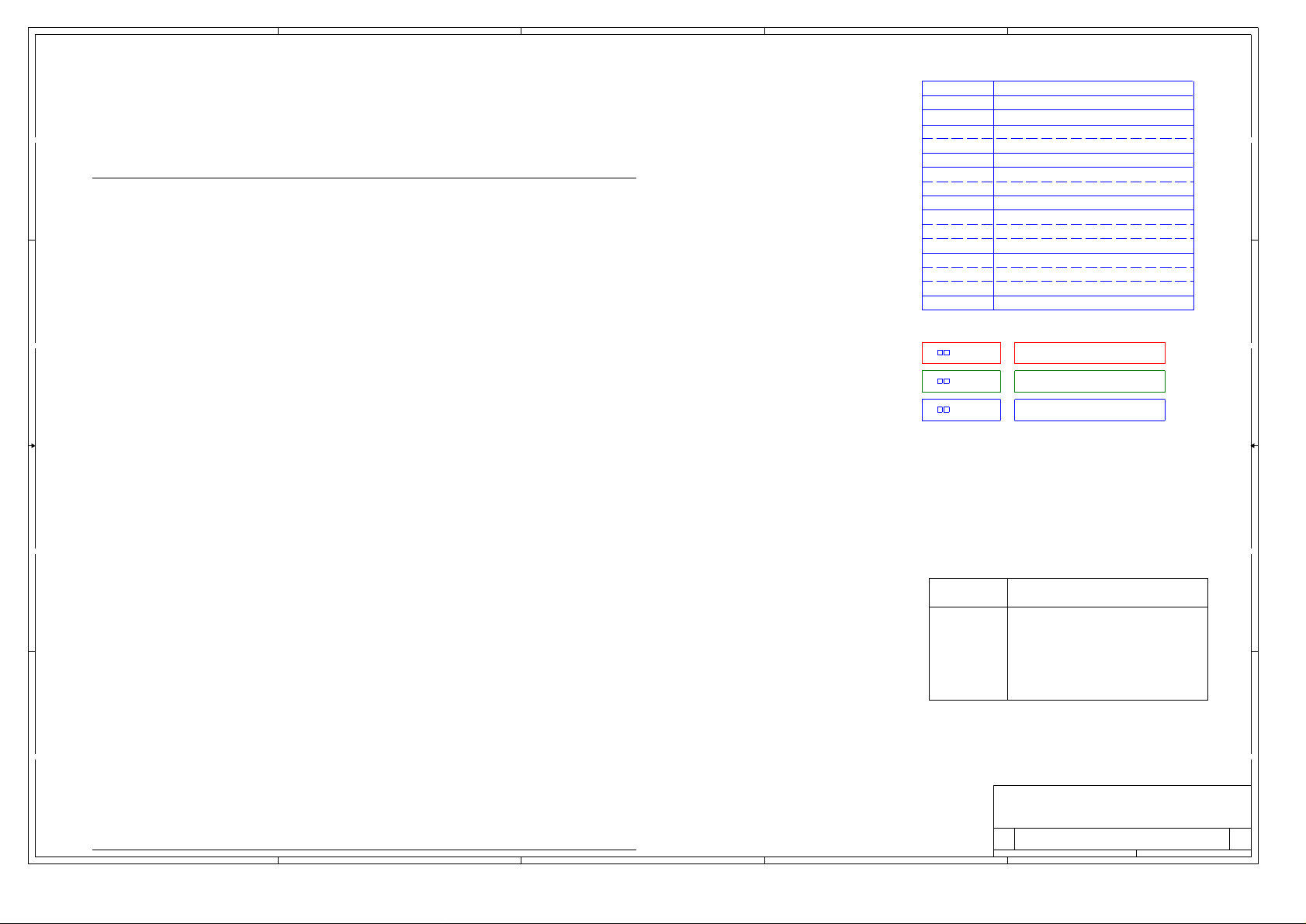

Power Rail

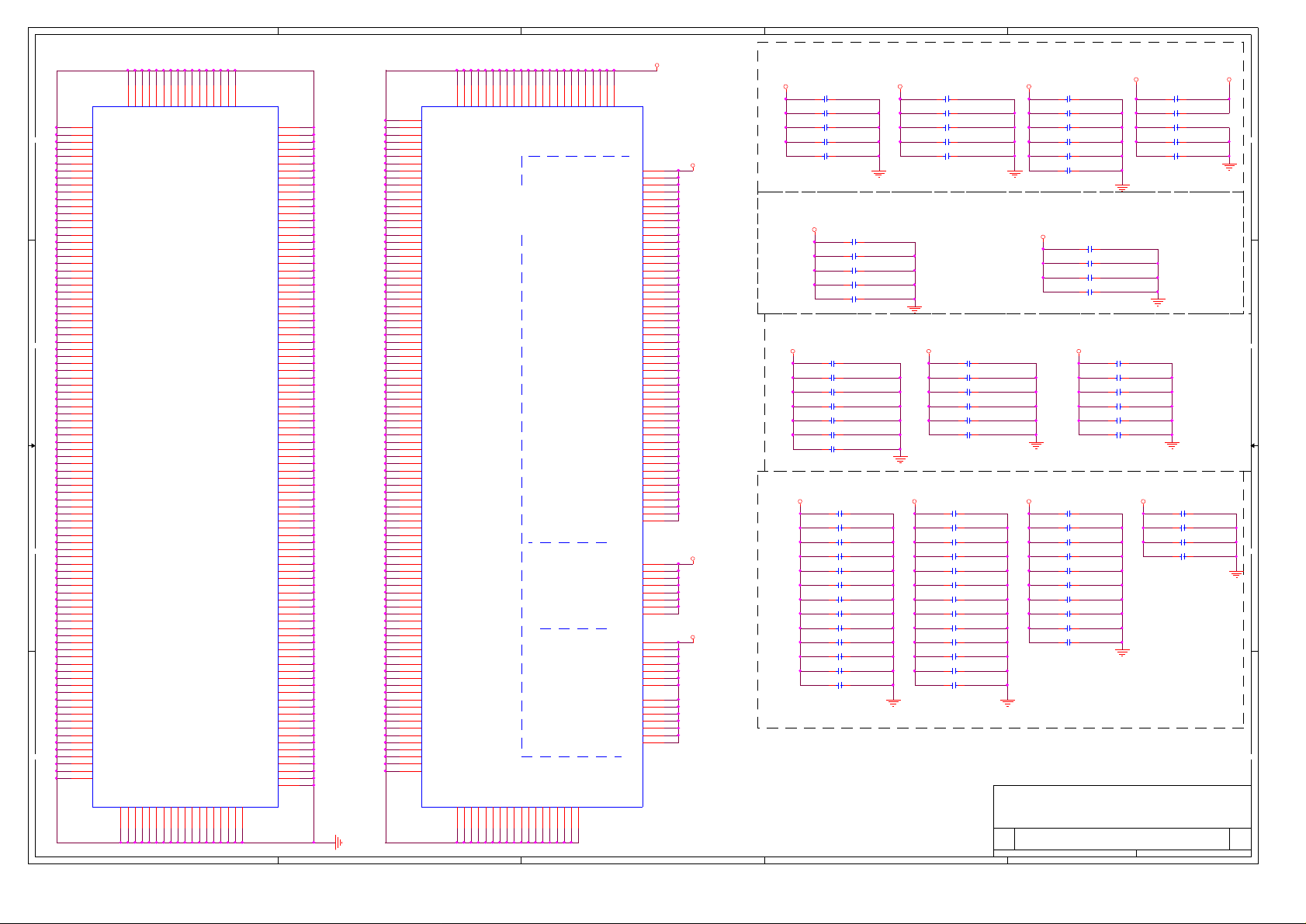

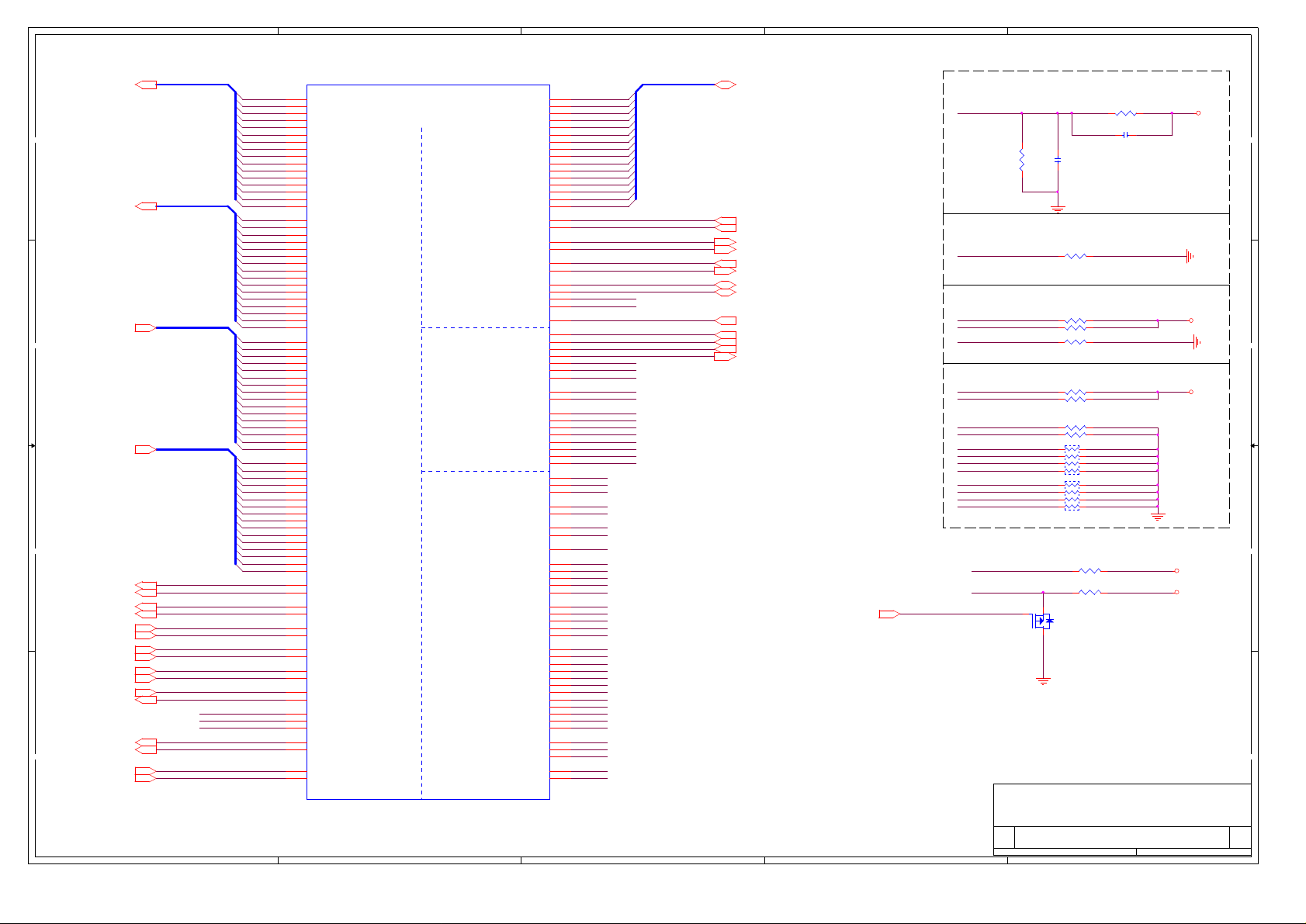

P50CA0 Schematics :

82GP50105-B2 SMT+MI M/B ASSY P50CA0 REV.B2 LF

DD

CC

BB

AA

(37GP50100-B2 PCB MAIN BD FOR P50CA0 REV:B2)

CONTENTPAGE

1.Cover Page

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

24.

25.

26.

27.

28.

29.

30.

31.VCC_MOSFET

5

System Block Diagram

AMD K8 CPU_HT -1

AMD K8 CPU_DDR -2

AMD K8 CPU_PWR&GND -3

DDR

DDR-DIMM

Clock Generator

K8T890 - HOST -1

K8T890 - PCIE -2

K8T890 - POWER & GND -3

K8T890 - POWER & GND -4

VGA MXM CONN

NEW CARD

LCD CONN. & INV. CONN

VT 8237 -1

VT 8237 -2

VT 8237 -3

IDE &SATA_HDD_CDROM

MINI PCI

IEEE1394

LAN - RTL8100C/RTL8110S

LAN -2 & VCORE-STOP

IT8510E - 1

IT8510E - 2

+3.3V,+5V & +12V

+2.6V,+1.3V & +1.8V(LDO)

+1.5V,+1.2V & +2.5V(LDO)

VCC_CORE (ISL6559)

INPUT & BATTERY CHARGER

Revision : B2 LF

4

+VCC_CORE

+V2.62.6V rail for Processor DDR VDDIO(off in S4-S5)

+V1.3

+V2.5S

+V2.5

+V1.2S

+V1.5S

+V1.5

+V1.8S

+V3.3ALWAYS

+V3.3S

+V3.3

+V5ALWAYS

+V5S

+V5

ALWAYS+V

+V

+VS

Core voltage for Processor(off in S3-S5)

1.3V rail for Processor DDR VTT(off in S4-S5)

2.5V switched power rail (off in S3-S5)

2.5V switched power rail (off in S4-S5)

1.2V rail for Processor VLDT(off in S3-S5)

1.5V switched power rail (off in S3-S5)

1.5V power rail (off in S4-S5)

1.8V switched power rail (off in S3-S5)

3.3V always on power rail

3.3V switched power rail (off in S3-S5)

3.3V power rail (off in S4-S5)

5V always on power rail

5V switched power rail (off in S3-S5)

5V power rail (off in S4-S5)

12V always on power rail+V12ALWAYS

Always on power rail

Switched power rail ( off in S4 - S5 )

Switched power rail ( off in S3 - S5 )

PCI Resure Allocation

DeviceIDSEL

REQ/GNT#

IEEE 1394AD190 0

GIGA LAN

MINI PCI

AD20

AD21

1 1

2 2

NBD

UNIWILL COMPUTER CORP.

Project : P50CA0

SizeDocument NumberRev

3159

3

2

Date:Sheet of

COVER

INT

A

B

C

131Monday, August 29, 2005

1

B2

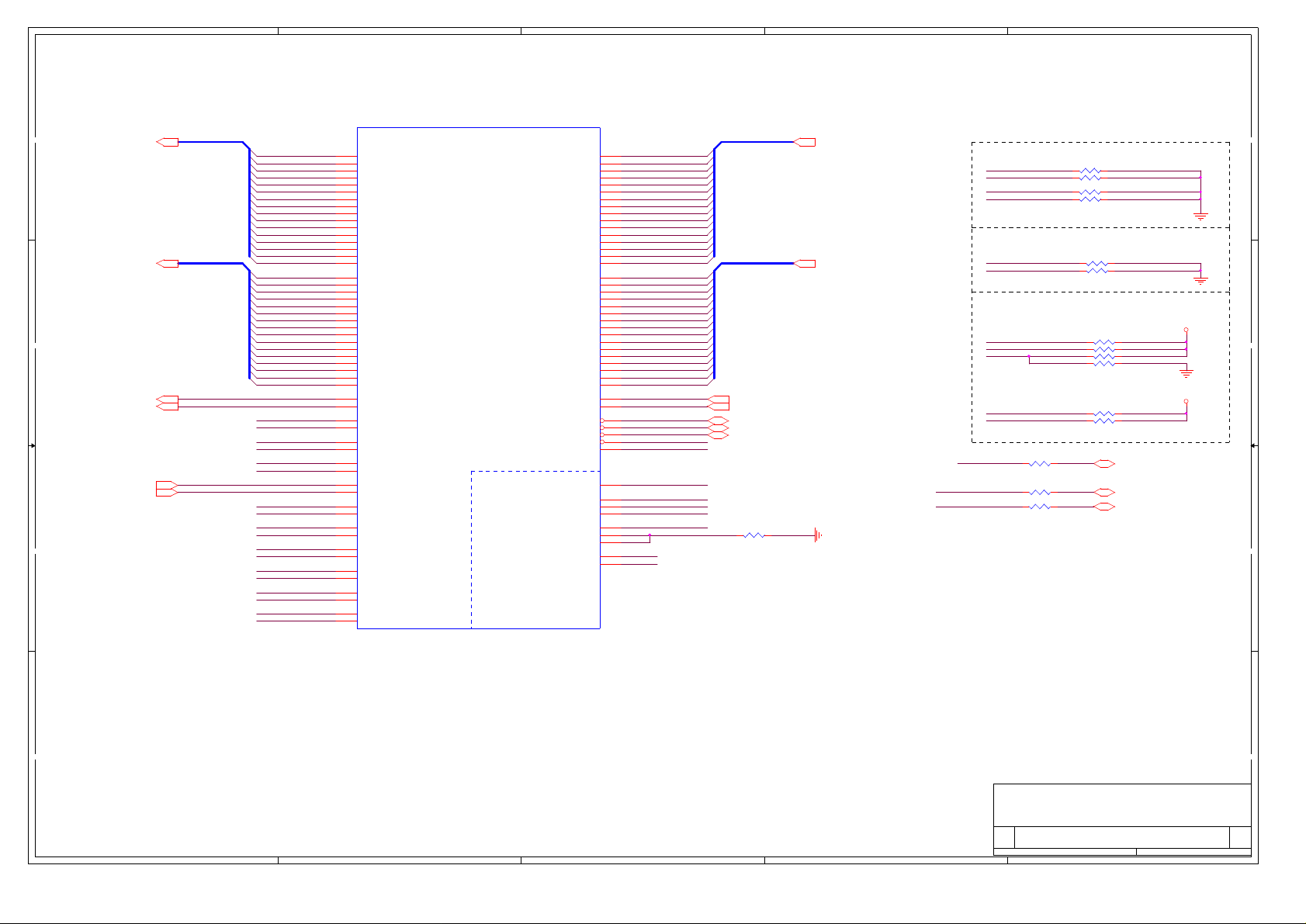

Page 2

5

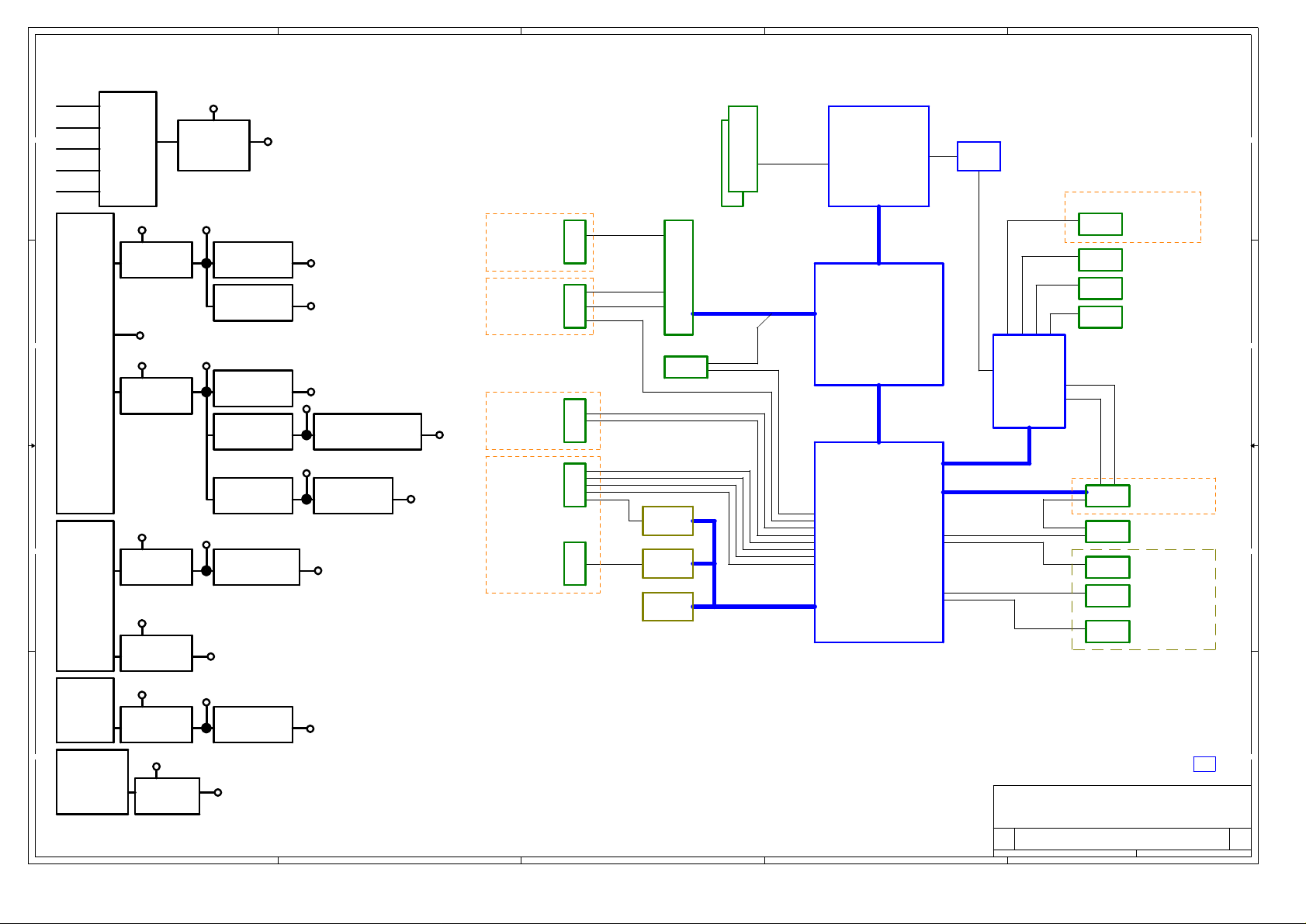

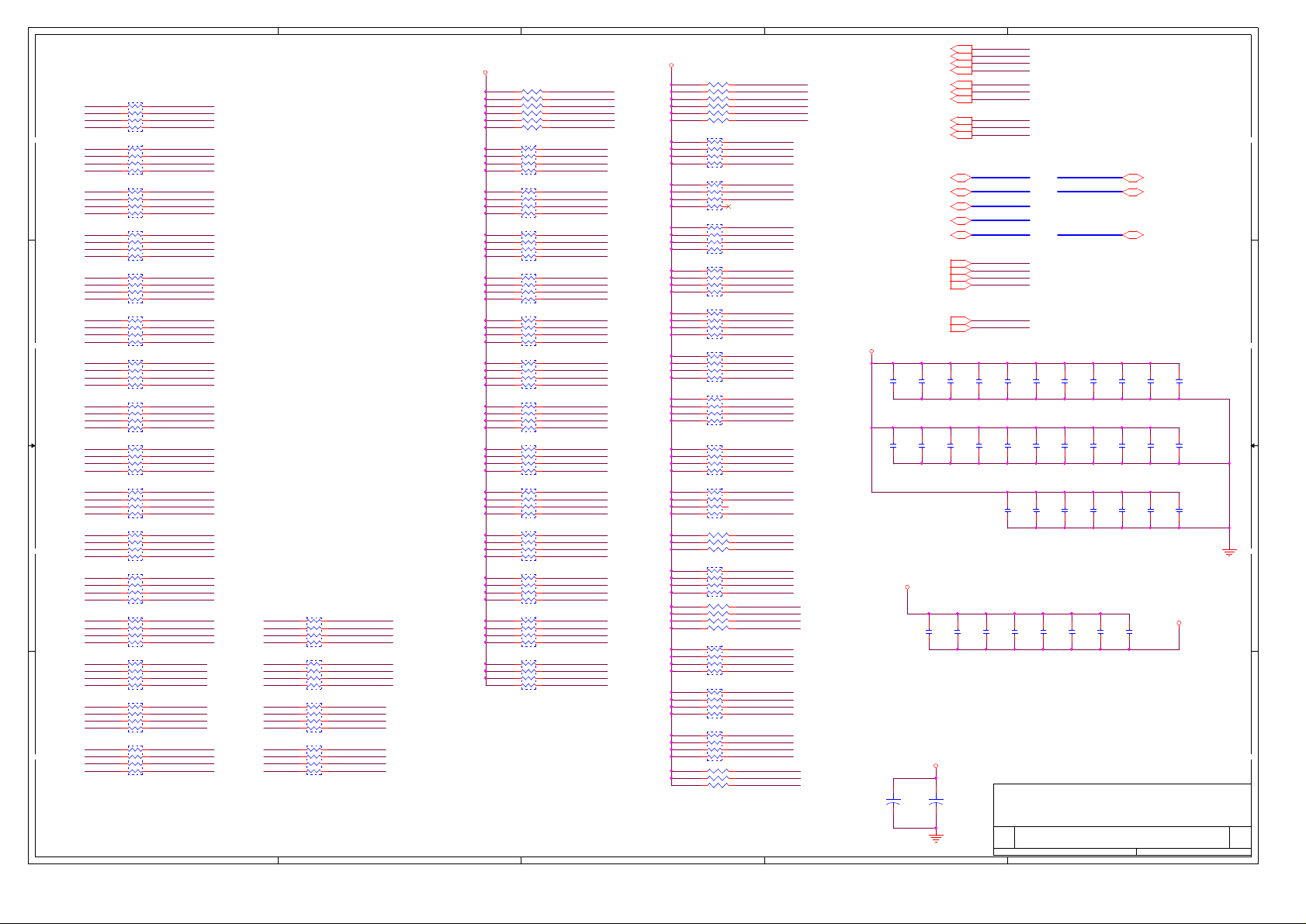

POWER BLOCK DIAGRAM

4

3

2

1

VID0

VIN

VID1

VID2

DD

VID3

ISL6559

(DC-DC)

RSS090N03

RQA200N03

+VCORE_ON

VCC_CORE/45A

CN.6/3

DDR1

AMD K8

ADM

1032

VID4

CN.15

CN.5

CN.12

CN.14

CN.17

To S/W

Board

TP

KB

RF-SW

To Auido

Board

CD-ROM

HDD

Option

Reserve

1

PCB

231Monday, August 29, 2005

VIN

RSS090N03

RQA200N03

CC

SC1404

(DC-DC)

+V12ALWAYS/100mA

VIN

RSS090N03

RQA200N03

VIN

BB

OZ813

(DC-DC)

RSS090N03

+V2.6_ON

+V5ALWAYS/100mA(8.5Amax)

AO4422(SW.)

+V5_ON

AO4422(SW.)

SUS_PWR_ON

+V3.3ALWAYS/300mA(7.5Amax)

AO4422(SW.)

+V3.3_ON

AO4422(SW.)

SUS_PWR_ON

CM8562(LDO)

+V2.5_ON

+V2.6/3.5A(6.2Amax)

RT9173B(LDO)

SUS_PWR_ON

+V5/4.2A

+V5S/4.04A

+V3.3/0.65A

+V3.3S/5A

MIC37302BR(LDO)

SUS_PWR_ON

+V2.5/0.441A(1.5Amax)

AO4422(SW.)

SUS_PWR_ON

+V1.2S/0.7A

+V1.8S/2A

+V2.5S/1.05A

To LCD

Module

To DVI

Board

New Card

To AC-IN

Board

To I/O Board

LVDS

CN.4

CRT

DVI

USB x 1

CN.8

USB x 2

CN.2

USB x 4

CN.18

CN.9

VIN

AO4912

SUS_PWR_ON

VIN

OZ813

(DC-DC)

AA

TL594

(CHARGER)

AO4912

+V1.5_ON

VADAP

FDS4435

SK34A

CHG_ON

5

+V1.3S/1.7A

+V1.5/14mA(3.5Amax)

AO4422(SW.)

SUS_PWR_ON

12.6V/2Amax

+V1.5S/3.25A

4

MXM

CN.20

1394

LAN

Mini-PCI

3

HyperTransport

CN.1

CN.16

CN.10

CN.19

PCI-E

PCI-E

USB x 1

PCI

V8T890

V-Link

VT8237R

2

IT8510

LPC

AC'97

PATA

SATA1

SATA2

UNIWILL COMPUTER CORP.

Project : P50CA0

SizeDocument NumberRev

BLOCK DIAGRAMB2

3159

Date:Sheet of

CN.13

LID

IR

Page 3

A

CADIP[0:15]9

44

CADIN[0:15]9

33

CADOP[0:15]9

CADON[0:15]9

22

11

CADIP[0:15]

CADIN[0:15]

CLKIP19

CLKIP09

CTLIP09

CLKIN19

CLKIN09

CTLIN09

CADOP[0:15]

CADON[0:15]

CLKOP19

CLKOP09

CTLOP09

CLKON19

CLKON09

CTLON09

A

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP2

CADIP1

CADIP0

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

CLKIP1

CLKIP0

CTLIP1

CTLIP0

CLKIN1

CLKIN0

CTLIN1

CTLIN0

CADOP15

CADOP14

CADOP13

CADOP12

CADOP11

CADOP10

CADOP9

CADOP8

CADOP7

CADOP6

CADOP5

CADOP4

CADOP3

CADOP2

CADOP1

CADOP0

CADON15

CADON14

CADON13

CADON12

CADON11

CADON10

CADON9

CADON8

CADON7

CADON6

CADON5

CADON4

CADON3

CADON2

CADON1

CADON0

CLKOP1

CLKOP0

CTLOP1

CTLOP0

CLKON1

CLKON0

CTLON1

CTLON0

H_LVREF1

H_LVREF0

W27

AA27

AB25

AC27

AD25

AB29

AB27

AD29

AD27

W26

AA26

AA25

AC26

AC25

W29

AA29

AB28

AC29

AD28

W25

AF27

AE26

T25

U27

V25

T27

V29

V27

Y29

R25

U26

U25

T28

U29

V28

Y25

Y27

R27

T29

Y28

R26

R29

N26

L25

L26

J25

G25

G26

E25

E26

N29

M28

L29

K28

H28

G29

F28

E29

N27

M25

L27

K25

H25

G27

F25

E27

P29

M27

M29

K27

H27

H29

F27

F29

J26

J29

N25

P28

J27

K29

P25

P27

U2A

L0_CADIN_H15

L0_CADIN_H14

L0_CADIN_H13

L0_CADIN_H12

L0_CADIN_H11

L0_CADIN_H10

L0_CADIN_H9

L0_CADIN_H8

L0_CADIN_H7

L0_CADIN_H6

L0_CADIN_H5

L0_CADIN_H4

L0_CADIN_H3

L0_CADIN_H2

L0_CADIN_H1

L0_CADIN_H0

L0_CADIN_L15

L0_CADIN_L14

L0_CADIN_L13

L0_CADIN_L12

L0_CADIN_L11

L0_CADIN_L10

L0_CADIN_L9

L0_CADIN_L8

L0_CADIN_L7

L0_CADIN_L6

L0_CADIN_L5

L0_CADIN_L4

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_L1

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_H0

L0_CTLIN_H1

L0_CTLIN_H0

L0_CLKIN_L1

L0_CLKIN_L0

L0_CTLIN_L1

L0_CTLIN_L0

L0_CADOUT_H15

L0_CADOUT_H14

L0_CADOUT_H13

L0_CADOUT_H12

L0_CADOUT_H11

L0_CADOUT_H10

L0_CADOUT_H9

L0_CADOUT_H8

L0_CADOUT_H7

L0_CADOUT_H6

L0_CADOUT_H5

L0_CADOUT_H4

L0_CADOUT_H3

L0_CADOUT_H2

L0_CADOUT_H1

L0_CADOUT_H0

L0_CADOUT_L15

L0_CADOUT_L14

L0_CADOUT_L13

L0_CADOUT_L12

L0_CADOUT_L11

L0_CADOUT_L10

L0_CADOUT_L9

L0_CADOUT_L8

L0_CADOUT_L7

L0_CADOUT_L6

L0_CADOUT_L5

L0_CADOUT_L4

L0_CADOUT_L3

L0_CADOUT_L2

L0_CADOUT_L1

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_H0

L0_CTLOUT_H1

L0_CTLOUT_H0

L0_CLKOUT_L1

L0_CLKOUT_L0

L0_CTLOUT_L1

L0_CTLOUT_L0

L0_REF1

L0_REF0

B

Control

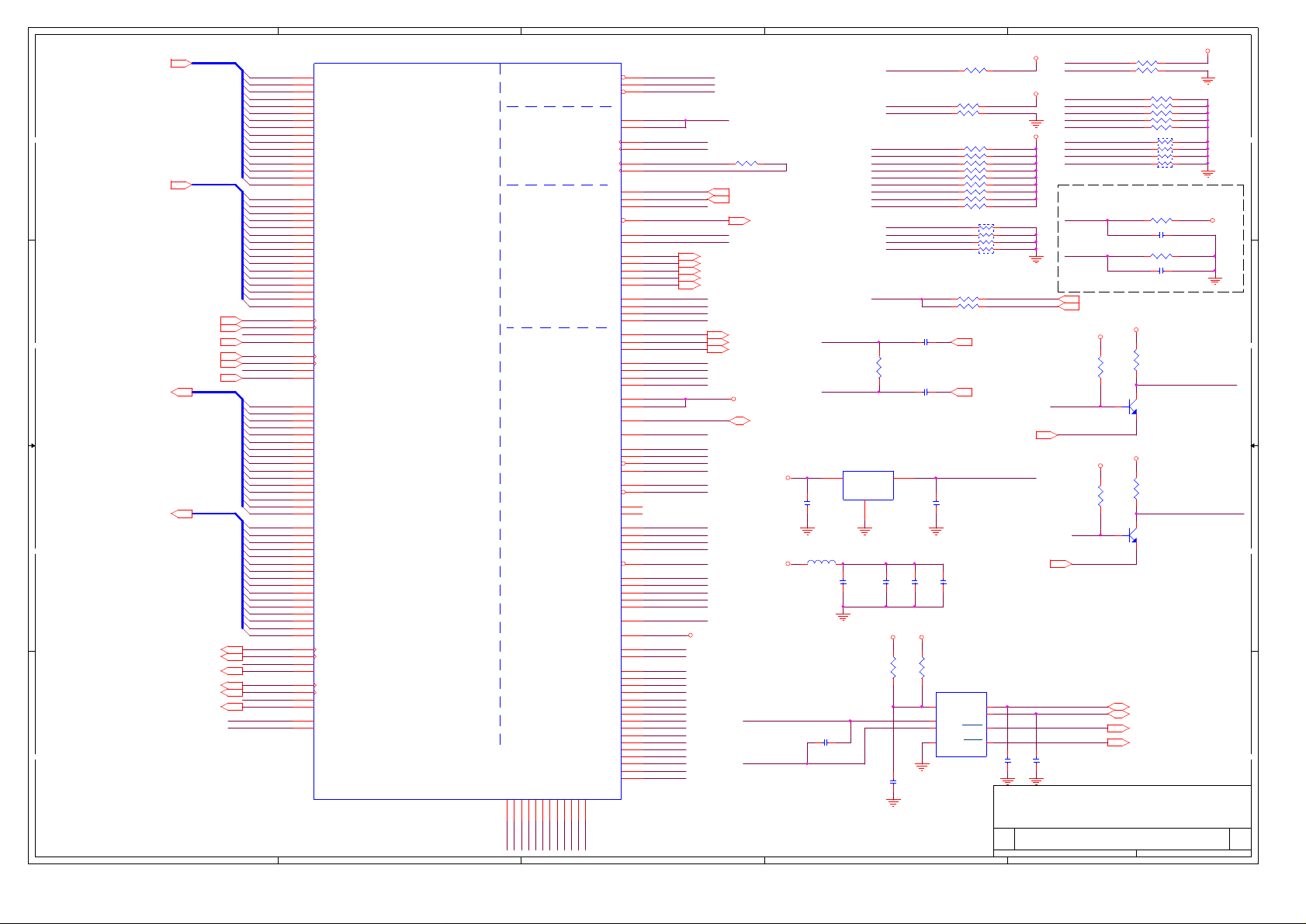

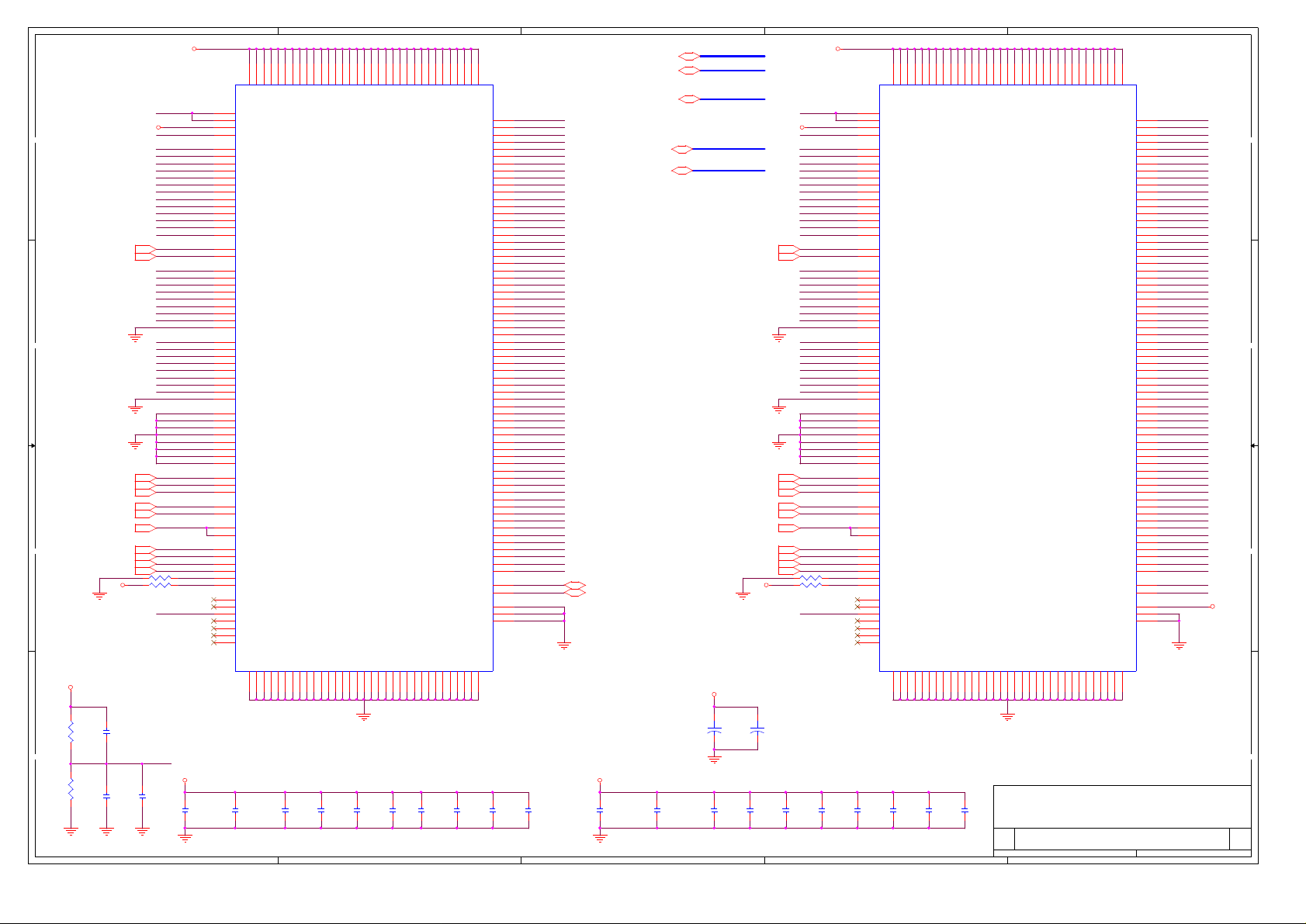

AMD K8 CPU 1/4

PLL

&

Clocks

CPU Core

Hyper Transport Interface

FREE25

FREE27

C24

A25

C9

TZ0320

TZ0321

TZ0322

B

C

CPURST#

AF20

RESET_L

PWROK

LDTSTOP_L

VDDA1

VDDA2

CLKIN_H

CLKIN_L

G_FBCLKOUT_H

G_FBCLKOUT_L

COREFB_H

COREFB_L

CORE_SENSE

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC

NC

NC

NC

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

NC

NC

NC

NC

VTT_A5

VTT_B5

DBRDY

NC

TMS

TCK

TRST_L

TDI

NC

NC

KEY1

KEY0

NC

NC

NC

NC

DBREQ_L

NC

NC

NC

NC

NC

TDO

NC

RSVD_SCL

RSVD_SDA

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

AG7

AE22

TZ0323

TZ0324

B7C3K1R2AA3F3C23

AMD_K8_754_uPGA

TZ0325

TZ0326

TZ0327

TZ0328

TZ0329

TZ0330

TZ0331

AE18

AJ27

AH25

AJ25

AJ21

AH21

AH19

AJ19

A23

A24

B23

A20

A26

A27

AG13

AF14

AG14

AF15

AE15

AG18

AH18

AG17

AJ18

AE12

AF12

AE11

AJ23

AH23

AE24

AF24

C16

AG15

AH17

C15

E20

E17

B21

A21

C18

A19

A28

AJ28

AE23

AF23

AF22

AF21

AE19

D20

C21

D18

C19

B19

A22

AF18

D22

C22

C1

J3

R3

AA2

D3

AG2

B18

AH1

AE21

C20

AG4

C6

AG6

AE9

AG9

B13

PM_PWROK_K8Q

H_LDSTOP_L

CPU_VDDA

H_CPUCK+

H_CPUCK-

FBCLKOUT+

FBCLKOUT-

COREFB+

COREFB-

CORE_SENSE

PM_THRMTRIP#

H_THERMDA

H_THERMDC

H_BP3

H_BP2

H_BP1

H_BP0

VDDIOFB+

VDDIOFB-

SNS_+2.6VDIMM

H_BPSCLK+

H_BPSCLK#

PLLCHRZ+

PLLCHRZ-

H_DBRDY

DCLKTWO

H_TMS

H_TCK

H_TRST#

H_TDI

H_SINCHN

H_BRN#

CLAW_ANALOG3

CLAW_ANALOG2

CLAW_ANALOG1

CLAW_ANALOG0

H_DBREQ#

H_SCANCLK1

H_SCANCLK2

H_SCANEN

H_SCANSHENB

H_SCANSHENA

H_TDO

TZ0302

TZ0303

TZ0304

TZ0305

TZ0306

TZ0307

TZ0308

TZ0309

TZ0310

TZ0311

TZ0312

TZ0313

TZ0314

TZ0315

TZ0316

TZ0317

TZ0318

TZ0319

C

R4580.6R/F

1 2

COREFB+29

COREFB-29

PM_THRMTRIP#4

VID429

VID329

VID229

VID129

VID029

VDDIOFB+27

VDDIOFB-27

SNS_+2.6VDIMM27

+V1.3

H_DBRDY

+V3.3S

+V2.5_VDDA

H_CPUCK+

H_CPUCK-

C E

C477

@1U

2 1

L28

100nH

Modify B.

+V2.6

Modify B.

H_THERMDA

H_THERMDC

Route H_THERMDA/C on same layer.

10 mil trace

10 mil spaceing

C104

2 1

2200P/50V/X7R

H_DBREQ#

H_DBRDY

H_TMS

H_TCK

H_TRST#

H_TDI

H_SINCHN

H_BRN#

PM_THRMTRIP#

H_LDSTOP_L

12

U15

@AME8800DEFT

VINVOUT

GND

B

CPU_VDDA

C471

@220U/4V

2 1

4.7U/10V/X5R

R73

200R

D

H_TDO

H_BPSCLK+

H_BPSCLK#

CLAW_ANALOG3

CLAW_ANALOG2

CLAW_ANALOG1

CLAW_ANALOG0

C69

R48

169R/F

C76

C453

2 1

+V3.3S

+V3.3

12

R328

@200R

Z0302

C127

0.1U

2 1

D

R53@560R

1 2

R56820R

1 2

R51820R

1 2

R44560R

1 2

R39560R

1 2

R314@470R

1 2

R47@470R

1 2

R50@470R

1 2

R49@470R

1 2

R35680R

1 2

R43680R

1 2

R46680R

1 2

RN54680R-8P4R

R570R

1 2

R60@0R

1 2

21

3900P

21

3900P

Modify B.

C474

@0.1U

2 1

C448

C447

3300P

0.1U

2 1

2 1

12

U3

1

VDD

SCLK

SDATA

2

D+

3

D-

THERM

5 6

GNDALERT

ADM1032

E

+V2.5

CTLIP1

R31749.9R/F

1 2

R31849.9R/F

1 2

R310@1K

1 2

R308@1K

1 2

R305680R

1 2

R311680R

1 2

R312680R

1 2

RN21680R-8P4R

1

8

7 2

3

6

5

4

+V2.5

+V2.5S

CTLIN1

H_BP3

H_BP2

H_BP1

H_BP0

H_SCANCLK1

H_SCANCLK2

H_SCANSHENA

H_SCANSHENB

H_SCANEN

HT I/O Compensation

1

8

7 2

3

6

5

4

HTSTOPSB#

HTSTOPNB#

CLK_CPU_BCLK+8

CLK_CPU_BCLK-8

PCI_RST#9,13,16,19,20,21,22,24

CPU_VDDA

+2.5V/300mA

PM_PWROK_K824

8

7

4

C485

68P

2 1

H_LVREF1

H_LVREF0

Z0301

SMB_CLK_BAT_B

SMB_DATA_BAT_B

PM_THRM_CPU#

THRM_ALERT#

C486

68P

2 1

Modify B.

PCI_RST#

R31344.2R/F

C459

R5244.2R/F

C83

HTSTOPSB#9,16,23

HTSTOPNB#9

+V2.5S

+V3.3S

12

R303

10K

B

+V2.5S

+V3.3S

12

R449

10K

Z0304

B

PM_PWROK_K8

Modify B.

SMB_CLK_BAT_B8,24

SMB_DATA_BAT_B8,24

PM_THRM_CPU#4

THRM_ALERT#17

1 2

1000P

1 2

1000P

12

R302

680R

Q7

2N2222

E C

12

R448

680R

Q41

2N2222

E C

21

21

Modify B2 LF

CPURST#

Modify B2 LF

PM_PWROK_K8Q

UNIWILL COMPUTER CORP.

Project : P50CA0

SizeDocument NumberRev

3159

Date:Sheet of

AMD CPU K8

E

331Monday, August 29, 2005

+V1.2S

+V1.2S

Modify B.

B2

Page 4

A

B

C

D

E

U2B

SNS_+V1.3

SNS_+V1.327

44

M_D[0..63]6

33

22

M_DQMA[0..7]6

M_DQS[0..7]6

11

+V1.3_REF

M_D[0..63]

M_DQMA[0..7]

M_DQS[0..7]

+V1.3_REF

MEMZN

MEMZP

M_D63

M_D62

M_D61

M_D60

M_D59

M_D58

M_D57

M_D56

M_D55

M_D54

M_D53

M_D52

M_D51

M_D50

M_D49

M_D48

M_D47

M_D46

M_D45

M_D44

M_D43

M_D42

M_D41

M_D40

M_D39

M_D38

M_D37

M_D36

M_D35

M_D34

M_D33

M_D32

M_D31

M_D30

M_D29

M_D28

M_D27

M_D26

M_D25

M_D24

M_D23

M_D22

M_D21

M_D20

M_D19

M_D18

M_D17

M_D16

M_D15

M_D14

M_D13

M_D12

M_D11

M_D10

M_D9

M_D8

M_D7

M_D6

M_D5

M_D4

M_D3

M_D2

M_D1

M_D0

M_DQMA8

M_DQMA7

M_DQMA6

M_DQMA5

M_DQMA4

M_DQMA3

M_DQMA2

M_DQMA1

M_DQMA0

M_DQS8

M_DQS7

M_DQS6

M_DQS5

M_DQS4

M_DQS3

M_DQS2

M_DQS1

M_DQS0

AE13

AG12

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AH13

AJ13

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

B9

C7

A6

C11

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

AC1

AC3

W2

Y1

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

R1

A13

A7

C2

H1

AA1

AG1

AH7

T1

A14

A8

D1

J1

AB1

AJ2

AJ8

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

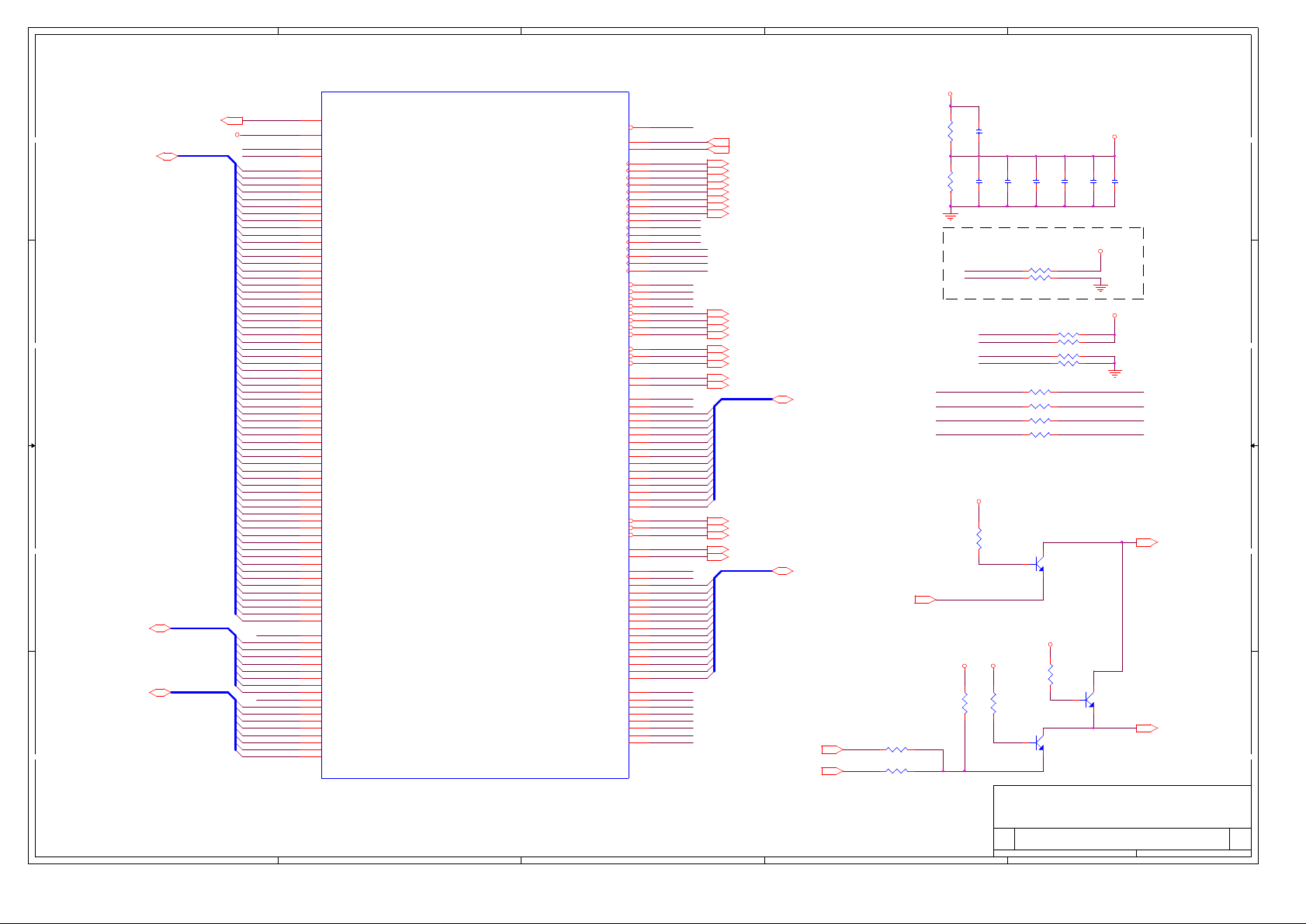

AMD K8 CPU 2/4

DDR SDRAM Interface

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

RSVD_MEMADDA15

RSVD_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

RSVD_MEMADDB_B15

RSVD_MEMADDB_B14

MEMADDB_B13

MEMADDB_B12

MEMADDB_B11

MEMADDB_B10

MEMADDB_B9

MEMADDB_B8

MEMADDB_B7

MEMADDB_B6

MEMADDB_B5

MEMADDB_B4

MEMADDB_B3

MEMADDB_B2

MEMADDB_B1

MEMADDB_B0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

AMD_K8_754_uPGA

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

MEMRST#

M_CKE0_R

M_CKE1_R

M_CLK_DDR+7

M_CLK_DDR-7

M_CLK_DDR+6

M_CLK_DDR-6

M_CLK_DDR+5

M_CLK_DDR-5

M_CLK_DDR+4

M_CLK_DDR-4

M_CLK_DDR+3

M_CLK_DDR-3

M_CLK_DDR+2

M_CLK_DDR-2

M_CLK_DDR+1

M_CLK_DDR-1

M_CLK_DDR+0

M_CLK_DDR-0

M_CS7_R#

M_CS6_R#

M_CS5_R#

M_CS4_R#

M_CS3_R#

M_CS2_R#

M_CS1_R#

M_CS0_R#

M_RAS#

M_CAS#

M_WE#

M_BAA1

M_BAA0

M_A15

M_A14

M_A13

M_A12

M_A11

M_A10

M_A9

M_A8

M_A7

M_A6

M_A5

M_A4

M_A3

M_A2

M_A1

M_A0

M_RASB#

M_CASB#

M_WEB#

M_BAB1

M_BAB0

M_AB15

M_AB14

M_AB13

M_AB12

M_AB11

M_AB10

M_AB9

M_AB8

M_AB7

M_AB6

M_AB5

M_AB4

M_AB3

M_AB2

M_AB1

M_AB0

MECC7

MECC6

MECC5

MECC4

MECC3

MECC2

MECC1

MECC0

M_CKE0_R6,7

M_CKE1_R6,7

M_CLK_DDR+77

M_CLK_DDR-77

M_CLK_DDR+67

M_CLK_DDR-67

M_CLK_DDR+57

M_CLK_DDR-57

M_CLK_DDR+47

M_CLK_DDR-47

M_CS3_R#6,7

M_CS2_R#6,7

M_CS1_R#6,7

M_CS0_R#6,7

M_RAS#6,7

M_CAS#6,7

M_WE#6,7

M_BAA16,7

M_BAA06,7

M_A[0..13]

M_RASB#6,7

M_CASB#6,7

M_WEB#6,7

M_BAB16,7

M_BAB06,7

M_AB[0..13]

PM_THRM_CPU#3

DK_MXM_THERM#13

M_A[0..13]6,7

M_AB[0..13]6,7

PM_THRMTRIP#3

R2900R

1 2

R320R

1 2

+V2.6

12

C50

R37

0.01U

2 1

100R/F

12

C34

R38

0.01U

2 1

100R/F

+V1.3_REF

C41

C44

0.47U

0.47U

2 1

2 1

2 1

Memory I/O Compensation

AMD SUGGESTION

MEMZN

R3434.8R/F

MEMZP

M_CLK_DDR+7

M_CLK_DDR+6

M_CLK_DDR+5

M_CLK_DDR+4M_CLK_DDR-4

Modify B2.

+V1.2S

12

10K

1 2

R3634.8R/F

1 2

M_CLK_DDR-1

M_CLK_DDR-0

M_CLK_DDR+1

M_CLK_DDR+0

R299120R/F

1 2

R300120R/F

1 2

R294120R/F

1 2

R301120R/F

1 2

12

R289

10K

Z0401

B

+V3.3S+V3.3S

12

R291

R33

10K

Z0403

B

Z0404

R2510K

1 2

R2710K

1 2

R2410K

1 2

R2610K

1 2

Modify B.

Q5

2N2222

E C

+V3.3S

12

R31

10K

Z0402

Q26

2N2222

E C

+V1.3_REF

C31

30P

2 1

+V2.6

M_CLK_DDR-7

M_CLK_DDR-6

M_CLK_DDR-5

B

E C

Modify B.

C38

0.1U

+V2.6

Q6

2N2222

C32

1000P

2 1

AUX_OFF#26

Modify B.

PM_THRM#16

UNIWILL COMPUTER CORP.

Project : P50CA0

SizeDocument NumberRev

3159

A

B

C

D

Date:Sheet of

AMD CPU K8_DDR

431Monday, August 29, 2005

E

B2

Page 5

A

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

U2D

B2

VSS1

AH20

AB21

44

W22

M23

L24

AG25

AG27

D2

AF2

W6

Y7

AA8

AB9

AA10

J12

B14

Y15

AE16

J18

G20

R20

U20

W20

AA20

AC20

AE20

AG20

AJ20

D21

AD21

AG21

AG29

AA22

AC22

AG22

AH22

AJ22

AB23

AD23

AG23

W24

AA24

AC24

AG24

AJ24

AD26

AF26

AH26

F21

H21

K21

M21

P21

T21

V21

Y21

B22

E22

G22

J22

L22

N22

R22

U22

D23

F23

H23

K23

P23

T23

V23

Y23

E24

G24

J24

N24

R24

U24

B25

C25

B26

D26

H26

M26

T26

Y26

C27

B28

D28

G28

F15

33

22

11

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS3

VSS4

VSS5

VSS6

AMD K8 CPU 4/4

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS187

VSS188

H15

VSS196

GND

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

AB17

AD17

B16

G18

AA18

AC18

D19

F19

A

VSS197

VSS198

VSS213

VSS214

H19

Y17

L28

VSS93

VSS205

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS221

VSS222

AMD_K8_754_uPGA

N20

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

K19

Y19

AB19

AD19

AF19

J20

L20

B

B

AE27

AA28

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

W21

AA21

AC21

AB22

AD22

W23

C

+VCC_CORE

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

P26

VDD130

VDD91

V26

VDD131

VDD132

VDD92

J28

VDD93

VDD94

VDD95

VDD133

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VTT_B4

VTT_B3

VTT_B2

VTT_B1

VTT_A3

VTT_A2

VTT_A1

VTT_A4

VLDT_A6

VLDT_A5

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

VLDT_A0

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

AMD_K8_754_uPGA

+V2.6

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

+V1.3

AJ17

AH16

AG16

AF16

C17

B17

A18

D17

+V1.2S

D29

D27

D25

C28

C26

B29

B27

AH29

AH27

AG28

AG26

AF29

AE28

AF25

C

U2C

W9

VDD113

U9

VDD112

R9

N9

J9

Y8

V8

T8

P8

M8

K8

W7

U7

R7

U28

N28

L7

H18

B20

E21

H22

J23

H24

F26

N7

L9

V10

G13

K14

Y14

G15

J15

H16

K16

Y16

G17

J17

F18

K18

Y18

E19

G19

J19

F20

H20

K20

M20

P20

T20

V20

Y20

G21

J21

L21

N21

R21

U21

F22

K22

M22

P22

T22

V22

Y22

E23

G23

L23

N23

R23

U23

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD111

VDD110

VDD109

VDD108

VDD107

VDD106

VDD105

VDD104

VDD103

VDD102

VDD101

VDD100

VDD99

VDD98

VDD97

VDD96

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD120

AMD K8 CPU 3/4

POWER

CPU CORE

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

AA23

AC23

B24

D24

F24

K24

M24

P24

VDD121

VDD82

VDD122

VDD83

T24

VDD123

VDD124

VDD84

VDD85

V24

Y24

VDD125

VDD126

VDD127

VDD128

DDR

+V2.6

DDR

+V1.3

HOST

+V1.2

VDD86

VDD87

VDD88

VDD89

AB24

AD24

AH24

AE25

VDD129

VDD90

K26

Place these decouping capacitors on solder layer of processor.

+VCC_CORE +VCC_CORE

21

21

21

21

21

Place these capacitors in uPGA socket cavity.

+V1.2S

C46010U/6.3V/X5R

C46710U/6.3V/X5R

Modify B.

Place these capacitors near socket

+VCC_CORE

C4624.7U/10V/X5R

C4634.7U/10V/X5R

C3594.7U/10V/X5R

C4614.7U/10V/X5R

C3614.7U/10V/X5R

C554.7U/10V/X5R

C564.7U/10V/X5R

EMI

+VCC_CORE +VCC_CORE +VCC_CORE +VCC_CORE

D

0.22UC135

0.22UC46

0.22UC40

0.22UC39

0.22UC42

C3510U/6.3V/X5R

C3610U/6.3V/X5R

0.22UC43

21

0.22UC45

21

0.22UC37

21

21

21

+V2.6

21

21

21

21

21

21

E

+V1.3 +V2.6

0.22UC286

0.22UC397

0.22UC299

0.22UC357

0.22UC306

0.22UC587

0.22UC402

21

C3310U/6.3V/X5R

21

220U/4VC4

21

0.22UC586

21

0.22UC588

21

Modify B.

Modify B.

21

21

0.1UC465

21

0.1UC450

21

0.22UC589

21

+V2.6 +V2.6

21

21

21

21

21

21

21

680PC414

21

680PC514

21

680PC413

21

680PC416

21

680PC437

21

680PC515

21

680PC417

21

680PC455

21

680PC454

21

680PC394

21

680PC441

21

680PC440

21

680PC392

21

C2844.7U/10V/X5R

C2954.7U/10V/X5R

C124.7U/10V/X5R

C3034.7U/10V/X5R

C3364.7U/10V/X5R

C3954.7U/10V/X5R

680PC415

21

680PC406

21

680PC452

21

680PC400

21

680PC428

21

680PC513

21

680PC401

21

680PC473

21

680PC390

21

680PC383

21

680PC430

21

680PC439

21

680PC412

21

+VCC_CORE

C42910U/6.3V/X5R

21

C44610U/6.3V/X5R

21

C42010U/6.3V/X5R

21

C41110U/6.3V/X5R

21

21

21

21

21

21

21

680PC391

21

680PC30

21

680PC451

21

680PC438

21

680PC444

21

680PC421

21

680PC389

21

680PC418

21

680PC369

21

680PC502

21

0.22UC291

21

0.22UC308

21

0.22UC367

21

0.22UC368

21

0.22UC294

21

@220U/4VC316

21

1000PC404

21

1000PC422

21

1000PC425

21

1000PC432

21

UNIWILL COMPUTER CORP.

Project : P50CA0

SizeDocument NumberRev

3159

D

Date:Sheet of

AMD K8 CPU_PWR&GND

531Monday, August 29, 2005

E

B2

Page 6

5

RN310R-8P4R

M_DQMA0

8

M_D6

7 2

M_D2

6

M_DQS0

5

DD

CC

BB

AA

RN510R-8P4R

M_D9

5

M_DQS1

6

M_DQMA1

7 2

M_D13

8

RN410R-8P4R

M_D12

8

M_D8

7 2

M_D7

6

M_D3

5

RN710R-8P4R

M_D16

5

M_D17

6

M_D20

7 2

M_D21

8

RN910R-8P4R

M_D24M_D_R_24

8

7 2

M_D23M_D_R_23

6

5

RN810R-8P4R

M_DQS2M_DQS_R2

5

M_D18M_D_R_18

6

M_DQMA2M_DQMA_R_2

7 2

M_D22M_D_R_22

8

RN1110R-8P4R

M_D30

8

M_D31

7 2

M_D27

6

M_D26

5

RN1010R-8P4R

5

M_D29

6

M_DQS3

7 2

M_DQMA3

8

RN1410R-8P4R

M_D40M_D_R_40

8

M_D44M_D_R_44

7 2

M_D39M_D_R_39

6

M_D38M_D_R_38

5

RN1210R-8P4R

M_D32

5

M_D33

6

M_D36

7 2

M_D37

8

RN1310R-8P4R

M_D35M_D_R_35

8

M_DQMA4

7 2

M_D34

6

M_DQS4

5

RN1510R-8P4R

M_D41M_D_R_41

5

M_DQS5

6

M_D45M_D_R_45

7 2

M_DQMA5

8

RN1710R-8P4R

M_D53

8

M_D52

7 2

M_D49

6

M_D48

5

RN210R-8P4R

M_D63

8

M_D62

7 2

M_D59

6

M_D58

5

RN110R-8P4R

M_D4

8

M_D5M_D_R_5

7 2

M_D1

6

M_D0M_D_R_0

5

RN1810R-8P4R

M_DQMA6

5

M_DQS6

6

M_D50

7 2

M_D54

8

1

3

4

4

3

1

1

3

4

4

3

1

1

3

4

4

3

1

1

3

4

4

3

1

1

3

4

4

3

1

1

3

4

4

3

1

1

3

4

1

3

4

1

3

4

4

3

1

5

M_D_R_62

M_D_R_59

M_D_R_58

M_DQMA_R_0

M_D_R_6

M_D_R_2

M_DQS_R0

M_D_R_9

M_DQS_R1

M_DQMA_R_1

M_D_R_13

M_D_R_12

M_D_R_8

M_D_R_7

M_D_R_3

M_D_R_16

M_D_R_17

M_D_R_20

M_D_R_21

M_D_R_28M_D28

M_D_R_19M_D19

M_D_R_30

M_D_R_31

M_D_R_27

M_D_R_26

M_D_R_25M_D25

M_D_R_29

M_DQS_R3

M_DQMA_R_3

M_D_R_32

M_D_R_33

M_D_R_36

M_D_R_37

M_DQMA_R_4

M_D_R_34

M_DQS_R4

M_DQS_R5

M_DQMA_R_5

M_D_R_53

M_D_R_52

M_D_R_49

M_D_R_48

M_D_R_63

M_D_R_4

M_D_R_1

M_DQMA_R_6

M_DQS_R6

M_D_R_50

M_D_R_54

RN1910R-8P4R

M_D56M_D_R_56

M_D60

M_D51

M_D55

M_D57

M_DQS7

M_D61M_D_R_61

M_DQMA7M_DQMA_R_7

M_D47

M_D46

M_D43

M_D42

M_D15

M_D11

M_D14

M_D10

1

8

7 2

3

6

5

4

RN2010R-8P4R

5

4

3

6

7 2

1

8

RN1610R-8P4R

1

8

7 2

3

6

5

4

RN610R-8P4R

1

8

7 2

3

6

5

4

M_D_R_60

M_D_R_51

M_D_R_55

M_D_R_57

M_DQS_R7

M_D_R_47

M_D_R_46

M_D_R_43

M_D_R_42

M_D_R_15

M_D_R_11

M_D_R_14

M_D_R_10

4

+V1.3

R25247R

1 2

R25347R

1 2

R25468R

1 2

R25568R

1 2

R25068R

1 2

R25168R

1 2

RN4068R-8P4R

1

3

RN3668R-8P4R

3

1

RN3968R-8P4R

1

3

RN3368R-8P4R

3

1

RN3568R-8P4R

1

3

RN3768R-8P4R

1

3

RN2868R-8P4R

3

1

RN3068R-8P4R

1

3

RN4368R-8P4R

3

1

RN2768R-8P4R

1

3

RN2968R-8P4R

1

3

RN3247R-8P4R

1

3

RN4747R-8P4R

1

3

4

8

6

5724

5724

6

8

8

6

5724

5724

6

8

8

6

5724

8

6

5724

5724

6

8

8

6

5724

5724

6

8

8

6

5724

8

6

5724

8

6

5724

8

6

5724

M_AB11

M_D_R_23

M_D_R_28

M_D_R_5

M_D_R_4

M_D_R_8

M_D_R_3

M_D_R_2

M_DQS_R0

M_D_R_12

M_D_R_7

M_D_R_6

M_DQMA_R_0

M_D_R_10

M_D_R_11

M_D_R_9

M_DQS_R1

M_D_R_30

M_D_R_31

M_D_R_29

M_DQMA_R_3

M_DQMA_R_1

M_D_R_13

M_D_R_15

M_D_R_14

M_D_R_26

M_DQS_R3

M_D_R_25

M_D_R_24

M_D_R_53

M_D_R_52

M_D_R_46

M_D_R_47

M_D_R_36

M_D_R_37

M_DQMA_R_4

M_D_R_38

M_D_R_50

M_DQS_R6

M_D_R_51

M_D_R_56

M_DQMA_R_6

M_D_R_54

M_D_R_55

M_D_R_60

M_D_R_39

M_D_R_44

M_D_R_45

M_DQMA_R_5

M_AB6

M_AB4

M_AB2

M_AB0

M_AB3

M_AB1

M_AB7

M_AB5

3

+V1.3

3

R26447R

1 2

R26747R

1 2

R27168R

1 2

R26368R

1 2

R26868R

1 2

R26968R

1 2

RN4847R-8P4R

1

8

3

6

5724

RN5147R-8P4R

1

8

3

6

5724

RN3468R-8P4R

5724

3

6

1

8

RN4268R-8P4R

1

8

3

6

5724

68R-8P4R

RN44

1

8

3

6

5724

RN49

47R-8P4R

1

8

3

6

5724

RN4668R-8P4R

5724

3

6

1

8

RN5047R-8P4R

1

8

3

6

5724

RN4147R-8P4R

1

8

3

6

5724

R27047R

1 2

R27947R

1 2

R26647R

1 2

RN4568R-8P4R

1

8

3

6

R27747R

R27647R

R27447R

R27547R

R27347R

R27247R

R26547R

5724

1 2

1 2

1 2

1 2

RN3868R-8P4R

1

8

3

6

5724

RN2668R-8P4R

1

8

3

6

5724

RN3147R-8P4R

1

8

3

6

5724

1 2

1 2

1 2

M_AB9

M_AB12M_AB8

M_D_R_27

M_D_R_16

M_D_R_0

M_D_R_1

M_A11

M_A8

M_A6

M_A4

M_BAA0

M_WE#

M_CS0_R#

M_D_R_22

M_DQMA_R_2

M_D_R_21

M_D_R_20

M_D_R_59

M_D_R_58

M_D_R_57

M_DQS_R7

M_D_R_49

M_D_R_48

M_D_R_42

M_D_R_43

M_A13

M_A9

M_A12

M_A5

M_D_R_33

M_D_R_32

M_D_R_34

M_DQS_R4

M_A7

M_A1

M_A3

M_A10

M_BAB0

M_WEB#

M_CS2_R#

M_AB10

M_CKE0_R

M_CKE1_R

M_D_R_41

M_DQS_R5

M_D_R_40

M_D_R_35

M_A2

M_A0

M_BAA1

M_RAS#

M_D_R_19

M_D_R_18

M_DQS_R2

M_D_R_17

M_D_R_61

M_DQMA_R_7

M_D_R_62

M_D_R_63

M_BAB1

M_RASB#

M_CASB#

M_CS3_R#

M_CS1_R#

M_CAS#

M_AB13

2

M_BAA04,7

M_BAA14,7

M_BAB04,7

M_BAB14,7

M_RAS#4,7

M_CAS#4,7

M_WE#4,7

M_RASB#4,7

M_CASB#4,7

M_WEB#4,7

M_DQS[0..7]4

M_D[0..63]4

M_A[0..13]4,7

M_AB[0..13]4,7

M_DQMA[0..7]4 M_DQMA_R_[0..7]7

M_CS0_R#4,7

M_CS1_R#4,7

M_CS2_R#4,7

M_CS3_R#4,7

M_CKE0_R4,7

M_CKE1_R4,7

M_BAA0

M_BAA1

M_BAB0

M_BAB1

M_RAS#

M_CAS#

M_WE#

M_RASB#

M_CASB#

M_WEB#

M_DQS[0..7]

M_D[0..63]

M_A[0..13]

M_AB[0..13]

M_DQMA[0..7]

M_CS0_R#

M_CS1_R#

M_CS2_R#

M_CS3_R#

M_CKE0_R

M_CKE1_R

M_DQS_R[0..7]

M_D_R_[0..63]

M_DQMA_R_[0..7]

+V1.3

C274

C278

0.1U

0.1U

2 1

2 1

C273

C256

0.1U

0.1U

2 1

2 1

C282

C279

0.1U

0.1U

2 1

2 1

C249

C268

0.1U

0.1U

2 1

2 1

2 1

2 1

0.015U

2 1

C292

0.1U

C255

0.1U

C253

2 1

2 1

0.015U

2 1

C247

0.1U

C250

0.1U

C269

C257

0.1U

2 1

C276

0.1U

2 1

C271

0.015U

2 1

C258

0.1U

2 1

C251

0.1U

2 1

C275

0.015U

2 1

2 1

2 1

0.015U

2 1

+V1.3

C612

C609

C610

C607

C608

0.1U

2 1

0.1U

0.1U

2 1

2 1

C611

0.1U

0.1U

2 1

2 1

C613

0.1U

0.1U

2 1

2 1

Modify B.

+V1.3

C313

@220U/4V

C296

+

@220U/4V

UNIWILL COMPUTER CORP.

Project : P50CA0

SizeDocument NumberRev

3159

Date:Sheet of

DDR

+

2

1

M_DQS_R[0..7]7

M_D_R_[0..63]7

C245

C252

0.1U

0.1U

2 1

C281

C254

0.1U

0.1U

2 1

C280

C270

0.015U

2 1

C614

0.1U

2 1

1

+V2.6

631Monday, August 29, 2005

C248

0.1U

2 1

C246

0.1U

2 1

C272

0.015U

2 1

B2

Page 7

5

+V2.6

91021223334364546575869708182929394113

CN6

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

SM_VREF_DIMM

+V3.3S

DD

M_BAA04,6

M_BAA14,6

CC

M_RAS#4,6

M_CAS#4,6

M_WE#4,6

M_CS0_R#4,6

M_CS1_R#4,6

M_CKE0_R4,6

+V2.6

12

12

M_CLK_DDR+54

M_CLK_DDR-54

M_CLK_DDR+74

M_CLK_DDR-74

R280

100R/F

R281

100R/F

+V2.6

C304

0.1U

2 1

SM_VREF_DIMM

C283

0.1U

2 1

BB

AA

TZ0701

M_A0

M_A1

M_A2

M_A3

M_A4

M_A5

M_A6

M_A7

M_A8

M_A9

M_A10

M_A11

M_A12

M_BAA0

M_BAA1

M_DQMA_R_0

M_DQMA_R_1

M_DQMA_R_2

M_DQMA_R_3

M_DQMA_R_4

M_DQMA_R_5

M_DQMA_R_6

M_DQMA_R_7

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_RAS#

M_CAS#

M_WE#

M_CS0_R#

M_CS1_R#

M_CKE0_R

M_CLK_DDR+5

M_CLK_DDR-5

M_CLK_DDR+7

M_CLK_DDR-7

R1110K

1 2

R1010K

M_A13

C3

0.1U

2 1

5

12

+V2.6

Z0701

Z0702

C297

10U/6.3V/X5R

2 1

1

VREF

2

VREF

197

VddSPD

199

VddID

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

78

DM8

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

118

RAS#

120

CAS#

119

WE#

121

CS0#

122

CS1#

96

CKE0

95

CKE1

35

CK0

37

CK0#

160

CK1

158

CK1#

89

CK2

91

CK2#

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

3415162728383940515263647576878890103

C265

10U/6.3V/X5R

2 1

C264

0.1U

2 1

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C266

0.1U

2 1

4

114

131

132

143

144

155

156

157

167

168

179

180

191

192

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

M_D_R_0

5

DQ0

M_D_R_1

7

DQ1

M_D_R_2

13

DQ2

M_D_R_3

17

DQ3

M_D_R_4

6

DQ4

M_D_R_5

8

DQ5

M_D_R_6

14

DQ6

M_D_R_7

18

DQ7

M_D_R_8

19

DQ8

M_D_R_9

23

DQ9

M_D_R_10

29

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

104

125

126

137

138

149

150

159

161

162

173

174

185

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

195

SCL

193

SDA

194

SA0

196

SA1

198

SA2

VSS

A5752D-A0G16-N_H5.2

186

DDR_SO-DIM

M_D_R_11

M_D_R_12

M_D_R_13

M_D_R_14

M_D_R_15

M_D_R_16

M_D_R_17

M_D_R_18

M_D_R_19

M_D_R_20

M_D_R_21

M_D_R_22

M_D_R_23

M_D_R_24

M_D_R_25

M_D_R_26

M_D_R_27

M_D_R_28

M_D_R_29

M_D_R_30

M_D_R_31

M_D_R_32

M_D_R_33

M_D_R_34

M_D_R_35

M_D_R_36

M_D_R_37

M_D_R_38

M_D_R_39

M_D_R_40

M_D_R_41

M_D_R_42

M_D_R_43

M_D_R_44

M_D_R_45

M_D_R_46

M_D_R_47

M_D_R_48

M_D_R_49

M_D_R_50

M_D_R_51

M_D_R_52

M_D_R_53

M_D_R_54

M_D_R_55

M_D_R_56

M_D_R_57

M_D_R_58

M_D_R_59

M_D_R_60

M_D_R_61

M_D_R_62

M_D_R_63

SMB_CLK

SMB_DATA

SMB_CLK8,17

SMB_DATA8,17

CHA Address : 0000H

+V2.6

C267

0.1U

2 1

C8

C7

0.1U

0.1U

2 1

2 1

4

C6

C290

0.1U

2 1

C5

0.1U

0.1U

2 1

2 1

M_DQMA_R_[0..7]6

C302

10U/6.3V/X5R

2 1

3

+V3.3S

+V2.6

SM_VREF_DIMM

TZ0702

M_AB0

M_AB1

M_AB2

M_AB3

M_AB4

M_AB5

M_AB6

M_AB7

M_AB8

M_AB9

M_AB10

M_AB11

M_AB12

M_BAB0

M_BAB1

M_DQMA_R_0

M_DQMA_R_1

M_DQMA_R_2

M_DQMA_R_3

M_DQMA_R_4

M_DQMA_R_5

M_DQMA_R_6

M_DQMA_R_7

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_A[0..13]4,6

M_AB[0..13]4,6

M_D_R_[0..63]6

M_DQS_R[0..7]6

M_A[0..13]

M_AB[0..13]

M_D_R_[0..63]

M_DQS_R[0..7]

M_DQMA_R_[0..7]

M_BAB04,6

M_BAB14,6

Modify B.Modify B.

M_RASB#

M_CASB#

M_WEB#

M_CS2_R#

M_CS3_R#

M_CKE1_R

M_CLK_DDR+4

M_CLK_DDR-4

M_CLK_DDR+6

M_CLK_DDR-6

1 2

C288

0.1U

2 1

12

M_AB13

2 1

R26010K

R25810K

C305

0.1U

3

C289

10U/6.3V/X5R

2 1

+V2.6

C382

+

@220U/4V

C285

0.1U

2 1

M_RASB#4,6

M_CASB#4,6

M_WEB#4,6

M_CS2_R#4,6

M_CS3_R#4,6

M_CKE1_R4,6

M_CLK_DDR+44

M_CLK_DDR-44

M_CLK_DDR+64

M_CLK_DDR-64

+V2.6

C312

+

220U/4V

C287

0.1U

2 1

Z0703

Z0704

2

91021223334364546575869708182929394113

CN3

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

3415162728383940515263647576878890103

C298

C301

0.1U

0.1U

2 1

2 1

2 1

197

199

112

111

110

109

108

107

106

105

102

101

115

100

117

116

134

148

170

184

133

147

169

183

118

120

119

121

122

160

158

123

124

200

C307

0.1U

99

12

26

48

62

78

11

25

47

61

77

71

73

79

83

72

74

80

84

96

95

35

37

89

91

85

86

97

98

1

VREF

2

VREF

VddSPD

VddID

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10 / AP

A11

A12

BA0

BA1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

RAS#

CAS#

WE#

CS0#

CS1#

CKE0

CKE1

CK0

CK0#

CK1

CK1#

CK2

CK2#

NC

NC/(RESET#)

NC/A13

NC/BA2

NC

NC

NC

2

1

114

131

132

143

144

155

156

157

167

168

179

180

191

192

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

M_D_R_0

5

DQ0

M_D_R_1

7

DQ1

M_D_R_2

13

DQ2

M_D_R_3

17

DQ3

M_D_R_4

6

DQ4

M_D_R_5

8

DQ5

M_D_R_6

14

DQ6

M_D_R_7

18

DQ7

M_D_R_8

19

DQ8

M_D_R_9

23

DQ9

M_D_R_10

29

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

104

125

126

137

138

149

150

159

161

162

173

174

185

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

195

SCL

193

SDA

194

SA0

196

SA1

198

SA2

VSS

A5792B-A0G16-N_H9.2

186

DDR_SO-DIM

M_D_R_11

M_D_R_12

M_D_R_13

M_D_R_14

M_D_R_15

M_D_R_16

M_D_R_17

M_D_R_18

M_D_R_19

M_D_R_20

M_D_R_21

M_D_R_22

M_D_R_23

M_D_R_24

M_D_R_25

M_D_R_26

M_D_R_27

M_D_R_28

M_D_R_29

M_D_R_30

M_D_R_31

M_D_R_32

M_D_R_33

M_D_R_34

M_D_R_35

M_D_R_36

M_D_R_37

M_D_R_38

M_D_R_39

M_D_R_40

M_D_R_41

M_D_R_42

M_D_R_43

M_D_R_44

M_D_R_45

M_D_R_46

M_D_R_47

M_D_R_48

M_D_R_49

M_D_R_50

M_D_R_51

M_D_R_52

M_D_R_53

M_D_R_54

M_D_R_55

M_D_R_56

M_D_R_57

M_D_R_58

M_D_R_59

M_D_R_60

M_D_R_61

M_D_R_62

M_D_R_63

SMB_CLK

SMB_DATA

+V3.3S

CHB Address : 0001H

UNIWILL COMPUTER CORP.

C300

0.1U

2 1

Project : P50CA0

SizeDocument NumberRev

3159

Date:Sheet of

DDR

731Monday, August 29, 2005

1

B2

Page 8

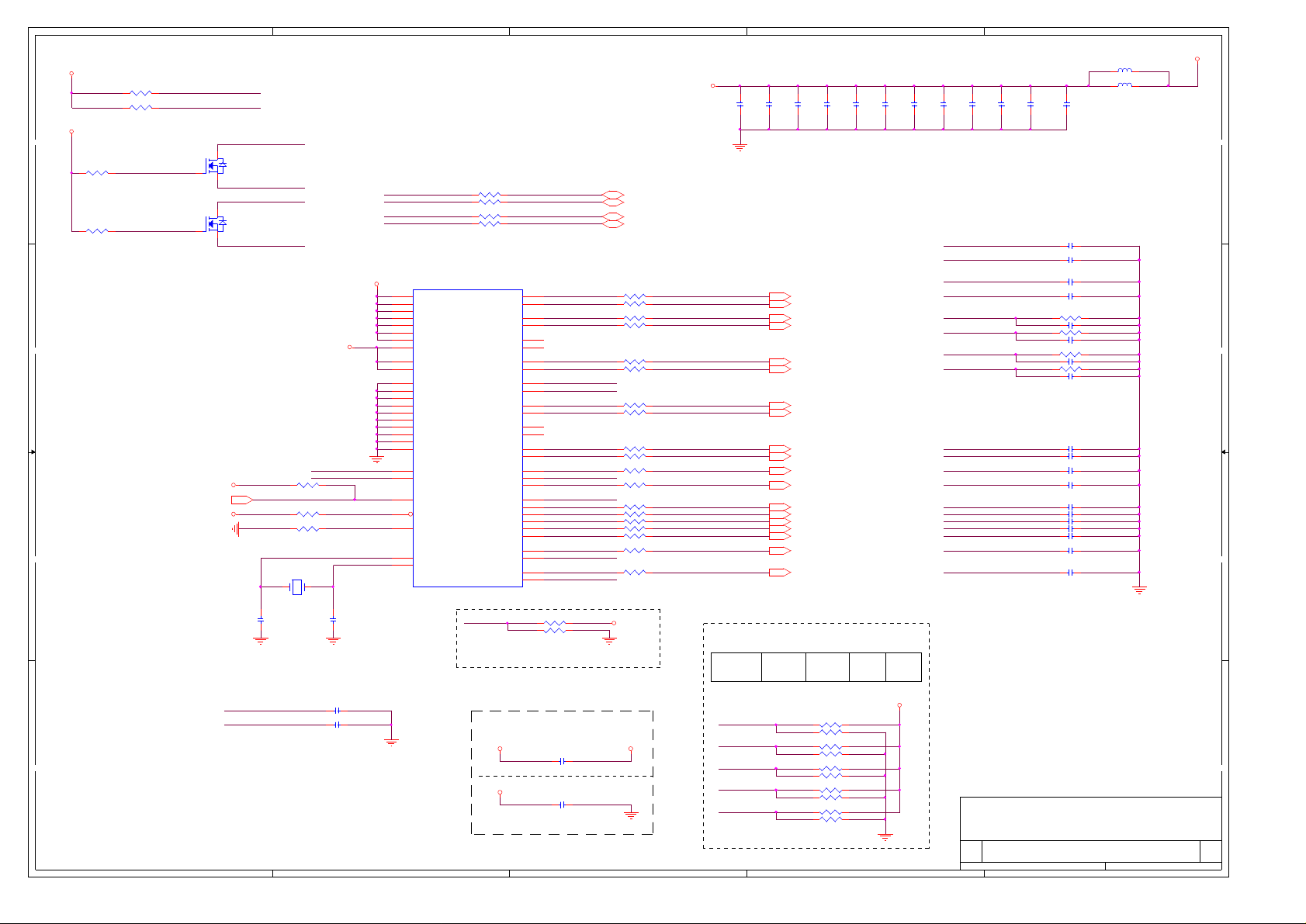

5

+V3.3S

R96@10K

1 2

R98@10K

1 2

+V5S

DD

R97

1 2

1 2

CC

BB

CK408_DATA_D

1K

R93

CK408_CLK_D

1K

SMB_DATA_CLKGEN

SMB_CLK_CLKGEN

D

G

S

D

G

S

+V3.3S_CLK

VR_PWRGD_CK410#

+V3.3S_CLK

SMB_DATA_SP

Q9

2N7002

SMB_DATA_CLKGEN

SMB_CLK_SP

Q8

2N7002

SMB_CLK_CLKGEN

R11410K

VR_PWRGD_CK410#

R1124.7K

R99475R/F

14.318MHz_DIP

C549

30P

2 1

+V3.3S_CLK

1 2

1 2

Y3

SMB_CLK_CLKGEN

SMB_DATA_CLKGEN

12

XTAL_IN

XTAL_OUT

C546

30P

2 1

Modify B:Place at Top side

Z0801

VR_PWRGD_CK410#

AA

5

C617@0.1U

C618@0.1U

+V3.3S_CLK

21

21

Z0801

Z0802

4

SMB_DATA_SP

SMB_CLK_SP

SMB_CLK_SP

SMB_DATA_SP

Modify B2

U17

1

VDDA

3

VDDREF

10

VDDPCI

16

VDDPCI

20

VDD

21

VDD48

26

VDDAGP

51

VDDCPU

39

VDDPCIEX

45

VDDPCIEX

2

GND

8

GNDREF

15

GNDPCI

19

GNDPCI

24

GND48

30

GNDAGP

32

GNDPCIEX

40

GNDPCIEX

50

GND

54

GNDCPU

31

SCLK

48

SDATA

9

VTTPWRGD/PD#

25

RESET#

49

IREF

6

X1

7

X2

ICS953201

4

Modify B2

R91@0R

1 2

R94@0R

1 2

R920R

1 2

R950R

1 2

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

PCIEXC0

PCIEXC1

PCIEXC2

PCIEXC3

PCIEXC4

PCIEXC5

AGPCLK0

FS4/AGPCLK1

AGPCLK2

FS2/PCI0

FS3/PCI1

FS0/REF0

FS1/REF1

SEL24_48#/24_48MHz

24_48MHz

Pin 23 Output Frequency select

0 : 48MHz / 1 : 24MHz

SMB_DATA

SMB_CLK

SMB_CLK_BAT_B

SMB_DATA_BAT_B

56

55

53

52

47

PCIEXT0

46

44

PCIEXT1

43

42

PCIEXT2

41

38

PCIEXT3

37

36

PCIEXT4

35

34

PCIEXT5

33

29

28

27

11

12

13

PCI2

14

PCI3

17

PCI4

18

PCI5

4

5

22

48MHz

23

R125@10K

1 2

R37210K

CPU1

CPU1#

CPU1_NB

CPU1#_NB

PECLK1

PECLK1#

PECLK2

PECLK2#

PECLK0

PECLK0#

PECLK5

PECLK5#

AGPCLK0

FS4

AGPCLK2

FS2

FS3

PCICLK2

PCICLK3

PCICLK4

PCICLK5

FS0

FS1

48MHz

24_48MHz

Stitching cap for HCLK_NB

+VCC_CORE

C840.01U

+V3.3S

C1200.01U

For CLK_CPU change layer

R34915R/F

1 2

R35015R/F

1 2

R35115R/F

1 2

R35215R/F

1 2

R35333R

1 2

R35433R

1 2

R35533R

1 2

R35633R

1 2

R35733R

1 2

R35833R

1 2

R34220R

1 2

R38010R

1 2

R37422R

1 2

R37522R

1 2

R37633R

1 2

R37733R

1 2

R37822R

1 2

R37322R

1 2

R37933R

1 2

+V3.3S_CLK

12

21

21

3

+V3.3S_CLK

SMB_DATA7,17

SMB_CLK7,17

SMB_CLK_BAT_B3,24

SMB_DATA_BAT_B3,24

+V1.5S

3

2

C543

C157

C154

0.1U

0.1U

2 1

2 1

CLK_CPU_BCLK+

CLK_CPU_BCLK-

CLK_NB_HCLK+

CLK_NB_HCLK-

CLK_PCIE_NEWCARD+

CLK_PCIE_NEWCARD-

CLK_PCIE_MXM+

CLK_PCIE_MXM-

CLK_PCIE_NB+

CLK_PCIE_NB-

VCLK_NB

VCLK_SB

CLKPCI_LANCLKPCI_LAN

CLKPCI_MPCI1

CLKPCI_1394

CLKPCI_EC

CLKPCI_SB

CLK14_SB_OSC

CLK48_USB

C542

0.1U

0.1U

2 1

2 1

CLK_CPU_BCLK+3

CLK_CPU_BCLK-3

CLK_NB_HCLK+9

CLK_NB_HCLK-9

CLK_PCIE_NEWCARD+14

CLK_PCIE_NEWCARD-14

CLK_PCIE_MXM+13

CLK_PCIE_MXM-13

CLK_PCIE_NB+10

CLK_PCIE_NB-10

VCLK_NB9

VCLK_SB16

CLKPCI_LAN22

CLKPCI_MPCI120

CLKPCI_139421

CLKPCI_EC24

CLKPCI_SB16

CLK14_SB_OSC17

CLK48_USB17

C156

C541

0.1U

0.1U

2 1

2 1

Modify B2 LF

Modify B2 LF

C552

0.1U

2 1

2 1

CLK_CPU_BCLK+

CLK_CPU_BCLK-

CLK_NB_HCLK+

CLK_NB_HCLK-

CLK_PCIE_MXM+

CLK_PCIE_MXM-

CLK_PCIE_NEWCARD+

CLK_PCIE_NEWCARD-

CLK_PCIE_NB+

CLK_PCIE_NB-

VCLK_NB

VCLK_SB

CLKPCI_MPCI1

CLKPCI_1394

CLKPCI_EC

CLKPCI_SB

CLK14_SB_OSC

CLK48_USB

C155

0.1U

CPU,AGP,PCI Frequency select

FS_[4:0]

10011

FS0

FS1

FS2

FS3

FS4

CPUPCIEXAGP

100.00

66.6733.33200.00

R11510K

R111@10K

R37110K

R126@10K

R113@10K

R11010K

R123@10K

R12410K

R12210K

R381@10K

1 2

1 2

1 2

1 2

1 2

12

12

12

12

12

2

PCI

+V3.3S

SizeDocument NumberRev

Date:Sheet of

1

L46QT2012RL030HC-3A

21

L47

21

QT2012RL030HC-3A

C555

C554

C553

C153

0.1U

0.1U

2 1

2 1

C52410P

C52510P

C526@10P

C527@10P

R7949.9R/F

C53010P

R7849.9R/F

C53110P

R8149.9R/F

C528@10P

R8049.9R/F

C529@10P

10U/10V

10U/10V

2 1

2 1

21

21

21

21

1 2

21

1 2

21

1 2

21

1 2

21

C53249.9R/F

21

C53349.9R/F

21

C52110P

21

C16610P

21

C172@10P

21

C171@10P

21

C170@10P

21

C169@10P

21

C168@10P

21

C173@10P

21

C167@10P

21

Modify B2 LF

Modify B2 LF

Modify B2 LF :

Add RW1 which is 10P near by NB(K8T890)

at "VCLK_NB".

UNIWILL COMPUTER CORP.

Project : P50CA0

CLK GeneratorB2

3159

831Monday, August 29, 2005

1

+V3.3S

Page 9

5

4

3

2

1

3

VLAD[0..15]

VLAD[0..15]16

UPSTB16

UPSTB#16

DNSTB16

DNSTB#16

UPCMD16

DNCMD16

VBE016

VPAR16

VCLK_NB8

PWROK_NB#16

PCI_RST#3,13,16,19,20,21,22,24

SUSST#16

AGP_BUSY#16

PM_SLP_S3#14,16,22,24

(LVREF_NB =>2.5V/4=0.625V)V-Link Voltage reference

LVREF_NB

12

R295

1K/F

R2923K/F

C3660.1U

C386

0.1U

2 1

1 2

+V2.5S

21

(Layout place near to K8T890CE)

V-Link Compensation

LCOMPP

2/24 modify to 360R

R296360R/F

1 2

(Layout place near to K8T890CE)

Host CPU Compensation

HTRCOMPN

HTRTCOMP

HTRCOMPP

R32349.9R/F

1 2

R325100R/F

1 2

R6749.9R/F

1 2

+V1.2S

(Layout place near to K8T890CE)

PM_SLP_S3#

TESTIN_NB

DFTIN_NB

TCLK600

DEBUG

RSVD5

RSVD6

RSVD3

RSVD4

RSVD7

RSVD0

RSVD1

RSVD2

HTSTOPNB#

HTSTOPSB#

R2974.7K

1 2

R2984.7K

1 2

R3071K

1 2

R3061K

1 2

RN531K-8P4R

8

7 2

6

5

RN521K-8P4R

8

7 2

6

5

R335680R

1 2

R334680R

1 2

G

Q37

SI2301BDS

D S

1

3

4

1

3

4

Modify.B2

+V1.5S

+V2.5S

+V2.5S

UNIWILL COMPUTER CORP.

Project : P50CA0

SizeDocument NumberRev

3159

2

Date:Sheet of

K8T890CE-HOST & VLINK

931Monday, August 29, 2005

1

B2

CADIP[0..15]3

DD

CADIN[0..15]3

CADOP[0..15]3

CC

CADON[0..15]3

BB

CLKIP03

CLKIP13

CLKIN03

CLKIN13

CLKOP03

CLKOP13

CLKON03

CLKON13

CTLOP03

CTLON03

HTSTOPSB#3,16,23

HTSTOPNB#3

CTLIP03

AA

CTLIN03

CLK_NB_HCLK+8

CLK_NB_HCLK-8

CADIP[0..15]

CADIN[0..15]

CADOP[0..15]

CADON[0..15]

5

CLKIP0

CLKIP1

CLKIN0

CLKIN1

CLKOP0

CLKOP1

CLKON0

CLKON1

CTLOP0

CTLON0

HTSTOPSB#

HTSTOPNB#

HTRCOMPP

HTRCOMPN

HTRTCOMP

CTLIP0

CTLIN0

CLK_NB_HCLK+

CLK_NB_HCLK-

CADIP0

CADIP1

CADIP2

CADIP3

CADIP4

CADIP5

CADIP6

CADIP7

CADIP8

CADIP9

CADIP10

CADIP11

CADIP12

CADIP13

CADIP14

CADIP15

CADIN0

CADIN1

CADIN2

CADIN3

CADIN4

CADIN5

CADIN6

CADIN7

CADIN8

CADIN9

CADIN10

CADIN11

CADIN12

CADIN13

CADIN14

CADIN15

CADOP0

CADOP1

CADOP2

CADOP3

CADOP4

CADOP5

CADOP6

CADOP7

CADOP8

CADOP9

CADOP10

CADOP11

CADOP12

CADOP13

CADOP14

CADOP15

CADON0

CADON1

CADON2

CADON3

CADON4

CADON5

CADON6

CADON7

CADON8

CADON9

CADON10

CADON11

CADON12

CADON13

CADON14

CADON15

V2

U1

R1

N1

M2

K2

V5

U4

R4

N4

M5

K5

V3

P1

M1

M3

K1

K3

U5

U3

R5

R3

N3

A21

C19

A19

C17

C15

A15

C13

A13

C20

E20

C18

E18

E16

C14

E14

C12

A20

B19

A18

B17

B15

A14

B13

A12

D20

E19

D18

E17

E15

D14

E13

D12

P2

P5

P3

N5

A17

C16

A16

D16

C11

B11

V1

W1

B9

A9

A8

H1

B25

A25

T2

L1

T5

L4

T1

T3

L5

L3

J4

J1

U13A

HTTCAD0+

HTTCAD1+

HTTCAD2+

HTTCAD3+

HTTCAD4+

HTTCAD5+

HTTCAD6+

HTTCAD7+

HTTCAD8+

HTTCAD9+

HTTCAD10+

HTTCAD11+

HTTCAD12+

HTTCAD13+

HTTCAD14+

HTTCAD15+

HTTCAD0HTTCAD1HTTCAD2HTTCAD3HTTCAD4HTTCAD5HTTCAD6HTTCAD7HTTCAD8HTTCAD9HTTCAD10HTTCAD11HTTCAD12HTTCAD13HTTCAD14HTTCAD15-

HTRCAD0+

HTRCAD1+

HTRCAD2+

HTRCAD3+

HTRCAD4+

HTRCAD5+

HTRCAD6+

HTRCAD7+

HTRCAD8+

HTRCAD9+

HTRCAD10+

HTRCAD11+

HTRCAD12+

HTRCAD13+

HTRCAD14+

HTRCAD15+

HTRCAD0HTRCAD1HTRCAD2HTRCAD3HTRCAD4HTRCAD5HTRCAD6HTRCAD7HTRCAD8HTRCAD9HTRCAD10HTRCAD11HTRCAD12HTRCAD13HTRCAD14HTRCAD15-

HTTCLK0+

HTTCLK1+

HTTCLK0HTTCLK1-

HTRCLK0+

HTRCLK1+

HTRCLK0HTRCLK1-

HTRCTL+

HTRCTL-

HTSTOPI#

HTSTOPO#

HTRCOMPP

HTRCOMPN

HTRTCOMP

HTTCTL+

HTTCTL-

HCLK+

HCLK-

VIA K8T890CE 1/5

V-Link

HOST

NC/(TVCLK/DVP0CLK)

NC/(TVCLKR/DVP0DET)

4

VD10

VD11

VD12

VD13

VD14

VD15

UPSTB+

UPSTB-

DNSTB+

DNSTBUPCMD

DNCMD

VBE#

VPAR

VLCOMPP

VLVREF

VCLK

PWROK

RESET#

SUSST#

BUSY#

TESTIN#

DFTIN#

TCLK

TCLK600

DEBUG

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

NC/AR

NC/AG

NC/AB

NC/HSYNC

NC/VSYNC

NC/SPCLK2

NC/SPD2

NC/XIN

NC/RSET

NC/BISTIN

NC/INTA#

NC/GPO0

NC/GPOUT

NC/CONFIG1

NC/CONFIG2

NC/CONFIG3

NC/ENVDD

NC/ENBLT

NC/(TVD0/DVP0D0)

NC/(TVD1/DVP0D1)

NC/(TVD2/DVP0D2)

NC/(TVD3/DVP0D3)

NC/(TVD4/DVP0D4)

NC/(TVD5/DVP0D5)

NC/(TVD6/DVP0D6)

NC/(TVD7/DVP0D7)

NC/(TVD8/DVP0D8)

NC/(TVD9/DVP0D9)

NC/(TVD10/DVP0D10)

NC/(TVD11/DVP0D11)

NC/(TVVS/DVP0VS)

NC/(TVHS/DVP0HS)

NC/(TVDE/DVP0DE)

K8T890CD

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VD8

VD9

VLAD1

R34

VLAD2

M33

VLAD3

L32

VLAD4

T32

VLAD5

R32

VLAD6

K33

VLAD7

L34

VLAD8

T33

VLAD9

U32

VLAD10

K32

VLAD11

J32

VLAD12

U34

VLAD13

V33

VLAD14

J34

VLAD15

J33

UPSTB

M32

UPSTB#

N32

DNSTB

N34

DNSTB#

N33

UPCMD

K34

DNCMD

M34

VBE0

R33

VPAR

T34

LCOMPP

V34

LVREF_NB

P32

VCLK_NB

C28

PWROK_NB#

G32

PCI_RST#

H32

SUSST#

G33

AGP_BUSY#

E34

TESTIN_NB

E32

DFTIN_NB

F32

TCLK

D34

TCLK600

B28

DEBUG

A28

RSVD0

A26

RSVD1

B26

RSVD2

C26

RSVD3

D26

RSVD4

E26

RSVD5

A27

RSVD6

C27

RSVD7

D27

TZ0901

AF2

TZ0902

AF1

TZ0903

AE1

TZ0904

AG1

TZ0905

AG2

TZ0906

AH1

TZ0907

AH2

TZ0908

AJ1

TZ0909

AF3

TZ0910

AG3

TZ0911

AJ2

TZ0912

AJ3

TZ0913

AH3

TZ0914

AM3

TZ0915

AM4

TZ0916

AN2

TZ0917

AP1

TZ0918

AN1

TZ0919

AH4

TZ0920

AJ4

TZ0921

AK3

TZ0922

AK2

TZ0923

AK1

TZ0924

AK4

TZ0925

AL1

TZ0926

AL2

TZ0927

AH5

TZ0928

AH6

TZ0929

AJ5

TZ0930

AJ6

TZ0931

AM1

TZ0932

AL3

TZ0933

AM2

TZ0934

AL4

TZ0935

AK5

VLAD0

P34

Page 10

5

4

3

2

1

DD

CC

BB

PE0_TX+[0..15]13

PE0_TX-[0..15]13

PE1_TX+014

PE1_TX-014

PE1_RX+014

PE1_RX-014

PE0_TX+[0..15]

PE0_TX-[0..15]

PE0_TX+0

PE0_TX+1

PE0_TX+2

PE0_TX+3

PE0_TX+4

PE0_TX+5

PE0_TX+6

PE0_TX+7

PE0_TX+8