Page 1

Am41DL32x4G

Data Sheet

July 2003

The following document specifies Spansion memory products that are now offered by both Advanced

Micro Devices and Fujitsu. Although the docu ment is ma rked with the name o f the comp any that o riginally developed the specification, these products will be offered to customers of both AMD and

Fujitsu.

Continuity of Specifications

There is no change to this datasheet as a result of offering the device as a Spansion product. Any

changes that have been made are the result of normal datasheet improvement and are noted in the

document revision summary, where supported. Future routine revisions will occur when appropriate,

and changes will be noted in a revision summary.

Continuity of Ordering Part Numbers

AMD and Fujitsu continue to support existing part numbers beginning with “Am” and “MBM”. To order

these products, please use only the Ordering Part Numbers listed in this document.

For More Information

Please contact your local AMD or Fujitsu sales office for additional information about Spansion

memory solutions.

Publication Number 25559 Revision A Amendment 0 Issue Date November 12, 2001

Page 2

PRELIMINARY

Am41DL32x4G

Stacked Multi-Chip Package (MCP) Flash Memory and SRAM

32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash

Memory and 4 Mbit (512 K x 8-Bit/256 K x 16- Bit) Static RAM

DISTINCTIVE CHARACTERISTICS

MCP Features

■ Power supply voltage of 2.7 to 3.3 volt

■ High performance

— Access time as fast as 70 ns

■ Package

— 73-Ball FBGA

■ Operating Temperatu r e

— –40°C to +85°C

Flash Memory Features

ARCHITECTURAL ADVANTAGES

■ Simultaneous Read/Write operations

— Data can be continuously read from one bank while

executing erase/program functions in other bank

— Zero latency between read and write operations

■ Secured Silicon (SecSi) Sector: Extra 256 Byte sector

— Factory locked and identifiable: 16 bytes available for

secure, random factory Electronic Serial Number; verifiable

as factory locked through autoselect function.

— Customer lockable: Sector is one-time programmable. Once

locked, data cannot be changed

■ Zero Power Operation

— Sophisticated power management circuits reduce power

consumed during inactive periods to nearly zero

■ Top or bottom boot block

■ Manufactured on 0.17 µm process technology

■ Compatible with JEDEC standards

— Pinout and software compatible with single-power-supply

flash standard

PERFORMANCE CHARACTERISTICS

■ High performance

— Access time as fast as 70 ns

— Program time: 4 µs/word typical utilizing Accelerate function

■ Ultra low power consumption (typical values)

— 2 mA active read current at 1 MHz

— 10 mA active read current at 5 MHz

— 200 nA in standby or automatic sleep mode

■ Minimum 1 million write cycles guaranteed per sector

■ 20 Year data retentio n at 12 5 °C

— Reliable operation for the life of the system

SOFTWARE FEATURES

■ Data Ma na gement Softw ar e (D M S)

— AMD-supplied software manages data programming and

erasing, enabling EEPROM emulation

— Eases sector erase limitations

■ Supports Common Flash Memory Interface (CFI)

■ Erase Suspend/Erase Resume

— Suspends erase operations to allow programming in same

bank

■ Data# Polling and Toggle Bits

— Provides a software method of detecting the status of

program or erase cycles

■ Unlock Bypass Program comma nd

— Reduces overall programming time when issuing multiple

program command sequences

HARDWARE FEATURES

■ Any combination of sectors can be erased

■ Ready/B u s y# ou tp u t (RY/BY #)

— Hardware method for detecting program or erase cycle

completion

■ Hardware reset pin (RESET#)

— Hardware method of resetting the internal state machine to

reading array data

■ WP#/ACC input pin

— Write protec t (WP# ) func ti on all ows p rot ecti on of two o ute rmost

boot secto rs, reg ardle ss of s ect or prot ect stat us

— Acceleration (ACC) function accelerates program timing

■ Sector protection

— Hardware method of locking a sector, either in-system or

using programming equipment, to prevent any program or

erase operation within that sector

— Temporary Sector Unprotect allows changing data in

protected sectors in-system

SRAM Features

■ Power dissipation

— Operating: 22 mA maximum

— Standby: 10 µA maximum

■ CE1s# an d CE 2s Chip S ele ct

■ Power down features using CE1s# and CE2s

■ Data retention supply voltage: 1.5 to 3.3 volt

■ Byte data control: LB#s (DQ7–DQ0), UB#s (DQ15–DQ8)

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you ev aluate thi s product. AMD res erves the righ t to change or dis continue wor k on this propos ed

product without notice.

Refer to AMD’s Website (www.amd.com) for the la test information.

Publication# 25559 Rev: A Amendment/0

Issue Date: November 12, 2001

Page 3

PRELIMINARY

GENERAL DESCRIPTION

Am29DL32xG Features

The Am29DL322G/323G/324G consists of 32 megabit,

3.0 volt-only flash memory devices, organized as

2,097,152 w or ds of 16 b its ea c h or 4, 194 ,30 4 bytes of

8 bits each. Word mode data appears on DQ0–DQ15;

byte mode data appears on DQ7–DQ0. The dev i ce is

designed to be programmed in-system with the standard 3.0 vo lt V

supply, and can also be programmed

CC

in standard EPROM programmers.

The devices ar e avai la ble wit h ac ces s times of 85 an d

70 ns. The device is offered in a 73-ball FBGA package. Standard control pins—chip en abl e (CE# f), write

enable (WE#), and output enable (OE#)—control no rmal read and write operations, and avoid bus

contention is sues .

The devices requires only a single 3.0 volt power

supply for both read and write functions. Internally

generate d a nd regu la ted vo ltages are provided for th e

program and eras e ope r ations .

Simultaneous Read/W rite Oper ations with

Zero Latency

The Simulta neous Rea d/Write archit ecture prov ides

simultaneous operation by di viding th e memory

space into two banks. The device can improve overall

system performance by allowing a host system to program or erase in one bank, then immediately and

simultaneo us ly re ad from t he oth er b an k, with ze ro l atency. This releases the system fr om waiting for the

completion of program or erase operations.

The Am29DL32xG device family uses multiple bank

architectures to provide flexibility for different applications. Three devices are av ailable with the f ollowing

bank sizes:

Device Bank 1 Bank 2

DL322 4 28

DL323 8 24

DL324 16 16

The Secured Silicon (SecSi) Sector is an extra 256

byte secto r capa ble of bei ng pe rmanen tly locked by

AMD or customers. The SecSi Secto r Indicator Bit

(DQ7) is permanently set to a 1 if the part is fa c tory

locked, and set to a 0 if customer lockable. Thi s

way, customer lockable parts can never be used to replace a factory locked part.

Factory lo cked par ts provide several options. Th e

SecSi Sector may store a secure, random 16 byte

ESN (Electronic Serial Number). Customer Lockable

devices are one-time programma ble and one-time

lockable.

DMS (Data Managemen t Software) allows systems

to easily take adva ntage of the ad van ced ar chitec ture

of the simultaneous read/write product line by allowing

removal of EEPROM devices. DMS will also allow the

system software to be simplified , as it will perform all

functions necessary to modify data in file structur es,

as opposed to single-byte modifications. To write or

update a particular piece of data (a phone number or

configuration data, for example), the user only needs

to state which piece of da ta is to be update d, and

where the up date d data is locate d in the syste m. Thi s

is an advantage compared to system s where

user-written software must keep track of the old data

location, statu s, logical to ph ysical tr anslati on of the

data onto the F lash mem ory device (or memory devices), and more. Using DMS , user-writte n software

does not need to interface with the Flash memory directly. Instead, the user's software accesses the Flas h

memory by c alli ng one of o nl y si x func ti on s. AM D pro vides this software to simplify system design and

software integration efforts.

The device offers complete compatibility with the

JEDEC single-power-supply Flash command set

standard. Commands are written to the command

register using standard microprocessor write timings.

Reading data out of the device is similar to reading

from other Flash or EPROM devices.

The host system can dete ct whether a program o r

erase operation is complete by using the device sta-

tus bits: RY/BY# pin, DQ7 (Data# Polling) and

DQ6/DQ2 (toggle bits ). After a program or erase cycle

has been completed, the device automatically returns

to reading array data.

The sector erase archit ecture allows memory sectors to be erased and reprog ramme d withou t affecting

the data contents of other sectors. The device is fully

erased when shipped from the factory.

Hardware data protection measures include a l ow

detector th at autom atical ly inhibi ts write opera-

V

CC

tions during power transitions. The hardware sector

protection feature disables both program and erase

operations in any combination of the sectors of memory. This can be achieved in-system or via

programming equipment.

The device offers two power-sa ving feature s. When

addresses have been stabl e for a speci fied am ount of

time, the d evice enters the aut omatic sle ep mode.

The system can also place the device into the

standby mo de. Power con sumptio n is greatly reduced in both modes.

2 Am41DL32x4G November 12, 2001

Page 4

PRELIMINARY

TABLE OF CONTENTS

Product Selector Guide . . . . . . . . . . . . . . . . . . . . . 5

MCP Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . 5

Flash Memory Block Diagram. . . . . . . . . . . . . . . . 6

Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . .7

Special Handling Instructions for FBGA Package ....................7

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Ordering Information . . . . . . . . . . . . . . . . . . . . . . .9

Device Bus Operations . . . . . . . . . . . . . . . . . . . . 10

Table 1. De vi ce Bus Operations — F l ash Word Mode, CI O f = VIH;

SRAM Word Mode, CIOs = V

Table 2. De vi ce Bus Operations — F l ash Word Mode, CI O f = V

SRAM Byte Mode, CIOs = V

Table 3. De vi ce Bus Operations — Flash Byte Mode , CI Of = V

SRAM Word Mode, CIOs = V

Table 4. Device Bus Operations—Flash Byte Mode, CIOf = V

Byte Mode, CIOs = V

SS

Word/Byte Configuration ........................................................15

Requirements for Reading Array Data ...................................15

Writing Commands/Command Sequences ............................15

Accelerated Program Operation ..........................................15

Autoselect Functions ...........................................................15

Simultaneous Read/Write Operations with Zero Latency .......15

Standby Mode ........................................................................16

Automatic Sleep Mode .................................. ....................... ..16

RESET#: Hardware Reset Pin ...............................................16

Output Disable Mode ..............................................................16

Table 5. Device Bank Division ........................................................16

Table 6. Top Boot Sector Addresses .............................................17

Top Boot SecSi Sector Addresses............................................. 18

Bottom Boot SecSi Sector Addresses................ ............... ......... 20

Autoselect Mode .....................................................................21

Sector/Sector Block Protection and Unprotection .................. 2 1

Table 10. Top Boot Sector/Sector Block Addresses

for Protection/Unprotection .............................................................21

Write Protect (WP#) ................................................................21

Temporary Sector/Sector Block Unprotect .............................22

Figure 1. Temporary Sector Unprotect Operation........................... 22

Figure 2. In-System Sector/Sector Block Protect and Unprotect Algo-

rithms.............................................................................................. 23

SecSi (Secured Silicon) Sector Flash Memory Region ..........24

Factory Locked: SecSi Sector Programmed and Protected At

the Factory ..........................................................................24

Customer Lockable: SecSi Sector NOT Programmed or Pro-

tected At the Factory ........................................................... 2 4

Hardware Data Protection ......................................................24

Write Inhibit ...........................................................24

Low V

CC

Write Pulse “Glitch” Protection ............................................24

Logical Inhibit ......................................................................25

Power-Up Write Inhibit .........................................................25

Common Flash Memory Interface (CFI) . . . . . . .25

Table 11. CFI Query Identification String........................................ 25

System Interface String................................................................... 26

Table 13. Device Geometry Definition............................................ 26

Table 14. Primary Vendor-Specific Extended Query...................... 27

Command Definitions . . . . . . . . . . . . . . . . . . . . . .28

Reading Array Data ................................................................28

Reset Command .....................................................................28

..................................................... 11

CC

......................................................12

SS

.....................................................13

CC

..................................................................14

;

IH

;

SS

; SRAM

IL

Autoselect Command Sequence ............................................28

Enter SecSi Sector/Exit SecSi Sector Command Sequence ..29

Byte/Word Program Command Sequence .............................29

Unlock Bypass Command Sequence ..................................29

Figure 3. Program Operation......................................................... 30

Chip Erase Command Sequence ...........................................30

Sector Erase Command Sequence ........................................30

Erase Suspend/Erase Resume Commands ...........................31

Figure 4. Erase Operation.............................................................. 31

Table 15. Command Definitions (Flash Word Mode)...................... 32

Table 16. Autoselect Device IDs (Word Mode) ..............................32

Table 17. Command Definitions (Flash Byte Mode)....................... 33

Table 18. Autoselect Device IDs (Byte Mode) ...............................33

Write Operation Status . . . . . . . . . . . . . . . . . . . . 34

DQ7: Data# Polling ..................... ....................... .....................34

Figure 5. Data# Polling Algorithm .................................................. 34

RY/BY#: Ready/Busy# ............................................................35

DQ6: Toggle Bit I ....................................................................35

Figure 6. Toggle Bit Algorithm........................................................ 35

DQ2: Toggle Bit II ...................................................................36

Reading Toggle Bits DQ6/DQ2 ...............................................36

DQ5: Exceeded Timing Limits ................................................36

DQ3: Sector Erase Timer .......................................................36

Table 19. Write Operation Status ...................................................37

Absolute Maximum Ratings . . . . . . . . . . . . . . . . 38

Operating Ranges. . . . . . . . . . . . . . . . . . . . . . . . . 38

Industrial (I) Devices ............................................................38

f/VCCs Supply Voltage ........................ ...... ...... ...............38

V

CC

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 39

CMOS Compatible ............................ ..... ....................... ...... ....39

SRAM DC and Operating Characteristics . . . . . 40

Zero-Power Flash .................................................................41

Figure 9. I

Currents)........................................................................................ 41

Figure 10. Typical I

Current vs. Time (Showing Ac tiv e and Auto mati c Sle ep

CC1

vs. Frequency............................................ 41

CC1

Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 11. Test Setup.................................................................... 42

Table 20. Test Specifications .........................................................42

Key To Switching Waveforms . . . . . . . . . . . . . . . 42

Figure 12. Input Waveforms and Measurement Levels................. 42

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 43

SRAM CE#s Timing ................................................................43

Figure 13. Timing Diagram for Alter nating Between SRAM to Fl ash. .

43

Flash Read-Only Operations .................................................44

Figure 14. Read Operation Timings............................................... 44

Hardware Reset (RESET#) ....................................................45

Figure 15. Reset Timings........................ ............... ............... ......... 45

Flash Word/Byte Configuration (CIOf) ....................................46

Figure 16. CIOf Timings for Read Operations................................ 46

Figure 17. CIOf Timings for Write Operations................................ 46

Flash Erase and Program Operations ....................................47

Figure 18. Program Operation Timings.......................................... 48

Figure 19. Accelerated Program Timing Diagram.......................... 4 8

Figure 20. Chip/Sector Erase Operation Timings.......................... 4 9

Figure 21. Back-to-back Read/Write Cycle Timings...................... 50

Figure 22. Data# Polling Timings (During Embedded Algorithms). 50

Figure 23. Toggle Bit Timings (During Embedded Algorithms)...... 5 1

November 12, 2001 Am41DL32x4G 3

Page 5

PRELIMINARY

Figure 24. DQ2 vs. DQ6.................................................................. 51

Temporary Sector/Sector Block Unprotect .............................52

Figure 25. Te m porary Sector/Se ct or Block Unprotect

Timing Diagram................................. ............... ............... ............... . 52

Figure 26. Se ct or/Sector Block P rotect and Unprote ct

Timing Diagram................................. ............... ............... ............... . 53

Alternate CE#f Controlled Erase and Program Operations ....54

Figure 27. Flash Alternate CE#f Controlled Write (Erase/Program) Op-

eration Timings........... ............... .... ............... ............... ............... ..... 55

SRAM Read Cycle ..................................................................56

Figure 28. SR AM Read Cycle—Address Controlled....................... 56

Figure 29. SRAM Read Cycle......................................................... 57

SRAM Write Cycle ..................................................................58

Figure 30. SR AM W r ite Cycle—WE# Control............. ............... ..... 58

Figure 31. SRAM Write Cycle—CE1#s Control ............................. 5 9

Figure 32. SRAM Write Cycle—UB#s and LB#s Control............... 60

Flash Erase And Programming Performance ........................61

Flash Latchup Characteristics. . . . . . . . . . . . . . . 61

Package Pin Capacitance . . . . . . . . . . . . . . . . . . 61

Flash Data Retention . . . . . . . . . . . . . . . . . . . . . . 61

SRAM Data Retention . . . . . . . . . . . . . . . . . . . . . 62

Figure 33. CE1#s Controlled Data Retention Mode....................... 62

Figure 34. CE2s Controlled Data Retention Mode......................... 62

Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . 63

FLB073—73-Ball Fine-Pitch Grid Array 8 x 11.6 mm .............63

Revision Summary . . . . . . . . . . . . . . . . . . . . . . . . 64

Revision A (October 25, 2001) ...............................................64

4 Am41DL32x4G November 12, 2001

Page 6

PRELIMINARY

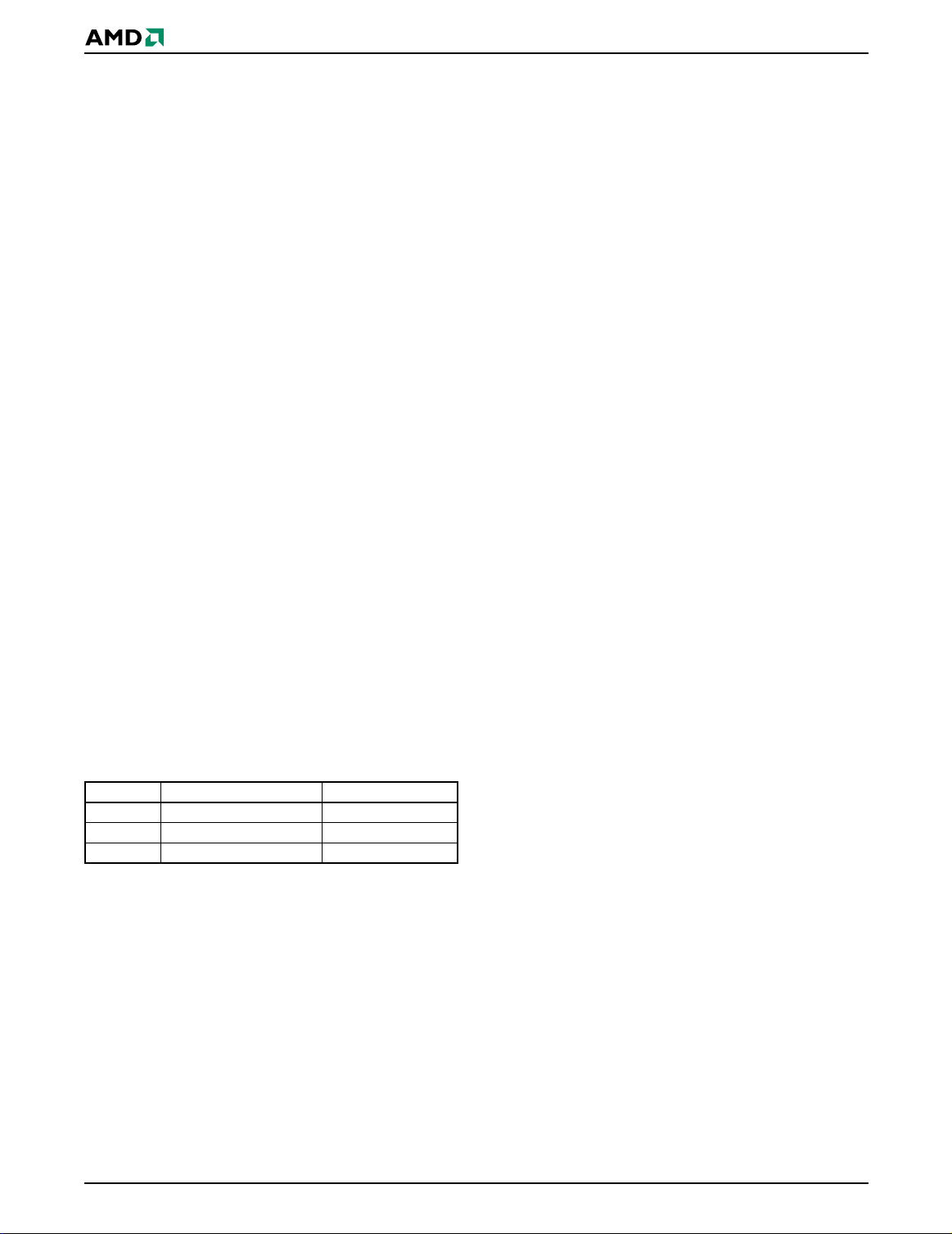

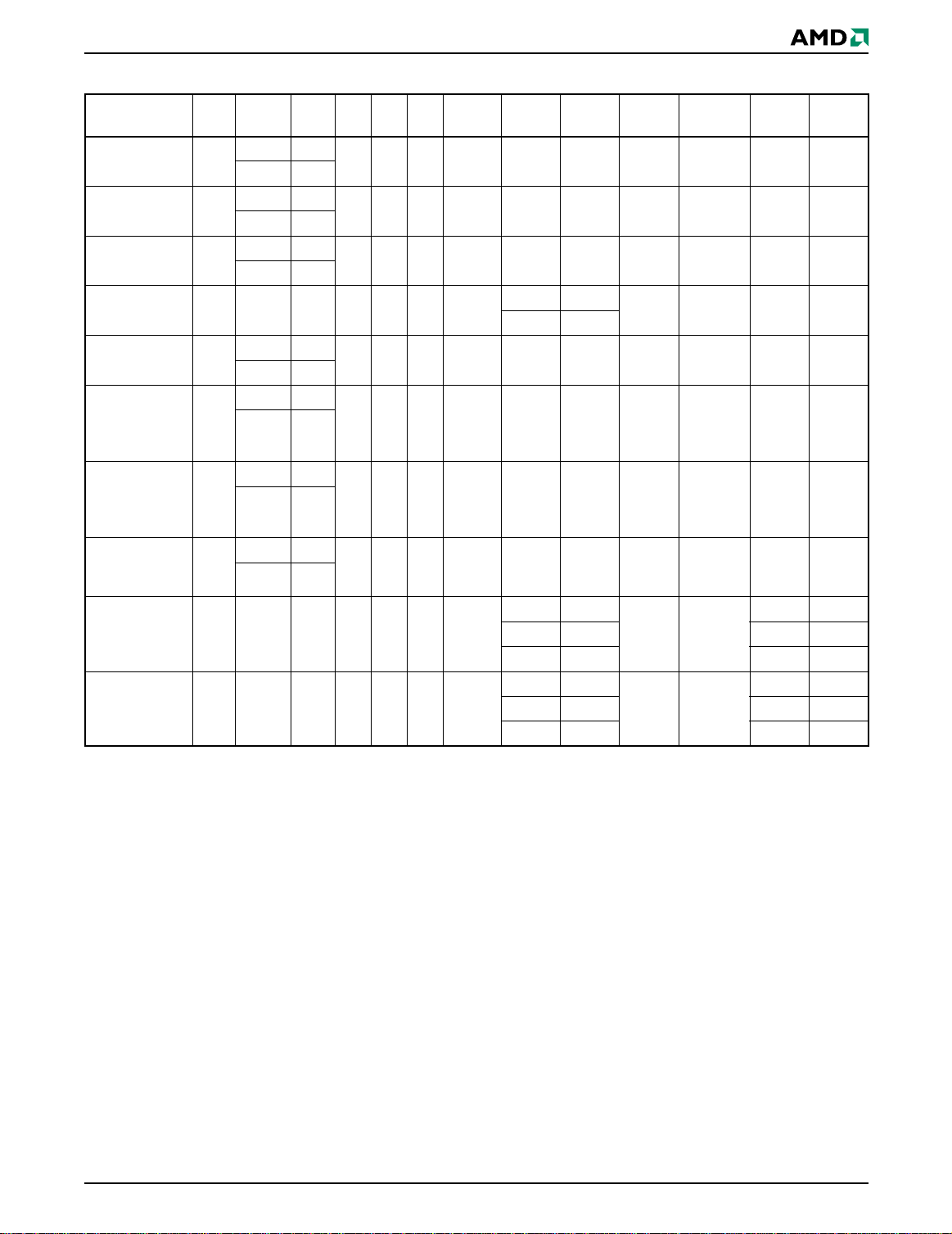

PRODUCT SELECTOR GUIDE

Part Number Am41DL32x4G

Speed

Options

Max Access Time (ns) 70 85 70 85

CE# Access (ns) 70 85 70 85

OE# Access (ns) 30 40 35 45

Standard V oltage Ra nge:

V

= 2.7–3.3 V

CC

Flash Memory SRAM

70 85 70 85

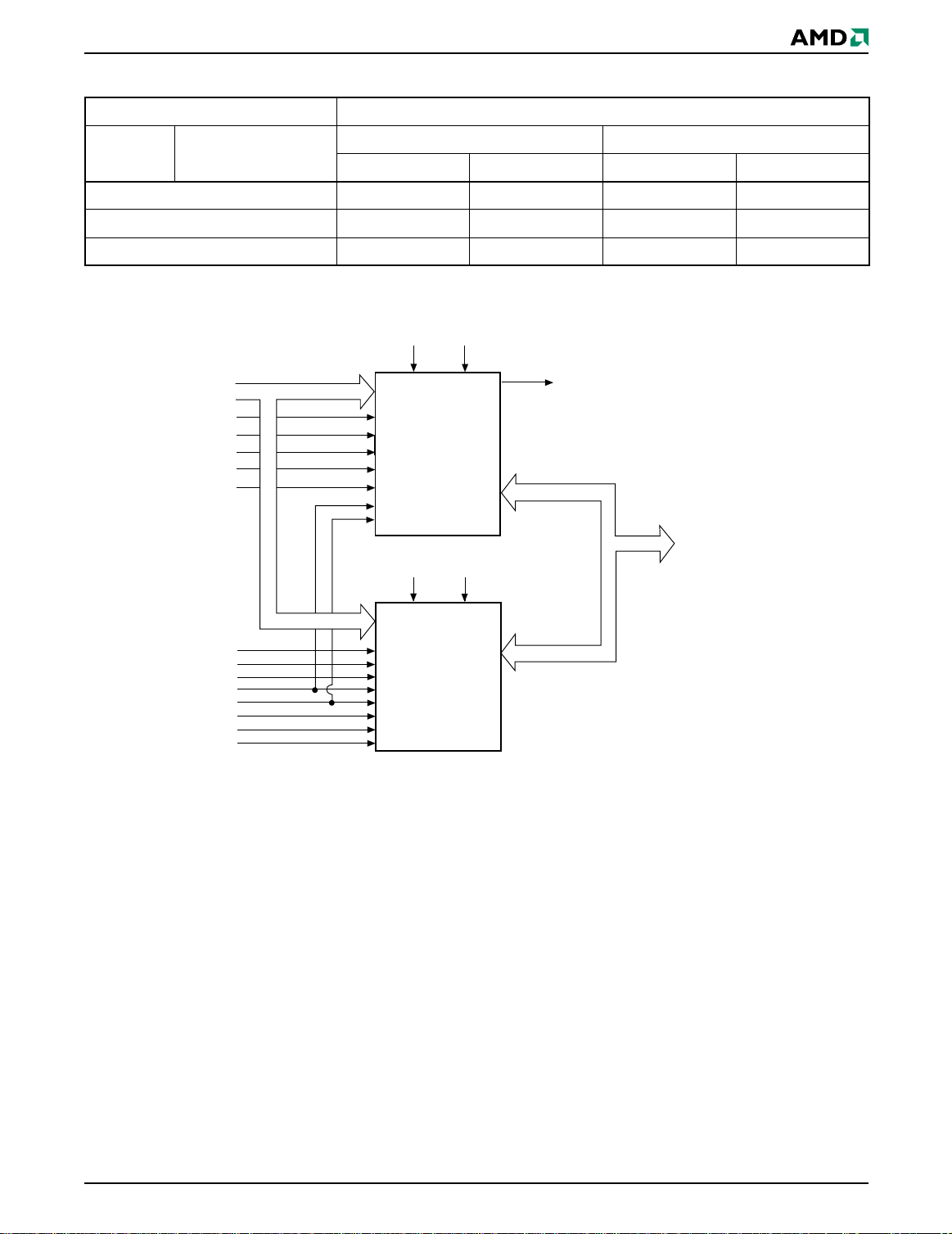

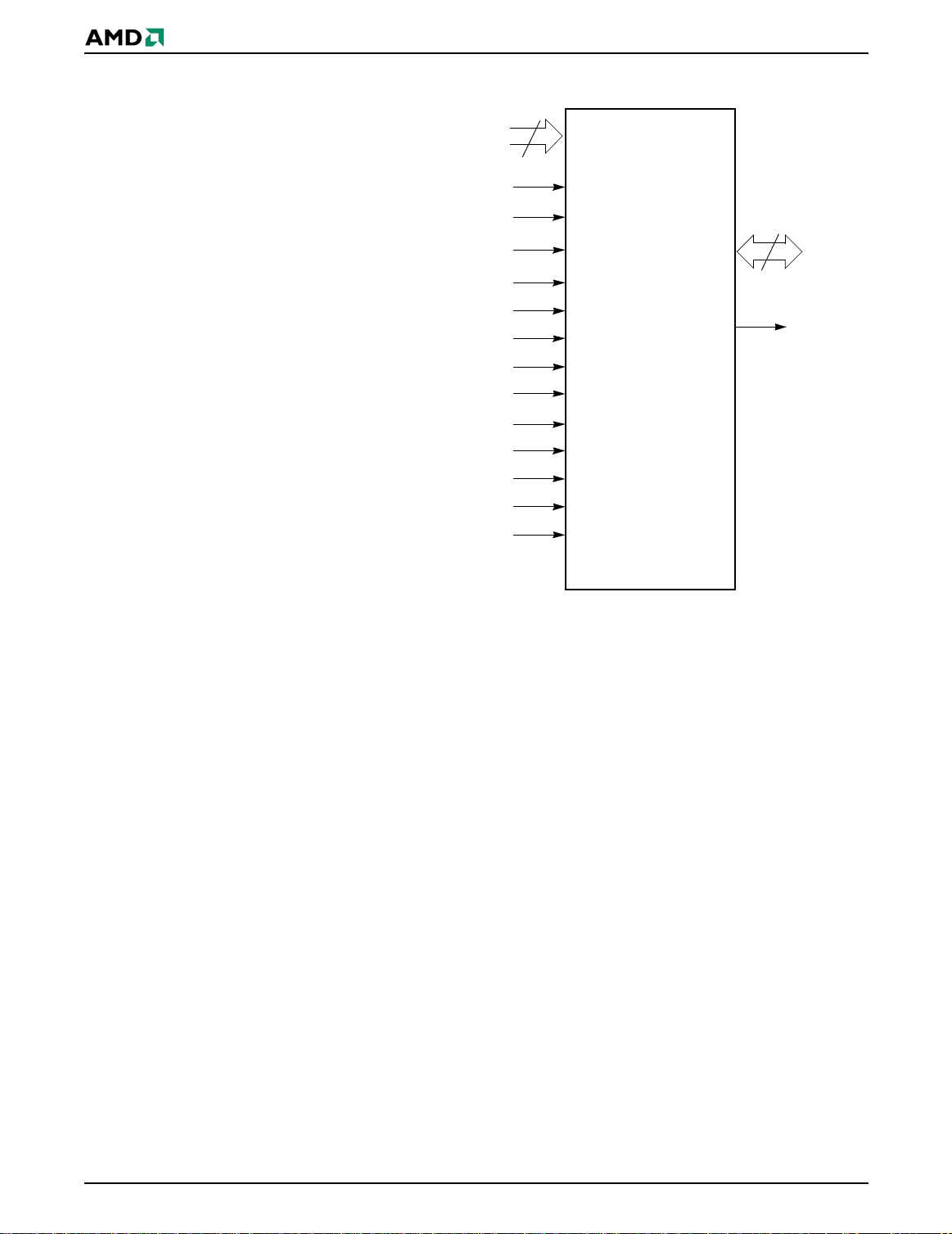

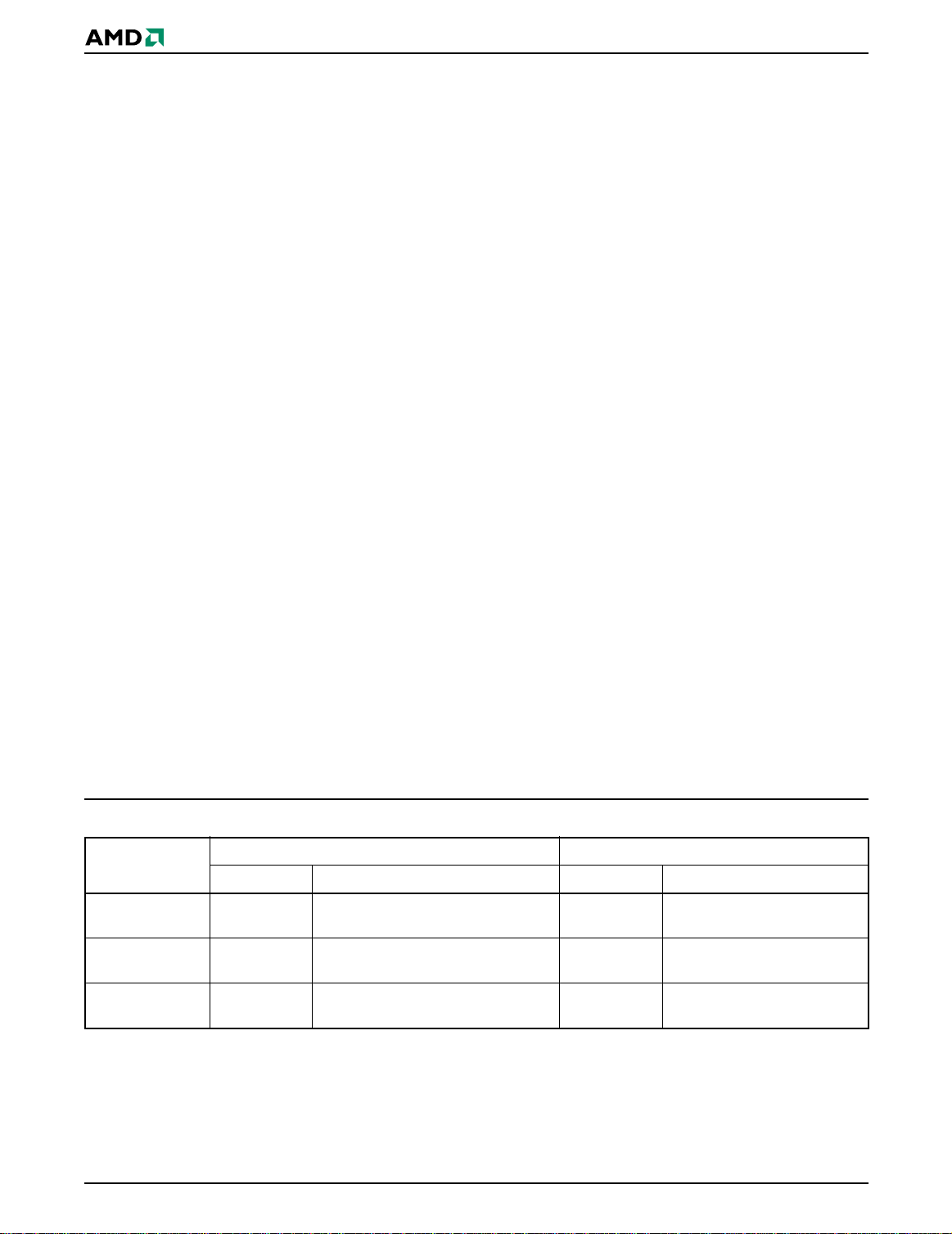

MCP BLOCK DIAGRAM

32 M Bit

CCQ

V

SS

VSS/V

DQ15/A-1 to DQ0

SSQ

RY/BY#

DQ15/A-1 to DQ0

A20 to A0

A

–

WP#/ACC

RESET#

CE#f

CIOf

VCCf

A20 to A0

1

Flash Memory

VCCs/V

SA

LB#s

UB#s

WE#

OE#

CE1#s

CE2s

CIOs

A0 to A19

A17 to A0

4 M Bit

Static RAM

DQ15/A-1 to DQ0

November 12, 2001 Am41DL32x4G 5

Page 7

PRELIMINARY

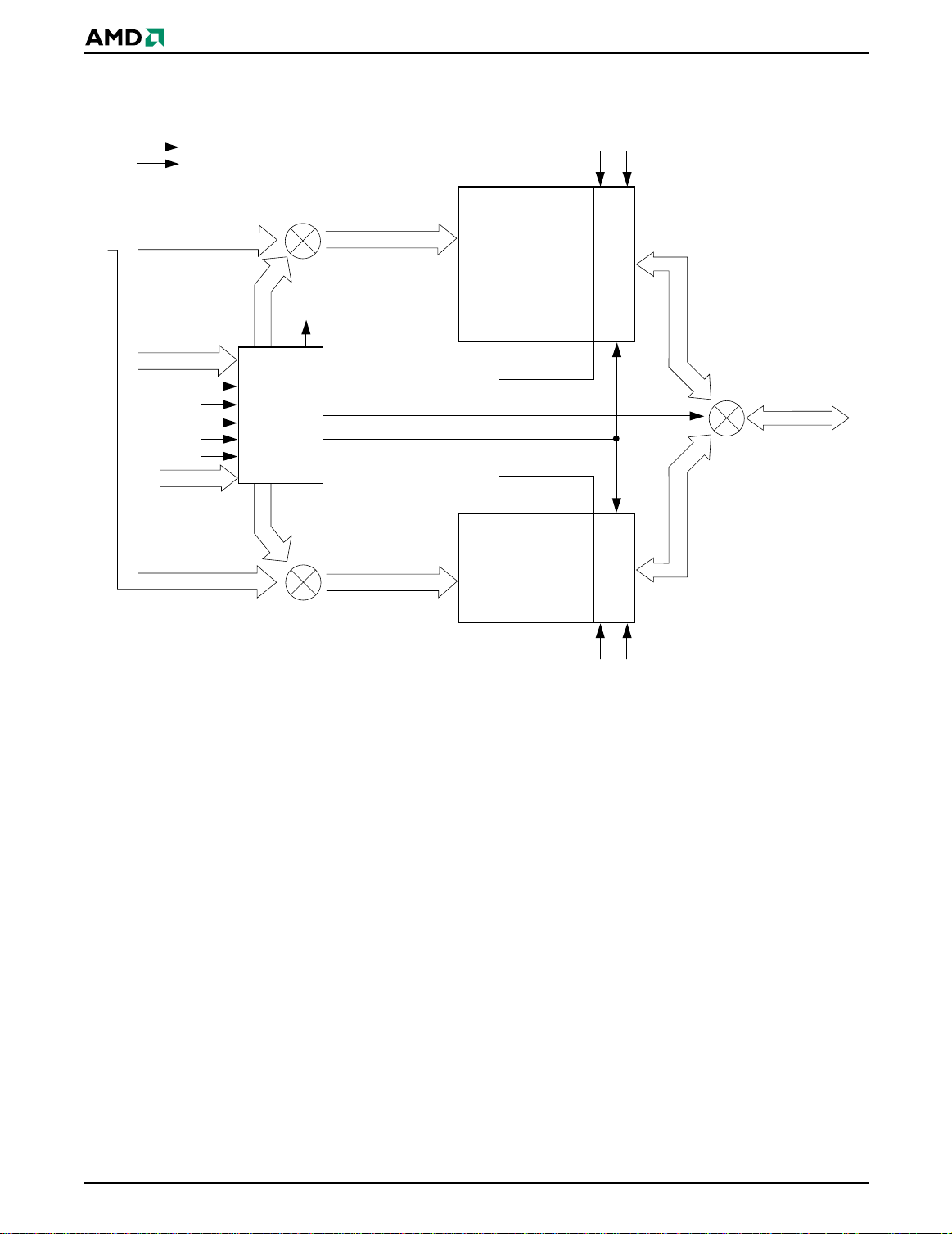

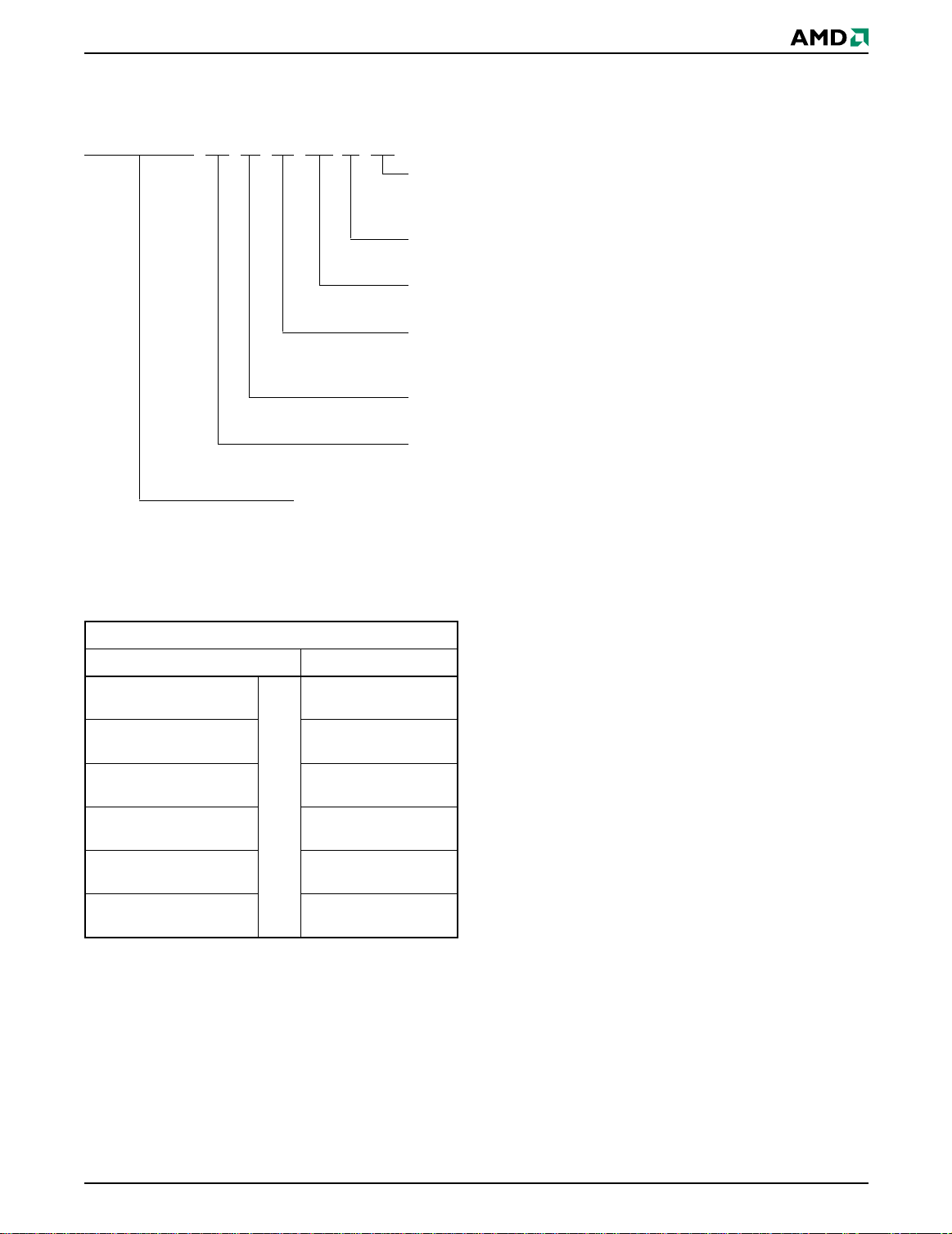

FLASH MEMORY BLOCK DIAGRAM

V

V

CC

SS

A20–A0

A20–A0

RESET#

WE#

CE#

CIOf

WP#/ACC

DQ15–DQ0

A20–A0

RY/BY#

A20–A0A20–A0

STATE

CONTROL

&

COMMAND

REGISTER

Upper Bank Address

Lower Bank Address

Y-Decoder

Status

Control

Y-Decoder

Upper Bank

X-Decoder

X-Decoder

Lower Bank

OE# CIOf

Latches and Control Logic

Latches and

Control Logic

DQ15–DQ0

DQ15–DQ0 DQ15–DQ0

OE# CIOf

6 Am41DL32x4G November 12, 2001

Page 8

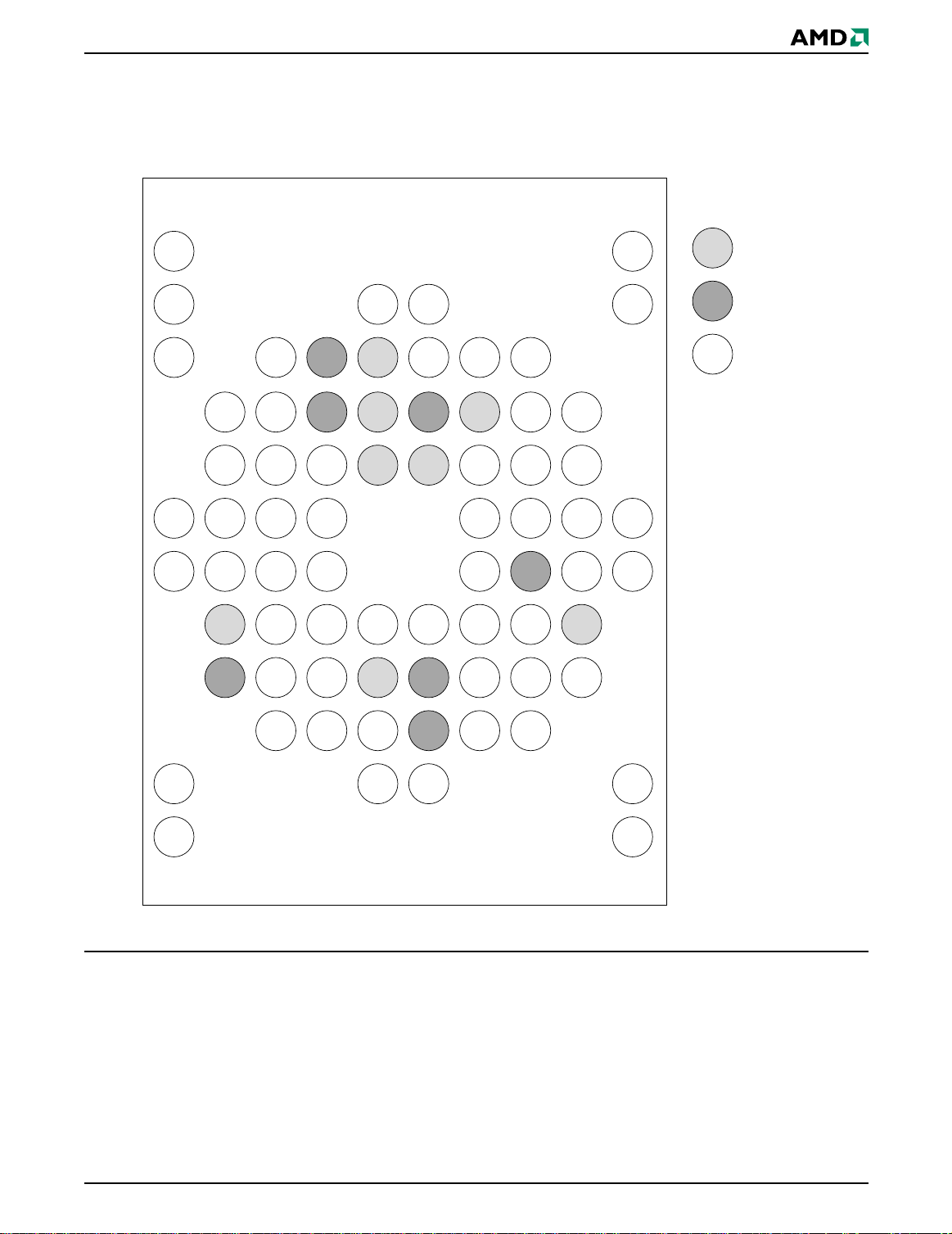

CONNECTION DIAGRAM

PRELIMINARY

73-Ball FBGA

Top View

A1

NC

B1

NC

C1

NC

F1

NC

G1

NC

L1

NC

M1

NC

D2

A3

E2

A2

F2

A1

G2

A0

H2

CE#f

J2

CE1#s

C3

A7

D3

A6

E3

A5

F3

A4

G3

V

SS

H3

OE#

J3

DQ0

K3

DQ8

C4

LB#

D4

UB#

E4

A18

F4

A17

G4

DQ1

H4

DQ9

J4

DQ10

K4

DQ2

B5

NC

C5

WP#/ACC

D5

RESET#

E5

RY/BY#

H5

DQ3

J5

V

f

CC

K5

DQ11

L5

NC

B6

NC

C6

WE#

D6

CE2s

E6

A20

H6

DQ4

J6

V

CC

K6

CIOs

L6

NC

A10

NC

B10

NC

C7

A8

D7

A19

E7

A9

F7

A10

G7

DQ6

H7

DQ13

J7

s

DQ12

K7

DQ5

C8

A11

D8

A12

E8

A13

F8

A14

G8

SA

H8

DQ15/A-1

J8

DQ7

K8

DQ14

D9

A15

E9

NC

F9

NC

G9

A16

H9

CIOf

J9

V

SS

F10

NC

G10

NC

Flash only

SRAM only

Shared

L10

NC

M10

NC

Special Handling Instructions for FBGA Package

Special handling i s required for Flas h Memory products in FBGA packages.

Flash memory devices in FBGA pac kages may be

damaged if exposed to ultrasonic c leaning methods.

The package and/or data integrity may be compromised if the package body is exposed to temperatures

above 150°C for prolonged periods of time.

November 12, 2001 Am41DL32x4G 7

Page 9

PRELIMINARY

PIN DESCRIPTION

A17–A0 = 18 Address Inputs (Common)

A-1, A20–A18 = 4 Addres s Input s (Flas h)

SA = Highest Order Address Pin (SRAM)

Byte mode

DQ15–DQ0 = 16 Data Inputs/Output s (Com mon )

CE#f = Chip Enable (Flash)

CE#s = Chip Enable (SRAM)

OE# = Output Enable (Common)

WE# = Write Enable (Common)

RY/BY# = Ready/Busy Output

UB#s = Upper Byte Control (SRAM)

LB#s = Lower Byte Control (SRAM)

CIOf = I/O Configur at ion (Fla sh)

CIOf = V

CIOf = V

CIOs = I/O Con figur at io n (SRA M)

CIOs = V

CIOs = V

RESET# = Hardware Reset Pin, Active Low

= Word mode (x16),

IH

= Byte mode (x8)

IL

= Word mode (x16),

IH

= Byte mode (x8)

IL

LOGIC SYMBOL

19

A18–A0

A-1, A20–A18

SA

CE#f

CE1#s

CE2s

OE#

WE#

WP#/ACC

RESET#

UB#s

LB#s

CIOf

CIOs

16 or 8

DQ15–DQ0

RY/BY#

WP#/ACC = Hardware Write Protect/

Acceleration Pin (Flash)

V

f = Flash 3.0 volt-only single power

CC

supply (see Product Selector Guide

for speed options and voltage sup-

ply tolerances)

s = SRAM Power Supply

V

CC

V

SS

= Device Ground (Common)

NC = Pin Not Connected Internally

8 Am41DL32x4G November 12, 2001

Page 10

PRELIMINARY

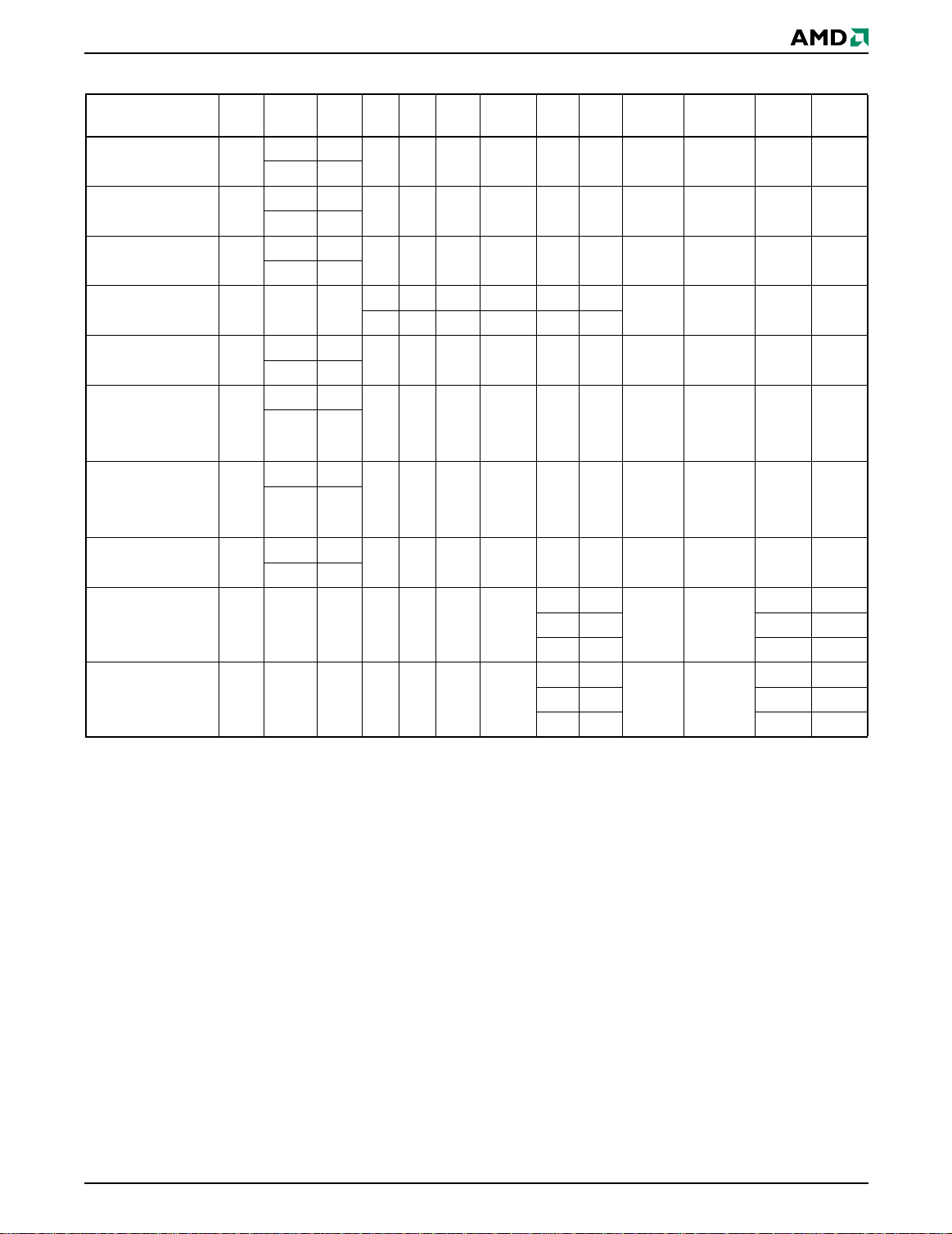

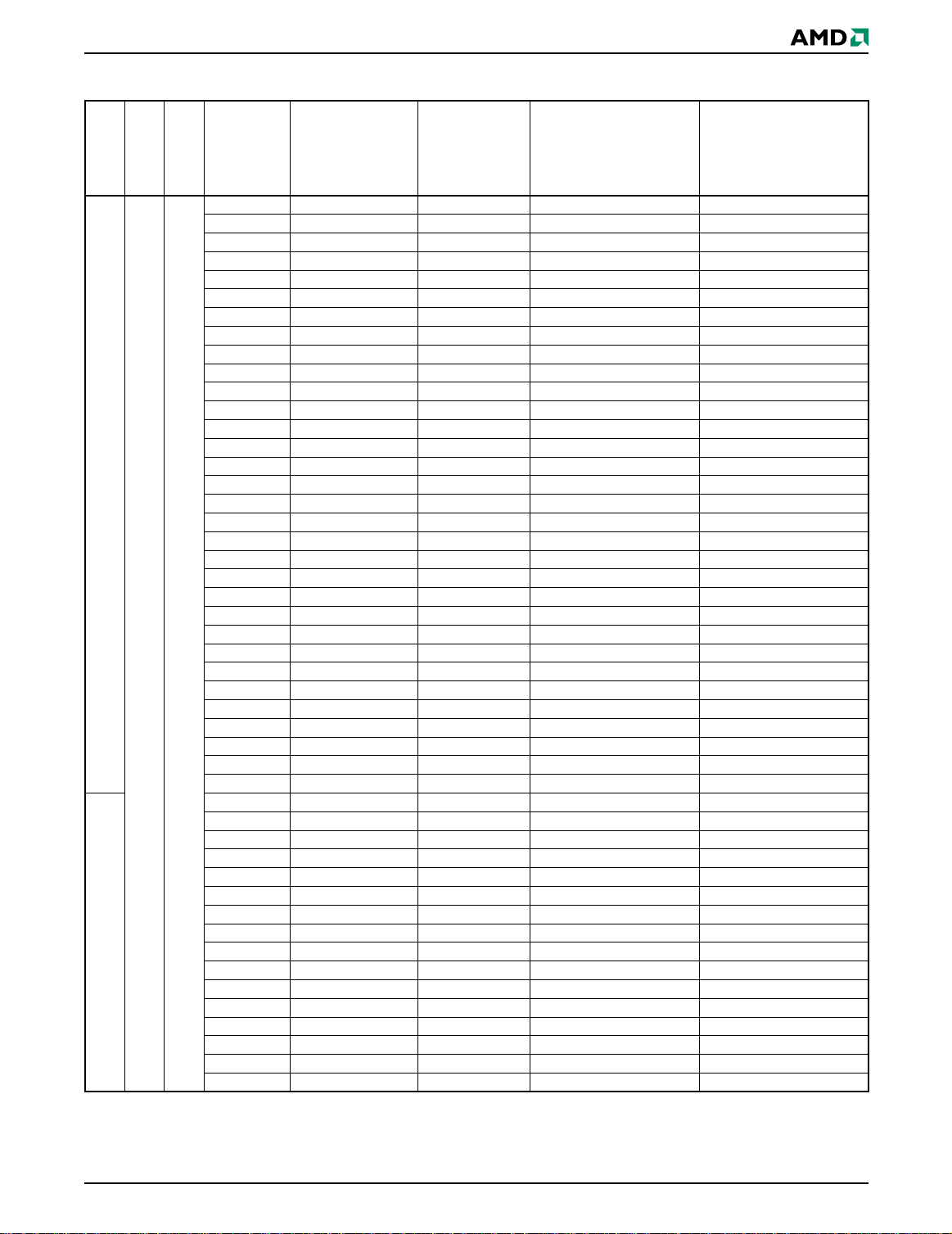

ORDERING INFORMATION

The order number (Valid Combination) is formed by the following:

Am41DL32x 4 G T 70 I T

TAPE AND REEL

T = 7 inches

S=13 inches

TEMPERATURE RANGE

I = Industrial (–40

SPEED OPTION

See Product Selector Guide and Valid Combinations

BOOT CODE SECTOR ARCHITECTURE

T=Top sector

B = Botto m sector

PROCESS TECHNOLOGY

G = 0.17 µm

SRAM DEVICE DENSITY

4= 4 Mbits

AMD DEVICE NUMBER/DESCRIPTION

Am41DL32x4G

Stacked Multi-Chip Package (MCP) Flash Memory and SRAM

Am29DL32xG 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation

Flash Memory and 4 Mbit (512 K x 8-Bit/256 K x 16-Bit) Static RAM

°C to +85°C)

Valid Combinations

Order Number Package Marking

Am41DL3224GT70I

Am41DL3224GB70I

Am41DL3224GT85I

Am41DL3224GB85I

Am41DL3234GT70I

Am41DL3234GB70I

T, S

Am41DL3234GT85I

Am41DL3234GB85I

Am41DL3244GT70I

Am41DL3244GB70I

Am41DL3244GT85I

Am41DL3244GB85I

M41000001W

M41000001X

M41000001Y

M41000001Z

M410000020

M410000021

M410000022

M410000023

M410000024

M410000025

M410000026

M410000027

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confi rm

availability of specific valid combinations and to ch eck on newl y released combinations

November 12, 2001 Am41DL32x4G 9

Page 11

PRELIMINARY

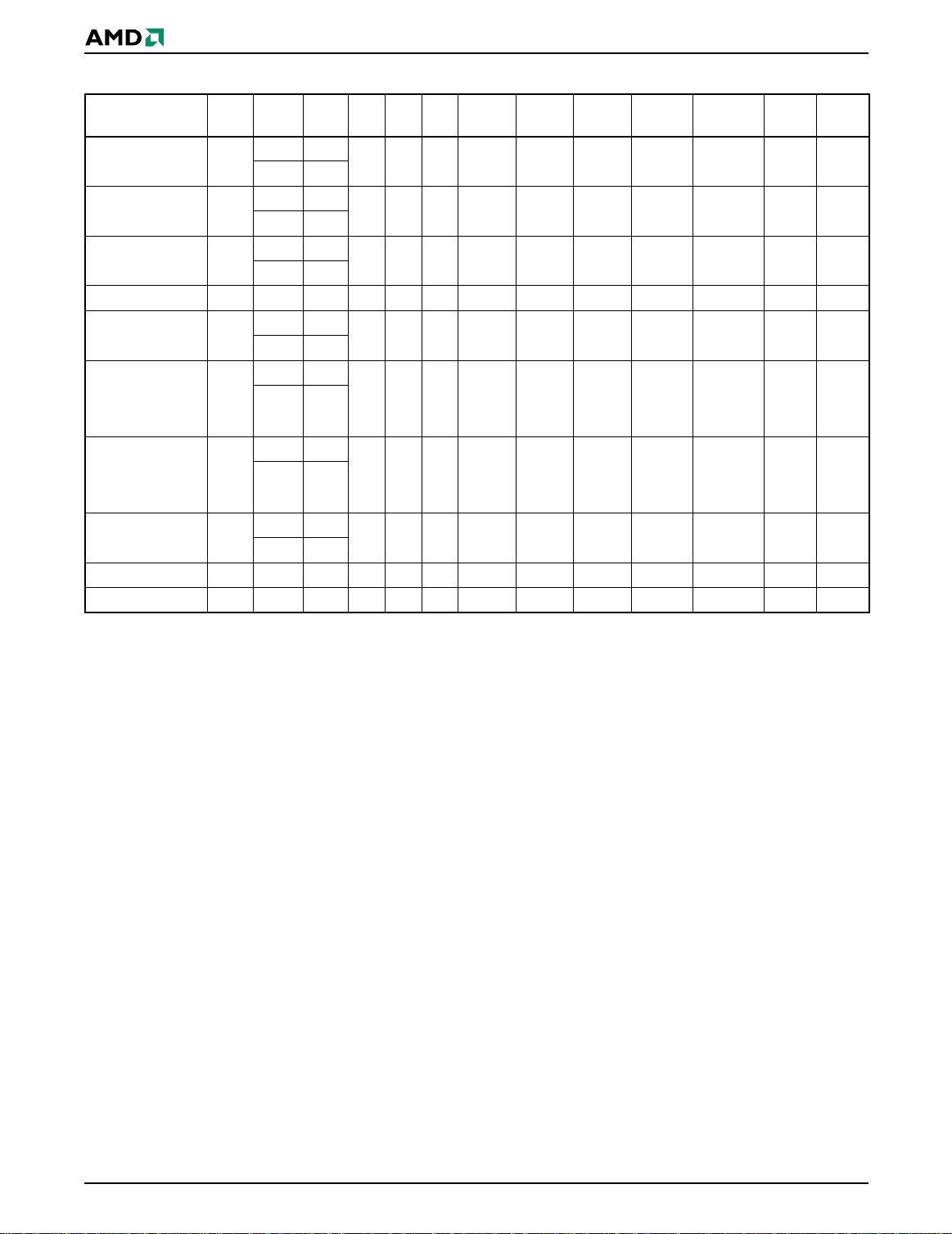

DEVICE BUS OPERATIONS

This section describes the requirements and use of

the device bus operations, which are initiated through

the internal command register. The command register

itself does not occupy any addressable memory location. The register is a latch used to store the

commands, along with the address and data information neede d to ex ecu te the co mm an d. T he conte nts of

the register serve as inputs to th e internal state machine. The state machine outputs dictate the function

of the device. Tables 1 through 3 li st the dev ice bus

operations, the inputs and control levels they require,

and the resulting output. The following subsections describe each of these operations in further detail.

10 Am41DL32x4G November 12, 2001

Page 12

PRELIMINARY

Table 1. Device Bus Operations—Flash Word Mode, CIOf = VIH; SRAM Word Mode, CIOs = VCC

Operation

(Notes 1, 2)

Read from Flash L

Write to Flash L

Standby

Output Disable L L H

Flash Hardware

Reset

Sector Prote ct

(Note 5)

CE#f CE1#s CE2s OE# WE# SA Addr. LB#s UB#s RESET#

V

CC

0.3 V

HX

XL

HX

XL

HX

±

XL

LH X A

HL X A

XX X X X X

HHXXLX

HH X X X L

HX

X

L

XL

HX

XL

X X X X X X L L/H High-Z High-Z

SADD,

HL X

A6 = L,

A1 = H,

A0 = L

Sector Unprotect

(Note 5)

Temporary Sector

Unprotect

L

X

HX

XL

HX

XL

HL X

XX X X X X V

SADD,

A6 = H,

A1 = H,

A0 = L

Read from SRAM H L H L H X A

Write to SRAM H L H X L X A

WP#/ACC

(Note 4)

XX H L/H D

IN

XX H (Note 4)DIND

IN

V

±

CC

0.3 V

H High-Z High-Z

H L/H High-Z High-Z

XX V

XX V

ID

ID

ID

L/H D

(Note 6) D

(Note 6) D

LL

H L High-Z D

IN

HX

LH D

LL

H L High-Z D

IN

HX

LH DINHigh-Z

DQ7–

DQ0

OUT

IN

IN

IN

D

OUT

OUT

D

IN

DQ15–

DQ8

D

OUT

IN

X

X

High-Z

D

OUT

OUT

High-Z

D

IN

IN

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 11.5–12.5 V, VHH = 9.0 ± 0.5 V, X = Don’t Care, SA = SRAM Address

Input, Byte Mode, SADD = Flash Sector Address, A

= Address In, DIN = Data In, D

IN

= Data Out

OUT

Notes:

1. Other operations except for those indicated in this column are inhibited.

2. Do not apply CE#f = V

, CE1#s = VIL and CE2s = VIH at the same time.

IL

3. Don’t care or open LB#s or UB#s.

4. If WP#/ACC = V

If WP#/ACC = V

, the boot sectors will be pr ot ected . I f WP#/ ACC = VIH the boot sectors protect ion will be removed.

IL

(9V), the program ti me wi ll be reduced by 40%.

ACC

5. The sector protect and sector unpr ot ect f uncti ons may als o be implemented via prog ramming equipm ent . S ee t he “Sector /Sec tor

Block Protection and Unpr otection” section.

6. If WP#/ACC = V

depends on whether they were l ast p rotec t ed or unprot ec ted usi ng t he me thod des cr ibed in “Sect or/Sector Bl ock Prot ec tion and

Unprotection”. If WP#/A CC = V

, the two outermost b oot sect or s remai n pr otected. If WP#/ACC = VIH, the two outermost boot se ctor pr otecti on

IL

all sectors will be unpr ot ec ted.

HH,

November 12, 2001 Am41DL32x4G 11

Page 13

PRELIMINARY

Table 2. Device Bus Operations—Flash Word Mode, CIOf = VIH; SRAM Byte Mode, CIOs = VSS

Operation

(Notes 1, 2)

Read from Flash L

Write to Flash L

Standby

CE#f CE1#s CE2s OE# WE# SA Addr.

V

CC

0.3 V

HX

XL

HX

XL

HX

±

XL

LHX A

HLX A

XXX X X X

Output Disable L L H H H SA X DNU DNU H L/H High-Z High-Z

Flash Hardware

Reset

Sector Protect

(Note 5)

X

L

HX

XL

HX

XL

XXX X X X L L/HHigh-ZHigh-Z

SADD,

HLX

A6 = L,

A1 = H,

A0 = L

Secto r Unprotect

(Note 5)

Temporary Sector

Unprotect

L

X

HX

XL

HX

XL

HLX

XXX A

SADD,

A6 = H,

A1 = H,

A0 = L

Read from SRAM H L H L H SA A

Write to SRAM H L H X L SA A

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 11.5–12.5 V, VHH = 9.0 ± 0.5 V, X = Don’t Care, SA = SRAM Address

Input, Byte Mode, SADD = Flash Sector Address, A

= Address In, DIN = Data In, D

IN

Notes:

1. Other operations except for those indicated in this column are inhibited.

2. Do not apply CE#f = V

, CE1#s = VIL and CE2s = VIH at the same time.

IL

3. Don’t care or open LB#s or UB#s.

4. If WP#/ACC = V

If WP#/ACC = V

, the boot sectors will be pr ot ected . I f WP#/ ACC = VIH the boot sectors protect ion will be removed.

IL

(9V), the program ti me wi ll be reduced by 40%.

ACC

5. The sector protect and sector unpr ot ect f uncti ons may als o be implemented via prog ramming equipm ent . S ee t he “Sec tor/Sector

Block Protection and Unpr otection” section.

6. If WP#/ACC = V

, the two outermost b oot sect or s remai n pr otected. If WP#/ACC = VIH, the two outermost boot se ctor pr otecti on

IL

depends on whether they were l ast p rotec t ed or unprot ec ted usi ng t he me thod des cr ibed in “Sect or/S ector Bl ock Pr otec t ion an d

Unprotection”. If WP#/ACC = V

all sectors will be unpr ot ec ted.

HH,

IN

IN

IN

IN

IN

LB#s

(Note 3)

UB#s

(Note 3)

RESET#

XXHL/HD

X X H (Note 3) D

V

0.3 V

XXV

XXV

CC

±

ID

ID

WP#/ACC

(Note 4)

DQ7–

DQ0

OUTDOUT

IN

H High-Z High-Z

L/H D

(Note 6) D

IN

IN

XXVID(Note 6) DINHigh-Z

XXH XD

OUT

XXH XDINHigh-Z

= Data Out, DNU = Do Not Use

OUT

DQ15–

DQ8

D

IN

X

X

High-Z

12 Am41DL32x4G November 12, 2001

Page 14

PRELIMINARY

Table 3. Device Bus Operations—Flash Byte Mode, CIOf = VSS; SRAM Word Mode, CIOs = VCC

Operation

(Not es 1, 2)

Read from Flash L

Write to Flash L

Standby

CE#f CE1#s CE2s OE#

V

CC

0.3 V

HX

XL

HX

XL

HX

±

XL

LHX A

HLX A

XXX X X X

WE# SA Addr.

Output Disable L L H H H X X

Flash Hardware

Reset

Sector Protect

(Note 5)

X

L

HX

XL

HX

XL

X X X X X X L L/H High-Z High-Z

SADD,

HLX

A6 = L,

A1 = H,

A0 = L

Sector

Unprotect

(Note 5)

Temporary

Sector

Unprotect

Read from

SRAM

HX

L

XL

HLX

Hx

X

XL

XXX A

HLHLHXA

SADD,

A6 = L,

A1 = H,

A0 = L

Write to SRAM H L H X L X A

IN

IN

IN

IN

IN

LB#s

(Note 3)

UB#s

(Note 3)

RESET#

WP#/ACC

(Note 4)

XXHL/HD

XXH

V

0.3 V

LX

XL

XXV

XXV

(Not e 3)

±

CC

H High-Z High-Z

H L/H High-Z High-Z

ID

ID

L/H D

(Note 6) D

XXVID(Note 6) D

LL

HL High-ZD

HX

LH D

LL

HL High-ZD

HX

LH DINHigh-Z

DQ7–

DQ0

OUT

D

IN

IN

IN

IN

D

OUT

OUT

D

IN

DQ15–

DQ8

High-Z

High-Z

X

X

High-Z

D

OUT

OUT

High-Z

D

IN

IN

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 11.5–12.5 V, VHH = 9.0 ± 0.5 V, X = Don’t Care, SA = SRAM Address

Input, Byte Mode, SADD = Flash Sector Address, A

= Address In (for Flash Byte Mode, DQ15 = A-1), DIN = Data In, D

IN

OUT

=

Data Out

Notes:

1. Other operations except for those indicated in this column are inhibited.

2. Do not apply CE#f = V

, CE1#s = VIL and CE2s = VIH at the same time.

IL

3. Don’t care or open LB#s or UB#s.

4. If WP#/ACC = V

If WP#/ACC = V

, the boot sectors will be pr ot ected . I f WP#/ ACC = VIH the boot sectors protect ion will be removed.

IL

(9V), the program ti me wi ll be reduced by 40%.

ACC

5. The sector protect and sector unpr ot ect f uncti ons may als o be implemented via prog ramming equipm ent . S ee t he “Sec tor/Sector

Block Protection and Unpr otection” section.

6. If WP#/ACC = V

, the two outermost b oot sect or s remai n pr otected. If WP#/ACC = VIH, the two outermost boot se ctor pr otecti on

IL

depends on whether they were l ast p rotec t ed or unprot ec ted usi ng t he me thod des cr ibed in “Sect or/S ector Bl ock Pr otec t ion an d

Unprotection”. If WP#/ACC = V

all sectors will be unpr ot ec ted.

HH,

November 12, 2001 Am41DL32x4G 13

Page 15

PRELIMINARY

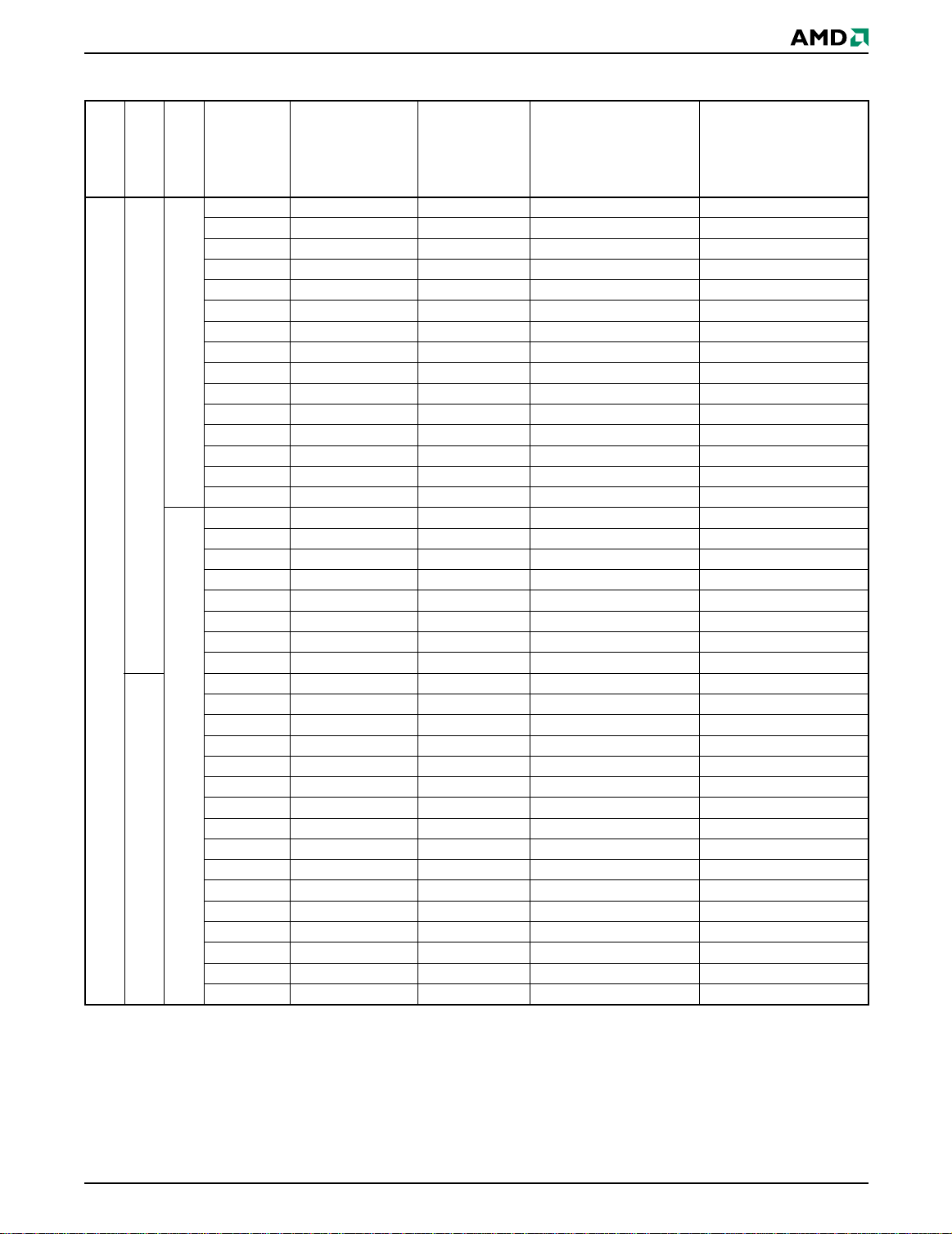

Table 4. Device Bus Operations—Flash Byte Mode, CIOf = VIL; SRAM Byte Mode, CIOs = VSS

Operation

(Not es 1, 2)

CE#f CE1#s CE2s OE#

Read from Flash L

Write to Flash L

Standby

V

0.3 V

CC

HX

XL

HX

XL

HX

±

XL

WE# SA Addr.

LH X A

HL X A

IN

IN

LB#s

(Note 3)

UB#s

(Note 3)

XXHL/HD

XXH

XX X X X X

RESET#

V

±

CC

0.3 V

WP#/ACC

(Note 4)

(Note 3)

H High-Z High-Z

DQ7–

DQ0

Output Disable H L H H H SA X DNU DNU H L/H High-Z High-Z

Flash Hardware

Reset

Sector Protect

(Note 5)

X

L

HX

XL

HX

XL

X X X X X X L L/H High-Z High-Z

SADD,

HL X

A6 = L,

A1 = H,

XXV

ID

L/H D

A0 = L

HX

Sector Unprotect

(Note 5)

Temporary

Sector Unprotect

L

X

XL

HX

XL

HL X

XX X A

Read from SRAM H L H L H SA A

Write to SRAM H L H X L SA A

SADD,

A6 = L,

A1 = H,

A0 = L

IN

IN

IN

XXV

ID

(Note 6) D

XXVID(Note 6) D

XXH XD

XXH XDINHigh-Z

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 11.5–12.5 V, VHH = 9.0 ± 0.5 V, X = Don’t Care, SA = SRAM Address

Input, Byte Mode, SADD = Flash Sector Address, A

= Address In (for Flash Byte Mode, DQ15 = A-1), DIN = Data In, D

IN

Data Out, DNU = Do Not Use

Notes:

1. Other operations except for those indicated in this column are inhibited.

2. Do not apply CE#f = V

, CE1#s = VIL and CE2s = VIH at the same time.

IL

3. Don’t care or open LB#s or UB#s.

4. If WP#/ACC = V

If WP#/ACC = V

, the boot sectors will be pr ot ected . I f WP#/ ACC = VIH the boot sectors protect ion will be removed.

IL

(9V), the program ti me wi ll be reduced by 40%.

ACC

5. The sector protect and sector unpr ot ect f uncti ons may als o be implemented via prog ramming equipm ent . S ee t he “Sec tor/Sector

Block Protection and Unpr otection”.

6. If WP#/ACC = V

, the two outermost b oot sect or s remai n pr otected. If WP#/ACC = VIH, the two outermost boot se ctor pr otecti on

IL

depends on whether they were l ast p rotec t ed or unprot ec ted usi ng t he me thod des cr ibed in “Sect or/S ector Bl ock Pr otec t ion an d

Unprotection”. If WP#/ACC = V

all sectors will be unpr ot ec ted.

HH,

D

OUT

IN

IN

IN

IN

OUT

DQ15–

DQ8

High-Z

High-Z

X

X

High-Z

High-Z

=

OUT

14 Am41DL32x4G November 12, 2001

Page 16

PRELIMINARY

Word/Byte Configuration

The CIOf pin controls whether the device data I/O pins

operate in the byte or word configuration. If the CIOf

pin is set at logic ‘1’, the device is in word configuration, DQ15–DQ0 are active and controlled by CE# and

OE#.

If the CIOf pin is set at logic ‘0’, the dev ice is in byte

configur atio n, a nd o nly data I/O pin s DQ 7–DQ0 are

active and controlled by CE# and OE#. The data I/O

pins DQ14–DQ8 are tri-stated, and the DQ15 pin is

used as an input for the LSB (A-1) address function.

Requirements for Reading Array Data

To read array data from the outputs, the system must

drive the CE# f a nd O E# pins to V

. CE#f is the po wer

IL

control an d se lec ts t he d ev ice . O E# i s th e ou tpu t c ontrol and gates array data to the output pins. WE#

should remain at V

. The CIOf pin determines

IH

whether the devi ce outputs arr ay data in words or

bytes.

The internal state machine is set for reading array data

upon device power-up, or after a hardware reset. This

ensures that no spuri ous alteration of the mem ory

content occurs during th e power tr ansition . No command is necessary in this mode to obtain array data.

Standard mi cropr oce ssor re ad cycles that as sert va lid

addresse s o n t he devi ce ad dres s i npu ts pr od uc e vali d

data on the device data outputs. Each bank remains

enabled fo r read acces s until the comm and regis ter

contents are altered.

See “Requirements for Reading Array Data” for more

information. Refer to the AC Flash Read-Only Operations table for timing specifications and to Figure 14 for

the timing diagram. I

in the DC Characteri stics

CC1

table represents the active current specification for

reading array data.

Writing Commands/Command Sequences

To write a command or comm an d sequ enc e ( whi ch includes programming data to the device and erasing

sectors of memory), the system must drive WE# and

CE#f to V

For program operations, the CIOf pin determines

whether the device accepts program data in bytes or

words. Refer to “Word/Byte Configuration” for more

information.

The devic e fea ture s an Unlock Bypa ss m od e to fa cilitate faste r programmin g. Once a bank ent ers the

Unlock Bypass mode, only two write cycles are required to program a word or byte, instead of four. The

“Word/Byte Configuration” section has details on pro-

gramming data to the device using both standard and

Unlock Bypass command sequences.

, and OE# to VIH.

IL

An erase operation can erase one sector, multiple sectors, or the entire device. Tables 6–9 indicat e the

address space that each sector occupies. The device

address spa ce is divi ded i nto two ba nks: Ba nk 1 c ontains the boot/par am ete r sec tors , and Ban k 2 conta in s

the larger, code sectors of uniform size. A “bank address” is the add res s bits requ ire d to un iq uel y select a

bank. Similarly, a “sector address” is the address bits

required to uniquely select a sector.

in the DC Ch arac te ris tics ta ble represents the ac-

I

CC2

tive current specification for the write mod e. The AC

Characteristics section contains timing specification

tables and timing diagrams for write operations.

Accelerated Program Operation

The device offers accelerated program operations

through the AC C fun ct ion. T his is on e of two functions

provided by the WP#/ACC pin. This function is primarily intended to allow faster manufacturing throughput

at the factory.

If the system asserts V

on this pin, the de vice a uto-

HH

matically en ters the af oreme ntioned Un lock Bypa ss

mode, temporarily unprotects any pr otected sectors,

and uses the higher voltage on the pin to reduce the

time required for program ope rations. The system

would use a two-cycle pr ogram com mand s equence

as required by the Unloc k Bypass m ode. Rem oving

from the WP#/ACC pin returns the device to nor-

V

HH

mal operation. Note that the WP#/ACC pin mu st not

be at V

for operations other than accelerate d pro-

HH

gramming, or device damage may result. In addition,

the WP#/ACC pin must not be left floating or un connected; inconsistent behavior of the device may result.

Autoselect Functions

If the system writes the autoselect command sequence, the device enters the autoselect mo de. The

system can the n rea d au tos e le ct co des fro m th e i nte rnal register (which is separate from the memory array)

on DQ7–DQ0. Standard read cycle timings apply in

this mode . Refe r to th e Au tosel ec t Mode and A uto select Command Sequence sections for more

information.

Simultaneous Read/Write Operations with Zero Latency

This device is capable of reading data from one bank

of memory while programming or erasing in the other

bank of memory. An erase operation may also be suspended to rea d from or prog ram to anoth er locati on

within the same bank (except the sector b eing

erased). Figure 21 shows how read and write cycles

may be initiated for simultaneous operation with zero

latency. I

CC6

and I

represent the current specifications for read-while-program and read-while-erase, respectively.

in the DC Characteristics table

CC7

November 12, 2001 Am41DL32x4G 15

Page 17

PRELIMINARY

Standby Mode

When the syste m is not rea ding or wr iting to the device, it can place the de vice in the standby mode. In

this mode, current consumption is greatly reduced,

and the outputs are placed in the high impedance

state, independent of the OE# input.

The devi ce en ter s t he CM OS st and by m od e w hen th e

CE#f and RESET# pins are both held at V

± 0.3 V.

CC

(Note that this is a more restricted voltage range than

.) If CE#f and RESE T# are held at VIH, but not

V

IH

within V

± 0.3 V, the device will b e in the stan dby

CC

mode, but the s tandby cu rrent will be greater. The device requires standard access time (t

) for read

CE

access when the device is in either of these standby

modes, before it is ready to read data.

If the device is desele cted during er asur e or prog ramming, the device draws active current until the

operation is completed.

in the DC Characteristics table represents the

I

CC3

standby current specification.

Automatic Sleep Mode

The automatic sleep mode minimizes Flash device energy consumption. The device automatically enables

this mode when addresses remain stable for t

ACC

+

30 ns. The automatic sleep mode is independent of

the CE# f, WE#, an d OE# co nt r ol si gn al s . S tan da r d ad dress access timings provide new data when

addresses are changed. While in sleep mode, output

data is latched and always available to the system.

in the DC Characteristics table represents the

I

CC4

automatic sleep mode current specification.

RESET#: Hardware Reset Pin

The RESET# pin provides a hardware m ethod of resetting the device to reading array data. When the

RESET# pin is driven low for at least a p eriod of t

RP

the device immediately terminates any operation in

progress, tristates all output pins, and ignores all

read/write commands for the duration of the RESET#

pulse. The de vice also resets th e internal state ma chine to read ing array data. The ope ration tha t was

interrupted should be reinitiated once the device is

ready to accept an other c ommand sequen ce, to ensure data integrity.

Current is reduced for the duration of the RESET#

pulse. When RESE T# is h eld at V

vice draws CMOS standby current (I

held at V

but not within V

IL

± 0.3 V, the standby cur-

SS

± 0.3 V, the de-

SS

). If RESET# is

CC4

rent will be greater.

The RESET# pin may be tied to the system reset cir-

cuitry. A system reset would thus also reset the Flash

memory, enabling the system to read the boot-up firmware from the Flash memory.

If RESET# is asserted during a program or erase operation, the RY/BY# pin remains a “0” (busy) until the

internal reset operation is complete, which requires a

time of t

(during Embedded Algorithms). The

READY

system can thus monitor RY/BY# to determine

whether the res e t op erat io n i s c om plete . If RESET# is

asserted when a program or erase operation is not executing (RY/BY# pin is “1”), the re set operat ion is

completed within a time of t

ded Algorithms). The system can read data t

the RESET# pin returns to V

(not during Embed-

READY

.

IH

RH

after

Refer to the AC Characteristics tables for RESET# parameters and to Figure 15 for the timing diagram.

Output Disable Mode

When the OE# input is at VIH, output from the device is

disabled. The output pins are placed in the high

impedance state.

,

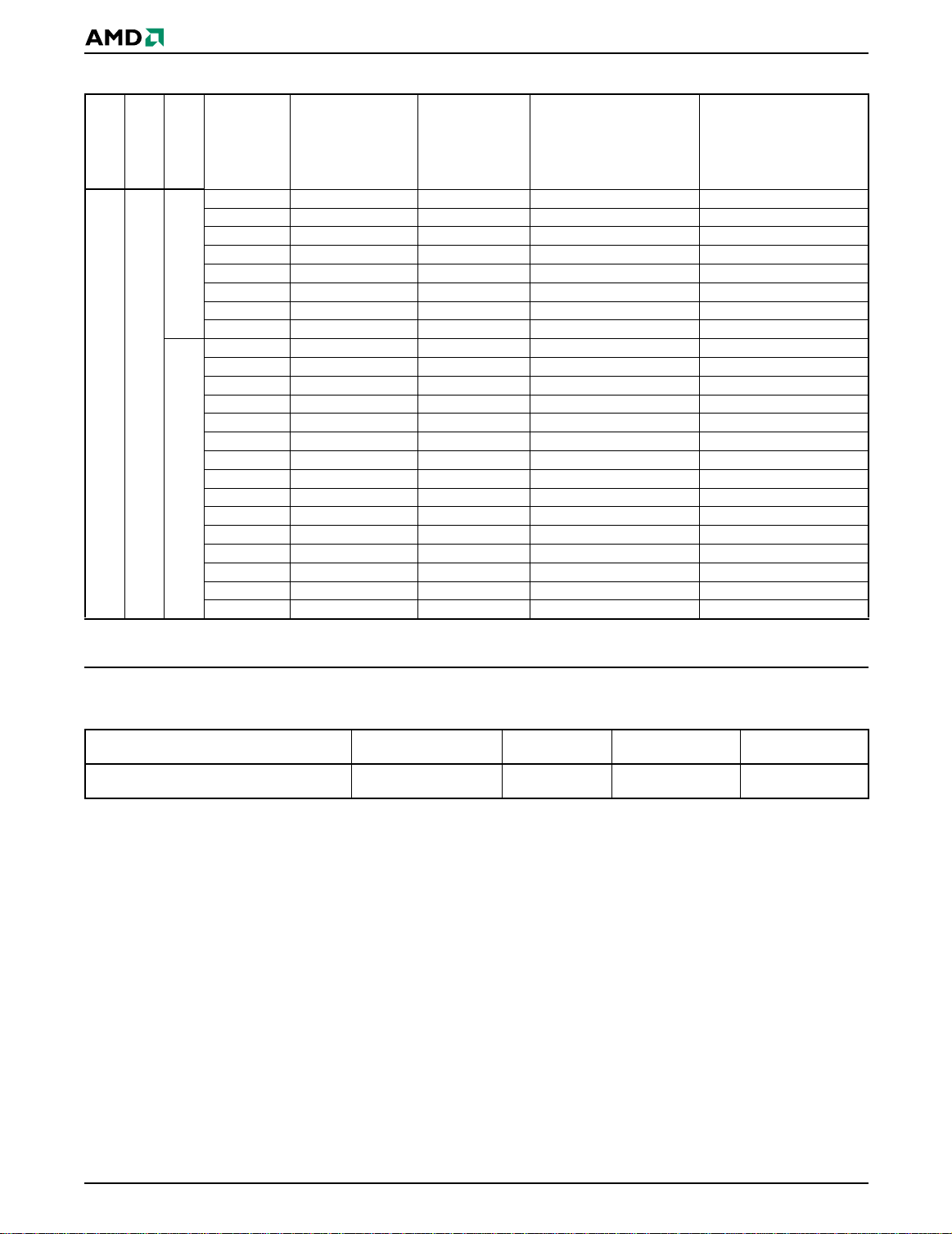

Table 5. Device Bank Division

Device

Part Number

Am29DL322G 4 Mbit

Am29DL323G 8 Mbit

Am29DL324G 16 Mbit

Megabits Sector Sizes Me ga bits Sector Sizes

Bank 1 Bank 2

Eight 8 Kbyte/4 Kword,

seven 64 Kbyte/32 Kword

Eight 8 Kbyte/4 Kword,

fifteen 64 Kbyte/32 Kword

Eight 8 Kbyte/4 Kword,

thirty-one 64 Kbyte/32 Kword

28 Mbit

24 Mbit

16 Mbit

Fifty-six

64 Kbyte/32 Kword

Forty-eight

64 Kbyte/32 Kword

Thirty-two

64 Kbyte/32 Kword

16 Am41DL32x4G November 12, 2001

Page 18

PRELIMINARY

Sector

Am29DL324GT

Am29DL323GT

Am29DL322GT

SA0 000000xxx 64/32 000000h–00FFFFh 000000h–07FFFh

SA1 000001xxx 64/32 010000h–01FFFFh 008000h–0FFFFh

SA2 000010xxx 64/32 020000h–02FFFFh 010000h–17FFFh

SA3 000011xxx 64/32 030000h–03FFFFh 018000h–01FFFFh

SA4 000100xxx 64/32 040000h–04FFFFh 020000h–027FFFh

SA5 000101xxx 64/32 050000h–05FFFFh 028000h–02FFFFh

SA6 000110xxx 64/32 060000h–06FFFFh 030000h–037FFFh

SA7 000111xxx 64/32 070000h–07FFFFh 038000h–03FFFFh

SA8 001000xxx 64/32 080000h–08FFFFh 040000h–047FFFh

SA9 001001xxx 64/32 090000h–09FFFFh 048000h–04FFFFh

SA10 001010xxx 64/32 0A0000h–0AFFFFh 050000h–057FFFh

SA11 001011xxx 64/32 0B0000h–0BFFFFh 058000h–05FFFFh

SA12 001100xxx 64/32 0C0000h–0CFFFFh 060000h–067FFFh

SA13 001101xxx 64/32 0D0000h–0DFFFFh 068000h–06FFFFh

SA14 001110xxx 64/32 0E0000h–0EFFFFh 070000h–077FFFh

SA15 001111xxx 64/32 0F0000h–0FFFFFh 078000h–07FFFFh

Bank 2

Bank 2

Bank 1

SA16 010000xxx 64/32 100000h–10FFFFh 080000h–087FFFh

SA17 010001xxx 64/32 110000h–11FFFFh 088000h–08FFFFh

SA18 010010xxx 64/32 120000h–12FFFFh 090000h–097FFFh

SA19 010011xxx 64/32 130000h–13FFFFh 098000h–09FFFFh

SA20 010100xxx 64/32 140000h–14FFFFh 0A0000h–0A7FFFh

SA21 010101xxx 64/32 150000h–15FFFFh 0A8000h–0AFFFFh

SA22 010110xxx 64/32 160000h–16FFFFh 0B0000h–0B7FFFh

SA23 010111xxx 64/32 170000h–17FFFFh 0B8000h–0BFFFFh

SA24 011000xxx 64/32 180000h–18FFFFh 0C0000h–0C7FFFh

Bank 2

SA25 011001xxx 64/32 190000h–19FFFFh 0C8000h–0CFFFFh

SA26 011010xxx 64/32 1A0000h–1AFFFFh 0D0000h–0D7FFFh

SA27 011011xxx 64/32 1B0000h–1BFFFFh 0D8000h–0DFFFFh

SA28 011100xxx 64/32 1C0000h–1CFFFFh 0E0000h–0E7FFFh

SA29 011101xxx 64/32 1D0000h–1DFFFFh 0E8000h–0EFFFFh

SA30 011110xxx 64/32 1E0000h–1EFFFFh 0F0000h–0F7FFFh

SA31 011111xxx 64/32 1F0000h–1FFFFFh 0F8000h–0FFFFFh

SA32 100000xxx 64/32 200000h–20FFFFh 100000h–107FFFh

SA33 100001xxx 64/32 210000h–21FFFFh 108000h–10FFFFh

SA34 100010xxx 64/32 220000h–22FFFFh 110000h–117FFFh

SA35 100011xxx 64/32 230000h–23FFFFh 118000h–11FFFFh

SA36 100100xxx 64/32 240000h–24FFFFh 120000h–127FFFh

SA37 100101xxx 64/32 250000h–25FFFFh 128000h–12FFFFh

SA38 100110xxx 64/32 260000h–26FFFFh 130000h–137FFFh

SA39 100111xxx 64/32 270000h–27FFFFh 138000h–13FFFFh

SA40 101000xxx 64/32 280000h–28FFFFh 140000h–147FFFh

SA41 101001xxx 64/32 290000h–29FFFFh 148000h–14FFFFh

SA42 101010xxx 64/32 2A0000h–2AFFFFh 150000h–157FFFh

SA43 101011xxx 64/32 2B0000h–2BFFFFh 158000h–15FFFFh

SA44 101100xxx 64/32 2C0000h–2CFFFFh 160000h–167FFFh

SA45 101101xxx 64/32 2D0000h–2DFFFFh 168000h–16FFFFh

SA46 101110xxx 64/32 2E0000h–2EFFFFh 170000h–177FFFh

SA47 101111xxx 64/32 2F0000h–2FFFFFh 178000h–17FFFFh

Ta ble 6. Top Boot Sector Addresses

Sector Address

A20–A12

Sector Size

(Kbytes/Kwords)

(x8)

Address Range

(x16)

Address Range

November 12, 2001 Am41DL32x4G 17

Page 19

PRELIMINARY

Table 6. Top Boot Sector Addresses (Continued)

Sector

Am29DL324GT

Am29DL323GT

Am29DL322GT

SA48 110000xxx 64/32 300000h–30FFFFh 180000h–187FFFh

SA49 110001xxx 64/32 310000h–31FFFFh 188000h–18FFFFh

SA50 110010xxx 64/32 320000h–32FFFFh 190000h–197FFFh

SA51 110011xxx 64/32 330000h–33FFFFh 198000h–19FFFFh

SA52 110100xxx 64/32 340000h–34FFFFh 1A0000h–1A7FFFh

Bank 2

SA53 110101xxx 64/32 350000h–35FFFFh 1A8000h–1AFFFFh

SA54 110110xxx 64/32 360000h–36FFFFh 1B0000h–1B7FFFh

SA55 110111xxx 64/32 370000h–37FFFFh 1B8000h–1BFFFFh

SA56 111000xxx 64/32 380000h–38FFFFh 1C0000h–1C7FFFh

SA57 111001xxx 64/32 390000h–39FFFFh 1C8000h–1CFFFFh

SA58 111010xxx 64/32 3A0000h–3AFFFFh 1D0000h–1D7FFFh

SA59 111011xxx 64/32 3B0000h–3BFFFFh 1D8000h–1DFFFFh

Bank 1

Bank 1

SA60 111100xxx 64/32 3C0000h–3CFFFFh 1E0000h–1E7FFFh

SA61 111101xxx 64/32 3D0000h–3DFFFFh 1E8000h–1EFFFFh

SA62 111110xxx 64/32 3E0000h–3EFFFFh 1F0000h–1F7FFFh

SA63 111111000 8/4 3F0000h–3F1FFFh 1F8000h–1F8FFFh

Bank 1

SA64 111111001 8/4 3F2000h–3F3FFFh 1F9000h–1F9FFFh

SA65 111111010 8/4 3F4000h–3F5FFFh 1FA000h–1FAFFFh

SA66 111111011 8/4 3F6000h–3F7FFFh 1FB000h–1FBFFFh

SA67 111111100 8/4 3F8000h–3F9FFFh 1FC000h–1FCFFFh

SA68 111111101 8/4 3FA000h–3FBFFFh 1FD000h–1FDFFFh

SA69 111111110 8/4 3FC000h–3FDFFFh 1FE000h–1FEFFFh

SA70 11 1111111 8/4 3FE000h–3FFFFFh 1FF000h–1FFFFFh

Sector Address

A20–A12

Sector Size

(Kbytes/Kwords)

(x8)

Address Range

(x16)

Address Range

Note: The address range is A20:A-1 in byte mode (BYTE#=VIL) or A20:A0 in word mode (BYTE#=VIH). The bank address bits are A20–A18 for

Am29DL322GT, A20 and A19 for Am29DL323GT, and A20 for Am29DL324GT.

Table 7. Top Boot SecSi Sector Addresses

Device

Am29DL322GT, Am29DL323GT,

Am29DL324GT

Sector Address

A20–A12

111111xxx 256/128 3FE000h–3FE0FFh 1FF000h–1FF07Fh

Sector Size

(bytes/words)

(x8)

Address Range

(x16)

Address Range

18 Am41DL32x4G November 12, 2001

Page 20

PRELIMINARY

Table 8. Bottom Boot Sector Addresses

Sector

Am29DL324GB

Am29DL323GB

Am29DL322GB

SA0 000000000 8/4 000000h-001FFFh

SA1 000000001 8/4 002000h-003FFFh

SA2 000000010 8/4 004000h-005FFFh

SA3 000000011 8/4 006000h-007FFFh

SA4 000000100 8/4 008000h-009FFFh

SA5 000000101 8/4 00A000h-00BFFFh

SA6 000000110 8/4 00C000h-00DFFFh

SA7 000000111 8/4 00E000h-00FFFFh

Bank 1

SA8 000001xxx 64/32 010000h-01FFFFh

SA9 000010xxx 64/32 020000h-02FFFFh

SA10 000011xxx 64/32 030000h-03FFFFh

SA11 000100xxx 64/32 040000h-04FFFFh

Bank 1

Bank 1

Bank 2

SA12 000101xxx 64/32 050000h-05FFFFh

SA13 000110xxx 64/32 060000h-06FFFFh

SA14 000111xxx 64/32 070000h-07FFFFh

SA15 001000xxx 64/32 080000h-08FFFFh

SA16 001001xxx 64/32 090000h-09FFFFh

SA17 001010xxx 64/32 0A0000h-0AFFFFh

SA18 001011xxx 64/32 0B0000h-0BFFFFh

SA19 001100xxx 64/32 0C0000h-0CFFFFh

SA20 001101xxx 64/32 0D0000h-0DFFFFh

SA21 001110xxx 64/32 0E0000h-0EFFFFh

SA22 001111xxx 64/32 0F0000h-0FFFFFh

SA23 010000xxx 64/32 100000h-10FFFFh

SA24 010001xxx 64/32 110000h-11FFFFh

SA25 010010xxx 64/32 120000h-12FFFFh

SA26 010011xxx 64/32 130000h-13FFFFh

SA27 010100xxx 64/32 140000h-14FFFFh

Bank 2

SA28 010101xxx 64/32 150000h-15FFFFh

SA29 010110xxx 64/32 160000h-16FFFFh

SA30 010111xxx 64/32 170000h-17FFFFh

SA31 011000xxx 64/32 180000h-18FFFFh

SA32 011001xxx 64/32 190000h-19FFFFh

SA33 011010xxx 64/32 1A0000h-1AFFFFh

SA34 011011xxx 64/32 1B0000h-1BFFFFh

SA35 011100xxx 64/32 1C0000h-1CFFFFh

SA36 011101xxx 64/32 1D0000h-1DFFFFh

SA37 011110xxx 64/32 1E0000h-1EFFFFh

SA38 0111 11xxx 64/32 1F0000h-1FFFFFh

Sector Address

A20–A12

Sector Size

(Kbytes/Kwords)

(x8)

Address Range

(x16)

Address Range

000000h–000FFFh

001000h–001FFFh

002000h–002FFFh

003000h–003FFFh

004000h–004FFFh

005000h–005FFFh

006000h–006FFFh

007000h–007FFFh

008000h–00FFFFh

010000h–017FFFh

018000h–01FFFFh

020000h–027FFFh

028000h–02FFFFh

030000h–037FFFh

038000h–03FFFFh

040000h–047FFFh

048000h–04FFFFh

050000h–057FFFh

058000h–05FFFFh

060000h–067FFFh

068000h–06FFFFh

070000h–077FFFh

078000h–07FFFFh

080000h–087FFFh

088000h–08FFFFh

090000h–097FFFh

098000h–09FFFFh

0A0000h–0A7FFFh

0A8000h–0AFFFFh

0B0000h–0B7FFFh

0B8000h–0BFFFFh

0C0000h–0C7FFFh

0C8000h–0CFFFFh

0D0000h–0D7FFFh

0D8000h–0DFFFFh

0E0000h–0E7FFFh

0E8000h–0EFFFFh

0F0000h–0F7FFFh

0F8000h–0FFFFFh

November 12, 2001 Am41DL32x4G 19

Page 21

PRELIMINARY

Ta ble 8. Bottom Boot Sector Addresses (Continued)

Sector

Am29DL324GB

Am29DL323GB

Am29DL322GB

SA39 100000xxx 64/32 200000h-20FFFFh 100000h–107FFFh

SA40 100001xxx 64/32 210000h-21FFFFh 108000h–10FFFFh

SA41 100010xxx 64/32 220000h-22FFFFh 110000h–117FFFh

SA42 100011xxx 64/32 230000h-23FFFFh 118000h–11FFFFh

SA43 100100xxx 64/32 240000h-24FFFFh 120000h–127FFFh

SA44 100101xxx 64/32 250000h-25FFFFh 128000h–12FFFFh

SA45 100110xxx 64/32 260000h-26FFFFh 130000h–137FFFh

SA46 100111xxx 64/32 270000h-27FFFFh 138000h–13FFFFh

SA47 101000xxx 64/32 280000h-28FFFFh 140000h–147FFFh

SA48 101001xxx 64/32 290000h-29FFFFh 148000h–14FFFFh

SA49 101010xxx 64/32 2A0000h-2AFFFFh 150000h–157FFFh

SA50 101011xxx 64/32 2B0000h-2BFFFFh 158000h–15FFFFh

SA51 101100xxx 64/32 2C0000h-2CFFFFh 160000h–167FFFh

SA52 101101xxx 64/32 2D0000h-2DFFFFh 168000h–16FFFFh

SA53 101110xxx 64/32 2E0000h-2EFFFFh 170000h–177FFFh

SA54 101111xxx 64/32 2F0000h-2FFFFFh 178000h–17FFFFh

Bank 2

Bank 2

SA55 111000xxx 64/32 300000h-30FFFFh 180000h–187FFFh

Bank 2

SA56 110001xxx 64/32 310000h-31FFFFh 188000h–18FFFFh

SA57 110010xxx 64/32 320000h-32FFFFh 190000h–197FFFh

SA58 110011xxx 64/32 330000h-33FFFFh 198000h–19FFFFh

SA59 110100xxx 64/32 340000h-34FFFFh 1A0000h–1A7FFFh

SA60 110101xxx 64/32 350000h-35FFFFh 1A8000h–1AFFFFh

SA61 110110xxx 64/32 360000h-36FFFFh 1B0000h–1B7FFFh

SA62 110111xxx 64/32 370000h-37FFFFh 1B8000h–1BFFFFh

SA63 111000xxx 64/32 380000h-38FFFFh 1C0000h–1C7FFFh

SA64 111001xxx 64/32 390000h-39FFFFh 1C8000h–1CFFFFh

SA65 111010xxx 64/32 3A0000h-3AFFFFh 1D0000h–1D7FFFh

SA66 111011xxx 64/32 3B0000h-3BFFFFh 1D8000h–1DFFFFh

SA67 111100xxx 64/32 3C0000h-3CFFFFh 1E0000h–1E7FFFh

SA68 111101xxx 64/32 3D0000h-3DFFFFh 1E8000h–1EFFFFh

SA69 111110xxx 64/32 3E0000h-3EFFFFh 1F0000h–1F7FFFh

SA70 111111xxx 64/32 3F0000h-3FFFFFh 1F8000h–1FFFFFh

Sector Address

A20–A12

Sector Size

(Kbytes/Kwords)

(x8)

Address Range

(x16)

Address Range

Note: The address range is A20:A-1 in byte mode (BYTE#=VIL) or A20:A0 in word mode (BYTE#=VIH). The bank address bits

are A20–A18 for Am29DL322GB, A20 and A19 for Am29DL323GB, and A20 for Am29DL324GB.

Ta ble 9. Bottom Boot SecSi Sector Addresses

Device

Am29DL322GB, Am29DL323GB

Am29DL324GB

Sector Address

A20–A12

,

000000xxx 256/128 000000h-0000FFh 00000h-0007Fh

Sector Size

(bytes/words)

(x8)

Address Range

(x16)

Address Range

20 Am41DL32x4G November 12, 2001

Page 22

PRELIMINARY

Autoselect Mod e

The autoselect mode provides manufacturer and device identifica tion, and s ector prote ction verification,

through identifier codes output on DQ7–DQ0. This

mode is primarily intended for programming equipment to automatically match a device to be

programmed with its corresponding programming

algorithm.

The autoselect codes can also be accessed in-system

through the command register. The host system can

issue the autoselect command via the command register, as shown in Tables 15 and 17. This method does

not require V

. Refer to the Auto se lect Com ma nd S e-

ID

quence section for more information.

Sector/Sector Block Protection and Unprotection

(Note: For the following discussion, the term “sector”

applies to both sectors and sector blocks. A sector

block consists of two or more adjacent sectors that are

protected or unprotected at the same time (see Table

10).

Table 10. Top Boot Sector/Sector Block

Addresses for Protection/Unprotection

Sector A20–A12

SA0

SA1-SA3

SA4-SA7

SA8-SA11

SA12-SA15

SA16-SA19

SA20-SA23

SA24-SA27

SA28-SA31

SA32-SA35

SA36-SA39

SA40-SA43

SA44-SA47

SA48-SA51

SA52-SA55

SA56-SA59

SA60-SA62

SA63

SA64

SA65

SA66

000000XXX 64 Kbytes

000001XXX,

000010XXX

000011XXX

0001XXXXX 256 (4x64) Kbytes

0010XXXXX 256 (4x64) Kbytes

0011XXXXX 256 (4x64) Kbytes

0100XXXXX 256 (4x64) Kbytes

0101XXXXX 256 (4x64) Kbytes

0110XXXXX 256 (4x64) Kbytes

0111XXXXX 256 (4x64) Kbytes

1000XXXXX 256 (4x64) Kbytes

1001XXXXX 256 (4x64) Kbytes

1010XXXXX 256 (4x64) Kbytes

1011XXXXX 256 (4x64) Kbytes

1100XXXXX 256 (4x64) Kbytes

1101XXXXX 256 (4x64) Kbytes

1110XXXXX 256 (4x64) Kbytes

111100XXX,

111101XXX,

111110XXX

111111000 8 Kbytes

111111001 8 Kbytes

111111010 8 Kbytes

111111011 8 Kbytes

Sector/

Sector Block Size

192 (3x64) Kbytes

192 (4x64) Kbytes

Sector A20–A12

SA67 111111100 8 Kbytes

SA68

SA69

SA70

111111101 8 Kbytes

111111110 8 K by tes

111111111 8 Kbytes

Sector/

Sector Block Size

The hardware sector protection feature disables both

program and erase operations in any sector. The hardware sector unprotection feature re-enables both

program an d er ase ope rat ions i n pre vious ly pr otect ed

sectors. Note that the sector unprotect algorithm unprotects all sectors in parallel. All previously protected

sectors must be individually re-protected. To change

data in protected sectors efficiently, the temporary

sector un protect function is available. See “Temporary

Sector/Sector Block Unprotect”.

Sector protection and unprotection can be implemented as follows.

Sector prote c tion an d u npr o tec ti on requi res V

on the

ID

RESET# pin only, and can be implemented either

in-system or via programm ing equipment. Fig ure 2

shows the algorithms and Figure 26 shows the timing

diagram. This method uses standard microprocessor

bus cycle timi ng. For sector un prot ect, all unpro tected

sectors must first be protected prior to the first sector

unprotect write cycle.

The device is shipped with all sectors unprotected.

It is possible to determine whether a sector is pro-

tected or unprotected. See the Autos elect Mode

section for details.

Write Protect (WP#)

The Write Pro tect function pr ovides a hardw are

method of protecting certain boot sectors without

using V

WP#/ACC pin.

If the system asserts V

vice disables program and erase functions in the two

“outermost” 8 Kbyte boot sectors independently of

whether those sectors were protected or unprotected

using the m et hod d escrib ed i n “Sector/Sector Blo ck

Protection and Unprotection”. The two outermost 8

Kbyte boot sectors are the two sectors containing the

lowest addresses in a top-boot-configured device, or

the two sectors containing the highest addresses in a

top-boot-configured device.

If the system asserts V

vice reverts to whether the two outermost 8 Kbyte boot

sectors were last set to be protected or unprotected.

That is, sector pr ote ct ion or unp rote ct ion for the se two

sectors depends on whether they were last protected

or unprotect ed using the me thod descr ibed in “Sec-

tor/Sector Block Protection and Unprotection”.

. This function is one of two provided by the

ID

on the WP#/AC C pi n, th e de -

IL

on the WP#/ACC pi n, the de -

IH

November 12, 2001 Am41DL32x4G 21

Page 23

PRELIMINARY

Note that the WP#/ACC pin must not be left floating or

unconne cted; inc onsis tent be havior of th e devi ce may

result.

Temporary Sector/Sector Block Unprotect

(Note: For the following discussion, the term “sector”

applies to both sectors and sector blocks. A sector

block consists of two or more adjacent sectors that are

protected or unprotected at the same time (see Table

10).

This feature all ows tempo rary unprote ction of previ-

ously protected sectors to change data in-system. The

Sector Un prote ct m ode i s ac ti vated b y s etting th e RESET# pin to V

formerly pr otected sec tors can be programm ed or

erased by se lectin g the sector addres ses. On ce V

removed from the RESET# pin, all the previously protected sectors are protected again. Figure 1 shows the

algorithm, and Figure 25 shows the timing diagrams,

for this feature.

(11.5 V – 12.5 V). During this mode,

ID

is

ID

START

RESET# = V

(Note 1)

Perform Erase or

Program Operations

RESET# = V

Temporary Sector

Unprotect Comp leted

(Note 2)

Notes:

1. All protected sectors unprotected (If WP#/ACC = V

outermost boot sectors will remain protected).

2. All previously protected sectors are protected once

again.

ID

IH

,

IL

Figure 1. Temporary Sector Unprotect Operation

22 Am41DL32x4G November 12, 2001

Page 24

PRELIMINARY

Temporary Sector

Unprotect Mode

Increment

PLSCNT

No

PLSCNT

= 25?

Yes

Device failed

Sector Protect

Algorithm

START

PLSCNT = 1

RESET# = V

Wait 1 µs

No

First Write

Cycle = 60h?

Set up sector

address

Sector Protect:

Write 60h to sector

address with

A6 = 0, A1 = 1,

A0 = 0

Wait 150 µs

Verify Sector

Protect: Write 40h

to sector address

with A6 = 0,

A1 = 1, A0 = 0

Read from

sector address

with A6 = 0,

A1 = 1, A0 = 0

No

Data = 01h?

Protect another

sector?

Remove V

from RESET#

Write reset

command

Sector Protect

complete

Yes

Yes

No

START

Protect all sectors:

The indicated portion

of the sector protect

ID

Reset

PLSCNT = 1

Yes

ID

algorithm must be

performed for all

unprotected sectors

prior to issuing the

first sector

unprotect address

Increment

PLSCNT

No

PLSCNT

= 1000?

Yes

Device failed

Sector Unprotect

PLSCNT = 1

RESET# = V

Wait 1 µs

First Write

Cycle = 60h?

No

All sectors

protected?

Set up first sector

address

Sector Unprotect:

Write 60h to sector

address with

A6 = 1, A1 = 1,

A0 = 0

Wait 15 ms

Verify Sector

Unprotect: Write

40h to sector

address with

A6 = 1, A1 = 1,

A0 = 0

Read from

sector address

with A6 = 1,

A1 = 1, A0 = 0

No

Data = 00h?

Last sector

verified?

Remove V

from RESET#

Yes

Yes

Yes

Yes

ID

No

Temporary Sector

Unprotect Mode

Set up

next sector

address

No

ID

Algorithm

Write reset

command

Sector Unprotect

complete

Note: The term “sector” in the figure applies to both sectors and sector blocks.

Figure 2. In-System Sector/Sector Block Protect and Unprotect Algorithms

November 12, 2001 Am41DL32x4G 23

Page 25

PRELIMINARY

SecSi (Secured Silicon) Sector Flash Memory Region

The SecSi (Secured Silicon) Sector feature provides a

Flash memory region that enables per manent part

identification throu gh an Electroni c Serial Number

(ESN). The SecSi Sector uses a SecSi Sector Indicator Bit to indicate whether or not the Sec Si Sector is

locked when shipped from the factory. This bit is permanently se t at the factory an d cannot be chan ged,

which prevents cloning of a fa ctory locked pa rt. This

ensures the security of the ESN onc e the produc t is

shipped to the field.

AMD offers the device with the SecSi Sector either

factory locked or customer lockable. The factory-locked version is always protected when shipped

from the factor y, and has the SecSi S ector Indicato r

Bit perman ently set to a “1.” The customer-lockable

version is shipped with the unprotected, allowing customers to utilize the that sector in any manner they

choose. The customer-lockable version has the SecSi

Sector Indicator Bit permanently set to a “0.” Thus, the

SecSi Sector Indicat or Bit pre vents c ustomer -loc kable

devices from being used to repl ace devices that are

factory locked .

The system accesses the SecSi Sector through a

command sequence (see “Enter SecSi Se ctor/Exit

SecSi Sector Command Sequence”). After the system

has written the Enter SecSi Sector command sequence, it may read the SecSi Sector by using the

addresses normally occupied by the boot sectors. This

mode of operation c ontinues un til the sys tem issues

the Exit SecSi Sector command sequence, or until

power is remove d from the device. O n power-up, or

following a hardware reset, the device reverts to sending commands to the boot sectors.

Factory Locked: SecSi Sector Programmed and Protected At the Factory

In a factory locked device, the SecSi Sector is protected when the device is shipped from the factory.

The SecSi Sector cannot be modified in any way. The

device is available preprogrammed with a random, secure ESN only.

In the Top Boot device the ESN is located at addresses 1FF000h–1FF007h in word mode (or addresses 3FE000h–3FE00Fh in byte mode). In the

Bottom Boot device the ESN is located at addresses

00000h–00007Fh in word mode (or

000000h–0000FFh in byte mode).

Customer Lockable: SecSi Sector NOT Programmed or Protected At the Factory

If the security feature is not required, the SecSi Sector

can be treated as an additional Flash memory space,

expanding the size of the availabl e Flash array. The

SecSi Secto r c an be r ead any nu mber of tim es, but

can be programmed and locked only once, and cannot

be erased. Note that the accelerated programming

(ACC) and unlock bypass functions are not available

when programming the SecSi Sector.

The SecSi Sector area can be protected using one of

the following procedures:

■ Write the three-cycle Enter SecSi Sector Region

command sequ en ce , and then fo llow the in-s y stem

sector protect algorithm as shown in Figure 2, except that RE SET # ma y be at e it her V

or VID. This

IH

allows in-system protection of the without raising

any device pin to a high voltage. Note that this

method is only applicable to the SecSi Sector.

■ Write the three-cycle Enter SecSi Sector Region

command sequence, and then use the alternate

method of s ector prote ction de scribed in the “Sec-

tor/S ector Block Pro tecti on and Unprote ction”.

Once the SecSi Sector is locked and verified, the system must write the Exit SecSi Sector Region

command sequenc e to return to reading and writing

the remainder of the arr ay.

The SecSi Sector protection must be used with caution since, once protected, there is no procedure

available for unprotecting the SecSi Sector area and

none of th e bits in the Sec Si Sec tor m emory space

can be modified in any way.

Hardware Data Protection

The command se qu enc e requi reme nt of un lo ck cy cle s

for programming or erasing p rovides da ta protection

against inadvertent writes (refer to Tables 15 and 17

for command definitions). In addition, the following

hardware data protection measures prevent accidental

erasure or programming, which might otherwise be

caused by spurio us system leve l signals during V

power-up an d p owe r -down tr a nsit ions , o r from s yst em

noise.

Low V

When V

Write Inhibit

CC

is less than V

CC

, the device does not ac-

LKO

cept any w rite cyc les. Thi s pro tects data during V

power-up and power-down. The command register

and all internal program/erase circuits are disabled,

and the de vice r esets to re ading arra y da ta. Sub sequent writes are ignored until V

is greater than V

CC

The system must provide the proper signals to the

control pins to prevent unintentional writes when V

is greater than V

LKO

.

Write Pulse “Glitch” Pro tect ion

Noise pulses of less than 5 ns (typical) on OE#, CE#f

or WE# do not initiate a write cycle.

CC

CC

LKO

CC

.

24 Am41DL32x4G November 12, 2001

Page 26

PRELIMINARY

Logical Inhibit

Write cycles are inhibited by holding any one of OE# =

, CE#f = VIH or WE# = VIH. To initiate a write cycle,

V

IL

CE#f and WE# must be a logical zero while OE# is a

logical one.

Power-Up Write Inhibit

If WE# = CE#f = V

and OE# = VIH during power up,

IL

the device does not accept comman ds on the rising

edge of WE#. The internal state machine is automatically reset to reading array data on power-up.

COMMON FLASH MEMORY INTERFACE (CFI)

The Common Flash Interface (CFI) specification outlines device and host system software interrogation

handshake, which allows specific vendor-specified

software al gorithms to be used for entire famili es of

devices. Software support can then be device-independent, JEDEC ID-independent, and forward- and

backward-compatible for the specified flash device

families. Flash vendors can standardize their existing

interfaces for long-term compatibility.