MMA955xL Intelligent,

Motion-Sensing Platform Hardware

Reference Manual

Devices Supported:

MMA9550L

MMA9551L

MMA9553L

MMA9559L

Document Number: MMA955xLHWRM

Rev. 1.0, 8/2013

How to Reach Us:

Home Page:

freescale.com

Web Support:

freescale.com/support

Information in this document is provided solely to enable system and software

implementers to use Freescale products. There are no express or implied copyright

licenses granted hereunder to design or fabric ate any int egrate d circuit s based on the

information in this document.

Freescale reserves the right to make changes without further notice to any products

herein. Freescale makes no warranty, representation, or guarantee regarding the

suitability of its products for any particular purpose, nor does Freescale assume any

liability arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation consequential or incidental

damages. “Typical” parameters that may be provided in Freescale data sheets and/or

specifications can and do vary in different applications, and actual perfor mance may

vary over time. All operating parameters, including “typicals,” must be validated for

each customer application by customer’s technical experts. Freescale do es not convey

any license under its patent rights nor the rights of others. Freescale sells products

pursuant to standard terms and conditions of sale, which can be found at the following

address: freescale.com/salestermsandconditions.

Freescale, the Freescale logo, CodeWarrior , ColdFire, Energy Ef ficient Solutions logo,

and Xtrinsic are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm.

Off. All other product or service names are the property of their respective owners.

© 2013 Freescale Semiconductor, Inc.

Document Number: MMA955xLHWRM

Rev. 1.0

8/2013

Contents

Chapter 1 About This Document

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.1.1 Purpose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.1.2 Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2 Terms and acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.3 Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.4 Register figure conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.5 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Chapter 2 Introduction

2.1 Hardware features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.2 Software features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3 Typical applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

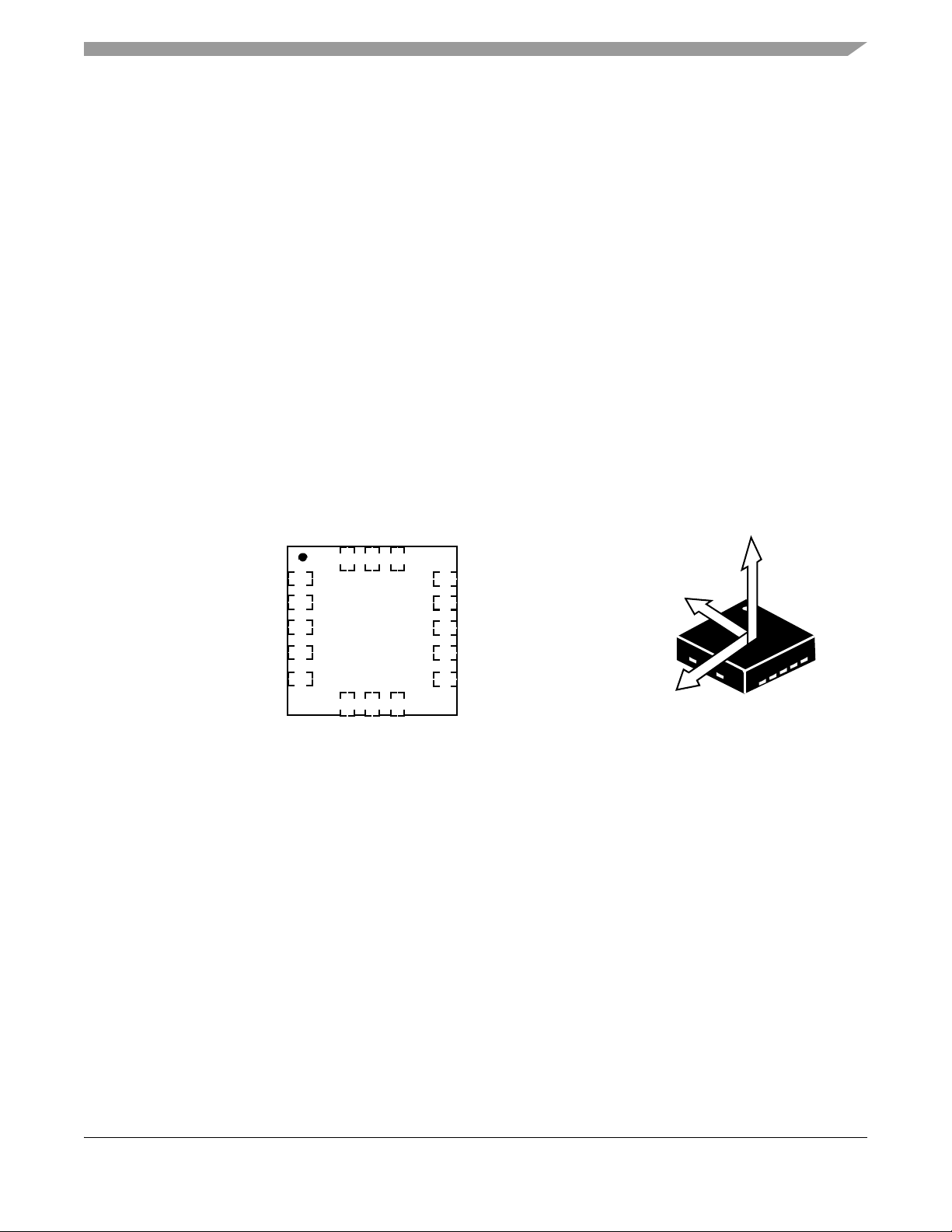

Chapter 3 Pins and Connections

3.1 Package pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

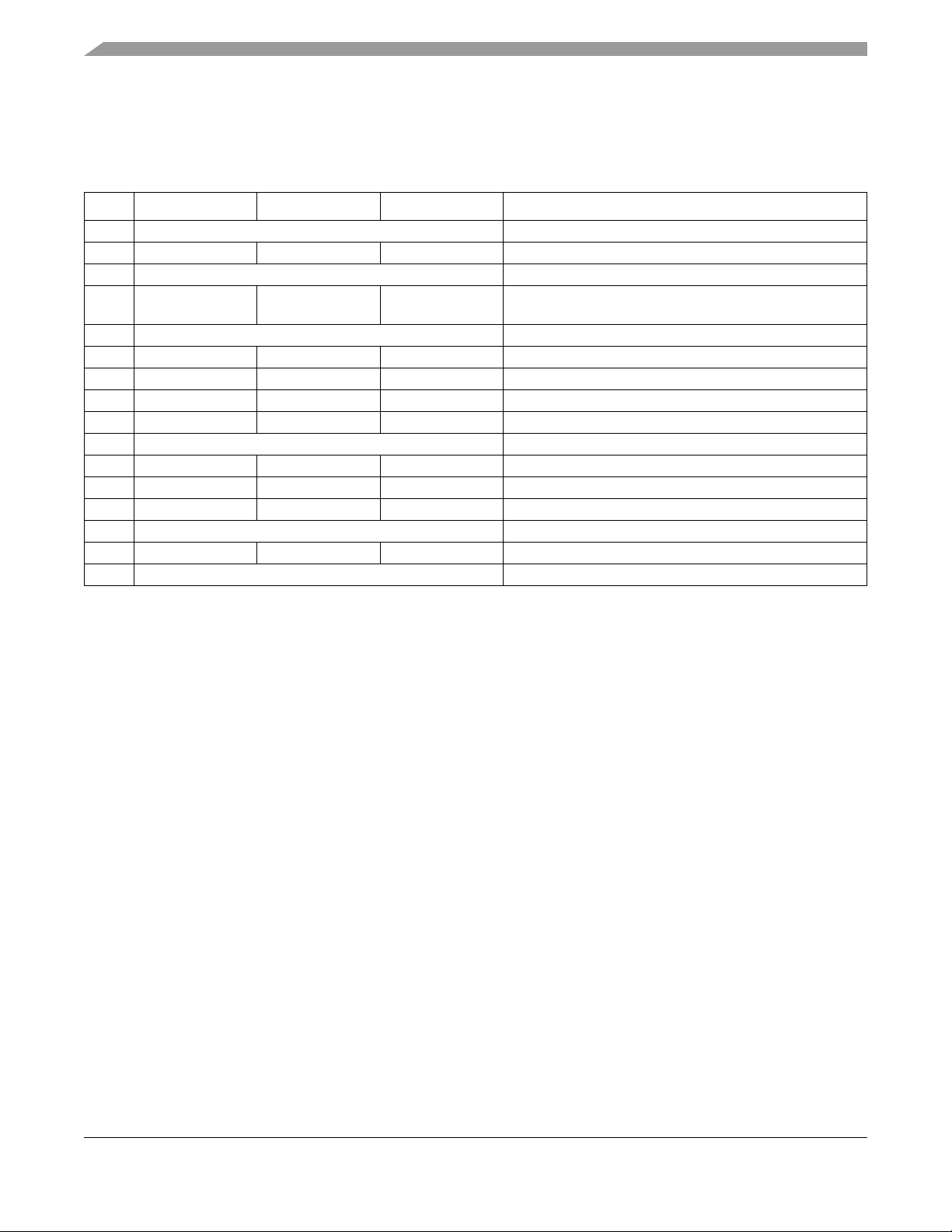

3.1.1 Pin functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

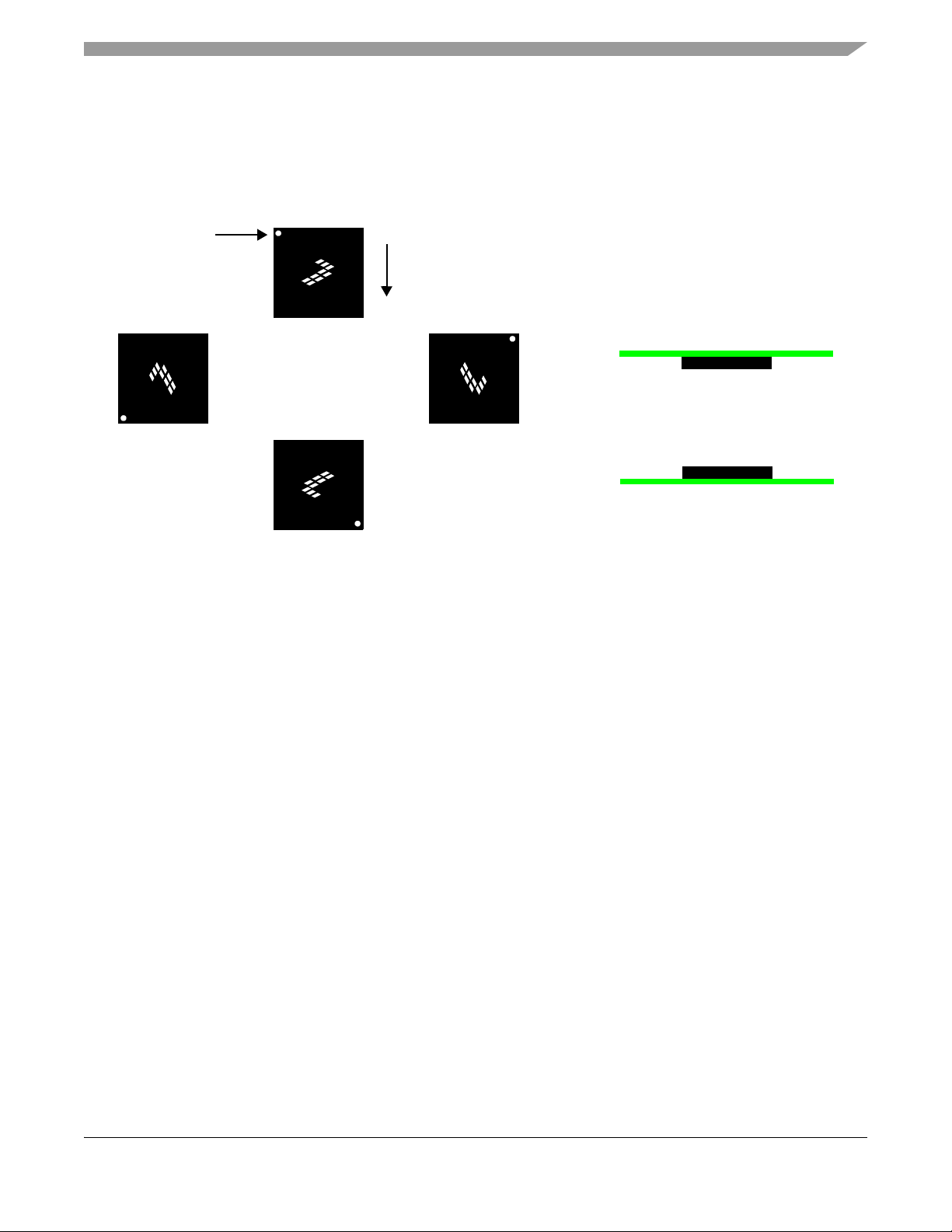

3.1.2 Sensing direction and output response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.2 Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.2.1 V

3.2.2 V

3.2.3 RESETB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.2.4 Slave I

3.2.5 Master I

3.2.6 Analog-to-digital conversion: AN0, AN1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2.7 Rapid General-Purpose I/O: RGPIO[9:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2.8 Interrupts: INT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2.9 Debug/mode control: BKGD/MS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2.10 Timer: PDB_A and PDB_B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.2.11 Slave SPI interface: SCLK, SDI, SDO and SSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.3 System connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

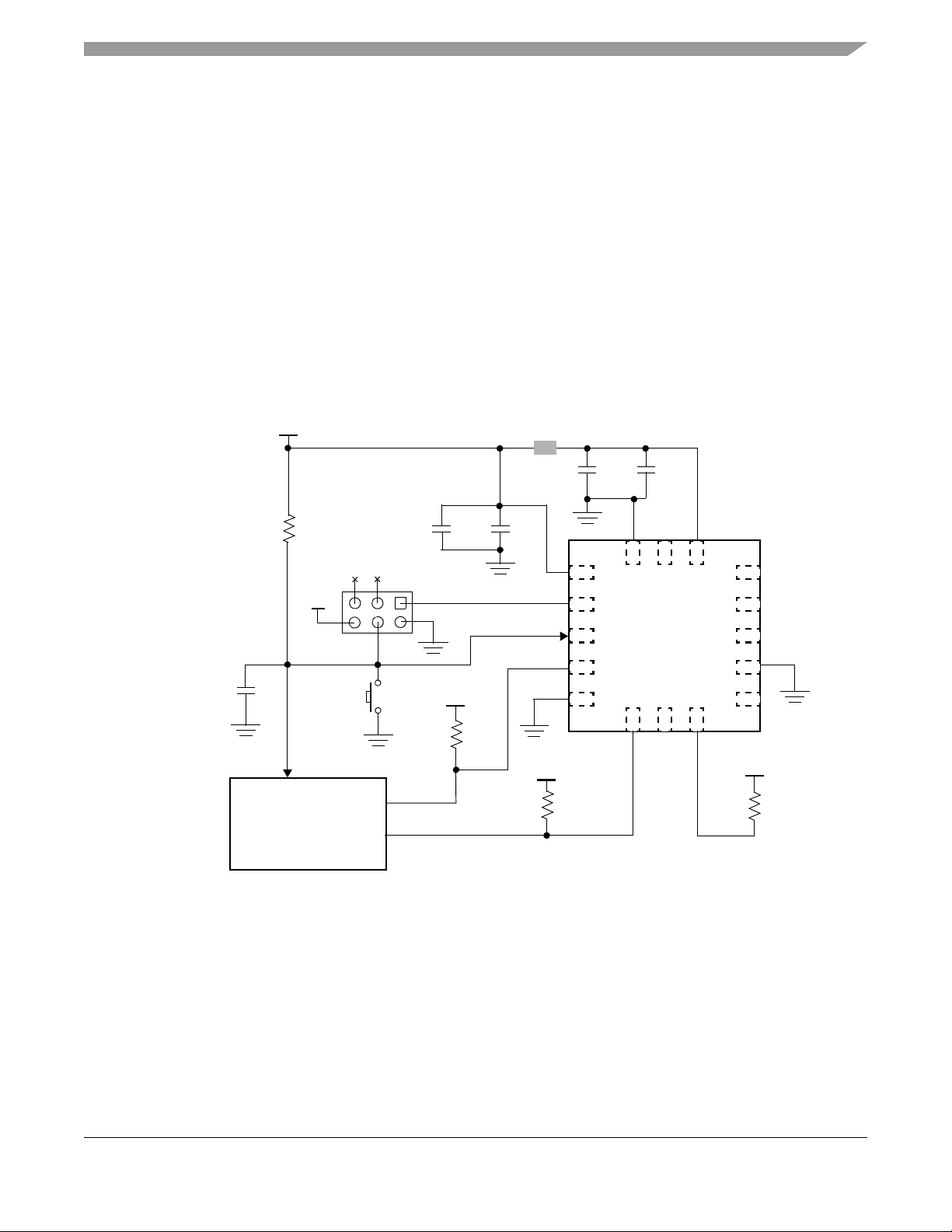

3.3.1 Platform as an intelligent slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

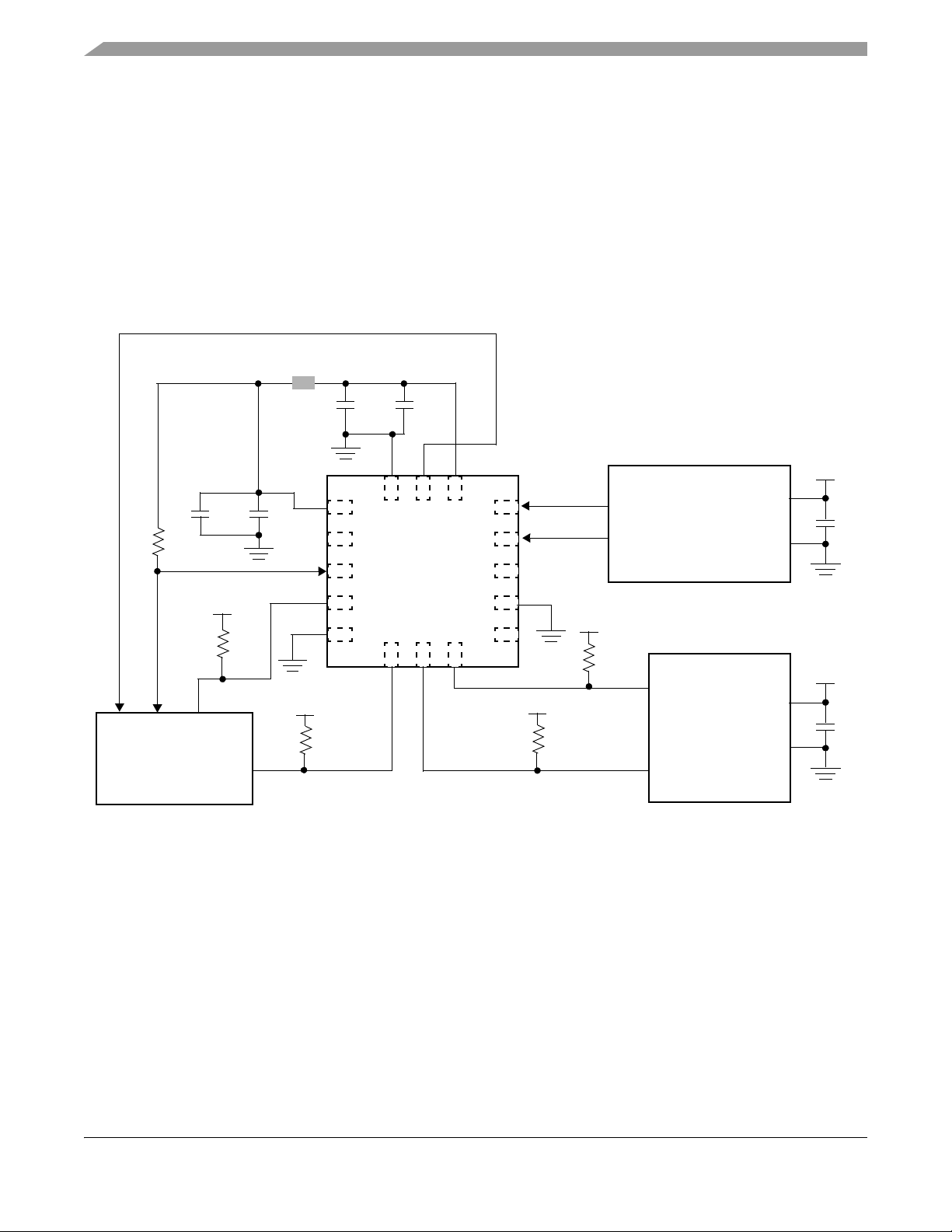

3.3.2 Platform as a sensor hub . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.3.3 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.3.4 RESETB pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.3.5 Background / mode select (BKGD/MS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

DD

DDA

and V

and V

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

SS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

SSA

C: SDA0 and SCL0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2

C: SDA1 and SCL1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

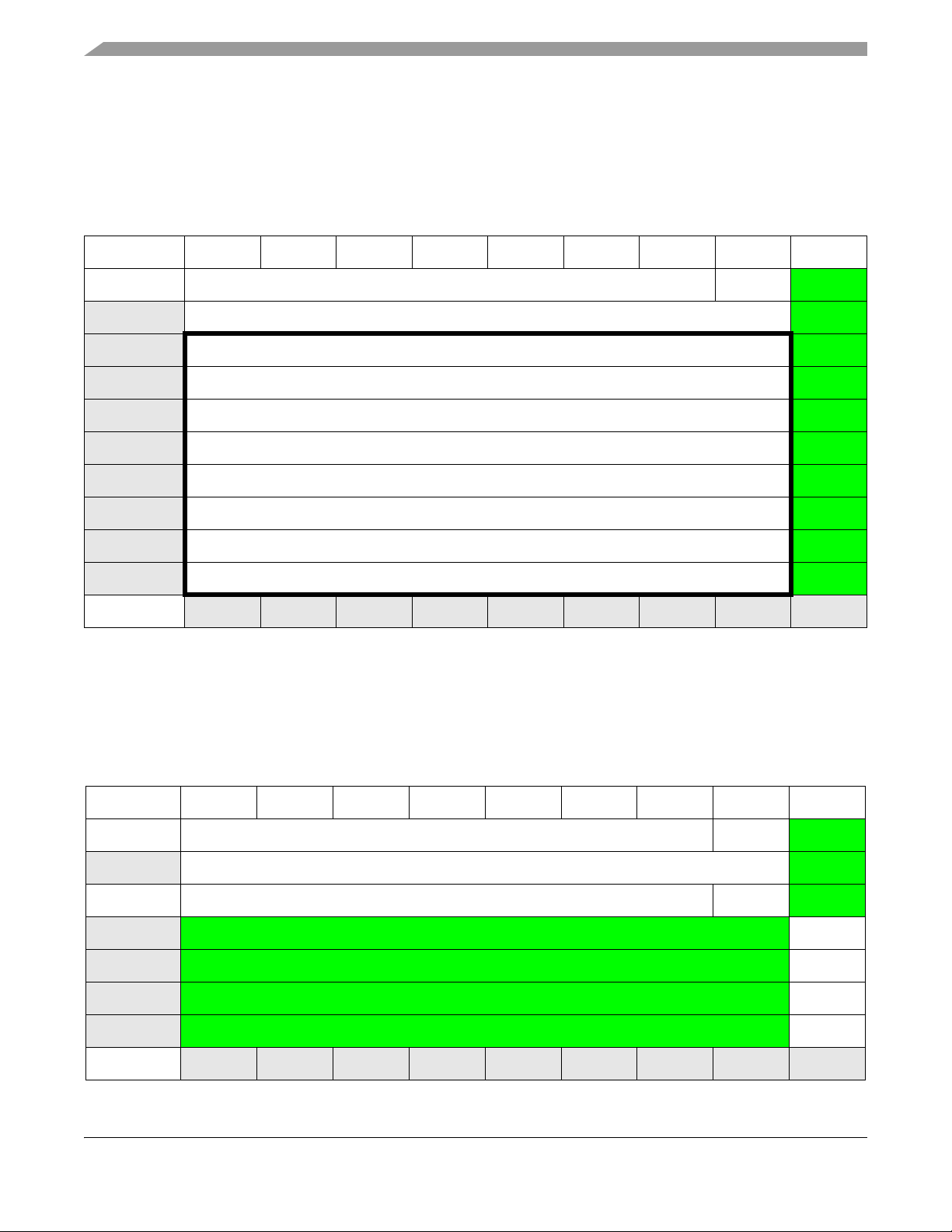

Chapter 4 Operational Phases and Modes of Operation

4.1 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.2 Frame structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.3 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.3.1 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.3.2 Additional timing parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3.3 Phase triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.4 Clock operation as a function of mode/phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 3

4.5 Power control modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Chapter 5 Memory Maps

5.1 High-level memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.2 Alignment issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.3 Memory-mapped components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.3.1 Interrupt controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.3.2 Nonvolatile register area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.3.3 RGPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.4 Detailed register set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

5.5 Interrupt vector table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.6 RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Chapter 6 Flash Memory Controller

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.2 Theory of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.3 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.3.1 Flash IDLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.3.2 Flash READ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.3.3 Flash PROGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.3.4 Flash ERASE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.4 Flash memory maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.4.1 Array memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.5 Flash registers and control bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.6 Flash memory map/register definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.6.1 Flash Options register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.7 Initialization information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.7.1 Factory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.7.2 End user . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.8 Programming model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.9 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Chapter 7 ROM

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

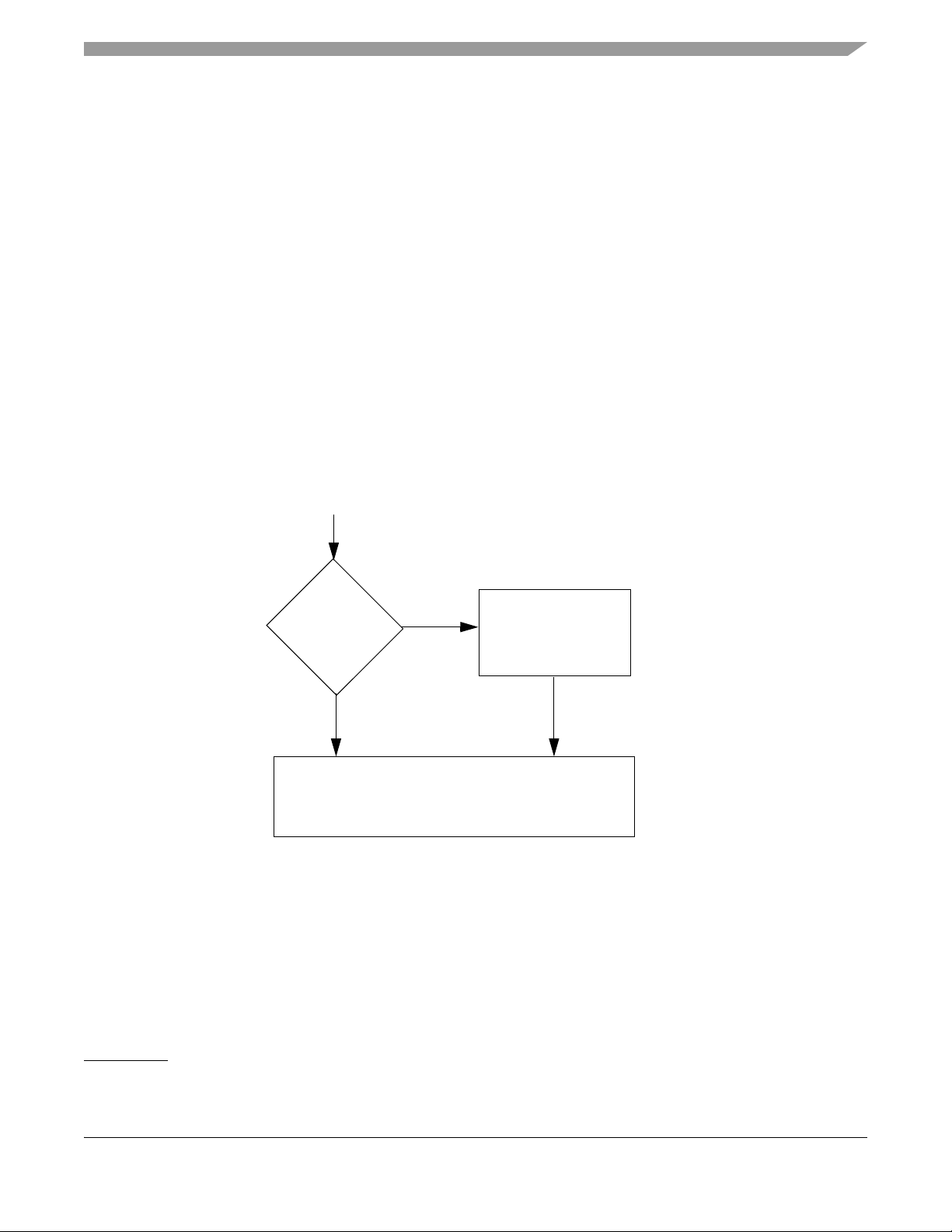

7.2 Boot ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

7.2.1 Boot Step 1: RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

7.2.2 Boot Step 2: Load PC and SSP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7.2.3 Boot Step 3: Load configuration parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7.2.4 Boot steps 4 and 9: For flash boots, jump to flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

7.2.5 Boot Step 5: Initialize Command Interpreter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

7.2.6 Boot Step 6: Launch ROM Command Interpreter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

7.3 Security and rights management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

7.3.1 Access and security rules of thumb . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

7.3.2 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

7.4 Rights management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7.4.1 Memory-map restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 4

7.4.2 Rights-management variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7.4.2.1 Device ID (DID) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7.4.2.2 Page-Release Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7.4.2.3 Hardware restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

7.5 ROM Command Interpreter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.5.1 Callable utilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.5.2 Packet transfers and commands overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

7.5.3 Common error codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

7.5.4 CI_DEV_INFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.5.4.1 CI_DEV_INFO command-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.5.4.2 CI_DEV_INFO response-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.5.4.3 CI_DEV_INFO access/security policies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

7.5.5 CI_READ_WRITE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.5.5.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.5.5.2 CI_READ_WRITE Read/Write memory command-packet format . . . . . . . . . . 85

7.5.5.3 CI_READ_WRITE Read/Write memory response-packet format . . . . . . . . . . . 87

7.5.5.4 CI_READ_WRITE access/security policies . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

7.5.5.5 CI_READ_WRITE Read/Write memory example . . . . . . . . . . . . . . . . . . . . . . . 88

7.5.6 CI_ERASE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.5.6.1 Erase-flash function description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.5.6.2 Erase-command packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.5.6.3 Erase command response-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

7.5.6.4 CI_ERASE access/security policies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

7.5.6.5 Erase example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

7.5.7 CI_CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.5.7.1 CI_CRC Checksum command-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.5.7.2 CRC response-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

7.5.7.3 CI_CRC access/security policies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

7.5.7.4 CRC example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.5.8 CI_RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

7.5.8.1 CI_RESET command-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

7.5.8.2 CI_RESET response-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.5.8.3 CI_RESET access/security policies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.5.9 CI_PROTECT and CI_UNPROTECT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.5.9.1 CI_PROTECT command-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.5.9.2 CI_UNPROTECT command-packet format . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.5.9.3 CI_PROTECT and CI_UNPROTECT response-packets format . . . . . . . . . . . . 99

7.5.9.4 CI_PROTECT and CI_UNPROTECT access/security policies . . . . . . . . . . . . . 99

7.6 User-callable ROM functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

7.6.1 RMF_GET_DEVICE_INFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.6.1.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.6.1.2 RMF_GET_DEVICE_INFO structure syntax . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.6.1.3 RMF_GET_DEVICE_INFO error codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.6.1.4 RMF_GET_DEVICE_INFO operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.6.1.5 RMF_GET_DEVICE_INFO access/security policies . . . . . . . . . . . . . . . . . . . 105

7.6.2 RMF_FLASH_PROGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.6.2.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.6.2.2 RMF_FLASH_PROGRAM input structure . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

7.6.2.3 RMF_FLASH_PROGRAM output structure . . . . . . . . . . . . . . . . . . . . . . . . . . 106

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 5

7.6.2.4 RMF_FLASH_PROGRAM access/security policies . . . . . . . . . . . . . . . . . . . . 107

7.6.3 RMF_FLASH_ERASE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.6.3.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.6.3.2 RMF_FLASH_ERASE input structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

7.6.3.3 RMF_FLASH_ERASE output structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

7.6.3.4 RMF_FLASH_ERASE access/security policies . . . . . . . . . . . . . . . . . . . . . . . 110

7.6.4 RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT . . . . . . . . . . . . . . . . . . . .111

7.6.4.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.6.4.2 RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT input structure . 111

7.6.4.3 RMF_FLASH_PROTECT and RMF_FLASH_UNPROTECT output structure 111

7.6.4.4 RMF_FLASH_PROTECT/UNPROTECT access/security policies . . . . . . . . . 111

7.6.5 RMF_FLASH_UNSECURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

7.6.5.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.6.5.2 RMF_FLASH_UNSECURE input structure . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

7.6.5.3 RMF_FLASH_UNSECURE output structure . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.6.5.4 RMF_FLASH_UNSECURE access/security policies . . . . . . . . . . . . . . . . . . . 112

7.6.6 RMF_CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.6.6.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.6.6.2 RMF_CRC input structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.6.6.3 RMF_CRC output structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.6.6.4 RMF_CRC error codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.6.6.5 RMF_CRC access/security policies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Chapter 8 Slave Port Interface

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

8.2 I

8.3 Data coherency issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

8.4 Slave memory map/register definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

2

C features and limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

8.2.1 I

8.2.2 I

2

C features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

2

C limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

8.2.3 SPI features and limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

8.2.4 SPI features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

8.2.5 SPI limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

8.3.1 Read buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

8.3.2 Binary semaphore (mutex) operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

8.4.1 Slave memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

8.4.2 Slave Port Interface register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.4.2.1 Slave Port Mailbox Register n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.4.2.2 Slave Port Binary Semaphore (Mutex) Register n . . . . . . . . . . . . . . . . . . . . . 126

2

8.4.2.3 Slave Port I

C address register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

8.4.2.4 Slave Port Status and Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

8.4.2.5 Slave Port Write Status Register 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

8.4.2.6 Slave Port Write Status Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

8.4.2.7 Slave Port Write Status Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

8.4.2.8 Slave Port Write Status Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

8.4.2.9 Slave Port Read Status Register 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

8.4.2.10 Slave Port Read Status Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

8.4.2.11 Slave Port Read Status Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

8.4.2.12 Slave Port Read Status Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 6

8.4.2.13 Slave Port Mutext Timeout Register n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

8.4.2.14 Slave Port Output Interrupt Control Register . . . . . . . . . . . . . . . . . . . . . . . . 138

8.4.3 Output interrupt timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

2

8.5 I

C serial protocol and timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

8.5.1 Baud rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

8.5.2 Serial-addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

8.5.3 Start, Stop and Repeated Start conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

8.5.4 Bit transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

8.5.5 Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

8.5.6 Slave address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

8.5.7 Message format for writing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

8.5.8 Message format for reading the platform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

8.6 SPI serial protocol and timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

8.6.1 SPI read operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

8.6.2 SPI write operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

8.7 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

8.7.1 Mailbox interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

8.7.2 Semaphore interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

8.8 Reset operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Chapter 9 Inter-Integrated Circuit

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

9.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

9.1.2 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

9.1.3 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

9.2 External signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

9.2.1 Serial clock line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

9.2.2 Serial data line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

9.3 Register definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

9.3.1 I

9.3.2 I

9.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

9.4.1 I

2

C memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

2

C register details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

9.3.2.1 I

9.3.2.2 I

9.3.2.3 I

9.3.2.4 I

9.3.2.5 I

9.3.2.6 I

9.3.2.7 I

2

C protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

2

C Address Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

2

C Frequency Divider register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

2

C Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

2

C Status register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

2

C Data I/O register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

2

C Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

2

C Programmable Input Glitch Filter register . . . . . . . . . . . . . . . . . . . . . . . . . 167

9.4.1.1 START signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

9.4.1.2 Slave address transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

9.4.1.3 Data transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

9.4.1.4 STOP signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

9.4.1.5 Repeated START signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

9.4.1.6 Arbitration procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

9.4.1.7 Clock synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

9.4.1.8 Handshaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

9.4.1.9 Clock stretching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 7

9.4.2 10-bit address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

9.4.2.1 Master-transmitter addresses a slave-receiver . . . . . . . . . . . . . . . . . . . . . . . . 171

9.4.2.2 Master-receiver addresses a slave-transmitter . . . . . . . . . . . . . . . . . . . . . . . . 172

9.4.3 Address matching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

9.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

9.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

9.6.1 Byte-transfer interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

9.6.2 Address-detect interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

9.6.3 Exit from Low-Power/Stop modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

9.6.4 Arbitration-lost interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

9.6.5 Programmable, input-glitch filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

9.6.6 Address-matching wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

9.7 Initialization/application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Chapter 10 Analog Front End

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

10.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

10.3 AFE architecture and theory of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

10.3.1 ADC operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

10.3.2 Accelerometer principle of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

10.4 Memory map overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Chapter 11 System Integration Module

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

11.2 Reset generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

11.2.1 Reset sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

11.2.2 Reset outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

11.3 Mode control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

11.3.1 STOP mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

11.3.2 DEBUG modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

11.4 Oscillator control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

11.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

11.4.2 CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

11.5 Clock gating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

11.6 SIM memory map and registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

11.6.1 SIM memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

11.6.2 SIM registers descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

11.6.2.1 STOP control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

11.6.2.2 Frame Control and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

11.6.2.3 Reset Control and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

11.6.2.4 Peripheral Clock Enable Register 0 for STOP

11.6.2.5 Peripheral Clock Enable Register 1 for STOP

11.6.2.6 Peripheral Clock Enable Register 0 for STOP

11.6.2.7 Peripheral Clock Enable Register 1 for STOP

11.6.2.8 Peripheral Clock Enable Register 0 for RUN Mode . . . . . . . . . . . . . . . . . . . 209

11.6.2.9 Peripheral Clock Enable Register 1 for RUN Mode . . . . . . . . . . . . . . . . . . . 211

11.6.2.10 Pin Mux Control Register0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

11.6.2.11 Pin Mux Control Register1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

11.6.2.12 Pin Mux Control Register2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Mode . . . . . . . . . . . . . . . . 203

FC

Mode . . . . . . . . . . . . . . . . 205

FC

Mode . . . . . . . . . . . . . . . . 206

SC

Mode . . . . . . . . . . . . . . . . 208

SC

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 8

Chapter 12 On-Chip Oscillator

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

12.2 High-level overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

12.3 CLKGEN Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

12.3.1 Oscillator Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

12.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Chapter 13 Programmable Delay Block

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

13.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

13.1.2 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

13.1.3 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

13.2 Programmable Delay Block memory map and registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

13.2.1 Programmable Delay Block memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

13.2.2 Programmable Delay Block registers descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

13.2.2.1 PDB Control and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

13.2.2.2 PDB Delay A Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

13.2.2.3 PDB Delay B Register (DELAYB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

13.2.2.4 PDB Modulus Register (MOD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

13.2.2.5 PDB COUNT Register (COUNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

13.2.3 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

13.2.3.1 Miscellaneous concerns and SoC integration . . . . . . . . . . . . . . . . . . . . . . . . 228

13.3 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

13.4 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

13.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

Chapter 14 Port Controls

14.1 Port Control customizations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

14.1.1 General rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

14.1.2 Exceptions to the general rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

14.1.3 Pins not covered by the port control modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

14.2 Standard pin controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

14.2.1 Pin controls overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

14.3 Port Controls memory map and registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

14.3.1 Port Controls memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

14.3.2 Port Controls registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

14.3.2.1 Port x Pull-Up Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

14.3.2.2 Port x Slew Rate Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

14.3.2.3 Port x Drive Strength Selection Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

14.3.2.4 Port x Input Filter Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

Chapter 15 Rapid GPIO

15.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

15.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

15.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

15.1.3 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

15.2 External signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

15.2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 9

15.2.2 Detailed Rapid GPIO signal descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

15.3 Rapid GPIO memory map/register definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

15.3.1 Rapid GPIO memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

15.3.2 Rapid GPIO register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

15.3.2.1 RGPIO Data Direction register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

15.3.2.2 RGPIO Data register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

15.3.2.3 RGPIO Pin Enable register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

15.3.2.4 RGPIO Clear Data register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

15.3.2.5 RGPIO Set Data register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

15.3.2.6 RGPIO Toggle Data register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

15.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

15.5 Initialization information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

15.6 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

15.6.1 Application 1: Simple square-wave generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

15.6.2 Application 2: 16-bit message transmission using SPI protocol . . . . . . . . . . . . . . . . . 250

Chapter 16 Pin Interrupt Function

16.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

16.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

16.3 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

16.4 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

16.5 Pin Interrupt signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

16.6 Pin Interrupt memory map and registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

16.6.1 Pin Interrupt memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

16.6.2 Register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

16.6.2.1 Interrupt Status and Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

16.7 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

16.7.1 External interrupt pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

16.7.2 IRQ edge select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

16.7.3 IRQ sensitivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

16.7.4 IRQ interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

16.7.5 Clearing an IRQ interrupt request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

16.8 Exit from low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

16.8.1 STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

16.9 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

16.10Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

Chapter 17 16-Bit Modulo Timer

17.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

17.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

17.2.1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

17.2.2 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

17.2.2.1 MTIM16 in stop modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

17.2.2.2 MTIM16 in active background mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

17.3 Model-timer memory map/registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

17.3.1 MTIM16 memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

17.3.2 MTM16 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

17.3.2.1 MTIM16 Status and Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

17.3.2.2 MTIM16 Clock Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 10

17.3.2.3 MTIM16 Counter Register High/Low . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

17.3.2.4 MTIM16 Modulo Register High/Low registers . . . . . . . . . . . . . . . . . . . . . . . . 265

17.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

17.4.1 MTIM16 operation example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

Chapter 18 Timer/PWM Module

18.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

18.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

18.1.2 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

18.1.2.1 Input-capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

18.1.2.2 Output-compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

18.1.2.3 Edge-aligned PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

18.1.2.4 Center-aligned PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

18.1.3 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

18.2 Timer/PWM signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

18.2.1 Timer/PWM detailed signal descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

18.2.1.1 TPMxCHn: TPM Channel n I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

18.3 Timer/PWM memory map/register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

18.3.1 Timer/PWM memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

18.3.2 Timer/PWM register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

18.3.2.1 TPM Status and Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

18.3.2.2 TPM Counter Register High . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

18.3.2.3 TPM Counter Register Low . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

18.3.2.4 TPM Counter Modulo Register High . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

18.3.2.5 TPM Counter Modulo Register Low . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

18.3.2.6 TPM Channel n Status and Control Register . . . . . . . . . . . . . . . . . . . . . . . . 284

18.3.2.7 TPM Channel Value Register High . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

18.3.2.8 TPM Channel Value Register Low . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

18.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

18.4.1 Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

18.4.1.1 Counter clock source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

18.4.1.2 Counter overflow and modulo reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

18.4.1.3 Counting modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

18.4.1.4 Manual counter reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

18.4.2 Channel-mode selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

18.4.2.1 Input-capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

18.4.2.2 Output-compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

18.4.2.3 Edge-aligned PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

18.4.2.4 Center-aligned PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

18.5 Reset overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

18.5.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

18.5.2 Description of reset operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

18.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

18.6.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

18.6.2 Description of interrupt operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

18.6.2.1 Timer overflow interrupt (TOF) description . . . . . . . . . . . . . . . . . . . . . . . . . . 295

18.6.2.2 Channel event interrupt description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 11

Chapter 19 Interrupt Controller

19.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

19.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

19.2.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

19.2.2 Modes of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

19.2.3 Device-specific exception and interrupt vector tables . . . . . . . . . . . . . . . . . . . . . . . . . 303

19.2.4 External signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

19.3 Interrupt Controller memory map and register definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

19.3.1 Interrupt Controller memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

19.3.2 Interrupt Controller register descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

19.3.2.1 INTC Force Interrupt register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

19.3.2.2 INTC Programmable Level 6, Priority {7,6} registers . . . . . . . . . . . . . . . . . . 306

19.3.2.3 INTC Wake-up Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

19.3.2.4 INTC Set Interrupt Force register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

19.3.2.5 INTC Clear Interrupt Force register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 309

19.3.2.6 INTC Software and Level-n IACK registers (n = 1,2,3,...,7) . . . . . . . . . . . . . 310

19.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

19.4.1 Handling of non-maskable, level-7 interrupt requests . . . . . . . . . . . . . . . . . . . . . . . . . 311

19.5 Initialization information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

19.6 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

19.6.1 Emulation of the HCS08’s one-level, IRQ handling . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

19.6.2 Using INTC_PL6P{7,6} registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

19.6.3 More on software IACKs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

Chapter 20 ColdFire Core

20.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

20.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

20.3 Memory map/register description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

20.3.1 Data registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

20.3.2 Address Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

20.3.3 Supervisor/user stack pointers (A7 and OTHER_A7) . . . . . . . . . . . . . . . . . . . . . . . . . 320

20.3.3.1 Condition Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 321

20.3.4 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 321

20.3.5 Vector Base Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

20.3.6 CPU Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

20.3.7 Status Register (SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

20.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

20.4.1 Instruction set architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

20.4.2 Exception-processing overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

20.4.2.1 Exception stack frame definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 329

20.4.3 Processor exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

20.4.3.1 Access-error exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

20.4.3.2 Address-error exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

20.4.3.3 Illegal-instruction exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

20.4.3.4 Privilege violation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

20.4.3.5 Trace exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 333

20.4.3.6 Unimplemented, Line-A opcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 333

20.4.3.7 Unimplemented, Line-F opcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

20.4.3.8 Debug interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 12

20.4.3.9 RTE and format-error exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

20.4.3.10 TRAP-instruction exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

20.4.3.11 Unsupported-instruction exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

20.4.3.12 Interrupt exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

20.4.3.13 Fault-on-fault halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

20.4.3.14 Reset exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

20.4.4 Instruction execution timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

20.4.4.1 Timing assumptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

20.4.4.2 MOVE instruction execution times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

20.4.4.3 Standard One operand instruction execution times . . . . . . . . . . . . . . . . . . . 341

20.4.4.4 Standard Two operand instruction execution times . . . . . . . . . . . . . . . . . . . 342

20.4.4.5 Miscellaneous instruction execution times . . . . . . . . . . . . . . . . . . . . . . . . . . 343

20.4.4.6 Branch-instruction execution times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344

Chapter 21 Version 1 ColdFire Debug

21.1 Chip-specific information about CF1_DEBUG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

21.2 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

21.2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 348

21.2.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

21.2.3 Modes of operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

21.3 External signal descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

21.4 Memory map/register definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

21.4.1 Configuration/Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

21.4.2 Extended Configuration/Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

21.4.3 Configuration/Status Register 2 (CSR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

21.4.4 Configuration/Status Register 3 (CSR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

21.4.5 BDM Address Attribute Register (BAAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

21.4.6 Address Attribute Trigger Register (AATR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

21.4.7 Trigger Definition Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368

21.4.8 Program Counter Breakpoint/Mask Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

21.4.9 Address Breakpoint Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 374

21.4.10Data Breakpoint and Mask Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

21.4.11Resulting set of possible trigger combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

21.5 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

21.5.1 Background Debug Mode (BDM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

21.5.1.1 CPU halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

21.5.1.2 Background Debug Serial interface controller (BDC) . . . . . . . . . . . . . . . . . . 379

21.5.1.3 BDM communication details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

21.5.1.4 BDM command set descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

21.5.1.5 BDM command set summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386

21.5.1.6 GO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

21.5.1.7 Serial interface hardware handshake protocol . . . . . . . . . . . . . . . . . . . . . . . 404

21.5.1.8 Hardware handshake abort procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

21.5.2 Real-time debug support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

21.5.3 Freescale-recommended BDM pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 13

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

14 Freescal e Semiconductor, Inc.

Chapter 1 About This Document

1.1 Overview

1.1.1 Purpose

This reference manual describes the features, architecture and programming model of the MMA955xL

platform, an intelligent, three-axis accelerometer.

1.1.2 Audience

This document is primarily for system architects and software application developers who are using or

considering use of the MMA955xL in a system.

1.2 Terms and acronyms

AFE Analog Front End

APP_ID Application identifier

API Application Programming Interface

BDM Background Debug Module

CC Command Complete

CI Command Interpreter

CMD Command

COCO Conversion Complete or Command Complete

CSR ColdFire Configuration Status Register

DFC Data Format Code

DTAP Double tap (n.)

FIFO First In First Out, a data structure

FOPT Flash Options register

GPIO General-Purpose Input/Output, a microcontroller pin that can be programmed by

software

hash A deterministic, cryptographic function that converts an arbitrary block of data

into a fixed-size bit string—the (cryptographic) hash value—such that an

accidental or intentional change to the data will change that hash value

HG High g

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 15

About This Document

JT AG Joint T e st Action Group (JT AG), the common name for the IEEE 1 149.1 standard

Standard Test Access Port and Boundary-Scan Architecture, for test-access ports

LG Low g

LL Landscape Left

LR Landscape Right

MBOX Mailbox

MCU Microcontroller

MTIMOV Module Timer Overflow Module

PC Program Counter

PD Portrait Down

PDB Program Delay Block

PL Portrait/Landscape

POR Power-on Reset

PU Portrait Up

SFD Start Frame Digital

Shared secret Encrypted data known only to the parties involved in a secure communication.

Can include a password, a pass phrase, a big number, or an array of randomly

chosen bytes.

SSP Supervisor Stack Pointer

TPM Timer Program Module

VBR Vector Base Register, a register in the ColdFire memory map that controls the

location of the exception vector table

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

16 Freescal e Semiconductor, Inc.

About This Document

1.3 Conventions

This document uses the following notational conventions:

cleared/set When a bit takes the value 0, it is said to be cleared; when it takes a value of 1, it

is said to be set.

MNEMONICS In text, instruction mnemonics are shown in uppercase.

mnemonics In code and tables, instruction mnemonics are shown in lowercase.

italics Italics indicate variable command parameters.

Book titles also are italicized.

0x0 Prefix to denote a hexadecimal number

0b0 Prefix to denote a binary number

REG[FIELD] Abbreviations for registers are shown in uppercase. Specific bits, fields or ranges

appear in brackets. For example, RAMBAR[BA] identifies the base address field

in the RAM base-address register.

nibble A 4-bit data unit

byte An 8-bit data unit

word A 16-bit data unit

longword A 32-bit data unit

x In some contexts, such as signal encodings, x indicates a “do not care.”

n Used to express an undefined numerical value.

~ NOT logical operator

& AND logical operator

| OR logical operator

|| Field concatenation operator

OVERBAR Indicates that a signal is active-low.

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 17

About This Document

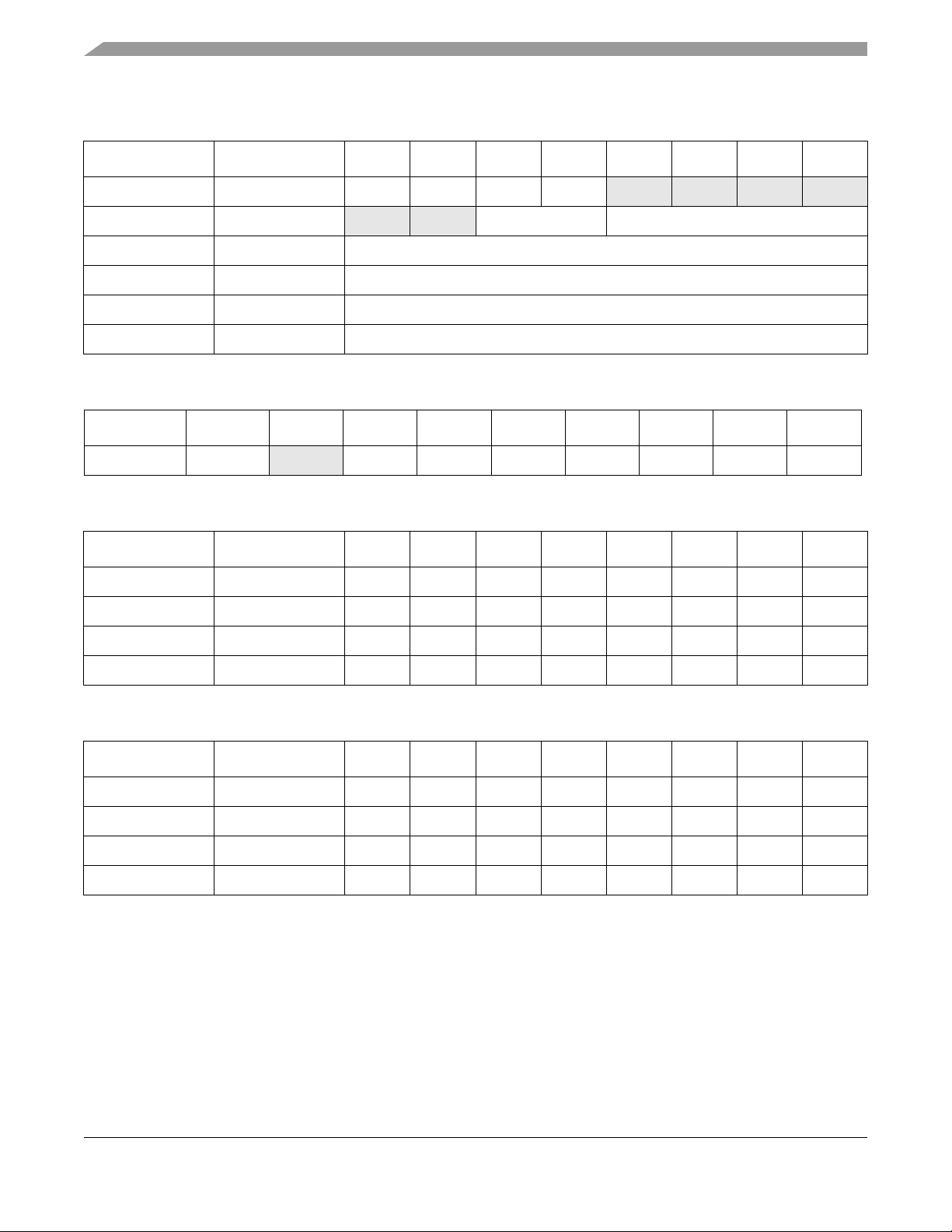

1.4 Register figure conventions

This document uses the following conventions for the register reset values:

— The bit is undefined at reset.

u The bit is unaffected by reset.

[signal_name] Reset value is determined by the polarity of the indicated signal.

The following register fields are used:

Read 0 Indicates a reserved bit field in a memory-mapped register. These bits are always read as 0.

Write

Read 1 Indicates a reserved bit field in a memory-mapped register. These bits are always read as 1.

Write

Read FIELDNAME Indicates a read/write bit.

Write

Read FIELDNAME Indicates a read-only bit field in a memory-mapped register.

Write

Read Indicates a write-only bit field in a memory-mapped register.

Write FIELDNAME

Read FIELDNAME Write 1 to clear: indicates that writing a 1 to this bit field clears it.

Write w1c

Read 0 Indicates a self-clearing bit.

Write FIELDNAME

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

18 Freescal e Semiconductor, Inc.

About This Document

1.5 References

1. MMA955xL intelligent, motion-sensing platform documentation: “MMA955xL: Product

Documentation Page”

2. IEEE Standard Test Access Port and Boundary-Scan Architecture, IEEE Std. 1149.1™-2001

(R2008)

3. The I2C-Bus Specification Version 2.1, January 2000, Philips Semiconductors

4. I2C-Bus Specification and User Manual, NXP Semiconductors Document UM10204, Rev. 03 19 June 2007

5. ColdFire Family Programmer’s Reference Manual, Freescale Semiconductor, CFPRM Rev. 3,

02/2005

6. Wikipedia entry for “Semaphore”: http://en.wikipedia.org/wiki/Semaphore_(programming)

7. ITU-T V.41 Recommendation: Code-Independent Error Control System, available at

http://www.itu.int/publications/index.html.

8. ITU-T X.25 Recommendation: Interface between Data Terminal Equipment (DTE) and Data

Circuit-terminating Equipment (DCE) for terminals operating in the packet mode and connected

to public data networks by dedicated circuit, available at

http://www.itu.int/publications/index.html.

9. ITU-T T.30 Recommendation: Procedures for document facsimile transmission in the general

switched telephone network, available at http://www.itu.int/publications/index.html.

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Freescale Semiconductor, Inc. 19

About This Document

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

20 Freescal e Semiconductor, Inc.

Chapter 2 Introduction

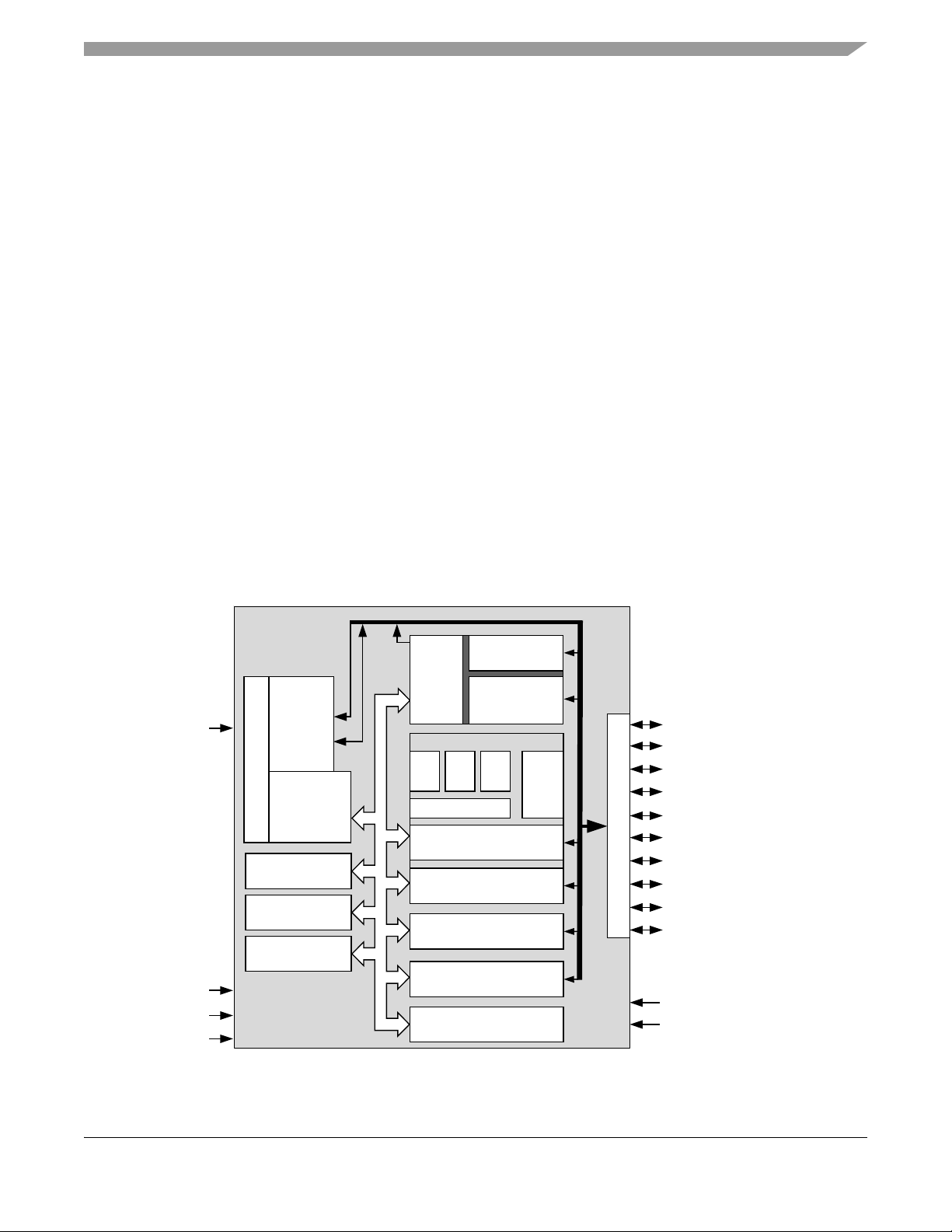

Analog Front End (AFE)()

BDM

INTC

DBG

X

axis

C to V

Temp

Sensor

I2C slave

SPI slave

Control

and

mailbox

CLKGEN

INT_O

Y

axisZaxis

RESET

V

DDA

V

SSA

RGPIO

SCL0/RGPIO0/SCLK

SDA0/RGPIO1/SDI

RGPIO2/SCL1/SDO

RGPIO3/SDA1/SSB

RGPIO4/INT

RGPIO5/PDB_A/INT_O

RGPIO6/AN0/TPMCH0

RGPIO7/AN1/TPMCH1

RGPIO8/PDB_B

BKGD/MS/RPGPIO9

SCLK

SDI

SDO

SSB

SCL0

SDA0

BKGD

INT

1

V

DD

V

SS

V

SS

V

ColdFire Core

with MAC

SIM

1 K x 32

ROM

4 K x 32

Flash

512 x 32

RAM

I2C Master

ADC

Two-channel, 16-bit

Timer / PWM module

16-bit

Modulo timer module

Programmable

delay block

AN0

AN1

TPMCH0

TPMCH1

SCL1

SCL0

PDB_A

PDB_B

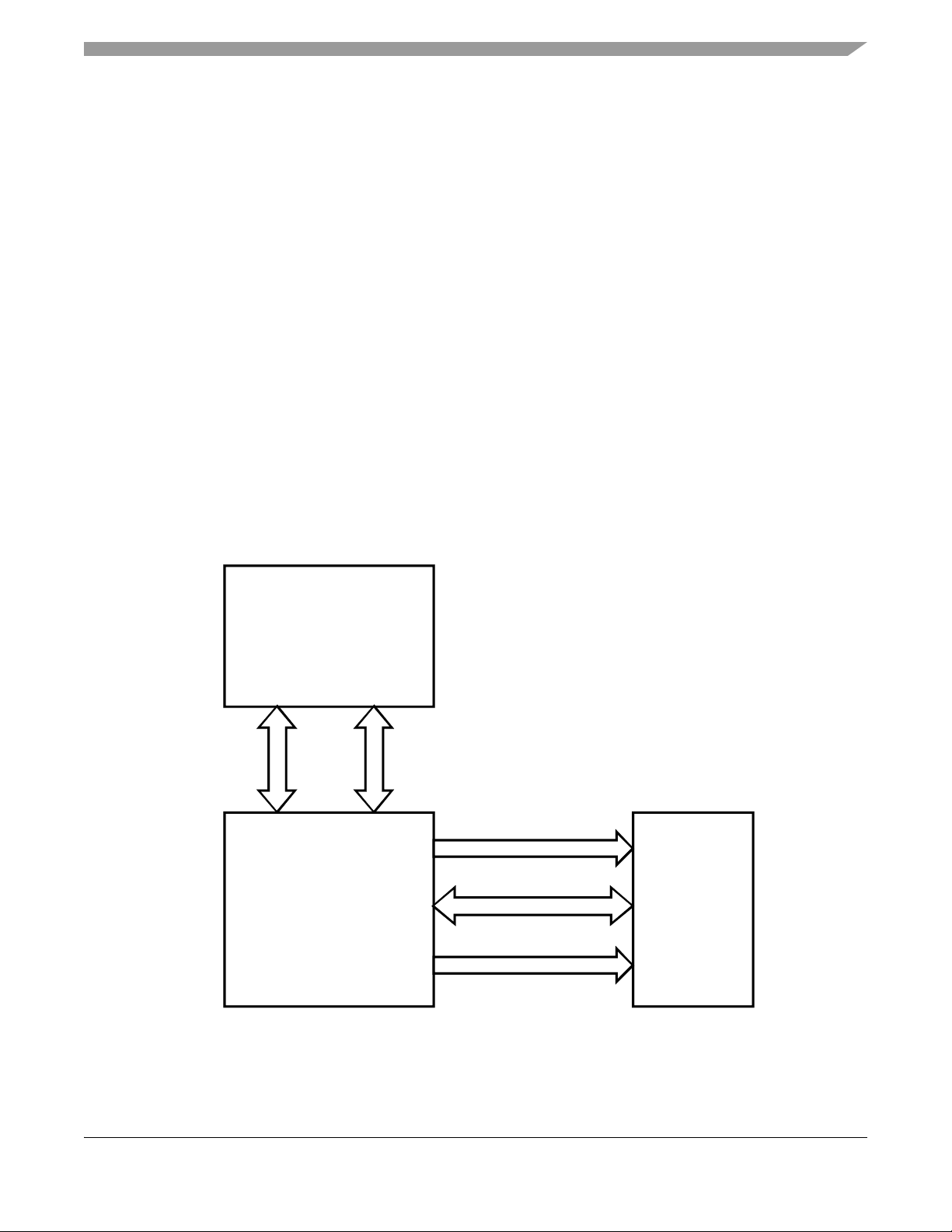

The MMA955xL three-axis accelerometer is a member of Freescale’ s Xtrinsic family of intelligent sensor

platforms. This device incorporates dedicated accelerometer MEMS transducers, signal conditioning, data

conversion and a 32-bit, programmable microcontroller.

This unique blend transforms Freescale’s MMA955xL devi ce into an intelligent, high-precision

motion-sensing platform able to manage multiple sensor inputs and make system-level decisions required

for sophisticated applications such as gesture recognition, tilt computation, and pedometer functionality.

The MMA955xL platform is programmed and configured with CodeWarrior Development Studio

software. This integrated-design environment enables customers to quickly and easily shape and

implement custom algorithms and features to exactly match their application needs.

Using its master I2C module, the MMA955xL platform can manage secondary sensors such as pressure

sensors, magnetometers or gyroscopes. This allows sensor initialization, calibration, data compensation

and computation functions to be off-loaded from the system application processor . Multiple sensor inputs

can be easily consolidated by the MMA955xL device which acts as an intelligent sensing hub and highly

configurable decision engine. T otal system power consumption is significantly r educed as the application

processor stays powered down until absolutely needed.

Freescale Semiconductor, Inc. 21

MMA955xL Intelligent, Motion-Sensing Platform Hardware Reference Manual, Rev. 1.0

Figure 2-1. Platform block diagram

Introduction

2.1 Hardware features

• Three accelerometer operating ranges:

— ±2g: Suits most user-interaction (mouse) motions and free fall

— ±4g: Covers most regular human dynamics (walking, jogging)

— ±8g: Detects most abrupt activities (gaming)

• Integrated temperature sensor

• One slave SPI or I2C interface operates up to 2 MHz dedicated to communication with host

processor

• One master I2C interface operates up to 400 kbps used to communicate with external sensors

• 10, 12, 14 and 16-bit ADC trimmed data formats available.

• 1.8V Supply voltage

• 32-bit ColdFire V1 CPU

• Extensive set of power management features and low power modes.

• Single Wire Background Debug Mode (BDM) pin interface

• 16 KB Flash memory

• 2 KB random access memory

• ROM-based flash controller and slave port command line interpreter

• Two channel timer with input capture, output capture or edge-aligned PWM

• Programmable delay block for scheduling events relative to start of frame

• Modulo timer for scheduling periodic events

2.2 Software features

This device may be programmed to provide any of the following:

• Orientation detection (portrait/landscape)

• High-g/low-g threshold detection

• Pulse detection (single, double and directional tap)

• Auto wake/sleep

• Linear and rotational free fall

• Flick detection

• Embedded smart FIFO

• Power management

• Pedometer

• Shock, vibration and sudden-motion detection

• Tilt-angle computation

The association of a high-performance accelerometer with a powerful, embedded ColdFire V1 MCU core

gives the possibility to grow and customize this list in an unprecedented way.