Page 1

MCF52211 ColdFire® Integrated

Microcontroller Reference Manual

Devices Supported:

MCF52210

MCF52211

MCF52212

MCF52213

Document Number: MCF52211RM

Rev. 2

09/2007

Page 2

How to Reach Us:

Home Page:

http://www.freescale.com

E-mail:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

+1-800-521-6274 or +1-480-768-2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064, Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 26668334

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and

software implementers to use Freescale Semiconductor products. There are

no express or implied copyright licenses granted hereunder to design or

fabricate any integrated circuits or integrated circuits based on the

information in this document.

Freescale Semiconductor reserves the right to make changes without further

notice to any products herein. Freescale Semiconductor makes no warranty,

representation or guarantee regarding the suitability of its products for any

particular purpose, nor does Freescale Semiconductor assume any liability

arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation consequential or

incidental damages. “Typical” parameters that may be provided in Freescale

Semiconductor data sheets and/or specifications can and do vary in different

applications and actual performance may vary over time. All operating

parameters, including “Typicals”, must be validated for each customer

application by customer’s technical exper ts. Freescale Semiconductor does

not convey any license under its patent rights nor the rights of others.

Freescale Semiconductor products are not designed, intended, or authorized

for use as components in systems intended for surgical implant into the body,

or other applications intended to support or sustain life, or for any other

application in which the failure of the Freescale Semico nductor product could

create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semicondu ctor products for any such unintended

or unauthorized application, Buyer shall indemnify and hold Freescale

Semiconductor and its officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized

use, even if such claim alleges that Freescale Semiconductor was negligent

regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale

Semiconductor, Inc. All other product or service names are the property of their

respective owners.

© Freescale Semiconductor, Inc. 2007. All rights reserved.

MCF52211RM

Rev. 2

09/2007

Page 3

Chapter 1

Overview

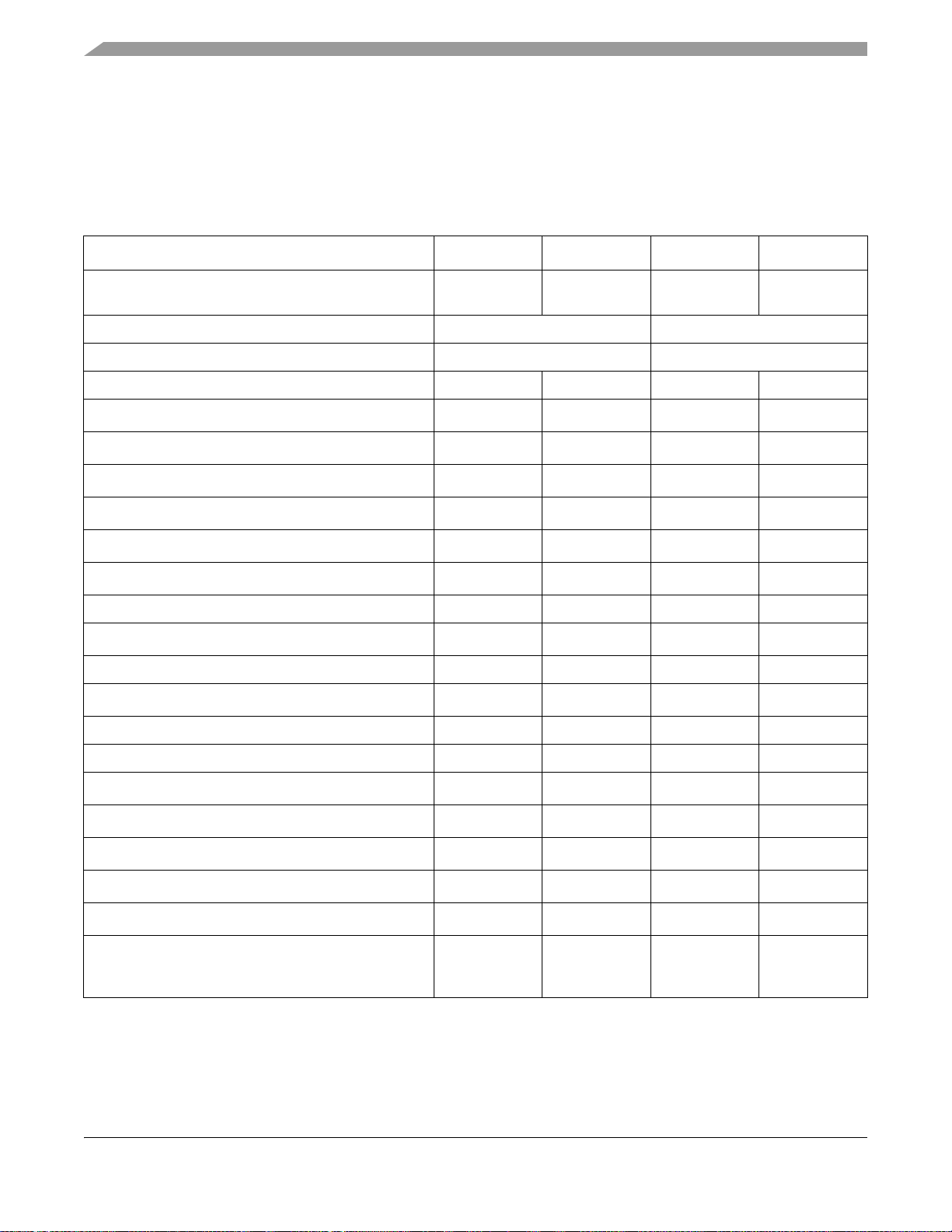

1.1 MCF52211 Family Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

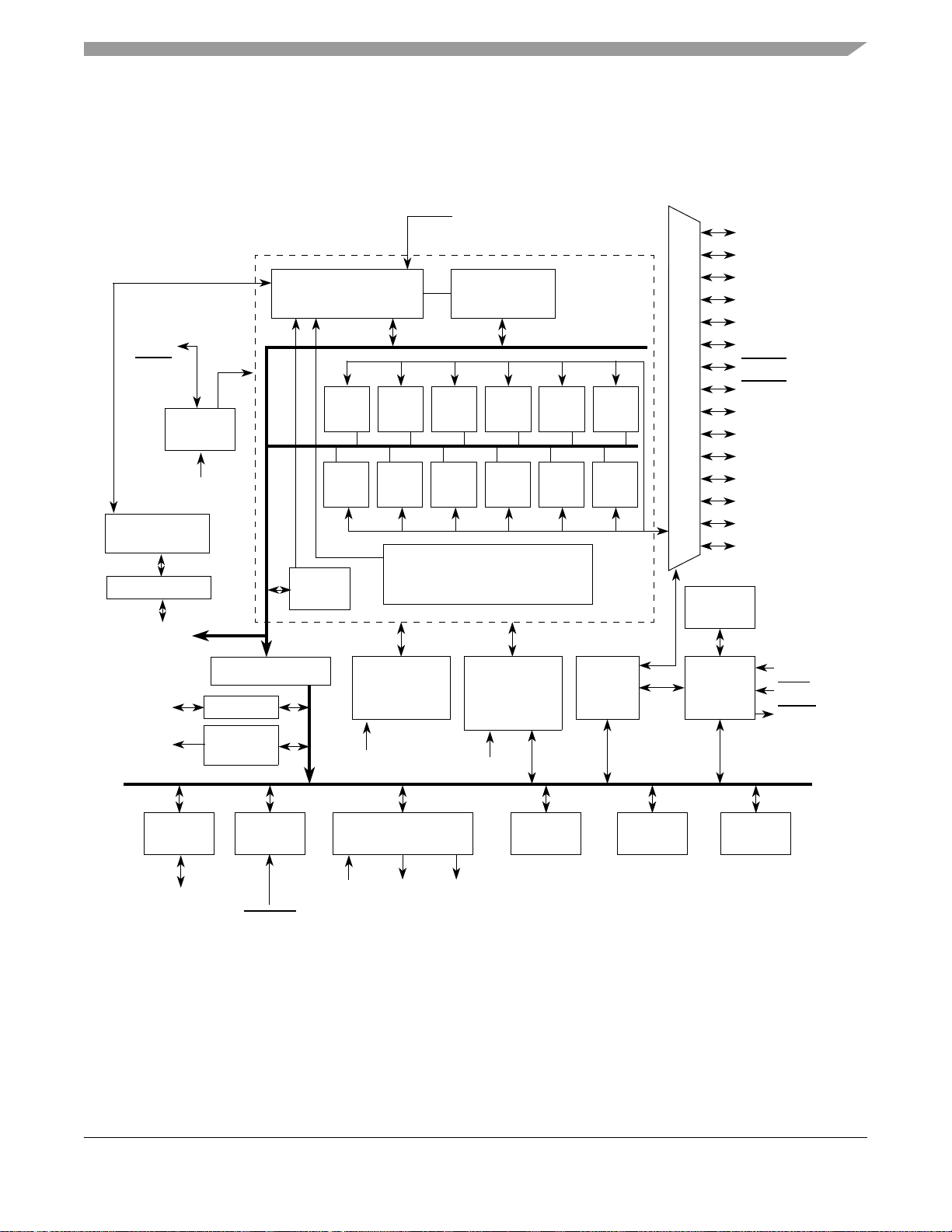

1.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

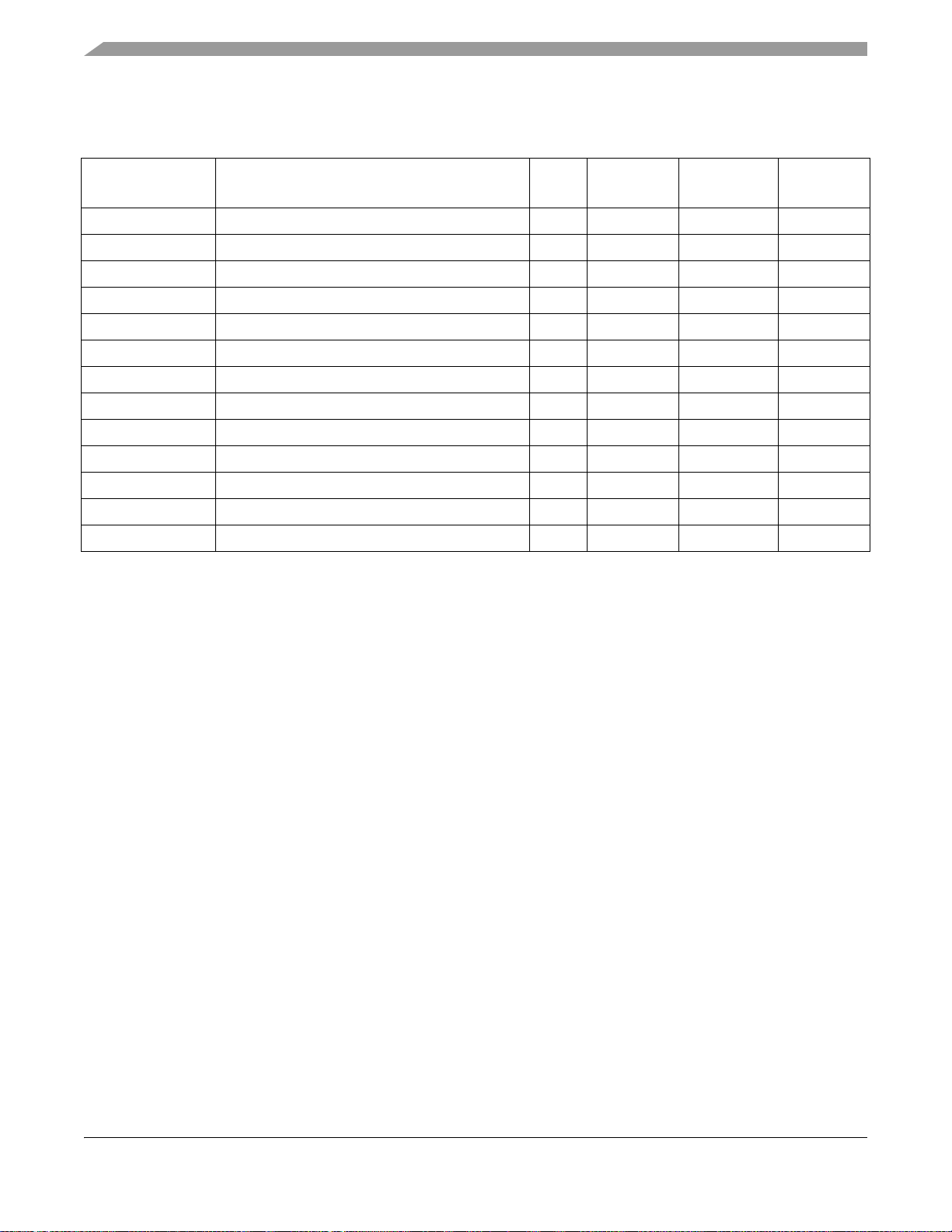

1.3 Part Numbers and Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.1 V2 Core Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.2.2 Integrated Debug Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.2.3 JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.2.4 On-Chip Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.5 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.6 USB On-The-Go Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.2.7 UARTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.2.8 I2C Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.2.9 QSPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.2.10 Fast ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.2.11 DMA Timers (DTIM0–DTIM3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.2.12 General Purpose Timer (GPT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.2.13 Periodic Interrupt Timers (PIT0 and PIT1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.2.14 Real-Time Clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.2.15 Pulse-Width Modulation (PWM) Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.2.16 Software Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.2.17 Backup Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.2.18 Phase-Locked Loop (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.2.19 Interrupt Controller (INTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.2.20 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.2.21 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.2.22 GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

Chapter 2

Signal Descriptions

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.3 Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.4 Reset Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.5 PLL and Clock Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.6 Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.7 External Interrupt Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.8 Queued Serial Peripheral Interface (QSPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.9 I

2.10 UART Module Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.11 DMA Timer Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.12 ADC Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.13 General Purpose Timer Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Freescale Semiconductor i

2

C I/O Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Page 4

2.14 Pulse-Width Modulator Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.15 Debug Support Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.16 EzPort Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.17 Power and Ground Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Chapter 3

ColdFire Core

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2 Memory Map/Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.2.1 Data Registers (D0–D7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.2.2 Address Registers (A0–A6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.2.3 Supervisor/User Stack Pointers (A7 and OTHER_A7) . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.2.4 Condition Code Register (CCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.2.5 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.2.6 Vector Base Register (VBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.2.7 Status Register (SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.2.8 Memory Base Address Registers (RAMBAR, FLASHBAR) . . . . . . . . . . . . . . . . . . . . 3-8

3.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.3.1 Version 2 ColdFire Microarchitecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.3.2 Instruction Set Architecture (ISA_A+) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.3.3 Exception Processing Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.3.4 Processor Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3.3.5 Instruction Execution Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

Chapter 4

Multiply-Accumulate Unit (MAC)

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2.1 MAC Status Register (MACSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2.2 Mask Register (MASK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.2.3 Accumulator Register (ACC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4.3.1 Fractional Operation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.3.2 MAC Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.3.3 MAC Instruction Execution Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.3.4 Data Representation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.3.5 MAC Opcodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Chapter 5

Static RAM (SRAM)

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor ii

Page 5

5.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 Memory Map/Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2.1 SRAM Base Address Register (RAMBAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.3 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.3.1 SRAM Initialization Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.3.2 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Chapter 6

Clock Module

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.3.1 Backup Watchdog Timer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.3.2 RTC Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.3 Normal PLL Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.4 1:1 PLL Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.5 External Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.4 Low-Power Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.6 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.6.1 EXTAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.6.2 XTAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.6.3 CLKOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.6.4 CLKMOD[1:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.6.5 RSTO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.7 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.7.1 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.8.1 System Clock Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.8.2 Clock Operation During Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.8.3 System Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-18

6.8.4 PLL Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-18

Chapter 7

Backup Watchdog Timer (BWT) Module

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.2 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.2.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.2.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor iii

Page 6

Chapter 8

Power Management

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.2 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.2.1 Peripheral Power Management Registers (PPMRH, PPMRL) . . . . . . . . . . . . . . . . . . . 8-2

8.2.2 Low-Power Interrupt Control Register (LPICR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.2.3 Peripheral Power Management Set Register (PPMRS) . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.2.4 Peripheral Power Management Clear Register (PPMRC) . . . . . . . . . . . . . . . . . . . . . . . 8-8

8.2.5 Low-Power Control Register (LPCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

8.3 IPS Bus Timeout Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

8.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.4.1 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.4.2 Peripheral Behavior in Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-12

8.4.3 Summary of Peripheral State During Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . 8-15

Chapter 9

Chip Configuration Module (CCM)

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.2 External Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.2.1 RCON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.2.2 CLKMOD[1:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.2.3 JTAG_EN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.2.4 TEST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.3 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.3.1 Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.3.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.3.3 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

Chapter 10

Reset Controller Module

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.4 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.4.1 RSTI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.4.2 RSTO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.5 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.5.1 Reset Control Register (RCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

10.5.2 Reset Status Register (RSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-4

10.6 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-5

10.6.1 Reset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-5

10.6.2 Reset Control Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-7

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor iv

Page 7

10.6.3 Concurrent Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

Chapter 11

Real-Time Clock

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

11.2 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

11.2.1 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

11.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-13

11.3.1 Prescaler and Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-13

11.3.2 Alarm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-14

11.3.3 Minute Stopwatch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-14

11.4 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-14

11.4.1 Flow Chart of RTC Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-14

11.4.2 Code Example for Initializing the Real-Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . 11-15

Chapter 12

System Control Module (SCM)

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.4 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-2

12.5 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-3

12.5.1 Internal Peripheral System Base Address Register (IPSBAR) . . . . . . . . . . . . . . . . . . 12-3

12.5.2 Memory Base Address Register (RAMBAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.5.3 Core Reset Status Register (CRSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-6

12.5.4 Core Watchdog Control Register (CWCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-7

12.5.5 Core Watchdog Service Register (CWSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-8

12.6 Internal Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-9

12.6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-9

12.6.2 Arbitration Algorithms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-10

12.6.3 Bus Master Park Register (MPARK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-10

12.7 System Access Control Unit (SACU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-12

12.7.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-12

12.7.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-12

12.7.3 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-13

Chapter 13

General Purpose I/O Module

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

13.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-2

13.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-2

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor v

Page 8

13.4 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-2

13.5 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-2

13.5.1 Ports Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-2

13.6 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-4

13.6.1 Port Output Data Registers (PORTn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-4

13.6.2 Port Data Direction Registers (DDRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-5

13.6.3 Port Pin Data/Set Data Registers (PORTnP/SETn) . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-7

13.6.4 Port Clear Output Data Registers (CLRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-9

13.6.5 Pin Assignment Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-10

13.6.6 Pad Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-13

13.7 Ports Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-15

Chapter 14

Interrupt Controller Module

14.1 68K/ColdFire Interrupt Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

14.1.1 Interrupt Controller Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-2

14.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-4

14.3 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-5

14.3.1 Interrupt Pending Registers (IPRHn, IPRLn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-6

14.3.2 Interrupt Mask Register (IMRHn, IMRLn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-7

14.3.3 Interrupt Force Registers (INTFRCHn, INTFRCLn) . . . . . . . . . . . . . . . . . . . . . . . . . 14-8

14.3.4 Interrupt Request Level Register (IRLRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-10

14.3.5 Interrupt Acknowledge Level and Priority Register (IACKLPRn) . . . . . . . . . . . . . . 14-10

14.3.6 Interrupt Control Registers (ICRnx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-11

14.3.7 Software and Level m IACK Registers (SWIACKn, LmIACKn) . . . . . . . . . . . . . . . 14-15

14.3.8 Global Level m IACK Registers (GLmIACK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-16

14.4 Low-Power Wakeup Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-16

Chapter 15

Universal Serial Bus, OTG Capable Controller

15.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-1

15.1.1 USB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-1

15.1.2 USB On-The-Go . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-3

15.1.3 USB-FS Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-4

15.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-4

15.2.1 Data Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-4

15.3 Programmers Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-4

15.3.1 Buffer Descriptor Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-4

15.3.2 Rx vs. Tx as a USB Target Device or USB Host . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-5

15.3.3 Addressing Buffer Descriptor Table Entries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-5

15.3.4 Buffer Descriptor Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-6

15.3.5 USB Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-8

15.4 Memory Map/Register Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-9

15.4.1 Capability Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-10

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor vi

Page 9

15.5 OTG and Host Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-33

15.6 Host Mode Operation Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-34

15.7 On-The-Go Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-36

15.7.1 OTG Dual Role A Device Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-36

15.7.2 OTG Dual Role B Device Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-38

15.7.3 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-39

15.7.4 USB Suspend State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-40

Chapter 16

Edge Port Module (EPORT)

16.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-1

16.2 Low-Power Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-2

16.3 Interrupt/GPIO Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-2

16.4 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-2

16.4.1 EPORT Pin Assignment Register (EPPAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-3

16.4.2 EPORT Data Direction Register (EPDDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.4.3 Edge Port Interrupt Enable Register (EPIER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.4.4 Edge Port Data Register (EPDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-5

16.4.5 Edge Port Pin Data Register (EPPDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-5

16.4.6 Edge Port Flag Register (EPFR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-6

Chapter 17

DMA Controller Module

17.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-1

17.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-1

17.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-2

17.2 DMA Transfer Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-3

17.3 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-3

17.3.1 DMA Request Control (DMAREQC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-4

17.3.2 Source Address Registers (SARn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-5

17.3.3 Destination Address Registers (DARn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-5

17.3.4 Byte Count Registers (BCRn) and DMA Status Registers (DSRn) . . . . . . . . . . . . . . 17-6

17.3.5 DMA Control Registers (DCRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-8

17.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-11

17.4.1 Transfer Requests (Cycle-Steal and Continuous Modes) . . . . . . . . . . . . . . . . . . . . . 17-12

17.4.2 Dual-Address Data Transfer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-12

17.4.3 Channel Initialization and Startup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-13

17.4.4 Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-14

17.4.5 Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-15

Chapter 18

ColdFire Flash Module (CFM)

18.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-1

18.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-1

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor vii

Page 10

18.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-2

18.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-3

18.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-3

18.3.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-3

18.3.2 Flash Base Address Register (FLASHBAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-4

18.3.3 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-7

18.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-16

18.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-16

18.4.2 Flash Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-17

18.4.3 Flash Security Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-30

Chapter 19

EzPort

19.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-1

19.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-1

19.3 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-2

19.3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-2

19.3.2 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-2

19.4 Command Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-3

19.4.1 Command Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-4

19.5 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-7

19.6 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-8

Chapter 20

Programmable Interrupt Timers (PIT0–PIT1)

20.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-1

20.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-1

20.1.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-1

20.1.3 Low-Power Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-1

20.2 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-2

20.2.1 PIT Control and Status Register (PCSRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-3

20.2.2 PIT Modulus Register (PMRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-4

20.2.3 PIT Count Register (PCNTRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-5

20.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-5

20.3.1 Set-and-Forget Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-5

20.3.2 Free-Running Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-6

20.3.3 Timeout Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-6

20.3.4 Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-6

Chapter 21

General Purpose Timer Module (GPT)

21.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-1

21.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-1

21.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-2

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor viii

Page 11

21.4 Low-Power Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-3

21.5 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-3

21.5.1 GPT[2:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-3

21.5.2 GPT3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-3

21.5.3 SYNCn . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-4

21.6 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-4

21.6.1 GPT Input Capture/Output Compare Select Register (GPTIOS) . . . . . . . . . . . . . . . . . 21-5

21.6.2 GPT Compare Force Register (GPCFORC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-6

21.6.3 GPT Output Compare 3 Mask Register (GPTOC3M) . . . . . . . . . . . . . . . . . . . . . . . . . 21-6

21.6.4 GPT Output Compare 3 Data Register (GPTOC3D) . . . . . . . . . . . . . . . . . . . . . . . . . . 21-7

21.6.5 GPT Counter Register (GPTCNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-7

21.6.6 GPT System Control Register 1 (GPTSCR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-8

21.6.7 GPT Toggle-On-Overflow Register (GPTTOV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-9

21.6.8 GPT Control Register 1 (GPTCTL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-9

21.6.9 GPT Control Register 2 (GPTCTL2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-10

21.6.10GPT Interrupt Enable Register (GPTIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-10

21.6.11GPT System Control Register 2 (GPTSCR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-11

21.6.12GPT Flag Register 1 (GPTFLG1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-12

21.6.13GPT Flag Register 2 (GPTFLG2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-12

21.6.14GPT Channel Registers (GPTCn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-13

21.6.15Pulse Accumulator Control Register (GPTPACTL) . . . . . . . . . . . . . . . . . . . . . . . . . 21-13

21.6.16Pulse Accumulator Flag Register (GPTPAFLG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-14

21.6.17Pulse Accumulator Counter Register (GPTPACNT) . . . . . . . . . . . . . . . . . . . . . . . . . 21-15

21.6.18GPT Port Data Register (GPTPORT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-16

21.6.19GPT Port Data Direction Register (GPTDDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-16

21.7 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-16

21.7.1 Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-17

21.7.2 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-17

21.7.3 Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-17

21.7.4 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-18

21.7.5 Event Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-18

21.7.6 Gated Time Accumulation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-18

21.7.7 General-Purpose I/O Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-19

21.8 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-21

21.9 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-21

21.9.1 GPT Channel Interrupts (CnF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-21

21.9.2 Pulse Accumulator Overflow (PAOVF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-21

21.9.3 Pulse Accumulator Input (PAIF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-22

21.9.4 Timer Overflow (TOF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-22

Chapter 22

DMA Timers (DTIM0–DTIM3)

22.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-1

22.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-1

22.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-2

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor ix

Page 12

22.2 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-2

22.2.1 DMA Timer Mode Registers (DTMRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-3

22.2.2 DMA Timer Extended Mode Registers (DTXMRn) . . . . . . . . . . . . . . . . . . . . . . . . . . 22-4

22.2.3 DMA Timer Event Registers (DTERn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-5

22.2.4 DMA Timer Reference Registers (DTRRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-6

22.2.5 DMA Timer Capture Registers (DTCRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-7

22.2.6 DMA Timer Counters (DTCNn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-7

22.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-8

22.3.1 Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-8

22.3.2 Capture Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-8

22.3.3 Reference Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-8

22.3.4 Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-8

22.4 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-9

22.4.1 Code Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-9

22.4.2 Calculating Time-Out Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-10

Chapter 23

Queued Serial Peripheral Interface (QSPI)

23.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-1

23.1.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-1

23.1.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-2

23.1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-2

23.1.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-2

23.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-2

23.3 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-3

23.3.1 QSPI Mode Register (QMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-3

23.3.2 QSPI Delay Register (QDLYR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-5

23.3.3 QSPI Wrap Register (QWR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-6

23.3.4 QSPI Interrupt Register (QIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-6

23.3.5 QSPI Address Register (QAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-7

23.3.6 QSPI Data Register (QDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-8

23.3.7 Command RAM Registers (QCR0–QCR15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-8

23.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-9

23.4.1 QSPI RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-11

23.4.2 Baud Rate Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-12

23.4.3 Transfer Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-13

23.4.4 Transfer Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-14

23.4.5 Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-14

23.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-15

Chapter 24

UART Modules

24.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-1

24.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-1

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor x

Page 13

24.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-2

24.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-3

24.3 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-3

24.3.1 UART Mode Registers 1 (UMR1n) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-5

24.3.2 UART Mode Register 2 (UMR2n) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-6

24.3.3 UART Status Registers (USRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-7

24.3.4 UART Clock Select Registers (UCSRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-9

24.3.5 UART Command Registers (UCRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-9

24.3.6 UART Receive Buffers (URBn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-11

24.3.7 UART Transmit Buffers (UTBn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-12

24.3.8 UART Input Port Change Registers (UIPCRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-12

24.3.9 UART Auxiliary Control Register (UACRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-13

24.3.10UART Interrupt Status/Mask Registers (UISRn/UIMRn) . . . . . . . . . . . . . . . . . . . . . 24-13

24.3.11UART Baud Rate Generator Registers (UBG1n/UBG2n) . . . . . . . . . . . . . . . . . . . . . 24-15

24.3.12UART Input Port Register (UIPn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-15

24.3.13UART Output Port Command Registers (UOP1n/UOP0n) . . . . . . . . . . . . . . . . . . . . 24-16

24.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-16

24.4.1 Transmitter/Receiver Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-16

24.4.2 Transmitter and Receiver Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-18

24.4.3 Looping Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-22

24.4.4 Multidrop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-24

24.4.5 Bus Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-26

24.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-26

24.5.1 Interrupt and DMA Request Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-26

24.5.2 UART Module Initialization Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-28

Chapter 25

2

C Interface

I

25.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-1

25.1.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-2

25.1.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-2

25.1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-3

25.2 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-3

25.2.1 I

25.2.2 I2C Frequency Divider Registers (I2FDRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-4

25.2.3 I2C Control Registers (I2CRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-5

25.2.4 I2C Status Registers (I2SRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-7

25.2.5 I

25.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-8

25.3.1 START Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-8

25.3.2 Slave Address Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-9

25.3.3 Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-9

25.3.4 Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-10

25.3.5 STOP Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-10

25.3.6 Repeated START . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-10

2

C Address Registers (I2ADRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-4

2

C Data I/O Registers (I2DRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-8

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor xi

Page 14

25.3.7 Clock Synchronization and Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-12

25.3.8 Handshaking and Clock Stretching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-13

25.4 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-13

25.4.1 Initialization Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-13

25.4.2 Generation of START . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-13

25.4.3 Post-Transfer Software Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-14

25.4.4 Generation of STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-14

25.4.5 Generation of Repeated START . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-15

25.4.6 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-15

25.4.7 Arbitration Lost . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-15

Chapter 26

Analog-to-Digital Converter (ADC)

26.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-1

26.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-1

26.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-2

26.4 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-2

26.4.1 Control 1 Register (CTRL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-3

26.4.2 Control 2 Register (CTRL2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-5

26.4.3 Zero Crossing Control Register (ADZCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-8

26.4.4 Channel List 1 and 2 Registers (ADLST1 and ADLST2) . . . . . . . . . . . . . . . . . . . . . . 26-8

26.4.5 Sample Disable Register (ADSDIS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-10

26.4.6 Status Register (ADSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-11

26.4.7 Limit Status Register (ADLSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-13

26.4.8 Zero Crossing Status Register (ADZCSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-14

26.4.9 Result Registers (ADRSLTn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-14

26.4.10Low and High Limit Registers (ADLLMTn and ADHLMTn) . . . . . . . . . . . . . . . . . 26-15

26.4.11Offset Registers (ADOFSn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-17

26.4.12Power Control Register (POWER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-17

26.4.13Voltage Reference Register (CAL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-20

26.5 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-21

26.5.1 Input MUX Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-23

26.5.2 ADC Sample Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-25

26.5.3 ADC Data Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-27

26.5.4 Sequential vs. Parallel Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-28

26.5.5 Scan Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-29

26.5.6 Scan Configuration and Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-30

26.5.7 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-32

26.5.8 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-32

26.5.9 ADC Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-34

26.5.10Voltage Reference Pins VREFH and VREFL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-37

26.5.11Supply Pins VDDA and VSSA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-38

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor xii

Page 15

Chapter 27

Pulse-Width Modulation (PWM) Module

27.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-1

27.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-1

27.2 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-2

27.2.1 PWM Enable Register (PWME) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-3

27.2.2 PWM Polarity Register (PWMPOL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-4

27.2.3 PWM Clock Select Register (PWMCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-4

27.2.4 PWM Prescale Clock Select Register (PWMPRCLK) . . . . . . . . . . . . . . . . . . . . . . . . 27-5

27.2.5 PWM Center Align Enable Register (PWMCAE) . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-6

27.2.6 PWM Control Register (PWMCTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-7

27.2.7 PWM Scale A Register (PWMSCLA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-8

27.2.8 PWM Scale B Register (PWMSCLB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-9

27.2.9 PWM Channel Counter Registers (PWMCNTn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-9

27.2.10PWM Channel Period Registers (PWMPERn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-10

27.2.11PWM Channel Duty Registers (PWMDTYn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-11

27.2.12PWM Shutdown Register (PWMSDN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-12

27.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-13

27.3.1 PWM Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-13

27.3.2 PWM Channel Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27-15

Chapter 28

Debug Module

28.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-1

28.1.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-1

28.1.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-1

28.2 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-2

28.3 Real-Time Trace Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-3

28.3.1 Begin Execution of Taken Branch (PST = 0x5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-5

28.4 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-6

28.4.1 Shared Debug Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-7

28.4.2 Configuration/Status Register (CSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-7

28.4.3 BDM Address Attribute Register (BAAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-10

28.4.4 Address Attribute Trigger Register (AATR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-10

28.4.5 Trigger Definition Register (TDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-12

28.4.6 Program Counter Breakpoint/Mask Registers (PBR0–3, PBMR) . . . . . . . . . . . . . . . 28-15

28.4.7 Address Breakpoint Registers (ABLR, ABHR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-17

28.4.8 Data Breakpoint and Mask Registers (DBR, DBMR) . . . . . . . . . . . . . . . . . . . . . . . . 28-18

28.5 Background Debug Mode (BDM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-19

28.5.1 CPU Halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-19

28.5.2 BDM Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-20

28.5.3 BDM Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-22

28.6 Real-Time Debug Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-39

28.6.1 Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-39

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor xiii

Page 16

28.6.2 Concurrent BDM and Processor Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-41

28.7 Processor Status, Debug Data Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-42

28.7.1 User Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-42

28.7.2 Supervisor Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-47

28.8 Freescale-Recommended BDM Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28-47

Chapter 29

IEEE 1149.1 Test Access Port (JTAG)

29.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-1

29.1.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-1

29.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-2

29.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-2

29.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-2

29.2.1 JTAG Enable (JTAG_EN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-2

29.2.2 Test Clock Input (TCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-3

29.2.3 Test Mode Select/Breakpoint (TMS/BKPT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-3

29.2.4 Test Data Input/Development Serial Input (TDI/DSI) . . . . . . . . . . . . . . . . . . . . . . . . . 29-3

29.2.5 Test Reset/Development Serial Clock (TRST/DSCLK) . . . . . . . . . . . . . . . . . . . . . . . 29-4

29.2.6 Test Data Output/Development Serial Output (TDO/DSO) . . . . . . . . . . . . . . . . . . . . 29-4

29.3 Memory Map/Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-4

29.3.1 Instruction Shift Register (IR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-4

29.3.2 IDCODE Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-4

29.3.3 Bypass Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-5

29.3.4 JTAG_CFM_CLKDIV Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-5

29.3.5 TEST_CTRL Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-5

29.3.6 Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-5

29.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-6

29.4.1 JTAG Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-6

29.4.2 TAP Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-6

29.4.3 JTAG Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-7

29.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-10

29.5.1 Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-10

29.5.2 Nonscan Chain Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29-10

B.1 Changes between Rev. 1 and Rev. 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31-1

B.2 Changes between Rev. 0 and Rev. 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31-2

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor xiv

Page 17

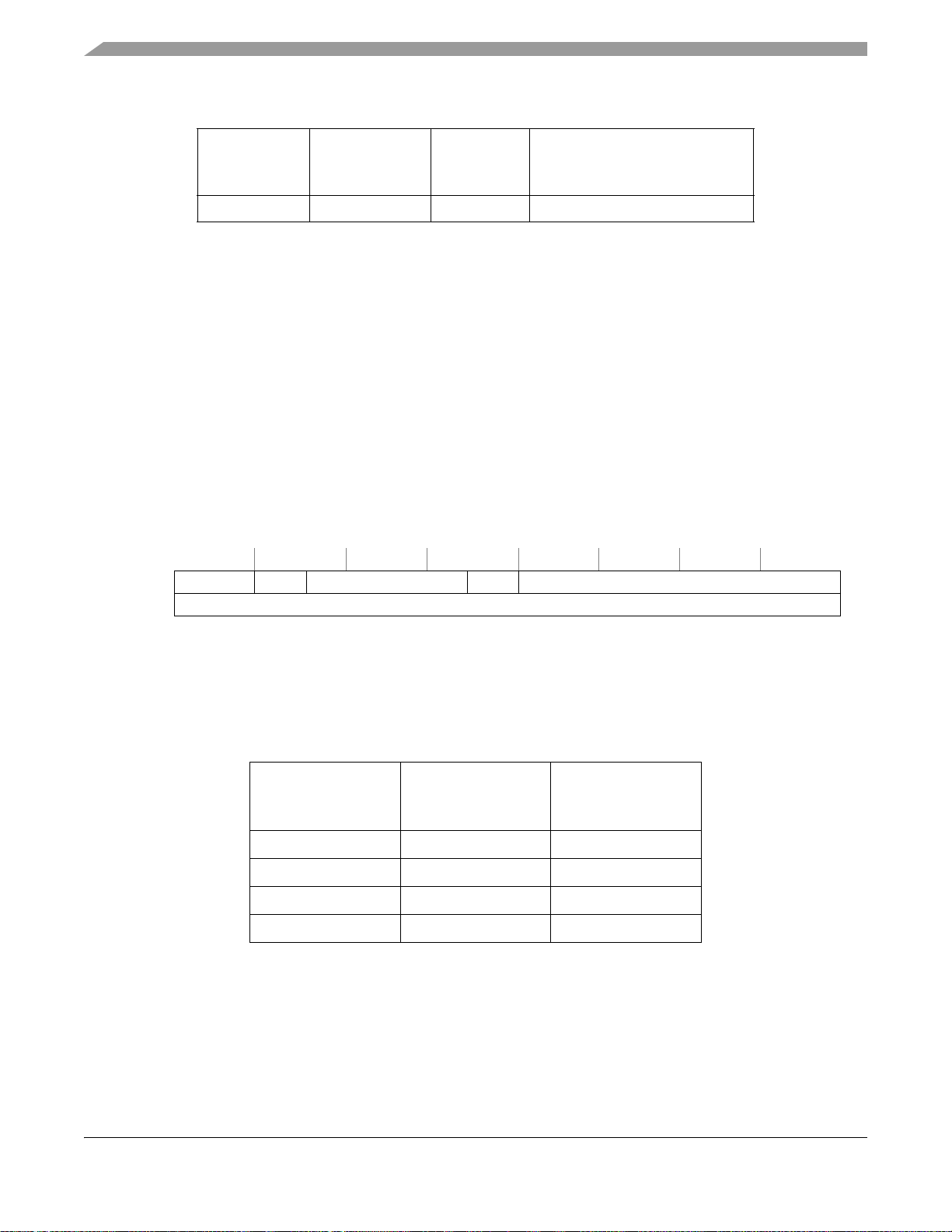

Chapter 1 Overview

This chapter provides an overview of the major features and functional components of the MCF52211

family of microcontrollers. The MCF52211 family is a highly integrated implementation of the ColdFire®

family of reduced instruction set computing (RISC) microcontrollers that also includes the MCF52210,

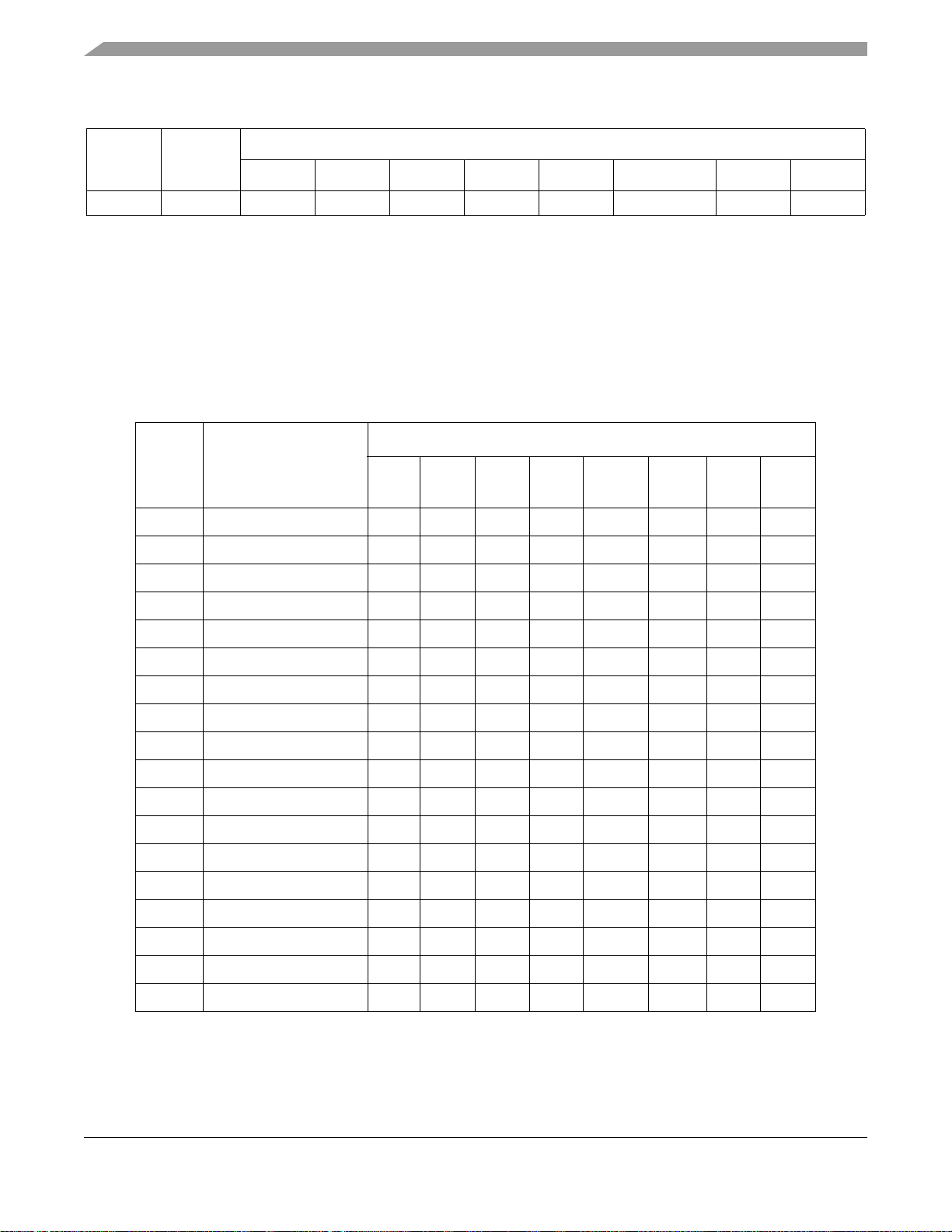

MCF52212, and MCF52213. The differences between these parts are summarized in Table 1-1. This

document is written from the perspective of the MCF52211.

The MCF52211 represents a family of highly-integrated 32-bit microcontrollers based on the V2 ColdFire

microarchitecture. Featuring up to 16 Kbytes of internal SRAM and up to 128 Kbytes of flash memory,

four 32-bit timers with DMA request capability , a 4-channel DMA controller , two I2C™ modules, up to 3

UAR T s and a queued SPI, the MCF5221 1 family has been designed for general-purpose industrial control

applications.

This 32-bit device is based on the Version 2 (V2) ColdFire reduced instruction set computing (RISC) core