MC9S12XHY256

Reference Manual

Covers MC9S12XHY Family

Data Sheet: Advance Information

This document contains information on a new product. Specifications and information here in are subject to change without notice.

S12

Microcontrollers

MC9S12XHY256RMV1

Rev. 1.04

06/2013

freescale.com

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

freescale.com/

A full list of family members and options is included in the appendices.

The following revision history table summarizes changes contained in this document.

This document contains information for all constituent modules, with the exception of the CPU. For CPU

information please refer to CPU12-1 in the CPU12 & CPU12X Reference Manual.

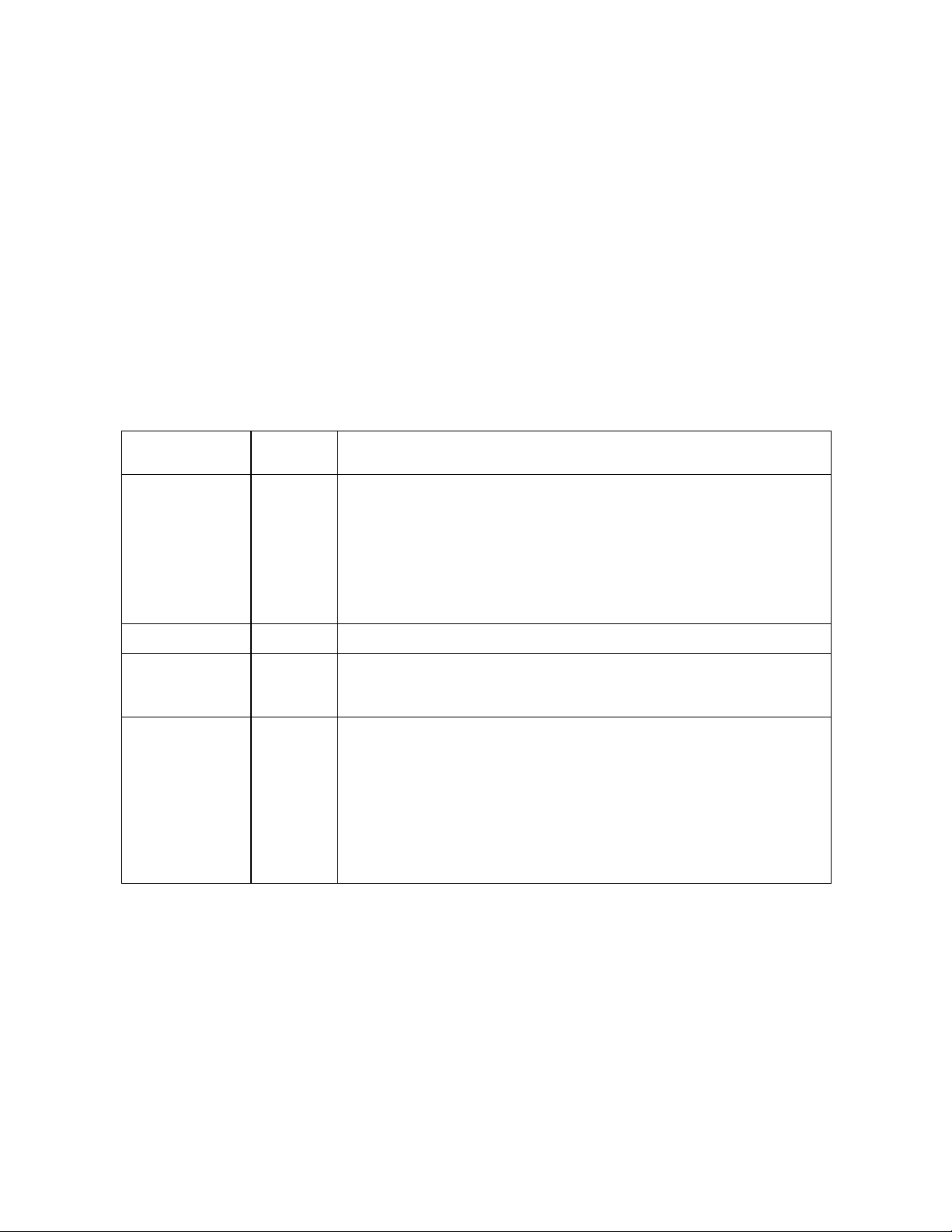

Revision History

Date

Mar,25,2011 1.01

May,09,2011 1.02 fix typo on Table 1-7,it is LQFP112 and LQFP100

May,13,2011 1.03

Jun,27,2013 1.04

Revision

Level

Description

update Appendix electrical parameter value

Table A-11., “Pseudo Stop and Full Stop Current,

Table A-9., “Module Run Supply Currents

Table A-6., “5-V I/O Characteristics, item 4b

update Appendix, change classifications or conditions

Table A-6., “5-V I/O Characteristics, item 4b, change from 80c to 150c

Table A-11., “Pseudo Stopand Full Stop Current,item11b,change from P toC

fix typo Table A-6., “5-V I/O Characteristics, 11 and 12, resistance not current

fix typo on Section 1.7.3.42, “PU[4] / IOC0_2 / M1C0M / M1COSM— Port U

I/O Pin [4],it is M1COSM

fix on Section Table A-12., “ATD Operating Characteristics,∆

update block version ADC1.06, MSCAN3.13, PWM1.1, BDM2.02, DBG3.26,

CRG2.01, INT2.07,FTMR256,FTMR128

add STOP/WAIT feature forSection Table 1-11., “Interrupt Vector Locations;

update FSL link; fix typo of unit at Table A-7, Table A-8, Table A-21, A.1.10.1,

A.1.10.2, A.1.10.3, Table A-10, Table A-14, Table A-15, A.3.1.15,Table A-16,

Table A-22, Table A-26, Table 1-1;

updateInstantaneous maximum current at Table A-1

fix reference link at 1.9 Modes of Operation and 1.10 Security

update Table A-6./A-725, leackage current

VDDX

=-0.1v

How to Reach Us:

Home Page:

freescale.com

Web Support:

freescale.com/support

Information in this document is provided solely to enable system and software

implementers to use Freescale products. There are no express or implied copyright

licenses granted hereunder to design or fabricate any integrated circuits based on the

information in this document.

Freescale reserves the right to make changes without further notice to any products

herein. Freescale makes no warranty, representation, or guarantee regarding the

suitability of its products for any particular purpose, nor does Freescale assume any

liability arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation consequential or incidental

damages. “Typical” parameters that may be provided in Freescale data sheets and/or

specifications can and do vary in different applications, and actual performance may

vary over time. All operating parameters, including “typicals,” must be validated for each

customer application by customer’s technical experts. Freescale does not convey any

license under its patent rights nor the rights of others. Freescale sells products

pursuant to standard terms and conditions of sale, which can be found at the following

address: freescale.com/SalesTermsandConditions

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc.,

Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their

respective owners.

© 2011, 2013 Freescale Semiconductor, Inc.

Document Number: MC9S12XHY256RMV1

06/2013

MC9S12XHY-Family Reference Manual, Rev. 1.04

4 Freescale Semiconductor

Chapter 1

Device Overview MC9S12XHY-Family. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Chapter 2

Port Integration Module (S12XHYPIMV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Chapter 3

Memory Mapping Control (S12XMMCV4) . . . . . . . . . . . . . . . . . . . . . . . . . . .157

Chapter 4

Interrupt (S12XINTV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

Chapter 5

Background Debug Module (S12XBDMV2) . . . . . . . . . . . . . . . . . . . . . . . . .199

Chapter 6

S12X Debug (S12XDBGV3) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

Chapter 7

S12XE Clocks and Reset Generator (S12XECRGV2) . . . . . . . . . . . . . . . . .261

Chapter 8

Pierce Oscillator (S12XOSCLCPV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .291

Chapter 9

Voltage Regulator (S12VREGL3V3V1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295

Chapter 10

Analog-to-Digital Converter (ADC12B12CV1) . . . . . . . . . . . . . . . . . . . . . . .313

Chapter 11

Freescale’s Scalable Controller Area Network (S12MSCANV3) . . . . . . . . .339

Chapter 12

Inter-Integrated Circuit (IICV3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .393

Chapter 13

Pulse-Width Modulator (S12PWM8B8CV1) . . . . . . . . . . . . . . . . . . . . . . . . . .421

Chapter 14

Serial Communication Interface (S12SCIV5) . . . . . . . . . . . . . . . . . . . . . . . .453

Chapter 15

Serial Peripheral Interface (S12SPIV5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .491

Chapter 16

Timer Module (TIM16B8CV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .517

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 5

Chapter 17

Liquid Crystal Display (LCD40F4BV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .545

Chapter 18

256 KByte Flash Module (S12XFTMR256K1V1) . . . . . . . . . . . . . . . . . . . . . .567

Chapter 19

128 KByte Flash Module (S12XFTMR128K1V1) . . . . . . . . . . . . . . . . . . . . . .617

Chapter 20

Motor Controller (MC10B8CV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .667

Chapter 21

Stepper Stall Detector (SSDV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .699

Appendix A

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .717

Appendix B

Package and Die Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .758

Appendix C

PCB Layout Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .765

Appendix D

Derivative Differences. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .768

Appendix E

Detailed Register Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .768

Appendix F

Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .799

MC9S12XHY-Family Reference Manual, Rev. 1.04

6 Freescale Semiconductor

Chapter 1

Device Overview MC9S12XHY-Family

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.3 Module Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.5 Device Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.6 Part ID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.7 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.8 System Clock Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1.9 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

1.10 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1.11 Resets and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1.12 COP Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

1.13 ATD External Trigger Input Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

1.14 ATD Channel[17] Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

1.15 VREG Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

1.16 Oscillator Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

1.17 Documentation Note . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Chapter 2

Port Integration Module (S12XHYPIMV1)

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

2.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

2.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

2.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

2.5 Initialization Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Chapter 3

Memory Mapping Control (S12XMMCV4)

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

3.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

3.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

3.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

3.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Chapter 4

Interrupt (S12XINTV2)

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

4.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

4.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

4.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

4.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 7

Chapter 5

Background Debug Module (S12XBDMV2)

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

5.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

5.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

5.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Chapter 6

S12X Debug (S12XDBGV3) Module

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

6.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

6.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

6.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Chapter 7

S12XE Clocks and Reset Generator (S12XECRGV2)

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

7.2 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

7.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

7.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

7.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

7.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

Chapter 8

Pierce Oscillator (S12XOSCLCPV2)

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

8.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

8.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

8.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

Chapter 9

Voltage Regulator (S12VREGL3V3V1)

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

9.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

9.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

9.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

Chapter 10

Analog-to-Digital Converter (ADC12B12CV1)

Block Description

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

10.2 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

10.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

MC9S12XHY-Family Reference Manual, Rev. 1.04

8 Freescale Semiconductor

10.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

10.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336

10.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

Chapter 11

Freescale’s Scalable Controller Area Network (S12MSCANV3)

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

11.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342

11.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

11.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

11.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

Chapter 12

Inter-Integrated Circuit (IICV3) Block Description

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 393

12.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 396

12.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 396

12.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408

12.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 413

12.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 413

12.7 Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 414

Chapter 13

Pulse-Width Modulator (S12PWM8B8CV1)

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

13.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

13.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 423

13.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

13.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

13.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

Chapter 14

Serial Communication Interface (S12SCIV5)

14.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 453

14.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

14.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

14.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

14.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 487

Chapter 15

Serial Peripheral Interface (S12SPIV5)

15.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 491

15.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493

15.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 9

15.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

Chapter 16

Timer Module (TIM16B8CV2) Block Description

16.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

16.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

16.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 522

16.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 539

16.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 543

16.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 543

Chapter 17

Liquid Crystal Display (LCD40F4BV2) Block Description

17.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 545

17.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 548

17.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 548

17.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 555

17.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 565

17.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 565

Chapter 18

256 KByte Flash Module (S12XFTMR256K1V1)

18.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 567

18.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 570

18.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 570

18.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 595

18.5 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 614

18.6 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 616

Chapter 19

128 KByte Flash Module (S12XFTMR128K1V1)

19.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 617

19.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 620

19.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 620

19.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 645

19.5 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 664

19.6 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 666

Chapter 20

Motor Controller (MC10B8CV1)

20.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 667

20.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 670

20.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 671

20.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 679

MC9S12XHY-Family Reference Manual, Rev. 1.04

10 Freescale Semiconductor

20.5 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 693

20.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 693

20.7 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 694

Chapter 21

Stepper Stall Detector (SSDV1) Block Description

21.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 699

21.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 701

21.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

21.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 710

Appendix A

Electrical Characteristics

A.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 717

A.1.1 Parameter Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 717

A.1.2 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 717

A.1.3 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 718

A.1.4 Current Injection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 719

A.1.5 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 719

A.1.6 ESD Protection and Latch-up Immunity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 720

A.1.7 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 721

A.1.8 Power Dissipation and Thermal Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 722

A.1.9 I/O Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 724

A.1.10 Supply Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 726

A.2 ATD Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 731

A.2.1 ATD Operating Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 731

A.2.2 Factors Influencing Accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 731

A.2.3 ATD Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 733

A.3 NVM, Flash. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 736

A.3.1 Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 736

A.3.2 NVM Reliability Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 741

A.4 Voltage Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 743

A.5 Output Loads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 744

A.5.1 Resistive Loads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 744

A.5.2 Capacitive Loads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 744

A.5.3 Chip Power-up and Voltage Drops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 744

A.6 Reset, Oscillator and PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 746

A.6.1 Startup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 746

A.6.2 Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 748

A.6.3 Phase Locked Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 748

A.7 LCD Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 750

A.8 MSCAN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 753

A.9 SPI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 754

A.9.1 Master Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 754

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 11

A.9.2 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 756

Appendix B

Package and Die Information

B.1 112-pin LQFP Mechanical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 759

B.2 100-Pin LQFP Mechanical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 762

Appendix C

PCB Layout Guidelines

C.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 765

C.1.1 112-Pin LQFP Recommended PCB Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 766

C.1.2 100-Pin QFP Recommended PCB Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 767

Appendix D

Derivative Differences

D.1 Memory Sizes and Package Options 9S12XHY family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 768

Appendix E

Detailed Register Address Map

E.1 Detailed Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 768

Appendix F

Ordering Information

F.1 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 799

MC9S12XHY-Family Reference Manual, Rev. 1.04

12 Freescale Semiconductor

Chapter 1 Device Overview MC9S12XHY-Family

1.1 Introduction

The MC9S12XHY family is an optimized, automotive, 16-bit microcontroller product line that is

specifically designed for entry level instrument clusters. This family also services generic automotive

applications requiring CAN, LCD, Motor driver control or LIN/SAE J2602. Typical examples of these

applications include instrument clusters for automobiles and 2 or 3 wheelers, HVAC displays, general

purpose motor control and body controllers.

The MC9S12XHY family uses many of the same features found on the MC9S12XS family and

MC9S12HY/HA family, including error correction code (ECC) on flash memory, a separate data-flash

module for diagnostic or data storage, a fast analog-to-digital converter (ATD) and a frequency modulated

phase locked loop (IPLL) that improves the EMC performance. The MC9S12XHY family features a 40x4

liquid crystal display (LCD) controller/driver and a motor pulse width modulator (MC) consisting of up to

16 high current outputs. The device is capable of stepper motor stall detection (SSD) via hardware or

software, please contact Freescale sales office for detailed information on software SSD.

The MC9S12XHY family deliver all the advantages and efficiencies of a 16-bit MCU while retaining the

low cost, power consumption, EMC, and code-size efficiency advantages currently enjoyed by users of

Freescale’s existing 8-bit and 16-bit MCU families. Like the MC9S12HY/HA family, the MC9S12XHY

family run 16-bit wide accesses without wait states for all peripherals and memories. The MC9S12XHY

family is available in 112-pin LQFP and 100-pin LQFP package options. In addition to the I/O ports

available in each module, further I/O ports are available with interrupt capability allowing wake-up from

stop or wait modes.

1.2 Features

This section describes the key features of the MC9S12XHY family.

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 13

Device Overview MC9S12XHY-Family

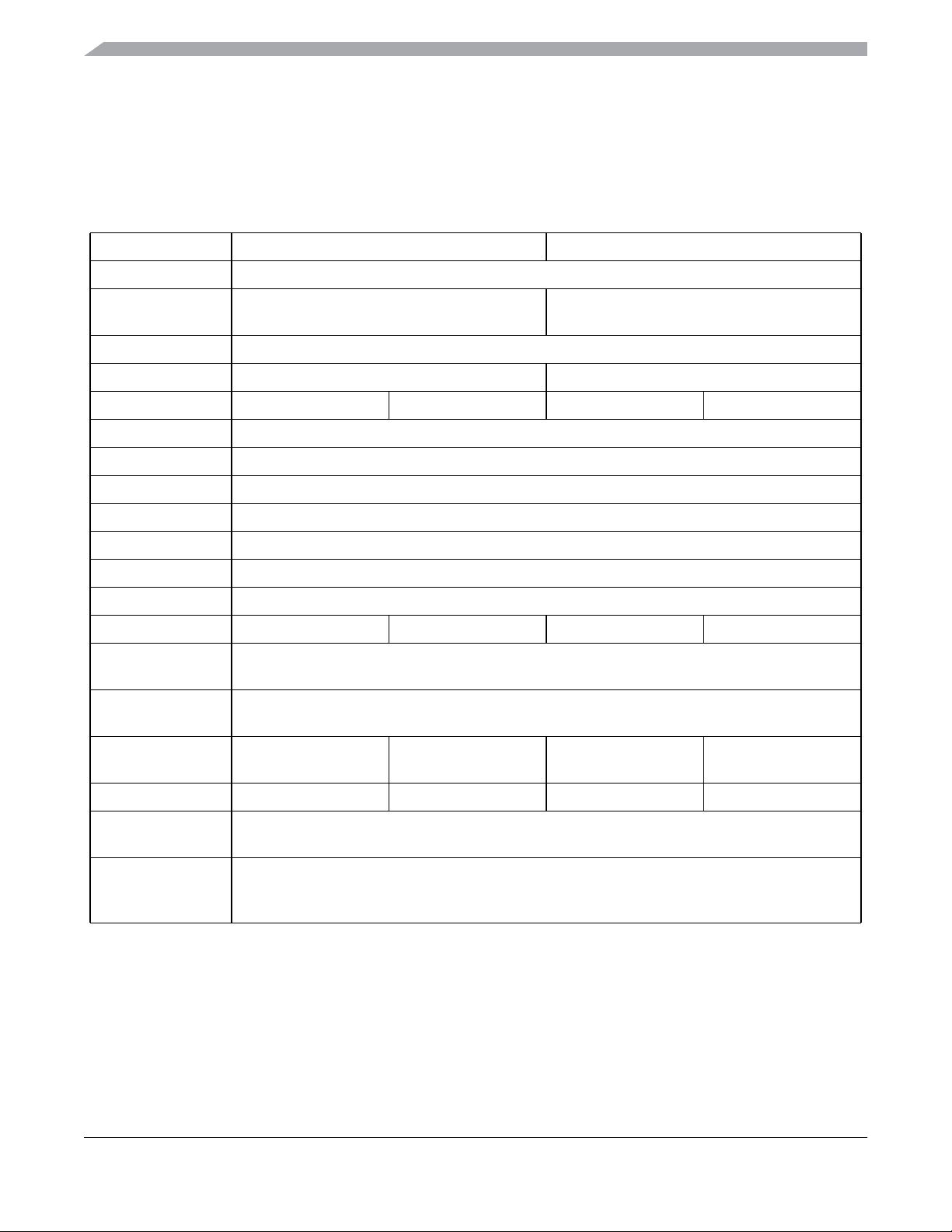

1.2.1 MC9S12XHY Family Comparison

Table 1-1 provides a summary of different members of the MC9S12XHY family and their proposed

features. This information is intended to provide an understanding of the range of functionality offered by

this microcontroller family.

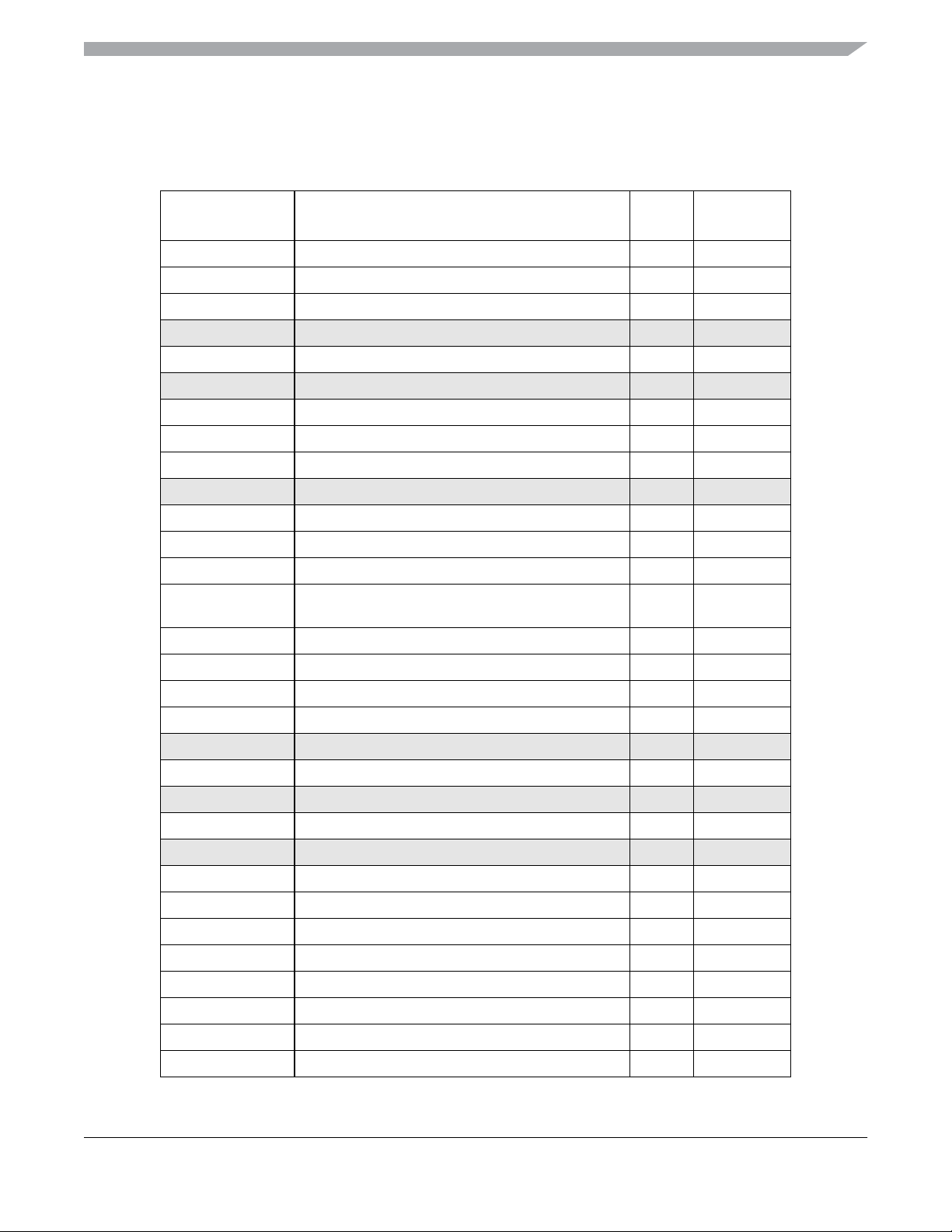

Table 1-1. MC9S12XHY Family

Feature

CPU

Flash memory

(ECC)

Data flash (ECC)

RAM

Pin Quantity

CAN

SCI

SPI

IIC

Timer 0

Timer 1

PWM

ADC (10-bit)

Stepper Motor

Controller

MC9S12XHY128 MC9S12XHY256

HCS12X V1

128Kbytes 256 Kbytes

8 Kbytes

8 Kbytes 12kbyte

100 112 100 112

2

2

1

1

8 ch x 16-bit

8 ch x 16-bit

8 ch x 8-bit or 4ch x16-bit

8 ch 12ch 8ch 12 ch

4

Stepper Stall

Detecter

LCD Driver

(FPxBP)

Key Wakeup Pins

Frequency Modulated PLL

External osc

(4–16 MHz Pierce

with loop control)

14 Freescale Semiconductor

38x4 40x4 38x4 40x4

23 25 23 25

MC9S12XHY-Family Reference Manual, Rev. 1.04

4

Yes

Yes

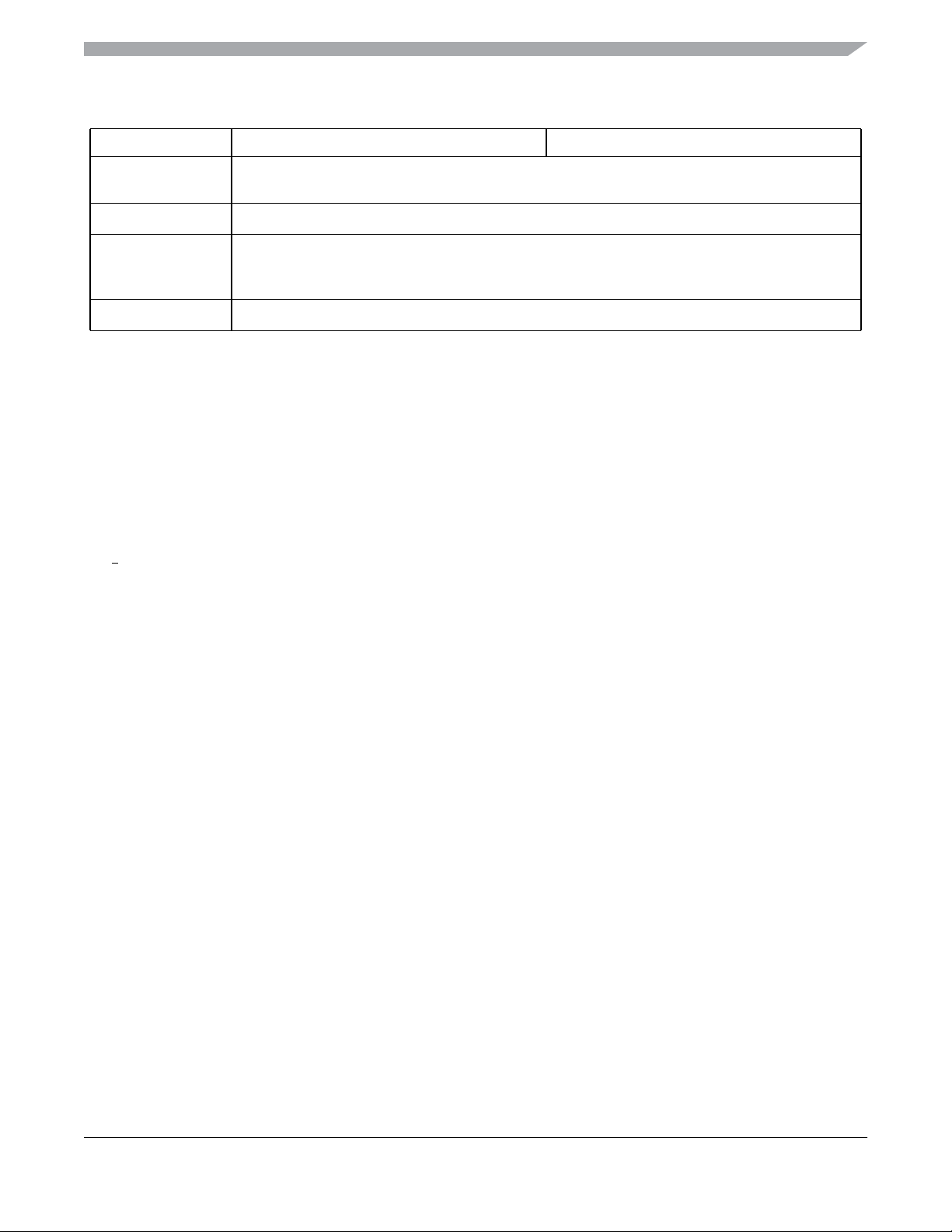

Table 1-1. MC9S12XHY Family

Device Overview MC9S12XHY-Family

Feature

Internal 1 MHz RC

osc

Supply voltage

RTI, LVI, CRG,

RST, COP, DBG,

POR, API

Execution speed

MC9S12XHY128 MC9S12XHY256

No

4.5 V – 5.5 V

Yes

Static-40 MHz

1.2.2 Chip-Level Features

On-chip modules available within the family include the following features:

• CPU12XV1 CPU core

• Up to 256 Kbyte on-chip flash with ECC

• 8Kbyte data flash with ECC

• Up to 12Kbyte on-chip SRAM

• Phase locked loop (IPLL) frequency multiplier with internal filter

• 4–16 MHz amplitude controlled Pierce oscillator

• Two timer modules (TIM0 and TIM1) supporting input/output channels that provide a range of 16bit input capture, output compare, counter and pulse accumulator functions

• Pulse width modulation (PWM) module with up to 8 x 8-bit channels

• Up to 12-channel, 10-bit resolution successive approximation analog-to-digital converter (ATD)

• Up to 40x4 LCD driver

• PWM motor controller (MC) with up to 16 high current drivers

• Output slew rate control on Motor driver pad

• One serial peripheral interface (SPI) module

• One Inter-IC bus interface (IIC) module

• Two serial communication interface (SCI) module supporting LIN communications

• Two multi-scalable controller area network (MSCAN) module (supporting CAN protocol 2.0A/B)

• On-chip voltage regulator (VREG) for regulation of input supply and all internal voltages

• Autonomous periodic interrupt (API)

• Stepper Motor Controller with up to drivers for up to 4 motors

• Four Stepper Stall Detector modules (one for each motor)

• Up to 25 key wakup inputs

1.3 Module Features

The following sections provide more details of the modules implemented on the MC9S12XHY family.

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 15

Device Overview MC9S12XHY-Family

1.3.1 S12 16-Bit Central Processor Unit (CPU)

The CPU12X is a high-speed, 16-bit processing unit that has a programming model identical to that of the

industry standard M68HC11 central processor unit (CPU).

• Upward compatible with S12 instruction set, with the exception of five Fuzzy instructions (MEM,

WAV, WAVR, REV, REVW) which have been removed

• Enhanced indexed addressing

• Access to large data segments independent of PPAGE

1.3.2 On-Chip Flash with ECC

On-chip flash memory on the MC9S12XHY features the following:

• Up to 256Kbyte of program flash memory

— 64data bits plus 8 syndrome ECC (error correction code) bits allow single bit error correction

and double fault bit detection

— Erase sector size 1024bytes

— Automated program and erase algorithm

— Protection scheme to prevent accidental program or erase

— Security option to prevent unauthorized access

— Sense-amp margin level setting for reads

• 8Kbyte data flash space

— 16 data bits plus 6 syndrome ECC (error correction code) bits allow single bit error correction

and double fault detection

— Erase sector size 256 bytes

— Automated program and erase algorithm

—

1.3.3 On-Chip SRAM

• Up to 12Kbytes of general-purpose RAM

1.3.4 Main External Oscillator (XOSC)

• Loop control Pierce oscillator using a 4 MHz to 16 MHz crystal

— Current gain control on amplitude output

— Signal with low harmonic distortion

— Low power

— Good noise immunity

— Eliminates need for external current limiting resistor

— Transconductance sized for optimum start-up margin for typical crystals

MC9S12XHY-Family Reference Manual, Rev. 1.04

16 Freescale Semiconductor

1.3.5 Internal Phase-Locked Loop (IPLL)

• Phase-locked-loop clock frequency multiplier

— No external components required

— Reference divider and multiplier allow large variety of clock rates

— Automatic bandwidth control mode for low-jitter operation

— Automatic frequency lock detector

— Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

–

1.3.6 Clocks and reset generation(CRG)

• COP watchdog

• Real time interrupt

• Clock monitor

• Fast wake up from STOP in self clock mode

1.3.7 System Integrity Support

Device Overview MC9S12XHY-Family

• Power-on reset (POR)

• System reset generation

• Illegal address detection with reset

• Low-voltage detection with interrupt or reset

• Real time interrupt (RTI)

• Computer operating properly (COP) watchdog

— Configurable as window COP for enhanced failure detection

— Initialized out of reset using option bits located in flash memory

• Clock monitor supervising the correct function of the oscillator

• Temperature sensor

1.3.8 Timer (TIM0)

• 8x 16-bit channels for input capture

• 8x 16-bit channels for output compare

• 16-bit free-running counter with 8-bit precision prescaler

• 1 x 16-bit pulse accumulator

1.3.9 Timer (TIM1)

• 8x 16-bit channels for input capture

• 8x 16-bit channels for output compare

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 17

Device Overview MC9S12XHY-Family

• 16-bit free-running counter with 8-bit precision prescaler

• 1 x 16-bit pulse accumulator

1.3.10 Liquid crystal display driver (LCD)

• Configurable for up to 40 frontplanes and 4 backplanes or general-purpose input or output

• 5 modes of operation allow for different display sizes to meet application requirements

• Unused frontplane and backplane pins can be used as general-purpose I/O

1.3.11 Motor Controller (MC)

• PWM motor controller (MC) with up to 16 high current drivers

• Each PWM channel switchable between two drivers in an H-bridge configuration

• Left, right and center aligned outputs

• Support for sine and cosine drive

• Dithering

• Output slew rate control

1.3.12 Pulse Width Modulation Module (PWM)

• 8channel x 8-bit or 4channel x 16-bit pulse width modulator

— Programmable period and duty cycle per channel

— Center-aligned or left-aligned outputs

— Programmable clock select logic with a wide range of frequencies

1.3.13 Inter-IC bus Module (IIC)

• 1 Inter-IC (IIC) bus module which has following feature

— Multi-master operation

— Soft programming for one of 256 different serial clock frequencies

— General Call(Broadcast) mode support

— 10-bit address support

1.3.14 Controller Area Network Module (MSCAN)

• 1 Mbit per second, CAN 2.0 A, B software compatible

— Standard and extended data frames

— 0–8 bytes data length

— Programmable bit rate up to 1 Mbps

• Five receive buffers with FIFO storage scheme

• Three transmit buffers with internal prioritization

• Flexible identifier acceptance filter programmable as:

MC9S12XHY-Family Reference Manual, Rev. 1.04

18 Freescale Semiconductor

Device Overview MC9S12XHY-Family

— 2 x 32-bit

— 4 x 16-bit

— 8 x 8-bit

• Wakeup with integrated low pass filter option

• Loop back for self test

• Listen-only mode to monitor CAN bus

• Bus-off recovery by software intervention or automatically

• 16-bit time stamp of transmitted/received messages

1.3.15 Serial Communication Interface Module (SCI)

• Full-duplex or single-wire operation

• Standard mark/space non-return-to-zero (NRZ) format

• Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

• 13-bit baud rate selection

• Programmable character length

• Programmable polarity for transmitter and receiver

• Active edge receive wakeup

• Break detect and transmit collision detect supporting LIN

1.3.16 Serial Peripheral Interface Module (SPI)

• Configurable 8- or 16-bit data size

• Full-duplex or single-wire bidirectional

• Double-buffered transmit and receive

• Master or slave mode

• MSB-first or LSB-first shifting

• Serial clock phase and polarity options

1.3.17 Analog-to-Digital Converter Module (ATD)

• Up to 12-channel, 10-bit analog-to-digital converter

— 3 us single conversion time

— 8-/10 bit resolution

— Left or right justified result data

— Internal oscillator for conversion in stop modes

— Wakeup from low power modes on analog comparison > or <= match

— Continuous conversion mode

— Multiple channel scans

• Pins can also be used as digital I/O

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 19

Device Overview MC9S12XHY-Family

1.3.18 On-Chip Voltage Regulator (VREG)

• Linear voltage regulator with bandgap reference

• Low-voltage detect (LVD) with low-voltage interrupt (LVI)

• Power-on reset (POR) circuit

• Low-voltage reset (LVR)

1.3.19 Background Debug (BDM)

• Background debug module (BDM) with single-wire interface

• Non-intrusive memory access commands

• Supports in-circuit programming of on-chip nonvolatile memory

1.3.20 Debugger (DBG)

• Three comparators A, B, C, and D to monitor CPU buses

• Trace buffer with depth of 64 entries

• Comparator A and C compares full address bus and 16-bit data bus with mask register

• Three modes: simple address/data match, inside address range, or outside address range

1.3.21 SSD

• Programmable Full Step State

• Programmable Integration polarity

• Blanking (recirculation) state

• 16-bit Integration Accumulator register

• 16-Bit Modulus Down Counter with interrupt

• Multiplex two stepper motors

1.3.22 INT (interrupt module)

• Seven levels of nested interrupts

• Flexible assignment of interrupt sources to each interrupt level.

• External non-maskable high priority interrupt (XIRQ)

• The following inputs can act as Wake-up Interrupts

— IRQ and non-maskable XIRQ

— CAN receive pins

— SCI receive pins

— Depending on the package option up to 25 pins on ports R, S, T and AD, configurable as rising

or falling edge sensitive

•

MC9S12XHY-Family Reference Manual, Rev. 1.04

20 Freescale Semiconductor

Device Overview MC9S12XHY-Family

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 21

Device Overview MC9S12XHY-Family

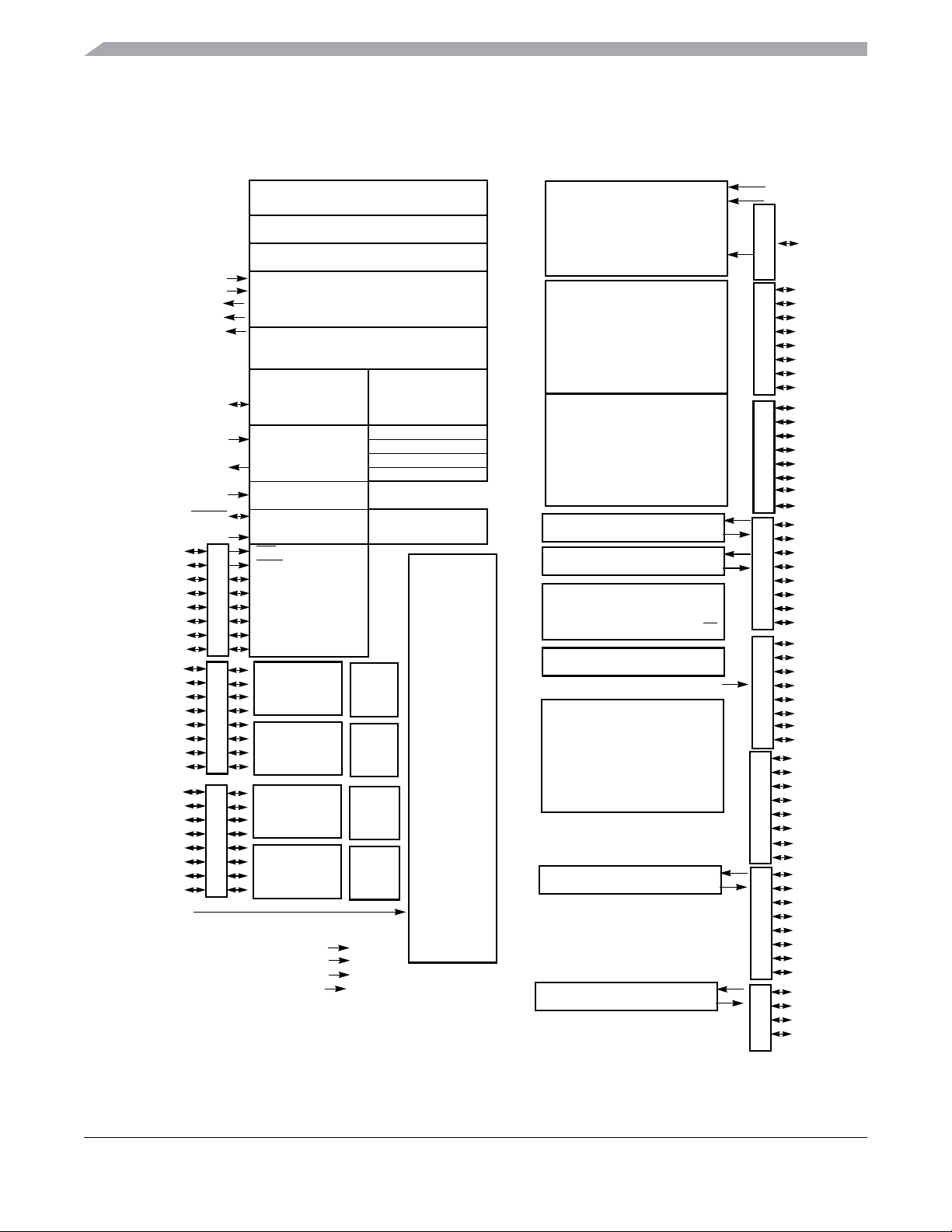

1.4 Block Diagram

Figure 1-1 shows a block diagram of the MC9S12XHY-Family devices

PA 0

PA 1

PA 2

PA 3

PA 4

PA 5

PA 6

PA 7

PU0

PU1

PU2

PU3

PU4

PU5

PU6

PU7

PV0

PV1

PV2

PV3

PV4

PV5

PV6

PV7

VLCD

VDDR

VSS3

VDD

VDDF

VDDPLL

BKGD

EXTAL

XTAL

VSSPLL

RESET

TEST

Single-wire Background

Debug Module

Amplitude Controlled

Low Power Pierce or

Full drive Pierce

Oscillator

PLL with Frequency

Modulation option

Reset Generation

and Test Entry

IRQ

XIRQ

PTA

Motor Driver0

PTU

Motor Driver1

Motor Driver2

PTV

Motor Driver3

5V IO Supply

VDDX/VSSX

VDDM1/VSSM1

VDDM2/VSSM2

VDDA/VSSA

256K/128K bytes Flash

12K/8K bytes RAM

8K bytes Data Flash

Voltage Regulator

CPU12X-V1

Debug Module

3 address breakpoints

1 data breakpoints

64 Byte Trace Buffer

Clock Monitor

COP Watchdog

Periodic Interrupt

Auto. Periodic Int.

Multilevel

Interrupt Module

SSD 0

SSD 1

SSD 2

SSD 3

ATD

10-bit 12-channel

Analog-Digital Converter

TIM1

TIM0

SCI0

Asynchronous Serial IF

CAN0

msCAN 2.0B

SPI

Synchronous Serial IF

IIC

PWM

8-bit 8channel

Pulse Width Modulator

40 X 4 LCD display

CAN1

msCAN 2.0B

SCI1

Asynchronous Serial IF

AN[7:0]

IOC1_0

IOC1_1

IOC1_2

IOC1_3

IOC1_4

IOC1_5

IOC1_6

IOC1_7

IOC0_0

IOC0_1

IOC0_2

IOC0_3

IOC0_4

IOC0_5

IOC0_6

IOC0_7

RXD

TXD

RXCAN

TXCAN

MISO

MOSI

SCK

SDA

SCL

ECLK

PWM0

PWM1

PWM2

PWM3

PWM4

PWM5

PWM6

PWM7

RXCAN

TXCAN

RXD

TXD

SS

VDDA/VRH

VSSA/VRL

PAD[11:0]

PTAD(KWU)

PT0

PT1

PT2

PT3

PT4

PT5

PTT(KWU)

PT6

PT7

PP0

PP1

PP2

PP3

PP4

PTP

PP5

PP6

PP7

PS0

PS1

PS2

PS3

PS4

PS5

PTS(KWU)

PS6

PS7

PH0

PH1

PH2

PH3

PH4

PTH

PH5

PH6

PH7

PB0

PB1

PB2

PB3

PB4

PTB

PB5

PB6

PB7

PR0

PR1

PR2

PR3

PR4

PR5

PTR(KWU)

PR6

PR7

PM0

PM1

PM2

PTM

PM3

Figure 1-1. MC9S12XHY-Family 112 LQFP Block Diagram

MC9S12XHY-Family Reference Manual, Rev. 1.04

22 Freescale Semiconductor

1.5 Device Memory Map

Table 1-2 shows the device register memory map.

Table 1-2. Device Register Memory Map

Device Overview MC9S12XHY-Family

Address Module

0x0000–0x0009 PIM (port integration module

0x000A–0x000B MMC (memory map control) 2 769

0x000C–0x000D PIM (port integration module) 2 769

0x000E–0x000F Reserved 2

0x0010–0x0017 MMC (memory map control) 8 769

0x0018–0x0019 Reserved 2

0x001A–0x001B Device ID register 2 770

0x001C–0x001F PIM (port integration module) 4 770

0x0020–0x002F DBG (debug module) 16 771

0x0030–0x0033 Reserved 4

0x0034–0x003F ECRG (clock and reset generator) 12 772

0x0040–0x006F TIM0 (timer module) 48 773

0x0070–0x009F ATD (analog-to-digital converter 10 bit 8-channel) 48 775

0x00A0–0x00C7 PWM (pulse-width modulator 8 channels) 40 776

0x00C8–0x00CF SCI0 (serial communications interface) 8 778

) 10 768

Size

(Bytes)

reference

pages

0x00D0–0x00D7 SCI1 (serial communications interface) 8 779

0x00D8–0x00DF SPI (serial peripheral interface) 8 779

0x00E0–0x00E7 IIC (Inter IC bus) 8 780

0x00E8–0x00FF Reserved 24

0x0100–0x0113 FTMR control registers 20 781

0x0114–0x011F Reserved 12

0x0120-0x012F INT (interrupt module) 16 782

0x0130–0x013F Reserved 16

0x0140–0x017F CAN0 64 783

0x0180–0x01BF CAN1 64 785

0x1C0–0x1FF MC(motor controller) 64 786

0x0200–0x021F LCD 32 788

0x0220–0x0227 Stepper Stall Detector 0 (SSD0) 8 789

0x0228–0x022F Stepper Stall Detector 1 (SSD1) 8 790

0x0230–0x0237 Stepper Stall Detector 2 (SSD2) 8 790

0x0238–0x023F Stepper Stall Detector 3 (SSD3) 8 791

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 23

Device Overview MC9S12XHY-Family

Address Module

0x0240–0x029F PIM (port integration module) 96 791

0x02A0–0x02CF TIM1(timer module) 48 795

0x02D0–0x02EF Reserved 32

0x02F0–0x02F7

0x02F8–0x02FF Reserved 8

0x0300–0x03FF Reserved 256

0x0400–0x07FF Reserved 1024

Voltage regulator

Size

(Bytes)

8 797

reference

pages

NOTE

Reserved register space shown in Table 1-2 is not allocated to any module.

This register space is reserved for future use. Writing to these locations have

no effect. Read access to these locations returns zero.

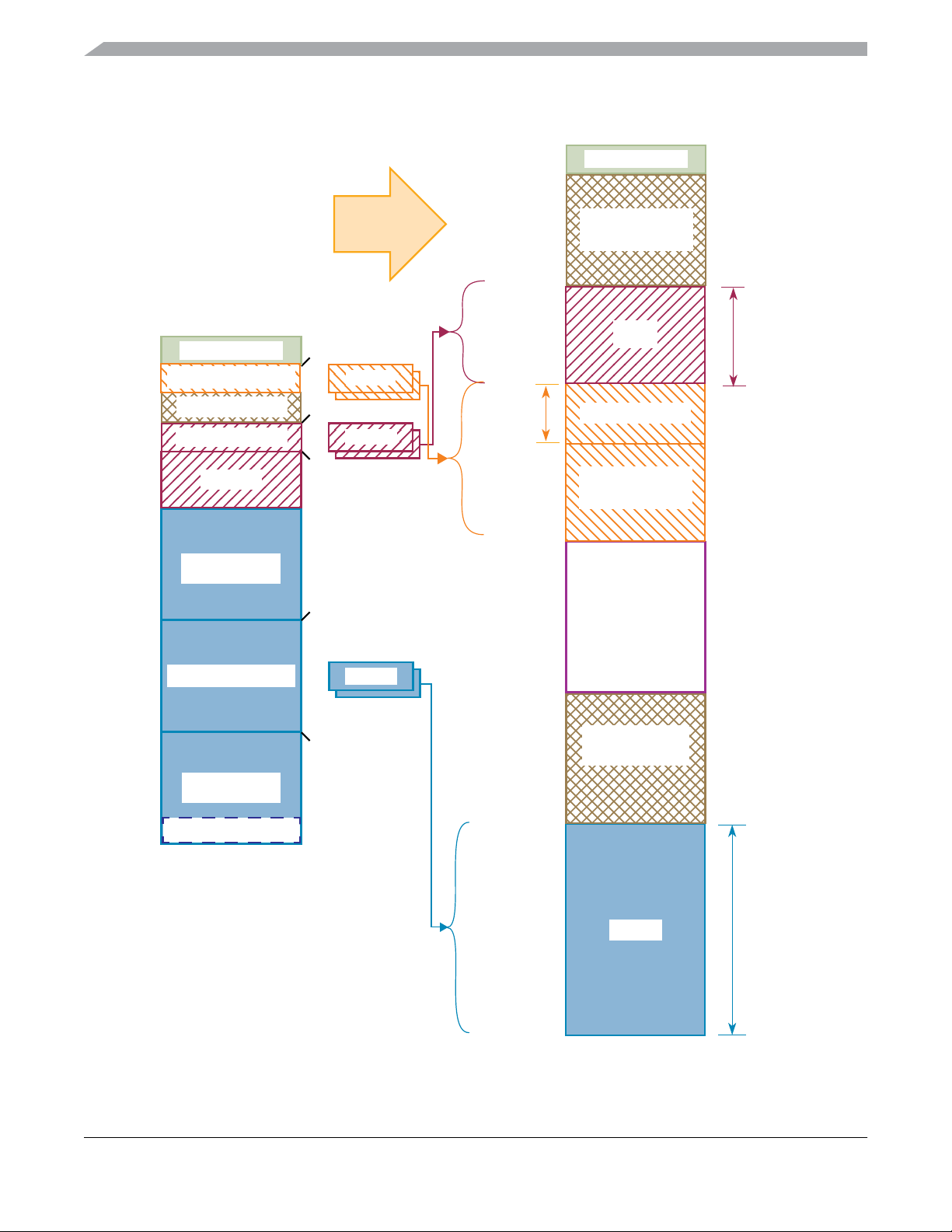

Figure 1-2 shows MC9S12XHY family CPU and BDM local address translation to the global memory

map. It indicates also the location of the internal resources in the memory map.

Accessing the reserved area in the range of 0x0C00 to 0x0FFF will return undefined data values.

A CPU access to any unimplemented space causes an illegal address reset.

The range between 0x10_0000 and 0x13_FFFF is mapped to DFLASH (Data Flash). The DFLASH block

sizes are listed in Table 1-3.

MC9S12XHY-Family Reference Manual, Rev. 1.04

24 Freescale Semiconductor

Device Overview MC9S12XHY-Family

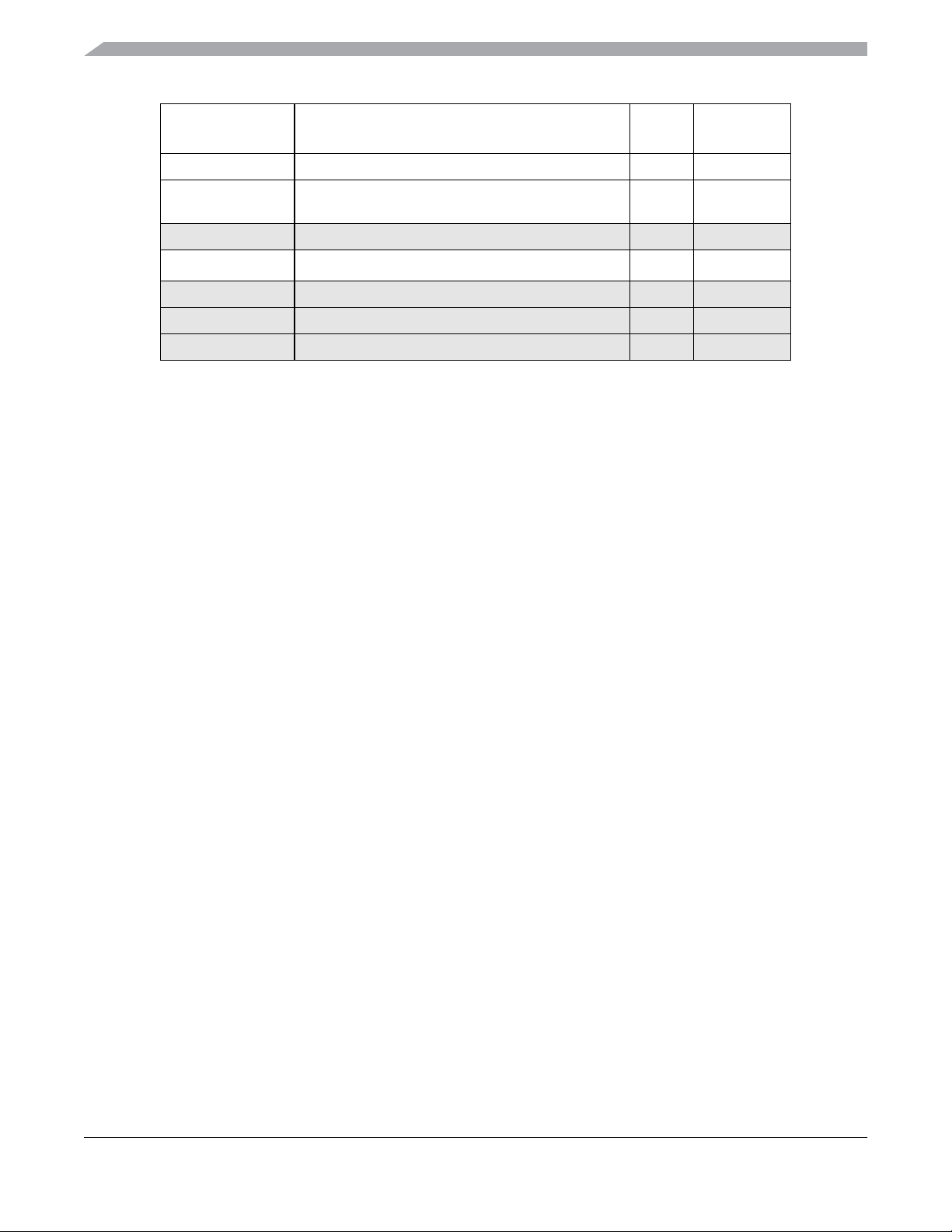

Table 1-3. Derivative Dependent Memory Parameters of Device Internal Resources

Device FLASH_LOW

SIZE/

PPAGE

(1)

RAM_LOW

SIZE/

RPAGE

(2)

DF_HIGH

S12XHY256 0x7C_0000 256K / 16 0x0F_D000 12K / 3 0x10_1FFF 8K / 8

S12XHY128 0x7E_0000 128K / 8 0x0F_E000 8K / 2 0x10_1FFF 8K / 8

1. Number of 16K pages addressable via PPAGE register

2. Number of 4K pages addressing the RAM.

3. Number of 1K pages addressing the DFLASH

SIZE/

EPAGE

(3)

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 25

Device Overview MC9S12XHY-Family

Figure 1-2. MC9S12XHY-Family Global Memory Map

CPU and BDM

Local Memory Map

0x0000

0x0800

0x0C00

0x1000

0x2000

0x4000

2K REGISTERS

1K DFLASH window

4K RAM window

Reserved

8K RAM

Unpaged

16K FLASH

EPAGE

RPAGE

0x00_0000

0x00_07FF

RAM_LOW

0x0F_FFFF

DF_HIGH

0x13_FFFF

2K REGISTERS

Unimplemented

RAM

RAM

RAMSIZE

DFLASH

DFLASH

Resources

0x8000

0xC000

0xFFFF

16K FLASH window

Unpaged

16K FLASH

Vectors

PPAGE

Unimplemented

Space

0x3F_FFFF

Unimplemented

FLASH

FLASH_LOW

FLASH

FLASHSIZE

0x7F_FFFF

MC9S12XHY-Family Reference Manual, Rev. 1.04

26 Freescale Semiconductor

Device Overview MC9S12XHY-Family

NOTE

MC9S12XHY-Family memory map is difference with MCU9S12HY64

Family device

1.6 Part ID Assignments

The part ID is located in two 8-bit registers PARTIDH and PARTIDL (addresses 0x001A and 0x001B).

The read-only value is a unique part ID for each revision of the chip. Table 1-4 shows the assigned part ID

number and Mask Set number.

The Version ID in Table 1-4. is a word located in a flash information row at address 0x40_00E8. The

version ID number indicates a specific version of internal NVM controller.

Table 1-4. Assigned Part ID Numbers

Device Mask Set Number Part ID

MC9S12XHY256 0M23Y $E010 $FFFF

MC9S12XHY128 0M23Y $E010 $FFFF

1. The coding is as follows:

Bit 15-12: Major family identifier

Bit 11-6: Minor family identifier

Bit 5-4: Major mask set revision number including FAB transfers

Bit 3-0: Minor — non full — mask set revision

(1)

Version ID

1.7 Signal Description

This section describes signals that connect off-chip. It includes a pinout diagram, a table of signal

properties, and detailed discussion of signals. It is built from the signal description sections of the

individual IP blocks on the device.

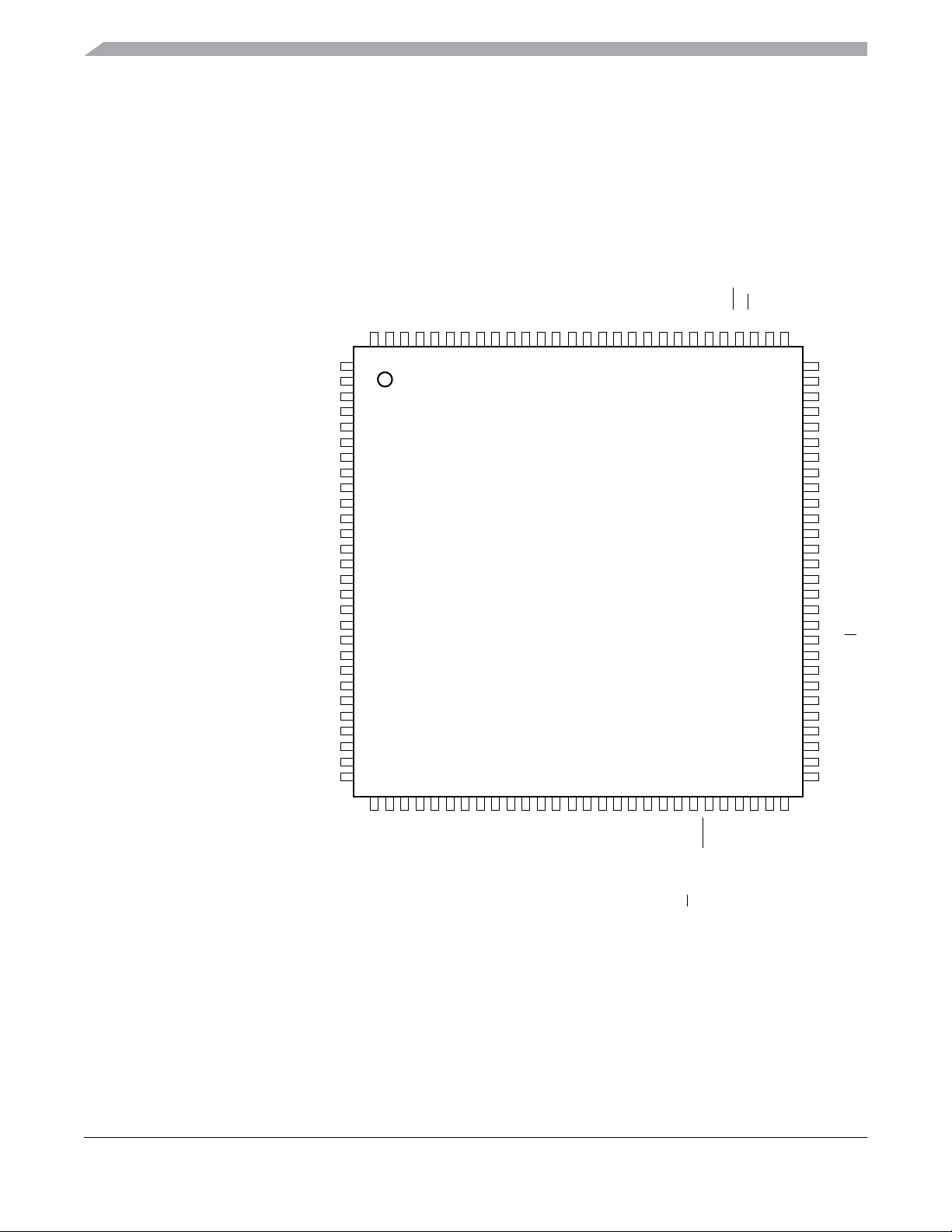

1.7.1 Device Pinout

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 27

Device Overview MC9S12XHY-Family

PAD04 /AN04 /KWAD4

PAD03 /AN03 /KWAD3

PAD02 /AN02 /KWAD2

PAD01 /AN01 /KWAD1

PAD00 /AN00 /KWAD0

VDDA /VRH

VSSA /VRL

BKGD /MODC

VLCD

PB7 /BP3

PB6 /BP2

PB5 /BP1

PB4 /BP0

VDD

VSS2

PB3 /FP39

PB2 /FP38

PB1 /FP37

PA7 /FP36

PA6 /FP35

PA5 /FP34

PA4 /FP33

PA3 /API_EXTCLK /XCLKS /FP32

PA2 /FP31

PA1 /XIRQ /FP30

PA0 /IRQ /FP29

PB0 /FP28

PR7 /FP27

KWAD5 /AN05 /PAD05

KWAD6 /AN06 /PAD06

KWAD7 /AN07 /PAD07

AN08 /PAD08

AN09 /PAD09

AN10 /PAD10

AN11 /PAD11

TEST

M0COSM /M0C0M /IOC0_0 /PU0

M0COSP /M0C0P /PU1

M0SINM /M0C1M /IOC0_1 /PU2

M0SINP /M0C1P /PU3

VDDM1

VSSM1

M1COSM /M1C0M /IOC0_2 /PU4

M1COSP /M1C0P /PU5

M1SINM /M1C1M /IOC0_3 /PU6

M1SINP /M1C1P /PU7

M2COSM /M2C0M /IOC0_4 /IOC1_0 /SCL /PWM4 /MISO /PV0

M2COSP /M2C0P /MOSI /PWM5 /PV1

M2SINM /M2C1M /IOC0_5 /IOC1_1 /SCK /PWM6 /PV2

M2SINP /M2C1P /SDA /PWM7 /SS /PV3

VDDM2

VSSM2

M3COSM /M3C0M /IOC0_6 /IOC1_2 /PV4

M3COSP /M3C0P /PV5

M3SINM /M3C1M /IOC0_7 /IOC1_3 /PV6

M3SINP /M3C1P /PV7

112

111

110

109

108

107

106

105

104

1

103

999897969594939291908988878685

102

101

100

2

3

4

5

6

7

8

9

10

11

MC9S12XHY-Family

112LQFP

12

13

14

15

16

17

18

19

Pins shown in BOLD are not

availableon the 100 LQFP package

20

21

22

23

24

25

26

27

28

293031323334353637383940414243444546474849505152535455

84

PH7 /FP26

83

PH6 /FP25

82

VDDPLL

81

XTAL

80

EXTAL

79

VSSPLL

78

VSS3

77

VDDR

76

PH5 /FP24

75

PH4 /FP23

74

VDDX1

73

VSSX1

72

PM3 /PWM7 /IOC1_3

71

PM2 /PWM6 /IOC1_2

70

PM1 /PWM5 /IOC0_3 /TXD1

69

PM0 /PWM4 /IOC0_2 /RXD1

68

VSS1

67

VDDF

66

PH3 /SS/ FP22

65

PH2 /ECLK /SCK /FP21

64

PH1 /MOSI /TXD1 /FP20

63

PH0 /MISO /RXD1 /FP19

62

PR6 /SCL /FP18

61

PR5 /SDA /FP17

60

PT7 /IOC0_7 /KWT7 /FP16

59

PT6 /IOC0_6 /KWT6 /FP15

58

PT5 /IOC0_5 /KWT5 /FP14

57

PT4 /IOC0_4 /KWT4 /FP13

56

VSSX2

FP0 /PWM0 /PP0

FP1 /PWM1 /PP1

FP2 /PWM2 /PP2

FP3 /PWM3 /PP3

FP4 /PWM4 /PP4

FP5 /PWM5 /PP5

FP6 /PWM6 /PP6

FP7 /PWM7 /PP7

TXD0 /PWM7 /PS1

RXD0 /PWM6 /PS0

KWR2 /IOC1_6 /PR2

KWR3 /IOC1_7 /PR3

VDDX2

MISO /SCL /PWM0 /PS4

KWS3 /TXCAN0 /PWM5 /PS3

KWS2 /RXCAN0 /PWM4 /PS2

KWR1 /TXCAN1 /IOC0_7 /PR1

KWR0 /RXCAN1 /IOC0_6 /PR0

RESET

SS /SDA /PWM3 /PS7

KWS6 /SCK /PWM2 /PS6

FP8 /KWT0 /IOC1_4 /PT0

KWS5 /MOSI /PWM1 /PS5

FP9 /KWT1 /IOC1_5 /PT1

FP10 /KWT2 /IOC1_6 /PT2

FP12 /KWR4 /PR4

FP11 /KWT3 /IOC1_7 /PT3

Figure 1-3. MC9S12XHY-Family 112 LQFP pinout

MC9S12XHY-Family Reference Manual, Rev. 1.04

28 Freescale Semiconductor

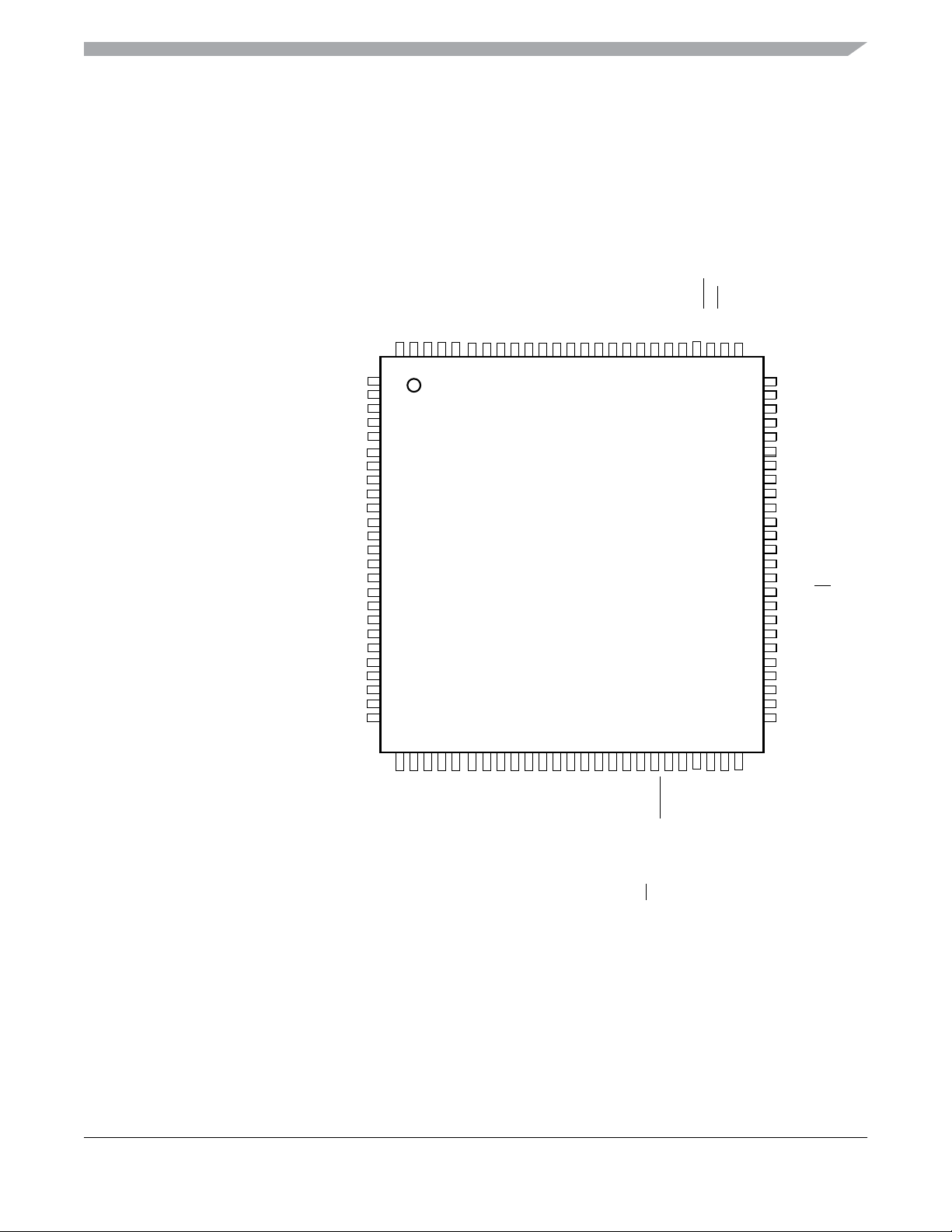

PAD04 /AN04 /KWAD4

PAD03 /AN03 /KWAD3

PAD02 /AN02 /KWAD2

PAD01 /AN01 /KWAD1

PAD00 /AN00 /KWAD0

VDDA /VRH

VSSA /VRL

BKGD /MODC

VLCD

PB7 /BP3

PB6 /BP2

PB5 /BP1

PB4 /BP0

VDD

VSS2

Device Overview MC9S12XHY-Family

PA0 /IRQ /FP29

PB1 /FP37

PA7 /FP36

PA6 /FP35

PA5 /FP34

PA4 /FP33

PA3 /API_EXTCLK /XCLKS /FP32

PA2 /FP31

PA1 /XIRQ /FP30

PB0 /FP28

KWAD5 /AN05 /PAD05

KWAD6 /AN06 /PAD06

KWAD7 /AN07 /PAD07

TEST

M0COSM /M0C0M /IOC0_0 /PU0

M0COSP /M0C0P /PU1

M0SINM /M0C1M /IOC0_1 /PU2

M0SINP /M0C1P /PU3

VDDM1

VSSM1

M1COSM /M1C0M /IOC0_2 /PU4

M1COSP /M1C0P /PU5

M1SINM /M1C1M /IOC0_3 /PU6

M1SINP /M1C1P /PU7

M2COSM/M2C0M/IOC0_4/IOC1_0/SCL/PWM4/MISO/PV0

M2COSP /M2C0P /MOSI /PWM5 /PV1

M2SINM /M2C1M /IOC0_5 /IOC1_1 /SCK /PWM6 /PV2

M2SINP /M2C1P /SDA /PWM7 /SS /PV3

VDDM2

VSSM2

M3COSM /M3C0M /IOC0_6 /IOC1_2 /PV4

M3COSP /M3C0P /PV5

M3SINM /M3C1M /IOC0_7 /IOC1_3 /PV6

M3SINP /M3C1P /PV7

FP0 /PWM0 /PP0

9998979695949392919089888786858483828180797877

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26272829303132333435363738394041424344454647484950

MC9S12XHY-Family

100 LQFP

VSSX2

VDDX2

RESET

76

PR7 /FP27

75

PH7 /FP26

74

PH6 /FP25

73

VDDPLL

72

XTAL

71

EXTAL

70

VSSPLL

69

VSS3

68

VDDR

67

PH5 /FP24

66

PH4 /FP23

65

VDDX1

64

VSSX1

63

VSS1

62

VDDF

61

PH3 /SS/ FP22

60

PH2 /ECLK /SCK /FP21

59

PH1 /MOSI /TXD1 /FP20

58

PH0 /MISO /RXD1 /FP19

57

PR6 /SCL /FP18

56

PR5 /SDA /FP17

55

PT7 /IOC0_7 /KWT7 /FP16

54

PT6 /IOC0_6 /KWT6 /FP15

53

PT5 /IOC0_5 /KWT5 /FP14

52

PT4 /IOC0_4 /KWT4 /FP13

51

FP1 /PWM1 /PP1

FP2 /PWM2 /PP2

FP3 /PWM3 /PP3

FP4 /PWM4 /PP4

FP5 /PWM5 /PP5

FP6 /PWM6 /PP6

FP7 /PWM7 /PP7

TXD0 /PWM7 /PS1

RXD0 /PWM6 /PS0

KWS3 /TXCAN0 /PWM5 /PS3

KWS2 /RXCAN0 /PWM4 /PS2

SS /SDA /PWM3 /PS7

MISO /SCL /PWM0 /PS4

KWS6 /SCK /PWM2 /PS6

KWS5 /MOSI /PWM1 /PS5

KWR1 /TXCAN1 /IOC0_7 /PR1

KWR0 /RXCAN1 /IOC0_6 /PR0

FP8 /KWT0 /IOC1_4 /PT0

FP12 /KWR4 /PR4

FP9 /KWT1 /IOC1_5 /PT1

FP10 /KWT2 /IOC1_6 /PT2

FP11 /KWT3 /IOC1_7 /PT3

Figure 1-4. MC9S12XHY-Family 100LQFP pinout

MC9S12XHY-Family Reference Manual, Rev. 1.04

Freescale Semiconductor 29

Device Overview MC9S12XHY-Family

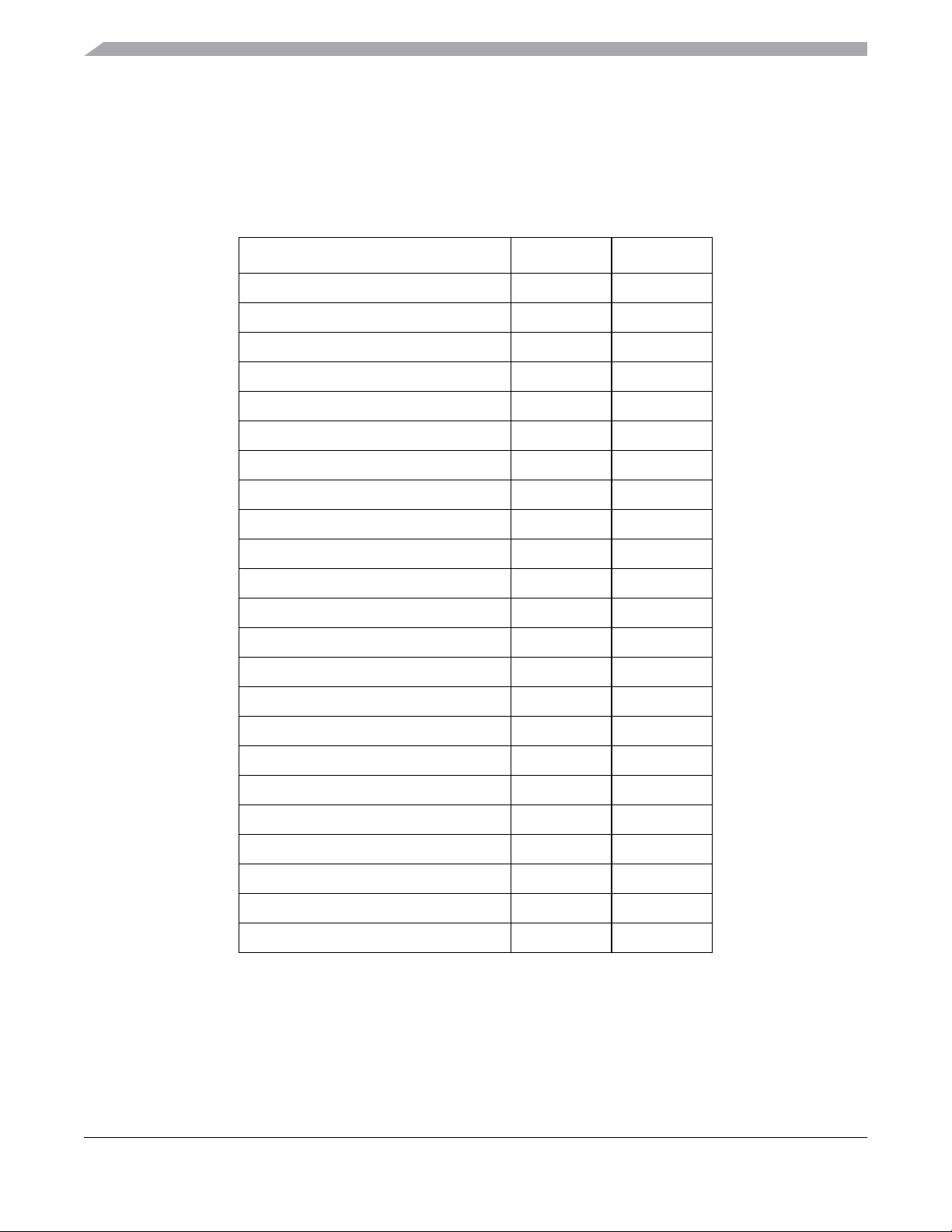

1.7.2 Pin Assignment Overview

Table 1-5 provides a summary of which Ports are available for each package option. Routing of pin

functions is summarized in Table 1-6.

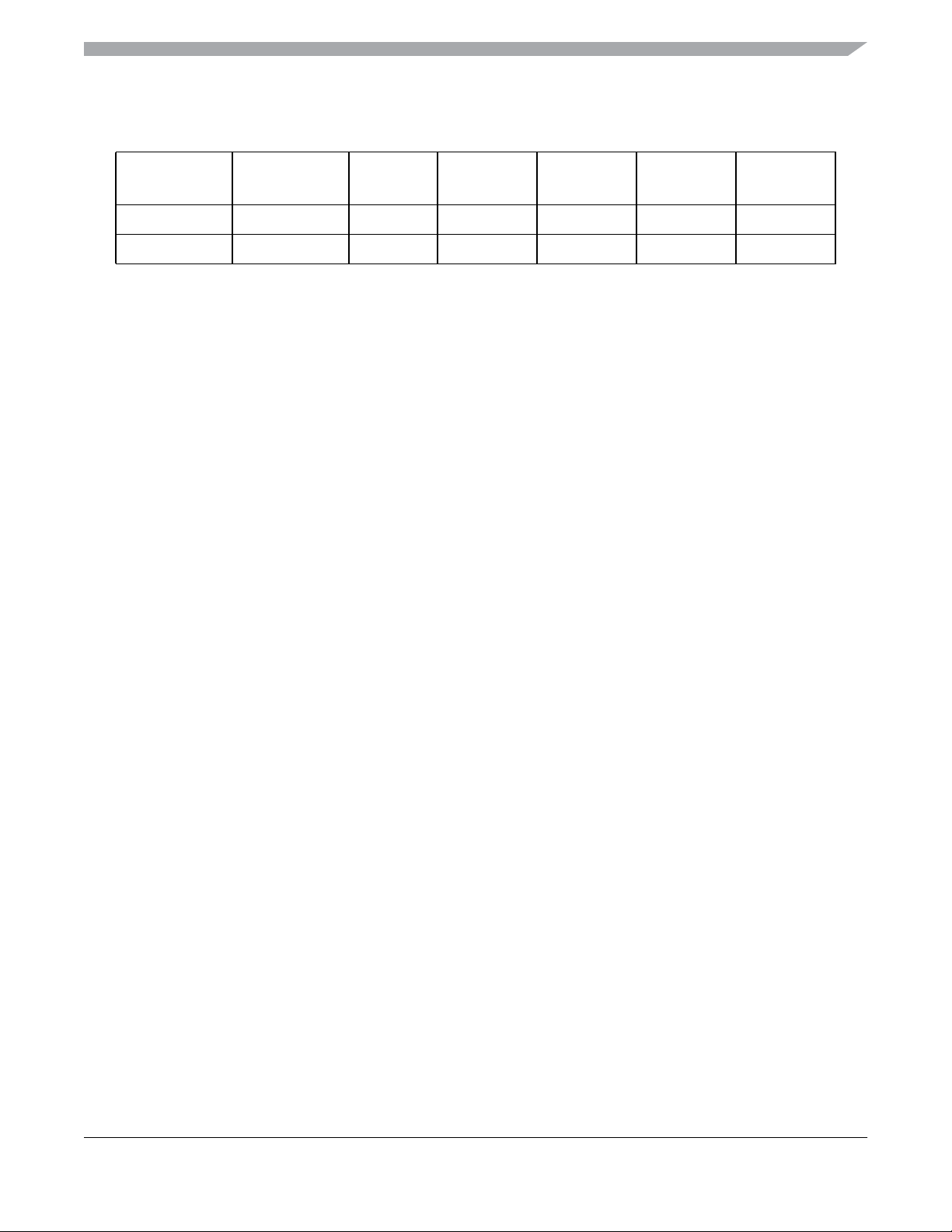

Table 1-5. Port Availability by Package Option

Port 112 LQFP 100 LQFP

Port AD/ADC Channels 12/12 8/8

Port A 8 8

Port B 8 6

Port H 8 8

Port P 8 8

Port R 8 6

Port S 8 8

Port T 8 8

Port U 8 8

Port V 8 8

Port M 4 0

Sum of Ports 88 76

I/O Power Pairs VDDM/VSSM 2/2 2/2

I/O Power Pairs VDDX/VSSX 2/2 2/2

I/O Power Pairs VDDA/VSSA

VREG Power Pairs VDDR/VSS3 1/1 1/1

VDD/VSS2 1/1 1/1

VDDF/VSSF 1/1 1/1

I/O Power Pair VDDPLL/VSSPLL 1/1 1/1

VLCD power 1 1

Sum of power pins 19 19

OSC pairs XTAL/EXTAL 1/1 1/1

other pins RESET/TEST/BKGD 1/1/1 1/1/1

1. VRH/VRL are sharing with VDDA/VSSA pins

(1)

1/1 1/1

MC9S12XHY-Family Reference Manual, Rev. 1.04

30 Freescale Semiconductor

Loading...

Loading...