查询MC56F8166VFV供应商

56F8366/56F8166

Data Sheet

Preliminary Technical Data

56F8300

16-bit Digital Signal Controllers

MC56F8366

Rev. 2.0

07/2005

freescale.com

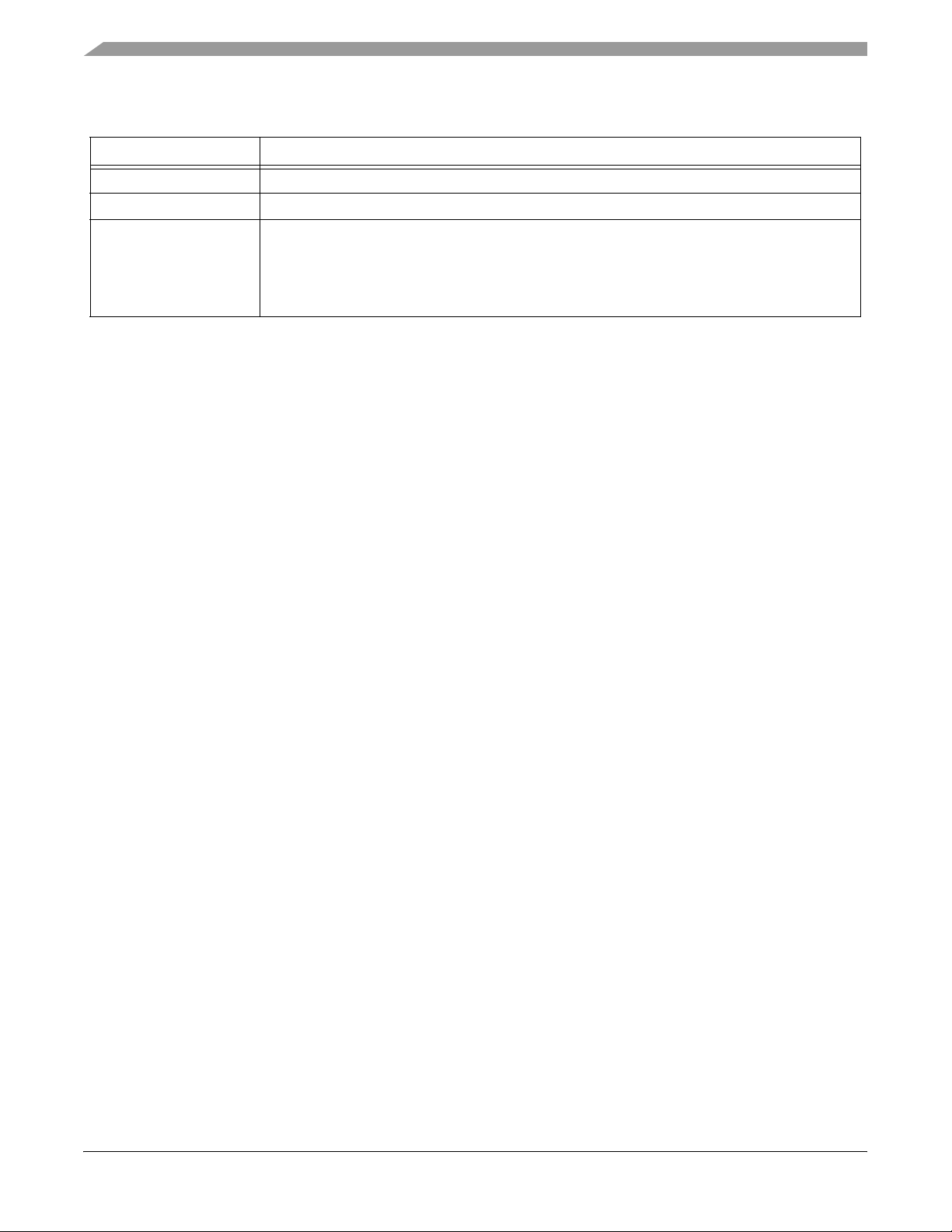

Document Revision History

Version History Description of Change

Rev 0

Rev 1.0

Rev. 2.0

Pre-release, Alpha customers only

Initial Public Release

Added output voltage maximum value and note to clarify in Table 10-1; also removed overall

life expectancy note, since life expectancy is dependent on customer usage and must be

determined by reliability engineering. Clarified value and unit measure for Maximum allowed

in Table 10-3. Corrected note ab ou t av erag e v alu e for Flash Data Retentio n in Table 10-4.

P

D

Added new RoHS-compliant orderable part numbers in Table 13-1.

Please see http://www.freescale.com for the most current Data Sheet revision.

56F8366 Technical Data, Rev. 2.0

2 Freescale Semiconductor

Preliminary

56F8366/56F8166 Ge neral Description

Note: Features in italics are NOT available in the 56F8166 device.

• Up to 60 MIPS at 60MHz core frequency

• DSP and MCU functionality in a unified,

C-efficient architecture

• Access up to 1MB of off -chip program and data memor y

• Chip Select Logic for glueless interface to ROM and

SRAM

• 512KB of Program Flash

• 4KB of Program RAM

• 32KB of Data Flash

• 32KB of Data RAM

• 32KB of Boot Flash

• Up to two 6-channel PWM modules

• Four 4-channel, 12-bit ADCs

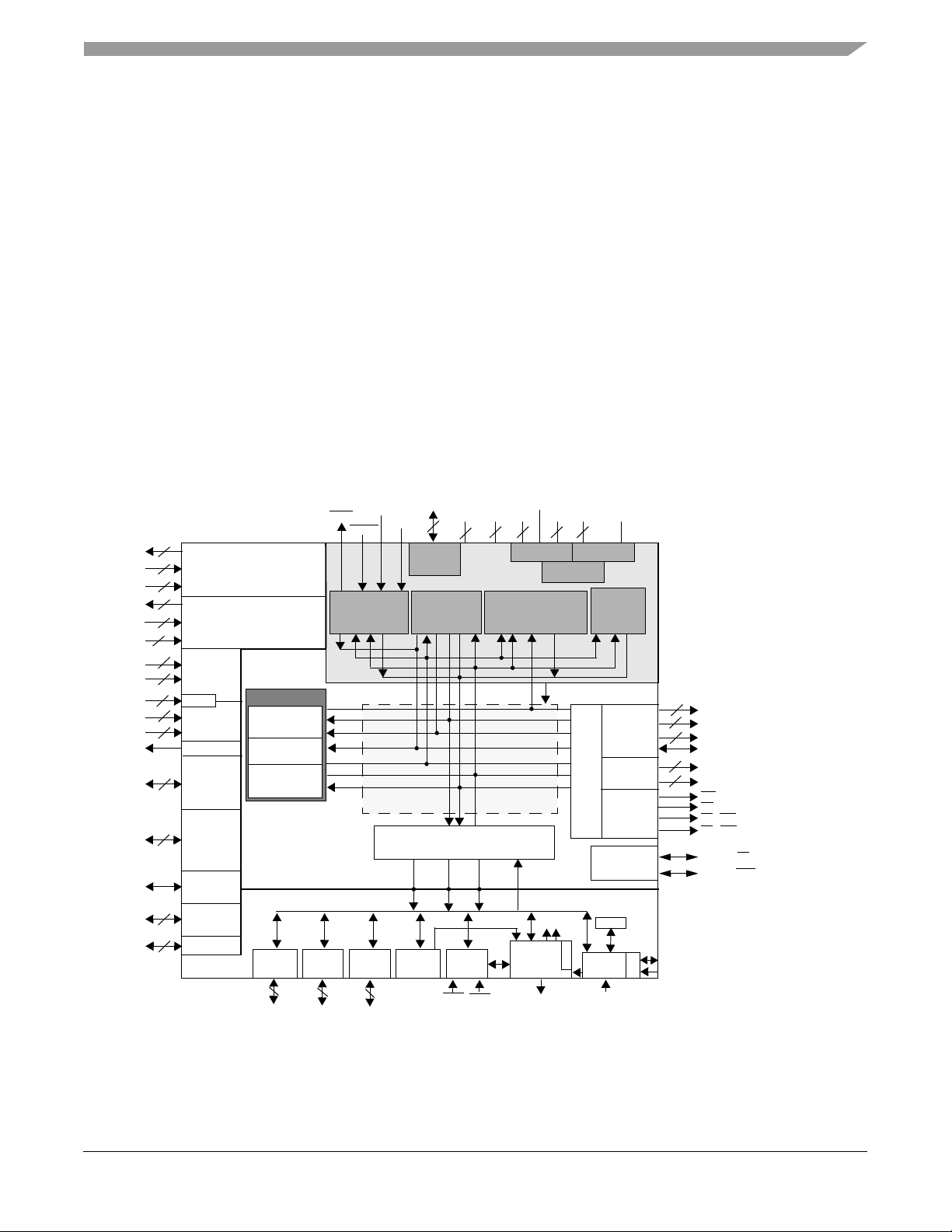

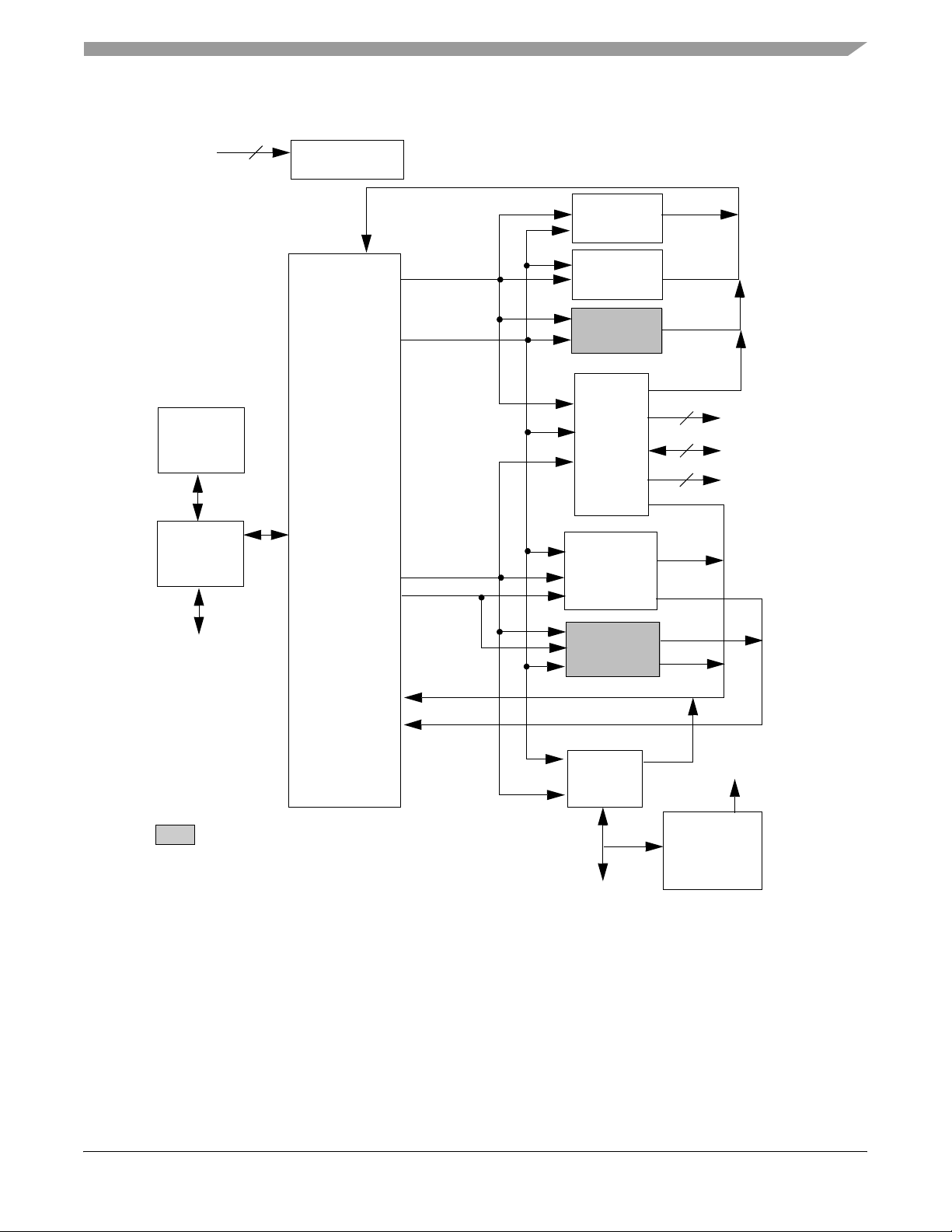

EMI_MODE

6

3

3

6

3

4

4

4

5

4

4

4

4

2

2

PWM Outputs

Current Sense Inpu ts

or GPIOC

Fault Inputs

PWM Outputs

Current Sense Inp uts

or GPIOD

Fault Inputs

AD0

ADCA

AD1

VREF

AD0

AD1

Temp_Sense

Quadrature

Decoder 0 or

Quad

Time r A or

GPIOC

Quadrature

Decoder 1 or

Quad

Timer B or

SPI1 or

GPIOC

Quad

Timer C or

GPIOE

Quad

Timer D or

GPIOE

FlexCAN

Program Memory

ADCB

Decoding

Peripherals

PWMA

PWMB

Memory

256K x 16 Flash

2K x 16 RAM

Boot ROM

16K x 16 Flash

Data Memory

16K x 16 Flash

16K x 16 RAM

SPI0 or

GPIOE

4

RSTO

Program Controller

Hardware Looping Unit

Device Selects

SCI1 or

GPIOD

2

RESET

and

XDB2

XAB1

XAB2

PAB

PDB

CDBR

CDBW

Peripheral

SCI0 or

GPIOE

EXTBOOT

PAB

PDB

CDBR

CDBW

5

JTAG/

EOnCE

Port

Address

Generation Unit

IPBus Bridge (IPBB)

RW

Control

COP/

Watchdog

2

Controller

IRQA

• Temperature Sensor

• Up to two Quadrature Decoders

• Optional On-Chip Regulator

• Up to two FlexCAN modules

• Two Serial Communication Interfaces (SCIs)

• Up to two Serial Peripheral Interfaces (SPIs)

• Up to four General Purpose Quad Timers

• Computer Operating Properly (COP) / Watchdog

• JTAG/Enhanced On-Chip Emulation (OnCE™) for

unobtrusive, real-time debugging

• Up to 62 GPIO lines

• 144-pin LQFP Package

OCR_DIS

V

V

PP

2

56800E Core

IPAB IPWDB IPRDB

Interrupt

IRQB

VDDVSSV

CAP

47 52

Digital Reg

16-Bit

Data ALU

16 x 16 + 36 -> 36-Bit MAC

Three 16-bit Input Registers

Four 36-bit Accumulators

System Bus

Control

System

Integration

Module

CLKO

DDA

Analog Reg

Low Voltage

Supervisor

R/W Control

Clock

resets

P

O

R

Manipulation

Address Bus

External Data

Bus Switch

External Bus

Interface Unit

Bus Control

EMI CS or

FlexCAN2

PLL

Clock

Generator

CLKMODE

V

SSA

Bit

Unit

External

Switch

GPIO or

6

A0-5 or GPIOA8-13

2

A6-7 or GPIOE2-3

8

A8-15 or GPIOA0-7

GPIOB0 or A16

7

D0-6 or GPIOF9-15

9

D7-15 or GPIOF0-8

WR

RD

PS / CS0 (GPIOD8)

DS / CS1 (GPIOD9)

GPIOD0 (CS

GPIOD1 (CS3 o r CAN2 _RX)

O

XTAL

S

EXTAL

C

2 or CAN2_TX)

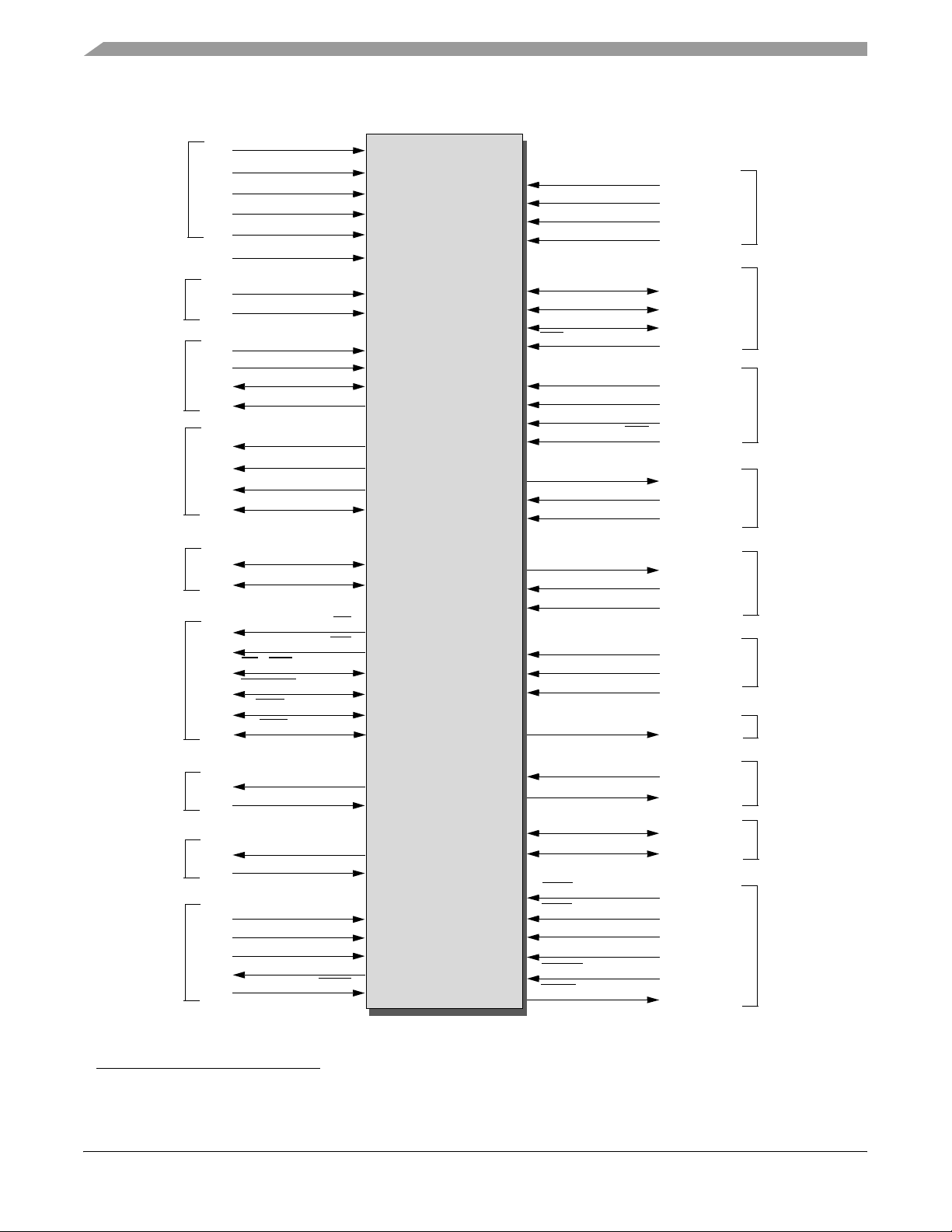

56F8366/56F8166 Block Diagram - 144 LQFP

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 3

Preliminary

Table of Contents

Part 1: Overview . . . . . . . . . . . . . . . . . . . . . . .5

1.1. 56F8366/56F8166 Features . . . . . . . . . . . . . 5

1.2. Device Description . . . . . . . . . . . . . . . . . . . . 7

1.3. Award-Winning Development Environment . 9

1.4. Architecture Block Diagram . . . . . . . . . . . . 10

1.5. Product Documentation . . . . . . . . . . . . . . . 14

1.6. Data Sheet Conventions . . . . . . . . . . . . . . 14

Part 2: Signal/Connection Descriptions . . .15

2.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.2. Signal Pins . . . . . . . . . . . . . . . . . . . . . . . . . 18

Part 3: On-Chip Clock Synthesis (OCCS) . .38

3.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.2. External Clock Operation . . . . . . . . . . . . . . 38

3.3. Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Part 4: Memory Map . . . . . . . . . . . . . . . . . . .40

4.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.2. Program Map . . . . . . . . . . . . . . . . . . . . . . . 41

4.3. Interrupt Vector Table . . . . . . . . . . . . . . . . . 44

4.4. Data Map . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.5. Flash Memory Map . . . . . . . . . . . . . . . . . . . 48

4.6. EOnCE Memory Map . . . . . . . . . . . . . . . . . 49

4.7. Peripheral Memory Mapped Registers . . . . 50

4.8. Factory Programmed Memory . . . . . . . . . . 83

Part 5: Interrupt Controller (ITCN) . . . . . . . .83

5.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.2. Features . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3. Functional Description . . . . . . . . . . . . . . . . 83

5.4. Block Diagram . . . . . . . . . . . . . . . . . . . . . . 85

5.5. Operating Modes . . . . . . . . . . . . . . . . . . . . 85

5.6. Register Descriptions . . . . . . . . . . . . . . . . . 86

5.7. Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Part 6: System Integration Module (SIM) .114

6.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . 114

6.2. Features . . . . . . . . . . . . . . . . . . . . . . . . . . 115

6.3. Operating Modes . . . . . . . . . . . . . . . . . . . 115

6.4. Operating Mode Register . . . . . . . . . . . . . 116

6.5. Register Descriptions . . . . . . . . . . . . . . . . 117

6.6. Clock Generation Overview . . . . . . . . . . . 132

6.7. Power-Down Modes Overview . . . . . . . . . 132

6.8. Stop and Wait Mode Disable Function . . . 133

6.9. Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Part 8: General Purpose Input/Output

(GPIO) . . . . . . . . . . . . . . . . . . . . . . 137

8.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . .137

8.2. Memory Maps . . . . . . . . . . . . . . . . . . . . . .138

8.3. Configuration . . . . . . . . . . . . . . . . . . . . . . .138

Part 9: Joint Test Action Group (JTAG) . 143

9.1. JTAG Information . . . . . . . . . . . . . . . . . . . .143

Part 10: Specifications . . . . . . . . . . . . . . . 144

10.1. General Characteristics . . . . . . . . . . . . . .144

10.2. DC Electrical Characteristics . . . . . . . . . .148

10.3. AC Electrical Characteristics . . . . . . . . . .152

10.4. Flash Memory Characteristics . . . . . . . . .152

10.5. External Clock Operation Timing . . . . . . .153

10.6. Phase Locked Loop Timing . . . . . . . . . . .153

10.7. Crystal Oscillator Timing . . . . . . . . . . . . .154

10.8. External Memory Interface Timing . . . . . .154

10.9. Reset, Stop, Wait, Mode Select, and

Interrupt Timing . . . . . . . . . . . . . .157

10.10. Serial Peripheral Interface (SPI) Timing .159

10.11. Quad Timer Timing . . . . . . . . . . . . . . . .162

10.12. Quadrature Decoder Timing . . . . . . . . . .163

10.13. Serial Communication Interface (SCI)

Timing . . . . . . . . . . . . . . . . . . . . .164

10.14. Controller Area Network (CAN) Timing .164

10.15. JTAG Timing . . . . . . . . . . . . . . . . . . . . . 1 65

10.16. Analog-to-Digital Converter (ADC)

Parameters . . . . . . . . . . . . . . . . .166

10.17. Equivalent Circuit for ADC Inputs . . . . . .169

10.18. Power Consumption . . . . . . . . . . . . . . . .169

Part 11: Packaging . . . . . . . . . . . . . . . . . . 171

11.1. 56F8366 Package and Pin-Out

Information . . . . . . . . . . . . . . . . . .171

11.2. 56F8166 Package and Pin-Out

Information . . . . . . . . . . . . . . . . . .174

Part 12: Design Considerations . . . . . . . . 178

12.1. Thermal Design Considerations . . . . . . . .178

12.2. Electrical Design Considerations . . . . . . .179

12.3. Power Distribution and I/O Ring

Implementation . . . . . . . . . . . . . .180

Part 13: Ordering Information . . . . . . . . . 181

Part 7: Security Features . . . . . . . . . . . . . .134

7.1. Operation with Security Enabled . . . . . . . 134

7.2. Flash Access Blocking Mechanisms . . . . 135

56F8366 Technical Data, Rev. 2.0

4 Freescale Semiconductor

Preliminary

Part 1 Overview

1.1 56F8366/56F8166 Features

1.1.1 Core

• Efficient 16-bit 56800E family controller engine with dual Harvard architecture

• Up to 60 Million Instructions Per Second (MIPS) at 60MHz core frequency

• Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

• Four 36-bit accumu l ators, including ext ension bits

• Arithmetic and logic mult i-bit shifter

• Parallel instruction set with unique DSP addressing modes

• Hardware DO and REP loops

• Three internal address buses

• Four internal data bus es

• Instruction set supports both DSP and controller functions

• Controller-style addressing modes and instructions for compact code

• Efficient C compiler and local variable support

• Software subroutine and interrupt stack with depth limited only by memory

• JTAG/EOnCE debug programming interface

56F8366/56F8166 Features

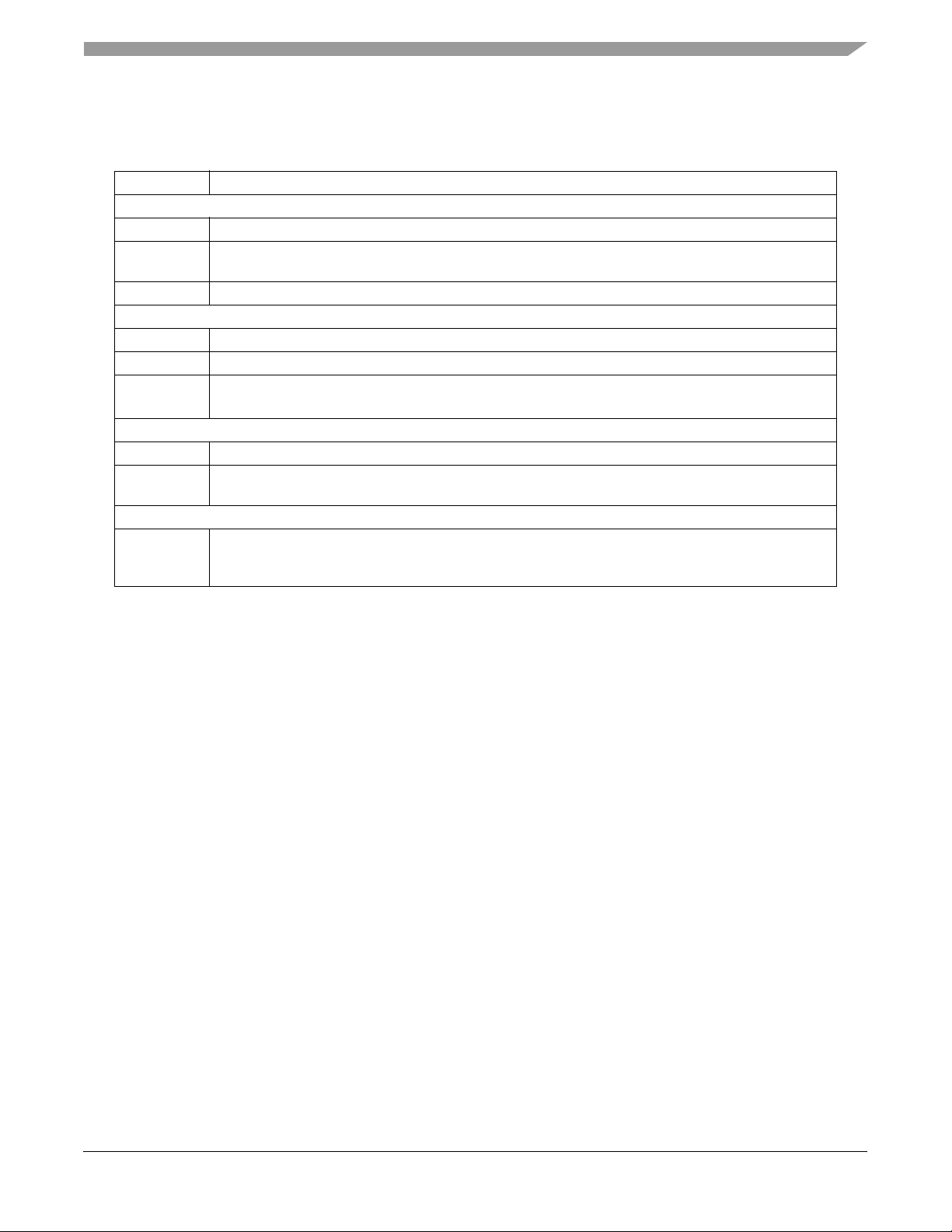

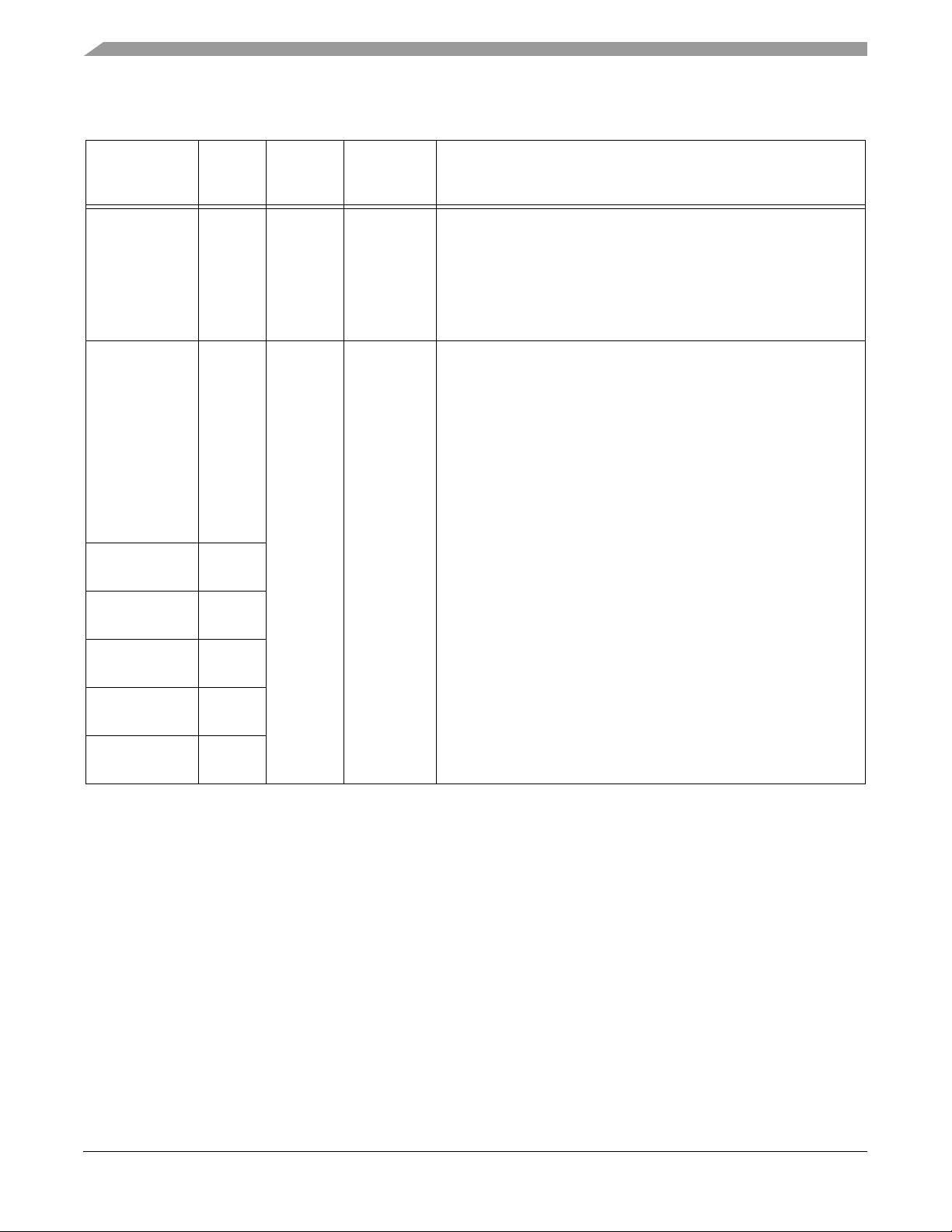

1.1.2 Differences Between Devices

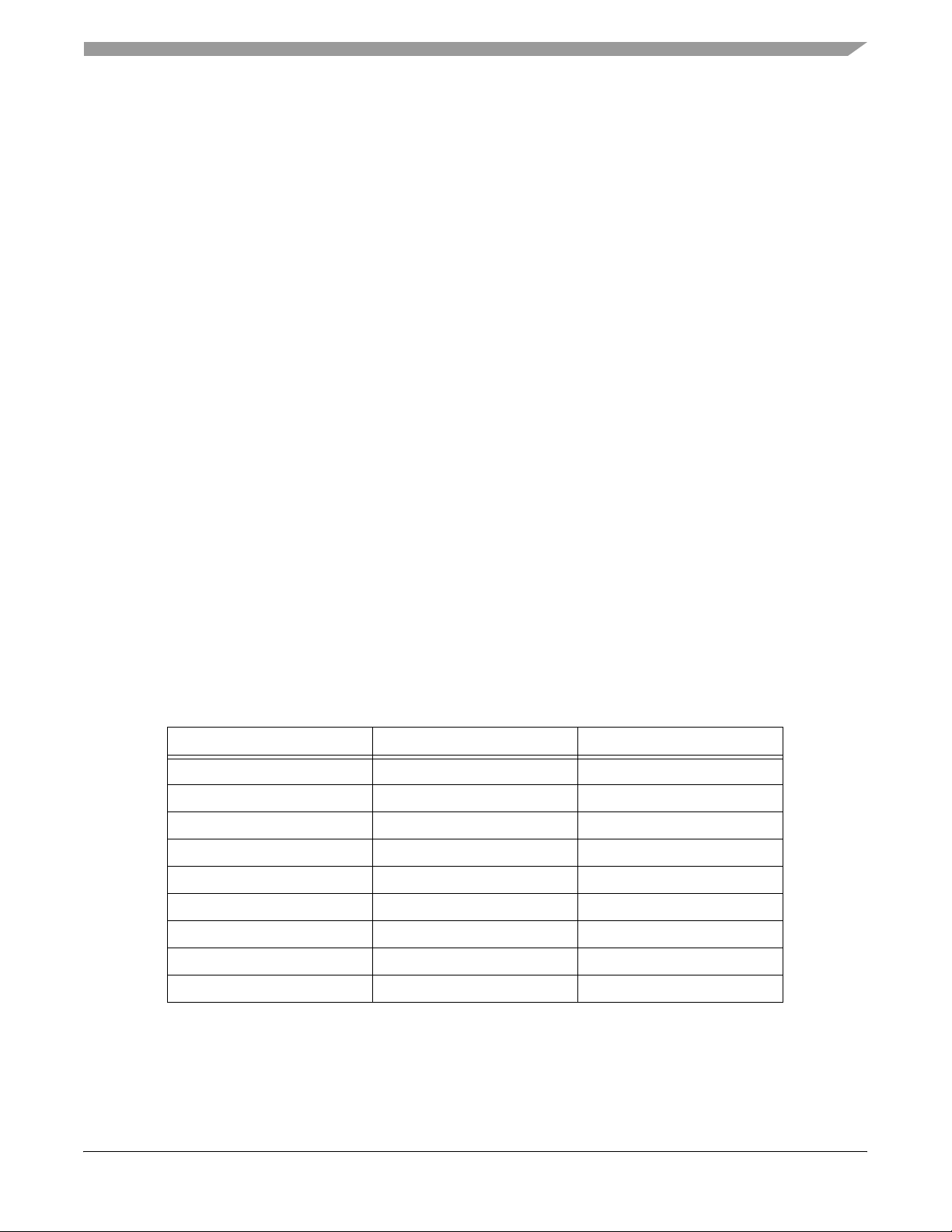

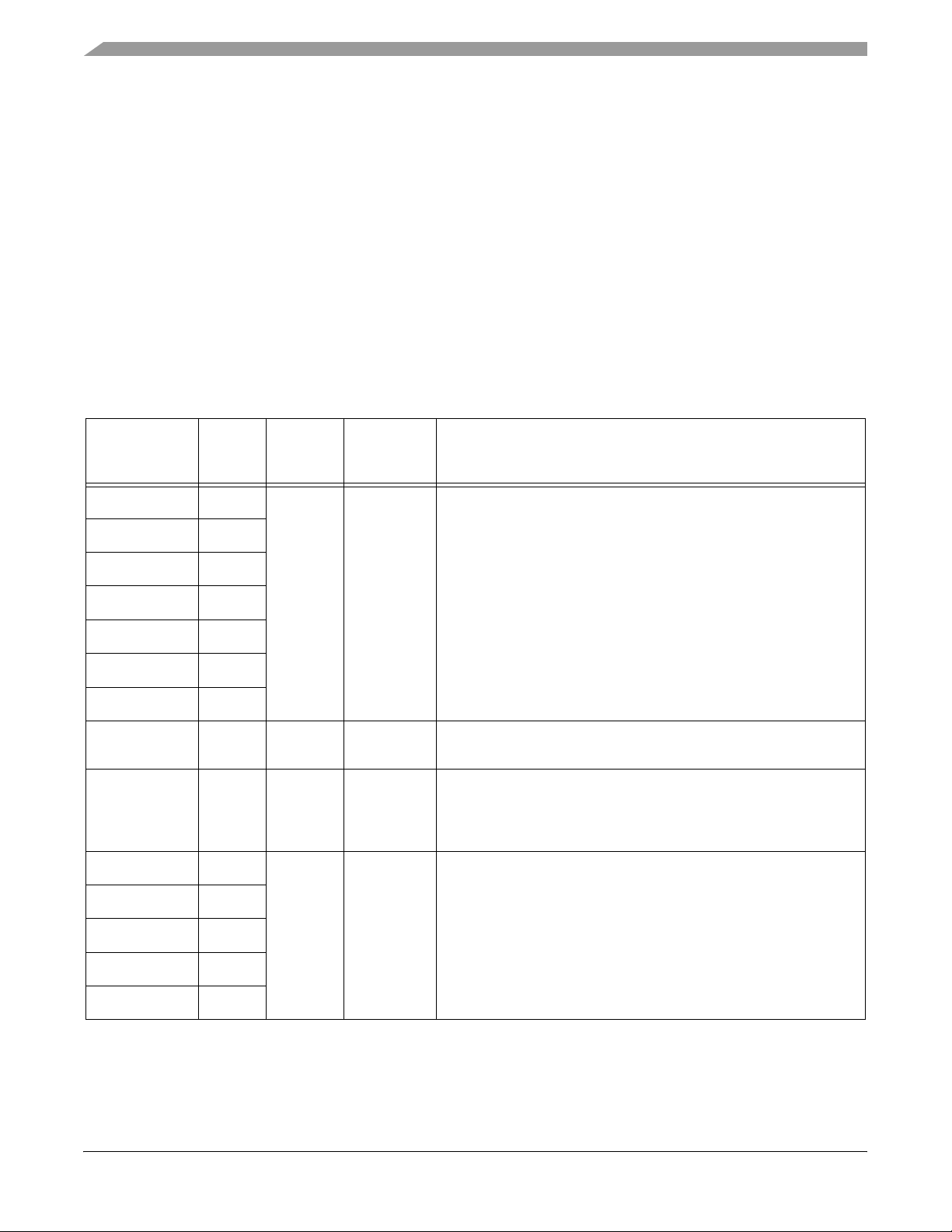

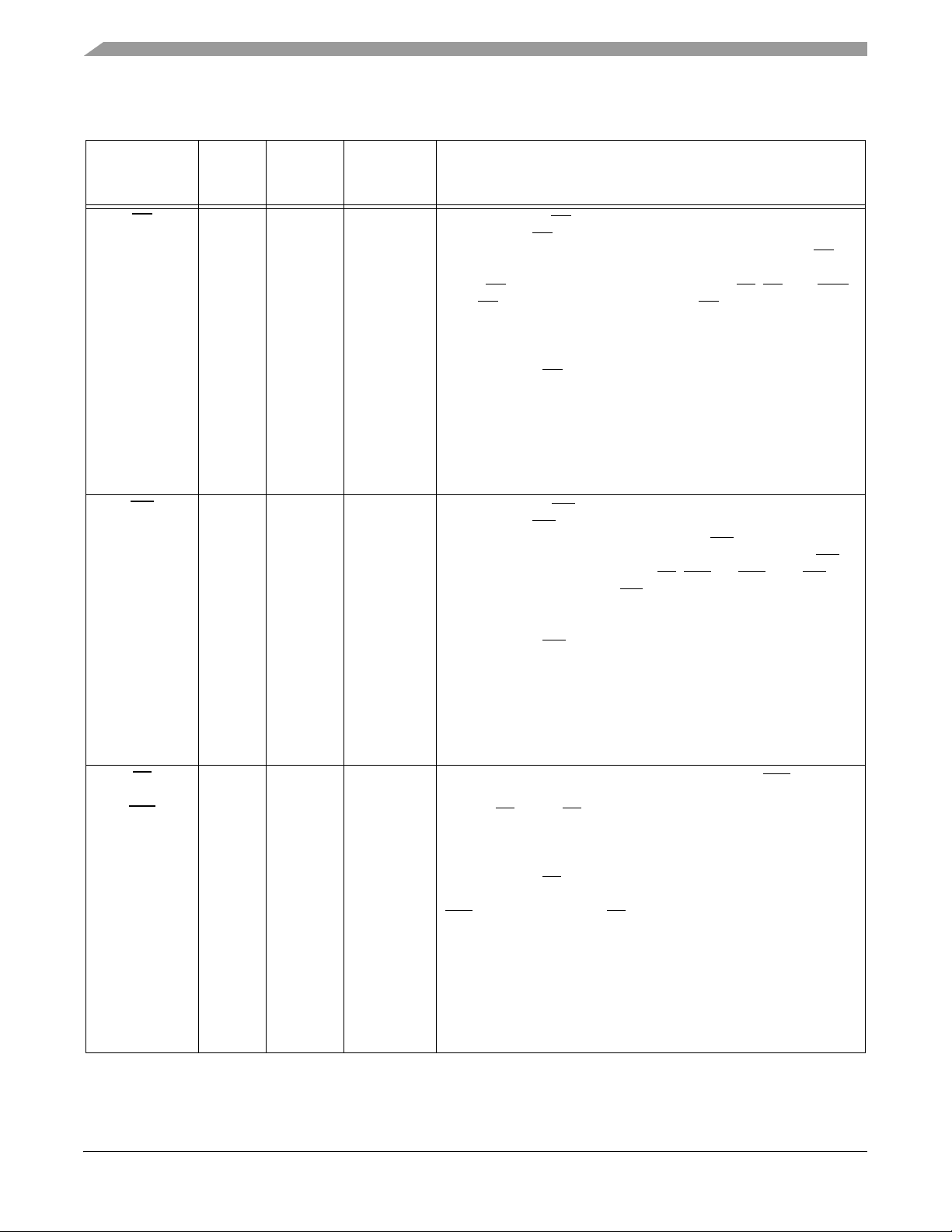

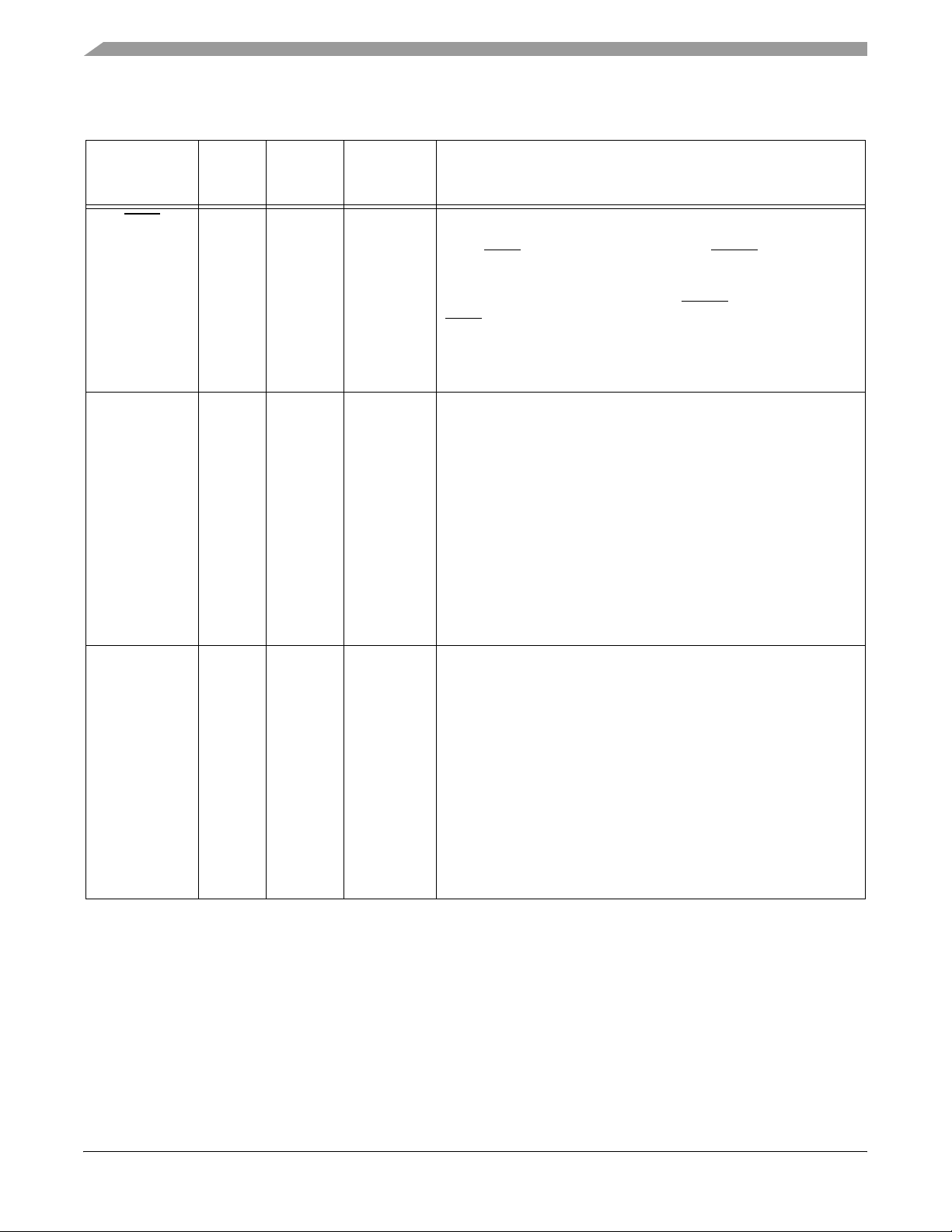

Table 1-1 outlines the key differences between the 56F8366 and 56F8166 devices.

Table 1-1 Device Differences

Feature 56F8366 56F8166

Guaranteed Speed 60MHz/60 MIPS 40MHz/40 MIPS

Program RAM 4KB Not Available

Data Flash 8KB Not Available

PWM 2 x 6 1 x 6

CAN 2 Not Available

Quad Timer 4 2

Quadrature Decoder 2 x 4 1 x 4

Temperature Sensor 1 Not Available

Dedicated GPIO — 5

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 5

Preliminary

1.1.3 Memory

Note: Features in italics are NOT available in the 56F8166 device.

• Harvard architecture permits as many as three simultaneous accesses to program and data memory

• Flash security protection feature

• On-chip memory, including a low-cost, high-volume Flash solution

— 512KB of Program Flash

— 4KB of Program RAM

— 32KB of Data Flash

—32KB of Data RAM

— 32KB of Boot Flash

• Off-chip memory expansion capabilities programmable for 0 - 30 wait states

— Access up to 1MB of program memory or 1MB of data memory

— Chip select logic for glueless interface to ROM and SRAM

• EEPROM emulation capability

1.1.4 Peripheral Circuits for 56F8366

Note: Features in italics are NOT available in the 56F8166 device.

• Pulse Width Modulator:

— In the 56F8366, two Pulse W idth Modulator modules, each with si x PWM outputs, three Cur rent Sense

inputs, and three Fault inputs; fault-tolerant design with dead time insertion; supports both

center-aligned and edge-aligned modes

— In the 56F8166, one Pulse Wid th Modulator module with six PWM outpu ts, three Current Sen se inputs,

and three Fault inp uts ; f ault-tolerant desi gn with dead time inserti on; supports both center -aligned and

edge-align ed modes

• Four 12-bit, Analog-to-Digital Converters (ADCs), which support four simultaneous conversions with

quad, 4-pin multiplexed inputs; ADC and PWM modules can be synchronized through Ti mer C, channels

2 and 3

• Quadrature Decoder:

— In the 56F8366, two four-input Quadrature Decoders or two additional Quad Ti mers

— In the 56F8166, one four-input Quadrature Decoder, which works in conjunction with Quad Timer A

• Temperature Sensor diode can be connect ed, on the boar d , to any of the ADC input s to monitor the on-chip

temperature

• Quad Timer:

— In the 56F8366, four dedicated general-purpose Quad Timers totaling three dedicated pins: Timer C

with one pin and Timer D with two pins

— In the 56F8166, two Quad Timers; Timer A and Timer C both work in conjunction with GPIO

• Optional On-Chip Regulator

• Up to two FlexCAN (CAN Version 2.0 B-compliant ) modules with 2-pin port for transmit and receive

56F8366 Technical Data, Rev. 2.0

6 Freescale Semiconductor

Preliminary

Device Description

• Two Serial Communication Interfaces (SCIs), each with two pins (or four additional GPIO lines)

• Up to two Serial Peripheral Interfaces (SPIs), both with configurable 4-pin port (or eight additional GPIO

lines)

— In the 56F8366, SPI1 can also be used as Quadrature Decoder 1 or Quad Timer B

— In the 56F8166, SPI1 can alternately be used only as GPIO

• Computer Operating Properly (COP) / Watchdog timer

• Two dedicated external interrupt pins

• 62 General Purpose I/O (GPIO) pins

• External reset input pin for hardware reset

• External reset output pin for system reset

• Integrated Low-Voltage Interrupt module

• JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time

debugging

• Software-programmable, Phase Lock Loop (PLL)-based frequency synthesizer for the core clock

1.1.5 Energy Information

• Fabricated in high-density CMOS with 5V-tolerant, TTL-compatible digital inputs

• On-board 3.3V down to 2.6V voltage regulator for powering internal logic and memories; can be disabled

• On-chip regulators for digital and analog circuitry to lower cost and reduce noise

• Wait and Stop modes available

• ADC smart power management

• Each peripheral can be individually disabled to save power

1.2 Device Description

The 56F8366 and 56F8166 are members of the 56800E core-based family of controllers. Each combines,

on a single chip, the processing power of a Digital Signal Processor (DSP) and the functionality of a

microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because

of its low cost, configuration flexibility, and compact program code, the 56F8366 and 56F8166 are

well-suited for many applications. The devices include many peripherals that are especially useful for

motion control, smart appliances, steppers, encoders, tachometers, limit switches, power supply and

control, automotive control (56F8366 only), engine management, noise suppression, remote utility

metering, industrial control for power, lighting, and automation applications.

The 56800E core is based on a Harvard-style architecture consisting of three execution units operating in

parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and

optimized instruction set allow straightforward generation of efficient, compact DSP and control code.

The instruction set is also highly efficient for C/C++ Compilers to enable rapid development of optimized

control applications.

The 56F8366 and 56F8166 support program execution from either internal or external memories. Two

data operands can be accessed from the on-chip data RAM per instruction cycle. These devices also

provides two external dedicated interrupt lines and up to 62 General Purpose Input/Output (GPIO) lines,

depending on peripheral configuration.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 7

Preliminary

1.2.1 56F8366 Features

The 56F8366 hybrid controller includes 512KB of Program Flash and 32KB of Data Flash (each

programmable through the JTAG port) with 4KB of Program RAM and 32KB of Data RAM. It also

supports program execution from external memory.

A total of 32KB of Boot Flash is incorporated for easy customer inclusion of field-programmable software

routines that can be used to program the main Program and Data Flash memory areas. Both Program and

Data Flash memories can be independently bulk erased or erased in pages. Program Flash page erase size

is 1KB. Boot and Data Flash page erase size is 512 bytes. The Boot Flash memory can also be either bulk

or page erased.

A key application-specific feature of the 56F8366 is the inclusion of two Pulse Width Modulator (PWM)

modules. These modules each incorporate three complementary, individually programmable PWM signal

output pairs (each module is also capable of supporting six independent PWM functions, for a total of 12

PWM outputs) to enhance motor control functionality. Complementary operation permits programmable

dead time insertion, distortion correction via current sensing by software, and separate top and bottom

output polarity control. The up-counter value is programmable to support a continuously variable PWM

frequency. Edge-aligned and center-aligned synchronous pulse width control (0% to 100% modulation) is

supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both

BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance

Motors); and stepper motors. The PWMs incorporate fault protection and cycle-by-cycle current limiting

with sufficient output drive capability to directly drive standard optoisolators. A “smoke-inhibit”,

write-once protection feature for key para meters is also included. A patented PWM waveform distortion

correction circuit is also provided. Each PWM is double-buffered and includes interrupt controls to permit

integral reload rates to be programmable from 1 to 16. The PWM modules provide reference outputs to

synchronize the Analog-to-Digital Converters through two channels of Quad Timer C.

The 56F8366 incorporates two Quadrature Decoders capable of capturing all four transitions on the

two-phase inputs, permitting generation of a number proportional to actual position. Speed computation

capabilities accommodate both fast- and slow-moving shafts. An integrated watchdog timer in the

Quadrature Decoder can be programmed with a time-out value to alert when no shaft motion is detected.

Each input is filtered to ensure only true transitions are recorded.

This controller also provides a full set of standard programmable peripherals that include two Serial

Communications Interfaces (SCIs), two Serial Peripheral Interfaces (SPIs), and four Quad Timers. Any of

these interfaces can be used as General-P urpose Input/Outputs (GPIOs) if that function is not required.

Two Flex Controller Area Network (FlexCAN) interfaces (CAN Version 2.0 B-compliant) and an internal

interrupt controller are included on the 56F8366.

1.2.2 56F8166 Features

The 56F8166 hybrid controller includes 512KB of Program Flash, programmable through the JTAG port,

with 32KB of Data RAM. It also supports program execution from external memory.

A total of 32KB of Boot Flash is incorporated for easy customer inclusion of field-programmable software

routines that can be used to program the main Program Flash memory area, which can be independently

56F8366 Technical Data, Rev. 2.0

8 Freescale Semiconductor

Preliminary

Award-Winning Development Environment

bulk erased or erased in pages. Program Flash page erase size is 1KB. Boot Flash page erase size is 512

bytes and the Boot Flash memory can also be either bulk or page erased.

A key application-specific feature of the 56F8166 is the inclusion of one Pulse Width Modulator (PWM)

module. This module incorporates three complementary, individually programmable PWM signal output

pairs and can also support six independent PWM functions to enhance motor control functionality.

Complementary operation permits programmable dead time insertion, distortion correction via current

sensing by software, and separate top and bottom output polarity control. The up-counter value is

programmable to support a continuously variable PWM frequency. Edge-aligned and center-aligned

synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of

controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless

DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWM

incorporates fault protection and cycle-by-cycle current limiting with sufficient output drive capability to

directly drive standard optoisolators. A “smoke-inhibit”, write-once protection feature for key parameters

is also included. A patented PWM waveform distortion correction circuit is also provided. Each PWM is

double-buffered and includes interrupt controls to permit integral reload rates to be programmable from 1

to 16. The PWM module provides reference outputs to synchronize the Analog-to-Digital Converters

through two channels of Quad Timer C.

The 56F8166 incorporates a Quadrature Decoder capable of capturing all four transitions on the two-phase

inputs, permitting generation of a number proportional to actual position. Speed computation capabilities

accommodate both fast- and slow-moving shafts. An integrated watchdog timer in the Quadrature Decoder

can be programmed with a time-out value to alert when no shaft motion is detected. Each input is filtered

to ensure only true transitions are recorded.

This controller also provides a full set of standard programmable peripherals that include two Serial

Communications Interfaces (SCIs); two Serial Peripheral Interfaces (SPIs); and two Quad Timers. Any of

these interfaces can be used as General Purpose Input/Outputs (GPIOs) if that function is not required. An

internal interrupt controller is also a part of the 56F8166.

1.3 Award-Winning Development Environment

Processor ExpertTM (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use

component-based software application creation with an expert knowledge system.

The CodeWarrior Integrated Development Environment is a sophisticated tool for code navigation,

compiling, and debugging. A complete set of evaluation modules (EVMs) and development system cards

will support concurrent engineering. Together, PE, CodeWarrior and EVMs create a complete, scalable

tools solution for easy, fast, and efficient development.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 9

Preliminary

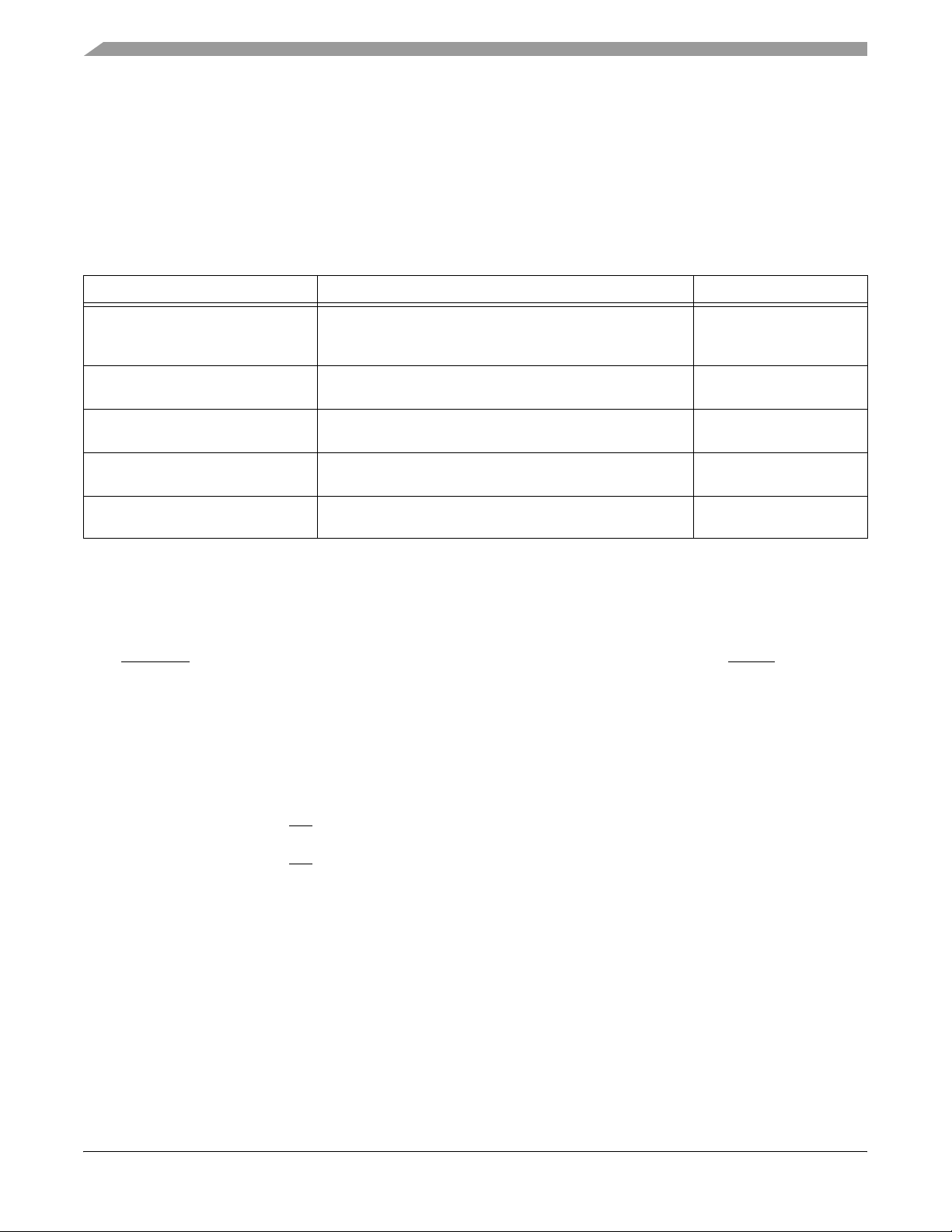

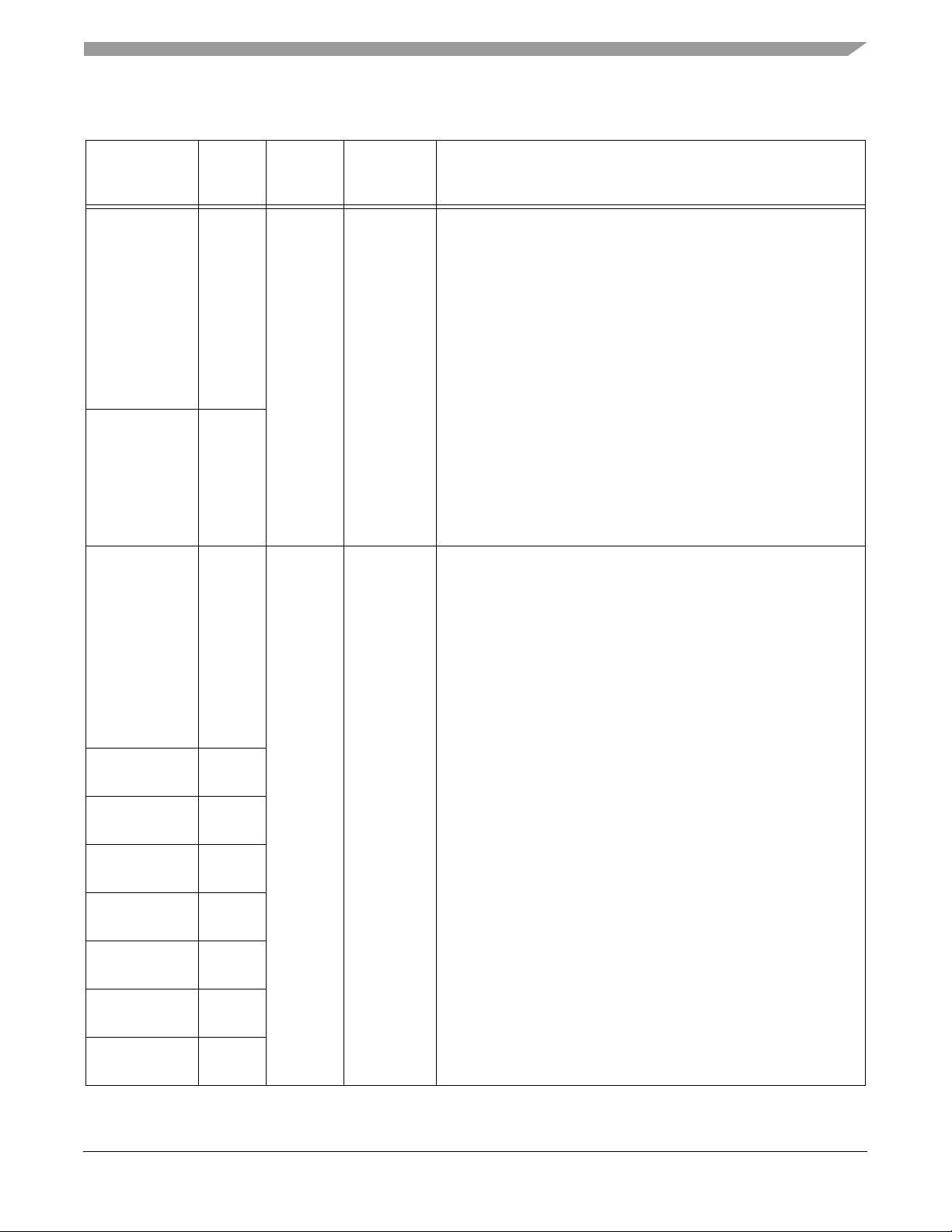

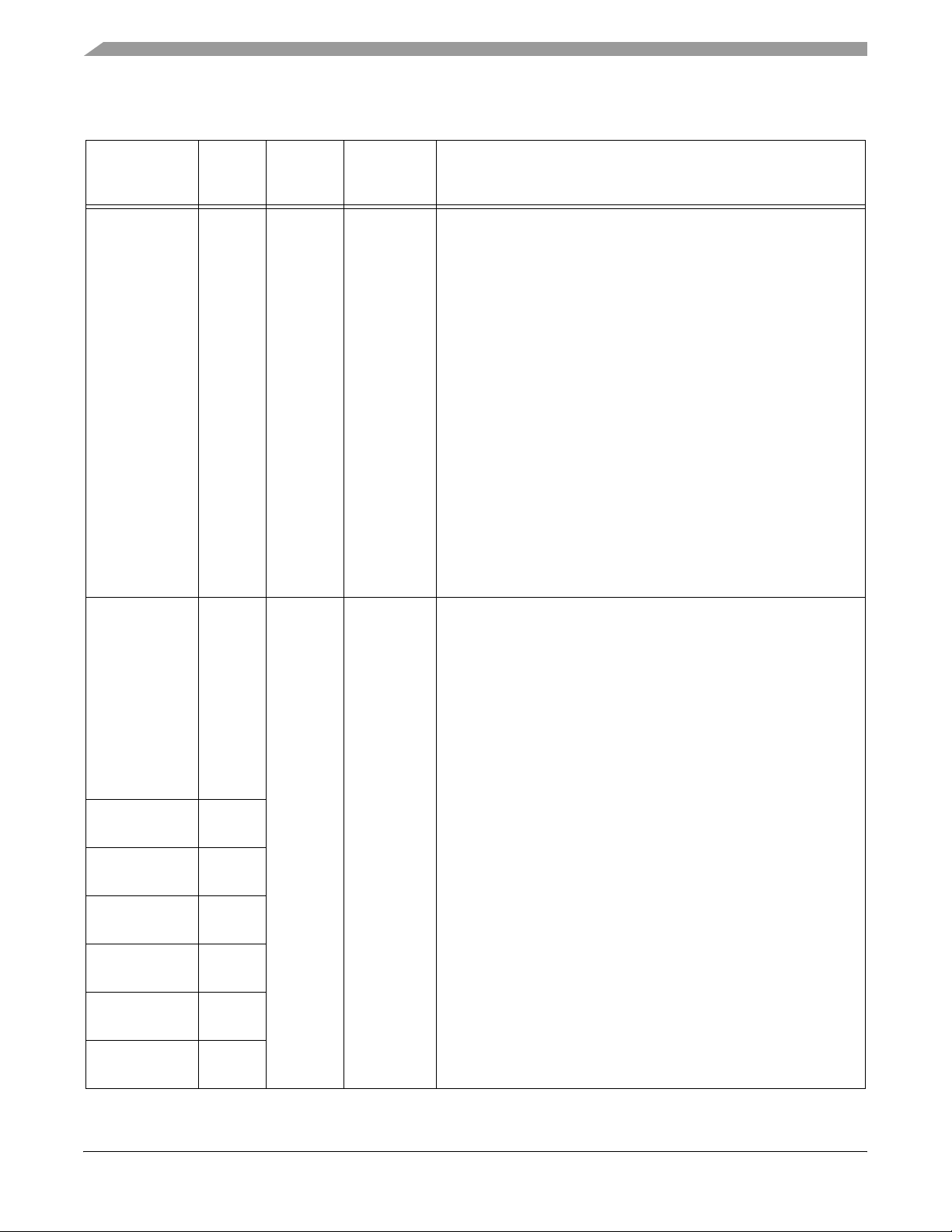

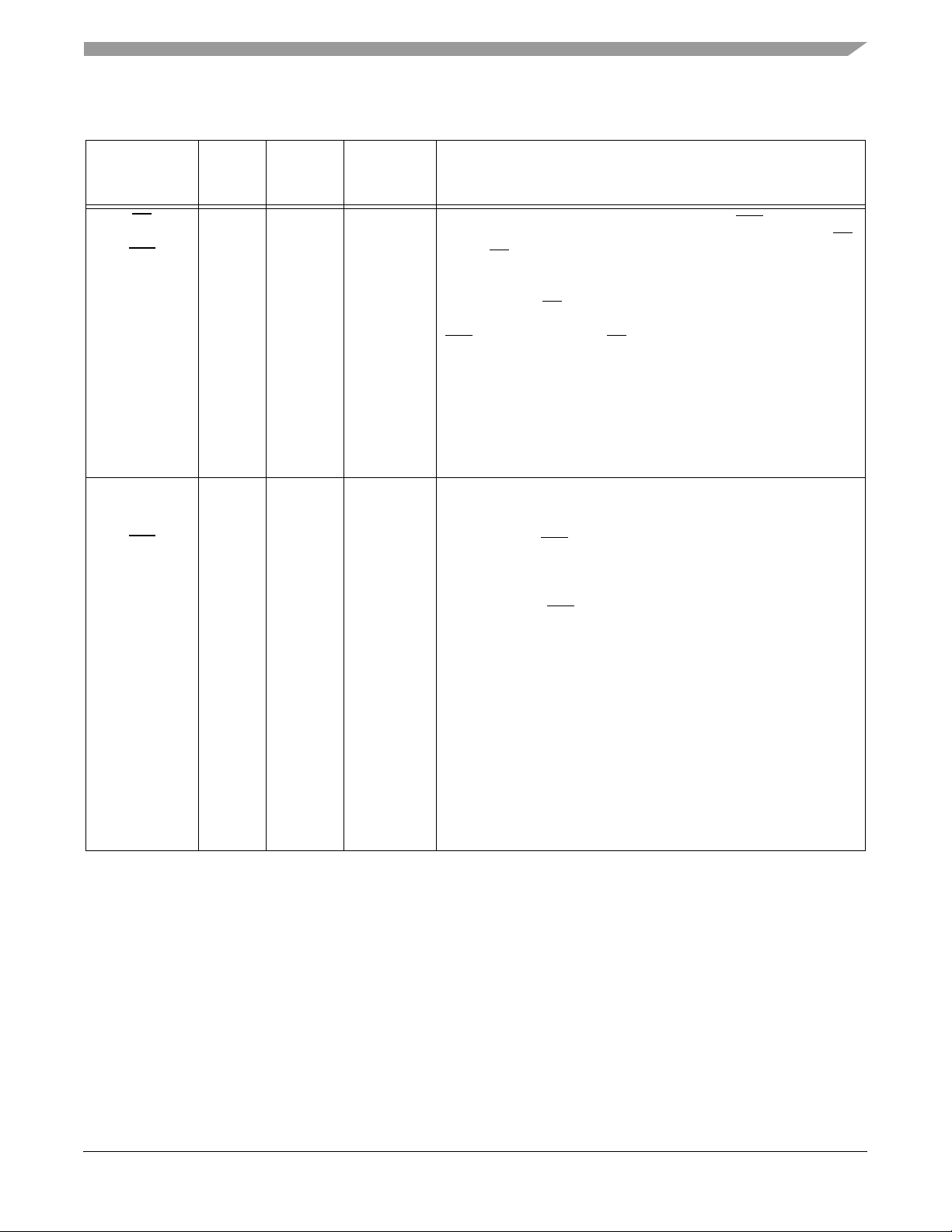

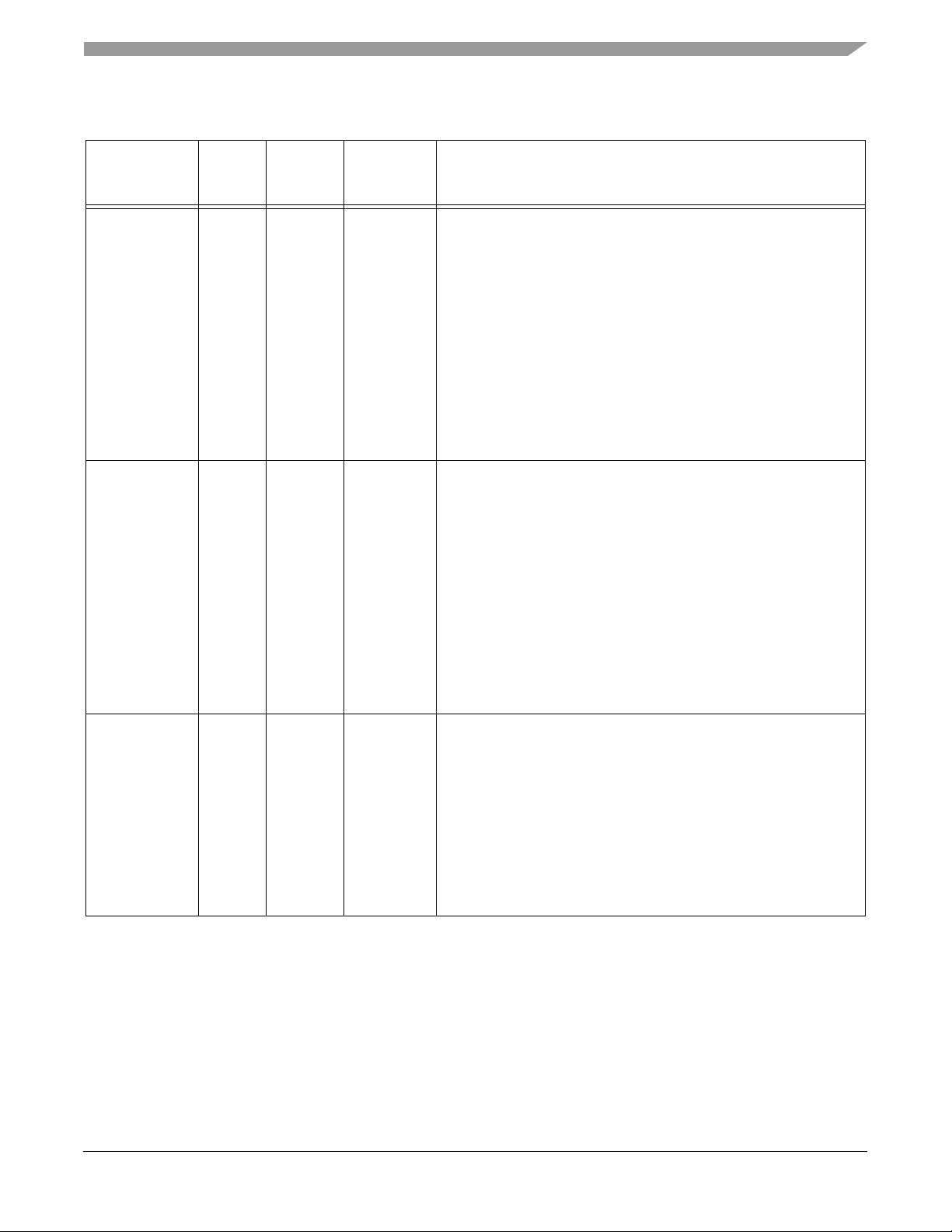

1.4 Architecture Block Diagram

Note: Features in italics are NOT available in the 56F8166 device and are shaded in the following figures.

The 56F8366/56F8166 architecture is shown in Figure 1-1 and Figure 1-2. Figure 1-1 illustrates how the

56800E system buses communicate with internal memories, the external memory interface and the IPBus

Bridge. Table 1-2 lists the internal buses in the 56800E architecture and provides a brief description of

their function. Figure 1-2 shows the peripherals and control blocks connected to the IPBus Bridge. The

figures do not show the on-board regulator and power and ground signals. They also do not show the

multiplexing between peripherals or the dedicated GPIOs. Please see Part 2, Signal/Connection

Descriptions, to see which signals are multiplexed with those of other peripherals.

Also shown in Figure 1-2 are connections between the PWM, Timer C and ADC blocks. These

connections allow the PWM and/or Timer C to control the timing of the start of ADC conversions. The

Timer C channel indicated can generate periodic start (SYNC) signals to the ADC to start its conversions.

In another operating mode, the PWM load interrupt (SYNC output) signal is routed internally to the Timer

C input channel as indicated. The timer can then be used to introduce a controllable delay before

generating its output signal. The timer output then triggers the ADC. To fully understand this interaction,

please see the 56F8300 Peripheral User Manual for clarification on the opera tion of all three of these

peripherals.

56F8366 Technical Data, Rev. 2.0

10 Freescale Semiconductor

Preliminary

Architecture Block Diagram

5

JTAG / EOnCE

Boot

Flash

CHIP

TAP

Controller

TAP

Linking

Module

External

JTAG

Port

pdb_m[15:0]

pab[20:0]

cdbw[31:0]

56800E

xab1[23:0]

xab2[23:0]

cdbr_m[31:0]

Program

Flash

Program

RAM

EMI

Data RAM

Data Flash

17

16

Address

Data

6

Control

xdb2_m[15:0]

To Flash

IPBus

Con trol Logic

Bridge

NOT available on the 56F8166 device.

Flash

Memory

Module

IPBus

Figure 1-1 System Bus Interfaces

Note: Flash memories are encapsulated within the Flash Memory (FM) Module. Flash control is

accomplished by the I/O to the FM over the peripheral bus, while reads and writes are completed

between the core and the Flash memories.

Note: The primary data RAM port is 32 bits wide. Other data ports are 16 bits.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 11

Preliminary

To/F

rom

IPB

us Bridge

CLKGEN

(OSC/PLL)

Interrupt

Controller

Low Voltage Interrupt

Timer A

POR & LVI

4

2

Quadrature Decoder 0

Timer D

Timer B

4

Quadrature Decoder 1

System POR

SIM

COP Reset

COP

FlexCAN

FlexCAN2

RESET

2

2

SPI 1

PWMA

12

GPIOA

GPIOB

PWMB

13

GPIOC

GPIOD

GPIOE

GPIOF

4

2

2

SPI0

SCI0

SCI1

IPBus

NOT available on the 56F8166 device.

Figure 1-2 Peripheral Subsystem

ch3i ch2i

Timer C

ch2och3o

1

8

ADCB

ADCA

TEMP_SENSE

Note: ADCA and ADCB use the same voltage

reference circuit with V

V

, and V

REFN

REFLO

REFH

pins.

8

1

, V

REFP, VREFMID

,

56F8366 Technical Data, Rev. 2.0

12 Freescale Semiconductor

Preliminary

Architecture Block Diagram

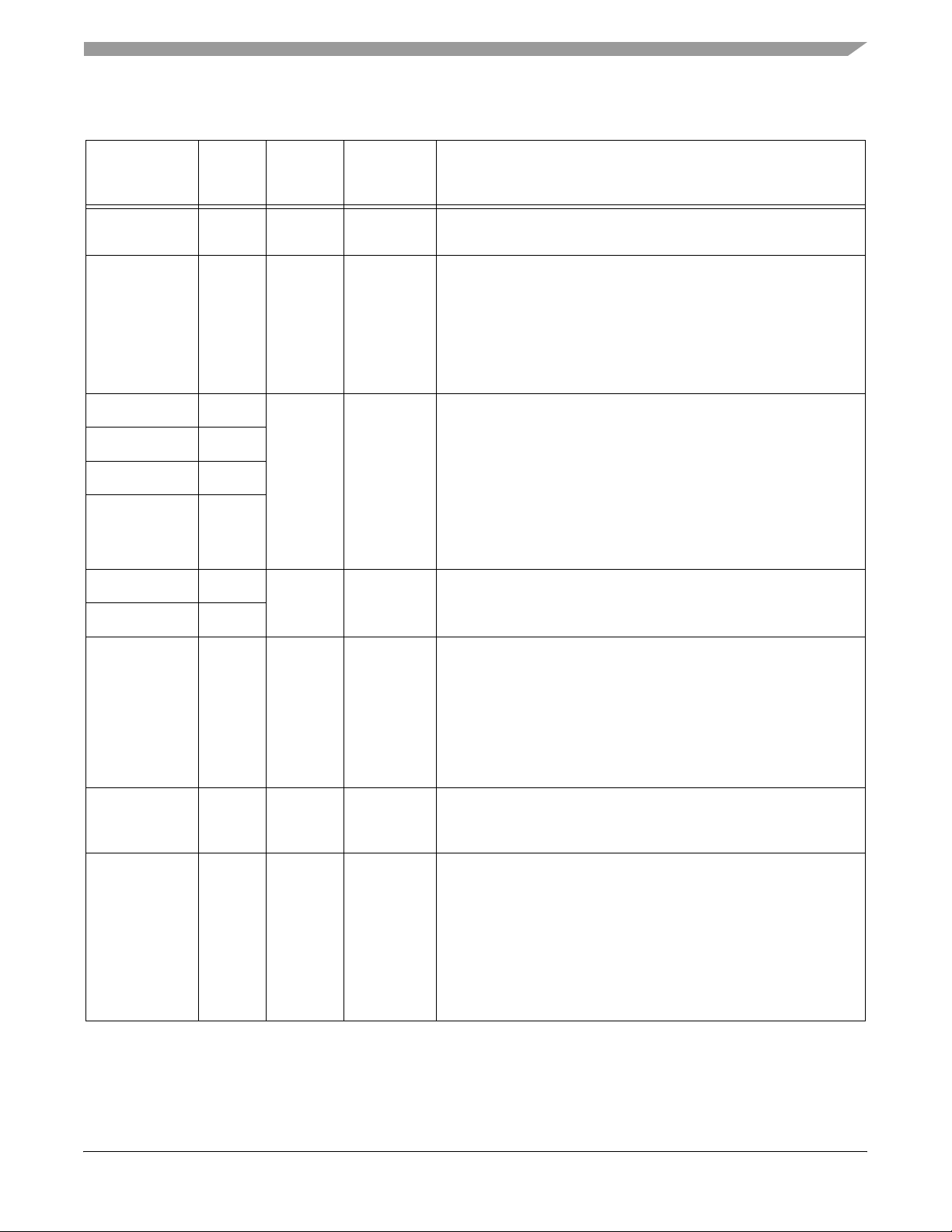

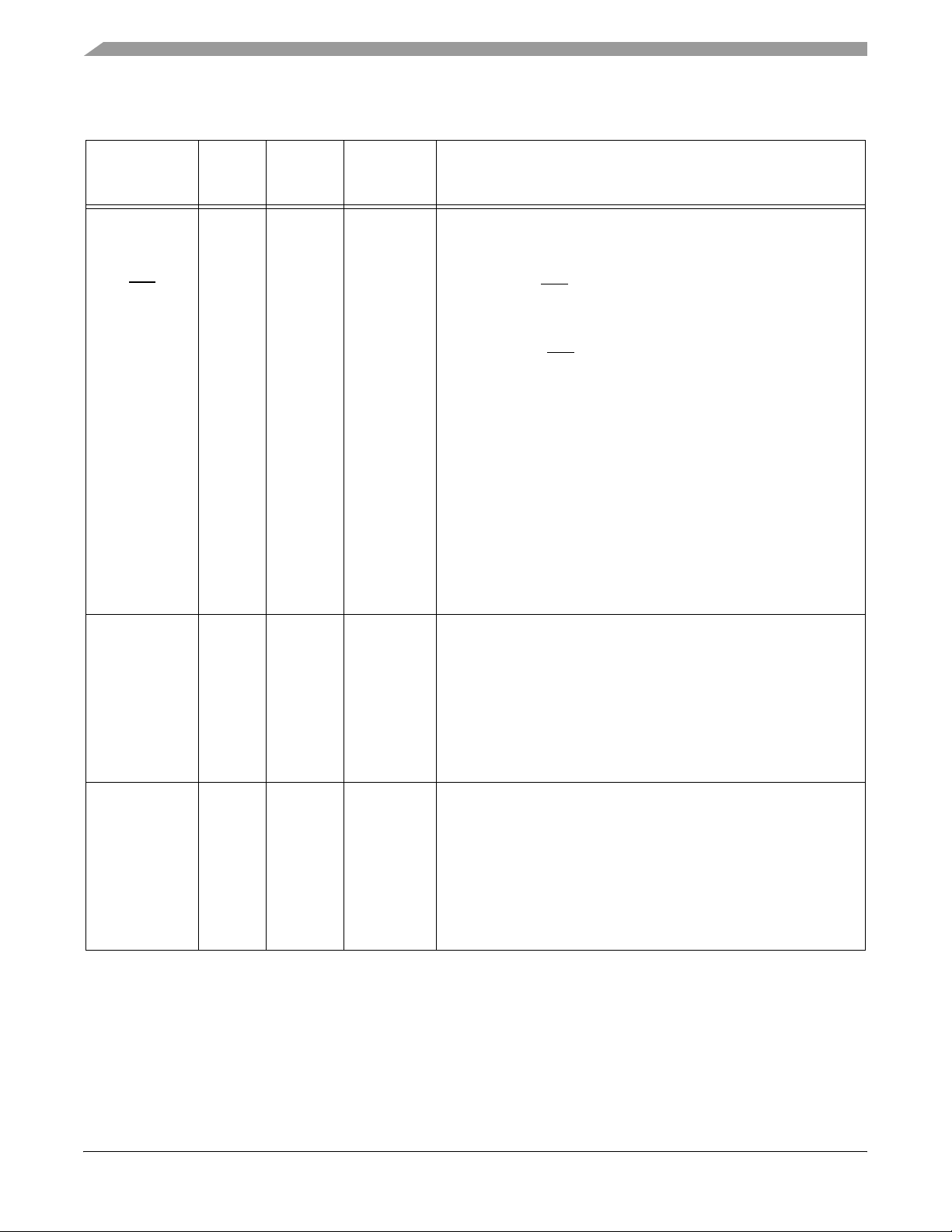

Table 1-2 Bus Signal Names

Name Function

Program Memory Interface

pdb_m[15:0] Program data bus for instruction word fetches or read operations.

cdbw[15:0] Primary core data bus used for program memory writes. (Only these 16 bits of the cdbw[31:0] bus

are used for writes to program memory.)

pab[20:0] Program memory address bus. Data is returned on pdb_m bus.

Primary Data Memory Interface Bus

cdbr_m[31:0] Primary core data bus for memory reads. Addressed via xab1 bus.

cdbw[31:0] Primary core data bus for memory writes. Addressed via xab1 bus.

xab1[23:0]

Primary data address bus. C apable of add ressing bytes

on cdbw and returned on cdbr_m. Also used to access memory-mapped I/O.

Secondary Data Memory Interface

xdb2_m[15:0] Secondary data bus used for secondary data address bus xab2 in the dual memory reads.

xab2[23:0] Secondary data address bus used for the second of two simultaneous accesses. Capable of

addressing only words. Data is returned on xdb2_m.

Peripheral Interface Bus

IPBus [15:0] Peripheral bus accesses all on-chip peripherals registers. This bus operates at the same clock rate

as the Primary Data Memory and therefore generates no delays when accessing the processor.

Write data is obtained from cdbw. Read data is provided to cdbr_m.

1. Byte accesses can only occur in the bottom half of the memory address space. The MSB of the address will be forced

to 0.

1

, words, and long data types. Data is written

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 13

Preliminary

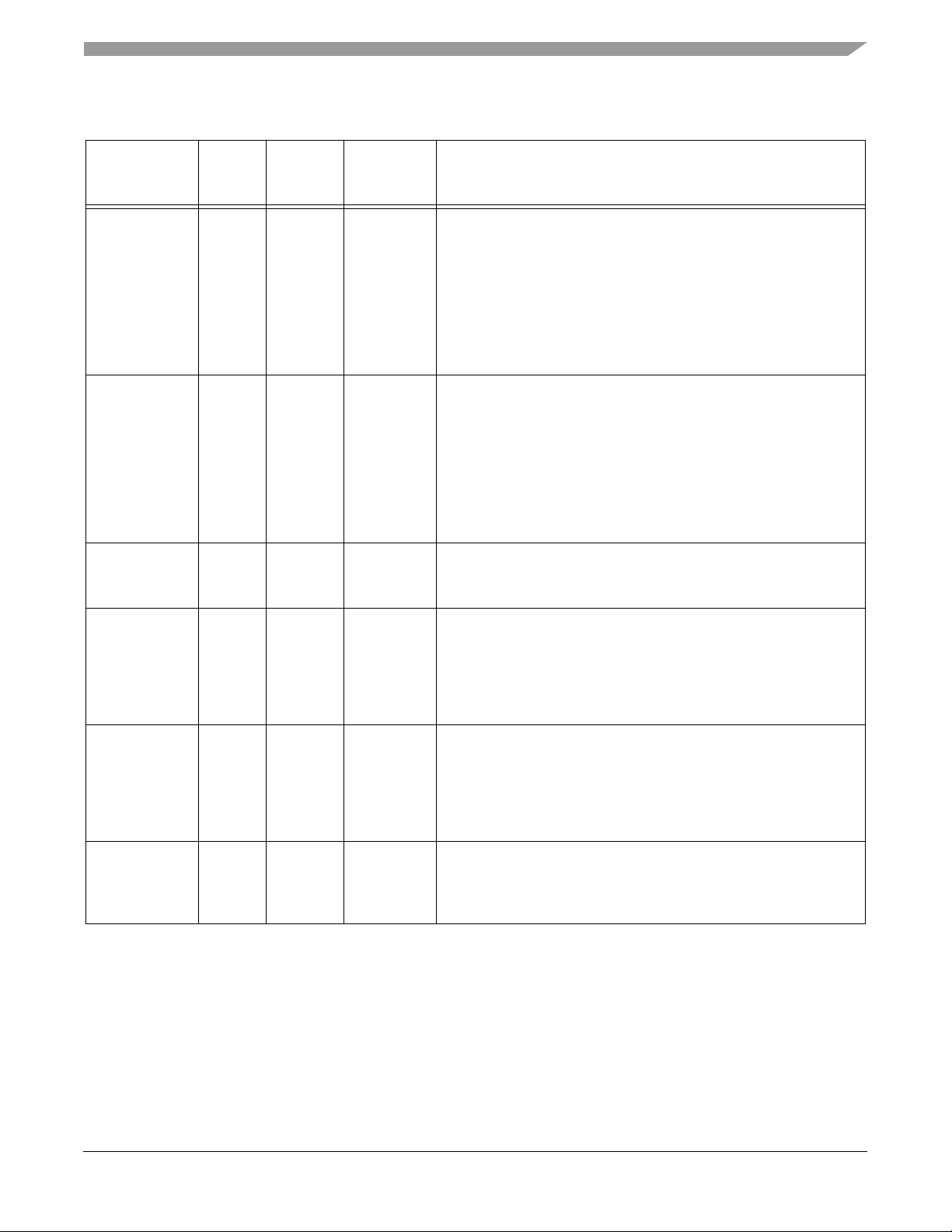

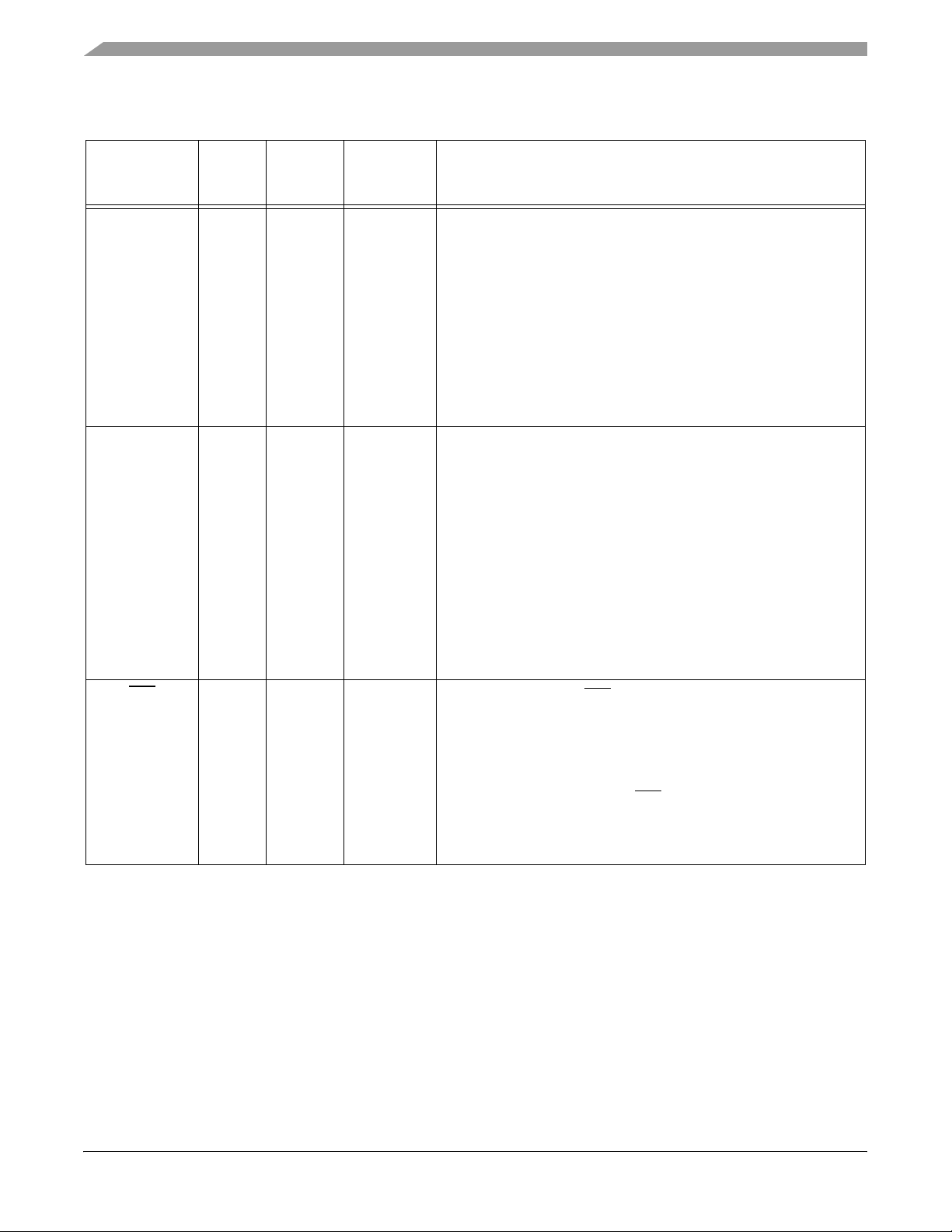

1.5 Product Documentation

The documents in Table 1-3 are required for a complete description and proper design with the

56F8366/56F8166 devices. Documentation is available from local Freescale distributors, Freescale

semiconductor sales offices, Freescale Literature Distribution Centers, or online at

http://www.freescale.com.

Table 1-3 Chip Documentation

Topic Description Order Number

DSP56800E

Reference Manual

56F8300 Peripheral User Manual Detailed description of peripherals of the 56F8300

56F8300 SCI/CAN Bootloader

User Manual

56F8366/56F8166

Technical Data Sheet

56F8366

Errata

Detailed description of the 56800E family architecture,

and 16-bit controller core processor and the instruction

set

devices

Detailed description of the SCI/CAN Bootloaders

56F8300 family of devices

Electrical and timing specifications, pin descriptions, and

package descriptions (this document)

Details any chip issues that might be present MC56F8366E

1.6 Data Sheet Conventions

This data sheet uses the following conventions:

OVERBAR

“asserted” A high true (active high) signal is high or a low true (active low) signal is low.

“deasserted” A high true (active high) signal is low or a low true (active low) signal is high.

This is used to indicate a signal that is active when pulled low. For example, the RESET pin is

active when low.

DSP56800ERM

MC56F8300UM

MC56F83xxBLUM

MC56F8366

MC56F8166E

Examples: Signal/Symbol Logic State Signal State

PIN True Asserted VIL/V

PIN False Deasserted VIH/V

PIN True Asserted VIH/V

PIN False Deasserted VIL/V

1. Val ues for VIL, VOL, VIH, and VOH ar e def i ne d by i ndividual product specificati on s.

56F8366 Technical Data, Rev. 2.0

14 Freescale Semiconductor

Voltage

1

OL

OH

OH

OL

Preliminary

Introduction

Part 2 Signal/Connection Descriptions

2.1 Introduction

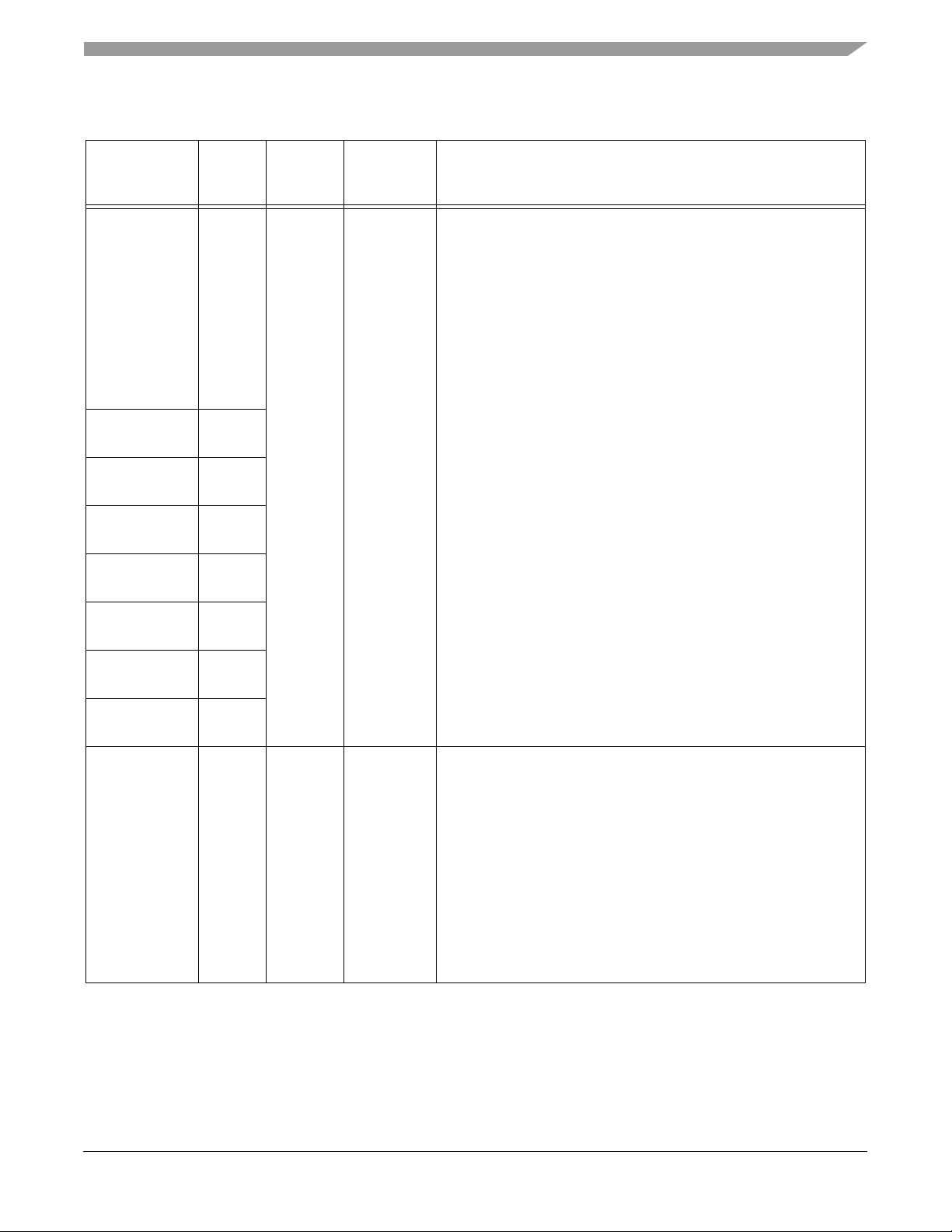

The input and output signals of the 56F8366 and 5 6F8166 are organized into functional groups, as detailed

in Table 2-1 and as illustrated in Figure 2-1. In Table 2-2, each table row describes the signal or signals

present on a pin.

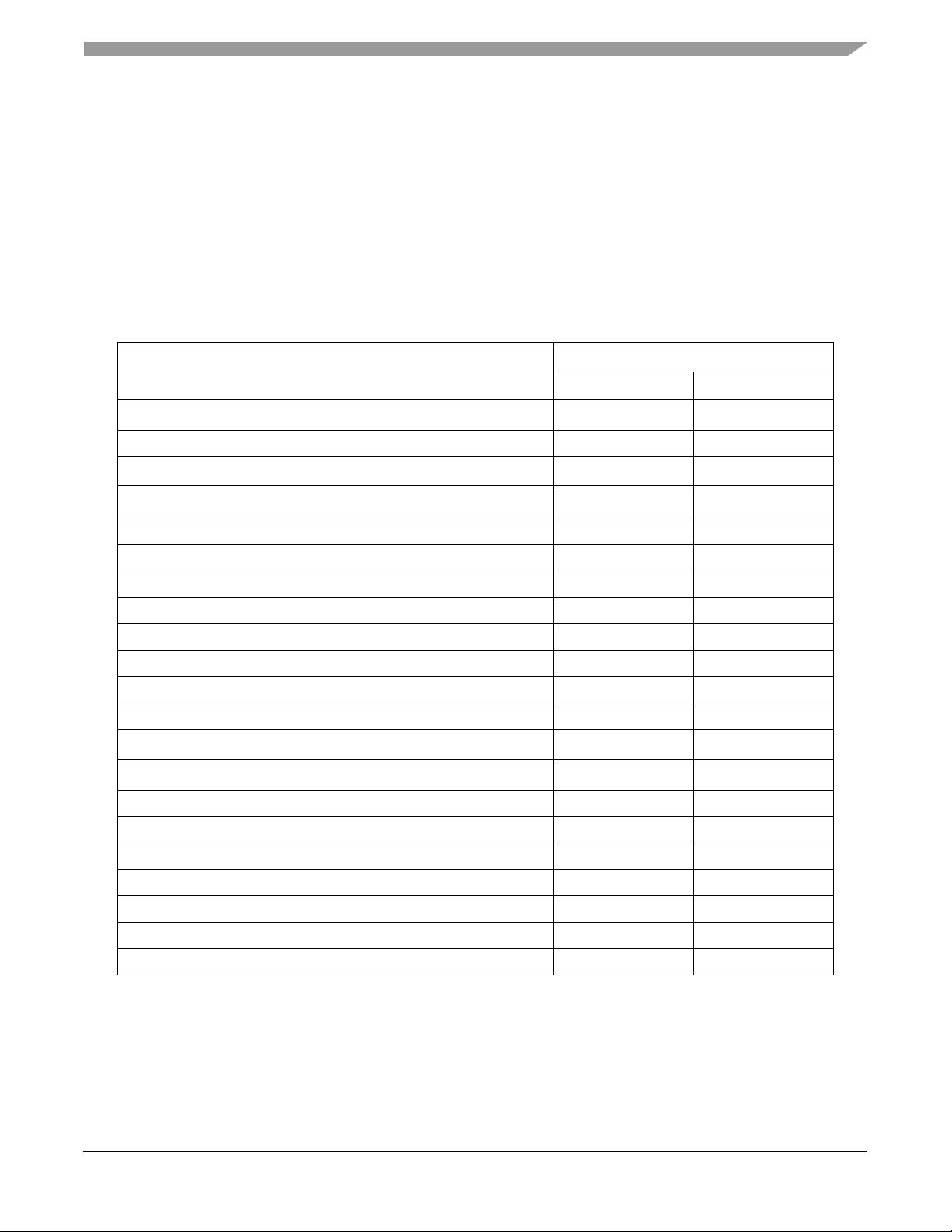

Table 2-1 Functional Group Pin Allocations

Functional Group

Power (V

Power Option Control 1 1

Ground (VSS or V

Supply Capacitors

PLL and Clock 4 4

Address Bus 17 17

Data Bus 16 16

Bus Control 6 6

Interrupt and Program Control 6 6

Pulse Width Modulator (PWM) Ports 25 13

Serial Peripheral Interface (SPI) Port 0 4 4

Serial Peripheral Interface (SPI) Port 1 — 4

Quadrature Decoder Port 0

Quadrature Decoder Port 1

Serial Communications Interface (SCI) Ports 4 4

DD

or V

)99

DDA

)66

SSA

1

& V

PP

2

3

Number of Pins in Package

56F8366 56F8166

66

44

4—

CAN Ports 2 —

Analog to Digital Converter (ADC) Ports 21 21

Quad Timer Module Ports 3 1

JTAG/Enhanced On-Chip Emulation (EOnCE) 5 5

Temperature Sense 1 —

Dedicated GPIO — 5

1. If the on-chip regulator is disabled, the V

2. Alternately, can function as Quad Timer pins or GPIO

3. Pins in this section can function as Quad Timer, SPI #1, or GPIO

Freescale Semiconduc tor 15

Preliminary

pins serve as 2.5V V

CAP

56F8366 Technical Data, Rev. 2.0

DD_CORE

power inputs

Power

Power

Power

Ground

Ground

Other

Supply

Ports

PLL

and

Clock

External

Address

Bus

or GPIO

V

DD_IO

V

DDA_ADC

V

DDA_OSC_PLL

V

SS

V

SSA_ADC

OCR_DIS

V

1 - V

CAP

CAP

1 & VPP2

V

PP

CLKMODE

EXTAL

XTAL

CLKO

A0 - A5 (GPIOA8 - 13)

A6 - A7 (GPIOE2 - 3)

A8 - A15 (GPIOA0 - 7)

GPIOB0 (A16)

7

1

1

5

1

PHASEA0 (TA0, GPIOC4)

1

PHASEB0 (TA1, GPIOC5)

1

INDEX0 (TA2, GPIOC6)

1

HOME0 (TA3, GPIOC7)

1

Quadrature

Decoder 0

or Quad

Timer A or

GPIO

1

4

56F8366

4

2

1

1

1

1

6

2

8

1

SCLK0 (GPIOE4)

1

MOSI0 (GPI O E5)

1

MISO0 (GPIOE6)

1

SS0

1

1

1

1

1

6

3

3

(GPIOE7)

PHASEA1(TB0, SCLK1, GPIOC0)

PHASEB1 (TB1, MOSI1, GPIOC1)

INDEX1 (TB2, MISO1, GPIOC2)

HOME1 (TB3, SS1, GPIOC3)

PWMA0 - 5

ISA0 - 2 (GPIOC8 - 10)

FAULTA0 - 2

SPI0 or

GPIO

Quadrature

Decoder 1 or

Quad Timer B

or SPI 1 or

GPIO

PWMA or

GPIO

External

Data Bus

or GPIO

External

Bus

Control or

GPIO

SCI 0 or

GPIO

SCI 1

or GPIO

JTAG/

EOnCE

Port

D0 - D6 (GPIOF9 - 15)

D7 - D15 (GPIOF0 - 8)

RD

WR

PS / CS0 (GPIOD8)

DS / CS1 (GPIOD9)

GPIOD0 (CS2, CAN2_TX)

GPIOD1 (CS3

, CAN2_RX

TXD0 (GPIOE0)

RXD0 (GPIOE1)

TXD1 (GPIOD6)

RXD1 (GPIOD7)

TCK

TMS

TDI

TDO

TRST

7

9

PWMB0 - 5

6

ISB0 - 2 (GPIOD10 - 12)

3

FAULTB0 - 3

4

PWMB or

GPIO

1

ANA0 - 7

1

1

1

1

1

1

1

1

8

V

5

8

1

1

1

1

2

REF

ANB0 - 7

TEMP_SENSE

CAN_RX

CAN_TX

TC0 (GPIOE8)

TD0 - 1 (GPIOE10 - 11)

ADCA

ADCB

Temperature

Sensor

FlexCAN

QUAD

TIMER C and

D or GPIO

1

IRQA

1

1

1

1

1

1

1

1

1

1

1

IRQB

EXTBOOT

EMI_MODE

RESET

RSTO

INTERRUPT/

PROGRAM

CONTROL

Figure 2-1 56F8366 Signals Identified by Functional Group1 (144-pin LQFP)

1. Alternate pin functionality is shown in parenthesis; pin direction/type shown is the default functionality.

56F8366 Technical Data, Rev. 2.0

16 Freescale Semiconductor

Preliminary

Power

Power

Power

Ground

Ground

Other

Supply

Ports

PLL

and

Clock

V

V

DDA_ADC

V

DDA_OSC_PLL

V

SSA_ADC

OCR_DIS

V

1 - V

CAP

V

1 & VPP2

PP

CLKMODE

EXTAL

DD_IO

V

SS

CAP

XTAL

CLKO

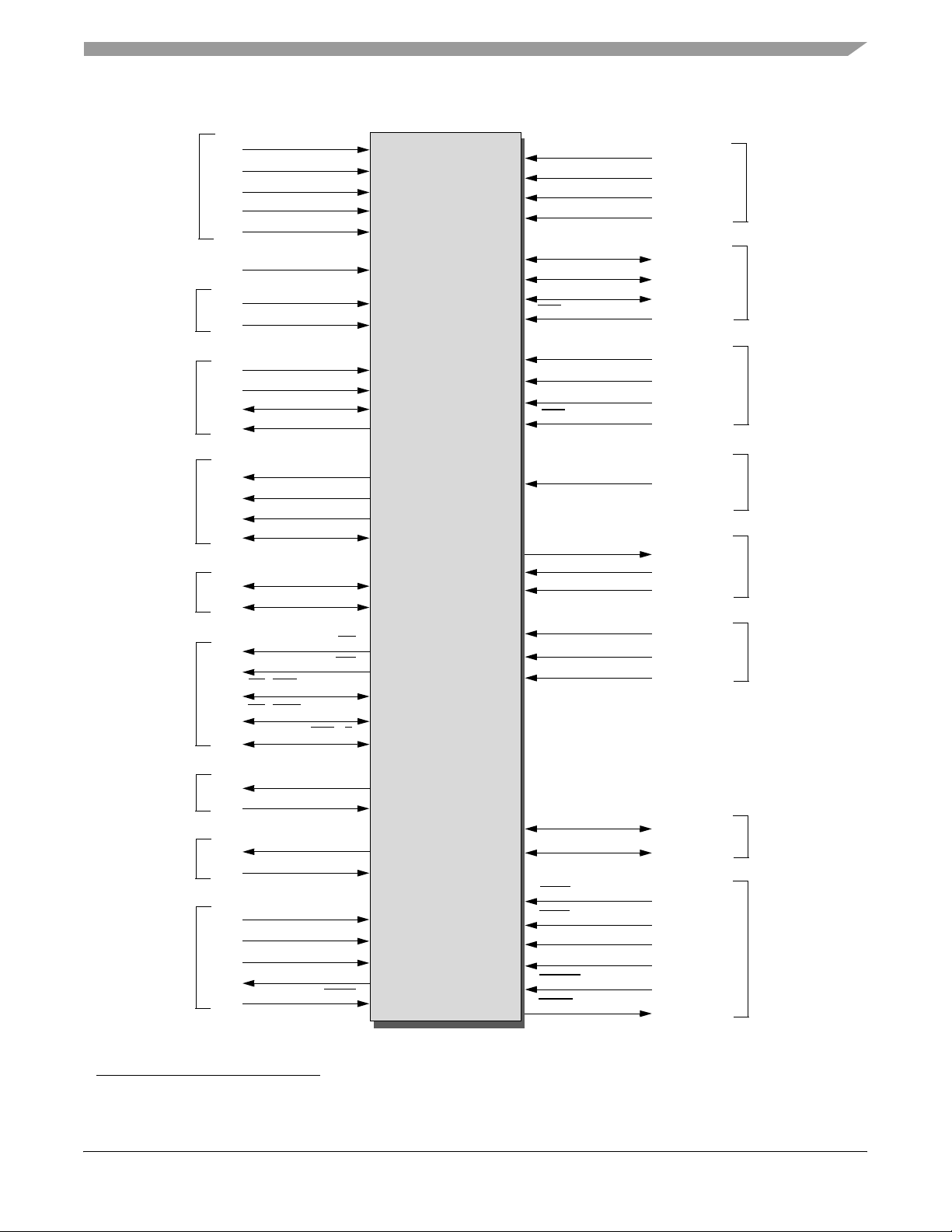

Introduction

7

1

1

5

PHASEA0 (TA0, GPIOC4)

1

PHASEB0 (TA1, GPIOC5)

1

INDEX0 (TA2, GPIOC6)

1

HOME0 (TA3, GPIOC7)

1

Quadrature

Decoder 0

or Quad

Timer A or

GPIO

1

56F8166

1

4

4

2

1

1

1

1

SCLK0

1

MOSI0

1

MISO0

1

SS0

1

(SCLK1, GPIOC0)

1

(MOSI1, GPIOC1)

1

(MISO1, GPIOC2)

1

(S

1

S1, GPIOC3)

SPI0 or

GPIO

(GPIOE7)

SPI 1 or

GPIO

External

Address

Bus

or GPIO

External

Data Bus

or GPIO

External

Bus

Control

or GPIO

SCI 0 or

GPIO

SCI 1

or GPIO

JTAG/

EOnCE

Port

A0 - A5 (GPIOA8 -

A6 - A7 (GPIOE2 - 3)

A8 - A15 (GPIOA0 - 7)

GPIOB0 (A16)

D0-D6 (GPIOF9 - 15)

D7 - D15 (GPIOF0 -

RD

WR

PS (CS0)(GPIOD8)

DS (CS1) (GPIOD9)

GPIOD0 - 1 (CS2 - 3)

TXD0 (GPIOE0)

RXD0 (GPIOE1)

TXD1 (GPIOD6)

RXD1 (GPIOD7)

TCK

TMS

TDI

TDO

TRST

6

3

(GPIOC8 - 10)

GPIO

2

8

1

7

PWMB0 - 5

6

ISB0 - 2 (GPIOD10 - 12)

3

FAULTB0 - 3

4

PWMB or

GPIO

9

ANA0 - 7

8

V

1

1

5

8

REF

ANB0 - 7

ADCA

ADCB

1

1

2

1

1

TC0 (GPIOE8)

1

1

2

(GPIOE10 - 11)

QUAD

TIMER C or

GPIO

1

IRQA

1

1

1

1

1

1

1

1

1

1

1

IRQB

EXTBOOT

EMI_MODE

RESET

RSTO

Interrupt/

Program

Control

Figure 2-2 56F8166 Signals Identified by Functional Group1 (144-pin LQFP)

1. Alternate pin functionality is shown in parenthesis; pin direction/type shown is the default functionality.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 17

Preliminary

2.2 Signal Pins

After reset, each pin is configured for its primary function (listed first). Any alternate functionality must

be programmed.

Note: Signals in italics are NOT available in the 56F8166 device.

If the “State During Reset” lists more than one state for a pin, the first state is the actual reset state. Other

states show the reset condition of the alternate function, which you get if the alternate pin function is

selected without changing the configuration of the alternate peripheral. For example, the A8/GPIOA0 pin

shows that it is tri-stated during reset. If the GPIOA_PER is changed to select the GPIO function of the

pin, it will become an input if no other registers are changed.

Table 2-2 Signal and Package Information for the 144-Pin LQFP

State

Signal Name Pin No. Type

During

Reset

Signal Description

V

DD_IO

V

DD_IO

V

DD_IO

V

DD_IO

V

DD_IO

V

DD_IO

V

DD_IO

V

DDA_ADC

V

DDA_OSC_PLL

V

SS

V

SS

V

SS

1 Supply I/O Power — This pin supplies 3.3V power to the ch ip I/O in terface

and also the Processor core th rought the on-c hip voltage reg ulator,

16

31

38

66

84

119

102 Supply ADC Power — This pin supplies 3. 3V po w er to th e ADC m odu le s.

80 Supply Oscillator and PLL Power — This pin supplies 3.3V power to the

27 Supply V

37

63

if it is enabled.

It must be connected to a clean analog power supply.

OSC and to the internal regulator that in turn supplies the Phase

Locked Loop. It must be connected to a clean analog power

supply.

— These pins provide ground for chip logic and I/O drivers.

SS

V

SS

V

SS

18 Freescale Semiconductor

69

144

56F8366 Technical Data, Rev. 2.0

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Pins

Signal Description

V

SSA_ADC

103 Supply ADC Analog Ground — This pin supplies an analog ground to the

ADC modules.

OCR_DIS 79 Input Input On-Chip Regulator Disable —

Tie this pin to V

to enable the on-chip regulator

SS

Tie this pin to VDD to disable the on-chip regulator

This pin is intended to be a static DC signal from power-up to

shut down. Do not try to toggle this pin for power savings

during operation.

1 51 Supply Supply V

V

CAP

1 - 4 — When OCR_DIS is tied to VSS (regulator enabled),

CAP

connect each pin to a 2.2µF or greater byp ass capacitor in order t o

2 128

V

CAP

V

3 83

CAP

V

4 15

CAP

bypass the core logic voltage regulator, required for proper chip

operation. When OCR_DIS is tied to V

these pins become V

DD_CORE

and should be connected to a

(regulator disabled),

DD

regulated 2.5V power supply.

Note: This bypass is required even if the chip is power ed with

an external supply.

V

1 125 Input Input VPP1 - 2 — These pins should be left unconnected as an open

PP

circuit for normal functionality.

VPP2 2

CLKMODE 87 Input Input Clock Input Mode Selection — This input det ermines the functi on

of the XTAL and EXTAL pins.

1 = External clock input on XTAL is used to directly drive the input

clock of the chip. The EXTAL pin should be grounded.

0 = A crystal or ceramic resonator should be connected between

XTAL and EXTAL.

EXTAL 82 Input Input External Crystal Oscillator Input — This input can be connected

to an 8MHz external cryst al. Tie this pin l ow if XT AL i s driven by a n

external clock source.

XTAL 81 Input/

Output

Chip-driven Crystal Oscillator Output — This output connects the internal

crystal oscillator output to an external crystal.

If an external clock is used, XTAL must be used as the input and

EXTAL connected to GND.

The input clock can be selected to provide the clock directly to the

core. This input clock can also be selected as the input clock for

the on-chip PLL.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 19

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

State

Signal Name Pin No. Type

CLKO 3 Output Tri-Stated Clock Output — This pin outputs a buffered clock signal. Using

During

Reset

Signal Description

the SIM CLKO Select Register (SIM_CLKOSR), this pin can be

programmed as any of the following: disabled, CLK_MSTR

(system clock), IPBus clock, oscillator output, prescaler clock and

postscaler clock. O ther si gnals are als o availab le for te st p urposes.

See Part 6.5.7 for details.

A0

(GPIOA8)

A1

(GPIOA9)

A2

(GPIOA10)

A3

(GPIOA11)

A4

(GPIOA12)

A5

(GPIOA13)

138 Output

Input/

Output

10

11

12

13

14

Tri-stated

Input

Address Bus — A0 - A5 specify six of the address lines for

external program or data memory accesses.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), A0–A5 and EMI control signals are tri-stated when the

external bus is inactive.

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

Port A GPIO — These six GPIO pins can be individually

programmed as input or output pins.

After reset, the default state is Address Bus.

To deactivate the internal pull-up resistor, set the appropriate

GPIO bit in the GPIOA_PUR register.

Example: GPIOA8, set bit 8 in the GPIOA_PUR register.

56F8366 Technical Data, Rev. 2.0

20 Freescale Semiconductor

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Pins

Signal Description

A6

(GPIOE2)

A7

(GPIOE3)

A8

17 Output

Schmitt

18

19 Output

Input/

Output

Tri-stated

Input

Tri-stated

Address Bus — A6 - A7 specify two of the address lines for

external program or data memory accesses.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), A6–A7 and EMI control signals are tri-stated when the

external bus is inactive.

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

Port E GPIO — These two GPIO pins can be individually

programmed as input or output pins.

After reset, the default state is Address Bus.

To deactivate the internal pull-up resistor, set the appropriate

GPIO bit in the GPIOE_PUR register.

Example: GPIOE2, set bit 2 in the GPIOE_PUR register.

Address Bus— A8 - A15 specify eight of the address lines for

external program or data memory accesses.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), A8–A15 and EMI control signals are tri-stated when

the external bus is inactive.

(GPIOA0)

A9

(GPIOA1)

A10

(GPIOA2)

A11

(GPIOA3)

A12

(GPIOA4)

A13

(GPIOA5)

A14

(GPIOA6)

A15

(GPIOA7)

20

21

22

23

24

25

26

Schmitt

Input/

Output

Input

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

Port A GPIO — These eight GPIO pins can be individually

programmed as input or output pins.

After reset, the default state is Address Bus.

To deactivate the internal pull-up resistor, set the appropriate

GPIO bit in the GPIOA_PUR register.

Example: GPIOA0, set bit 0 in the GPIOA_PUR register.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 21

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Description

GPIOB0

(A16)

D0

33 Schmitt

Input/

Output

Output

59 Input/

Output

Input

Tri-stated

Tri-stated

Port B GPIO — This GPIO pin can be programmed as an input or

output pin.

Address Bus — A16 specifies one of the address lines for

external program or data memory accesses.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), A16 and EMI control signals are tri-stated when the

external bus is inactive.

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

After reset, the startup state of GPIOB0 (GPIO or address) is

determined as a function of EXTBOOT, EM I_MODE a nd the Fla sh

security setting. See Table 4-4 for further information on when this

pin is configured as an addre ss pin at res et. In al l cas es , this stat e

may be changed by writing to GPIOB_PER.

To deactivate the internal pull-up resistor, set bit 0 in the

GPIOB_PUR register.

Data Bus — D0 - D6 specify part of the data for external program or

data memory accesses.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), D0 - D6 are tri-stated when the external bus is

inactive.

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

(GPIOF9)

D1

(GPIOF10)

D2

(GPIOF11)

D3

(GPIOF12)

D4

(GPIOF13)

D5

(GPIOF14)

D6

(GPIOF15)

22 Freescale Semiconductor

60

72

75

76

77

78

Input/

Output

Input

56F8366 Technical Data, Rev. 2.0

Port F GPIO — These seven GPIO pins can be individually

programmed as input or output pins.

At reset, these pins default to the EMI Data Bus function.

To deactivate the internal pull-up resistor, set the appropriate

GPIO bit in the GPIOF_PUR register.

Example: GPIOF9, set bit 9 in the GPIOF_PUR register.

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Pins

Signal Description

D7

(GPIOF0)

D8

(GPIOF1)

D9

(GPIOF2)

D10

(GPIOF3)

D11

(GPIOF4)

D12

(GPIOF5)

D13

(GPIOF6)

28 Input/

Output

Input/

Output

29

30

32

133

134

135

Tri-stated

Input

Data Bus — D7 - D14 specify part of the data for external pro gram

or data memory accesses.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), D7 - D14 are tri-stated when the external bus is

inactive.

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

Port F GPIO — These eight GPIO pins can be individually

programmed as input or output pins.

At reset, these pins default to Data Bus functionality.

To deactivate the internal pull-up resistor, clear the appropriate

GPIO bit in the GPIOF_PUR register.

Example: GPIOF0, clear bit 0 in the GPIOF_PUR register.

D14

(GPIOF7)

D15

(GPIOF8)

Freescale Semiconduc tor 23

Preliminary

136

137 Input/

Output

Input/

Output

Tri-stated

Input

56F8366 Technical Data, Rev. 2.0

Data Bus — D15 specifie s part of the data fo r ex ter nal pro gra m or

data memory accesses.

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

Port F GPIO — This GPIO pin can be individually programmed as

an input or output pin.

At reset, this pin defaults to the data bus function.

To deactivate the internal pull-up resistor, set bit 8 in the

GPIOF_PUR register.

Table 2-2 Signal and Package Information for the 144-Pin LQFP

State

Signal Name Pin No. Type

RD 45 Output Tri-stated Read Enable — RD is asserted during external memory read

During

Reset

Signal Description

cycles. When RD

and an external device is enabled onto the data bus. When RD

deasserted high, the external data is latched inside the device.

When RD

pins. RD can be connected directly to the OE pin of a static RAM or

ROM.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), RD

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

To deactivate the internal pull-up resistor, set the CTRL bit in the

SIM_PUDR register.

is asserted low, pins D0 - D15 become inputs

is asserted, it qualifies the A0 - A16, PS, DS, and CSn

is tri-stated when the external bus is inactive.

is

WR

PS

(CS0)

44 Output Tri-stated Write Enable — WR is asserted during external memory write

46 Output

Tri-stated

cycles. When WR

and the device put s data on th e bus. When WR

the external data is latch ed inside th e externa l device . When WR

asserted, it qualifies the A0 - A16, PS

be connected directly to the WE

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), WR

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

To deactivate the internal pull-up resistor, set the CTRL bit in the

SIM_PUDR register.

Program Memory Select — This signal is actually CS0 in the

EMI, which is programmed at reset for compatibility with the

56F80x PS signal. PS is asserted low for external program

memory access.

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), PS

CS0 resets to provide the PS function as defined on the 56F80x

devices.

is asserted low, pins D0 - D15 become outputs

is deasserted high,

, DS, and CSn pins. WR can

pin of a static RAM.

is tri-sta ted when the external bus is inacti ve.

is tri-stated when the external bus is inactive.

is

(GPIOD8)

24 Freescale Semiconductor

Input/

Output

Input

56F8366 Technical Data, Rev. 2.0

Port D GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

To deactivate the Internal pull-up resistor, clear bit 8 in the

GPIOD_PUR register.

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Pins

Signal Description

DS

(CS1)

(GPIOD9)

GPIOD0

(CS2

)

47 Output

Input/

Output

48 Input/

Output

Output

Tri-stated

Input

Input

Tri-stated

Data Memory Select — This signal is actually CS1 in the EMI,

which is programmed at reset for compatib ility with the 56F80 x DS

signal. DS

Depending upon the state of the DRV bit in the EMI bus control

register (BCR), DS

CS1

devices.

Port D GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

To deactivate the Internal pull-up resistor, clear bit 9 in the

GPIOD_PUR register.

Port D GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

Chip Select — CS2 may be programmed within the EMI module to

act as a chip select for speci fic areas of the externa l me mory map .

Depending upon the state of the DRV bit in the EMI Bus Control

Register (BCR), CS2

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

is asserted low for external data memory access.

is tri-stated when the external bus is inactive.

resets to provide the DS function as defined on the 56F80x

is tri-stated when the external bu s is inactiv e.

(CAN2_TX)

Open

Drain

Output

Output

56F8366 Technical Data, Rev. 2.0

FlexCAN2 Transmit Data — CAN output.

At reset, this pin is configured as GPIO. This configuration can be

changed by setting bit 0 in the GPIO_D_PER register. Then

change bit 4 in the SIM_GPS register to select the desired

peripheral function.

To deactivate the internal pull-up resistor, clear bit 0 in the

GPIOD_PUR register.

Freescale Semiconduc tor 25

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Description

GPIOD1

(CS3

)

(CAN2_RX)

TXD0

(GPIOE0)

49 Schmitt

Input/

Output

Output

Schmitt

Input

4Output

Input/

Output

Input

Tri-stated

Input

Tri-stated

Input

Port D GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

Chip Select — CS3 may be programmed within the EMI module to

act as a chip select for speci fic areas of the externa l me mory map .

Depending upon the state of the DRV bit in the EMI Bus Control

Register (BCR), CS3

Most designs will want to change the DRV state to DRV = 1 instead of

using the default setting.

FlexCAN2 Receive Data — This is the CAN input. This pin has an

internal pull-up resistor.

At reset, this pin is configured as GPIO. This configuration can be

changed by setting bit 1 in the GPIO_D_PER register. Then

change bit 5 in the SIM_GPS register to select the desired

peripheral function.

To deactivate the internal pull-up resistor, clear bit 1 in the

GPIOD_PUR register.

Transmit Data — SCI0 transmit data output

Port E GPIO — This GPIO pin can be in div id ually programmed as

an input or output pin.

is tri-stated when the external bu s is inactiv e.

After reset, the default state is SCI output.

To deactivate the internal pull-up resistor, clear bit 0 in the

GPIOE_PUR register.

RXD0

(GPIOE1)

26 Freescale Semiconductor

5 Input

Input/

Output

Input

Input

56F8366 Technical Data, Rev. 2.0

Receive Data — SCI0 receive data input

Port E GPIO — This GPIO pin can be in div id ually programmed as

an input or output pin.

After reset, the default state is SCI output.

To deactivate the internal pull-up resistor, clear bit 1 in the

GPIOE_PUR register.

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Pins

Signal Description

TXD1

(GPIOD6)

RXD1

(GPIOD7)

TCK 121 Schmitt

TMS 122 Schmitt

42 Output

43 Input

Input/

Output

Input/

Output

Input

Input

Tri-stated

Input

Input

Input

Input,

pulled low

internally

Input,

pulled high

internally

Transmit Data — SCI1 transmit data output

Port D GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

After reset, the default state is SCI output.

To deactivate the internal pull-up resistor, clear bit 6 in the

GPIOD_PUR register.

Receive Data — SCI1 receive data input

Port D GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

After reset, the default state is SCI input.

To deactivate the internal pull-up resistor, clear bit 7 in the

GPIOD_PUR register.

Test Clock Input — This input pin provides a gated clock to

synchronize the test logic and sh ift serial data to the JTAG/EOnCE

port. The pin is connected internally to a pull-down resistor.

Test Mode Select Input — This in pu t pin is us ed to se que nc e the

JTAG TAP controller’s state machine. It is sampled on the rising

edge of TCK and has an on-chip pull-up resistor.

To deactivate the internal pull-up res is tor, set the JTAG bit in the

SIM_PUDR register.

TDI 123 Schmitt

Input

TDO 124 Output Tri-stated Test Data Output — This tri-stateable output pin prov id es a serial

Input,

pulled high

internally

56F8366 Technical Data, Rev. 2.0

Test Data Input — This input pin provides a serial input data

stream to the JTAG/EOnCE port. It is sampled on the rising edge

of TCK and has an on-chip pull-up resistor.

To deactivate the internal pull-up res is tor, set the JTAG bit in the

SIM_PUDR register.

output data stream from the JTAG/EOnCE port. It is driven in the

shift-IR and shift-DR controller states, and changes on the falling

edge of TCK.

Freescale Semiconduc tor 27

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Description

TRST 120 Schmitt

PHASEA0

(TA0)

(GPIOC4)

PHASEB0

139 Schmitt

Schmitt

Input/

Output

Schmitt

Input/

Output

140 Schmitt

Input

Input

Input

Input,

pulled high

internally

Input

Input

Input

Input

Test Reset — As an input, a low s ignal on this pi n prov ides a re set

signal to the JTAG TAP controller. To ensure complete hardware

reset, TRST should be asserted whenever RESET is asserted.

The only exception occurs in a debugging environment when a

hardware device reset is required and the JTAG/EOnCE module

must not be reset. In this case, assert RESET

.

TRST

To deactivate the internal pull-up res is tor, set the JTAG bit in the

SIM_PUDR register.

Phase A — Quadrature Decoder 0, PHASEA input

TA0 — Timer A, Channel 0

Port C GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

After reset, the default state is PHASEA0.

To deactivate the internal pull-up resistor, clear bit 4 of the

GPIOC_PUR register.

Phase B — Quadrature Decoder 0, PHASEB input

, but do not assert

(TA1)

(GPIOC5)

Schmitt

Input/

Output

Schmitt

Input/

Output

Input

Input

56F8366 Technical Data, Rev. 2.0

TA1 — Timer A, Channel

Port C GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

After reset, the default state is PHASEB0.

To deactivate the internal pull-up resistor, clear bit 5 of the

GPIOC_PUR register.

28 Freescale Semiconductor

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Pins

Signal Description

INDEX0

(TA2)

(GPOPC6)

HOME0

(TA3)

(GPIOC7)

141 Schmitt

Input

Schmitt

Input/

Output

Schmitt

Input/

Output

142 Schmitt

Input

Schmitt

Input/

Output

Schmitt

Input/

Output

Input

Input

Input

Input

Input

Input

Index — Quadrature Decoder 0, INDEX input

TA2 — Timer A, Channel 2

Port C GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

After reset, the default state is INDEX0.

To deactivate the internal pull-up resistor, clear bit 6 of the

GPIOC_PUR register.

Home — Quadrature Decoder 0, HOME input

TA3 — Timer A, Channel 3

Port C GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

After reset, the default state is HOME0.

SCLK0

(GPIOE4)

130 Schmitt

Input/

Output

Schmitt

Input/

Output

Input

Input

To deactivate the internal pull-up resistor, clear bit 7 of the

GPIOC_PUR register.

SPI 0 Serial Clock — In the master mode, this pin serves as an

output, clocking slaved listeners. In slave mode, this pin serves as

the data clock input.

Port E GPIO — This GPIO pin can be in div id ually programmed as

an input or output pin.

After reset, the default state is SCLK0.

To deactivate the internal pull-up resistor, clear bit 4 in the

GPIOE_PUR register.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 29

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Description

MOSI0

(GPIOE5)

MISO0

(GPIOE6)

132 Input/

Output

Input/

Output

131 Input/

Output

Input/

Output

Tri-stated

Input

Input

Input

SPI 0 Master Out/Slave In — This serial data pin is an output from

a master devic e a nd an input to a slav e d ev ic e. The m aster device

places data on the MOSI li ne a half -cycle b efore the clock e dge th e

slave device uses to latch the data.

Port E GPIO — This GPIO pin can be in div id ually programmed as

an input or output pin.

After reset, the default state is MOSI0.

To deactivate the internal pull-up resistor, clear bit 5 in the

GPIOE_PUR register.

SPI 0 Master In/Slave Out — This serial data pin is an input to a

master device and an outp ut from a slav e device. Th e MISO line o f

a slave device is placed in the high-impedance state if the slave

device is not selected. The slave device places data on the MISO

line a half-cycle before the clock edge the master device uses to

latch the data.

Port E GPIO — This GPIO pin can be in div id ually programmed as

an input or output pin.

After reset, the default state is MISO0.

To deactivate the internal pull-up resistor, clear bit 6 in the

GPIOE_PUR register.

SS0

(GPIOE7)

129 Input

Input/

Output

Input

Input

56F8366 Technical Data, Rev. 2.0

SPI 0 Slave Select — SS0

SPI module that the current transfer is to be received.

Port E GPIO — This GPIO pin can be in div id ually programmed as

input or output pin.

After reset, the default state is SS0

To deactivate the internal pull-up resistor, clear bit 7 in the

GPIOE_PUR register.

is used in slave mode to ind icate to the

.

30 Freescale Semiconductor

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Pins

Signal Description

PHASEA1

(TB0)

(SCLK1)

(GPIOC0)

PHASEB1

6Schmitt

Input

Schmitt

Input/

Output

Schmitt

Input/

Output

Schmitt

Input/

Output

7Schmitt

Input

Input

Input

Input

Input

Input

Phase A1 — Quadrature Decoder 1, PHASEA i npu t fo r dec od er 1.

TB0 — Timer B, Channel 0

SPI 1 Serial Clock — In the master mode, this pin serves as an

output, clocking slaved listeners. In slave mode, this pin serves as

the data clock input. To activate the SPI function, set the

PHSA_ALT bit in the SIM_GPS register. For details, see Part

6.5.8.

Port C GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

In the 56F8366, the default state after reset is PHASEA1.

In the 56F8166, the d efault state i s not o ne of th e func tions o ffered

and must be reconfigured.

To deactivate the internal pull-up resistor, clear bit 0 in the

GPIOC_PUR register.

Phase B1 — Quadrature Decoder 1, PHASEB i npu t fo r dec od er 1.

(TB1)

(MOSI1)

(GPIOC1)

Schmitt

Input/

Output

Schmitt

Input/

Output

Schmitt

Input/

Output

Input

Tri-stated

Input

TB1 — Timer B, Channel 1

SPI 1 Master Out/Slave In — This serial data pin is an output from

a master devic e a nd an input to a slav e d ev ic e. The m aster device

places data on the MOSI li ne a half -cycle b efore the clock e dge th e

slave device uses to latch the data. To activate the SPI function,

set the PHSB_ALT bit in the SIM_GPS register. For details, see

Part 6.5.8.

Port C GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

In the 56F8366, the default state after reset is PHASEB1.

In the 56F8166, the d efault state i s not o ne of th e func tions o ffered

and must be reconfigured.

To deactivate the internal pull-up resistor, clear bit 1 in the

GPIOC_PUR register.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 31

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Description

INDEX1

(TB2)

(MISO1)

(GPIOC2)

HOME1

(TB3)

8Schmitt

Input

Schmitt

Input/

Output

Schmitt

Input/

Output

Schmitt

Input/

Output

9Schmitt

Input

Schmitt

Input/

Output

Input

Input

Input

Input

Input

Input

Index1 — Quadrature Decoder 1, INDEX input

TB2 — Timer B, Channel 2

SPI 1 Master In/Slave Out — This serial data pin is an input to a

master device and an outp ut from a slav e device. Th e MISO line o f

a slave device is placed in the high-impedance state if the slave

device is not selected. The slave device places data on the MISO

line a half-cycle before the clock edge the master device uses to

latch the data. To activa te the SPI fu nction , set the INDEX_ALT bit

in the SIM_GPS register. For details, see Part 6.5.8.

Port C GPIO — This GPIO pin can be individually programm ed as

an input or output pin.

After reset, the default state is INDEX1.

To deactivate the internal pull-up resistor, clear bit 2 in the

GPIOC_PUR register.

Home — Quadrature Decoder 1, HOME input

TB3 — Timer B, Channel 3

)

(SS1

(GPIOC3)

32 Freescale Semiconductor

Schmitt

Input

Schmitt

Input/

Output

Input

Input

56F8366 Technical Data, Rev. 2.0

SPI 1 Slave Select — In the master mode, this pin is used to

arbitrate multiple masters. In slave mode, this pin is used to select

the slave. To activate the SPI function, set the HOME_ALT bit in

the SIM_GPS register. For details, see Part 6.5.8.

Port C GPIO — This GPIO pin can be individually programm ed as

input or an output pin.

In the 56F8366, the default state after reset is HOME1.

In the 56F8166, the d efault state i s not o ne of th e func tions o ffered

and must be reconfigured.

To deactivate the internal pull-up resistor, clear bit 3 in the

GPIOC_PUR register.

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

State

Signal Name Pin No. Type

PWMA0 62 Output Tri-State PWMA0 - 5 — These are six PWMA outputs.

PWMA1 64

PWMA2 65

PWMA3 67

PWMA4 68

PWMA5 70

During

Reset

Signal Description

Signal Pins

ISA0

(GPIOC8)

ISA1

(GPIOC9)

ISA2

(GPIOC10)

FAULTA0 71 Schmitt

FAULTA1 73

FAULTA2 74

PWMB0 34 Output Tri-State PWMB0 - 5 — Six PWMB output pins.

PWMB1 35

PWMB2 36

113 Schmitt

Input

Schmitt

114

115

Input/

Output

Input

Input

Input

Input FAULTA0 - 2 — These three fault input pins are used fo r disa bling

ISA0 - 2 — These three input current status pins are used for

top/bottom pulse width correction in complementary channel

operation for PWMA.

Port C GPIO — These three GPIO pins can be individually

programmed as input or output pins.

In the 56F8366, these pins default to ISA functionality after reset.

In the 56F8166, the d efault state i s not o ne of th e func tions o ffered

and must be reconfigured.

To deactivate the internal pull-up resistor, clear the appropriate bit

of the GPIOC_PUR register. For details, see Part 6.5.8.

selected PWMA outputs in cases where fault conditions originate

off-chip.

To deactivate the in ternal pul l-up resis tor, set t he PWMA0 bi t in the

SIM_PUDR register. For details, see Part 6.5.8.

PWMB3 39

PWMB4 40

PWMB5 41

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 33

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Description

ISB0

50 Schmitt

Input

Input

ISB0 - 2 — These three input current status pins are used for

top/bottom pulse width correction in complementary channel

operation for PWMB.

(GPIOD10)

ISB1

52

(GPIOD11)

ISB2

53

(GPIOD12)

FAULTB0 56 Schmitt

FAULTB1 57

FAULTB2 58

FAULTB3 61

Schmitt

Input/

Output

Input

Input

Port D GPIO — These GPIO pins can b e indi vidua lly pro gramm ed

as input or output pins.

At reset, these pins default to ISB functionality.

To deactivate the internal pull-up resistor, clear the appropriate bit

of the GPIOD_PUR register. For details, see Part 6.5.8.

Input FAULTB0 - 3 — These four fault input pins are used for disabling

selected PWMB outputs in cases where fault conditions originate

off-chip.

To deactivate the internal pull-up resistor, set the PWMB bit in the

SIM_PUDR register. For details, see Part 6.5.8.

ANA0 88 Input Input ANA0 - 3 — Analog inputs to ADC A, channel 0

ANA1 89

ANA2 90

ANA3 91

ANA4 92 Input Input ANA4 - 7 — Analog inputs to ADC A, channel 1

ANA5 93

ANA6 94

ANA7 95

V

REFH

V

REFP

V

REFMID

V

REFN

V

REFLO

101 Input Input V

100 Input/

Output

Input/

Output

99

98

97 Input Input V

— Analog Reference Voltage High. V

REFH

than or equal to

V

, V

REFP

REFMID

VDDA_ADC.

& V

REFN

— Internal pins for voltage reference

which are brought off-chip so they can be bypassed. Connect to a

0.1µF or low ESR capacitor.

— Analog Reference Voltage Low. This should normally

REFLO

be connected to a low-noise V

SSA

.

must be less

REFH

56F8366 Technical Data, Rev. 2.0

34 Freescale Semiconductor

Preliminary

Signal Pins

Table 2-2 Signal and Package Information for the 144-Pin LQFP

State

Signal Name Pin No. Type

ANB0 104 Input Input ANB0 - 3 — Analog inputs to ADC B, channel 0

ANB1 105

ANB2 106

ANB3 107

ANB4 108 Input Input ANB4 - 7 — Analog inputs to ADC B, channel 1

ANB5 109

ANB6 110

ANB7 111

TEMP_SENSE 96 Output Output Temperature Sense Diode — This signal connects to an on-chip

During

Reset

Signal Description

diode that can be connected to one of the ADC input s an d us ed to

monitor the temperature of the die. Must be bypassed with a

0.01µF capacitor.

CAN_RX 127 Schmitt

Input

CAN_TX 126 Open

Drain

Output

TC0

(GPIOE8)

118 Schmitt

Input/

Output

Schmitt

Input/

Outpu

Input FlexCAN Receive Data — This is the CAN input. This pin has an

internal pull-up resistor.

To deactivate the internal pull-up resistor, set the CAN bit in the

SIM_PUDR register.

Open

Drain

Output

Input

Input

FlexCAN Transmit Data — CAN output

TC0 — Timer C, Channel 0

Port E GPIO — These GPIO pin can be individually programmed

as an input or output pin.

At reset, this pin defaults to timer functionality.

To deactivate the internal pull-up resistor, clear bit 8 of the

GPIOE_PUR register.

56F8366 Technical Data, Rev. 2.0

Freescale Semiconduc tor 35

Preliminary

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name Pin No. Type

State

During

Reset

Signal Description

TD0

(GPIOE10)

TD1

(GPIOE11)

IRQA

IRQB

RESET

116 Schmitt

Input/

Output

Schmitt

117

54 Schmitt

55

86 Schmitt

Input/

Output

Input

Input

Input

Input

Input External Interrupt Request A and B — The IRQA and IRQB

Input Reset — This input is a direct hardware reset on the processor.

TD0 - TD1 — Timer D, Channels 0 and 1

Port E GPIO — These GPIO pins can be indiv idual ly progr ammed

as input or output pins.

At reset, these pins default to Timer functionality.

To deactivate the internal pull-up resistor, clear the appropriate bit

of the GPIOE_PUR register. See Part 6.5.6 for details.

inputs are asynchronous external interrupt requests during Stop

and Wait mode operation. During other operating modes, they are

synchronized external interrupt requests, which indicate an

external device is req ues ti ng s erv ic e. Th ey ca n be prog ram me d to

be level-sensitive or negative-edge triggered.

To deactivate the internal pull-up resistor, set the IRQ bit in the

SIM_PUDR register. See Part 6.5.6 for details.

When RESET

in the reset state. A Schmitt trigger input is used for noise