Page 1

5

4

3

2

1

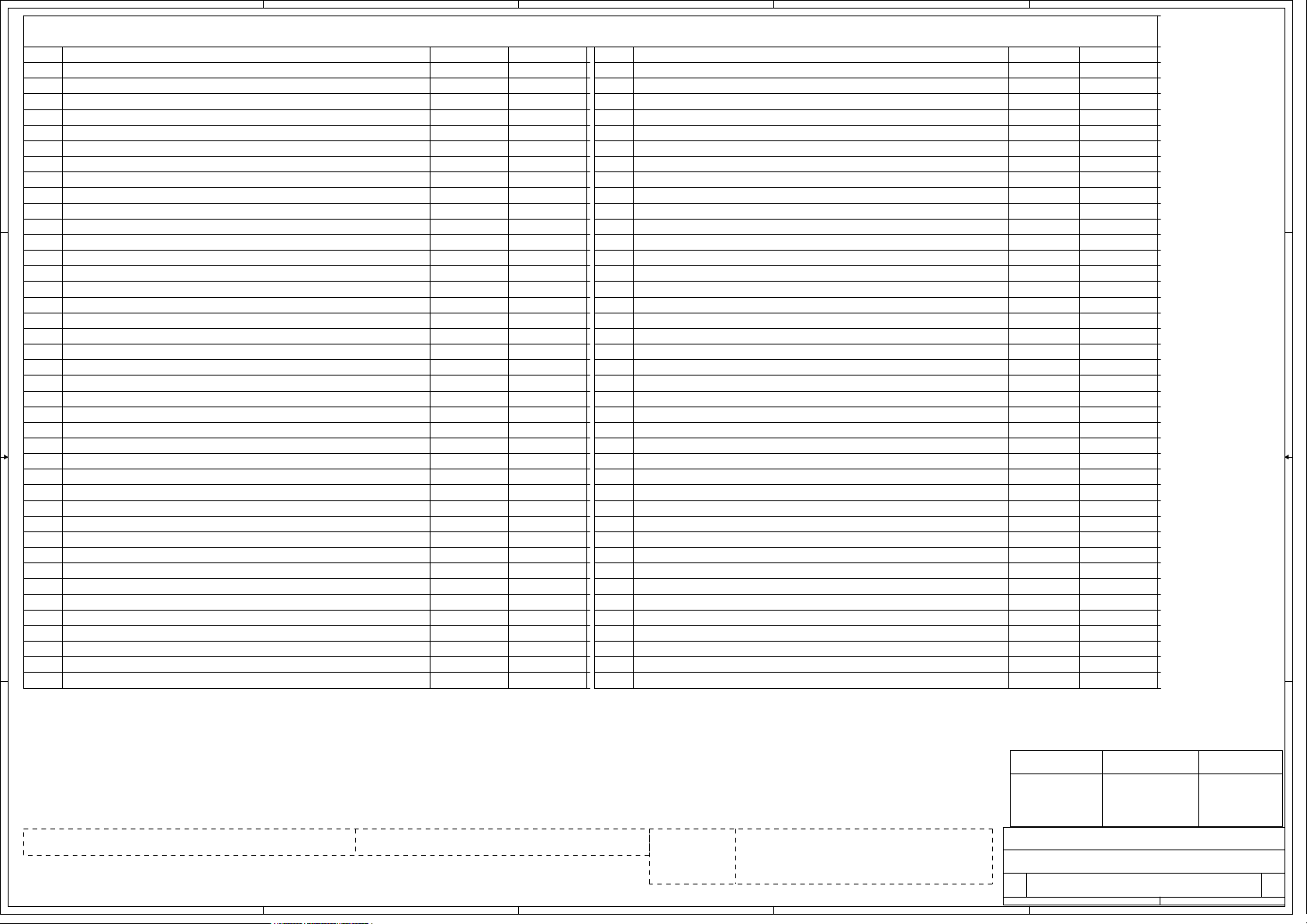

Schematics Page Index (Title / Revision / Change Date)

Page

01

02

03

04

D D

05

06

07

08

09

10

11

12

13

14

15

16

17

18

C C

19

20

21

22

23

24

25

26

27

28

29

30

31

32

B B

33

34

35

36

37

38

39

40

Title of Schematics Page

Schematics Page Index

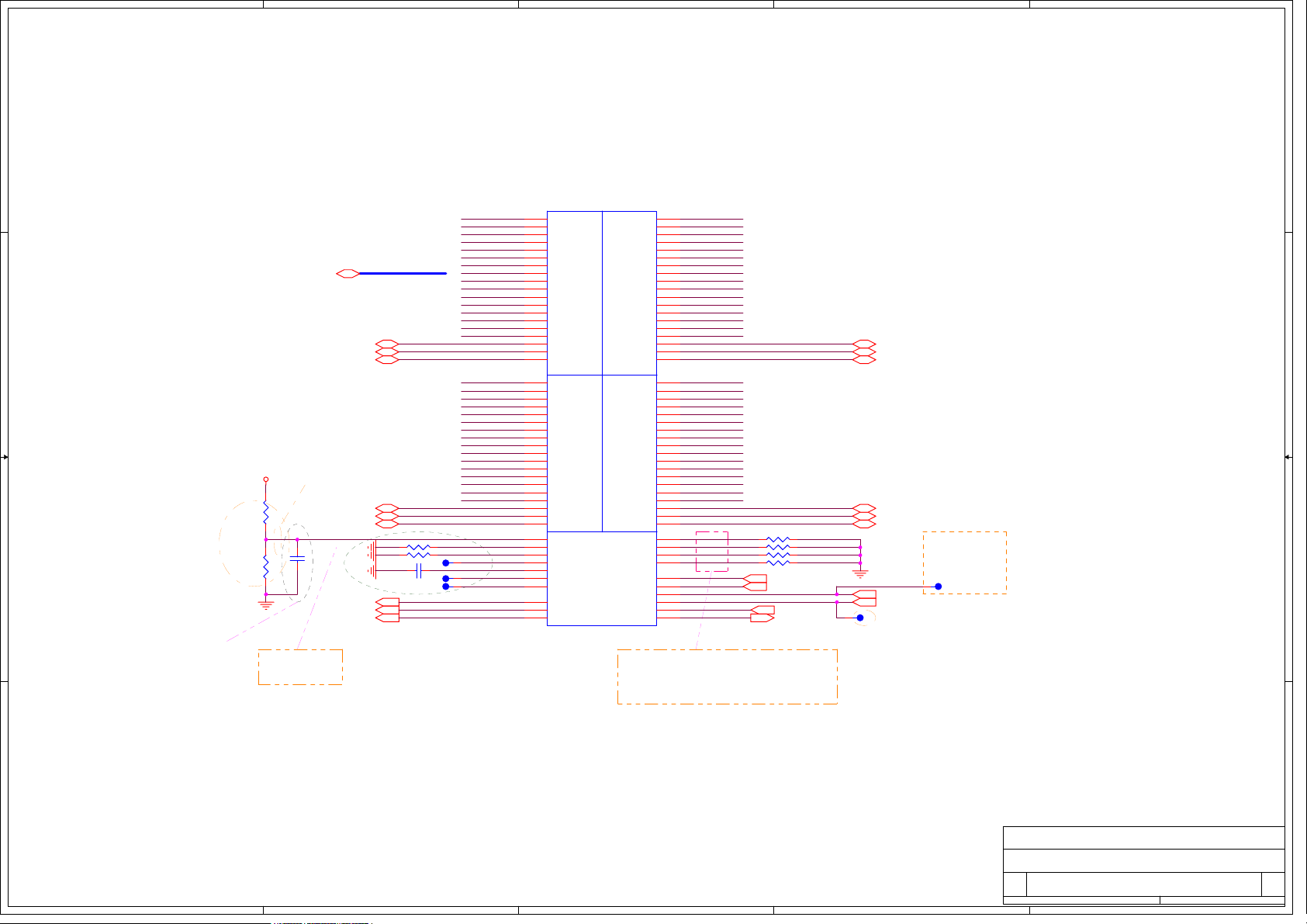

Block Diagram

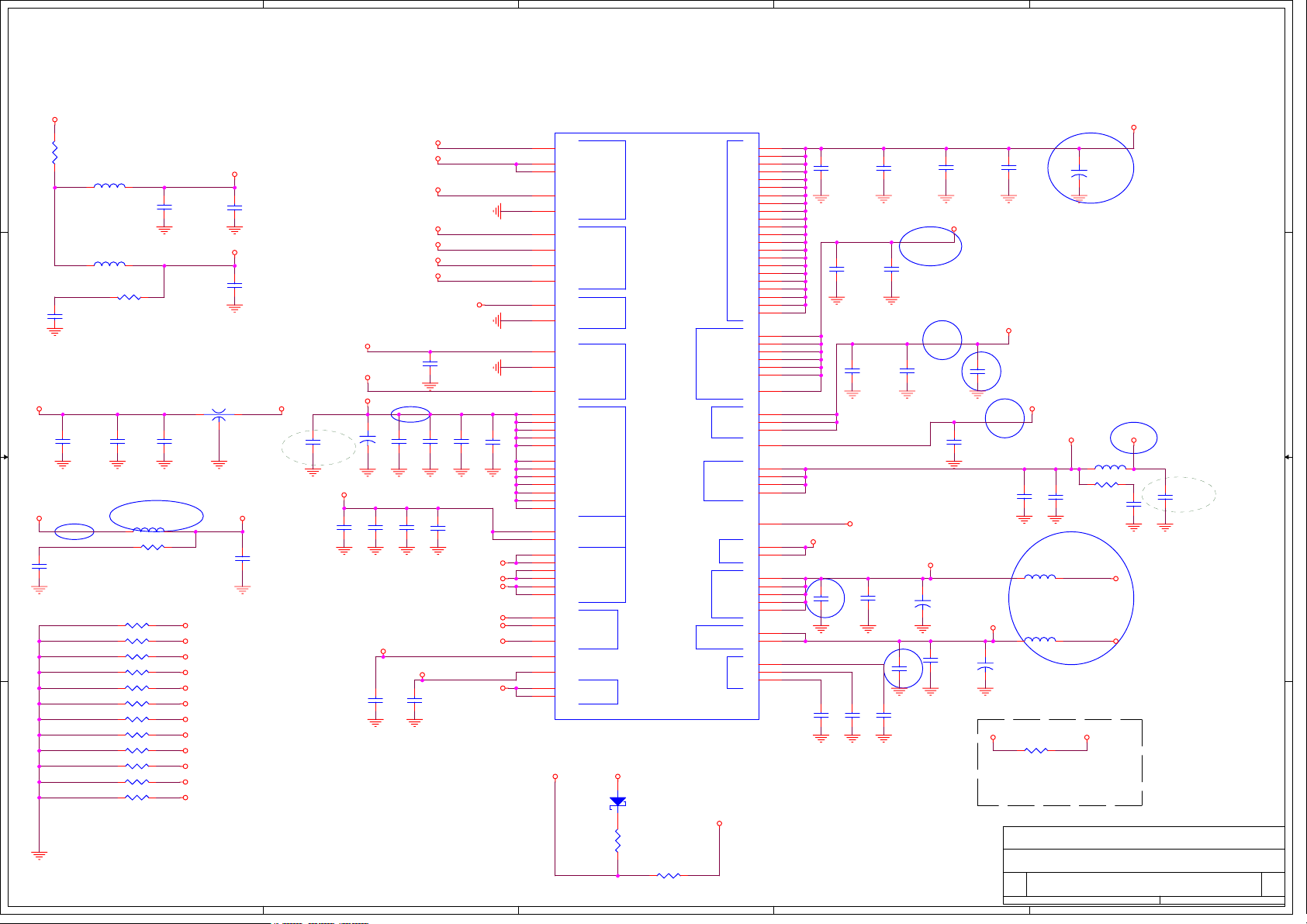

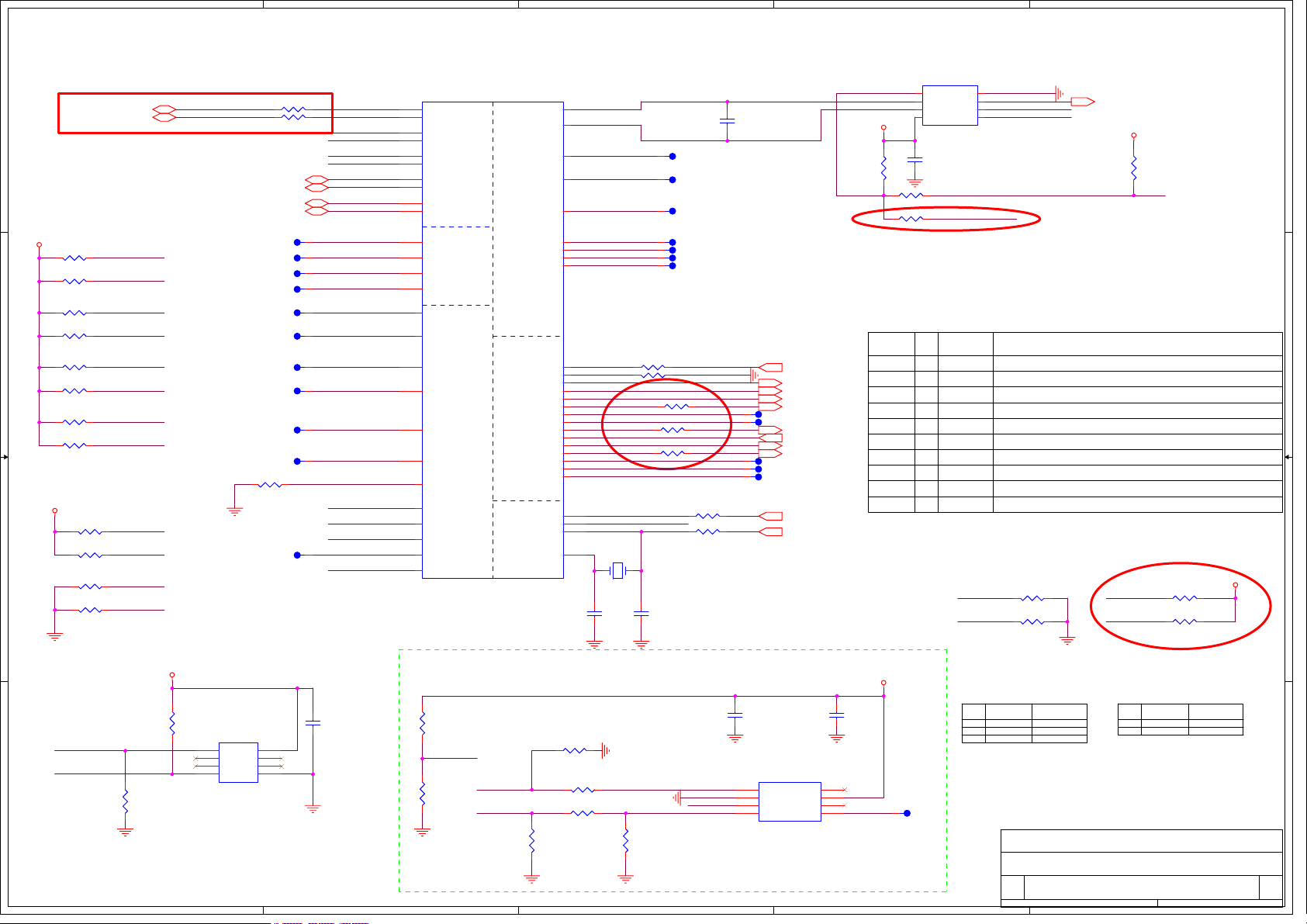

CLOCK GEN (CK505)

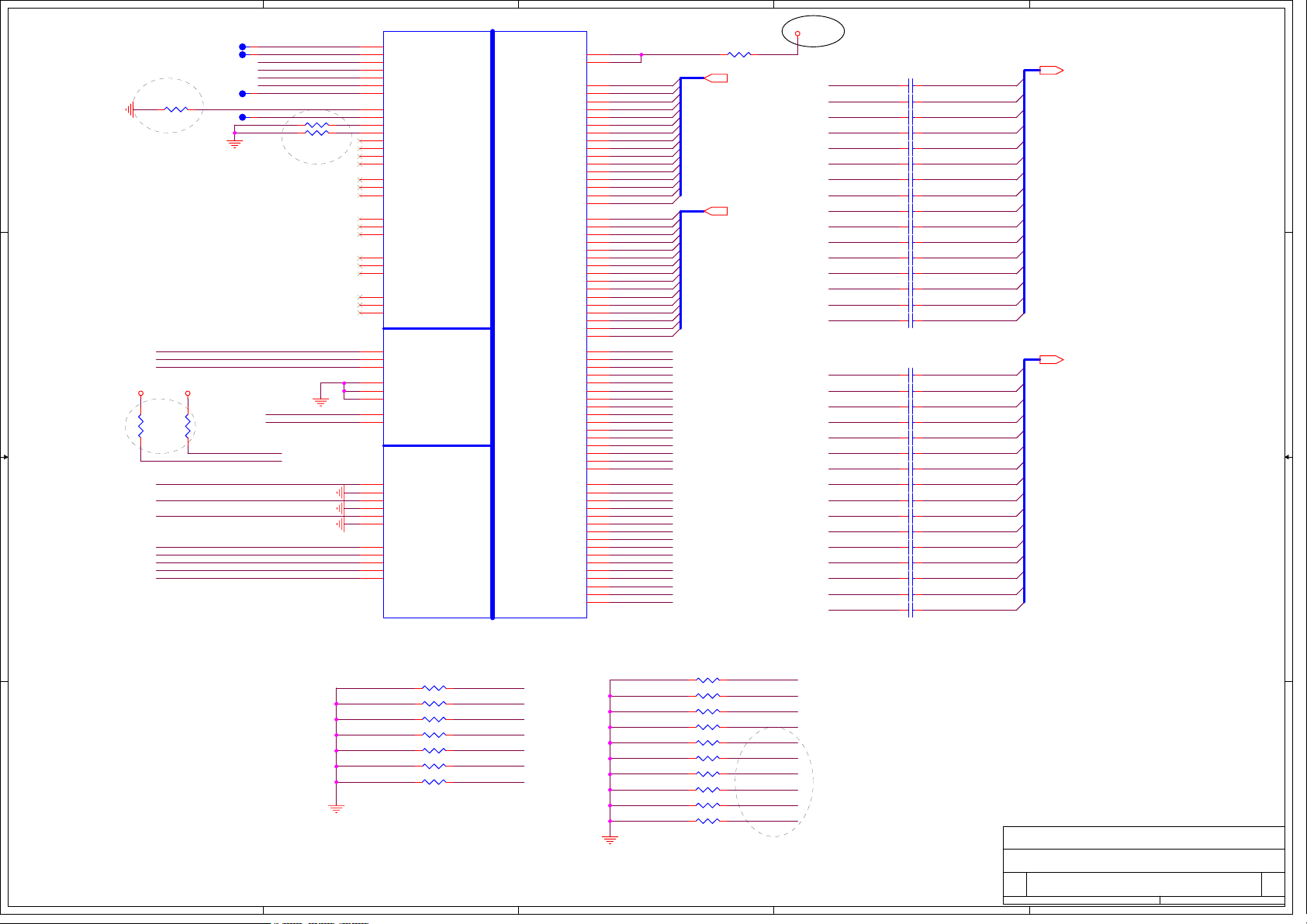

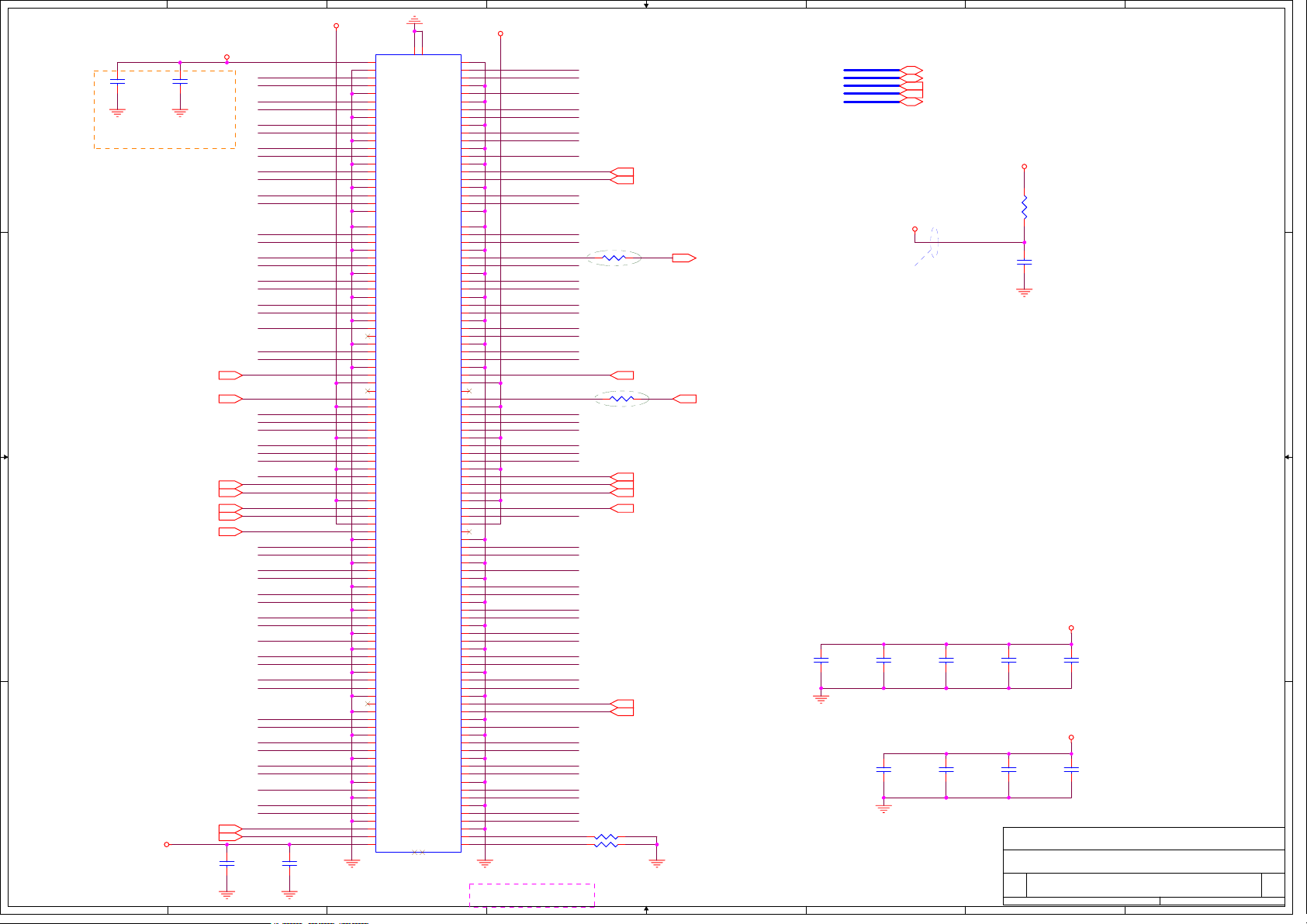

MEROM(HOST BUS) 1/2

MEROM(HOST BUS) 2/3

MEROM(Power/Gnd) 3/3

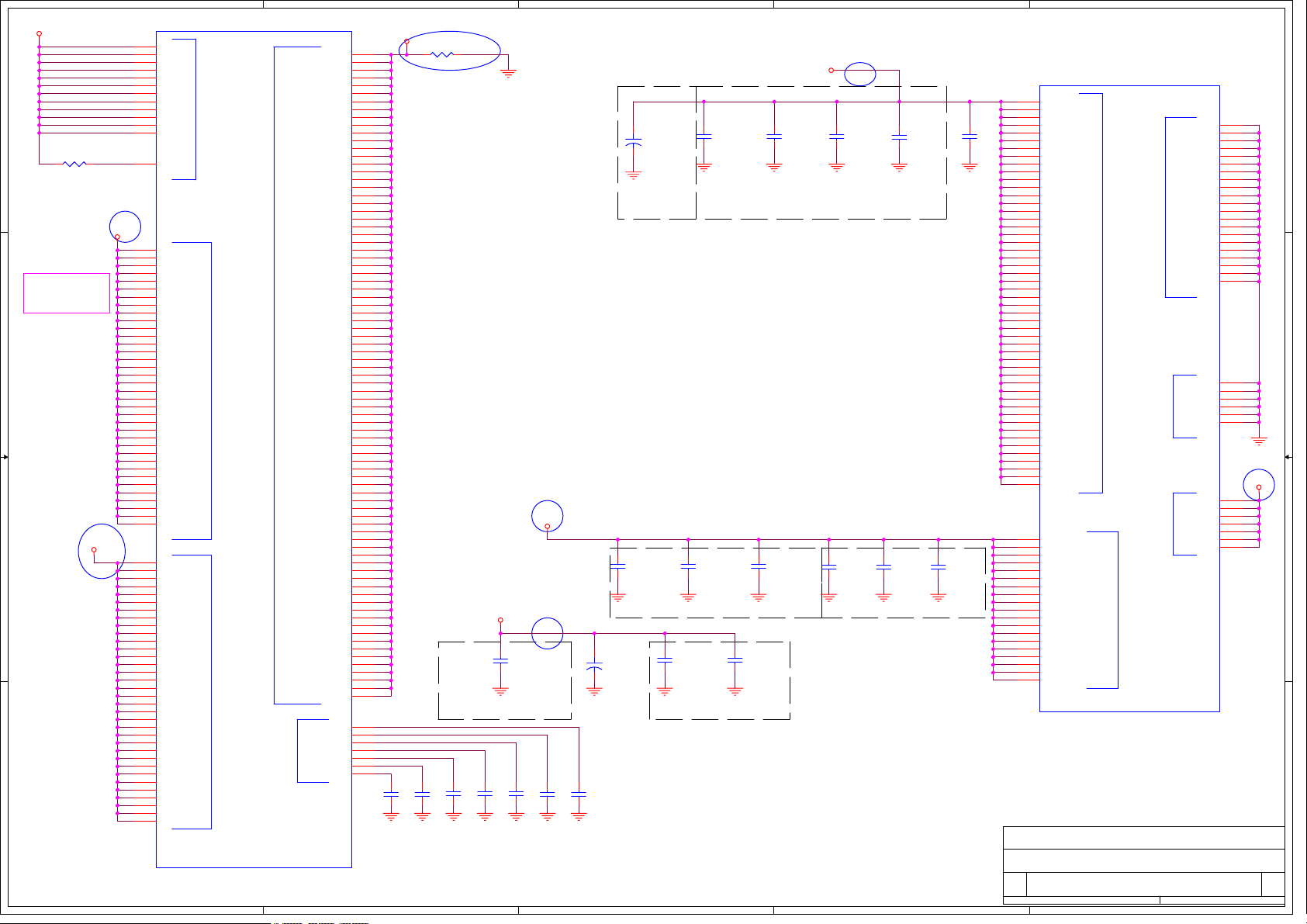

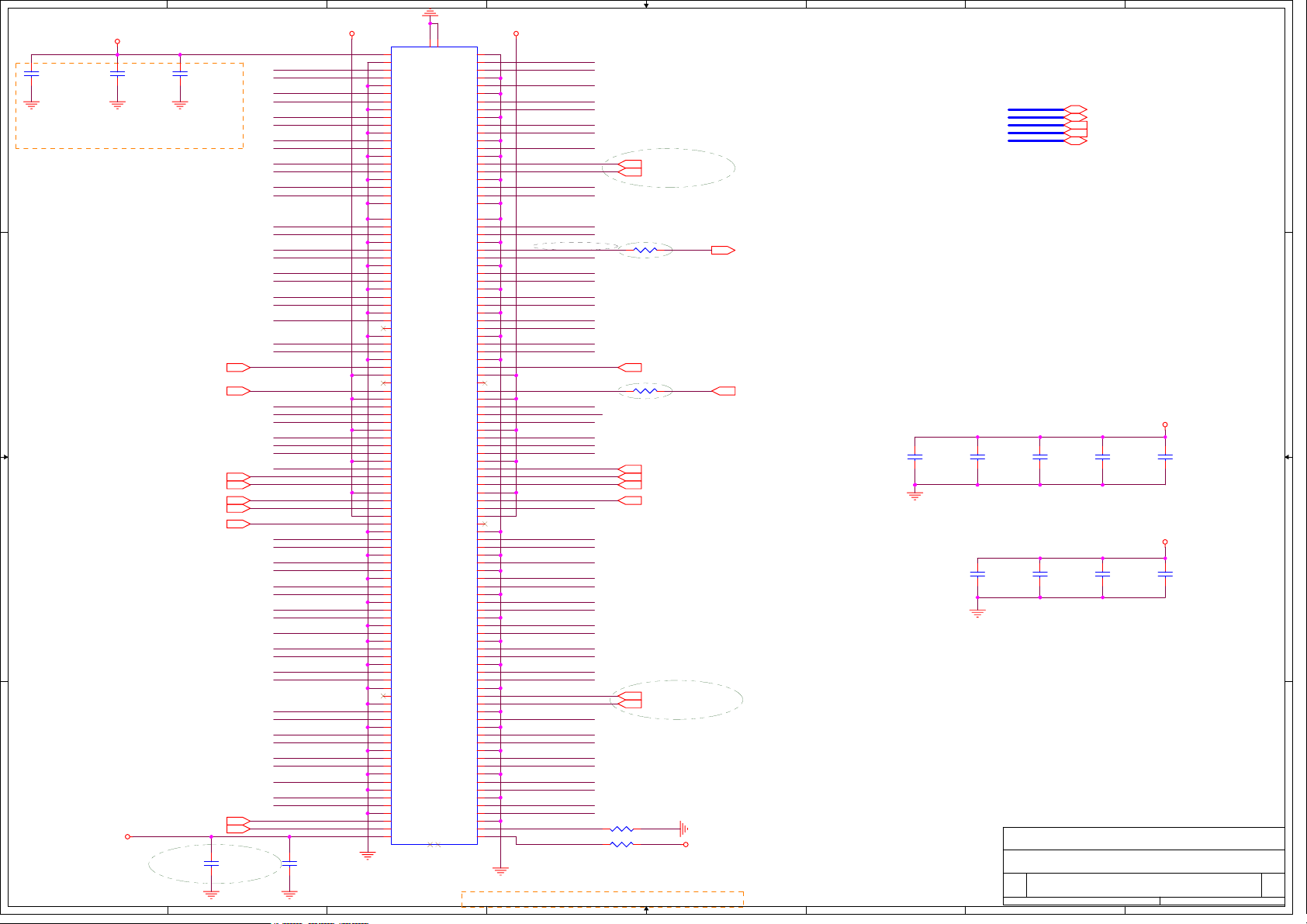

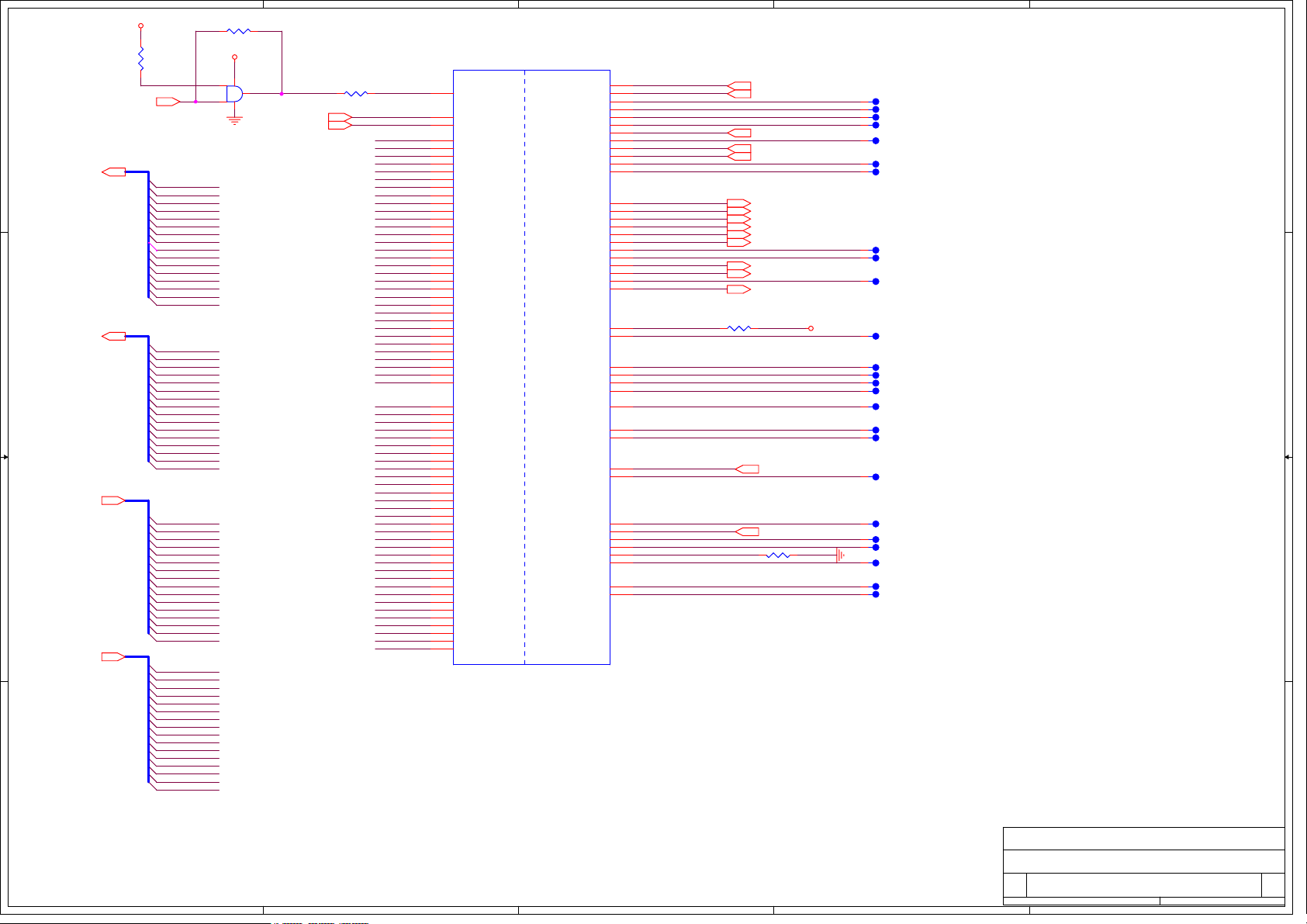

Crestline (HOST) 1/7

Crestline (DMI) 2/7

Crestline (GRAPHIC) 3/7

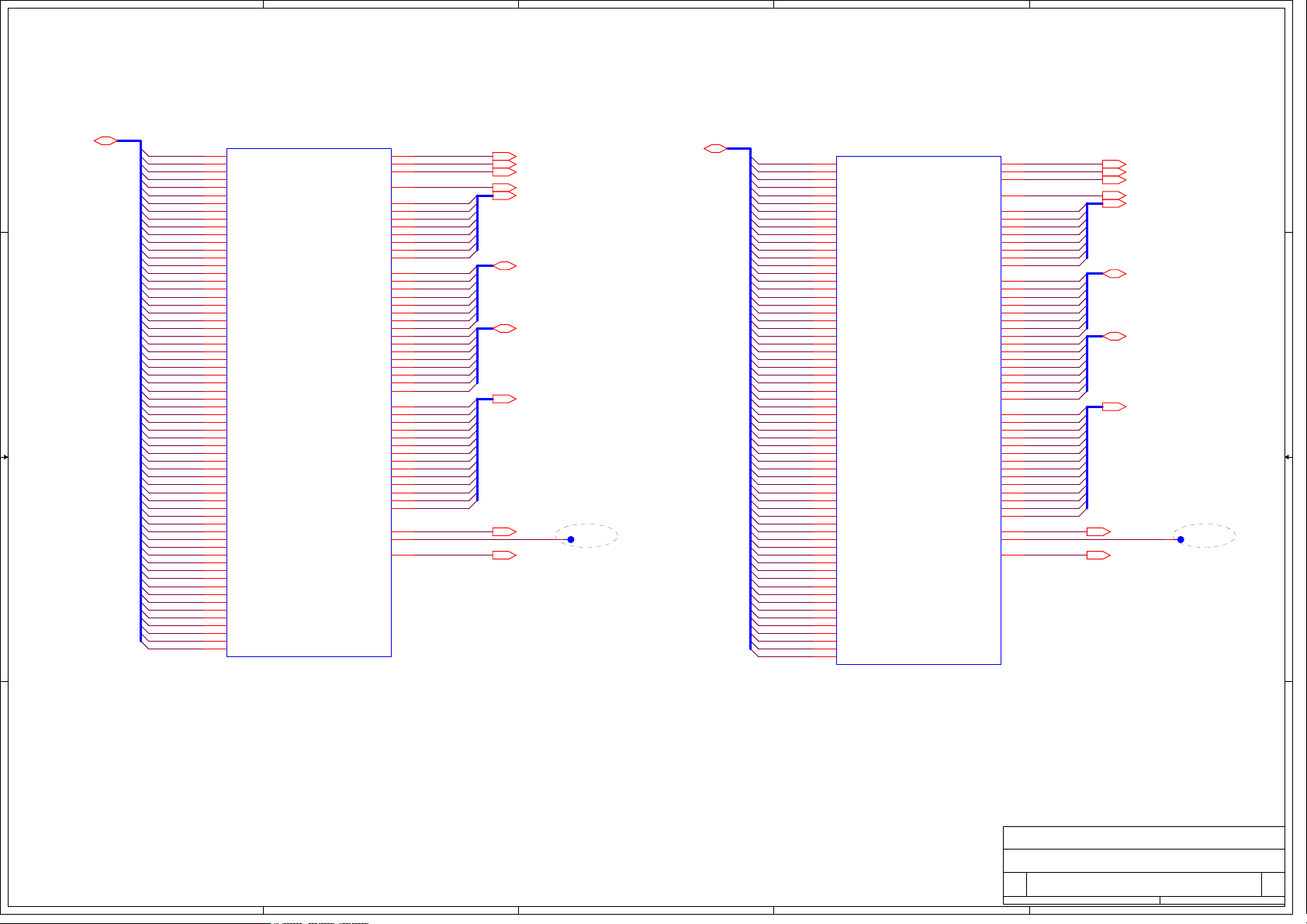

Crestline (DDRII) 4/7

Crestline (POWER,VCC) 5/7

Crestline (VCC CORE) 6/7

Crestline (VSS) 7/7

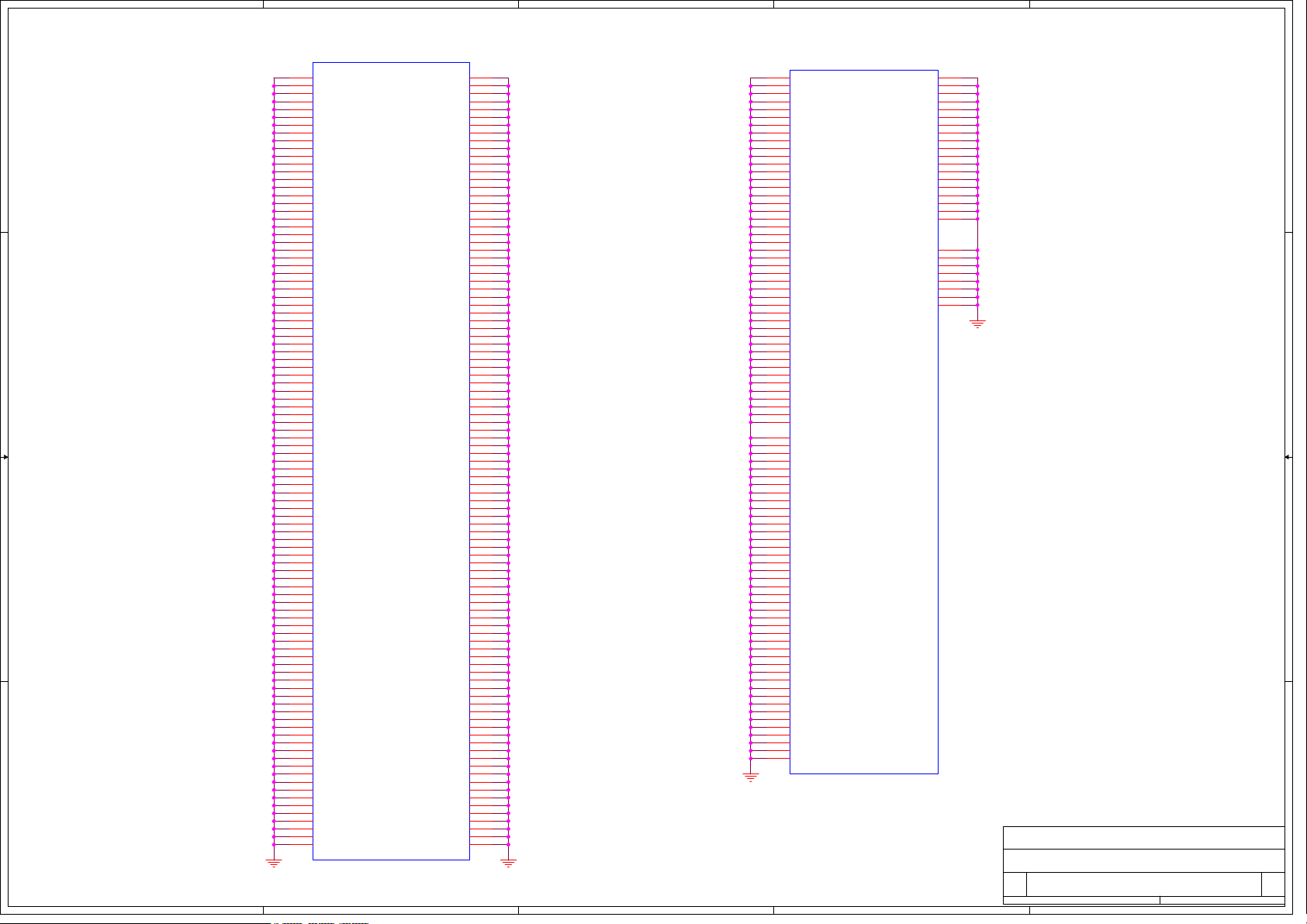

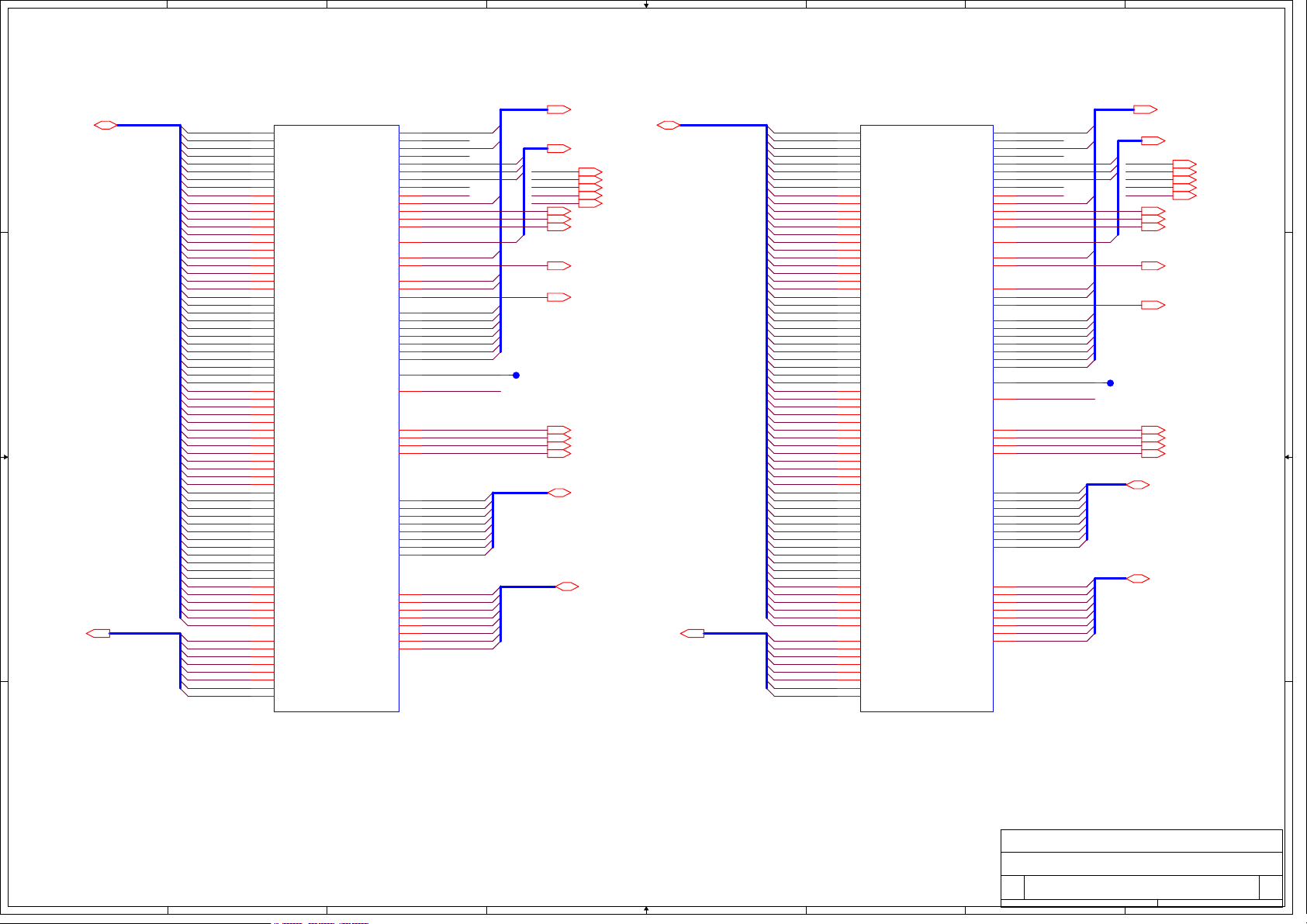

DDRII(SO-DIMM_0) 1/3

DDRII(SO-DIMM_1) 2/3

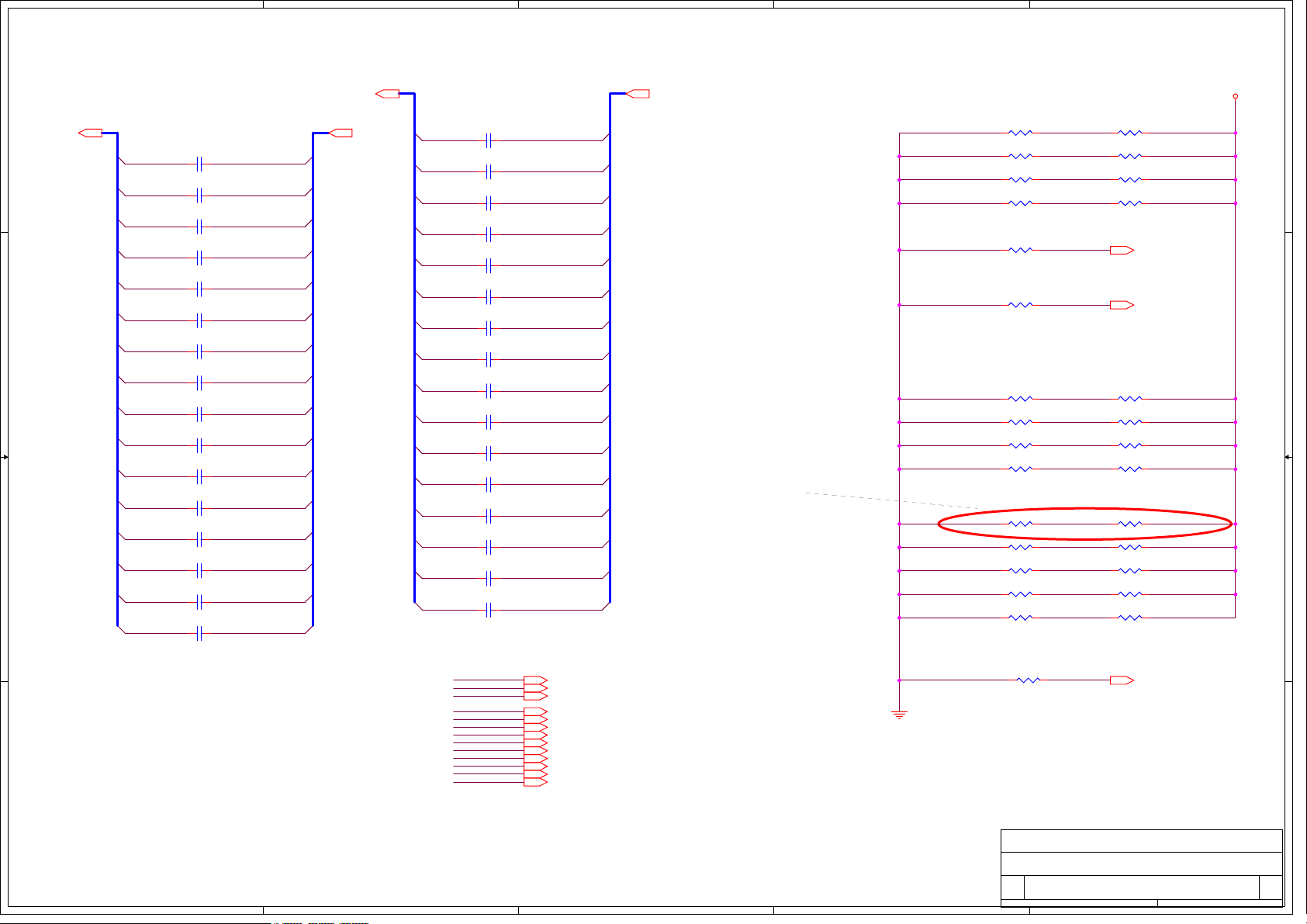

DDRII(Termination) 3/3

VGA(PCI-E)

VGA(STRAP)

VGA(GDDR)

VGA(MULTIUSE)

VGA(LVD/VDAC )

VRAM(GDDR)# 1/4

VRAM(GDDR)# 2/4

VRAM(GDDR)# 3/4

VRAM(GDDR)# 4/4

VGA(POWER) 1/3

VGA(POWER) 2/3

VGA(POWER) 3/3

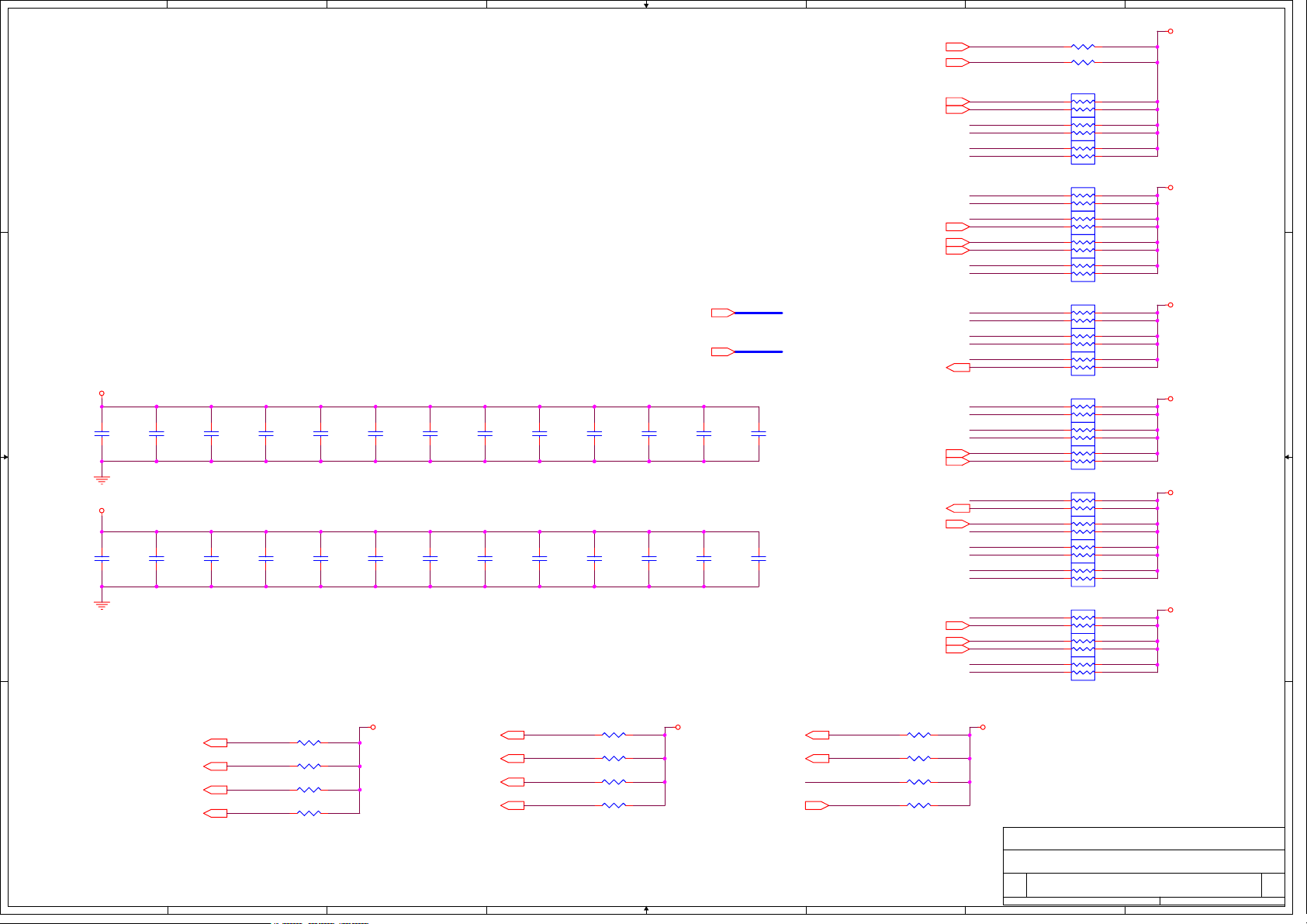

VRAM(BYPASS) 1/4

VRAM(BYPASS) 2/4

VRAM(BYPASS) 3/4

VRAM(BYPASS) 4/4

TVIN and OUT/Semi-PnP#

CRT

LVDS

HDMI

MINI PCI (TV)

ICH8-M( PCI/USB ) 1/5

ICH8-M(LPC,IDE,SATA)2/5

ICH8-M( GPIO) 3/5

Rev.

1.0

1.0

1.0

2.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

Date

2007/8/24

2007/8/24

2007/8/24

2007/8/30

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

Page

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

ICH8-M( POWER) 4/5

ICH8-M( GND) 5/5

LAN (88E8055 MARVELL)

EC+KBC (3910)

Flash ROM/XBUS

SATA HDD RAID

PATA CD-ROM

PCI (PCI BUS)

PCI ( ILINK)

PCI (MS-STD/DUO/MDC/SD)

PCI ( PCMCIA)

Bluetooth

Mini-PCIE Card

EXPRESS

USB2.0

CIR Reciver

FAN / HW THERMAL PROTECTION

Daughter Board Conn.

CAM/OIDE

Logo LED

AUDIO(CODEC & POWER)

AUDIO( AMP & HP & SPK)

AUDIO (MUTE & INTMIC)

AUDIO (Second Codec)

Audio BOARD conn

Power Design Diagram

DCIN&Charger

SYS Power (+3_3V/+5V)

SYS Power(+1_5V/+1_05V)

DDR2 Power(+1_8V/+0_9V)

CPU_Vcore ---MAX8771

Others power plan

OVP protection

VGA POWER(+1_1V/ +1_2V)

Inverter Boost Circuit

HOLE & BOSS

HISTORY(DVT)

1.0

1.0

1.0

2.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

2.0

1.0

1.0

1.0

1.0

DateRev.Title of Schematics Page

2007/8/24

2007/8/24

2007/8/24

2007/8/30

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/24

2007/8/30

2007/8/24

2007/8/24

2007/8/24

2007/8/24

Design byP. Leader Check by

A A

Project Code & Schematics Subject:

5

PCB P/N:M612 PVT Main Board

黃田

翰宇博德

4

3

2

FOXCONN

Title

Index Page

Size Document Number Rev

(M612-1-01 )MainBoard (MBX-176) 2007.8.24

A3

Date: Sheet

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

181Friday, August 31, 2007

1

of

1.0

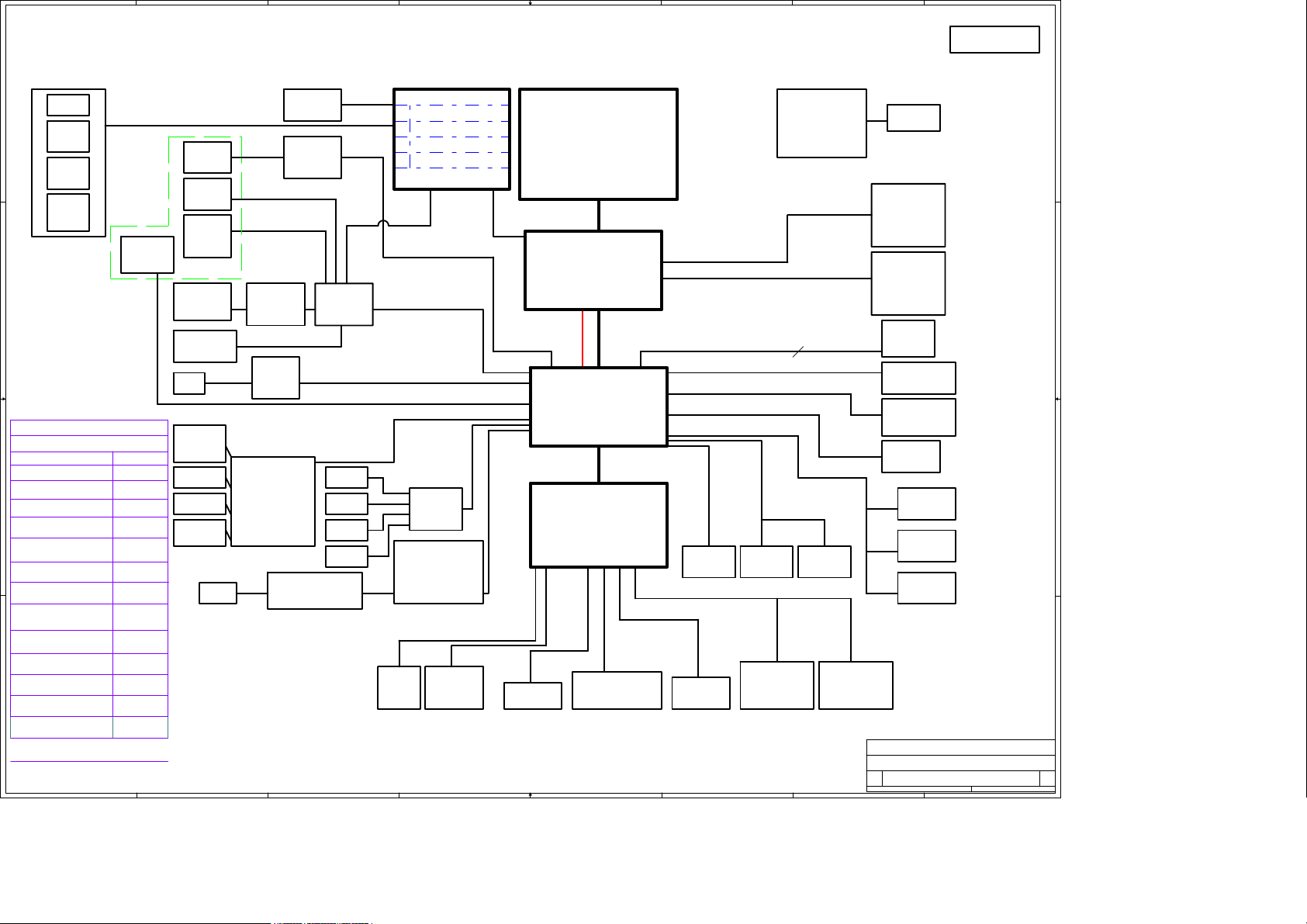

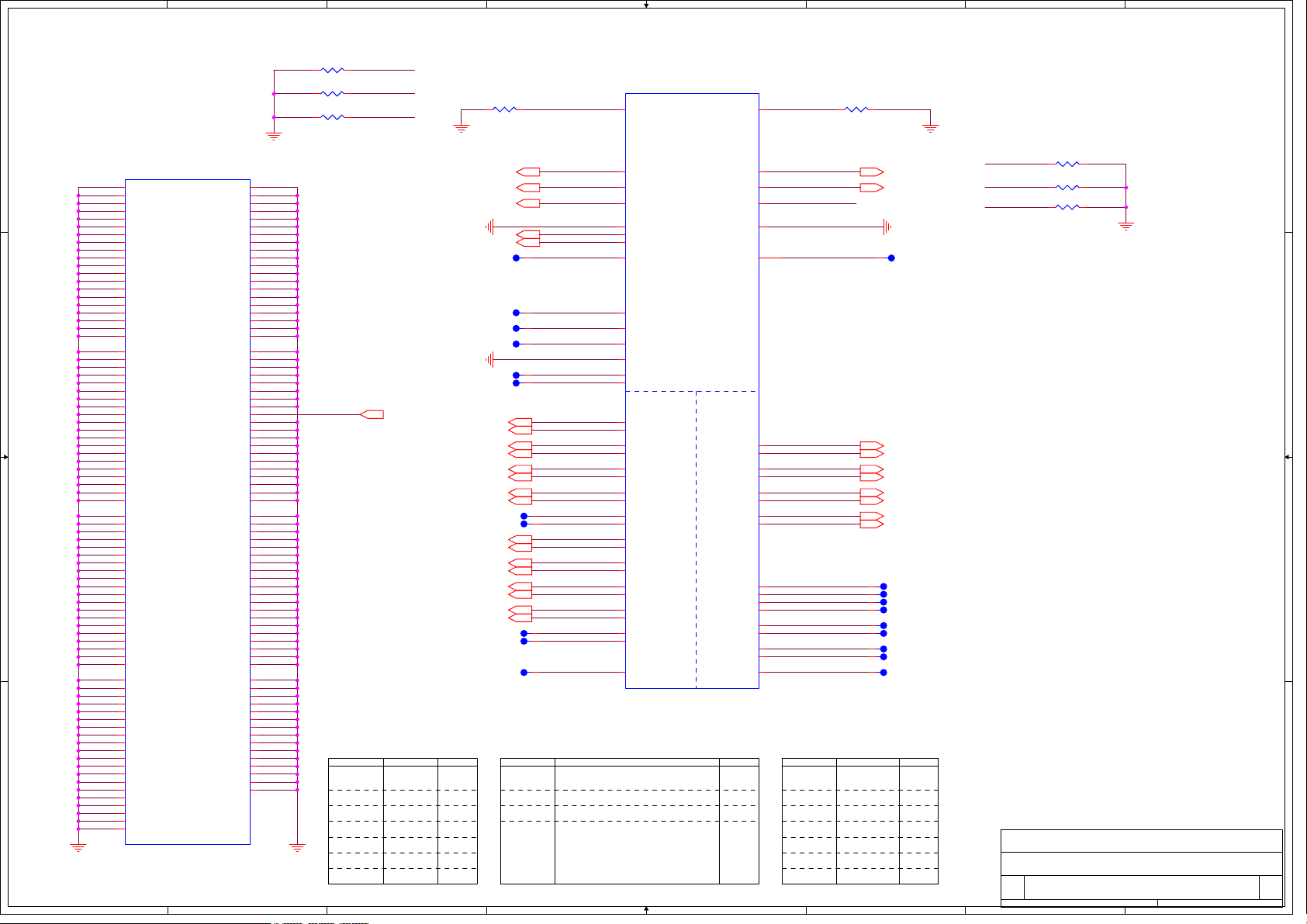

Page 2

1

M612(Beagle Santa Rosa )Block Diagram

2

3

4

5

6

7

8

Red texts:

New modified

A A

B B

S-OUT

PAGE 29

LVDS

WSXGA+

PAGE 31

VGA

D-type-15p

PAGE 30

HDMI

(HDCP)

PAGE 32

Audio

Daughter

Board

USB 2.0

CONN

Audio board

S-OUT/LVDS/VGA/HDMI

SPDIF

Audio board

Ext. Mic In

Jack

Audio board

HEAD

PHONE

JACK

Audio board

Int. Speaker

1.0 Walt x 2

PAGE 58

Int. Microphone

PAGE 59

RJ11

SPDIF

APA2068KAI-TRL

PAGE 58

MDC 1.5

Modem

12 pin

PAGE 46

EEPROM

HDMI A KEY

ACL262

CODEC

PAGE 60

CXD9872AKD

CODEC

PAGE 57

ANPEC

GFX

nVIDIA

H

NB8P-GS(HDMI)

M

NB8M-GT(HDMI)

L NB8M-GT(HDMI)

GDDR3 1.8V SDRAM

PAGE 17~31

SPDIF

for

HDMI

AZALIA

AZALIA

AZALIA

USB2.0

33MHZ, 3.3V PCI BUS

M611 BOM configuration

unstuff

NB8P-GS + NB8M-GT

NB8P-GS

NB8M-GT

C C

NB8M-GT

NB8M-GT for L Model

NB8X + Hynix VRAM

NB8M+16Mx32 VRAM

NB8P + 16Mx32bit VRAM

NB8M + 8Mx32bit VRAM

NB8X + Infineon VRAM

NB8X +

Infineon & Samsung VRAM

NB8X +

Hynix & Infineon VRAM

D D

NB8X + 16Mx32bit VRAM

NB8X + 8Mx32bit VRAM

*JP Digital TV Tuner SKU

unstuff

Mini PCI CONN,BT CONN,

IR CONN,FeliCa CONN

unstuff for L Model

NC_

NV_

NV8P_

NV8M_

NV8MM_

NV8ML_

NVH_

NVNEW

NVNOR

NVNOR

NVI_

NVIS_

NVHS_

NV16_

NV8_

JDTVNC_

LNC_

1

PCMCIA

Conn.

PAGE 47

MS DUO

PAGE 46

SD Mini P C I

PAGE 46

i.LINK

PAGE 45

RJ45

PAGE 39

TI PCI8412ZHK

CardBus

CardReader

i.LINK

PAGE 44~47

Transformer

Netswap,

NS682403P,

Mini stereo

PAGE 29

B-CAS

PAGE 33

S-IN

PAGE 29

F/PAL

PAGE 39

JP Digital only

Ethernet G-LAN

88E8055

MARVELL

10/100/1000

(TV)

PAGE 33

PAGE 39

PWM

FAN Lid Switch

PAGE 53

2

3

& LED

PAGE 54 PAGE 54 PAGE 41

4

CPU

Merom

Processor

Micro-FCBGA-478

(Socket 478 -pin Micro FCPGA)

PCIE X16

PAGE 4~6

North Bridge

Crestline

FCBGA-1299pin

PAGE 7~13

Controller

Link0

South Bridge

ICH8M / ICH8M-E

BGA_652pin

SKU(H):Enhanced

SKU(M)(L):Base

PAGE 34~38

LCI

PCIE

ENE KB3910SFC1

LQFP-176

Touchpad

PS/2

Flash BIOS

1MB

5

FSB

800 MHZ

X2/X4 DMI

(Direct Media Interface)

LPC

SMB Channel 1

SMB Channel 2

ISA

IDE ATA 100

PATA

ODD

PAGE 43

BATT CONN.

PAGE 63

USB2.0

PCIE + USB2.0

PCIE

USB2.0

USB2.0

SATA 3Gb/s

SATA

HDD -RAID0

PAGE 42

Thermal Sensor

F75384M

(CPU/GMCH)

uSOP-8

PAGE 4

6

Clock Gen.

CK505

ICS,ICS9LPR358YGLFT

PAGE 3

2

SATA

HDD -RAID1

PAGE 42

Thermal Sensor

F75383M

(VGA/DIMM)

uSOP8

PAGE 20

X,TAL

14.318MHZ

256MB/512MB/1GMB/2GMB

SO-DIMM 0

667 MHZ

DDR(II)

200 pin

PAGE 14

SO-DIMM 1

667 MHZ

DDR(II)

200 pin

PAGE 15

USB 2.0

CONN.X2

PAGE 51

Express Card

PAGE 50

Mini-Card

PCIE

PAGE 49

CAM(1.3M)

PAGE 50

Bluetooth

USB2.0

PAGE 48

Oide

USB2.0

PAGE 50PAGE 40

IR Reciver

USB2.0

PAGE 52

FOXCONN

Title

Block Diagram

Size Document Number Rev

(M612-1-01 )MainBoard (MBX-176) 2007.8.24 1.0

C

Date: Sheet

7

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Divisio n

281Friday, August 31, 2007

of

8

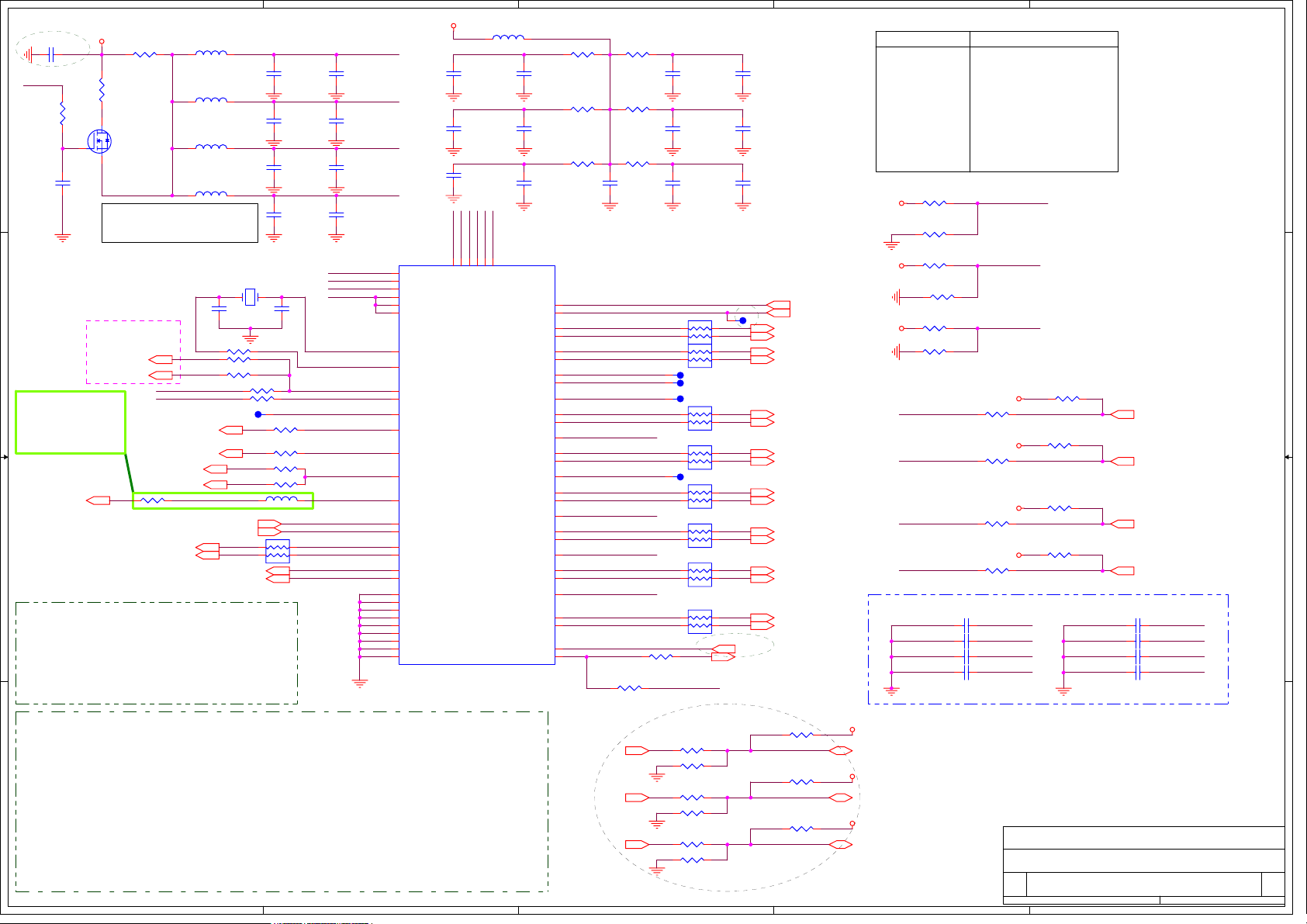

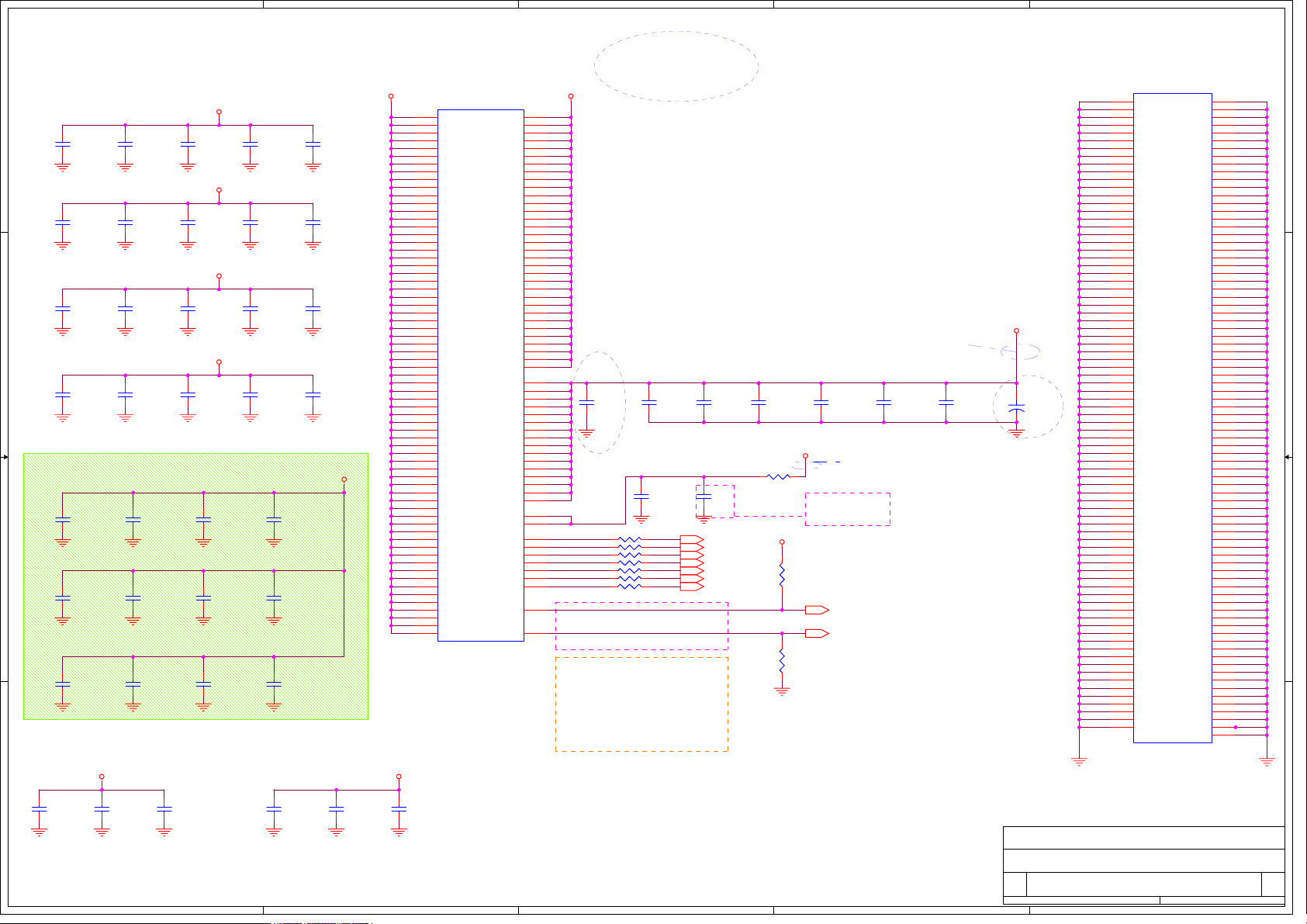

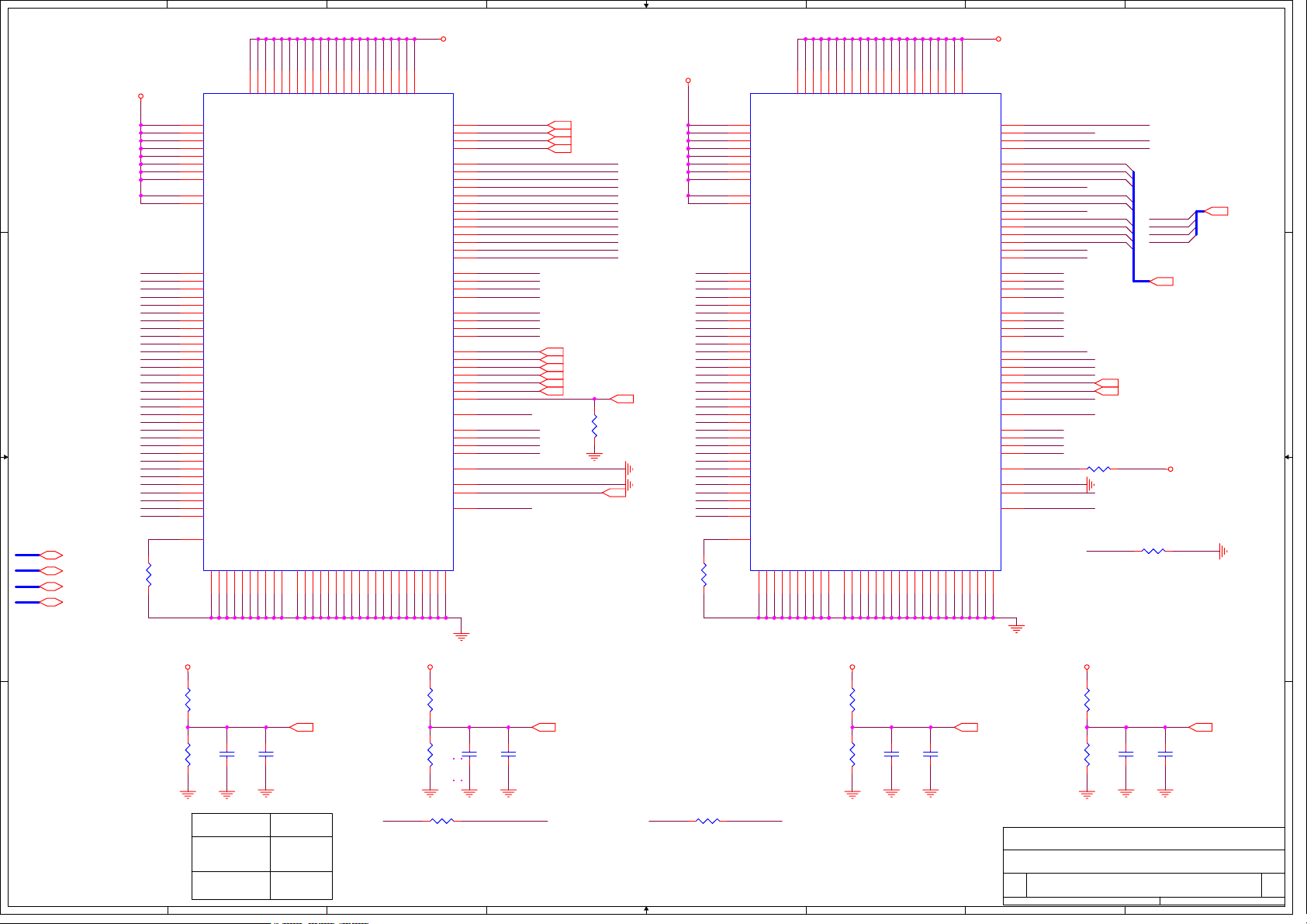

Page 3

11/2 backup

for EMI request

close to R46

NC_0.1U_10V_K

0402_X5R

CKG_IO_VOUT

D D

C C

This dumping resistor

and FB should be

placed close to U18,

update for MOR

requirement on12/23.

B B

33 MHz Port

PCI0 (pin1)

PCI1 (pin3)

PCI2 (pin4)

PCI3 (pin5)

PCI4 (pin6)

PCI5-F (pin7)

100 MHz Port

SRC0 (pin13,14)

SRC1 (pin17,18)

SRC2 (pin21,22)

SRC3 (pin24,25)

SRC4 (pin27,28)

A A

SRC6(pin40,41)

SRC7(pin43,44)

SRC8(pin46,47)

SRC9(pin30,31)

SRC10(pin34,35)

SRC11(pin32,33)

+1_25VRUN

C1941

12

R1023

NC_33_J

0402

1 2

1

G

12

0402

C928

NC_100P_50V_K_N

Length as short

as possible.

PCLK_MINI37

5

HCB2012KF-121T30

33P_50V_J_N

CPU_BSEL0

CLK_ICHPCI38

PCLK_CB48

CLK_KBCPCI44

PCLK_JIG45

0402

L6 120R-100MHZ_0805

HCB2012KF-121T30

L10 120R-100MHZ_0805

HCB2012KF-121T30

L15 120R-100MHZ_0805

HCB2012KF-121T30

L13 120R-100MHZ_0805

A0501

C80

R1055 0_J 0402

R59 12.1_F 0402

R62 12.1_F 0402

TP943 26MIL

R_PCLK_MINI

SMB_CLK_SUS14,15,40,54

SMB_DATA_SUS14,15,40,54

R_SRCT1_27M_NON20

R_SRCC1_27M_SS20

R46 0_J 0805

1 2

R47

NC_10_J

0603

1 2

32

D

Q23

NC_BSS138

S

If 9LP505, populate R47,R1023,C928,Q23

and depopulate R46.

Ig 9LP501, populate R46 and depopulate

R47,R1023,C928,Q23.

CLK_CB4848

CLK_USB4840

R71 100_J

1 2

CLK_PCIE_ICH#38

CLK_PCIE_ICH38

M610

NC

NC

Debug card/EC(KBC)

PCI8402

TV tuner

ICH8

M610 setting configuration

GFX PCIE_PEG

(SRC0 /SRC1 only either one)

PCIE SATA

PCIE ICH8

PCIE MINI

PCIE G-LAN

NC

NC

MCH 3GPLL

PCIE EXPRESS

CR#G(MCH)/CR#H(EXPRESS)

5

12

C151

0.1U_16V_Y_Y

0402

12

C135

0.1U_16V_Y_Y

0402

12

C155

0.1U_16V_Y_Y

0402

12

C149

0.1U_16V_Y_Y

0402

Y1

ITTI_L5030-14.31818-20

14.318MHZ_20P_30PPM

1 2

12

0402

1 2

1 2

1 2

R65 2.2K_J 0402

R74 0_J 0402

33

RP6

0404_4P2R

MS90

NC

NC

Debug card

PCI8402

EC(KBC)

ICH8

12

C81

33P_50V_J_N

0402

1 2

1 2

1

R72 22_F 0402

1 2

R68 22_F 0402

1 2

R2203 12.1_F 0402

1 2

R2204 12.1_F 0402

1 2

L150

MMZ1005D241CT

240R-100MHZ_0402

2 3

1

S/W Setting this pin type

(B2b0=0) for use SRC0

(B4b7=1;B5b3=0,B5b1=0) for use SRC3

(B2b1=0) for use SRC4

12

12

12

12

V1P0B

V1P0D

V1P0C

V1P0S

U2_XTALIN

U2_XTALOUT

R_FSLA_USB48M

R_FSLB_TEST_MODECPU_BSEL1

CKG_IO_VOUT

R_PCI_F5_ITP_EN

R_PCI3

R_PCI2_TME

R_PCI4_27M_SEL

R_CLK_PCIE_ICH#

R_CLK_PCIE_ICH

4

R_SRCT1_27M_NON

R_SRCC1_27M_SS

C87

10U_6.3V_M

0805_X5R

C96

10U_6.3V_M

0805_X5R

C97

10U_6.3V_M

0805_X5R

C150

10U_6.3V_M

0805_X5R

(B3b3=1,B6b7=0,B6b6=0) for use SRC7(not control CR#E/F)

(B3b7=0,B3b6=0 for use CLKREQ G,H)

4

+3VRUN

V1P0B

V1P0D

V1P0C

V1P0S

12

49

20

45

36

26

60

59

10

57

48

7

5

4

6

64

63

25

24

17

18

15

19

23

29

42

11

52

8

58

U18

VDD96_IO

VDDCPU_IO

VDDPLL3_IO

VDDSRC_IO3

VDDSRC_IO2

VDDSRC_IO1

X1

X2

FSLA/USB_48MHZ

FSLB/TEST_MODE

NC

PCI_F5/ITP_EN

PCI3

PCI2/TME

PCI4/27_Select

SCLK

SDATA

SRCC3/CR#_D

SRCT3/CR#_C

SRCT1/SE1/27MHZ_nonss

SRCC1/SE2/27MHZ_SS

GND1

GND2

GNDSRC1

GNDSRC2

GNDSRC3

GND48

GNDCPU

GNDPCI

GNDREF

ICS9LPR358YGLFT

12

12

12

+3V_CLK_3F

55

S/W Setting CLKREQ for this pin

CR#A (B5b7=1;B5b6=1)

CR#B (B5b5=1,B5b4=1)

CR#E (not control)

CR#F (not control)

CR#G (B6b5=1)

CR#H (B6b4=1)

4

HCB2012KF-121T30

L17 120R-100MHZ_0805

+3V_CLK_3D

C43

0.01U_16V_K_B

0402

+3V_CLK_3E

C44

0.01U_16V_K_B

0402

+3V_CLK_3F

C45

0.01U_16V_K_B

0402

+3V_CLK_3D

+3V_CLK_3C

+3V_CLK_3A

+3V_CLK_3E

+3V_CLK_3B

2

9

16

61

39

VDD48

VDDPCI

VDDREF

VDDCPU

VDDSRC

VDDPLL3

PCI_STOP#

CPU_STOP#

CPUT1_F

CPUC1_F

SRCT8/CPUT2_ITP

SRCC8/CPUC2_ITP

SRCT7/CR#_F

SRCC11/CR#_G

SRCC7/CR#_E

PCI1/CR#_B

SRCT11/CR#_H

SRCT2/SATAT

SRCC2/SATAC

PCI0/CR#_A

SRCT0/DOTT_96

SRCC0/DOTC_96

CK_PWRGD/PD#

FSLC/REF0/TEST_SEL

SM bus Address :

1101001 (ICH7)

For clock generator

12

C782

1U_25V_K_B

0603

12

C784

1U_25V_K_B

0603

12

C781

1U_25V_K_B

0603

CPUT0

CPUC0

SRCT9

SRCC9

SRCT6

SRCC6

SRCT4

SRCC4

SRCC10

SRCT10

R39

1_F 0402

1 2

R42

1_F 0402

1 2

R43

1_F 0402

1 2

38

37

51

50

54

53

47

46

44

30

31

32

41

40

43

27

28

3

35

34

33

21

22

1

13

14

56

62

12

R_CLK_MCH_BCLK

R_CLK_MCH_BCLK#

R_CLK_CPU_BCLK

R_CLK_CPU_BCLK#

R_SRC8_CPU2ITP

R_SRC8#_CPU2#ITP

R_SRCT7_CR#_F

R_CLK_MCH_3GPLL

R_CLK_MCH_3GPLL#

R_SRCC11_CR#_G

R_SRC6

R_SRC6#

R_SRCC7_CR#_E

R_CLK_PCIE_MINI

R_CLK_PCIE_MINI#

R_PCI1_CR#_B

R_CLK_PCIE_EXP#

R_CLK_PCIE_EXP

R_SRCT11_CR#_H

R_CLK_PCIE_SATA

R_CLK_PCIE_SATA#

R_PCI0_CR#_A

DOT96_OR_SRC0

DOT96#_OR_SRC0#

R_CLK_ICH14

1 2

R2190 10K_J 0402

CPU_BSEL05

CPU_BSEL15

CPU_BSEL25

3

R41

1_F 0402

1 2

R44

1_F 0402

1 2

R45

1_F 0402

1 2

C83

10U_6.3V_M

0805_X5R

RP1

RP2

RP4

RP104

RP7

RP8

RP5

RP9

1 2

R79 33_F 0402

CPU_BSEL2

R83

R91

R86

R2121

R89

R2123

3

+3V_CLK_3A

12

C46

0.01U_16V_K_B

0402

+3V_CLK_3B

12

C47

0.01U_16V_K_B

0402

+3V_CLK_3C

12

C48

0.01U_16V_K_B

0402

4

4

1

TP997 26MIL

1

TP998 26MIL

1

TP999 26MIL

4

4

1

TP1000 26MIL

4

1

2 3

4

4

0_J 0402

1 2

1 2

NC_1K_J 0402

0_J 0402

1 2

1 2

NC_1K_J 0402

0_J 0402

1 2

1 2

NC_1K_J 0402

12

C785

1U_25V_K_B

0603

12

C783

1U_25V_K_B

0603

12

C786

1U_25V_K_B

0603

TP737

1

26MIL

23

1

330404_4P2R

23

1

330404_4P2R

1

23

330404_4P2R

23

1

330404_4P2R

1

23

330404_4P2R

4

330404_4P2R

1

23

330404_4P2R

1

23

330404_4P2R

CLK_EN 40

CLK_ICH14 40

Connect this pin via a 10 K

series resistor to the FSC

pin on the processor

Connect this pin via a 2.2 K

series resistor to the FSA

pin on the processor,

R2119

R2120

R2122

PM_STPPCI# 40

STP_CPU# 40

2007/1/1 Roger request

CLK_MCH_BCLK 7

CLK_MCH_BCLK# 7

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_3GPLL 8

CLK_MCH_3GPLL# 8

CLK_PCIE_GLAN 43

CLK_PCIE_GLAN# 43

CLK_PCIE_MINI 53

CLK_PCIE_MINI# 53

CLK_PCIE_EXPRESS# 54

CLK_PCIE_EXPRESS 54

CLK_PCIE_SATA 39

CLK_PCIE_SATA# 39

CLK_PCIE_PEG 17

CLK_PCIE_PEG# 17

1 2

NC_1K_J 0402

1 2

NC_1K_J 0402

1 2

NC_1K_J 0402

+1_05VRUN

MCH_BSEL0 8

+1_05VRUN

MCH_BSEL1 8

+1_05VRUN

MCH_BSEL2 8

2

FSB Frequency Table:

FSLC FSLB FSLA CPU SRC[7:0] PCI FSB

1 0 1 100 100 33 /

0 0 1 133 100 33

0 1 1 166 100 33 667

0 1 0 200 100 33 800

0 0 0 266 100 33

1 0 0 333 100 33

1 1 0 400 100 33

1 1 1 (Reserced)

R2113 NC_10K_J0402

1 2

+3VRUN

R2103 NC_10K_J 0402

1 2

R2104 10K_J 0402

1 2

+3VRUN

R2285 NC_10K_J 0402

1 2

R2105 10K_J 0402

1 2

+3VRUN

R2106 NC_10K_J 0402

1 2

R_PCI0_CR#_A

R_PCI1_CR#_B

R_SRCC11_CR#_G

R_SRCT11_CR#_H

Check List 1.301

*.CFG[2:0] do not have internal pullups or pull downs.

Please refer to the latest Crestline EDS volume 1 for

configuration options

*.1 k pull-up or pull-down or direct connect from processor.

MS90

only MCH_BSEL[0..2]pull down 1K

2

R_PCI_F5_ITP_EN

R_PCI2_TME

R_PCI2_TME

R_PCI4_27M_SEL

+3VRUN

475_F 0402

1 2

R2108

+3VRUN

475_F 0402

1 2

R2110

+3VRUN

475_F 0402

1 2

R2116

+3VRUN

475_F 0402

1 2

R2118

close to terminal side (For EMI)

CLK_CB48

12

C1839NC_10P_50V_E_N 0402

CLK_USB48

12

C1841NC_10P_50V_E_N 0402

CLK_KBCPCI

12

C1843NC_10P_50V_E_N 0402

PCLK_CB

12

C1845NC_10P_50V_E_N 0402

FOXCONN

Title

Size Document Number Rev

A3

Date: Sheet

pin7 setting 0=SRC8,1=ITP for pin 46,47

pin4 setting 0= Overclocking of CPU and SRC Allowed

1= Overclock i ng o f C P U a n d S R C N O T al l o w e d

pin6 setting 0= LCD_SST 100MHz differential clock.

for pin17,18 1= 27MHz non-spread SE clock,

R2107 10K_J 0402

1 2

R2109 10K_J 0402

1 2

R2115 10K_J 0402

1 2

R2117 10K_J 0402

1 2

CLOCK GEN(CK505)

(M610-1-01 )MainBoard (MBX-176) 2007.1.4 2.0

1

/

/

/

/

SATACLKREQ# 40

MINI_CARD_DET# 53

MCH_CLK_REQ# 8

EXPRESS_DET# 54

PCLK_MINI

12

C1840NC_10P_50V_E_N 0402

CLK_ICHPCI

12

C1842NC_10P_50V_E_N 0402

CLK_ICH14

12

C1844NC_10P_50V_E_N 0402

PCLK_JIG

12

C1846NC_10P_50V_E_N 0402

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

1

of

381Friday, August 31, 2007

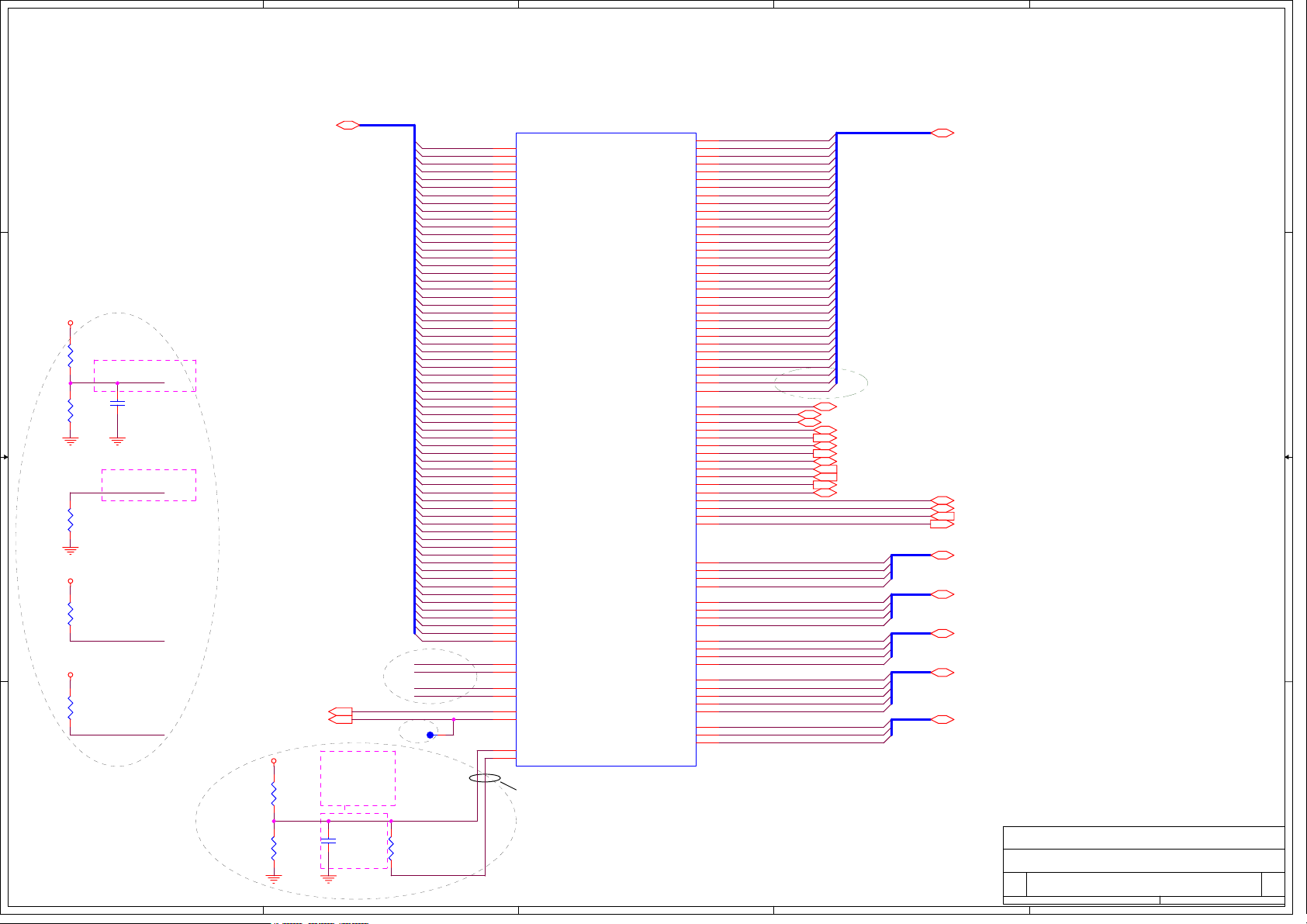

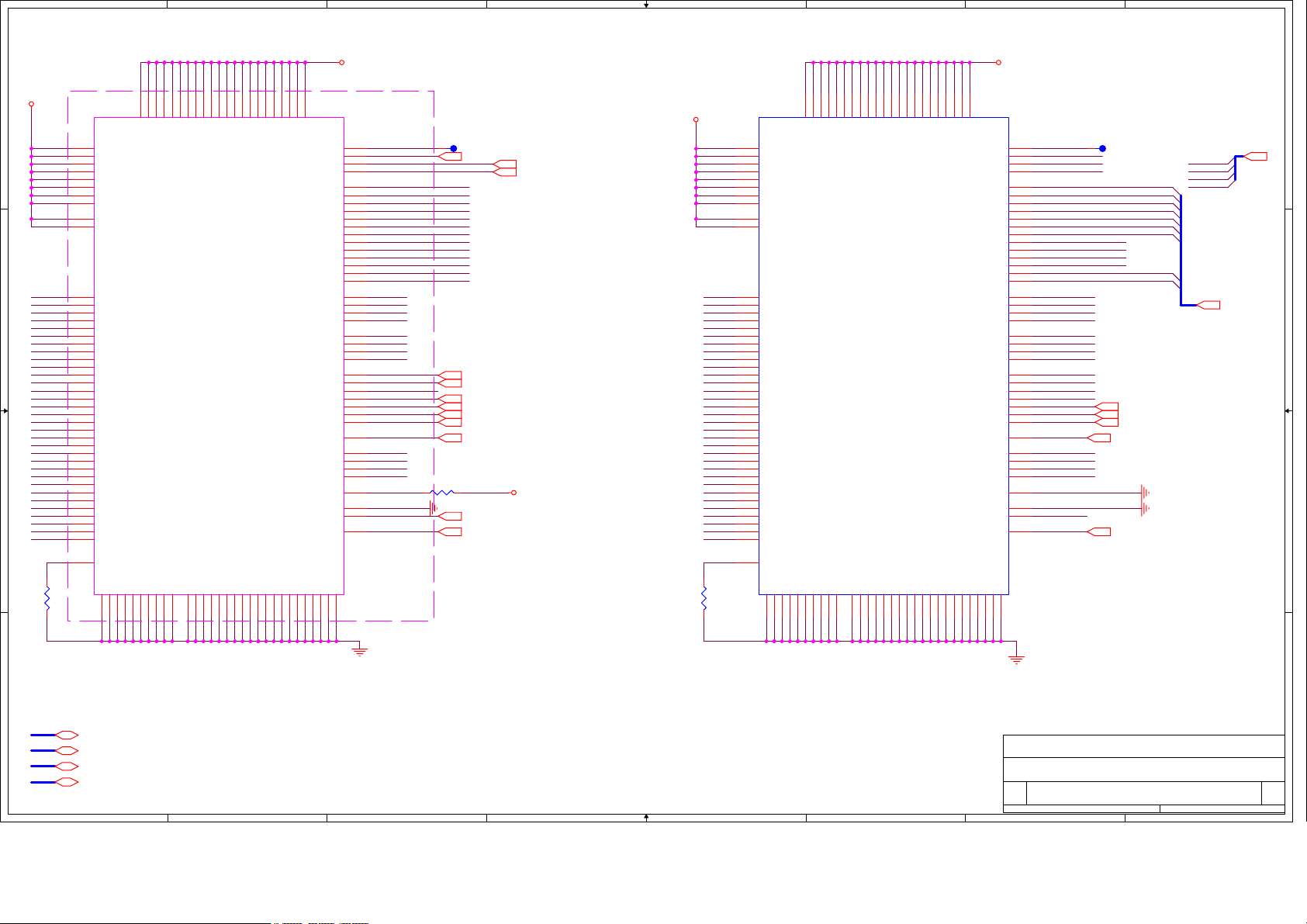

Page 4

5

H_A#[35..3]7

D D

H_ADSTB#07

H_REQ#[4..0]7

Layout note:

no stub on H_STPCLK TP.

H_STPCLK# to be routed in daisy

chain fashion from ICH to LPC slot

and then to CPU.

+1_05VRUN

12

32

D

G

S

2N7002

Add H_A#[32..35]

TP7 26MIL

TP8 26MIL

TP10 26MIL

TP11 26MIL

TP12 26MIL

TP14 26MIL

TP16 26MIL

TP18 26MIL

TP20 26MIL

TP22 26MIL

PROCHOT#

Q70

C C

H_ADSTB#17

H_A20M#39

H_FERR#39

H_IGNNE#39

H_STPCLK#39

H_INTR39

H_NMI39

H_SMI#39

B B

+3VRUN

Q71

OVT_EC#

A A

B

2

12

R1118

2.2K_J

0402

A0205

C

E

DTC144EUA

1 3

5

R1117

68_J

0402

1

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

TP_CPU_RSVD01

1

TP_CPU_RSVD02

1

TP_CPU_RSVD03

1

TP_CPU_RSVD04

1

TP_CPU_RSVD05

1

TP_CPU_RSVD06

1

TP_CPU_RSVD07

1

TP_CPU_RSVD08

1

TP_CPU_RSVD09

1

TP_CPU_RSVD10

1

Base on BRC change net name

NC_S-80927CLMC-G6XT2G_3.1

1 2

4

4

CD1

C1904

NC_470P_50V_K_B

0402

NC

5

CD

4

U1A

J4

0

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

1

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

CPU SOCKET_478P

FOX_PZ4782A-274M-01

+ECVCC

23

U154

VDDVSS

OUT

ADDR GROUP

BPRI#

DEFER#

DRDY#

DBSY#

IERR#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

ADDR GROUP

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

XDP/ITP SIGNALS

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

THERMTRIP#

H CLK

BCLK[0]

BCLK[1]

RESERVED

1

ADS#

BNR#

BR0#

INIT#

HIT#

TCK

TDI

TDO

TMS

DBR#

+1_05VRUN

H1

E2

G5

H5

F21

E1

F1

H_IERR#

D20

B3

H4

TP721 26MIL

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

XDP_BPM#0

AD4

XDP_BPM#1

AD3

XDP_BPM#2

AD1

XDP_BPM#3

AC4

XDP_BPM#4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

XDP_TDO

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

A0206

C20

PROCHOT#

D21

H_THERMDA

A24

H_THERMDC

B25

PM_THRMTRIP#

C7

A22

A21

R2243

NC_0_J 0402

PLT_RST#8,17,38,43,44,45,47,51,53,54

R1537

1 2

2.2K_J

0402

PM_THRMTRIP#

3

2007/1/1

TP736

1

12

Roger request

26MIL

1

1

1

1

1

1

1

1

ICH8M's GPIO12: VIL---> -0.5V ~ 0.8V

VIH---> 2.0V ~ 3.3+0.5V

MEROM's PROCHOT#: VIL---> -0.1V ~ 0.3*VCCP

VIH---> 0.7*VCCP ~ VCCP+0.1

1

Q4

1

A0203

+ECVCC

G

B

3

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BREQ#0 7

H_INIT# 39

H_LOCK# 7

H_CPURST# 7

H_RS#[2..0] 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

TP126MIL

TP226MIL

TP326MIL

TP426MIL

TP526MIL

TP27626MIL

TP56826MIL

PM_THRMTRIP# 8

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

12

R15

47K_J

0402

32

Q3

D

S

2N7002

A0202

C

E

MMBT3904

2 3

TP72 26MIL

TP71 26MIL

+1_05VRUN

12

R1

56_J

0402

1

2200P_50V_K_B

1

OVT_EC#40,44,71

When using Reset IC solution , C3 & R15

need to change to NC condition

12

C3

0.1U_16V_M_B

0402

Close to CPU side

+1_05VRUN

12

R4

56_J

PM_THRMTRIP#

PM_THRMTRIP#

should connect to

ICH7-M and GMCH

without T-ing (No

stub)

C2

0402

ECRST# 20,44

0402

H_THERMDA

12

H_THERMDC

1 2

R12 0_J0402

2

R_OVT_EC#

2

XDP_TDI

XDP_TMS

XDP_BPM#5

XDP_TCK

XDP_TRST#

Debug port not used .

resistors close to CPU.

1 2

1 2

W/S:10/10 (microstrip)

+3VRUN

12

R1116

4.7K_J

0402

12

C1

0.1U_16V_M_B

0402

U2

1

VDD

SMCLK

2

DP

SMDATA

3

DN

ALERT#

4 5

THERM# GND

EMC1402-2-ACZL-TR

null

SM bus Address :

1001101 = 9A

For F75384M

Place Thermal-Sensor near

CPU & GMCH.

11/16 change part from

F75384M

( 15-F75384M-0000) to

G781-1P8f

(15-G7811P8-0000)

FOXCONN

Title

Merom(HOST BUS)1/3

Size Document Number Rev

(M610-1-01 )MainBoard (MBX-176) 2007.1.4 2.0

A3

Date: Sheet

+1_05VRUN

R2150_J0402

12

R339_D0402

12

R2102NC_54.9_F0402

R527_F0402

R6649_F0402

12

R8

4.7K_J

0402

1 2

8

7

6

Friday, August 31, 2007

1

Beagle1=150R(5%)

CRB1.301=54.9R(1%)

Check 1.201=150R(5%)

MS90 EVT=150R(5%)

Beagle1=39R(5%)

CRB1.301=54.9R(1%)

Check 1.201=39R(1%)

MS90 EVT=39R(0.5%)

Beagle1=--CRB1.301=54.9R(1%)

Check 1.201=--MS90 EVT=NC_54.9(1%)

Beagle1=27R(5%)

CRB1.301=54.9R(1%)

Check 1.201=27R(1%)

MS90 EVT=27R(5%)

Beagle1=680R(5%)

CRB1.301=649R(1%)

Check 1.201=500~680R(5%)

MS90 EVT=649R(1%)

R9

R10

2.2K_J

2.2K_J

0402

1 2

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

0402

1 2

SMB_THRM_CLK 20,44

SMB_THRM_DATA 20,44

PM_THRM# 44

481

1

of

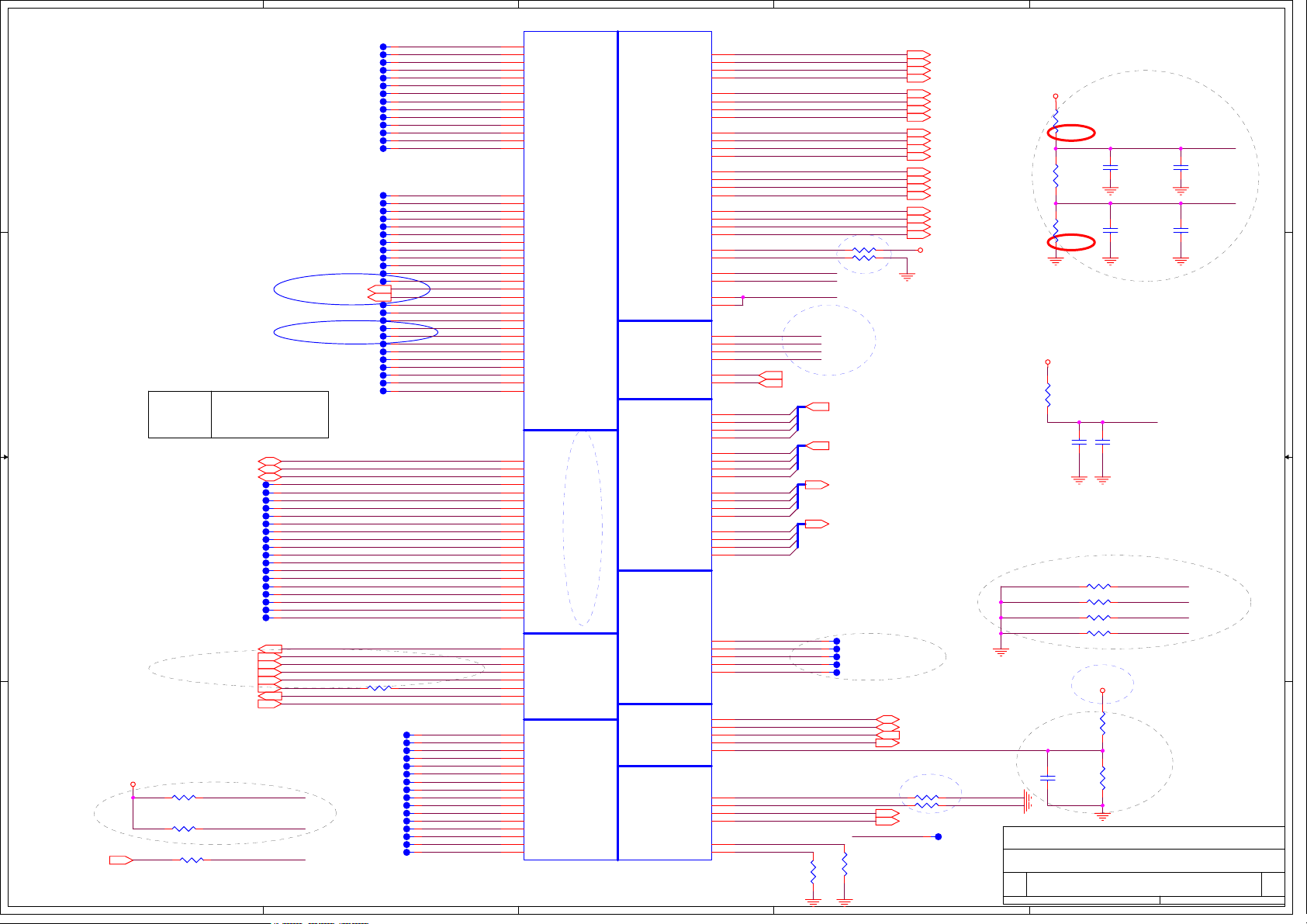

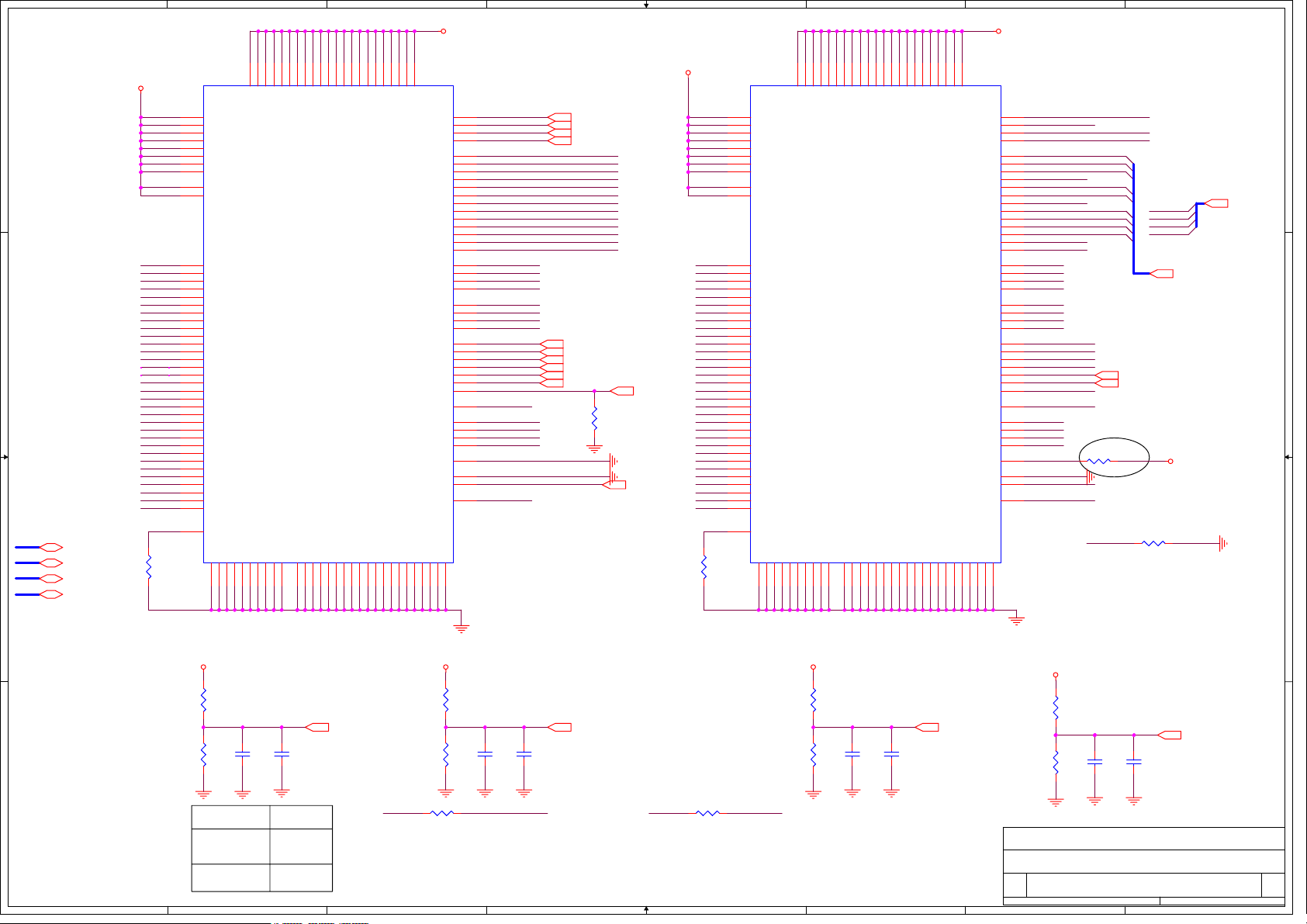

Page 5

5

D D

4

3

2

1

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#[63..0]7

C C

+1_05VRUN

R19

1K_F

0402

1 2

B B

Place close to CPU

11/02

change from 0603 to 0402

R23

2K_F

0402

1 2

Layout Note:

Zo=55 ohm, 0.5"

max for GTLREF.

H_DSTBN#07

H_DSTBP#07

H_DINV#07

5 mil(microstrip)

H_DSTBN#17

H_DSTBP#17

H_DINV#17

Max Length 0.5 inch

12

C1756

0402_X5R

0402

C1610

NC_0.1U_10V_K

CPU_BSEL03

NC_0.1U_16V_M_B

CPU_BSEL13

CPU_BSEL23

R24 NC_1K_J 0402

R26 NC_1K_J 0402

TP940 26MIL

TP941 26MIL

TP942 26MIL

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_GTLREF

CPU_TEST1

12

CPU_TEST2

12

CPU_TEST3

1

CPU_TEST4

12

CPU_TEST5

1

CPU_TEST6

1

U1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

CPU SOCKET_478P

FOX_PZ4782A-274M-01

D[32]#

D[33]#

D[34]#

DATA GRP 0

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

DATA GRP 2DATA GRP 3

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

DATA GRP 1

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

MISC

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Layout Note:

Comp0,2 connect with Zo=27.4 ohm, make

trace length shorter then 0.5".

Comp1,3 connect with Zo=55 ohm, make

trace length shorter then 0.5".

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

R20 27.4_F 0402

COMP0

R21 54.9_F 0402

COMP1

R22 27.4_F 0402

COMP2

R25 54.9_F 0402

COMP3

H_D#32

Y22

12

12

12

12

H_DPRSTP# 8,39,71

H_DPSLP# 39

H_CPUSLP# 7

PSI# 71

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#2 7

H_DSTBN#3 7

H_DSTBP#3 7

H_DINV#3 7

1

H_DPWR# 7

H_PWRGD 39

TP963

1

26MIL

2007/1/1 Roger request

Layout:

Connect test

point with no

stub

TP27 30MIL

A A

FOXCONN

Title

Merom(HOST BUS)2/3

Size Document Number Rev

(M610-1-01 )MainBoard (MBX-176) 2007.1.4 2.0

A3

5

4

3

2

Date: Sheet

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

of

581Friday, August 31, 2007

1

Page 6

5

4

3

2

1

CPU_VCCA---->130mA

CPU_VCCP----->4.5A

VHCORE VHCORE

VHCORE

D D

C C

B B

12

C4

22U_6.3V_M_B

0805

12

C9

22U_6.3V_M_B

0805

12

C14

22U_6.3V_M_B

0805

12

C19

22U_6.3V_M_B

0805

12

C1642

NC_10U_6.3V_M

0805_X5R

12

C1646

NC_10U_6.3V_M

0805_X5R

12

C1650

NC_10U_6.3V_M

0805_X5R

12

C5

22U_6.3V_M_B

0805

12

C10

22U_6.3V_M_B

0805

12

C15

22U_6.3V_M_B

0805

12

C20

22U_6.3V_M_B

0805

12

12

12

C1643

NC_10U_6.3V_M

0805_X5R

C1647

NC_10U_6.3V_M

0805_X5R

C1651

NC_10U_6.3V_M

0805_X5R

12

C6

22U_6.3V_M_B

0805

12

C11

22U_6.3V_M_B

0805

12

C16

22U_6.3V_M_B

0805

12

C21

22U_6.3V_M_B

0805

12

12

12

VHCORE

VHCORE

VHCORE

C1644

NC_10U_6.3V_M

0805_X5R

C1648

NC_10U_6.3V_M

0805_X5R

C1652

NC_10U_6.3V_M

0805_X5R

12

C7

22U_6.3V_M_B

0805

12

C12

22U_6.3V_M_B

0805

12

C17

22U_6.3V_M_B

0805

12

C22

22U_6.3V_M_B

0805

12

12

12

12

C8

22U_6.3V_M_B

0805

12

C13

22U_6.3V_M_B

0805

12

C18

22U_6.3V_M_B

0805

12

C23

22U_6.3V_M_B

0805

C1645

NC_10U_6.3V_M

0805_X5R

C1649

NC_10U_6.3V_M

0805_X5R

C1653

NC_10U_6.3V_M

0805_X5R

VHCORE

U1C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

CPU SOCKET_478P

FOX_PZ4782A-274M-01

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

Backup 10uF capacitors for 22uF shortage.

VHCOREVHCORE

A A

12

C1271

NC_0.1U_16V_M_B

0402

12

C1272

NC_0.1U_16V_M_B

0402

12

C1273

NC_0.1U_16V_M_B

0402

5

12

C1278

1000P_50V_K_B

0402

12

C1279

1000P_50V_K_B

0402

12

C1280

1000P_50V_K_B

0402

4

(Design check 1.301) 2006.9.3

No Stuff 27.4 ± 1% pull-down to GND

near Intel MVP 6 controller for testing purposes.

CPU_VCC------>44A

Beagle1=10U

CRB1.301=NO

Check 1.201=NO

MS90 EVT=NO

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

C24

0.1U_25V_M_B

0603

+1_5VRUN_A_CPU

12

C35

10U_6.3V_M

0805_X5R

3

12

C1554

NC_10U_6.3V_M

0805_X5R

R29 0_J 0402

R30 0_J 0402

R31 0_J 0402

R32 0_J 0402

R33 0_J 0402

R35 0_J 0402

R36 0_J 0402

VCCSENSE

VSSSENSE

Same Length

Layout Note: Route

VCCSENSE traces at 27.4

Ohms with 50 mil spacing.

Place PU and PD within 1

inch of cpu.

width=18 mil

spacing=7 mil

+1_05VRUN

12

C25

0.1U_25V_M_B

0603

12

C36

0.01U_25V_M_B

0402

VID0 71

VID1 71

VID2 71

VID3 71

VID4 71

VID5 71

VID6 71

12

C26

0.1U_25V_M_B

0603

+1_5VRUN

R28

1 2

0_J 0402

VHCORE

12

12

LAYOUT NOTE:

Place 0.01uF

near PIN B26

R34

100_F

0402

R37

100_F

0402

12

C27

0.1U_25V_M_B

0603

20 mil

VCCSENSE 71

VSSSENSE 71

12

C28

0.1U_25V_M_B

0603

2

100 mil

12

C29

0.1U_25V_M_B

0603

CAP7 move from page11

fix PAD location,but change

CAP val from NC_47U to 330U

+1_05VRUN

FOXCONN

Title

Size Document Number Rev

A3

Date: Sheet

MS90 check

CAP26

330U_2V_T

EEFSX0D331ER

12

+

U1D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

P3 A25

VSS[081] VSS[162]

CPU SOCKET_478P

FOX_PZ4782A-274M-01

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF25

Merom(POWER/GND)

(M610-1-01 )MainBoard (MBX-176) 2007.1.4 2.0

1

of

681Friday, August 31, 2007

Page 7

5

4

3

2

1

D D

+1_05VRUN

C C

12

R2094

221_F

0402

W/S = 10/20mil

12

R2095

100_F

0402

H_SWING

C1754

0.1U_16V_M_B

1 2

0402

H_D#[63..0]5

W/S = 10/20mil

12

B B

+1_05VRUN

12

+1_05VRUN

12

Different with 945PM

A A

H_RCOMP

R2096

24.9_F

0402

R2097

54.9_F

0402

H_SCOMP

R2098

54.9_F

0402

H_SCOMP#

Different with 945PM

5

Different with 945PM

H_CPURST#4

H_CPUSLP#5

+1_05VRUN

R2099

1K_F

0402

1 2

R2100

2K_F

0402

1 2

H_D#[63..0]

Place Cap.

near GMCH

within 100

mils.

C1755

0.1U_10V_K

1 2

0402_X5R

TP724 26MIL

R2101

0_J

0402

1 2

4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

1

H_AVREF

H_DVREF

U4A

E2

H_D#0

G2

H_D#1

G7

H_D#2

M6

H_D#3

H7

H_D#4

H3

H_D#5

G4

H_D#6

F3

H_D#7

N8

H_D#8

H2

H_D#9

M10

H_D#10

N12

H_D#11

N9

H_D#12

H5

H_D#13

P13

H_D#14

K9

H_D#15

M2

H_D#16

W10

H_D#17

Y8

H_D#18

V4

H_D#19

M3

H_D#20

J1

H_D#21

N5

H_D#22

N3

H_D#23

W6

H_D#24

W9

H_D#25

N2

H_D#26

Y7

H_D#27

Y9

H_D#28

P4

H_D#29

W3

H_D#30

N1

H_D#31

AD12

H_D#32

AE3

H_D#33

AD9

H_D#34

AC9

H_D#35

AC7

H_D#36

AC14

H_D#37

AD11

H_D#38

AC11

H_D#39

AB2

H_D#40

AD7

H_D#41

AB1

H_D#42

Y3

H_D#43

AC6

H_D#44

AE2

H_D#45

AC5

H_D#46

AG3

H_D#47

AJ9

H_D#48

AH8

H_D#49

AJ14

H_D#50

AE9

H_D#51

AE11

H_D#52

AH12

H_D#53

AJ5

H_D#54

AH5

H_D#55

AJ6

H_D#56

AE7

H_D#57

AJ7

H_D#58

AJ2

H_D#59

AE5

H_D#60

AJ3

H_D#61

AH2

H_D#62

AH13

H_D#63

B3

H_SWING

C2

H_RCOMP

W1

H_SCOMP

W2

H_SCOMP#

B6

H_CPURST#

E5

H_CPUSLP#

B9

H_AVREF

A9

H_DVREF

Crestline MCH-QN14_ES2

20 mil

12-CRESTL1-ES02

HOST

3

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_DEFER# 4

H_DBSY# 4

CLK_MCH_BCLK 3

CLK_MCH_BCLK# 3

H_DPWR# 5

H_DRDY# 4

Add H_A#[32..35]

2

H_A#[3..35] 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

H_DINV#[3..0] 5

H_DSTBN#[3..0] 5

H_DSTBP#[3..0] 5

H_REQ#[4..0] 4

H_RS#[2..0] 4

Title

Size Document Number Rev

Date: Sheet

FOXCONN

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

Crestline (HOST)1/7

(M610-1-01 )MainBoard (MBX-176) 2007.1.4 2.0

A3

1

781Friday, August 31, 2007

of

Page 8

5

TP881

TP882

TP883

TP884

TP885

TP902

TP886

TP887

TP888

M_A_A1414,16

M_B_A1415,16

TP889

TP890

TP891

TP892

TP893

TP894

TP895

TP896

TP897

TP898

TP899

TP900

TP901

TP903

TP904

TP905

TP906

TP907

TP908

TP909

TP976

TP977

TP910

TP911

TP912

TP913

TP914

TP915

TP916

D D

DDR SYSTEM MEM

LVDS

C C

CFG[2:0]

010 = FSB 800 MHz

011 = FSB 667 MHz

B B

MS90 /CRB

MS90 /CRB

MCH_CFG_9

(PCIE

Graphics

Lane)

Low = Reverse Lane

High = Normal

operation

For layout convenience

MCH_BSEL03

MCH_BSEL13

MCH_BSEL23

26MIL

TP978

26MIL

TP979

26MIL

TP980

26MIL

TP981

26MIL

TP982

26MIL

TP983

26MIL

TP984

26MIL

TP985

26MIL

TP986

26MIL

TP987

26MIL

TP988

26MIL

TP989

26MIL

TP990

26MIL

TP991

26MIL

TP992

26MIL

TP993

26MIL

TP994

26MIL

TP995

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Wait to confirm with Page 13 / CRB

PM_BMBUSY#40

H_DPRSTP#5,39,71

PM_EXTTS#014

PM_EXTTS#115

IMVP_PWRGD40,44

PLT_RST#4,17,38,43,44,45,47,51,53,54

PM_THRMTRIP#4

DPRSLPVR40,71

Design check 1.201

DDR2 Connect to PM_EXT_TS#0/1 pins

of GMCH, pull up with 10K to Vcc3_3

+3VRUN

A A

DDR_ALERT#20,44

Form (U8)thermal sanser & (EC)

R2088 10K_J

R2091 10K_J

R1143 0_J

5

1 2

PM_EXTTS#1

0402

PM_EXTTS#0

0402

PM_EXTTS#0

0402

R109 100_J 0402

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

1 2

TP923

TP924

TP925

TP926

TP927

TP928

TP929

TP930

TP931

TP932

TP933

TP934

TP935

TP936

TP938

TP939

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

26MIL

4

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

4

MCH_RSVD_1

MCH_RSVD_2

MCH_RSVD_3

MCH_RSVD_4

MCH_RSVD_5

MCH_RSVD_6

MCH_RSVD_7

MCH_RSVD_8

MCH_RSVD_9

MCH_RSVD_10

MCH_RSVD_11

MCH_RSVD_12

MCH_RSVD_13

MCH_RSVD_14

MCH_RSVD_20

MCH_RSVD_21

MCH_RSVD_22

MCH_RSVD_23

MCH_RSVD_24

MCH_RSVD_25

MCH_RSVD_26

MCH_RSVD_27

MCH_RSVD_28

MCH_RSVD_29

MCH_RSVD_30

MCH_RSVD_31

M_A_A14

M_B_A14

MCH_RSVD_34

MCH_RSVD_35

MCH_RSVD_36

GM_ODD_RXIN3GM_ODD_RXIN3+

MCH_RSVD_39

MCH_RSVD_40

MCH_RSVD_41

MCH_RSVD_42

MCH_RSVD_43

MCH_RSVD_44

MCH_RSVD_45

PLTRST#_R

PM_THRMTRIP#

MCH_NC1

1

MCH_NC2

1

MCH_NC3

1

MCH_NC4

1

MCH_NC5

1

MCH_NC6

1

MCH_NC7

1

MCH_NC8

1

MCH_NC9

1

MCH_NC10

1

MCH_NC11

1

MCH_NC12

1

MCH_NC13

1

MCH_NC14

1

MCH_NC15

1

MCH_NC16

1

3

U4B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

SA_MA14

BE24

SB_MA14

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

LVDSA_DATA#3

D47

LVDSA_DATA3

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG0

N27

CFG1

N24

CFG2

C21

CFG3

C23

CFG4

F23

CFG5

N23

CFG6

G23

CFG7

J20

CFG8

C20

CFG9

R24

CFG10

L23

CFG11

J23

CFG12

E23

CFG13

E20

CFG14

K23

CFG15

M20

CFG16

M24

CFG17

L32

CFG18

N33

CFG19

L35

CFG20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#0

J36

PM_EXT_TS#1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

BJ51

NC1

BK51

NC2

BK50

NC3

BL50

NC4

BL49

NC5

BL3

NC6

BL2

NC7

BK1

NC8

BJ1

NC9

E1

NC10

A5

NC11

C51

NC12

B50

NC13

A50

NC14

A49

NC15

BK2 R32

NC16 TEST2

Crestline MCH-QN14_ES2

CFG[20:18] internal pull-down

DDR MUXINGCLKDMI

CFG[17:3] internal pull-up

CFGRSVD

PM

GRAPHICS VIDME

NC

MISC

SM_CK0

SM_CK1

SM_CK3

SM_CK4

SM_CK#0

SM_CK#1

SM_CK#3

SM_CK#4

SM_CKE0

SM_CKE1

SM_CKE3

SM_CKE4

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF0

SM_VREF1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLKREQ#

ICH_SYNC#

TEST1

3

AV29

BB23

BA25

AV23

AW30

BA23

AW25

AW23

BE29

AY32

BD39

BG37

BG20

BK16

BG16

BE13

BH18

BJ15

BJ14

BE16

BL15

BK14

BK31

BL31

AR49

AW4

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

H35

K36

G39

G40

A37

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SMDDR_VREF

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

CLK_MCH_3GPLL 3

CLK_MCH_3GPLL# 3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DFGT_VID_0

DFGT_VID_1

DFGT_VID_2

DFGT_VID_3

DFGT_VR_EN

MCH_CLVREF

SDVO_CTRLCLK

SDVO_CTRLDATA

MCH_CLK_REQ#

MCH_TEST_1

MCH_TEST_2

R2076 20_F 0402

1 2

R2077 20_F 0402

1 2

DMI_TXN[3:0] 38

DMI_TXP[3:0] 38

DMI_RXN[3:0] 38

DMI_RXP[3:0] 38

TP97126MIL

TP97226MIL

TP97326MIL

TP97426MIL

TP97526MIL

R2089 NV_0_J 0402

R2090 NV_0_J 0402

MCH_CLK_REQ#

12

R2093

0_J

0402

1 2

1

1

1

1

1

R2092

20K_J

0402

2

M_CLK_DDR0 14

M_CLK_DDR1 14

M_CLK_DDR2 15

M_CLK_DDR3 15

M_CLK_DDR#0 14

M_CLK_DDR#1 14

M_CLK_DDR#2 15

M_CLK_DDR#3 15

M_CKE0 14,16

M_CKE1 14,16

M_CKE2 15,16

M_CKE3 15,16

M_CS#0 14,16

M_CS#1 14,16

M_CS#2 15,16

M_CS#3 15,16

M_ODT0 14,16

M_ODT1 14,16

M_ODT2 15,16

M_ODT3 15,16

+1_8VSUS

CL_CLK0 40

CL_DATA0 40

MPWROK 40

CL_RST#0 40

1 2

1 2

MCH_CLK_REQ# 3

MCH_ICH_SYNC# 40

1

2

1

+1_8VSUS

12

R2073

waiting change 0.1%

1K_F

0402

12

R2074

3.01K_F

0402

12

R2075

waiting change 0.1%

1K_F

0402

Note:If the voltage regulator for the system memory

interface already supplies a VREF output and meets

the voltage tolerance and current requirements for

these pins, then a voltage divider would not be needed.

DDRDIMM_VREF

12

R2079

0_J

0402

C1751

0402

0.1U_16V_M_B

1 2

12

C1745

0.01U_16V_K_B

0402

12

C1747

0.01U_16V_K_B

0402

SMDDR_VREF

C1752

0.1U_16V_M_B

1 2

0402

SM_RCOMP_VOH

12

C1746

2.2U_10V_Y

0603_Y5V

SM_RCOMP_VOL

SM_RCOMP_VOL

12

C1748

2.2U_10V_Y

0603_Y5V

External Graphics (GMCH CRT/TVOUT Disable)

R2082 NV_0_J 0402

R2083 NV_0_J 0402

R2084 NV_0_J 0402

R2085 NV_0_J 0402

TP93726MIL

FOXCONN

Title

Size Document Number Rev

A3

Date: Sheet

1 2

1 2

1 2

1 2

+1_25VRUN

C1753

0.1U_10V_K

1 2

0402_X5R

Crestline (DMI)2/7

(M610-1-01 )MainBoard (MBX-176) 2007.1.4 2.0

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

12

R2086

1K_F

0402

12

R2087

392_F

0402

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

1

of

881Friday, August 31, 2007

Page 9

5

L_BKLT_CTRL

1

26MIL

TP77

26MIL

TP75

Check List=2.4K

CRB=2.37K

MS90=2.37K

R119

1 2

NC_2.4K_F

D D

C C

TYPE is open drawn(Output)

Check list 2.2K to 3.3V

MS90 2.2KK to 3.3V

CRB 2.2KK to 3.3V

10/27

Change NC to stuff

B B

0402

+3VRUN +3VRUN

R1951

NC_2.2K_J

0402

1 2

TP76

TP74

1 2

R1948

NC_2.2K_J

0402

26MIL

26MIL

TV_DCONSEL0

TV_DCONSEL1

GM_BLUE

GM_GREEN

GM_RED

GM_DDCCLK

GM_DDCDATA

GM_HSYNC_R

CRT_IREF

GM_VSYNC_R

L_BKLT_EN

1

L_CTRL_CLK

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

L_VDD_EN

1

L_IBG

L_VBG

1

R2306 NC_0_J 0402

R2307 NC_0_J 0402

10/27

FAE suggest NC to GND

GM_DACA

GM_DACB

GM_DACC

1 2

1 2

TV_DCONSEL0

TV_DCONSEL1

4

U4C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#0

E51

LVDSA_DATA#1

F49

LVDSA_DATA#2

G50

LVDSA_DATA0

E50

LVDSA_DATA1

F48

LVDSA_DATA2

G44

LVDSB_DATA#0

B47

LVDSB_DATA#1

B45

LVDSB_DATA#2

E44

LVDSB_DATA0

A47

LVDSB_DATA1

A45

LVDSB_DATA2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL0

P33

TV_DCONSEL1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

Crestline MCH-QN14_ES2

3

PEG_COMP

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

N43

M43

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

PEG_COMPI

PEG_COMPO

LVDS

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

TV VGA

PEG_TX#10

PCI-EXPRESS GRAPHICS

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

R118

24.9_F

1 2

PEG_RXN[15..0] 18

PEG_RXP[15..0] 18

+VCC_PEG

0402

(source)+1_05VRUN

2

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9 PEG_RXP_C9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

C100 NV_0.1U_16V_M_B

1 2

C101 NV_0.1U_16V_M_B

1 2

C102 NV_0.1U_16V_M_B

1 2

C103 NV_0.1U_16V_M_B

1 2

C104 NV_0.1U_16V_M_B

1 2

C105 NV_0.1U_16V_M_B

1 2

C106 NV_0.1U_16V_M_B

1 2

C107 NV_0.1U_16V_M_B

1 2

C108 NV_0.1U_16V_M_B

1 2

C109 NV_0.1U_16V_M_B

1 2

C110 NV_0.1U_16V_M_B

1 2

C111 NV_0.1U_16V_M_B

1 2

C112 NV_0.1U_16V_M_B

1 2

C113 NV_0.1U_16V_M_B

1 2

C114 NV_0.1U_16V_M_B

1 2

C115 NV_0.1U_16V_M_B

1 2

C116 NV_0.1U_16V_M_B

1 2

C117 NV_0.1U_16V_M_B

1 2

C118 NV_0.1U_16V_M_B

1 2

C119 NV_0.1U_16V_M_B

1 2

C120 NV_0.1U_16V_M_B

1 2

C121 NV_0.1U_16V_M_B

1 2

C122 NV_0.1U_16V_M_B

1 2

C123 NV_0.1U_16V_M_B

1 2

C124 NV_0.1U_16V_M_B

1 2

C125 NV_0.1U_16V_M_B

1 2

C126 NV_0.1U_16V_M_B

1 2

C127 NV_0.1U_16V_M_B

1 2

C128 NV_0.1U_16V_M_B

1 2

C129 NV_0.1U_16V_M_B

1 2

C130 NV_0.1U_16V_M_B

1 2

C131 NV_0.1U_16V_M_B

1 2

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

PEG_RXN_C0

PEG_RXN_C1

PEG_RXN_C2

PEG_RXN_C3

PEG_RXN_C4

PEG_RXN_C5

PEG_RXN_C6

PEG_RXN_C7

PEG_RXN_C8

PEG_RXN_C9

PEG_RXN_C10

PEG_RXN_C11

PEG_RXN_C12

PEG_RXN_C13

PEG_RXN_C14

PEG_RXN_C15

PEG_RXP_C0

PEG_RXP_C1

PEG_RXP_C2

PEG_RXP_C3

PEG_RXP_C4

PEG_RXP_C5

PEG_RXP_C6

PEG_RXP_C7

PEG_RXP_C8

PEG_RXP_C10

PEG_RXP_C11

PEG_RXP_C12

PEG_RXP_C13

PEG_RXP_C14

PEG_RXP_C15

1

PEG_RXN_C[15..0] 17

PEG_RXP_C[15..0] 17

External Graphics (GMCH CRT/TVOUT Disable)

R2057 NV_0_J 0402

R2059 NV_0_J 0402

R2061 NV_0_J 0402

R2063 NV_0_J 0402

R2065 NV_0_J 0402

R2067 NV_0_J 0402

R2069 NV_0_J 0402

A A

5

1 2

1 2

1 2

1 2

1 2

1 2

1 2

4

GM_BLUE

GM_GREEN

GM_RED

CRT_IREF

GM_DACA

GM_DACB

GM_DACC

R2056 NV_0_J 0402

R2058 NV_0_J 0402

R2060 NV_0_J 0402

R2062 NV_0_J 0402

R2064 NV_0_J 0402

R2066 NV_0_J 0402

R2068 NV_0_J 0402

R2070 NV_0_J 0402

R2071 NV_0_J 0402

R2072 NV_0_J 0402

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

3

GM_HSYNC_R

GM_VSYNC_R

GM_DDCCLK

GM_DDCDATA

L_DDC_CLK

L_DDC_DATA

TV_DCONSEL0

TV_DCONSEL1

L_CTRL_CLK

L_CTRL_DATA

Base on below document:

Mobile Merom Processor and Crestline Chipset

- Santa Rosa Platform Design Guide-21112,1.0

.pvd.pdf (May 2006/ Rev 1.0)page 193

Table 82. External Graphics (GMCH Integrated Graphics Disable)

Connect these signals to GND

FOXCONN

Title

Crestline(GRAPHIC)3/7

Size Document Number Rev

(M610-1-01 )MainBoard (MBX-176) 2007.1.4 2.0

A3

2

Date: Sheet

HON HAI PRECISION IND. CO., LTD.

CPBG - R&D Division

1

of

981Friday, August 31, 2007

Page 10

5

D D

M_A_DQ[63..0]14

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

U4D

AR43

SA_DQ0

AW44

SA_DQ1

BA45

SA_DQ2

AY46

SA_DQ3

AR41

SA_DQ4

AR45

SA_DQ5

AT42

SA_DQ6

AW47

SA_DQ7

BB45

SA_DQ8

BF48

SA_DQ9

BG47

SA_DQ10

BJ45

SA_DQ11

BB47

SA_DQ12

BG50

SA_DQ13

BH49

SA_DQ14

BE45

SA_DQ15

AW43

SA_DQ16

BE44

SA_DQ17

BG42

SA_DQ18

BE40

SA_DQ19

BF44

SA_DQ20

BH45

SA_DQ21

BG40

SA_DQ22

BF40

SA_DQ23

AR40

SA_DQ24

AW40

SA_DQ25

AT39

SA_DQ26

AW36

SA_DQ27

AW41

SA_DQ28

AY41

SA_DQ29

AV38

SA_DQ30

AT38

SA_DQ31

AV13

SA_DQ32

AT13

SA_DQ33

AW11

SA_DQ34

AV11

SA_DQ35

AU15

SA_DQ36

AT11

SA_DQ37

BA13

SA_DQ38

BA11

SA_DQ39

BE10

SA_DQ40

BD10

SA_DQ41

BD8

SA_DQ42

AY9

SA_DQ43

BG10

SA_DQ44

AW9

SA_DQ45

BD7

SA_DQ46

BB9

SA_DQ47

BB5

SA_DQ48

AY7