Page 1

1

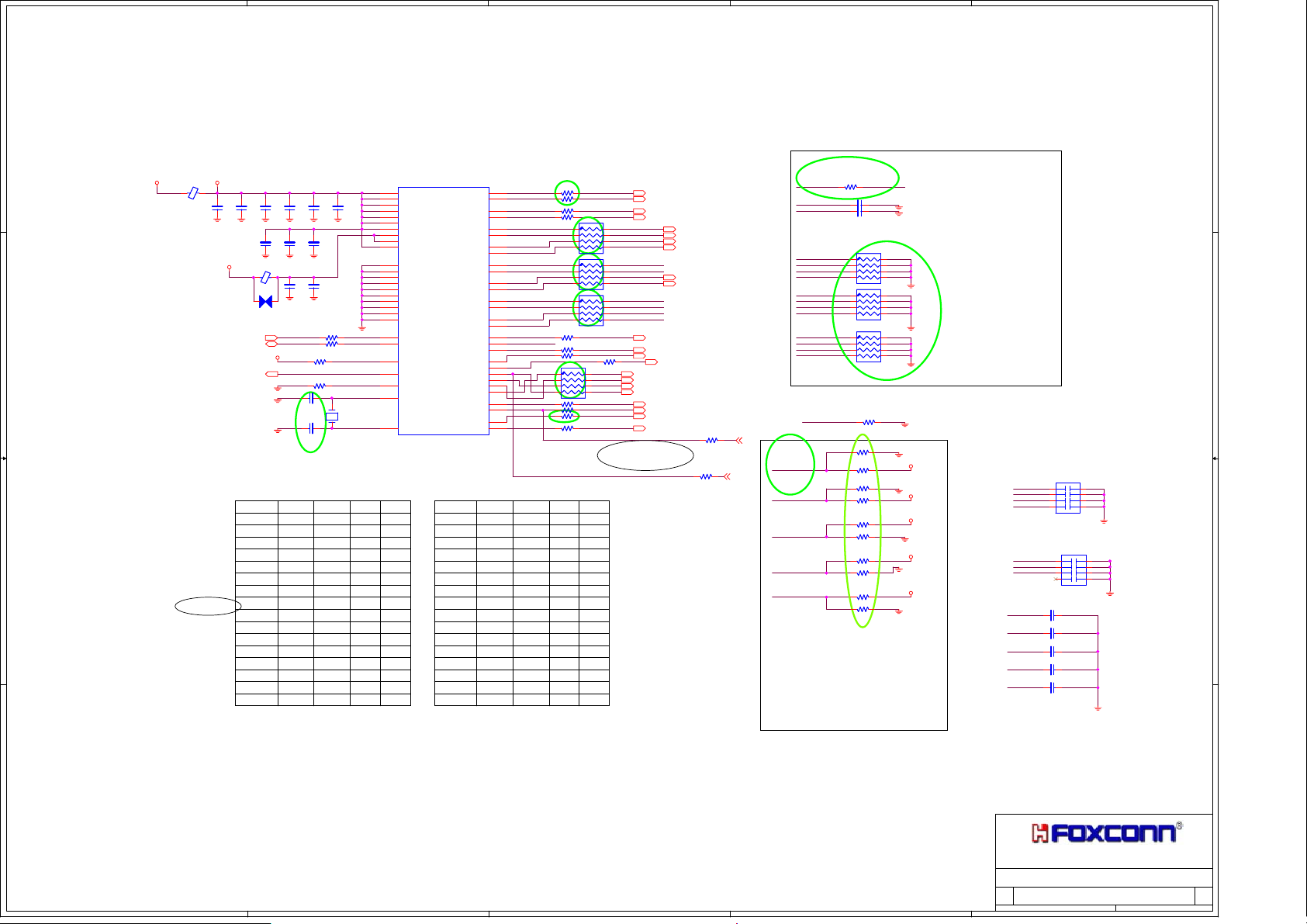

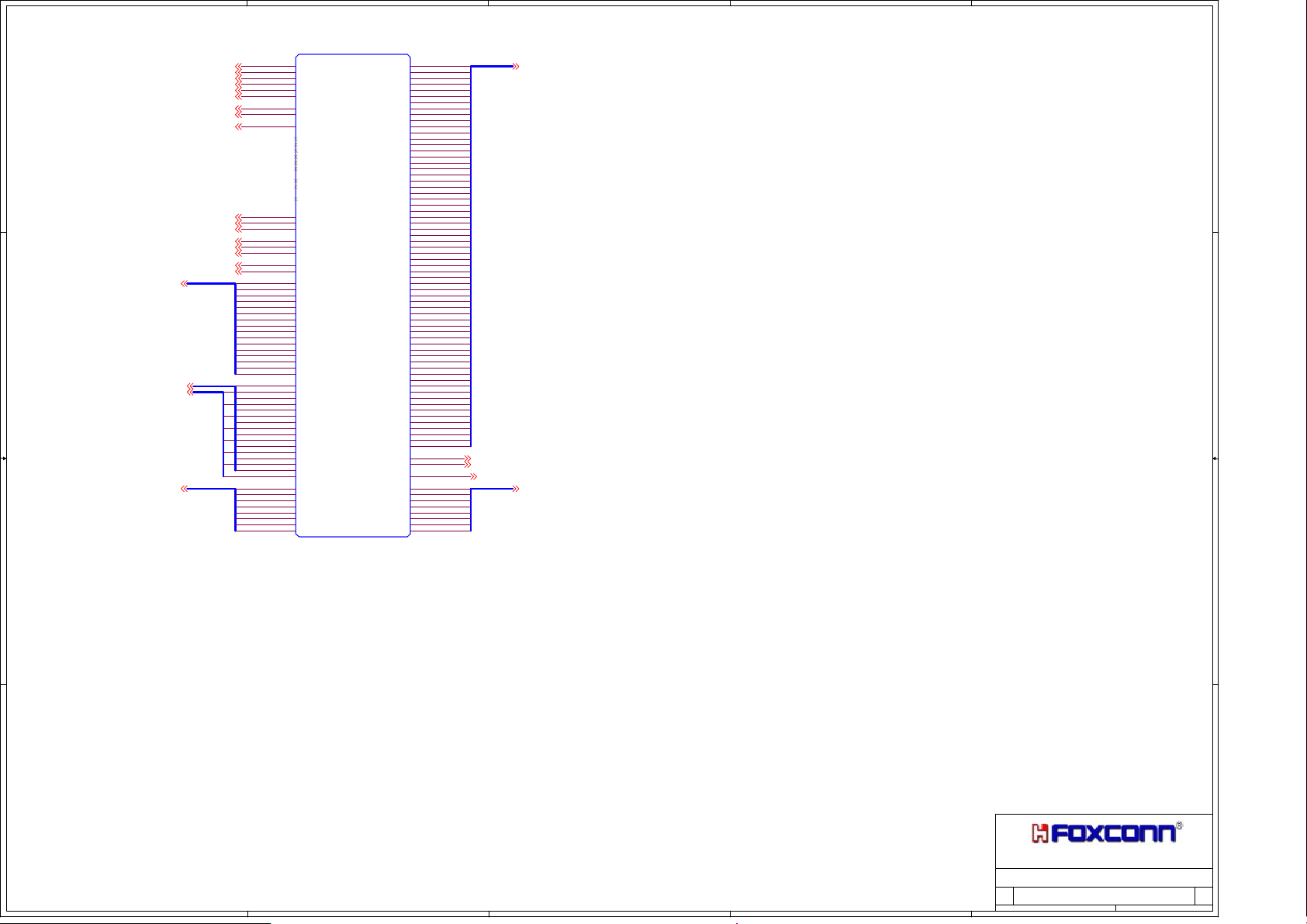

Cover Sheet 1

K8M890M01

Version 0A

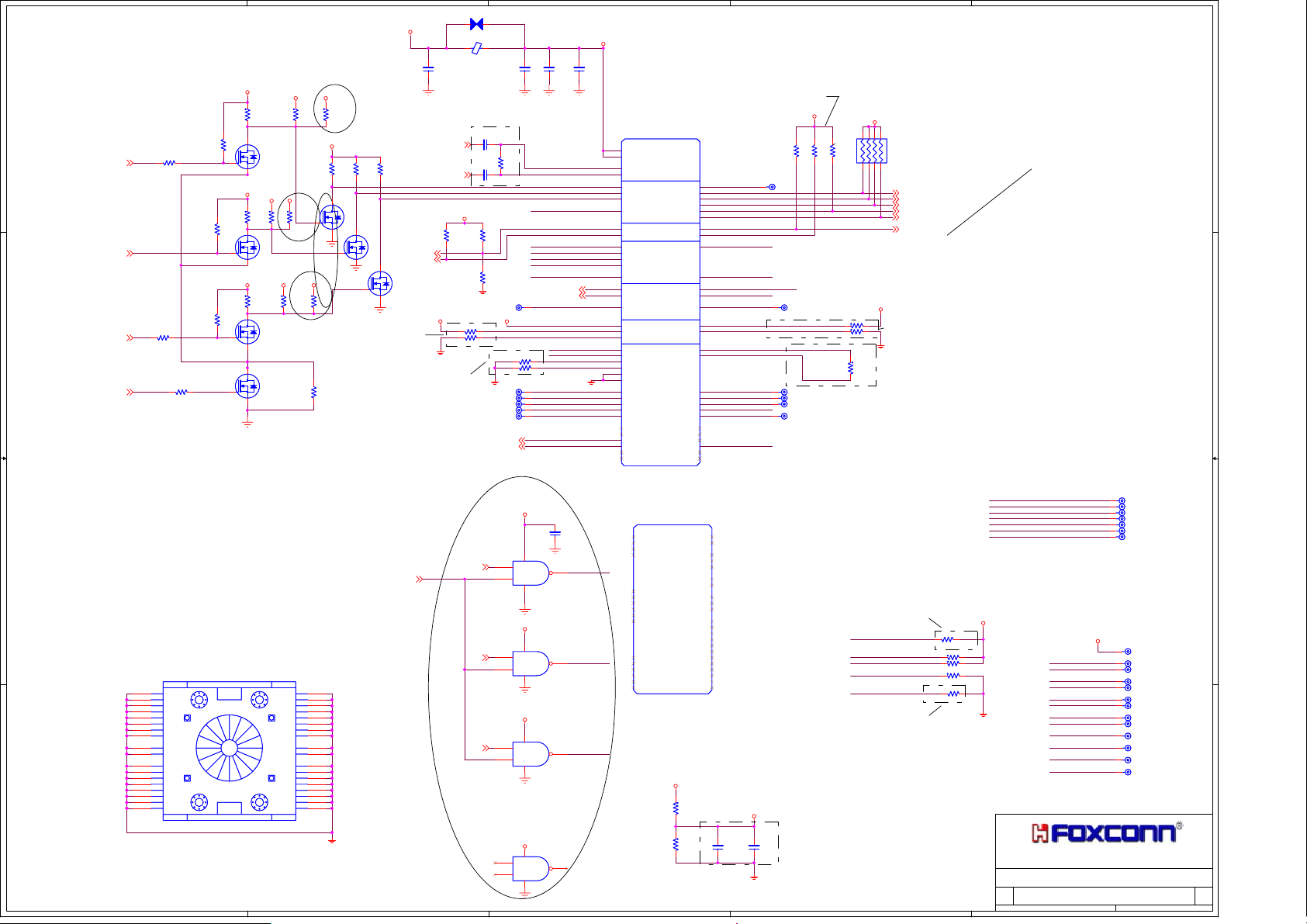

2Block Diagram

Clock & Power Delivery Map

GPIO List

3

4

VIA K8M890 CE + VT8237/ R / R Plus / A Chipset

AMD AM2 Processor

Clock Gen ICS 953201 BF 5

6VRM ISL6566 CR

7AM2_1 Hyper Transport

AM2_2 DDRII -1 & AM2_2 DDRII -2

AM2_ 3 MISC

AM2_4 Power

DDRII SDRAM DIMM1 & DIMM2

DDRII Terminator Part

NORTH BRIDGE (K8M890) 1-3

SOUTH BRIDGE (VT8237) 1-3

PCIe-16X & 1X Slot

PCI Slot1 & Slot2

A A

ATX & Front Panel & FAN

8 - 9

10

11

12

13

14 - 16

17 - 19

20

21

22

SIO IT8716-AX / BX 23

VGA CONNECTOR

1394A VT6308P

PCI LAN RTL8100C / 8110SC

ATA IDE & BIOS ROM

Audio ALC653 & ALC880 (883)

USB CONNECTOR

ACPI Controller W83304G

EMI Part & Front Audio & MH

Change History List

24

25

26

27

28

29

30

31

32

CPU:

AMD AM2

System Chipset:

VIA K8M890 CE (North Bridge)

VIA VT8237 / R / R Plus / A (South Bridge)

On Board Chipset:

BIOS -- LPC EEPROM / SPI ROM

Audio Codec -- AC97 ALC653 / Azania ALC880/883

LPC Super I/O -- IT8716 AX

LAN --PCI LAN (10/100M) RTL8100C / PCI LAN (Giga) 8110SC

CLOCK --ICS 953201 BF

Main Memory:

Dual Channel DDRII DIMM * 2

Expansion Slots:

PCIe 16X SLOT * 1

PCIe 1X SLOT * 1

PCI SLOT *2

VRM:

Controller: Intersill ISL6566 CR

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

1

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

132Wednesday, May 17, 2006

132Wednesday, May 17, 2006

132Wednesday, May 17, 2006

AC

AC

AC

of

of

of

Page 2

A

B

C

D

E

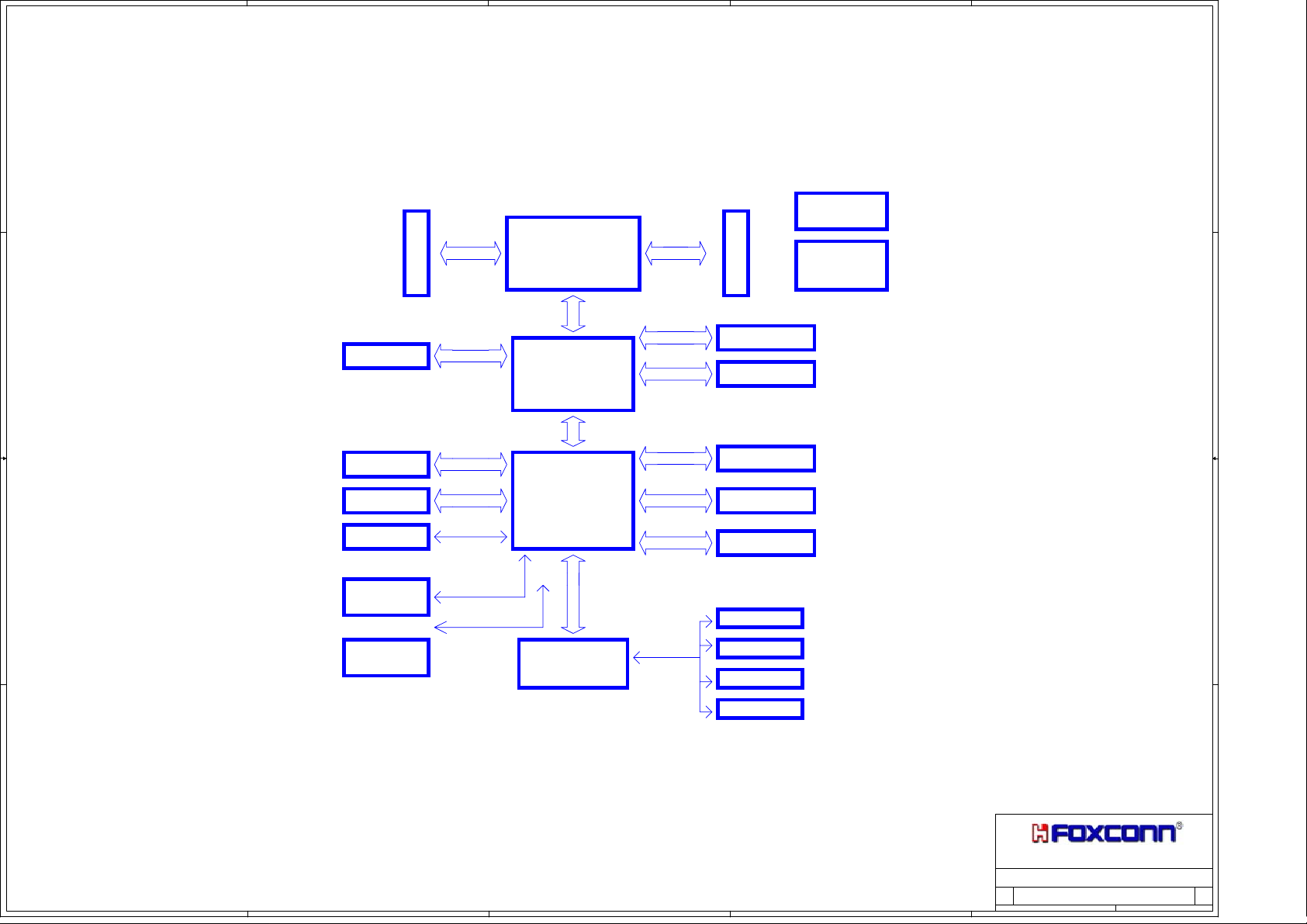

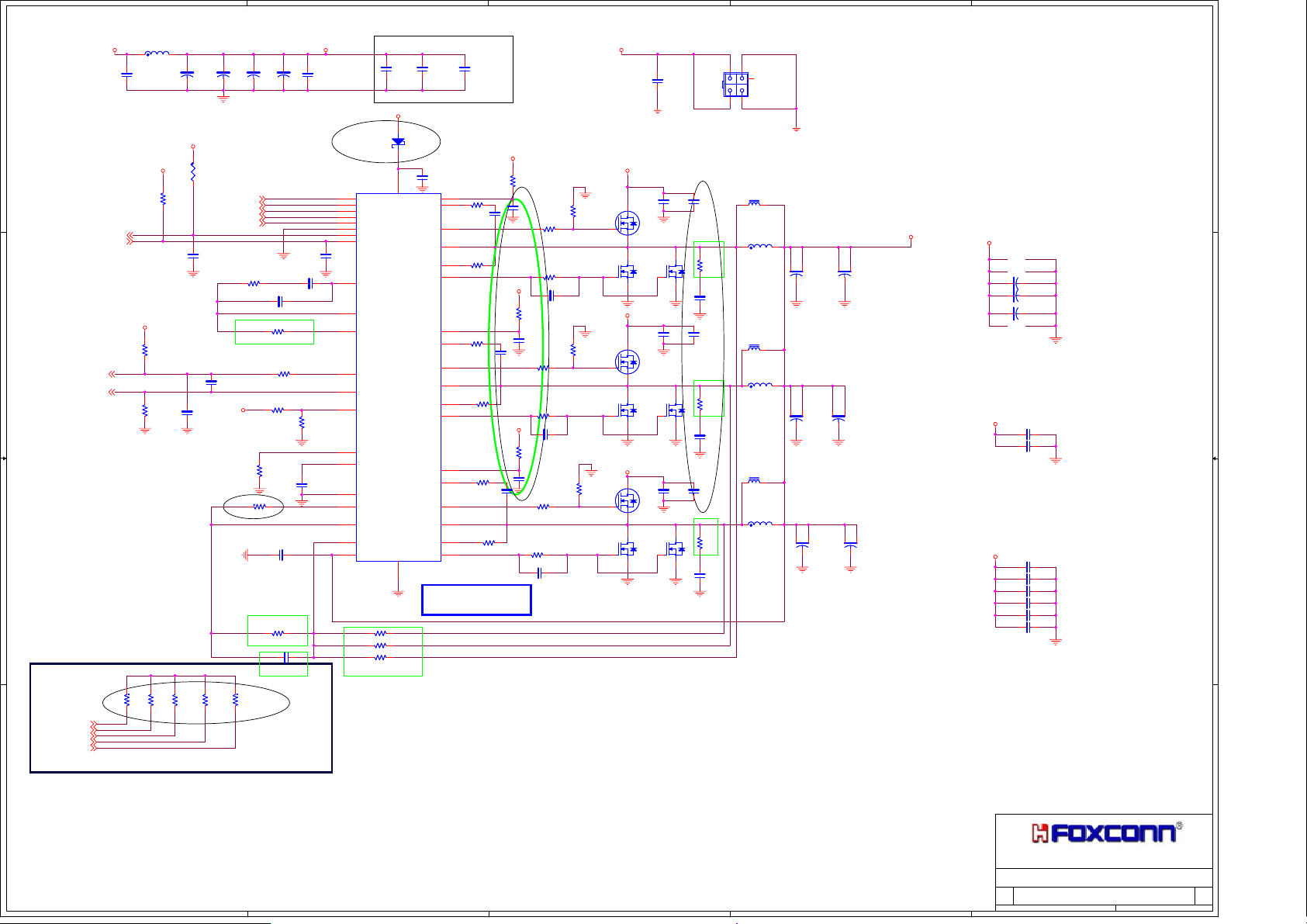

Block Diagram(Micro ATX)

4 4

VCORE

Intersill ISL6566 CR

Channel B

Memory BUS

PCI-E x16

PCI-E x1

DDR2

SLOT

PCI-E x16 SLOT x1

PCI-E x1 SLOT x1

CLOCK

GENERATOR

ICS953201BF

DDR2

SLOT

Channel A

Memory BUS

AMD M2

Processor

940-Pin SOCKET

HT BUS

3 3

VGA

RGB

K8M890CE

V-LINK

USB PORTS X8

AC97/Azalia

USB 2.0

AC97/HD

VT8237R_Plus

IDE BUS

PCI BUS

IDE X2

PCI SLOT X2

VT8237A

KB/MOUSE

2 2

PCI LAN

RTL8100C/8110SC

PCI 1394A

VT6308P

1 1

A

B

SUPER I/O

LPC BUS

IT8716 AX

C

SATA

SATA X2

FLOPPY

LPT PORT

COM 1/COM2

BIOS

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

E

232Wednesday, May 17, 2006

232Wednesday, May 17, 2006

232Wednesday, May 17, 2006

AC

AC

AC

of

of

of

Page 3

5

4

3

2

1

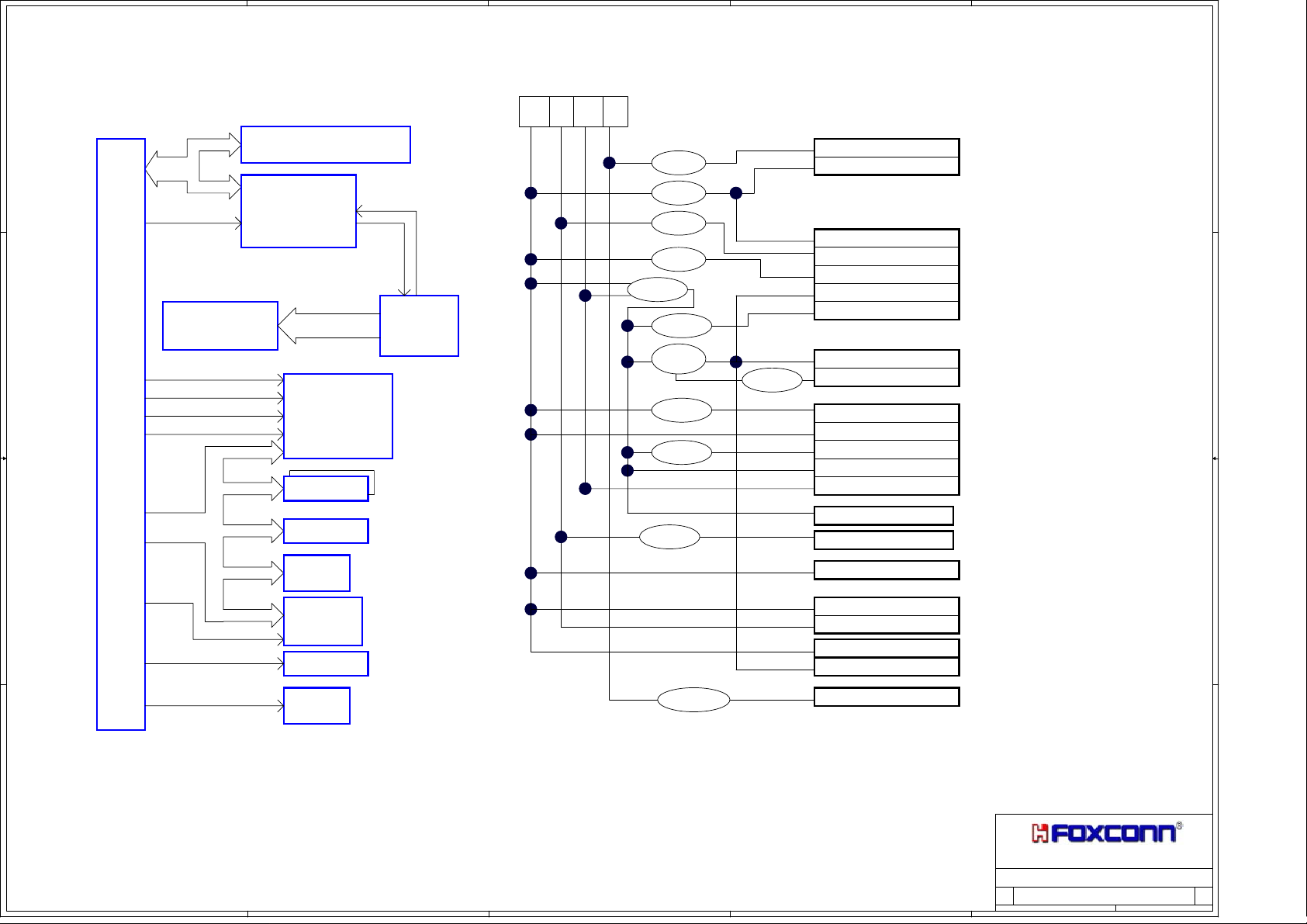

P4M800 PRO PLATFORM CLOCK GENERATOR MAP

D D

Intel LG775 Processor

CPU HOST

CLK

DCLKI

DCLKO

CLOCK

BUFFER

PCI CLK

PCI CLK 0~3

PCI CLK

North Bridge

P4M890 PRO

MEM CLK

Sorth Bridge

VT8237

PCI Slot 1~2

RTL PCI LAN

66MHZ

DDRI/II DIMM Slot1~4

C C

CLOCK GENERATOR

14.318MHZ

APIC

66MHZ

48MHZ

3.3V 5V 5VSB 12V

1.2V VREG

1.5V VREG

1.5V VREG

3VSB VREG

1.5VSB VREG

DDR 2.6V

VREG

2.5VSB VREG

3.3V VREG

VRM

2.5V VREG

P4M800 PRO PLATFORM POWER DELIVERY MAP

PROCESSOR VCCP

PROCESSOR 1.2V

NORTH BRIDGE VTT

NORTH BRIDGE AGP

NORTH BRIDGE +1.5V

NORTH BRIDGE SYSEM MEMORY

VCC_DDR

NORTH BRIDGE RESUME 1.5V_SB

DDR DIMM1 / DIMM2 2.6V

VTT 1.3V VREG

DDR VTT 1.3V

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

LAN VCC3_SB , 2.5V

1394 3.3V

B B

48MHZ

PCI CLK

PCI CLK

LPC

ROM

ITE

IT8712F/JX

100M

14.318M

A A

5

PCIE Slot

AC'97

CODEC

AC97 VDD5

VREG

4

3

BIOS 3.3V

LPC SUPER I/O 3.3V

LPC SUPER I/O VCC5

CLK 3.3V

DDR BUFFER +2.5V

AC97 VDD5

2

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Dirgram

Dirgram

Dirgram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

1

332Wednesday, May 17, 2006

332Wednesday, May 17, 2006

332Wednesday, May 17, 2006

of

of

of

AC

AC

AC

Page 4

5

South Bridge Super I/O

4

3

2

1

*

D D

*

*

*

*

*

*

*

*

*

*

*

*

C C

*

*

*

*

*

*

*

*

*

*

*

*

*

B B

*

*

*

*

*

*

*

*

*

*

*

*

A A

*

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

GPIO List

GPIO List

GPIO List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

1

432Wednesday, May 17, 2006

432Wednesday, May 17, 2006

432Wednesday, May 17, 2006

AC

AC

AC

of

of

of

Page 5

5

4

3

2

1

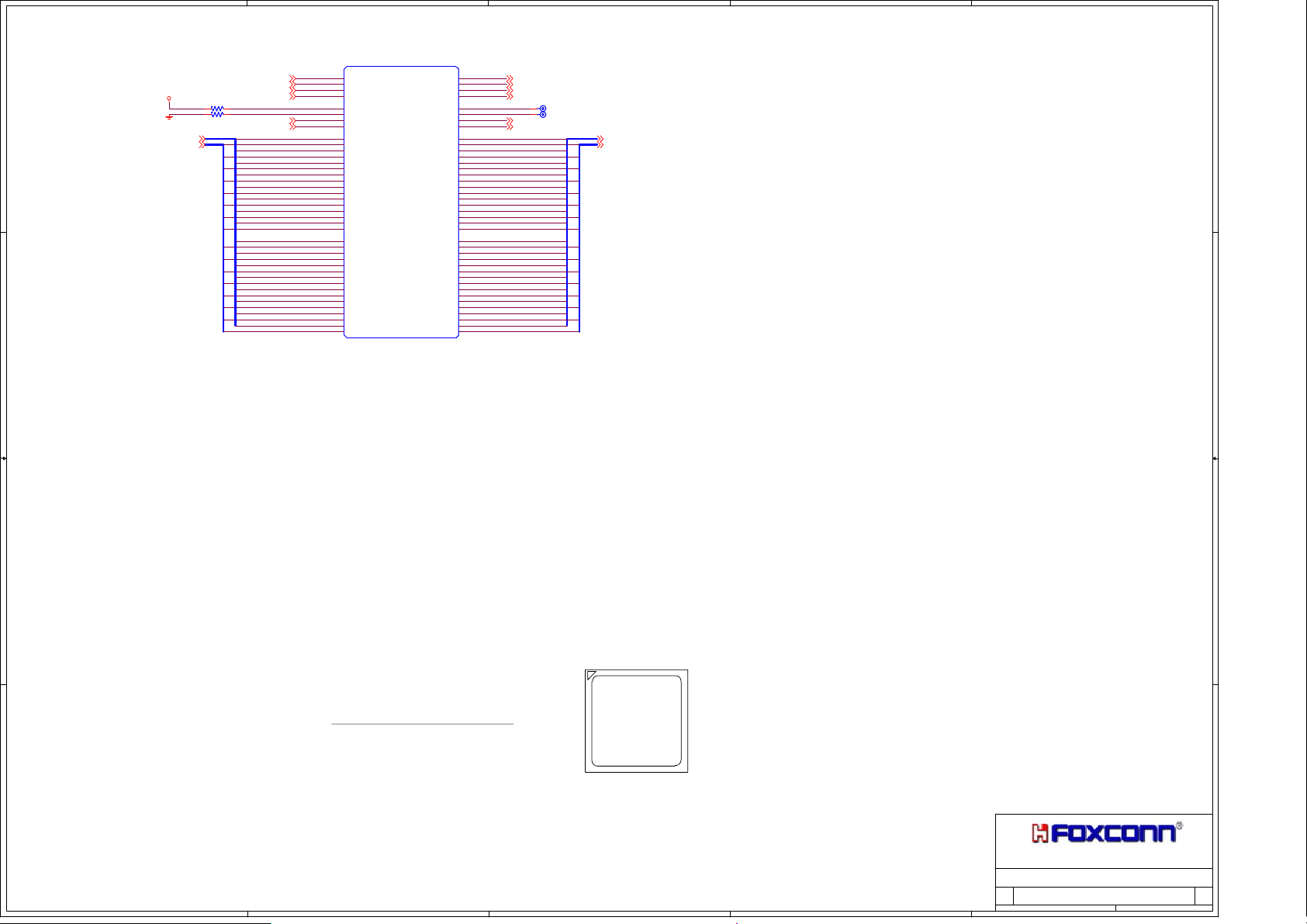

Clock Synthesizer

D D

+3.3VCLKVCC3

L22

L22

FB L0805 60 Ohm

FB L0805 60 Ohm

C C

21

C187

C187

*

*

10uF

10uF

C1206

C1206

+3.3VCLK

X_FB L0805 60 Ohm

X_FB L0805 60 Ohm

C221

*

*

*

*

0.1uF

0.1uF

C0603

C0603

*

*

L23

L23

CP2003

CP2003

dummy

dummy

SMBCLK12,18,20,26,30

SMBDATA12,18,20,26,30

-RESET_CLK22

*

*

10nF

10nF

C0603

C0603

C233

C233

*

*

10nF

10nF

C0603

C0603

21

*

*

X_COPPER

X_COPPER

VCC3

50V, NPO, +/-5%

50V, NPO, +/-5%

*

*

10nF

10nF

C0603

C0603

C240

C240

*

*

10nF

10nF

C0603

C0603

*

*

C229

C229

10nF

10nF

C0603

C0603

R195 10K

R195 10K

R187 475

R187 475

*

*

C195 56pF

C195 56pF

C0603

C0603

*

*

C196 56pF

C196 56pF

*

*

10nF

10nF

C0603

C0603

C232

C232

10nF

10nF

C0603

C0603

C215

C215

0.1uF

0.1uF

C0603

C0603

R235 22

R235 22

*

*

R0603

R0603

R188 22

R188 22

*

*

R0603

R0603

*

*

+/-5%R0603

+/-5%R0603

*

*

+/-1%R0603

+/-1%R0603

12

50V, NPO, +/-5%C0603

50V, NPO, +/-5%C0603

C197

C197

C198

C198

C212

C212

C221

ICS CRB & VIA CRB bom value different

FS[4:0]

00000

00001

00010

00011

禬繵

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

01111

B B

TABLE

CPU PCIEX AGP PCI

100.90 100.90 67.27 33.63

133.90 100.43 66.95 33.48

168.00 100.80 67.20 33.60

202.00 101.00 67.33 33.67

100.20 100.20 66.80 33.40

133.50 100.13 66.75 33.38

166.70 100.02 66.68 33.34

200.40 100.20 66.80 33.40

160.00 100.00 66.67 33.33

202.00 101.00 67.33 33.67

210.00 105.00 70.00 35.00

212.00 106.00 70.67 35.33

270.00 101.25 67.50 33.75

225.00 112.50 75.00 37.50

266.67 100.00 66.67 33.33

300.00 112.50 75.00 37.50

ICS CRB & VIA CRB bom value different

U18

U18

C209

C209

10nF

10nF

C0603

C0603

+/-5%

+/-5%

+/-5%

+/-5%

14MHZX1

XTAL 14.31818MHz

XTAL 14.31818MHz

+/-30ppm

+/-30ppm

X3

X3

14MHZX2

1

VDDA

3

VDDREF

10

VDDPCI1

16

VDDPCI2

20

VDD

21

VDD48

26

VDDAGP

39

VDDPCIEX1

45

VDDPCIEX2

51

VDDCPU

2

GND

8

GNDREF

15

GNDPCI1

19

GNDPCI2

24

GND48

30

GNDAGP

32

GNDPCIEX1

40

GNDPCIEX2

50

GND

54

GNDCPU

31

SCLK

48

SDATA

9

VTTPWRGD/PD#

25

RESET#

49

IREF

6

X1

7

X2

ICS953201BF

ICS953201BF

SEL24_48#/24_48MHz

FS[4:0] CPU PCIEX AGP PCI

10000

10001

10010

10011

10100

10101

10110

10111

11000

11001

11010

11011

11100

11101

11110

11111

56

CPUCLK8T0

55

CPUCLK8C0

53

CPUCLK8T1

52

CPUCLK8C1

47

PCIEXT0

46

PCIEXC0

44

PCIEXT1

43

PCIEXC1

42

PCIEXT2

41

PCIEXC2

38

PCIEXT3

37

PCIEXC3

36

PCIEXT4

35

PCIEXC4

34

PCIEXT5

33

PCIEXC5

29

AGPCLK0

28

FS4/AGPCLK1

27

AGPCLK2

11

FS2/PCI0

12

FS3/PCI1

13

PCI2

14

PCI3

17

PCI4

18

PCI5

4

FS0/REF0

5

FS1/REF1

22

48MHz

23

166.66 104.16 69.44 34.72

210.00 105.00 70.00 35.00

215.00 107.50 71.67 35.83

230.00 115.00 76.67 38.33

240.00 120.00 80.00 40.00

CPU_CLK+

R169 47.5 R0603

R169 47.5 R0603

CPU_CLK- CPUCLK-

R174 47.5 R0603

R174 47.5 R0603

H_CLK+

R180 15

R180 15

H_CLK-

R182 15

R182 15

PECLKNB+

PECLKNB-

PECLK_1+

PECLK_1-

PECLK_4+

PECLK_4-

PECLK_2+

PECLK_2-

PECLK_3+

PECLK_3-

PECLK_5+

PECLK_5-

R236 22+/-5% R0603

R236 22+/-5% R0603

FS4

R232 22+/-5% R0603

R232 22+/-5% R0603

FS2

R201 22+/-5% R0603

R201 22+/-5% R0603

FS3

*

*

FS0

R181 22+/-5%

R181 22+/-5%

FS1

R184 22+/-5% R0603

R184 22+/-5% R0603

R220 33R0603

R220 33R0603

48MHZSEL

R219 22+/-5% R0603

R219 22+/-5% R0603

*

*

*

*

R0603

R0603

*

*

R0603

R0603

*

*

RN21

RN21

*

*

1

3

5

7 8

47

47

RN24

RN24

+/-5%

+/-5%

*

*

1

8p4r0603h7

8p4r0603h7

3

5

7 8

RN26

RN26

47

47

+/-5%

+/-5%

*

*

1

8p4r0603h7

8p4r0603h7

3

5

7 8

47

47

+/-5%

+/-5%

*

*

8p4r0603h7

8p4r0603h7

*

*

*

*

R204 22+/-5% R0603

R204 22+/-5% R0603

RN23

RN23

1

2

3

4

5

6

7 8

SIO_OSC

47

47

*

*

+/-5%

+/-5%

*

*

8p4r0603h7

8p4r0603h7

*

*

*

*

2

4

6

2

4

6

2

4

6

R0603

R0603

CPUCLK+

HCLK+

HCLK-

12崩 惠单

100.00 66.67 33.33100.00

100.00 66.67 33.33133.00

100.00 66.67 33.33200.00

103.00 68.67 34.33103.00

103.00 68.66 34.33137.33

103.00 68.66 34.33171.66

103.00 68.67 34.33206.00

104.00 69.33 34.67208.00

110.00 73.33 36.67220.00

113.00 75.33 37.67226.00

125.00 83.33 41.67250.00

cpu nb dampping

CPU_CLKIN_H 10

CPU_CLKIN_L 10

HCLK+ 16

HCLK- 16

PECLK_NB+

PECLK_NBPECLK1+

PECLK1-

PECLK4+

PECLK4PECLK2+

PECLK2-

PECLK3+

PECLK3PECLK5+

PECLK5-

RN&R change to 22ohm

*

*

VCLK_NB 16

VCLK_SB 19

LAN_CLK 26

PCI_CLK_1394 25

SB_CLK 19

PCICLK2 21

PCICLK1 21

PCICLKSIO 23

SB_OSC 18

GUICLK 16

USBCLK 17

SIOCLK 23

PECLK_NB+ 15

PECLK_NB- 15

PECLK1+ 20

PECLK1- 20

PECLK2+ 20

PECLK2- 20

R186 22

R186 22

R0603

R0603

R207

R207

*

*

*

*

+/-5%

+/-5%

22+/-5%

22+/-5%

R0603

R0603

CPUCLK+ CPUCLK-

HCLK+

HCLK-

PECLK_NB+

PECLK_NBPECLK1+

PECLK1-

PECLK4+

PECLK4PECLK2+

PECLK2-

PECLK3+

PECLK3PECLK5+

PECLK5-

CHECK VIA

ICS CRB &

VIA CRB

bom value

different

AC_14M 28

BIOS_CLK 27

48MHZSEL

SIO_OSC

FS1

FS2

FS3

FS4

Place these components close to

their respective series damping

resistor of the clock ouput.

Set FS[4:0] value at 10011 for

default frequencies as below:

CPU PCIEX AGP PCI

R172 261

R172 261

*

*

+/-1%R0603

+/-1%R0603

C199 10pFC0603

C199 10pFC0603

C205 10pFC0603

C205 10pFC0603

*

*

*

*

RN22

RN22

*

*

1

3

5

7 8

RN25

RN25

47

47

+/-5%

+/-5%

*

*

1

8p4r0603h7

8p4r0603h7

3

5

7 8

47

47

+/-5%

+/-5%

8p4r0603h7

8p4r0603h7

RN27

RN27

*

*

1

3

5

7 8

47

47

+/-5%

+/-5%

8p4r0603h7

8p4r0603h7

R223 10K

R223 10K

R173 8.2K

R173 8.2K

*

*

R179 10K

R179 10K

*

*

R185 8.2K

R185 8.2K

*

*

R183 10K

R183 10K

*

*

R194 10K

R194 10K

*

*

R206 8.2K

R206 8.2K

*

*

R200 10K

R200 10K

*

*

R205 8.2K

R205 8.2K

*

*

R239 10K

R239 10K

*

*

R233 8.2K

R233 8.2K

*

*

check clock table

check value & layout location

ICS CRB & VIA CRB bom value

different

2

4

6

2

4

6

2

4

6

*

*

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

change to 51ohm

Place these components

close to their respective

series damping resistor of

the clock ouput.

VCC3

FS0

VCC3

FS1

VCC3

FS2

VCC3

FS3

VCC3

FS4

PCICLKSIO

PCICLK1

PCICLK2

SB_CLK

LAN_CLK

PCI_CLK_1394

BIOS_CLK

AC_14M

SIOCLK

USBCLK

VCLK_NB

VCLK_SB

CN2

CN2

7 8

5 6

3 4

1 2

X_8P4C-10P50N

X_8P4C-10P50N

CN3

CN3

7 8

5 6

3 4

1 2

X_8P4C-10P50N

X_8P4C-10P50N

C756 X_10pFC0603

C756 X_10pFC0603

*

*

C757 X_10pFC0603

C757 X_10pFC0603

*

*

C758 X_10pFC0603

C758 X_10pFC0603

*

*

C759 X_10pFC0603

C759 X_10pFC0603

*

*

C760 X_10pFC0603

C760 X_10pFC0603

*

*

Dummy

Dummy

Dummy

Dummy

200.00 100.00 66.67 33.33

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Clock Gen

Clock Gen

Clock Gen

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

1

532Tuesday, June 27, 2006

532Tuesday, June 27, 2006

532Tuesday, June 27, 2006

AC

AC

AC

of

of

of

Page 6

5

L21 Choke 1.1uH

L21 Choke 1.1uH

*

*

C698

C698

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

D D

HIGH(>1.24V)

ENABLE VRM

VRM_GD22,30

VRM_EN30

VRM_EN > 0.6V ENABLE

C C

CPU_VDD_RUN_FB_H10

CPU_VDD_RUN_FB_L10

+V_CPU

*

*

16V, +/-20%

16V, +/-20%

VCC3

VCC3

R271

R271

1K

1K

*

*

+/-1%

+/-1%

R0603

R0603

R226

R226

*

*

51

51

+/-5%

+/-5%

R0603

R0603

R234

R234

*

*

51

51

*

*

+/-5%

+/-5%

R0603

R0603

dummy

dummy

C114

C114

C120

C120

1500uF

1500uF

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

16V, +/-20%

16V, +/-20%

*

*

R274

R274

10K

10K

+/-5%

+/-5%

R0603

R0603

VREG_VID410

VREG_VID310

VREG_VID210

VREG_VID110

VREG_VID010

C282

C282

0.1uF

0.1uF

*

*

C0603

C0603

R245 10K

R245 10K

R0603

R0603

C241

C241

X_1nF

X_1nF

*

*

C0603

C0603

dummy

dummy

C242

C242

X_1nF

X_1nF

VCC5

C0603

C0603

V1.0 bom change to 1K/1%

B B

OVL

R304

R300

R300

R301

R301

R302

R302

*

*

*

*

12K

12K

3.24K

3.24K

1.62K

1.62K

+/-1%

+/-1%

+/-1%

R0603

R0603

+/-1%

R0603

R0603

+/-1%

+/-1%

PWM_GIOP123

PWM_GIOP223

PWM_GIOP323

PWM_GIOP423

PWM_GIOP523

R304

R303

R303

*

*

750

750

1.62K

1.62K

+/-1%

+/-1%

+/-1%

+/-1%

R0603

R0603

C115

C115

C121

C121

1500uF

1500uF

*

*

*

*

C244 47pF

C244 47pF

C0603

C0603

R240 1K

R240 1K

R0603

R0603

Orig 2K

R225 100

R225 100

R0603

R0603

R255 X_150K

R255 X_150K

R0603

R0603

+10mV

OFFSET

R272

R272

*

*

120K

120K

+/-5%

+/-5%

R0603

R0603

R224

R224

+/-1%

+/-1%

C239 0.1uF

C239 0.1uF

C0603

C0603

Orig 33K

R227 13.3K

R227 13.3K

R0603 +/-1%

R0603 +/-1%

C235 47nF

C235 47nF

C0603

C0603

Orig 47nF Y5V

need modifyneed modify

*

*

16V, +/-20%

16V, +/-20%

+/-5%

+/-5%

*

*

*

*

*

*

dummy

dummy

1K

1K

*

*

*

*

1500uF

1500uF

*

*

C247 5.6nF

C247 5.6nF

C0603

C0603

+/-1%

+/-1%

+/-5%

+/-5%

*

*

*

*

*

*

*

*

C157

C157

4.7uF

4.7uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

*

*

*

*

+/-1%

+/-1%

R257

R257

51K

51K

+/-5%

+/-5%

R0603

R0603

C264

C264

10nF

10nF

C0603

C0603

V1.0 CHANGE BOM VALUE

32PIN 5x5QFN

38

39

40

1

2

3

35

37

C270

C270

0.1uF

0.1uF

C0603

C0603

8

9

10

OVL

12

11

6

36

5

4

13

14

15

16

R0603

R0603

R0603

R0603

R0603

R0603

4

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

D7

B120D7B120

U19

U19

VID4

VID3

VID2

VID1

VID0

DACSEL/VID5

PGOOD

ENLL

COMP

FB

VDIFF

VSEN

RGND

OFST

FS

REF

VRM10

OCSET

ICOMP

ISUM

IREF

R214 24K

R214 24K

*

*

R215 24K

R215 24K

*

*

R216 24K

R216 24K

*

*

Orig 33K

C138

C138

0.1uF

0.1uF

C0603

C0603

dummy

dummy

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

VCC5

2 1

7

VCC

PVCC2/EN_PH3

BOOT2/NC

UGATE2/PWM3

PHASE2/NC

ISEN2/ISEN3

LGATE2/NC

GND

ISL6566CR

ISL6566CR

41

+/-1%

+/-1%

+/-1%

+/-1%

+/-1%

+/-1%

*

*

*

*

PVCC1

BOOT1

UGATE1

PHASE1

LGATE1

PVCC3

BOOT3

UGATE3

PHASE3

LGATE3

emi

ISEN1

ISEN3

C140

C140

C136

C136

0.1uF

0.1uF

0.1uF

0.1uF

*

*

C0603

C0603

C0603

C0603

dummy

dummy

dummy

dummy

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C253

C253

4.7uF

4.7uF

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C0805

C0805

33

R273 2.2

R273 2.2

30

*

*

R0805

R0805

C267

C267

0.1uF

0.1uF

C0603

C0603

31

29

R258 1.8K

R258 1.8K

32

*

*

R0603 +/-5%

R0603 +/-5%

1PHASE_LGATE

34

24

R256 2.2

R256 2.2

26

*

*

R0805

R0805

27

28

R249 1.8K

R249 1.8K

25

R0603 +/-5%

R0603 +/-5%

23

18

R237 2.2

R237 2.2

21

R0805

R0805

20

22

R230 1.8K

R230 1.8K

19

R0603 +/-5%

R0603 +/-5%

17

BOTTOM PAD CONNECT TO

GND THROUGH 10vias

C256

C256

0.1uF

0.1uF

C0603

C0603

*

*

*

*

*

*

C243

C243

0.1uF

0.1uF

C0603

C0603

*

*

10U/1206 CHANGE TO 1U/0805

12V_VIN

R261

R261

*

*

2.2

2.2

+/-5%

+/-5%

R0805

R0805

C277

*

*

12V_VIN

12V_VIN

*

*

C277

*

*

1uF

1uF

C0805

C0805

R149 1

R149 1

R0805

R0805

R151 0

R151 0

R0805

R0805

*

*

2.2

2.2

+/-5%

+/-5%

R0805

R0805

C246

C246

*

*

1uF

1uF

C0805

C0805

R142 1

R142 1

R0805

R0805

R124 0

R124 0

R0805

R0805

R229

R229

*

*

2.2

2.2

+/-5%

+/-5%

R0805

R0805

C238

C238

*

*

1uF

1uF

C0805

C0805

R157 1

R157 1

R0805

R0805

R126 0

R126 0

R0805

R0805

R244

R244

*

*

*

*

C171

C171

22nF

22nF

C0603

C0603

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

+/-5%

+/-5%

*

*

*

*

C145

C145

22nF

22nF

C0603

C0603

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

+/-5%

+/-5%

*

*

+/-5%

+/-5%

*

*

C148

C148

22nF

22nF

C0603

C0603

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

+/-5%

+/-5%

+/-5%

+/-5%

*

*

+/-5%

+/-5%

*

*

Dummy

Dummy

Dummy

Dummy

R148

R148

10K

10K

+/-5%

+/-5%

R0603

R0603

Dummy

Dummy

R145

R145

10K

10K

+/-5%

+/-5%

R0603

R0603

R154

R154

*

*

10K

10K

+/-5%

+/-5%

R0603

R0603

3

PWR2

12V_VIN12V_VIN 12V_VRM

12V_VRM

C176

C176

10nF

10nF

*

*

C0603

C0603

PWR2

2

4

5

1

3

ATX12V_P1_2X2

ATX12V_P1_2X2

2

1

bom change to 10uF

C850

C850

C137

C137

*

*

*

*

1uF

1uF

DS

C0805

C0805

Q19

Q19

G

AOD436

AOD436

DS

G

12V_VRM

DS

G

DS

G

12V_VRM

DS

G

DS

G

Q20

Q20

AOD438

AOD438

Q18

Q18

AOD436

AOD436

Q14

Q14

AOD438

AOD438

Q21

Q21

AOD436

AOD436

Q17

Q17

AOD438

AOD438

G

G

G

*

*

*

*

C135

C135

1uF

1uF

C0805

C0805

C139

C139

1uF

1uF

C0805

C0805

DS

Q23

Q23

AOD438

AOD438

DS

Q15

Q15

AOD438

AOD438

DS

Q16

Q16

AOD438

AOD438

*

*

*

*

Orig 2.2R 0603

1uF

1uF

C1206

C1206

Orig 2.2R 0603

R160

R160

*

*

2.2

2.2

+/-5%

+/-5%

R0805

R0805

C182

C182

1nF

1nF

*

*

C0603

C0603

C851

C851

1uF

1uF

C1206

C1206

Orig 2.2R 0603

R158

R158

*

*

2.2

2.2

+/-5%

+/-5%

R0805

R0805

C191

C191

1nF

1nF

*

*

C0603

C0603

C852

C852

1uF

1uF

C1206

C1206

R164

R164

*

*

2.2

2.2

+/-5%

+/-5%

R0805

R0805

C188

C188

1nF

1nF

*

*

C0603

C0603

L29 600nH@100KHz

L29 600nH@100KHz

dummy

dummy

L28

L28

*

*

600nH@100KHz

600nH@100KHz

**

**

L27 600nH@100KHz

L27 600nH@100KHz

dummy

dummy

L26

L26

*

*

600nH@100KHz

600nH@100KHz

**

**

L25 600nH@100KHz

L25 600nH@100KHz

dummy

dummy

L24

L24

*

*

600nH@100KHz

600nH@100KHz

C223

C223

3300uF

3300uF

6.3V, +/-20%

6.3V, +/-20%

C220

C220

3300uF

3300uF

6.3V, +/-20%

6.3V, +/-20%

**

**

6.3V, +/-20%

6.3V, +/-20%

C226

C226

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

**

**

6.3V, +/-20%

6.3V, +/-20%

dummy

dummy

**

**

C222

C222

3300uF

3300uF

C225

C225

X_3300uF

X_3300uF

C224

C224

3300uF

3300uF

6.3V, +/-20%

6.3V, +/-20%

+V_CPU

+V_CPU

C218 X_560uF

C218 X_560uF

C202 X_560uF

C202 X_560uF

C204 X_560uF

C204 X_560uF

+V_CPU

+V_CPU

4V, +/-20% dummy

4V, +/-20% dummy

*

*

4V, +/-20% dummy

4V, +/-20% dummy

*

*

4V, +/-20%

4V, +/-20%

*

*

C250 10uF

C250 10uF

C1206

C1206

*

*

C249 10uF

C249 10uF

C1206

C1206

*

*

C275 10uF

C275 10uF

C1206

C1206

*

*

C295 10uF

C295 10uF

C1206

C1206

*

*

C294 10uF

C294 10uF

C1206

C1206

*

*

C280 10uF

C280 10uF

C1206

C1206

*

*

C251 10uF

C251 10uF

C1206

C1206

*

*

C252 10uF

C252 10uF

C1206

C1206

*

*

dummy

dummy

VCORE over VID CKT

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Vcore ISL6559 + ISL6614 + ISL6612

Vcore ISL6559 + ISL6614 + ISL6612

Vcore ISL6559 + ISL6614 + ISL6612

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

1

632Friday, June 09, 2006

632Friday, June 09, 2006

632Friday, June 09, 2006

AC

AC

AC

of

of

of

Page 7

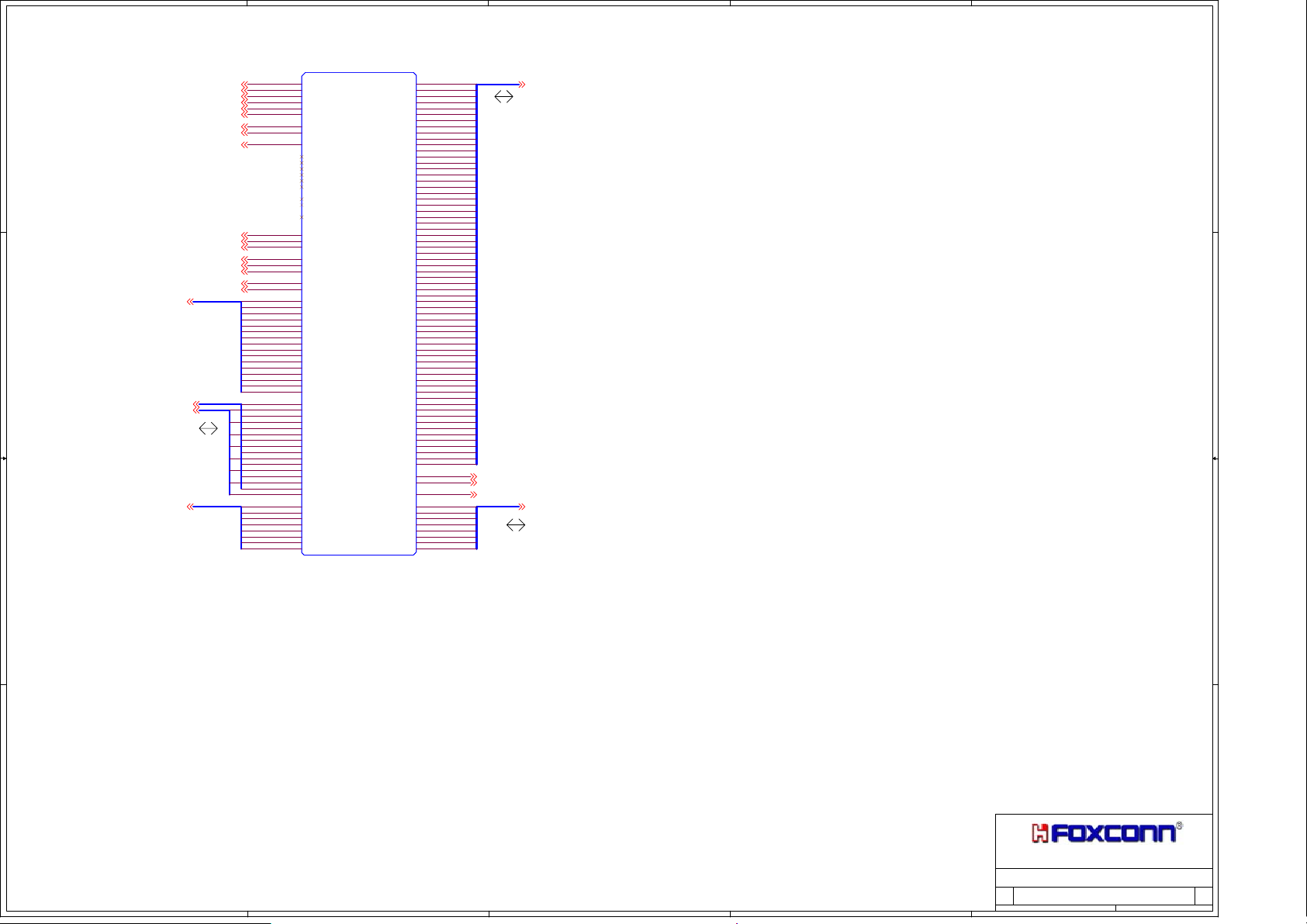

5

HT_RC_CPU_CLK_H114

HT_RC_CPU_CLK_L114

+1.2V_HT

D D

C C

GND

HT_RC_CPU_CAD_H[15..0]14

HT_RC_CPU_CAD_L[15..0]14

HT_RC_CPU_CLK_H014

HT_RC_CPU_CLK_L014

R283 49.9 r0603h6 +/-1%R283 49.9 r0603h6 +/-1%

R282 49.9 r0603h6 +/-1%R282 49.9 r0603h6 +/-1%

HT_RC_CPU_CTL_H014

HT_RC_CPU_CTL_L014

HT_RC_CPU_CAD_H15

HT_RC_CPU_CAD_L15

HT_RC_CPU_CAD_H14

HT_RC_CPU_CAD_L14

HT_RC_CPU_CAD_H13

HT_RC_CPU_CAD_L13

HT_RC_CPU_CAD_H12

HT_RC_CPU_CAD_L12

HT_RC_CPU_CAD_H11

HT_RC_CPU_CAD_L11

HT_RC_CPU_CAD_H10

HT_RC_CPU_CAD_L10

HT_RC_CPU_CAD_H9

HT_RC_CPU_CAD_L9

HT_RC_CPU_CAD_H8

HT_RC_CPU_CAD_L8

HT_RC_CPU_CAD_H7

HT_RC_CPU_CAD_L7

HT_RC_CPU_CAD_H6

HT_RC_CPU_CAD_L6

HT_RC_CPU_CAD_H5

HT_RC_CPU_CAD_L5

HT_RC_CPU_CAD_H4

HT_RC_CPU_CAD_L4

HT_RC_CPU_CAD_H3

HT_RC_CPU_CAD_L3

HT_RC_CPU_CAD_H2

HT_RC_CPU_CAD_L2

HT_RC_CPU_CAD_H1

HT_RC_CPU_CAD_L1

HT_RC_CPU_CAD_H0 HT_CPU_RC_CAD_H0

HT_RC_CPU_CAD_L0

HT_CPU_CTLIN_H1

HT_CPU_CTLIN_L1

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

4

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

U22A

U22A

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

AD5

AD4

AD1

AC1

HT_CPU_CTLOUT_H1

Y6

HT_CPU_CTLOUT_L1

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_CPU_RC_CLK_H1 14

HT_CPU_RC_CLK_L1 14

HT_CPU_RC_CLK_H0 14

HT_CPU_RC_CLK_L0 14

TP3TP3

1

TP2TP2

1

HT_CPU_RC_CTL_H0 14

HT_CPU_RC_CTL_L0 14

HT_CPU_RC_CAD_H15

HT_CPU_RC_CAD_L15

HT_CPU_RC_CAD_H14

HT_CPU_RC_CAD_L14

HT_CPU_RC_CAD_H13

HT_CPU_RC_CAD_L13

HT_CPU_RC_CAD_H12

HT_CPU_RC_CAD_L12

HT_CPU_RC_CAD_H11

HT_CPU_RC_CAD_L11

HT_CPU_RC_CAD_H10

HT_CPU_RC_CAD_L10

HT_CPU_RC_CAD_H9

HT_CPU_RC_CAD_L9

HT_CPU_RC_CAD_H8

HT_CPU_RC_CAD_L8

HT_CPU_RC_CAD_H7

HT_CPU_RC_CAD_L7

HT_CPU_RC_CAD_H6

HT_CPU_RC_CAD_L6

HT_CPU_RC_CAD_H5

HT_CPU_RC_CAD_L5

HT_CPU_RC_CAD_H4

HT_CPU_RC_CAD_L4

HT_CPU_RC_CAD_H3

HT_CPU_RC_CAD_L3

HT_CPU_RC_CAD_H2

HT_CPU_RC_CAD_L2

HT_CPU_RC_CAD_H1

HT_CPU_RC_CAD_L1

HT_CPU_RC_CAD_L0

3

HT_CPU_RC_CAD_H[15..0] 14

HT_CPU_RC_CAD_L[15..0] 14

2

1

B B

A1

A31

Layout: Add stitching caps if crossing plane split

HyperTransport Net Naming Convention

HT_"link driver"_"link receiver"_"function"_"polarity"_"number"

M2

Top View

AL1

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

M2 HyperTransport

M2 HyperTransport

M2 HyperTransport

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

1

732Wednesday, May 17, 2006

732Wednesday, May 17, 2006

732Wednesday, May 17, 2006

AC

AC

AC

of

of

of

Page 8

5

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

AC25

AA24

AC28

AE20

AE19

AD27

AA25

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

G19

H19

U27

U26

G20

G21

V27

W27

N25

Y27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

D29

C29

C25

D25

E19

G15

B29

E24

E18

H15

L27

F19

F15

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MEM_MA0_CLK_H212,13

MEM_MA0_CLK_L212,13

MEM_MA0_CLK_H112,13

MEM_MA0_CLK_L112,13

MEM_MA0_CLK_H012,13

D D

MEM_MA_ADD[15..0]12,13

C C

MEM_MA_DQS_H[7..0]12

MEM_MA_DQS_L[7..0]12

MEM_MA0_CLK_L012,13

MEM_MA0_CS_L112,13

MEM_MA0_CS_L012,13

MEM_MA0_ODT012,13

MEM_MA_CAS_L12,13

MEM_MA_WE_L12,13

MEM_MA_RAS_L12,13

MEM_MA_BANK212,13

MEM_MA_BANK112,13

MEM_MA_BANK012,13

MEM_MA_CKE113

MEM_MA_CKE012,13

MEM_MA_DM[7..0]12

B B

4

U22B

U22B

MEMORY INTERFACE A

MEMORY INTERFACE A

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_DQS_H8 12

MEM_MA_DQS_L8 12

MEM_MA_DM8 12

MEM_MA_DATA[63..0] 12

MEM_MA_CHECK[7..0] 12

3

2

1

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

M2- 2 DDR -1

M2- 2 DDR -1

M2- 2 DDR -1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

1

832Wednesday, May 17, 2006

832Wednesday, May 17, 2006

832Wednesday, May 17, 2006

AC

AC

AC

of

of

of

Page 9

5

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AK19

AE30

AC31

AD29

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AK17

AK23

AH17

AK29

AJ19

AL19

AL18

W29

W28

AJ13

AJ17

AL23

AL28

AL29

AJ14

AJ23

A18

A19

U31

U30

C19

D19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MEM_MB0_CLK_H212,13

MEM_MB0_CLK_L212,13

MEM_MB0_CLK_H112,13

MEM_MB0_CLK_L112,13

MEM_MB0_CLK_H012,13

MEM_MB0_CLK_L012,13

MEM_MB0_CS_L112,13

D D

MEM_MB_ADD[15..0]12,13

C C

MEM_MB_DQS_H[7..0]12

MEM_MB_DQS_L[7..0]12

MEM_MB0_CS_L012,13

MEM_MB0_ODT012,13

MEM_MB_CAS_L12,13

MEM_MB_WE_L12,13

MEM_MB_RAS_L12,13

MEM_MB_BANK212,13

MEM_MB_BANK112,13

MEM_MB_BANK012,13

MEM_MB_CKE113

MEM_MB_CKE012,13

MEM_MB_DM[7..0]12

U22C

U22C

MEMORY INTERFACE B

MEMORY INTERFACE B

4

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DQS_H8 12

MEM_MB_DQS_L8 12

MEM_MB_DM8 12

MEM_MB_DATA[63..0] 12

MEM_MB_CHECK[7..0] 12

3

2

1

B B

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

M2- 2 DDR -2

M2- 2 DDR -2

M2- 2 DDR -2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

K8M890M01

K8M890M01

K8M890M01

1

932Wednesday, May 17, 2006

932Wednesday, May 17, 2006

932Wednesday, May 17, 2006

AC

AC

AC

of

of

of

Page 10

5

Level translation buffers

Assuming system devices

Do not provide VDDIO

compatible voltage levels

Note:V1.0 CHANGE SCH.

+2.5V

VCC3

R329

R329

680

680

+/-5%

D D

R327

R327

*

CPU_PWRGD22

LDTSTOP_L14

C C

PCIRST#17,22,23

ALL_PWRGD16,19,22,30

Note 1

5-bit VID Implementation:

VID4:0 connects to VID4:0 of regulator*

VID5 should be left unconnected.

VID1 should be pulled up to VDDIO for compatibility with

future processors *

Translation may be needed to meet the input requirements

of the regulator inputs (See datasheet for processor Voh

specs & regulator datasheet for Vih min requirements)

6-bit VID Implementation:

VID5:0 directly connects to VID5:0 of regulator.

VID1 should be pulled up to VDDIO for compatibility with

future processors

B B

NOTE: There is an incompatibility between the 5-bit VID

code & 6-bit VID code x11111b. VID code 11111b is 慜FF

for 5-bit VID controllers & a valid VID code for 6-bit VID

controllers (011111b is 775mv & 111111b is 375mv). These

are not planned to be operating VID for non-mobile抯

processors so no adverse system implications will occur

using a 5-bit VID or 6-bit controller in non-mobile

implementations. Please see AMD Socket M2 Motherboard

Design Guide, PID #33165 for more details.

A A

0

0

R0603

R0603

+/-5%

+/-5%

R286

R286

*

*

0

0

R0603

R0603

+/-5%

+/-5%

CPUHS

CPUHS

HEATSINK_SOCKET_940_M2

HEATSINK_SOCKET_940_M2

BGA940_M2_1_27MM_HEATSINK

BGA940_M2_1_27MM_HEATSINK

5

6

7

8

9

10

11

12

1

2

13

14

15

16

17

18

19

20

I118

I118

5

*

R292

R292

*

*

0

0

R0603

R0603

+/-5%

+/-5%

MTG1

MTG1

MTG1

MTG1

MTG1

MTG1

MTG1

MTG1

EMI

EMI

MTG2

MTG2

MTG2

MTG2

MTG2

MTG2

MTG2

MTG2

+/-5%

r0603h6

r0603h6

R328

R328

1K

1K

+/-5%

+/-5%

R0603

R0603

2.5

R306

R306

*

*

1K

1K

r0603h6

r0603h6

+/-5%

+/-5%

R0603

R0603

r0603h6

r0603h6

R285

R285

*

*

1K

1K

+/-5%

+/-5%

R0603

R0603

r0603h6

r0603h6

DS

*

*

Q31

Q31

2N7002

2N7002

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=10V

7.5 Ohm Vgs=10V

G

+2.5V

VCC3

R601

R601

R606

R606

R307

R307

680

680

680

680

680

680

+/-5%

+/-5%

+/-5%

+/-5%

+/-5%

+/-5%

r0603h6

r0603h6

r0603h6

r0603h6

DS

Q29

Q29

2N7002

2N7002

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=10V

7.5 Ohm Vgs=10V

G

+2.5V

R602

R602

R284

R284

680

680

680

680

+/-5%

+/-5%

+/-5%

+/-5%

r0603h6

r0603h6

DS

Q26

Q26

2N7002

2N7002

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=10V

7.5 Ohm Vgs=10V

G

DS

Q27

Q27

2N7002

2N7002

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=10V

7.5 Ohm Vgs=10V

G

VCC3_SB

R600

R600

R605

R605

680

680

680

680

+/-5%

+/-5%

+/-5%

+/-5%

r0603h6

r0603h6

VCC3_SB

CPU_PWRGD_G

G

LDTSTOP_L_G

VCC3

VCC3_SB

R607

R607

680

680

+/-5%

+/-5%

r0603h6

r0603h6

*

*

These signals must be

driven low during S3

and S5 states, including

state transitions, to meet

HT I/O Link Specification

21

MTG3

22

MTG3

23

MTG3

24

MTG3

25

MTG3

26

MTG3

27

MTG3

28

MTG3

3

EMI

4

EMI

29

MTG4

30

MTG4

31

MTG4

32

MTG4

33

MTG4

34

MTG4

35

MTG4

36

MTG4

4

VDDA_25

*

*

Keep trace to resistor

less than 600mils from CPU pin and

VCC_DDR

R323

R323

*

*

300

300

+/-5%

+/-5%

R0603

R0603

DS

7.5 Ohm Vgs=10V

7.5 Ohm Vgs=10V

G

PCIRST#_G

Keep trace to resistors less

than 1.5" from CPU pin

dummy

dummy

Erratum 133, Revision Guide for

+/-5%

+/-5%

R0603

R0603

AMD NPT 0Fh Processors

0

0

R322

R322

GND

trace to AC caps less than 1250mils

CPU_CLKIN_H5

R291

R291

R321

R321

*

*

*

*

300

300

300

300

+/-5%

+/-5%

+/-5%

+/-5%

R0603

R0603

Q32

Q32

2N7002

2N7002

SOT23_GSD

SOT23_GSD

DS

G

ALL_PWRGD16,19,22,30

R0603

R0603

Q30

Q30

2N7002

2N7002

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=10V

7.5 Ohm Vgs=10V

DS

Q28

Q28

2N7002

2N7002

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=10V

7.5 Ohm Vgs=10V

4

CPU_CLKIN_L5

CPU_SIC23

CPU_SID23

CP2001

CP2001

X_COPPER

X_COPPER

L38

L38

X_FB L0805 200 Ohm

X_FB L0805 200 Ohm

dummy

dummy

C362

C362

22uF

22uF

C1206

C1206

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

dummy

dummy

VCC_DDR

GND

CPU_PWRGD22

LDTSTOP_L14

PCIRST#17,22,23

21

dummy

dummy

C317 3.9nF C0603 50V, X7R, +/-10%

C317 3.9nF C0603 50V, X7R, +/-10%

*

*

C314 3.9nF C0603 50V, X7R, +/-10%

C314 3.9nF C0603 50V, X7R, +/-10%

*

*

VCC_DDR

R295

R295

R293

R293

*

*

*

*

300

300

300

300

+/-5%

+/-5%

+/-5%

+/-5%

R0603

R0603

R0603

R0603

dummy

dummy

dummy

dummy

R294

R294

*

*

300

300

+/-5%

+/-5%

R0603

R0603

GND

R318 39.2 R0603 +/-1%

R318 39.2 R0603 +/-1%

*

*

R317 39.2 R0603 +/-1%

R317 39.2 R0603 +/-1%

*

*

R312 300 R0603 +/-5%

R312 300 R0603 +/-5%

R313 300 R0603 +/-5%

R313 300 R0603 +/-5%

GND

CPU_THERMDC23

CPU_THERMDA23

3

CPU_VDDA_RUN

C338

C339

C339

3.3nF

3.3nF

*

*

C0603

C0603

16V, NPO, +/-5%

16V, NPO, +/-5%

CPU_CLKIN_SC_H

CPU_ALL_PWROK

CPU_LDTSTOP_L

CPU_HT_RESET_L

CPU_PRESENT_L

M_ZN

M_ZP

CPU_TEST25_H

CPU_TEST25_L

*

*

3

6

8

11

C338

0.22uF

0.22uF

*

*

C0603

C0603

GND

C800

C800

0.1uF

0.1uF

C0603

C0603

dummy

dummy

CPU_PWRGD_G

LDTSTOP_L_G

PCIRST#_G

10V, X7R, +/-10%

10V, X7R, +/-10%

AH10

AH11

AL10

AJ10

AJ11

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL9

A5

G2

G1

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

AE27

AE28

AG31

AF31

3

U22D

U22D

MISC

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

THERMTRIP_L

SIC

PROCHOT_L

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDDIO_FB_H

VDD_FB_H

VDDIO_FB_L

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST29_H

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

L25

L26

L31

L30

W26

W25

U24

V24

Y31

Y30

V31

W31

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

TEST29_L

TEST28_H

TEST28_L

U22E

U22E

INTERNAL MISC

INTERNAL MISC

CPU_M_VREF_SUS

VCC_DDR

C349

C349

4.7uF

4.7uF

*

*

C0805

C0805

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

R308

R308

*

*

169

169

+/-1%

+/-1%

CPU_CLKIN_SC_L

R0603

R0603

CPU_SIC

CPU_SID

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

CPU_VDD_RUN_FB_H6

CPU_VDD_RUN_FB_L6

TP6TP6

1

CPU_M_VREF_SUS

*

*

*

*

TP11TP11

1

CPU_TEST16

TP17TP17

1

CPU_TEST15

TP26TP26

1

CPU_TEST14

TP13TP13

1

CPU_TEST12

TP23TP23

1

CPU_THERMDC

CPU_THERMDA CPU_TEST26

VCC3_SB

147

U58A

U58A

1

2

SN74LVC00APWR

SN74LVC00APWR

VCC3_SB

147

U58B

U58B

4

5

SN74LVC00APWR

SN74LVC00APWR

VCC3_SB

147

U58C

U58C

9

10

SN74LVC00APWR

SN74LVC00APWR

VCC3_SB

147

U58D

U58D

12

13

SN74LVC00APWR

SN74LVC00APWR

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

DBRDY

PSI_L

HTREF1

HTREF0

TEST24

TEST23

TEST22

TEST21

TEST20

TEST27

TEST26

TEST10

TEST8

R320

R320

16.9

16.9

+/-1%

+/-1%

r0603h6

r0603h6

R319

R319

16.9

16.9

+/-1%

+/-1%

r0603h6

r0603h6

TDO

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

2

CPU Control & Debug Interfaces

Required for compatibility

with future processors

CPU_VID5

D2

CPU_VID4

D1

CPU_VID3

C1

CPU_VID2

E3

CPU_VID1

E2

CPU_VID0

E1

CPU_THERMTRIP_L

AK7

CPU_PROCHOT_L_1.8

AL7

CPU_TDO

AK10

CPU_DBRDY

B6

CPU_VDDIO_SUS_FB_H

AK11

CPU_VDDIO_SUS_FB_L

AL11

CPU_PSI_LCPU_VTT_SUS_SENSE

F1

CPU_HTREF1

V8

CPU_HTREF0

V7

CPU_TEST29_H

C11

CPU_TEST29_L

D11

CPU_TEST24CPU_TEST17

AK8

CPU_TEST23

AH8

CPU_TEST22

AJ9

CPU_TEST21

AL8

CPU_TEST20

AJ8

J10

H9

AK9

AK5

G7

D4

E20

B19

AL4

AK4

AK3

F2

F3

G4

G3

G5

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

C323

C323

*

*

0.1uF

0.1uF

C0603

C0603

1

CPU_M_VREF_SUS

C322

C322

1nF

1nF

*

*

C0603

C0603

GND

VCC_DDR

R315

R315

R314

R314

300

300

300

300

*

*

*

*

+/-5%

+/-5%

+/-5%

+/-5%

R0603

R0603

R0603

R0603

TP10TP10

TP8TP8

1

R296 44.2 r0603h6 +/-1%R296 44.2 r0603h6 +/-1%

R297 44.2 r0603h6 +/-1%R297 44.2 r0603h6 +/-1%

TP18TP18

1

TP22TP22

1

TP24TP24

1

TP4TP4

1

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

R309

R309

300

300

*

*

+/-5%

+/-5%

R0603

R0603

VCC_DDR

*

*

135

R324

R324

80.6

80.6

+/-1%

+/-1%

r0603h6

r0603h6

CPU_TEST26

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST21

Layout: Place near CPU socket

2

+/-5%

+/-5%

78

8P4R0603

8P4R0603

300

300

642

RN30

RN30

dummy

dummy

VREG_VID4 6

VREG_VID3 6

VREG_VID2 6

VREG_VID1 6

VREG_VID0 6

CPU_THERMTRIP* 22

+1.2V_HT

Keep trace to resistors

less than 1.5" from CPU pin

GND

Route as 80-Ohm differential impedance

Keep trace to resistor less than 1" from CPU pin

R298 300 R0603 +/-5%

R298 300 R0603 +/-5%

*

*

R299 1K r0603h6 +/-5%R299 1K r0603h6 +/-5%

R311 510 r0603h6 +/-1%R311 510 r0603h6 +/-1%

R310 510 r0603h6 +/-1%R310 510 r0603h6 +/-1%

R316 300 R0603 +/-5%

R316 300 R0603 +/-5%

*

*

Voltage translation to meet VIH min of regulator

CPU_DBREQ_L

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST_L

CPU_TDO

VCC_DDR

GND

Title

Title

Title

M2- 3 MISC

M2- 3 MISC

M2- 3 MISC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

CPU_CLKIN_H

CPU_CLKIN_L

CPU_VDD_RUN_FB_H

CPU_VDD_RUN_FB_L

CPU_TEST29_H

CPU_TEST29_L

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_ALL_PWROK

CPU_LDTSTOP_L

CPU_HT_RESET_L

CPU_THERMTRIP_L

K8M890M01

K8M890M01

K8M890M01

1

See Note 1

TP1TP1

1

TP16TP16

1

TP25TP25

1

TP19TP19

1

TP29TP29

1

TP27TP27

1

TP12TP12

1

CPU_VDDA_RUN

TP28TP28

1

TP7TP7

1

TP9TP9

1

TP2005TP2005

1

TP2004TP2004

1

TP2029TP2029

1

TP5TP5

1

TP31TP31

1

TP30TP30

1

TP2030TP2030

1

TP20TP20

1

TP15TP15

1

TP21TP21

1

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

10 32Friday, June 09, 2006

10 32Friday, June 09, 2006

1

10 32Friday, June 09, 2006

AC

AC

AC

of

of

of

Page 11

5

4

3

2

1

Processor Power & Ground

D D

VLDT_RUN_B is connected to the VLDT_RUN power

supply through the package or on the die. It is only connected

+V_CPU

C C

B B

AA10

AA12

AA14

AA16

AA18

AB11

AC10

AE10

U22F

U22F

VDD1

VDD1

A4

VDD1

A6

VDD2

AA8

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

AB7

VDD9

AB9

VDD10

VDD11

AC4

VDD12

AC5

VDD13

AC8

VDD14

VDD15

AD2

VDD16

AD3

VDD17

AD7

VDD18

AD9

VDD19

VDD20

AF7

VDD21

AF9

VDD22

AG4

VDD23

AG5

VDD24

AG7

VDD25

AH2

VDD26

AH3

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

E10

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

G10

VDD49

G12

VDD50

H7

VDD51

H11

VDD52

H23

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

K11

VDD64

K13

VDD65

K15

VDD66

K17

VDD67

K19

VDD68

K21

VDD69

K23

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

Y17

VDD150

Y19

VDD151

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

GND

+V_CPU

W10

W12

W14

W16

W18

W20

U22G

U22G

VDD2

VDD2

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

GND

+V_CPU

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

U22H

U22H

VDD3

VDD3

N17

VSS1

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

M21

VDD21

M23

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

W22

VDD31

Y23

VDD32

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

N19

N21

N23

P2

P3

P8

P10