Page 1

5

4

3

2

1

CK804A07

D D

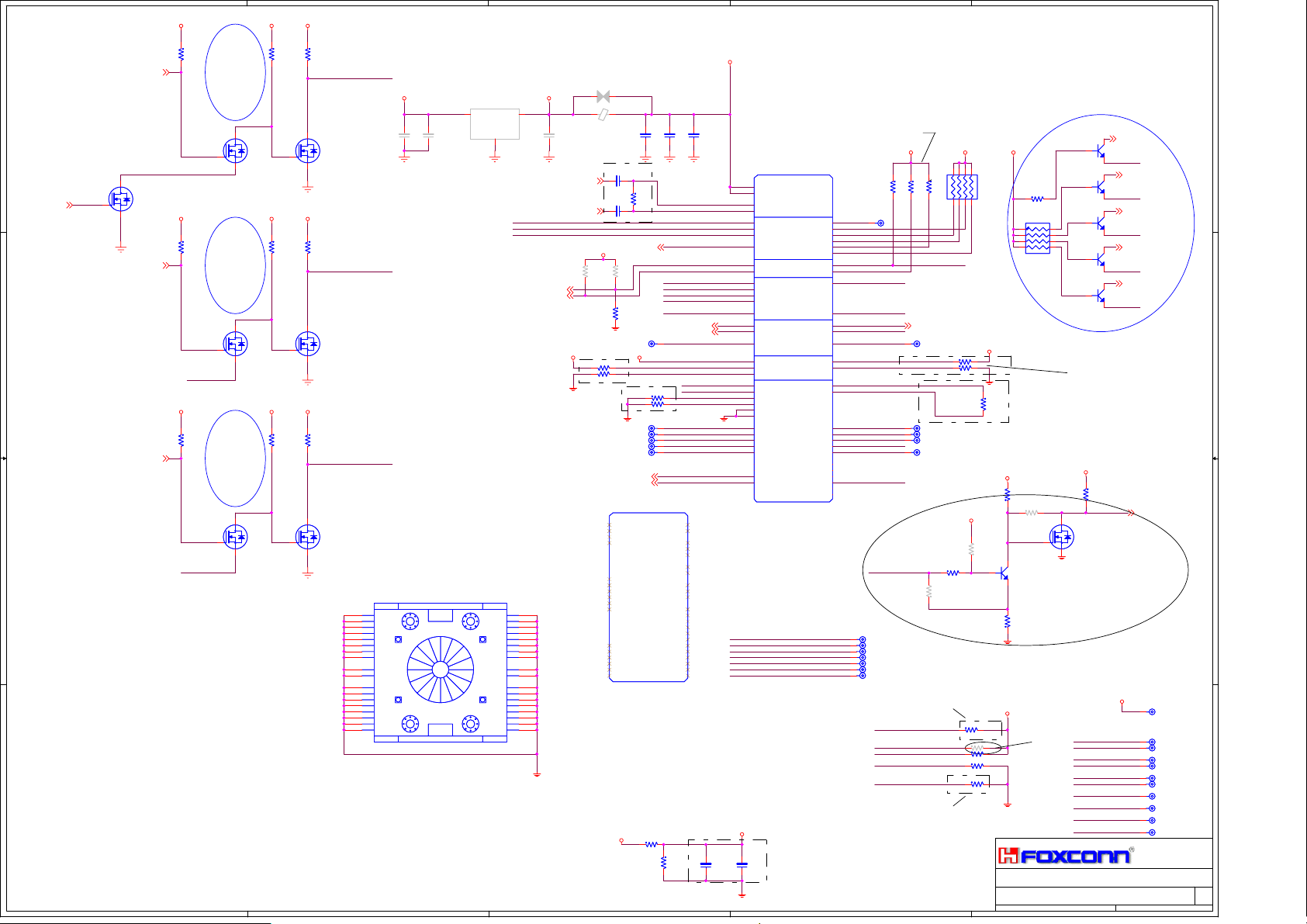

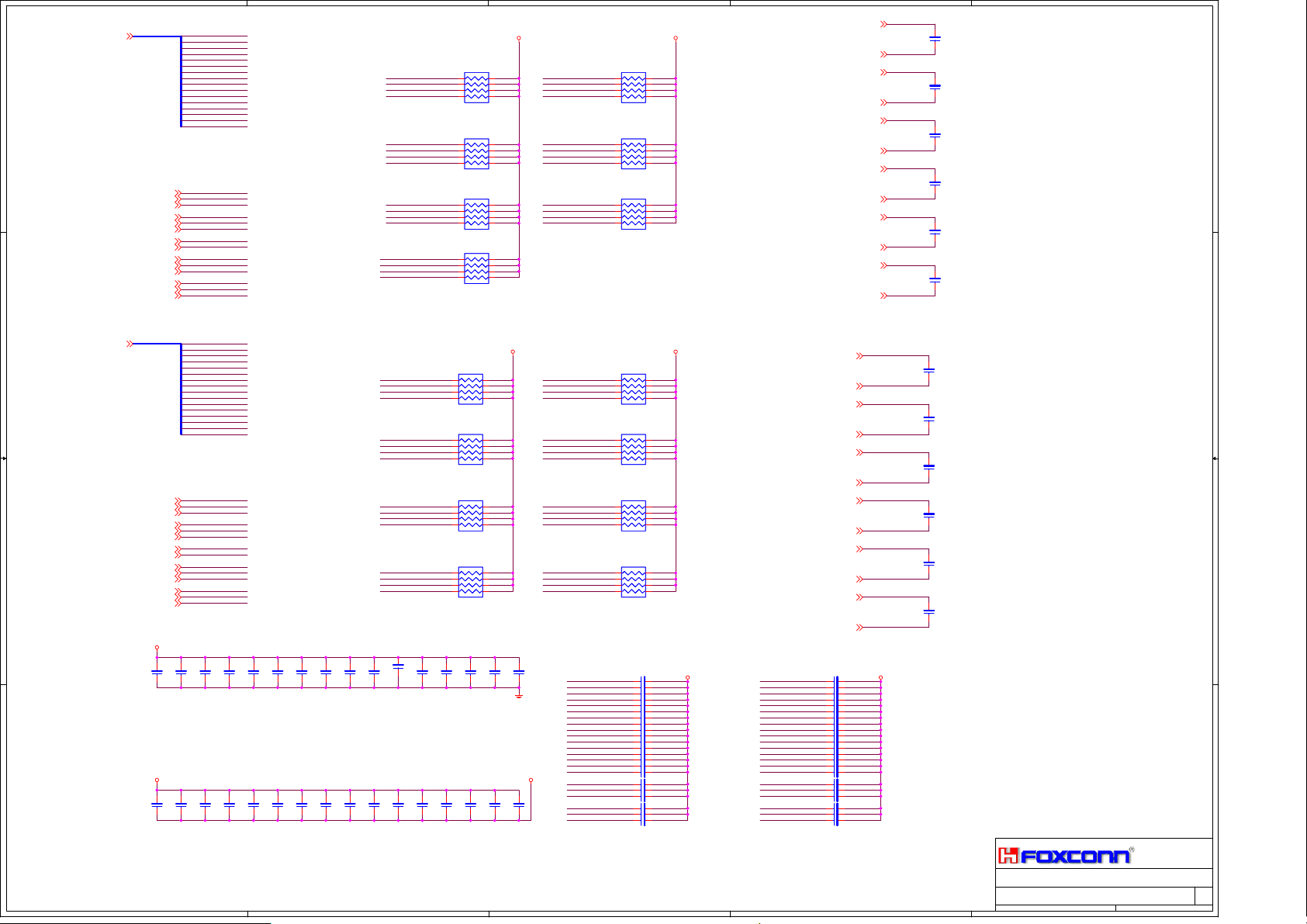

nVIDIA CK804 Chipset forAM2 CPU

10/25/2006)

PAGE PAGECONTENT CONTENT

1

2

3

4

C C

5

6

7

8

9

10

11

12

13

14

B B

15

16

17

18

19

20

21

Index

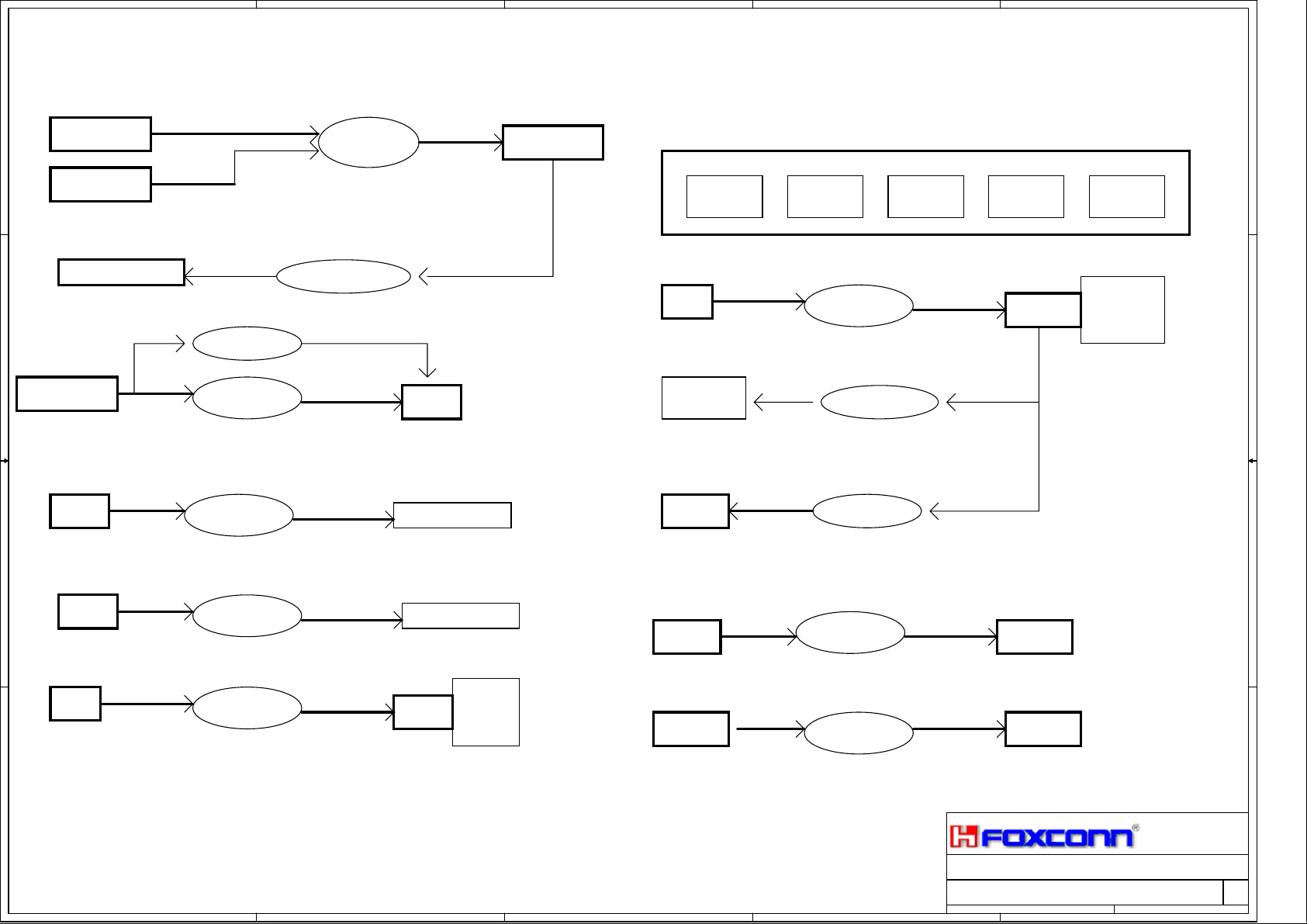

Topology

RESET MAP

CLOCK DISTRIBUTION

Power Delivery

M2-1 Hyper Transport

M2-2 DDR-1

M2-2 DDR-2

M2-4 MISC

M2-5 Power

DDRII SDRAM DIMM1-2

DDRII SDRAM DIMM3-4

DDRTerminator

CK804 HT

CK804 PCI EXPRESS

CK804 PCI

CK804 SATA / IDE

CK804 G/MII / AC97 / USB

CK804 DECOUPLING

PCI EXPRESS X16 CONNECTOR

PCI EXPRESS X1 CONNECTORS

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

42

PCI CONNECTOR 1-2

PCI CONNECTOR 3-4

PCI TERMINATION

VT6307/6308

LAN RTL8211BL

FWH & SPI

USB CONNECTORS

IDE CONNECTORS

AUDIO 653/850

AUDIO CONNECTORS 653/850

SIO ITE8716

FDD / PS2

FAN / HARDWARE MONITOR

PRT COM PORT

PWM ST L6711 AM2

DDR POWER

CK804 CORE

Power sequence

PWR CON / FNT PNL / VBAT

VID CONTROLLER

CHANGELIST

42

A A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Index

Index

Index

CK804A07

CK804A07

CK804A07

1

TECHNOLOGY COPR.

of

142Tuesday, October 31, 2006

of

142Tuesday, October 31, 2006

of

142Tuesday, October 31, 2006

A

A

A

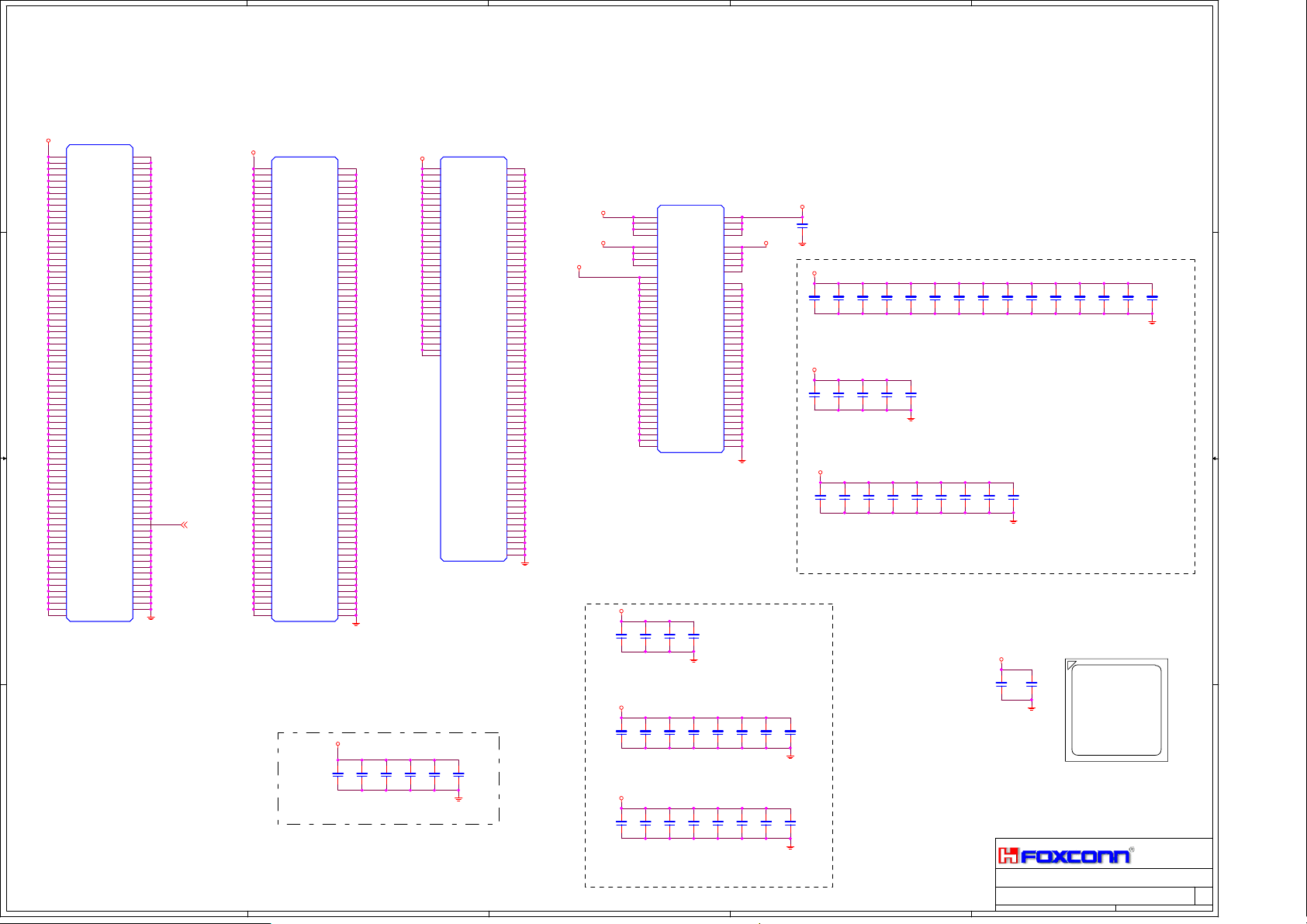

Page 2

5

4

3

2

1

D D

POWER

SUPPLY

CONNECTOR

PEX X1

PEX X16

PEX X1 (2)

C C

PRIMARY IDE

SECONDARY IDE

X4 - SATA CONN

FLOPPY CONN

PS2/KBRD CONN

PARALLEL CONN

SERIAL CONN

B B

SIO

ITE IT8712F

VREG

PCI EXPRESS/NEW CARD

PCI EXPRESS

PCI EXPRESS

ATA 133

INTEGRATED SATA

LPC BUS 33MHZ

4MB FLASH

BLOCK DIAGRAM

SOCKET 940

AM2

HT 16X16 1GHZ

NFORCE

CRUSH K804

RGMII

PCI 33MHZ

AC97

X10 USB2

MII/RGMII

AC97

BACK PANEL CONN

USB2 PORTS 4-5

QUAD STACK

USB2 PORTS 8-9

FRONT PANEL HDR

USB2 PORTS 1-0

USB2 PORTS 7-6

DDR SDRAM CONN A1

DDR SDRAM CONN B1

DDR SDRAM CONN A2

DDR SDRAM CONNB2

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

X2/GBIT LAN

A A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

Index

Index

Index

CK804A07

CK804A07

CK804A07

1

TECHNOLOGY COPR.

of

242Tuesday, October 31, 2006

242Tuesday, October 31, 2006

242Tuesday, October 31, 2006

A

A

A

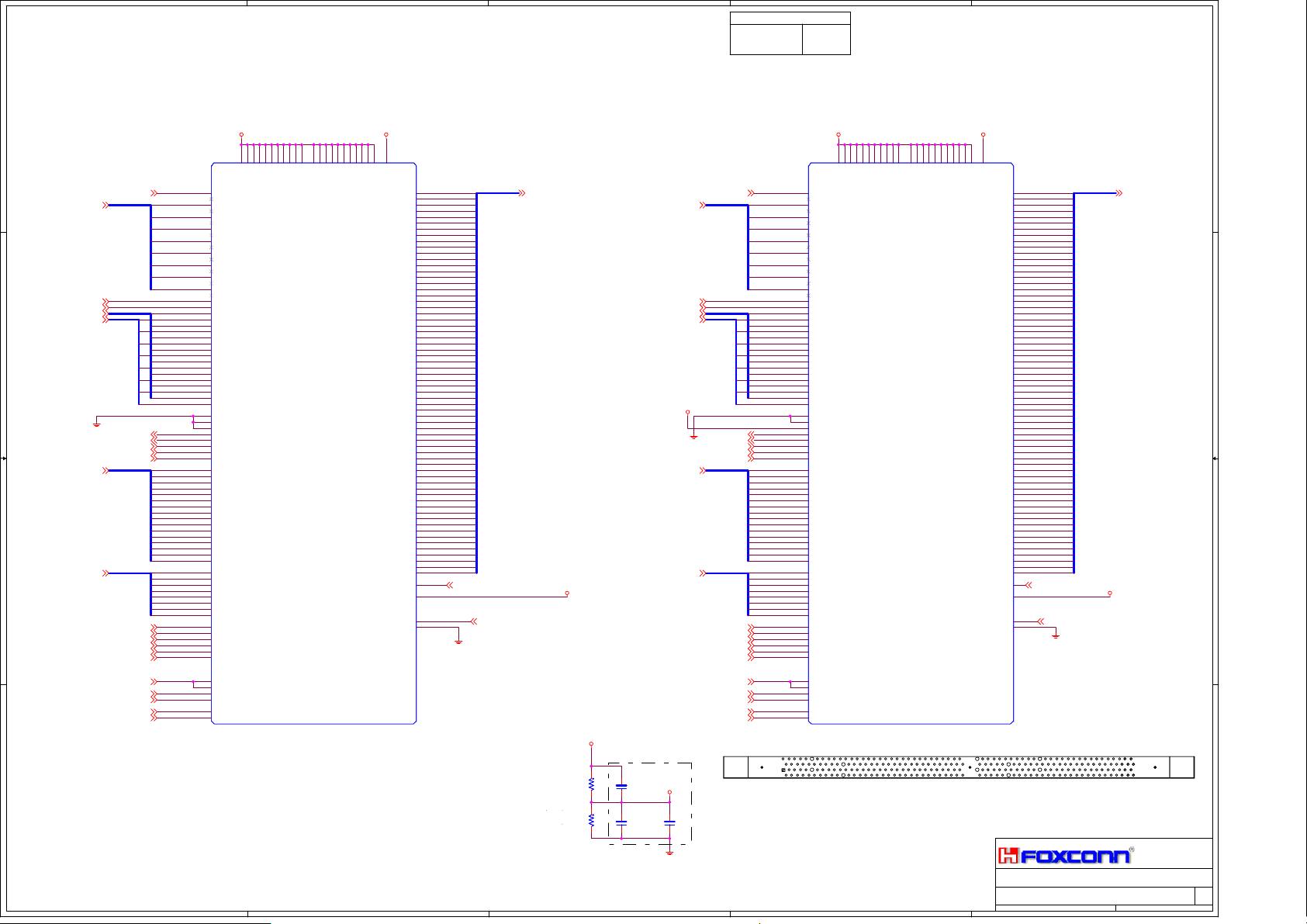

Page 3

5

4

3

2

1

RESET MAP

D D

AM2

CPU RST*

CPU PWRGD

C C

CPU_RST*

CPU_PWRGD

PWR SWTCH

CK804

PWR CONN

PS ON

PWR GOOD

PWRGD SB

B B

CIRCUIT

SLP_S3*

POWER_GOOD

PEX X16

PWRBTN*

PWRGD_SB

PWR BUTTON

SLP S3*

PWRGD

PWRGD_SB

PE_RESET*

CPU PWRGD

CPU RST*

PCI RST0*

PCI RST1*

PCI RST2*

PCI RST3*

LPC_RST*

GPIO_AUX*

CPU_PWRGD

CPU_RST*

PCIRST_SLOT1*

PCIRST_SLOT2*

PCIRST_SLOT3-4*

PCIRST_IDE*

LPCRST_FLASH*

LPCRST_SIO*

SIO

FLASH

PRI IDE

PCI SLOT 3

PCI SLOT 4SEC IDE

PCI SLOT 2

PCI SLOT 1394

1394

PEX X1(2)

PEX X1NC

A A

5

4

LAN_PHY

RESET*

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

Reset Map

Reset Map

Reset Map

CK804A07

CK804A07

CK804A07

TECHNOLOGY COPR.

of

342Tuesday, October 31, 2006

of

342Tuesday, October 31, 2006

of

342Tuesday, October 31, 2006

1

A

A

A

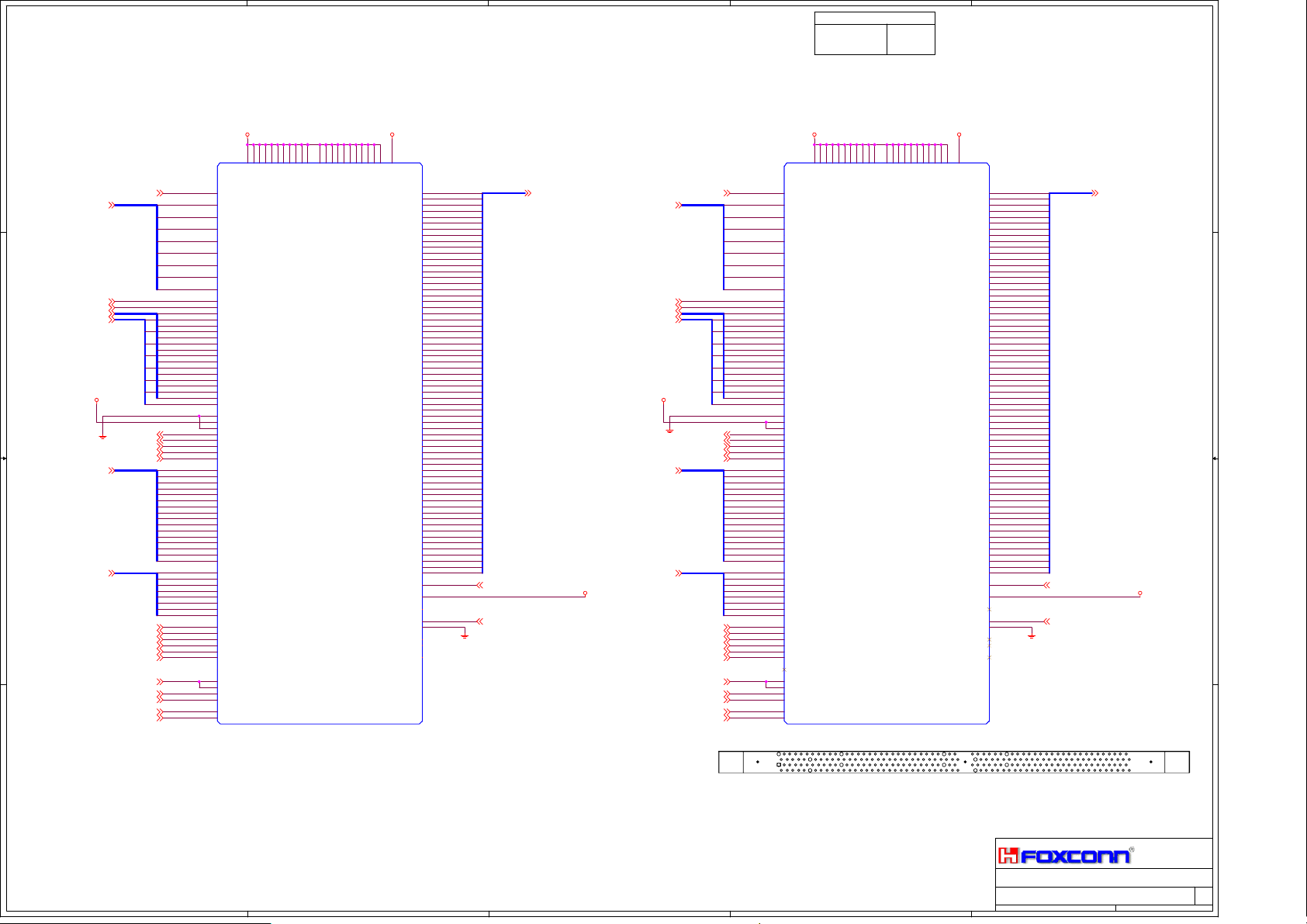

Page 4

5

4

3

2

1

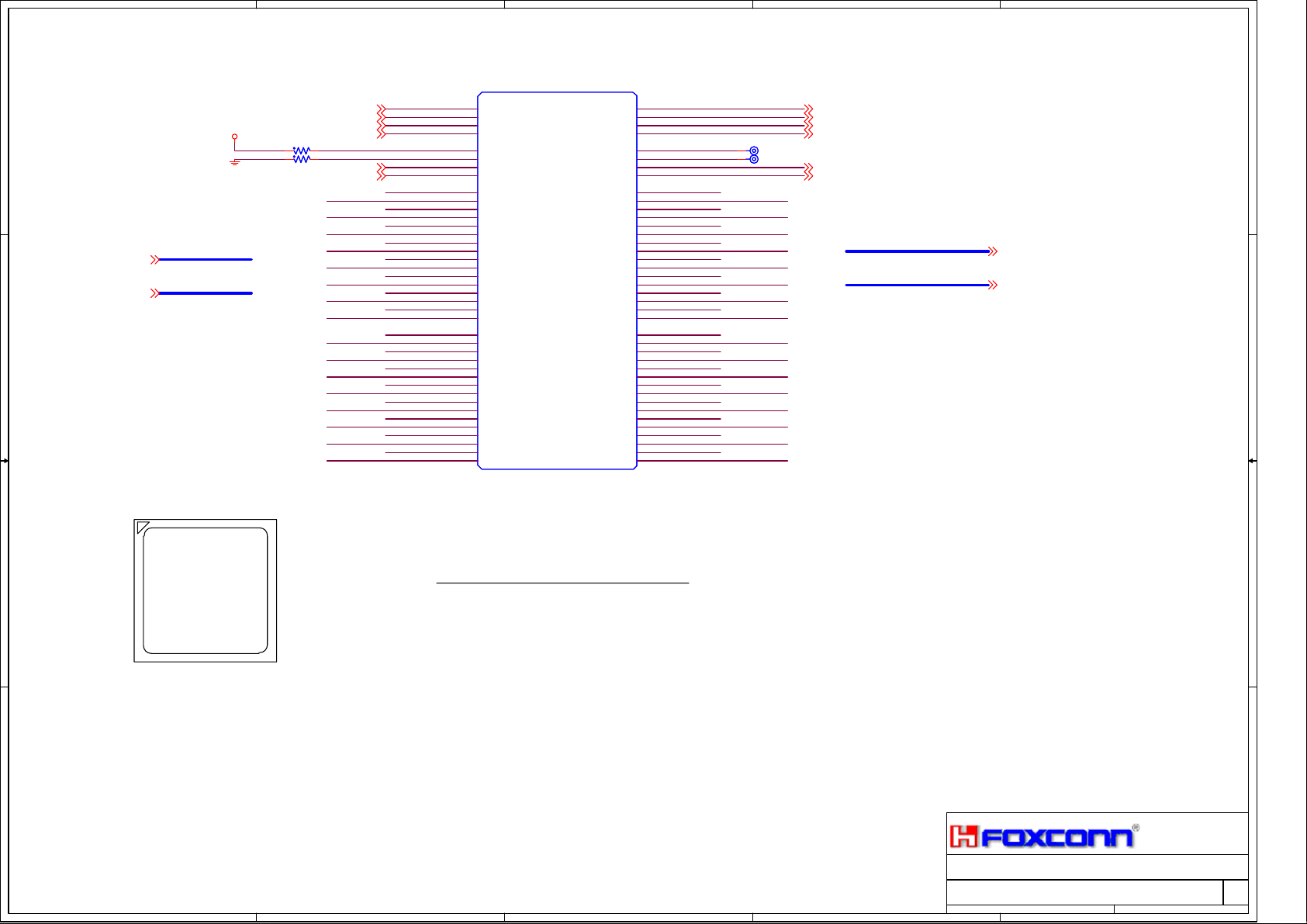

K8 AM2 CPU

L0_CLKIN_H(1)

L0_CLKIN_L(1)

D D

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

CPU_CLK_IN*

CPU_CLK_IN

MEMORY_A0_CLK[2:0]

MEMORY_A0_CLK[2:0]*

MEMORY_B0_CLK[2:0]

MEMORY_B0_CLK[2:0]*

MEMORY_A1_CLK[2:0]

MEMORY_A1_CLK[2:0]*

MEMORY_B1_CLK[2:0]

MEMORY_B1_CLK[2:0]*

CHANNEL A1 0-63

CHANNEL B1 0-63

CHANNEL A2 0-63

CHANNEL B2 0-63

DIMM A1

DIMM B1

DIMM A2

DIMM B2

CK804

CPU_CLK_IN

CPU_CLK_IN*

HT_RXCLK0*

HT_RXCLK0

HT_RXCLK1*

HT_RXCLK1

C C

32.0 KHZ

25 MHZ

B B

HT_TXCLK1*

HT_TXCLK1

HT_TXCLK0*

HT_TXCLK0

XTAL_IN

XTAL_OUT

XTAL_IN

XTAL_OUT

PE0_REFCLK

PE0_REFCLK*

PE1_REFCLK

PE1_REFCLK*

PE2_REFCLK

PE2_REFCLK*

PE3_REFCLK

PE3_REFCLK*

BUF_SIO

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK5

PCI_CLK_FB

AC_97CLK

AC_BITCLK

BUF_25MHZ

SUSCLK

LPC_CLK1

14MHZ OR 24MHZ

AC '97 LINK

SIO

AC97

CODEC

PEX X16

PEX X1

PEX X1

PCI SLOT 2

PCI SLOT 1

PCI SLOT 3

PCI SLOT 4

PCI_CLKLPC

1394

A A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Clock Distribution

Clock Distribution

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

5

4

3

2

Clock Distribution

CK804A07

CK804A07

CK804A07

TECHNOLOGY COPR.

of

442Tuesday, October 31, 2006

of

442Tuesday, October 31, 2006

of

442Tuesday, October 31, 2006

1

A

A

A

Page 5

5

4

3

2

1

D D

+5V

AOD4600

+5V_DUAL

POWER CONN

+5V_STBY

12V_SYS 5V_SYS 3.3V_SYS 5V_STBY -12V_SYS

3D3V__DUAL

C C

3D3V_SYS/5V_SYS

3D3V_SYS

AP15N03H

AME8800 +2.5V

RT9166A-15PXL +1.5V_SP_PLLPWR

AZ1084D-ADJTRE1

5V_DUAL

VTT_DDR

1D2V_HT

RT9214PS 1D8V_STR

RT9173

AP15N03H

MEM-POWER

B B

12V_SYS

12V_VRM

A A

5

LM78L05 5V_AUDIO

L6711TR +V_CPU

4

CPU-POWER

3

3.3V_DUAL

5V_SYS

RT9166A-15PXL

RT9214PS

2

+1.5V_DUAL

1D5V_CORE

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Reset Map

Reset Map

Reset Map

CK804A07

CK804A07

CK804A07

TECHNOLOGY COPR.

of

541Tuesday, October 31, 2006

of

541Tuesday, October 31, 2006

of

541Tuesday, October 31, 2006

1

A

A

A

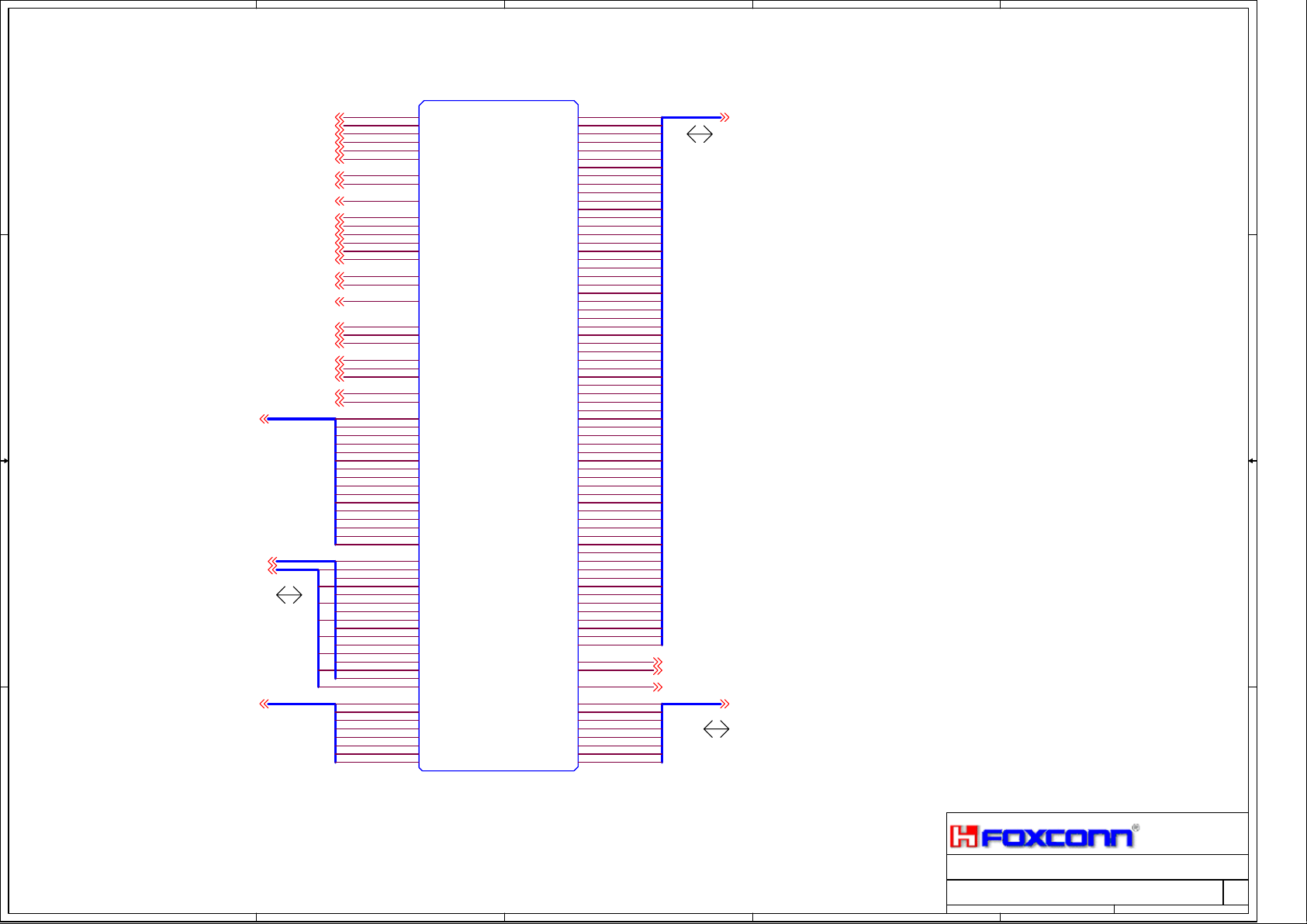

Page 6

5

HT_UPCLK114

D D

HT_UP[15..0]14

HT_UP*[15..0]14

C C

HT_UP[15..0]

HT_UP*[15..0]

1D2V_HT

GND

R100 49.9 r0603h6 +/-1%R100 49.9 r0603h6 +/-1%

R101 49.9 r0603h6 +/-1%R101 49.9 r0603h6 +/-1%

HT_UPCLK1*14

HT_UPCLK014

HT_UPCLK0*14

HT_UPCNTL14

HT_UPCNTL*14

HT_UP*15

HT_UP*14

HT_UP*13

HT_UP*12

HT_UP*11

HT_UP*10

HT_UP*9

HT_UP*8

HT_UP*7

HT_UP*6

HT_UP*5

HT_UP*4

HT_UP*3

HT_UP*2

HT_UP*1

HT_UP*0

4

HT_UPCLK1

HT_UPCLK1*

HT_UPCLK0

HT_UPCLK0*

HT_CPU_CTLIN_H1

HT_CPU_CTLIN_L1

HT_UPCNTL

HT_UPCNTL*

HT_UP15

HT_UP14

HT_UP13

HT_UP12

HT_UP11

HT_UP10

HT_UP9

HT_UP8

HT_UP7

HT_UP6

HT_UP5

HT_UP4

HT_UP3

HT_UP2

HT_UP1

HT_UP0

N6

L0_CLKIN_H(1)

P6

L0_CLKIN_L(1)

N3

L0_CLKIN_H(0)

N2

L0_CLKIN_L(0)

V4

L0_CTLIN_H(1)

V5

L0_CTLIN_L(1)

U1

L0_CTLIN_H(0)

V1

L0_CTLIN_L(0)

U6

L0_CADIN_H(15)

V6

L0_CADIN_L(15)

T4

L0_CADIN_H(14)

T5

L0_CADIN_L(14)

R6

L0_CADIN_H(13)

T6

L0_CADIN_L(13)

P4

L0_CADIN_H(12)

P5

L0_CADIN_L(12)

M4

L0_CADIN_H(11)

M5

L0_CADIN_L(11)

L6

L0_CADIN_H(10)

M6

L0_CADIN_L(10)

K4

L0_CADIN_H(9)

K5

L0_CADIN_L(9)

J6

L0_CADIN_H(8)

K6

L0_CADIN_L(8)

U3

L0_CADIN_H(7)

U2

L0_CADIN_L(7)

R1

L0_CADIN_H(6)

T1

L0_CADIN_L(6)

R3

L0_CADIN_H(5)

R2

L0_CADIN_L(5)

N1

L0_CADIN_H(4)

P1

L0_CADIN_L(4)

L1

L0_CADIN_H(3)

M1

L0_CADIN_L(3)

L3

L0_CADIN_H(2)

L2

L0_CADIN_L(2)

J1

L0_CADIN_H(1)

K1

L0_CADIN_L(1)

J3

L0_CADIN_H(0)

J2

L0_CADIN_L(0)

U1A

U1A

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

3

AD5

AD4

AD1

AC1

HT_CPU_CTLOUT_H1

Y6

HT_CPU_CTLOUT_L1

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_DWN15

HT_DWN14

HT_DWN13

HT_DWN12

HT_DWN11

HT_DWN10

HT_DWN9

HT_DWN8

HT_DWN7

HT_DWN6

HT_DWN5

HT_DWN4

HT_DWN3

HT_DWN2

HT_DWN1

HT_DWN0

HT_DWNCLK1

HT_DWNCLK1*

HT_DWNCLK0

HT_DWNCLK0*

1

1

HT_DWNCNTL

HT_DWNCNTL*

HT_DWN*15

HT_DWN*14

HT_DWN*13

HT_DWN*12

HT_DWN*11

HT_DWN*10

HT_DWN*9

HT_DWN*8

HT_DWN*7

HT_DWN*6

HT_DWN*5

HT_DWN*4

HT_DWN*3

HT_DWN*2

HT_DWN*1

HT_DWN*0

TP1TP1

TP2TP2

2

HT_DWNCLK1 14

HT_DWNCLK1* 14

HT_DWNCLK0 14

HT_DWNCLK0* 14

HT_DWNCNTL 14

HT_DWNCNTL* 14

HT_DWN[15..0]

HT_DWN*[15..0]

1

HT_DWN[15..0] 14

HT_DWN*[15..0] 14

A1

B B

M2

Top View

A31

Layout: Add stitching caps if crossing plane split

HyperTransport Net Naming Convention

HT_"link driver"_"link receiver"_"function"_"polarity"_"number"

AL1

A A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

M2-1 Hyper Transport

M2-1 Hyper Transport

M2-1 Hyper Transport

CK804A07

CK804A07

CK804A07

TECHNOLOGY COPR.

of

641Tuesday, October 31, 2006

of

641Tuesday, October 31, 2006

of

641Tuesday, October 31, 2006

1

A

A

A

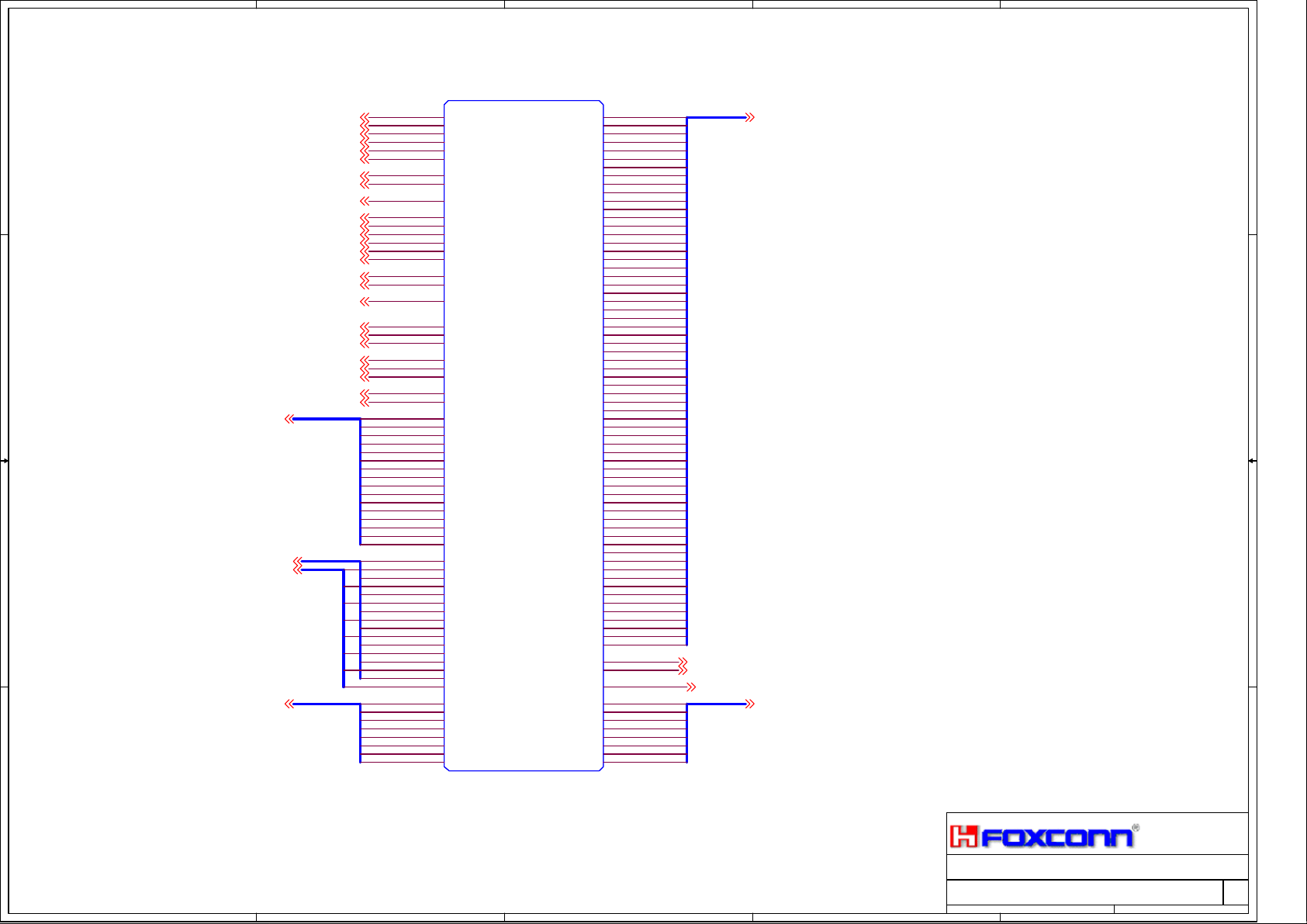

Page 7

5

D D

MEM_MA0_CLK_H211,13

MEM_MA0_CLK_L211,13

MEM_MA0_CLK_H111,13

MEM_MA0_CLK_L111,13

MEM_MA0_CLK_H011,13

MEM_MA0_CLK_L011,13

MEM_MA0_CS_L111,13

MEM_MA0_CS_L011,13

MEM_MA0_ODT011,13

MEM_MA1_CLK_H212,13

MEM_MA1_CLK_L212,13

MEM_MA1_CLK_H112,13

MEM_MA1_CLK_L112,13

MEM_MA1_CLK_H012,13

MEM_MA1_CLK_L012,13

MEM_MA1_CS_L112,13

MEM_MA1_CS_L012,13

MEM_MA1_ODT012,13

MEM_MA_CAS_L11,12,13

MEM_MA_WE_L11,12,13

C C

MEM_MA_RAS_L11,12,13

MEM_MA_BANK211,12,13

MEM_MA_BANK111,12,13

MEM_MA_BANK011,12,13

MEM_MA_CKE112,13

MEM_MA_CKE011,13

MEM_MA_ADD[15..0]11,12,13

MEM_MA_DQS_H[7..0]11,12

B B

MEM_MA_DQS_L[7..0]11,12

MEM_MA_DM[7..0]11,12

4

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

G19

H19

U27

U26

AC25

AA24

AC28

AE20

AE19

G20

G21

V27

W27

AD27

AA25

AC27

AB25

AB27

AA26

N25

Y27

AA27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

F19

F15

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

L27

MEMORY INTERFACE A

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

U1B

U1B

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

3

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_DATA[63..0] 11,12

MEM_MA_DQS_H8 11,12

MEM_MA_DQS_L8 11,12

MEM_MA_DM8 11,12

MEM_MA_CHECK[7..0] 11,12

2

1

A A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

M2-2 DDR-1

M2-2 DDR-1

M2-2 DDR-1

CK804A07

CK804A07

CK804A07

TECHNOLOGY COPR.

of

741Tuesday, October 31, 2006

of

741Tuesday, October 31, 2006

of

741Tuesday, October 31, 2006

1

A

A

A

Page 8

5

D D

MEM_MB0_CLK_H211,13

MEM_MB0_CLK_L211,13

MEM_MB0_CLK_H111,13

MEM_MB0_CLK_L111,13

MEM_MB0_CLK_H011,13

MEM_MB0_CLK_L011,13

MEM_MB0_CS_L111,13

MEM_MB0_CS_L011,13

MEM_MB0_ODT011,13

MEM_MB1_CLK_H212,13

MEM_MB1_CLK_L212,13

MEM_MB1_CLK_H112,13

MEM_MB1_CLK_L112,13

MEM_MB1_CLK_H012,13

MEM_MB1_CLK_L012,13

MEM_MB1_CS_L112,13

MEM_MB1_CS_L012,13

MEM_MB1_ODT012,13

MEM_MB_CAS_L11,12,13

MEM_MB_WE_L11,12,13

C C

MEM_MB_RAS_L11,12,13

MEM_MB_BANK211,12,13

MEM_MB_BANK111,12,13

MEM_MB_BANK011,12,13

MEM_MB_CKE112,13

MEM_MB_CKE011,13

MEM_MB_ADD[15..0]11,12,13

MEM_MB_DQS_H[7..0]11,12

B B

MEM_MB_DQS_L[7..0]11,12

MEM_MB_DM[7..0]11,12

4

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

A18

A19

U31

U30

AE30

AC31

AD29

AL19

AL18

C19

D19

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

N31

AA31

AA28

M31

M29

N28

N29

AE31

N30

P29

AA29

P31

R29

R28

R31

R30

T31

T29

U29

U28

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AH17

AJ23

AK29

C30

A23

B17

B13

MEMORY INTERFACE B

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

U1C

U1C

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

3

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DATA[63..0] 11,12

MEM_MB_DQS_H8 11,12

MEM_MB_DQS_L8 11,12

MEM_MB_DM8 11,12

MEM_MB_CHECK[7..0] 11,12

2

1

A A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

M2-3 DDR-2

M2-3 DDR-2

M2-3 DDR-2

CK804A07

CK804A07

CK804A07

TECHNOLOGY COPR.

of

841Tuesday, October 31, 2006

of

841Tuesday, October 31, 2006

of

841Tuesday, October 31, 2006

1

A

A

A

Page 9

5

Level translation buffers

Assuming system devices

Do not provide VDDIO

compatible voltage levels

HT_STOP*14

D D

DS

Q3

CK8_PWRGD18,39

These signals must be

driven low during S3

and S5 states, including

C C

state transitions, to meet

HT I/O Link Specification

B B

A A

G

2N7002-7-FQ32N7002-7-F

CPU_RST*14

CPU_PWRGD14

Note 1

5-bit VID Implementation:

VID4:0 connects to VID4:0 of regulator*

VID5 should be left unconnected.

VID1 should be pulled up to VDDIO for compatibility with

future processors *

Translation may be needed to meet the input requirements

of the regulator inputs (See datasheet for processor Voh

specs & regulator datasheet for Vih min requirements)

6-bit VID Implementation:

VID5:0 directly connects to VID5:0 of regulator.

VID1 should be pulled up to VDDIO for compatibility with

future processors

NOTE: There is an incompatibility between the 5-bit VID

code & 6-bit VID code x11111b. VID code 11111b is FF

for 5-bit VID controllers & a valid VID code for 6-bit VID

controllers (011111b is 775mv & 111111b is 375mv). These

are not planned to be operating VID for non-mobile抯

processors so no adverse system implications will occur

using a 5-bit VID or 6-bit controller in non-mobile

implementations. Please see AMD Socket M2 Motherboard

Design Guide, PID #33165 for more details.

5

M2_DE_Glitching

R102

R102

1K

1K

+-5%

+-5%

r0603h6

r0603h6

R112

R112

1K

1K

+-5%

+-5%

r0603h6

r0603h6

M2_DE_Glitching

R125

R125

1K

1K

+-5%

+-5%

r0603h6

r0603h6

M2_DE_Glitching

DS

Q1

G

2N7002-7-FQ12N7002-7-F

DS

Q4

G

2N7002-7-FQ42N7002-7-F

DS

Q7

G

2N7002-7-FQ72N7002-7-F

1D8V_STR3D3V_SYS 3D3V_DUAL

R104

R104

R103

R103

300

300

680

680

+/-5%

+/-5%

+/-5%

+/-5%

R0603

R0603

r0603h6

r0603h6

DS

Q2

G

2N7002-7-FQ22N7002-7-F

3D3V_DUAL 1D8V_STR3D3V_SYS

R107

R107

R106

R106

300

300

680

680

+/-5%

+/-5%

+/-5%

+/-5%

R0603

R0603

r0603h6

r0603h6

DS

Q5

G

2N7002-7-FQ52N7002-7-F

3D3V_DUAL 1D8V_STR3D3V_SYS

R127

R127

R126

R126

300

300

680

680

+/-5%

+/-5%

+/-5%

+/-5%

R0603

R0603

r0603h6

r0603h6

DS

Q8

G

2N7002-7-FQ82N7002-7-F

慜

4

CPU_LDTSTOP_L

5V_SYS

C100

C100

1uF

1uF

*

*

*

*

Dummy

Dummy

Dummy

Dummy

C0603

C0603

Keep trace to resistor

less than 600mils from CPU pin and

trace to AC caps less than 1250mils

CPU_HT_RESET_L

CPU_ALL_PWROK

U1J

U1J

<PART_NAME>

<PART_NAME>

bga940j_socket-m2h64

bga940j_socket-m2h64

5

MTG1

6

MTG1

7

MTG1

8

MTG1

9

MTG1

10

MTG1

11

MTG1

12

MTG1

1

EMI

2

EMI

13

MTG2

14

MTG2

15

MTG2

16

MTG2

17

MTG2

18

MTG2

19

MTG2

20

MTG2

<PATH>

<PATH>

4

C101

C101

0.1uF

0.1uF

C0603

C0603

U3 AME8800

U3 AME8800

Dummy

Dummy

3

V_IN

V_OUT

GND

1

MTG3

MTG3

MTG3

MTG3

MTG3

MTG3

MTG3

MTG3

MTG4

MTG4

MTG4

MTG4

MTG4

MTG4

MTG4

MTG4

EMI

EMI

2

21

22

23

24

25

26

27

28

3

4

29

30

31

32

33

34

35

36

GND

+2.5V

C102

C102

22uF

22uF

*

*

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

Dummy

Dummy

C1206

C1206

CPU_CLKIN_H14

CPU_CLKIN_L14

CPU_SIC32

CPU_SID32

1D8V_STR

GND

3

CPU_VDDA_RUN

CP1

CP1

Dummy

Dummy

12

X_COPPER

X_COPPER

FB1

FB1

Dummy

Dummy

*

*

FB L0805 200 Ohm

FB L0805 200 Ohm

C106

C106

1D8V_STR

R108

R108

300

300

+/-5%

+/-5%

R0603

R0603

Dummy

Dummy

R118 39.2 +/-1% r0402h4

R118 39.2 +/-1% r0402h4

*

*

R120 39.2 +/-1% r0402h4

R120 39.2 +/-1% r0402h4

*

*

CPU_THERMDC34

CPU_THERMDA34

L25

L26

L31

L30

W26

W25

AE27

U24

V24

AE28

Y31

Y30

AG31

V31

W31

AF31

C103

C103

4.7uF

4.7uF

*

*

C0805

C0805

3.9nF C0603 50V, X7R, +/-10%

3.9nF C0603 50V, X7R, +/-10%

*

*

R109

R109

169 Ohm

169 Ohm

+/-1%

+/-1%

r0603h6

r0603h6

C107

C107

3.9nF C0603 50V, X7R, +/-10%

3.9nF C0603 50V, X7R, +/-10%

*

*

CPU_PRESENT36

R113

R113

300

300

+/-5%

+/-5%

R0603

R0603

Dummy

Dummy

R116

R116

300

300

+/-5%

+/-5%

R0603

R0603

CPU_VDD_RUN_FB_H36

CPU_VDD_RUN_FB_L36

GND

TP4TP4

CPU_M_VREF_SUS

R123 300 +/-5% R0603R123 300 +/-5% R0603

R122 300 +/-5% R0603R122 300 +/-5% R0603

GND

TP6TP6

TP7TP7

TP9TP9

TP13TP13

TP12TP12

U1E

U1E

INTERNAL MISC

INTERNAL MISC

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

C104

C104

0.22uF

0.22uF

*

*

*

*

C0603

C0603

CPU_CLKIN_SC_H

CPU_CLKIN_SC_L

CPU_ALL_PWROK

CPU_LDTSTOP_L

CPU_HT_RESET_L

CPU_PRESENT_L

CPU_SIC

CPU_SID

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

1

M_ZN

M_ZP

1

CPU_TEST16

1

CPU_TEST15

1

CPU_TEST14

1

CPU_TEST12

1

CPU_THERMDC

CPU_THERMDA CPU_TEST26

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

CPU Control & Debug Interfaces

VREG_VID4----RN1.6VREG_VID2---RN1.4VREG_VID3---RN1.2

C105

C105

3.3nF

3.3nF

C0603

C0603

C10

VDDA1

D10

VDDA2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

AL3

CPU_PRESENT_L

AL6

SIC

AK6

SID

AL10

TDI

AJ10

TRST_L

AH10

TCK

AL9

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

E12

VTT_SENSE

F12

M_VREF

AH11

M_ZN

AJ11

GND

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

CPU_DBREQ_L

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST_L

CPU_TDO

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

CPU_TEST25_H

CPU_TEST25_L

E20

B19

AL4

AK4

AK3

F2

F3

G4

G3

G5

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

CPU_M_VREF_SUS

*

*

0.1uF

0.1uF

C0603

C0603

C108

C108

CPU_M_VREF_SUS

C109

C109

1nF

1nF

*

*

Layout: Place near CPU socket

C0603

C0603

GND

1D8V_STR

3

R133

R133

16.9

16.9

r0603h6

r0603h6

+/-1%

+/-1%

R134

R134

16.9

16.9

+/-1%

+/-1%

r0603h6

r0603h6

2

Required for compatibility

with future processors

See Note 1

U1D

U1D

MISC

MISC

CPU_VID5

D2

CPU_VID4

D1

CPU_VID3

C1

CPU_VID2

E3

CPU_VID1

E2

CPU_VID0

E1

AK7

CPU_PROCHOT_L_1.8

AL7

CPU_TDO

AK10

CPU_DBRDY

B6

AK11

CPU_VDDIO_SUS_FB_L

AL11

CPU_PSI_LCPU_VTT_SUS_SENSE

F1

CPU_HTREF1

V8

CPU_HTREF0

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

1

1

1

1

1

1

1

2

1

CPU_TEST29_H

CPU_TEST29_L

CPU_TEST24CPU_TEST17

CPU_TEST23

CPU_TEST22

CPU_TEST21

CPU_TEST20

TP15TP15

TP16TP16

TP18TP18

TP17TP17

TP20TP20

TP19TP19

TP21TP21

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

THERMTRIP_L

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

Erratum 133, Revision Guide for

AMD NPT 0Fh Processors

1

1D8V_STR

R105

R105

R110

R110

300

300

300

300

+/-5%

+/-5%

+/-5%

+/-5%

R0603

R0603

R0603

R0603

TP3TP3

CPU_THERMTRIP_L

1

1

1

1

1

FAB B change

CPU_THERMTRIP_L

R646

R646

Dummy

Dummy

CPU_TEST26

CPU_PRESENT_L CPU_VDD_RUN_FB_L

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST21

1D8V_STR

R111

R111

300

300

*

*

135

+/-5%

+/-5%

R0603

R0603

CPU_VDDIO_SUS_FB_H

TP5TP5

R119 44.2R119 44.2

R121 44.2R121 44.2

TP8TP8

TP10TP10

TP11TP11

TP14TP14

1D8V_STR

Dummy

Dummy

R647

r0603h6R647

r0603h6

1K +-5%

1K +-5%

0

0

R128 300 R0603 +/-5%R128 300 R0603 +/-5%

R129 1K +-5%

R129 1K +-5%

R130 510

R131 510 r0603h6 +/-1%R131 510 r0603h6 +/-1%

R132 300 R0603 +/-5%R132 300 R0603 +/-5%

1D8V_STR

+/-5%

+/-5%

78

8P4R0603

8P4R0603

330

330

642

RN1

RN1

R114 4.7K

R114 4.7K

r0603h6 +/-5%

r0603h6 +/-5%

RN21

RN21

*

*

1

3

5

7 8

4.7K

4.7K

8p4r0603h7

8p4r0603h7

+/-5%

+/-5%

1D2V_HT

GND

R124

R124

80.6

80.6

Route as 80-Ohm differential impedance

+/-1%

+/-1%

r0603h6

r0603h6

Keep trace to resistor less than 1" from CPU pin

5V_SB_SYS

R644

R644

680

680

+/-5%

+/-5%

r0603h6

r0603h6

R649 0

R649 0

Dummy

r0603h6

r0603h6

+-5%

+-5%

1K

1K

R648

R648

Dummy

Dummy

Dummy

Q70

Q70

B

PMBT3904

PMBT3904

E C

R6500R650

0

GND

1D8V_STR

FAB B change

r0603h6

r0603h6

r0603h6

r0603h6

+/-1%R130 510

+/-1%

GND

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

B

Q38

Q38

PMBT3904

PMBT3904

B

Q39

Q39

PMBT3904

PMBT3904

B

2

Q42

Q42

4

PMBT3904

PMBT3904

6

B

Q43

Q43

PMBT3904

PMBT3904

B

Q63

Q63

PMBT3904

PMBT3904

Keep trace to resistors

less than 1.5" from CPU pin

3D3V_DUAL

R645

R645

1K

1K

+-5%

+-5%

r0603h6

r0603h6

DS

Q71

Q71

G

2N7002-7-F

2N7002-7-F

GND

CPU_VDD_RUN_FB_H

CPU_TEST29_H

CPU_TEST29_L

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_ALL_PWROK

CPU_LDTSTOP_L

CPU_HT_RESET_L

CPU_THERMTRIP_L

M2-4 MISC

M2-4 MISC

M2-4 MISC

CK804A07

CK804A07

CK804A07

1

3V_CPU_VID4 32,41

CPU_VID4

E C

3V_CPU_VID3 32,41

CPU_VID3

E C

3V_CPU_VID2 32,41

CPU_VID2

E C

3V_CPU_VID1 32,41

CPU_VID1

E C

3V_CPU_VID0 32,41

CPU_VID0

E C

CPU_VDDA_RUN

CPU_THERMTRIP* 14

TP22TP22

1

TP25TP25

1

TP26TP26

1

TP28TP28

1

TP27TP27

1

TP30TP30

1

TP29TP29

1

TP31TP31

1

TP32TP32

1

TP33TP33

1

TP34TP34

1

TECHNOLOGY COPR.

TECHNOLOGY COPR.

TECHNOLOGY COPR.

of

941Tuesday, October 31, 2006

941Tuesday, October 31, 2006

941Tuesday, October 31, 2006

A

A

A

Page 10

5

4

3

2

1

Processor Power & Ground

D D

+V_CPU

C C

B B

A A

AA10

AA12

AA14

AA16

AA18

AB11

AC10

AE10

U1F

U1F

VDD1

VDD1

A4

VDD1

A6

VDD2

AA8

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

AB7

VDD9

AB9

VDD10

VDD11

AC4

VDD12

AC5

VDD13

AC8

VDD14

VDD15

AD2

VDD16

AD3

VDD17

AD7

VDD18

AD9

VDD19

VDD20

AF7

VDD21

AF9

VDD22

AG4

VDD23

AG5

VDD24

AG7

VDD25

AH2

VDD26

AH3

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

E10

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

G10

VDD49

G12

VDD50

H7

VDD51

H11

VDD52

H23

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

K11

VDD64

K13

VDD65

K15

VDD66

K17

VDD67

K19

VDD68

K21

VDD69

K23

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

Y17

VDD150

Y19

VDD151

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

GND

5

CPU_AH14 41

+V_CPU

U1G

U1G

VDD2

VDD2

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

W10

VDD62

W12

VDD63

W14

VDD64

W16

VDD65

W18

VDD66

W20

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

GND

Place near processor on VLDT pour.

1D2V_HT

C155

C155

C154

C154

4.7uF

4.7uF

4.7uF

4.7uF

*

*

*

*

C0805

C0805

*

*

C0805

C0805

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

4

C156

C156

0.22uF

0.22uF

C0603

C0603

+V_CPU

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

C157

C157

0.22uF

0.22uF

*

*

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

U1H

U1H

VDD3

VDD3

N17

VSS1

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

M21

VDD21

M23

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

W22

VDD31

Y23

VDD32

C158

C158

C159

C159

180pF

180pF

180pF

180pF

*

*

*

*

C0603

C0603

C0603

C0603

GND

50V, NPO, +/-5%

50V, NPO, +/-5%

N19

VSS2

N21

VSS3

N23

VSS4

P2

VSS5

P3

VSS6

P8

VSS7

P10

VSS8

P12

VSS9

P14

VSS10

P16

VSS11

P18

VSS12

P20

VSS13

P22

VSS14

R7

VSS15

R9

VSS16

R11

VSS17

R13

VSS18

R15

VSS19

R17

VSS20

R19

VSS21

R21

VSS22

R23

VSS23

T8

VSS24

T10

VSS25

T12

VSS26

T14

VSS27

T16

VSS28

T18

VSS29

T20

VSS30

T22

VSS31

U4

VSS32

U5

VSS33

U7

VSS34

U9

VSS35

U11

VSS36

U13

VSS37

U15

VSS38

U17

VSS39

U19

VSS40

U21

VSS41

U23

VSS42

V2

VSS43

V3

VSS44

V10

VSS45

V12

VSS46

V14

VSS47

V16

VSS48

V18

VSS49

V20

VSS50

V22

VSS51

W9

VSS52

W11

VSS53

W13

VSS54

W15

VSS55

W17

VSS56

W19

VSS57

W21

VSS58

W23

VSS59

Y8

VSS60

Y10

VSS61

Y12

VSS62

W7

VSS63

Y20

VSS64

Y22

VSS65

GND

50V, NPO, +/-5%

50V, NPO, +/-5%

VLDT_RUN_B is connected to the VLDT_RUN power

supply through the package or on the die. It is only connected

on the board to decoupling near the CPU package.

U1I

1D2V_HT

VTT_DDR VTT_DDR

1D8V_STR

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

U1I

VDDIO

VDDIO

AJ4

VLDT_A1

AJ3

VLDT_A2

AJ2

VLDT_A3

AJ1

VLDT_A4

D12

VTT1

C12

VTT2

B12

VTT3

A12

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO29

M24

VDDIO9

M26

VDDIO10

M28

VDDIO11

M30

VDDIO12

P24

VDDIO13

P26

VDDIO14

P28

VDDIO15

P30

VDDIO16

T24

VDDIO17

T26

VDDIO18

T28

VDDIO19

T30

VDDIO20

V25

VDDIO21

V26

VDDIO22

V28

VDDIO23

V30

VDDIO24

Y24

VDDIO25

Y26

VDDIO26

Y28

VDDIO27

Y29

VDDIO28

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

GND

VLDT_RUN_B

*

*

GND

Decoupling Between Processor and DIMMs

Place as close to processor as possible.

1D8V_STR

C140

VTT_DDR

VTT_DDR

3

C140

C141

C141

4.7uF

4.7uF

4.7uF

4.7uF

*

*

*

*

C0805

C0805

C0805

C0805

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C146

C146

C147

C147

4.7uF

4.7uF

4.7uF

4.7uF

*

*

*

*

C0805

C0805

C0805

C0805

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C161

C161

C160

C160

4.7uF

4.7uF

4.7uF

4.7uF

*

*

*

*

C0805

C0805

C0805

C0805

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C143

C143

C142

C142

0.22uF

0.22uF

0.22uF

0.22uF

*

*

*

*

C0603

C0603

C0603

C0603

GND

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

C148

C148

C149

C149

0.22uF

0.22uF

0.22uF

0.22uF

*

*

*

*

C0603

C0603

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

C163

C163

C162

C162

0.22uF

0.22uF

0.22uF

0.22uF

*

*

*

*

C0603

C0603

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

10V, X7R, +/-10%

C151

C151

C150

C150

1nF

1nF

1nF

1nF

*

*

*

*

C0603

C0603

C0603

C0603

50V, X7R, +/-10%

50V, X7R, +/-10%

C164

C164

C165

C165

1nF

1nF

1nF

1nF

*

*

*

*

C0603

C0603

C0603

C0603

50V, X7R, +/-10%

50V, X7R, +/-10%

50V, X7R, +/-10%

50V, X7R, +/-10%

50V, X7R, +/-10%

50V, X7R, +/-10%

C153

C153

C152

C152

180pF

180pF

180pF

180pF

*

*

*

*

C0603

C0603

C0603

C0603

GND

50V, NPO, +/-5%

50V, NPO, +/-5%

C166

C166

C167

C167

180pF

180pF

180pF

180pF

*

*

*

*

C0603

C0603

C0603

C0603

GND

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

C110

C110

4.7uF

4.7uF

C0805

C0805

Bottomside Decoupling

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

+V_CPU

C111

*

*

+V_CPU

*

*

1D8V_STR

*

*

C111

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

C126

C126

0.22uF

0.22uF

*

*

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

@BOTTOM

@BOTTOM

C131

C131

22uF

22uF

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

C112

C112

22uF

22uF

C1206

C1206

@BOTTOM

@BOTTOM

C127

C127

0.22uF

0.22uF

C0603

C0603

@BOTTOM

@BOTTOM

*

*

*

*

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

*

*

10V, X7R, +/-10%

10V, X7R, +/-10%

C132

C132

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

2

C116

*

*

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

*

*

GND

50V, X7R, +/-10%

50V, X7R, +/-10%

C134

C134

4.7uF

4.7uF

*

*

C0805

C0805

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

@BOTTOM

@BOTTOM

C115

C115

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

C130

C130

180pF

180pF

C0603

C0603

50V, NPO, +/-5%

50V, NPO, +/-5%

@BOTTOM

@BOTTOM

C135

C135

0.22uF

0.22uF

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

@BOTTOM

@BOTTOM

C116

22uF

22uF

C1206

C1206

@BOTTOM

@BOTTOM

*

*

C113

C113

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

C128

C128

0.22uF

0.22uF

*

*

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

@BOTTOM

@BOTTOM

C133

C133

4.7uF

4.7uF

C0805

C0805

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

@BOTTOM

@BOTTOM

C114

C114

22uF

22uF

C1206

C1206

@BOTTOM

@BOTTOM

C129

C129

10nF

10nF

C0603

C0603

@BOTTOM

@BOTTOM

*

*

Decoupling Between Processor and DIMMs

*

*

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

C136

C136

0.22uF

0.22uF

*

*

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

@BOTTOM

@BOTTOM

C117

C117

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

C137

C137

0.22uF

0.22uF

C0603

C0603

10V, X7R, +/-10%

10V, X7R, +/-10%

@BOTTOM

@BOTTOM

C118

C118

22uF

22uF

C1206

C1206

@BOTTOM

@BOTTOM

*

*

C125

M2

C125

C124

C124

22uF

22uF

22uF

22uF

*

*

*

*

C1206

C1206

C1206

C1206

GND

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

A31

*

*

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

C138

C138

10nF

10nF

*

*

C0603

C0603

GND

50V, X7R, +/-10%

50V, X7R, +/-10%

@BOTTOM

@BOTTOM

1D8V_STR

C144

C144

180pF

180pF

*

*

C0603

C0603

C119

C119

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

C139

C139

180pF

180pF

C0603

C0603

50V, NPO, +/-5%

50V, NPO, +/-5%

@BOTTOM

@BOTTOM

*

*

GND

50V, NPO, +/-5%

50V, NPO, +/-5%

C120

C120

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

A1

C145

C145

180pF

180pF

C0603

C0603

50V, NPO, +/-5%

50V, NPO, +/-5%

C121

C121

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

C122

C122

22uF

22uF

*

*

C1206

C1206

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

@BOTTOM

@BOTTOM

Top View

C123

C123

22uF

22uF

C1206

C1206

@BOTTOM

@BOTTOM

AL1

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

M2-5 Power

M2-5 Power

M2-5 Power

CK804A07

CK804A07

CK804A07

1

TECHNOLOGY COPR.

of

10 41Tuesday, October 31, 2006

10 41Tuesday, October 31, 2006

10 41Tuesday, October 31, 2006

A

A

A

Page 11

5

4

3

SMB_MEM BUS ADDRESS

DIMM 0

DIMM 1

DIMM 2

DIMM 3

1010 000

1010 001

1010 010

1010 011

2

1

DIMMA0

D D

MEM_MA_DM[7..0]7,12

MEM_MA_DQS_H87,12

MEM_MA_DQS_L87,12

MEM_MA_DQS_H[7..0]7,12

MEM_MA_DQS_L[7..0]7,12

C C

MEM_MA_ADD[15..0]7,12,13

B B

MEM_MA_CHECK[7..0]7,12

A A

MEM_MA_DM87,12

GND

SMB_MEM_SDA12,18

MEM_MA_BANK27,12,13

MEM_MA_BANK17,12,13

MEM_MA_BANK07,12,13

MEM_MA0_CLK_H07,13

MEM_MA0_CLK_L07,13

MEM_MA0_CLK_H17,13

MEM_MA0_CLK_L17,13

MEM_MA0_CLK_H27,13

MEM_MA0_CLK_L27,13

MEM_MA_CKE07,13

MEM_MA_RAS_L7,12,13

MEM_MA_CAS_L7,12,13

MEM_MA0_CS_L07,13

MEM_MA0_CS_L17,13

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_CKE0

5

1D8V_STR

172

178

184

187

189

197

64

69

170

175

181

191

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

VDD1067VDD11

VDDQ1

VDDQ2

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDDQ3

3D3V_SYS 3D3V_SYS

238

78

194

72

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

VDDQ1075VDDQ11

VDDSPD

ERR_OUT_L

4

First Logical DDR2 DIMM

DIMM1DIMM1

MEM_MA_DATA63

236

DQ63

MEM_MA_DATA62

235

DQ62

MEM_MA_DATA61

230

DQ61

MEM_MA_DATA60

229

DQ60

MEM_MA_DATA59

117

DQ59

MEM_MA_DATA58

116

DQ58

MEM_MA_DATA57

111

DQ57

MEM_MA_DATA56

110

DQ56

MEM_MA_DATA55

227

DQ55

MEM_MA_DATA54

226

DQ54

MEM_MA_DATA53

218

DQ53

MEM_MA_DATA52

217

DQ52

MEM_MA_DATA51

108

DQ51

MEM_MA_DATA50

107

DQ50

MEM_MA_DATA49

99

DQ49

MEM_MA_DATA48

98

DQ48

MEM_MA_DATA47

215

DQ47

MEM_MA_DATA46

214

DQ46

MEM_MA_DATA45

209

DQ45

MEM_MA_DATA44

208

DQ44

MEM_MA_DATA43

96

DQ43

MEM_MA_DATA42

95

DQ42

MEM_MA_DATA41

90

DQ41

MEM_MA_DATA40

89

DQ40

MEM_MA_DATA39

206

DQ39

MEM_MA_DATA38

205

DQ38

MEM_MA_DATA37

200

DQ37

MEM_MA_DATA36

199

DQ36

MEM_MA_DATA35

87

DQ35

MEM_MA_DATA34

86

DQ34

MEM_MA_DATA33

81

DQ33

MEM_MA_DATA32

80

DQ32

MEM_MA_DATA31

159

DQ31

MEM_MA_DATA30

158

DQ30

MEM_MA_DATA29

153

DQ29

MEM_MA_DATA28

152

DQ28

MEM_MA_DATA27

40

DQ27

MEM_MA_DATA26

39

DQ26

MEM_MA_DATA25

34

DQ25

MEM_MA_DATA24

33

DQ24

MEM_MA_DATA23

150

DQ23

MEM_MA_DATA22

149

DQ22

MEM_MA_DATA21

144

DQ21

MEM_MA_DATA20

143

DQ20

MEM_MA_DATA19

31

DQ19

MEM_MA_DATA18

30

DQ18

MEM_MA_DATA17

25

DQ17

MEM_MA_DATA16

24

DQ16

MEM_MA_DATA15

141

DQ15

MEM_MA_DATA14

140

DQ14

MEM_MA_DATA13

132

DQ13

MEM_MA_DATA12

131

DQ12

MEM_MA_DATA11

22

DQ11

MEM_MA_DATA10

21

DQ10

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

MEM_MA_DATA0MEM_MA_CHECK7

3

DQ0

73

1

102

195

77

55

68

19

MEM_MA_WE_L 7,12,13

MEM_MA0_ODT0 7,13

GND

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

NC1

MEM_M_VREF_SUS

MEM_MA_DATA[63..0] 7,12

MEM_M_VREF_SUS

1D8V_STR

MEM_MB_DM[7..0]8,12

MEM_MB_DQS_H88,12

MEM_MB_DQS_L88,12

MEM_MB_DQS_H[7..0]8,12

MEM_MB_DQS_L[7..0]8,12

MEM_MB_DM88,12

3D3V_SYS

GND

MEM_MB_BANK28,12,13

MEM_MB_BANK18,12,13

MEM_MB_ADD[15..0]8,12,13

MEM_MB_BANK08,12,13

MEM_MB_CHECK[7..0]8,12

MEM_MB0_CLK_H08,13

MEM_MB0_CLK_L08,13

MEM_MB0_CLK_H18,13

MEM_MB0_CLK_L18,13

MEM_MB0_CLK_H28,13

MEM_MB0_CLK_L28,13

MEM_MB_CKE08,13

MEM_MB_RAS_L8,12,13

MEM_MB_CAS_L8,12,13

MEM_MB0_CS_L08,13

MEM_MB0_CS_L18,13

121 240

R135

R135

C168

C168

59

59

*

*

MEM_M_VREF_SUS

0.1uF

0.1uF

+/-1%

+/-1%

C0603

C0603

R0603

R0603

R136

R136

59

59

*

*

0.1uF

0.1uF

+/-1%

+/-1%

C0603

C0603

R0603

R0603

Layout: Place near DIMM sockets

3

C169

C169

C170

C170

1nF

1nF

*

*

C0603

C0603

GND

SMB_MEM_SCL12,18SMB_MEM_SCL12,18

SMB_MEM_SDA12,18

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

1

1D8V_STR

172

178

184

187

VDD1

VDD2

VDD3

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDD4

CON_DDR2_240_STD

2

DIMMB0

189

197

64

69

170

175

181

191

194

VDD5

VDD6

VDD753VDD859VDD9

VDD1067VDD11

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

DIMM2DIMM2

238

78

72

VDDQ1075VDDQ11

VDDSPD

ERR_OUT_L

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

MEM_MB_DATA63