Page 1

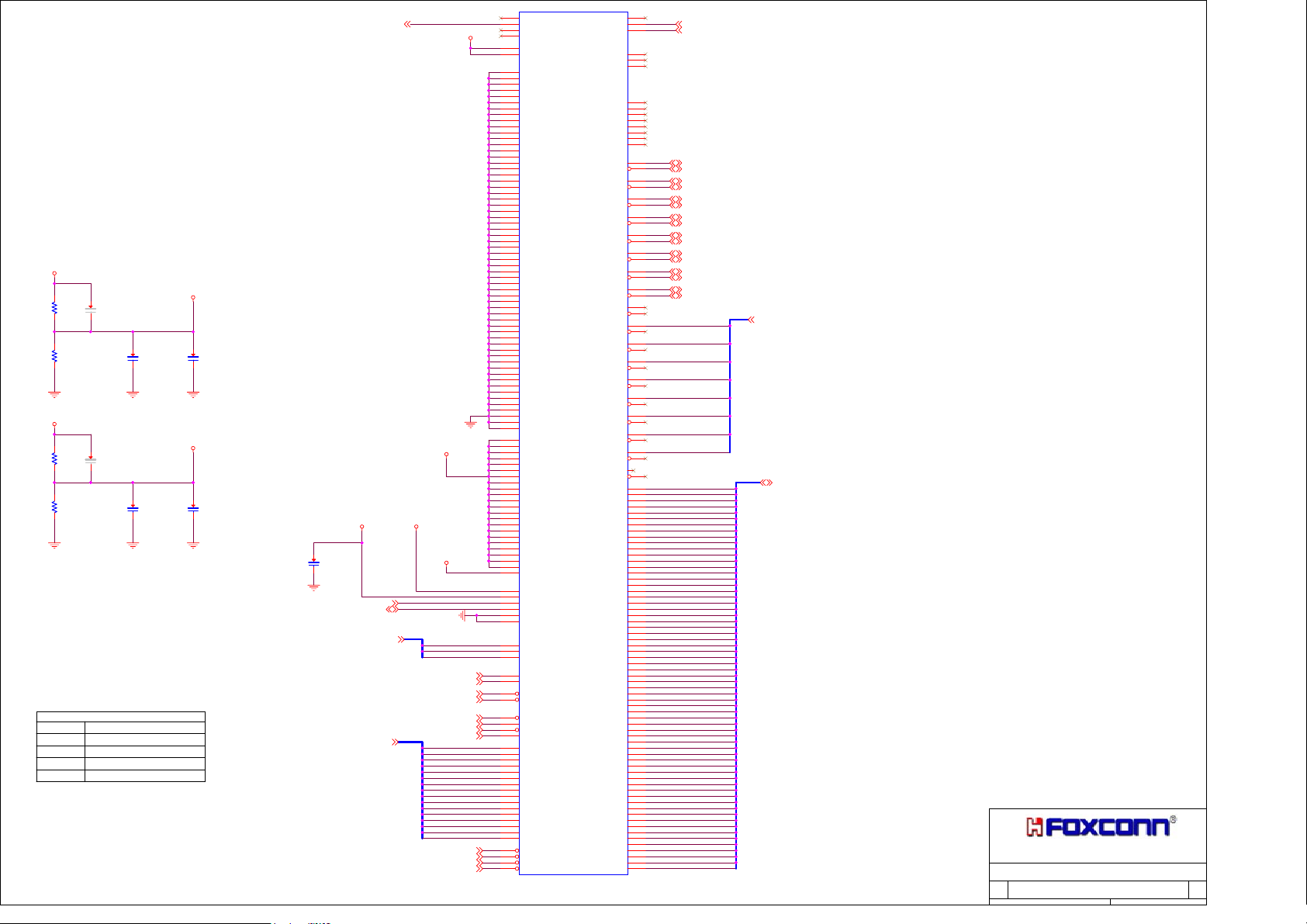

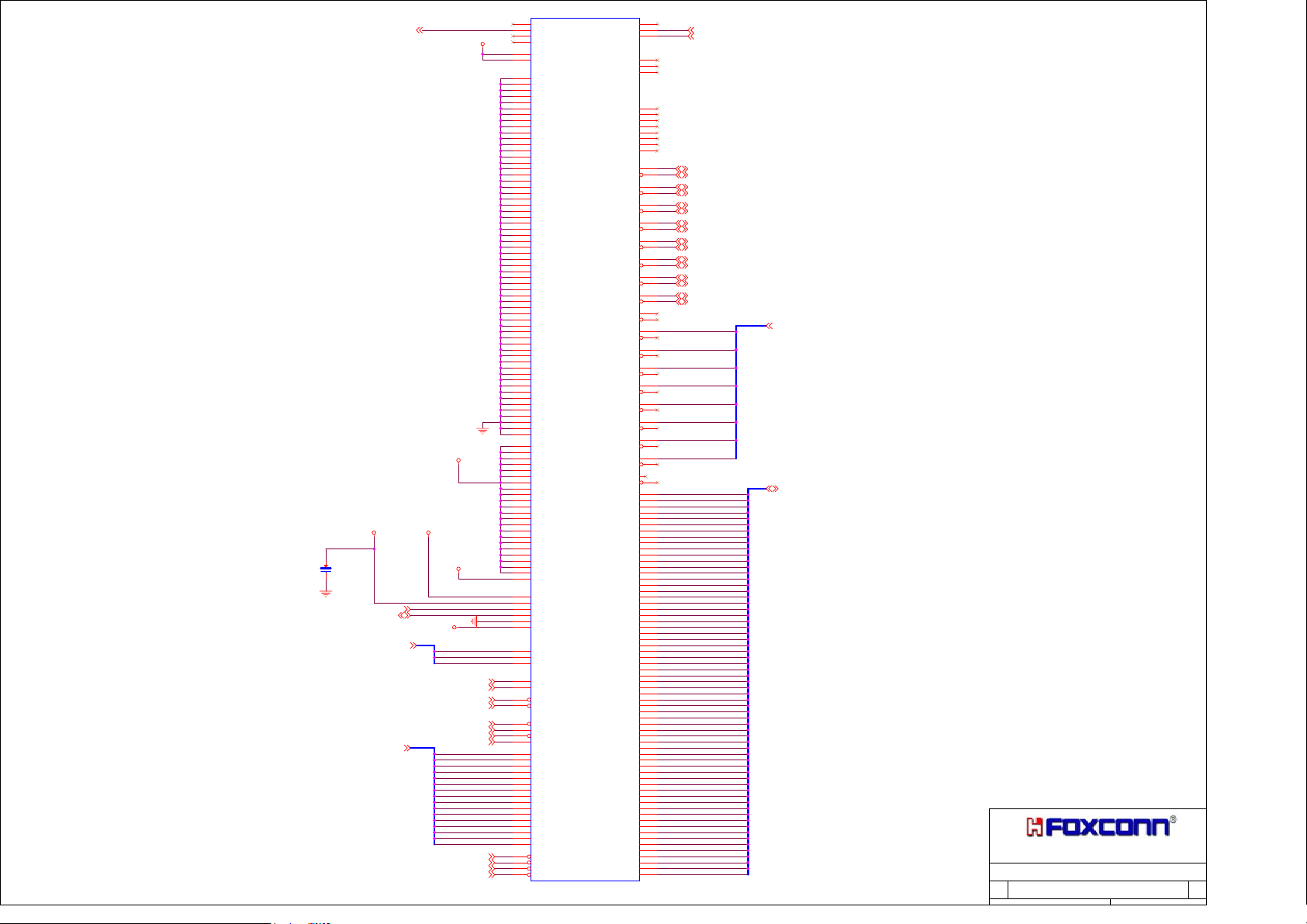

FOXCONN A75M02

FAB: 1.0

AMD FM1 APU + FCH HUDSON D2/D3 CHIPSET

TABLE OF CONTENTS

P01: TABLE OF CONTENTS

P02: BLOCK DIAGRAM

P03: POWER DELIVERY CHART

P04: CLOCK DISTRIBUTION

P05: MISC TABLES

P06: FM1 PCIE I/F

P07: FM1 DDR3 MEM I/F

P08: FM1 DISPLAY & MISC

P09: FM1 POWER & GND

P10: CHANNEL A DDR3 DIMM1

P11: BLANK

P12: CHANNEL B DDR3 DIMM2

P13: FCH-PCIE/PCI/APU/LPC/CLK

P14: FCH-ACPI/GPIO/USB/PHY/AZ

P15: FCH-SATA/HWM/SPI

P16: FCH-POWER & DECOUPLING

P17: FCH-STRAPS

P18: HDMI CONNECTOR

P19: CRT CONNECTOR

P20: PCIE X16 & X1 SLOT

P21: PCI SLOT *1

P22: USB2.0 FRONT HEADER

P23: USB3.0 FRONT HEADER

P24: USB3.0 CONNECTOR

P25: GBE LAN RTL8112B

P26: AUDIO CODEC ALC662/VT1705CE

P27: AUDIO CONNECTOR

P28: HW MONITOR/CIR & IT8772E/CX

P29: FAN & COM HEADER

P30: PS2 &REAR USB2.0 CONNECTOR

P31: FP/ATX CONN

P32: PWR MAIN & OTHER POWERS

P33: PWR DDRIII MEMORY

P34: PWR FM1-1

P35: PWR FM1-2

P36: PWR VDDP/VDDR & 1D1V_RUN

P37: POWER SEQUENCE

P38: EMC & MH & FD

P39: CHANGE HISTORY

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

A75M02

A75M02

A75M02

1

1

1

of

39

of

39

of

39

1.0

1.0

1.0

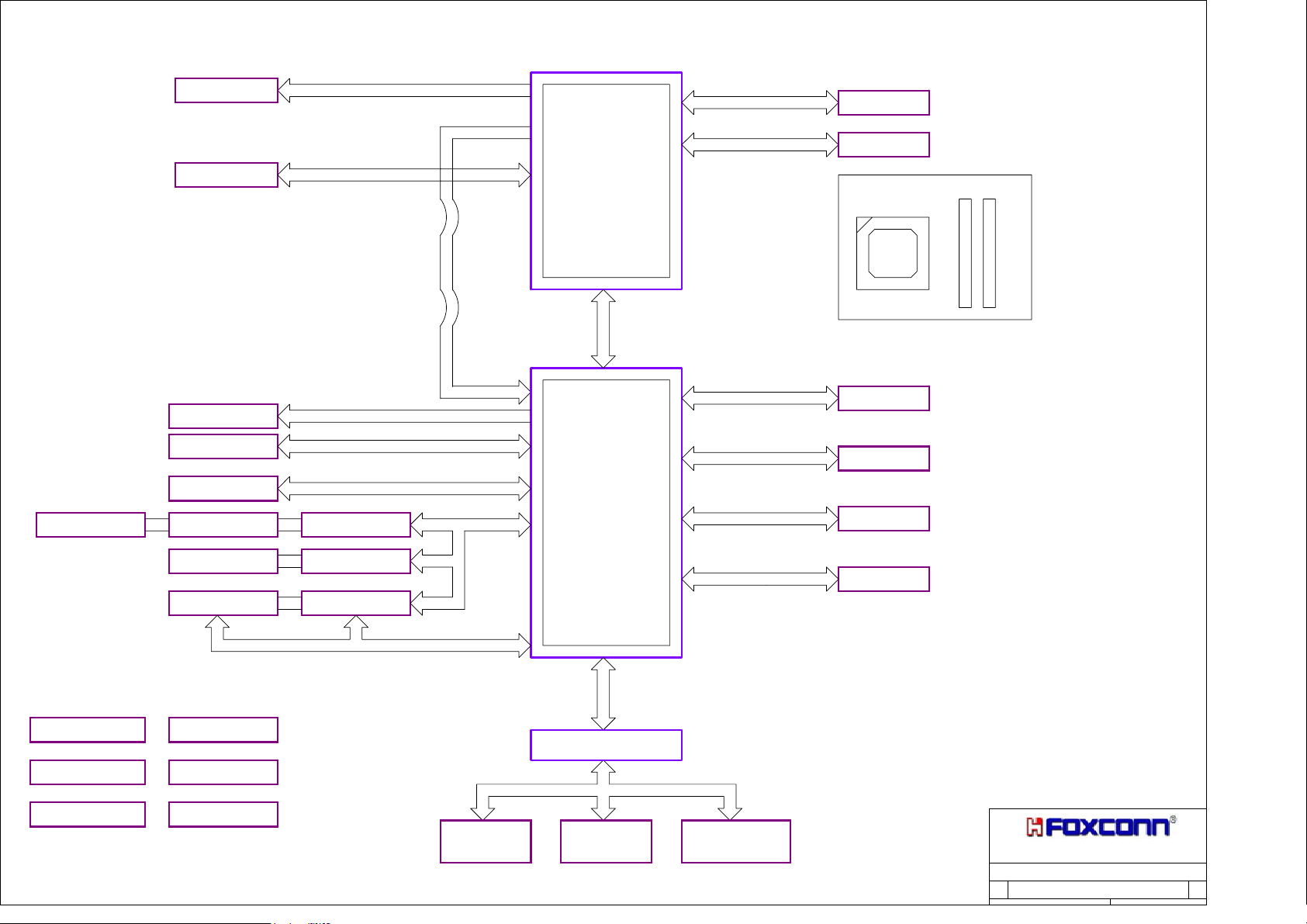

Page 2

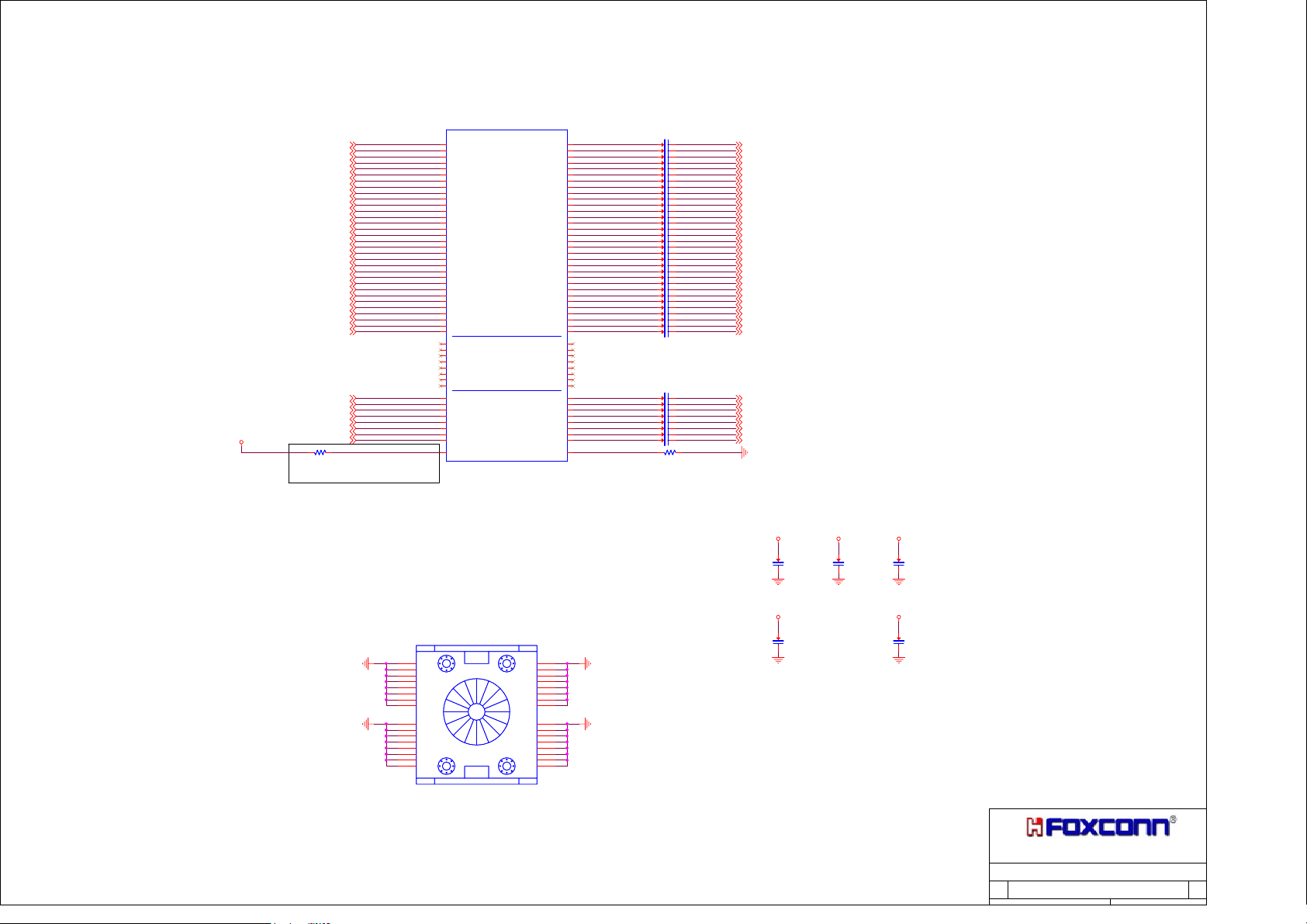

A75M02 BLOCK DIAGRAM

USB4~ USB5

P30

HDMI CON

X16 GFX SLOT

VGA CON

X1 GPP SLOT

GBE LAN RTL8112B

USB2 ~ USB3

USB8 ~ USB9

USB12 ~ USB13

USB3.0 2 ~ USB3.0 3

P18

GFX PCIE INTERFACE GEN2 X16

P20

P19

GPP PCIE INTERFACE GEN2 X1

P20

P25 GPP PCIE INTERFACE GEN1 X1

P30

P22

P23

USB0 ~ USB1

USB6 ~ USB7

USB10 ~ USB11

USB3.0 0 ~ USB3.0 1

P25

P22

P24

P19

DP0

DP1

USB 2.0

APU

AMD

Fusion

Llano FM1

937 -Pin uFCPGA

DX10.1 IGP

DISPLAY PORT X4

1X16 PCIE GFX I/F

4X1 PCIE GPP I/F

1X4 UMI I/F TO HUDSON-D2/D3

P07P06 P08 P09

UMI

PCIE GEN2 X4

FCH

HUDSON-D2/D3

D3: USB3.0(4)+USB2.0(10)+USB1.1(2)

D2: USB2.0(14)+USB1.1(2)

SATAIII(6 PORTS)

4X1 PCIE GEN2 I/F

INT. CLK GEN

GB MAC

HW MONITOR

PCI/PCI BDGE

INT. RTC

HD AUDIO

EC

SPI I/F

ACPI 1.1

LPC I/F

CHANNEL A DDR3 1333 1600 1866

CHANNEL B DDR3 1333 1600 1866

HD AUDIO I/F

SATA III I/F

SPI I/F

PCI I/F

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

P10

P12

APU AND DIMM PLACEMENTS

APU

HD AUDIO

SATA1 ~ SATA4

SPI ROM

PCI SLOT *1

P26

P27

P15

P15

P21

DIMM 1A0DIMM 2

B0

3D3V_ALW

5V_ALW

APU CORE POWER

FCH 1D1V_ALW POWER

FCH 1D1V_RUN POWER

P32

P34

P35

P32

P36

DDRIII POWER

APU VDDP POWER

APU VDDR POWER

POWER ENABLE

POWER SEQUENCE

P32

P36

P37

USB 3.0

COM HEADER

FAN HEADER

P13 P14 P15 P16 P17

ITE LPC SIO 8772E/CX

29

KB CON

LPC I/F

P28

HW MONITOR

P30

CIR HEADER

CASE OPEN HEADER

P28

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

A75M02

A75M02

A75M02

2

2

2

of

39

of

39

of

39

1.0

1.0

1.0

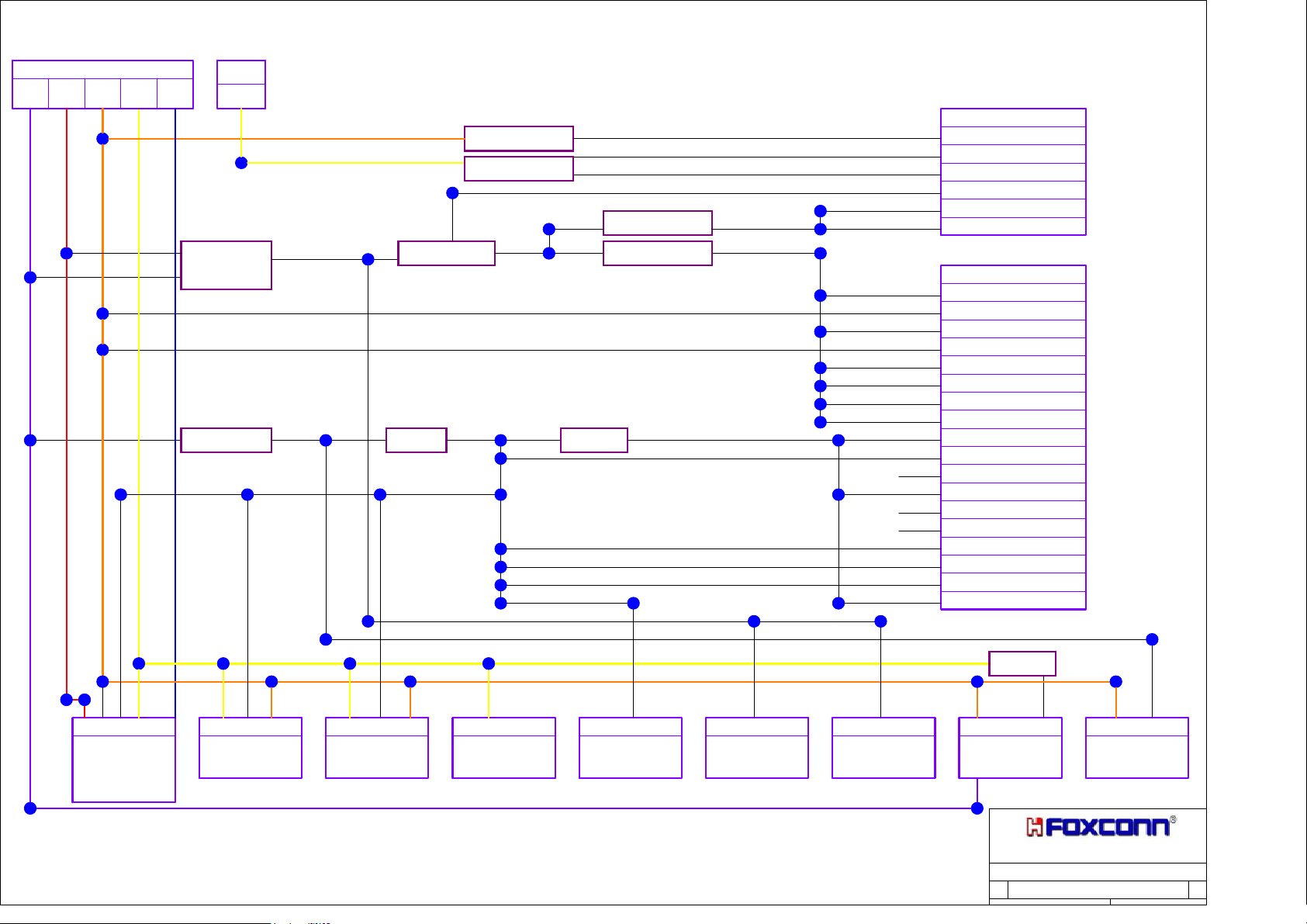

Page 3

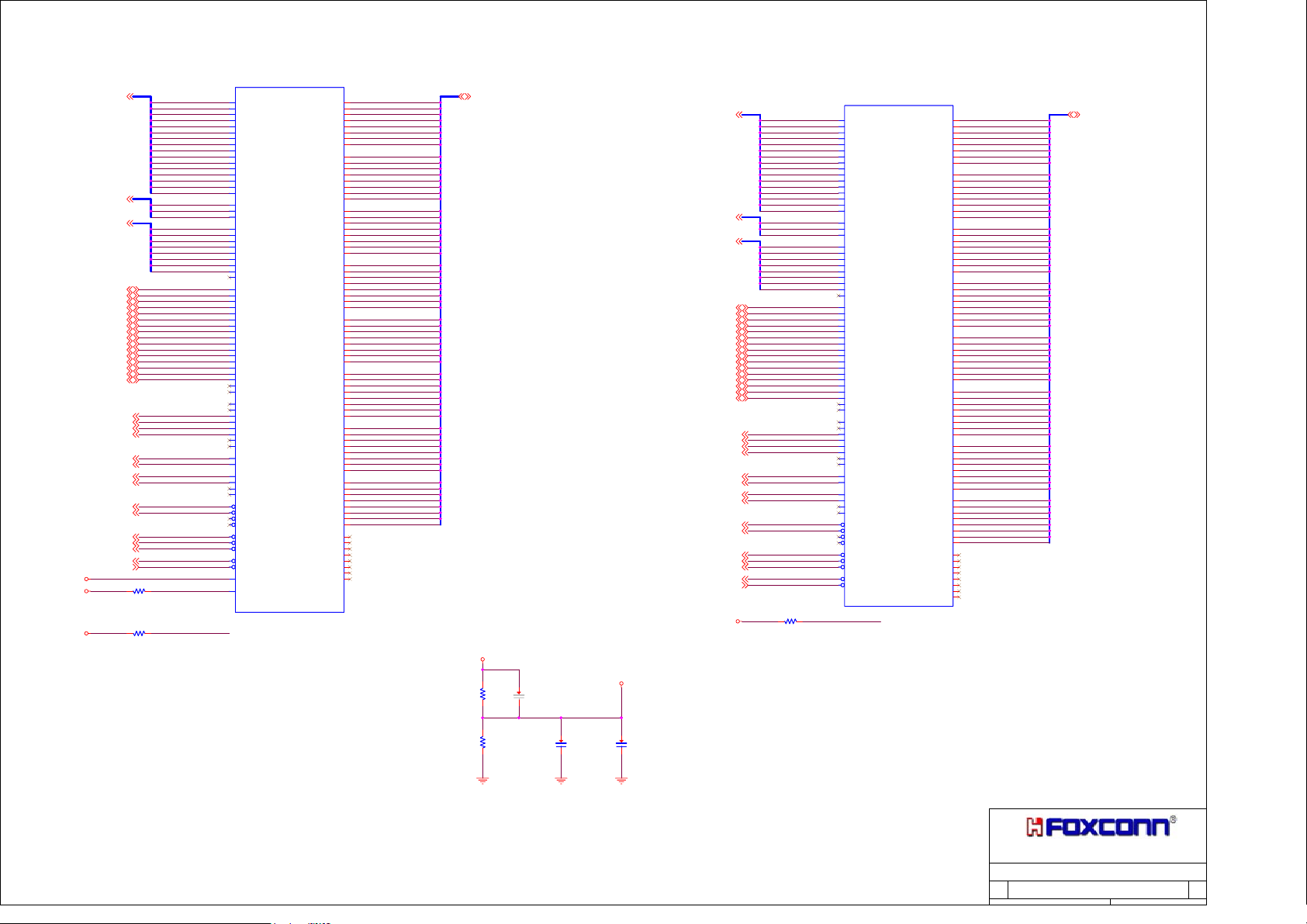

A75M02 POWER DELIVERY CHART

ATX P/S WITH 1A STBY CURRENT

5VSB

+/- 5%5V+/- 5%

5V_SB (S0,S1,S3,S4,S5)

5V_SB

3.3V 12V -12V

+/- 5% +/- 5% +/- 5%

3D3V_RUN (S0,S1)

5V_RUN (S0,S1)

3D3V_RUN

3D3V_RUN

3D3V_RUN

5V_RUN

12A

3A

3D3V_ALW 0.375A

12V_RUN

APU

POWER

18.5A

UP7501M8

P-MOS

N-MOS

AZ1084D-ADJTRE1

12V

+/- 5%

12V_VRM (S0,S1)

U35

Q34

Q32 Q33

Q28

3D3V_ALW3D3V_ALW 3D3V_ALW

3D3V_ALW 0.1A

12V_RUN

8.5A

5V_ALW (S0,S1,S3,S4,S5)

3D3V_SB (S0,S1,S3,S4,S5)

3D3V_SB 3D3V_SB

12V_RUN 12V_RUN

3D3V_RUN

3D3V_ALW

3D3V_ALW

3D3V_ALW

3D3V_ALW

3D3V_ALW

U2

U39

RT9199PSP

LM358 (OP)

N-MOS

LM358 (OP)

N-MOS

1D1V_ALW (S0,S1,S3,S4,S5)

U34

3D3V_ALW 0.034A

3D3V_ALW

U301

Q92,Q93

U301

Q62

1D1V_RUN(S0,S1)

1D1V_RUN 3.3A

1D1V_ALW 0.65A

AP2114H-2.5TRG1

ISL6328CRZ-T

10.5A

APW7120KE-TRL

FDN340P

Q29

3D3V_ALW 0.1A

5V_ALW 5V_ALW

3D3V_RUN

U37

3D3V_ALW 1.7A

3D3V_ALW (S0,S1,S3,S4,S5)

3D3V_ALW

3D3V_ALW 0.44A

APU_VDDA_RUN(S0,S1)

APU_VDD_RUN(S0,S1)

APU_VDDNB_RUN(S0,S1)

APU_VDDIO_SUS(S0,S1,S3)

APU_VDDP_RUN(S0,S1)

APU_VDDR_RUN(S0,S1)

1D1V_RUN

1D1V_RUN

1D1V_RUN

1D1V_RUN

1D1V_RUN

1D1V_RUN

1D1V_ALW

1D1V_ALW

1D1V_ALW

5V_ALW

GND

GND

GND

12V_RUN

3D3V_RUN

APU FM1

VDDA

VDD CORE

VDDNB

DDR III MEM I/F

VDDP

VDDR

2.5V(2.4~2.6V) 0.75A

0.8V~2.0V/120A

1.2V/20A

VDDIO 0.8-2.3V 30A

1.2V 5A

1.2V 5A

FCH HUDSON-D2/D3

VDDPL_11_DAC

VDDIO_33_PCIGP

VDDAN_11_ML

VDDPL_33_*_RUN

VDDCR_11

VDDAN_11_SATA

VDDAN_11_CLK

VDDAN_11_PCIE

VDDCR/AN_11_SUSB_S

VDDPL_33_*_ALW

VDDIO_33_GBE_S

VDDCR/AN_11_USB_S

VDDIO_GBE_S

VDDCR_11_GBE_S

VDDAN_33_USB_S

VDDXL_33_S

VDDIO_33_S

VDDCR_11_S

H78L05AA

20mA

300mA

100mA

320mA

500mA

700mA

400mA

900mA

500mA

34mA

1mA

52mA

200mA

100mA

130mA

6mA

30mA

100mA

Q9

5VA

5V_SB

PCI SLOT

5.0A

5V

7.6A

3.3V

0.375A

3.3Vaux

0.5A

12V

0.1A

-12V

X1 PCIE SLOT

3.0A

3.3V

0.1A

3.3Vaux

0.5A

12V

X16 PCIE SLOT

3.0A

3.3V

0.1A

3.3Vaux

5.5A

12V

FAN X2

12V

1.2A X2

LAN RTL8112B

0.271A

3.3Vaux

USB2.0 X10

5A

5V

USB3.0 X4

3.6A

5V

5V_SB

HD AUDIO

0.3A

3.3V

0.15A

5V

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

SIO 8772E/CX

0.15A

3.3V

0.15A

3D3V_SB

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

POWER DELIVERY CHART

POWER DELIVERY CHART

POWER DELIVERY CHART

A75M02

A75M02

A75M02

3

3

3

of

of

of

1.0

1.0

1.0

39

39

39

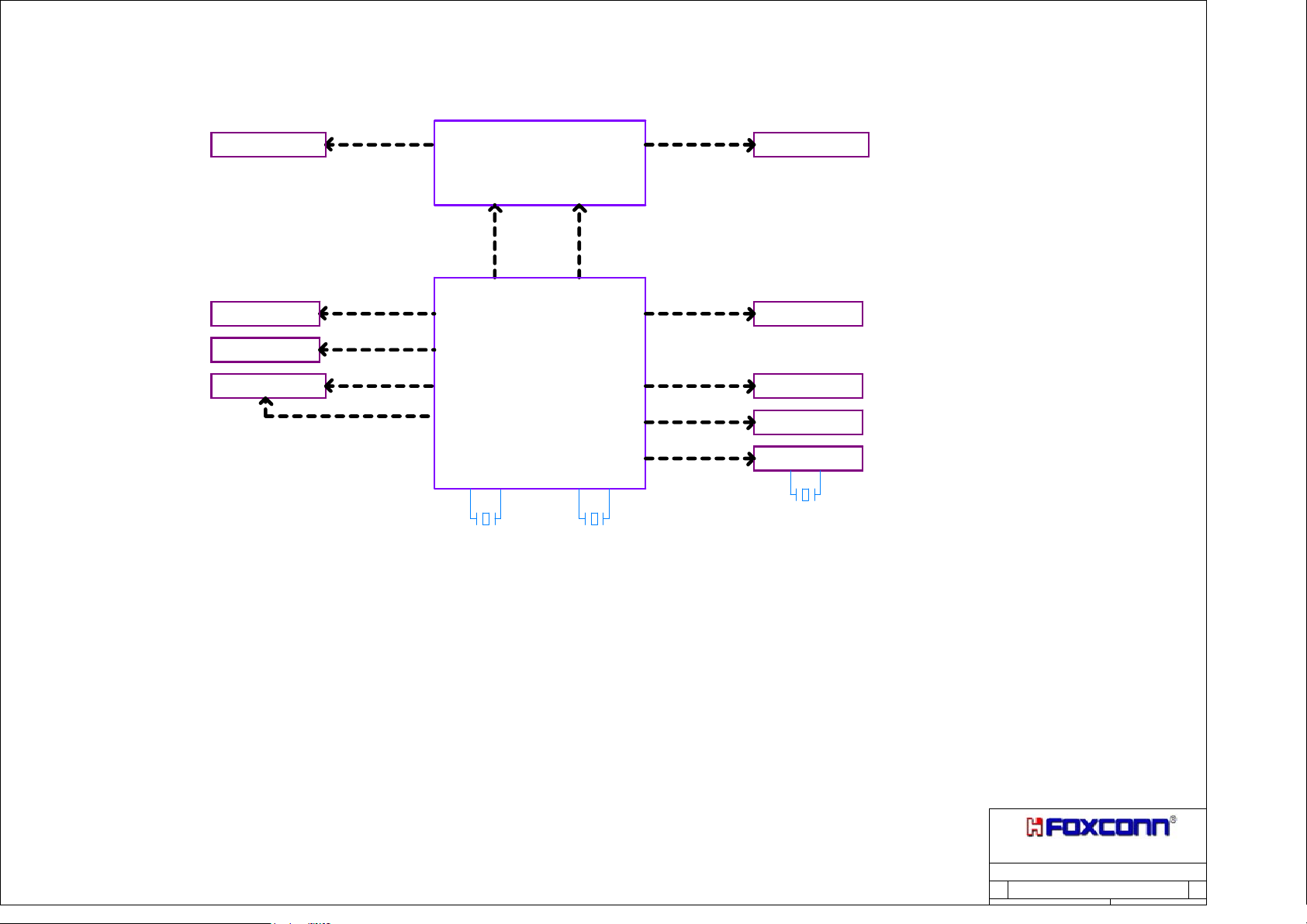

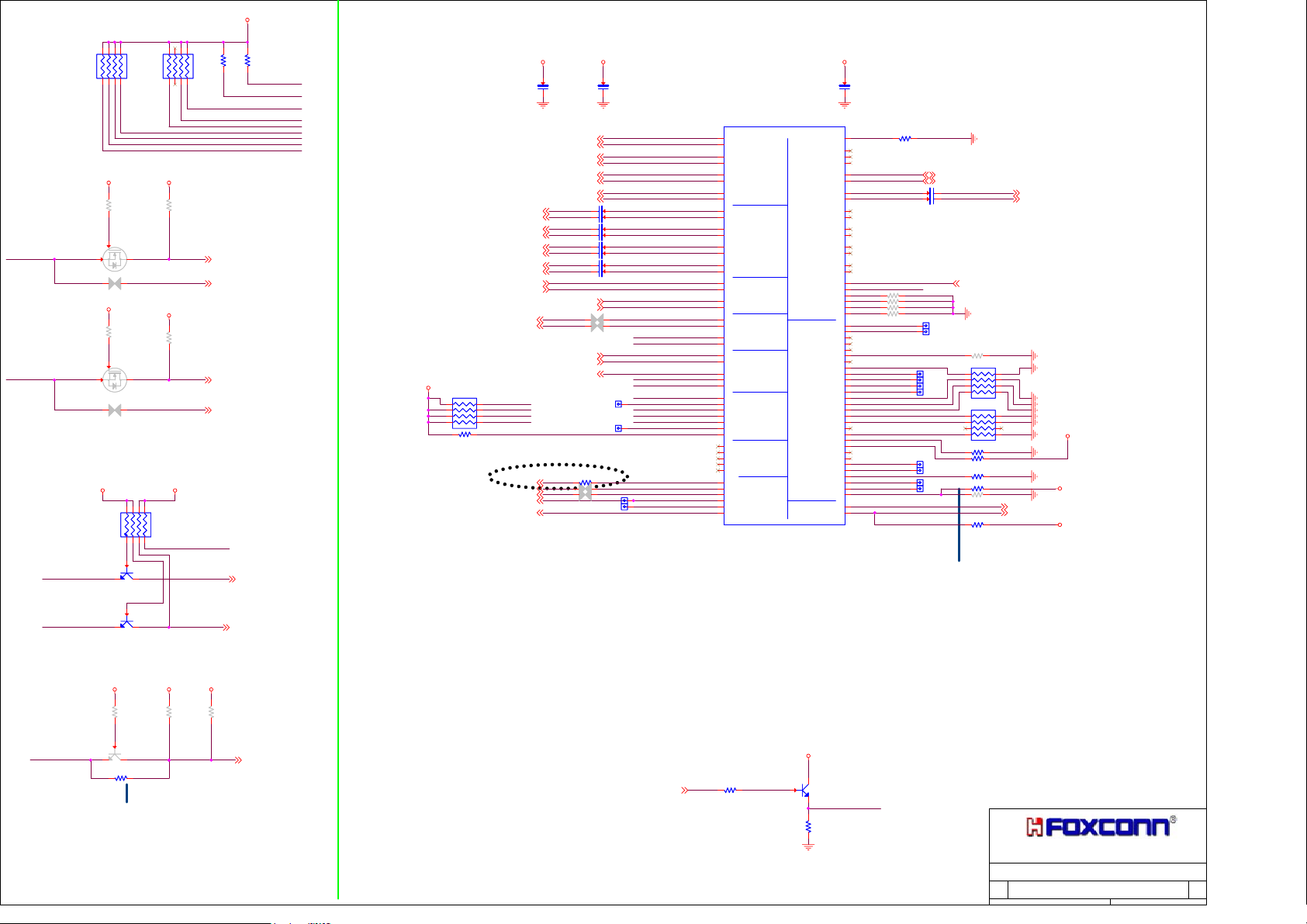

Page 4

A75M02 INTERNAL CLOCK MODE

UNBUFFERED DIMM1

HD AUDIO

SPI ROM

ITE LPC SIO 8772E/CX

MEM_MA_CLK1

MEM_MA_CLK2

AZ_BITCLK

SPI_CLK

LPCCLK0

14M_25M_48M_OSC

APU

AMD FM1

CLKIN_H/L DISP_CLKIN_H/L

APU_CLKP

APU_CLKN

DISP_CLKP

DISP_CLKN

FCH

AMD HUDSON D2/D3

INTERNAL CLOCK GENERATOR

25M_X1 25M_X2 32K_X1 32K_X2

25M Hz

32.768K Hz

MEM_MB_CLK1

MEM_MB_CLK2

PCICLK0

SLT_GFX_CLKP

SLT_GFX_CLKN

GPP_CLK0P

GPP_CLK0N

GPP_CLK1P

GPP_CLK1N

UNBUFFERED DIMM2

PCI SLOT 1

X16 GFX SLOT

X1 GPP SLOT

GBE LAN RTL8112B

25M Hz

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

A75M02

A75M02

A75M02

4

4

4

of

39

of

39

of

39

1.0

1.0

1.0

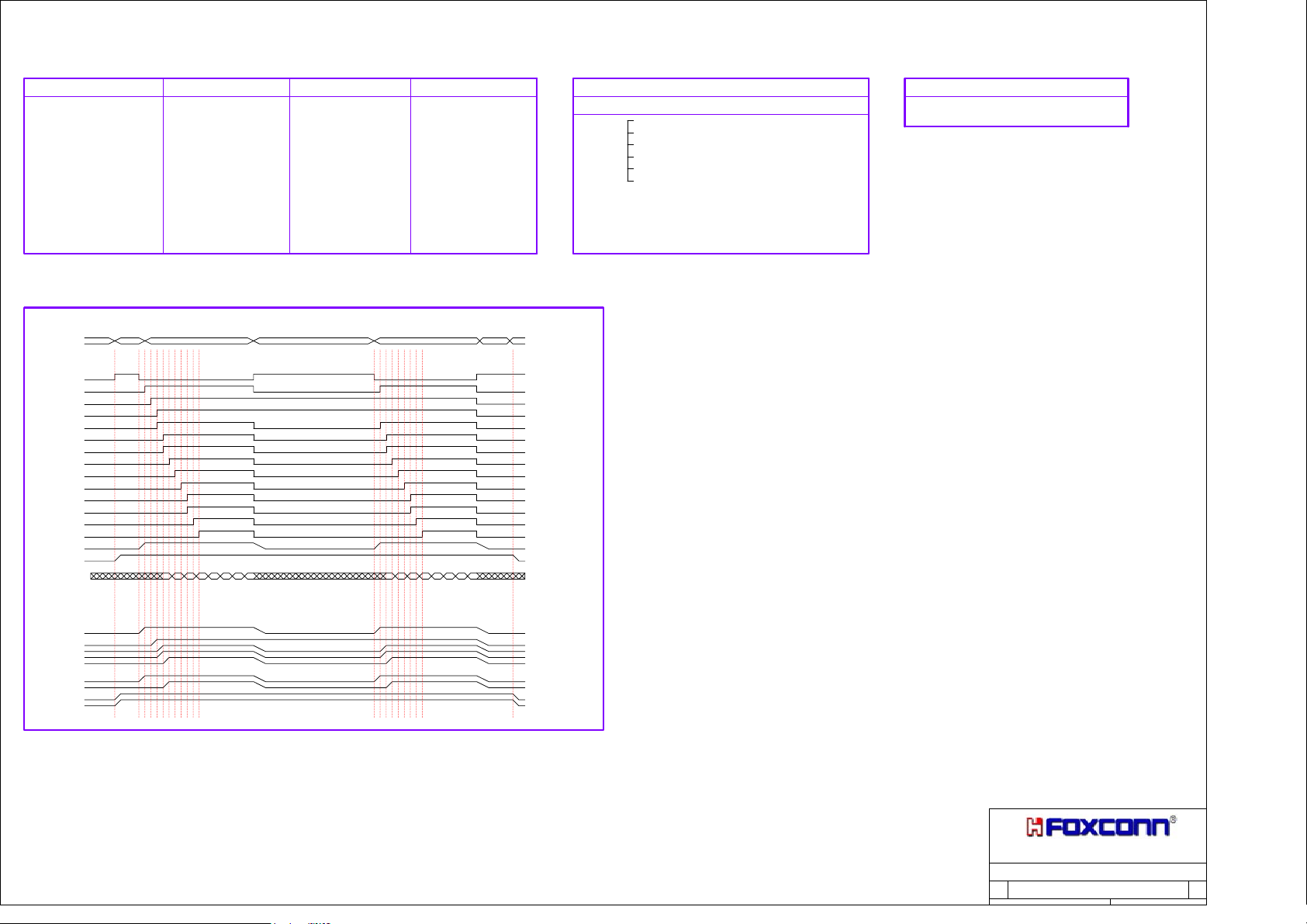

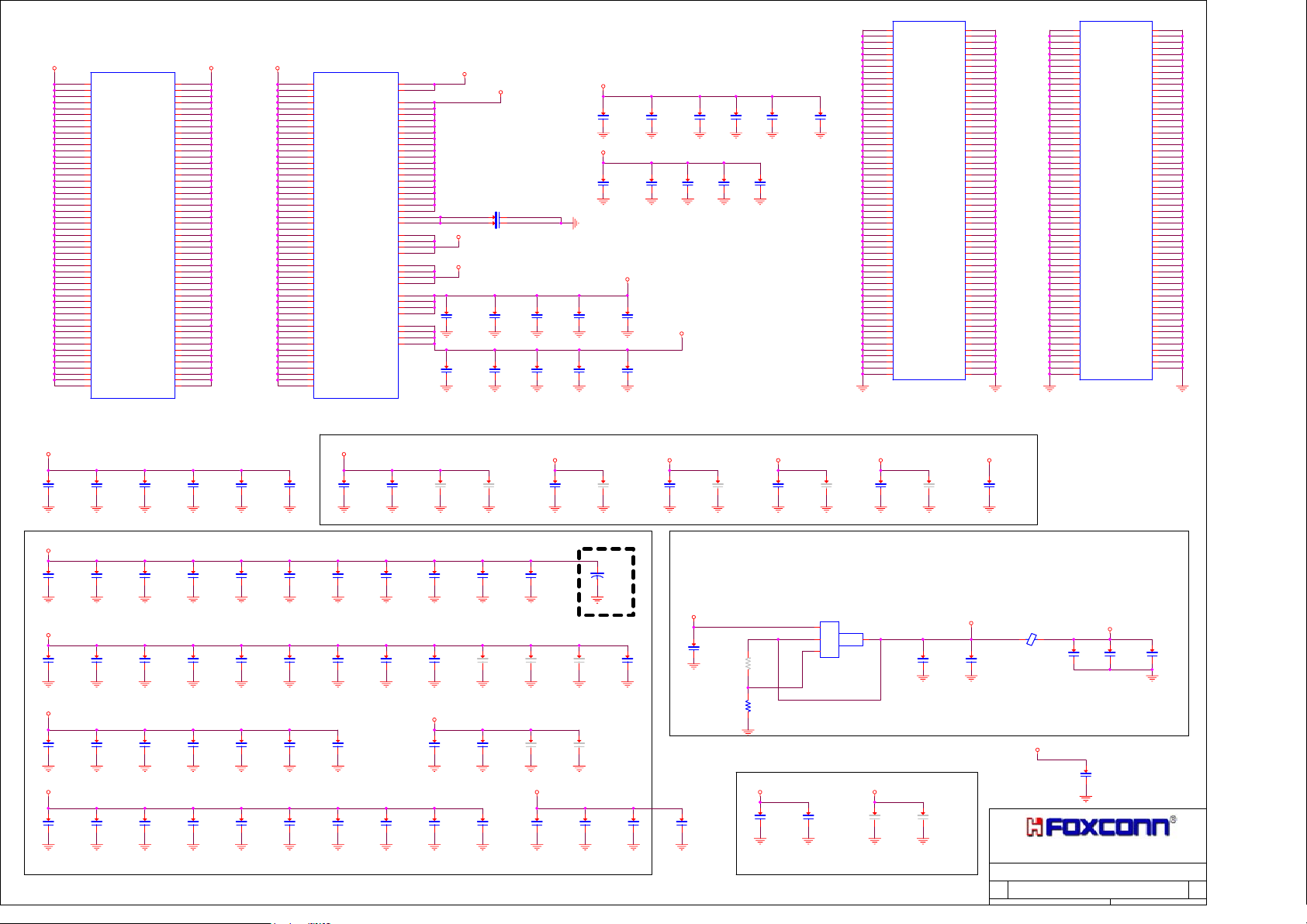

Page 5

A75M02 MISC TABLES

POWER RAIL

12V_RUN +12V

12V_VRM +12V

N_12V_RUN -12V

5V_SB

3D3V_SB

5V_ALW

3D3V_ALW

A_VBAT

1D1V_ALW

5V_RUN

3D3V_RUN

5VA

POWER ON/OFF SEQUENCE

PS_ONJ

ATX_PWRGD

APU_VDDIO_SUS_EN

APU_VDDIO_SUS_PG

APU_VDD_RUN_EN

APU_VDD_RUN_PG

1D1V_RUN_EN

ALL_PWROK

NB_PWRGD

APU_VDDIO_PG

PCIE_ARSTJ

FCH_PCIE_RSTJ_GPP

PCI_RSTJ

FCH_APU_RSTJ

5V_RUN/3D3V_RUN

3D3V_ALW/5V_ALW

EXT CLKX

+5V

+3.3V

+5V

+3.3V

+3.0V

+1.1V

+5V

+3.3V

+5V

G3

S5 S0 S3 S0 S5 G3

S0 S1 S3 S4 S5

OFF

ON ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

ON

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

ON

ON

ON

ON

OFF

OFF

OFF

1D1V_RUN +1.1V

OFF

APU_VDD_RUN SVI

OFF

APU_VDDNB_RUN SVI

OFF

APU_VDDA_RUN +2.5V

ON

APU_VDDIO_SUS +1.5V

ON

APU_VTT_SUS +0.75V

ON

APU_VDDR_RUN +1.2V

ON

APU_VDDP_RUN +1.2V

ON

ON

OFF

OFF

OFF

S0 S1 S3 S4 S5POWER RAIL RESET TABLE Explanation

OFF

ON

ON

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

ON

OFF

ON

ON

ON

OFF

ON

OFF

ON

OFF

ON

OFF

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

PS_ONJ

ATX_PWRGD

APU_VDDIO_SUS_EN

APU_VDDIO_SUS_PG

APU_VDD_RUN_EN

APU_VDD_RUN_PG

1D1V_RUN_EN

ALL_PWROK

NB_PWRGD

APU_VDDIO_PG

PCIE_ARSTJ

FCH_PCIE_RSTJ_GPP

PCI_RSTJ

FCH_APU_RSTJ

5V_RUN/3D3V_RUN

3D3V_ALW/5V_ALW

EXT CLKX

SOURCE SIGNAL NAME LINKED DEVICES

FCH

APU

APU

PWR BTN

PCIE_RST2J_GPP

FCH_PCIE_RSTJ_GPP GFX X16 SLOT

PCIE_ARSTJ LPC SIO 8772E/CX

PCI_RSTJ PCI SLOT 0

FCH_APU_RSTJ

A_HDA_RSTJ HD AUDIO CODEC ALC662/VT1705CE

MEM_MA_RSTJ

MEM_MB_RSTJ

MASTER_RSTJ FCH

GPP X1 SLOT/ LAN RTL8112B

APU

DIMM1

DIMM2

FCH Fusion Controller Hub

UMI Unified Media Interface

AMD APU POWER

APU_VDDA_RUN

APU_VDDIO_SUS

APU_VDD_RUN

APU_VDDNB_RUN

VDDP/VDDR

FCH HUDSON-D2/D3 POWER

3D3V_RUN

1D1V_RUN

3D3V_ALW

1D1V_ALW

AMD APU POWER

APU_VDDA_RUN

APU_VDDIO_SUS

APU_VDD_RUN

APU_VDDNB_RUN

VDDP/VDDR

FCH HUDSON-D2/D3 POWER

3D3V_RUN

1D1V_RUN

3D3V_ALW

1D1V_ALW

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

MISC TABLES

MISC TABLES

MISC TABLES

A75M02

A75M02

A75M02

5

5

5

of

39

of

39

of

39

1.0

1.0

1.0

Page 6

APU_VDDP_B_RUN

GFX_RXP020

GFX_RXN020

GFX_RXP120

GFX_RXN120

GFX_RXP220

GFX_RXN220

GFX_RXP320

GFX_RXN320

GFX_RXP420

GFX_RXN420

GFX_RXP520

GFX_RXN520

GFX_RXP620

GFX_RXN620

GFX_RXP720

GFX_RXN720

GFX_RXP820

GFX_RXN820

GFX_RXP920

GFX_RXN920

GFX_RXP1020

GFX_RXN1020

GFX_RXP1120

GFX_RXN1120

GFX_RXP1220

GFX_RXN1220

GFX_RXP1320

GFX_RXN1320

GFX_RXP1420

GFX_RXN1420

GFX_RXP1520

GFX_RXN1520

UMI_RXP013

UMI_RXN013

UMI_RXP113

UMI_RXN113

UMI_RXP213

UMI_RXN213

UMI_RXP313

UMI_RXN313

+/-1%

+/-1%

R1 196

R1 196

*

*

$CDS_IMAGE|layout_23.bmp|149|152 Within 1500mil from APU

APU_PCIE_ZVDDP APU_PCIE_ZVSS

U1H

U1H

PCI EXPRESS

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_GFX_RXP4

P_GFX_RXN4

P_GFX_RXP5

P_GFX_RXN5

P_GFX_RXP6

P_GFX_RXN6

P_GFX_RXP7

P_GFX_RXN7

P_GFX_RXP8

P_GFX_RXN8

P_GFX_RXP9

P_GFX_RXN9

P_GFX_RXP10

P_GFX_RXN10

P_GFX_RXP11

P_GFX_RXN11

P_GFX_RXP12

P_GFX_RXN12

P_GFX_RXP13

P_GFX_RXN13

P_GFX_RXP14

P_GFX_RXN14

P_GFX_RXP15

P_GFX_RXN15

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

P_ZVDDP

PCI EXPRESS

AE2

C_GFX_TXP0

P_GFX_TXP0

AE1

C_GFX_TXN0

P_GFX_TXN0

AE4

C_GFX_TXP1

P_GFX_TXP1

AE5

C_GFX_TXN1

P_GFX_TXN1

AD2

C_GFX_TXP2

P_GFX_TXP2

AD3

C_GFX_TXN2

P_GFX_TXN2

AC2

C_GFX_TXP3

P_GFX_TXP3

AC1

C_GFX_TXN3

P_GFX_TXN3

AC4

C_GFX_TXP4

P_GFX_TXP4

AC5

C_GFX_TXN4

P_GFX_TXN4

AB2

C_GFX_TXP5

P_GFX_TXP5

AB3

C_GFX_TXN5

P_GFX_TXN5

AA2

C_GFX_TXP6

P_GFX_TXP6

AA1

C_GFX_TXN6

P_GFX_TXN6

AA4

C_GFX_TXP7

P_GFX_TXP7

AA5

C_GFX_TXN7

P_GFX_TXN7

Y2

C_GFX_TXP8

P_GFX_TXP8

Y3

C_GFX_TXN8

P_GFX_TXN8

W2

C_GFX_TXP9

P_GFX_TXP9

W1

C_GFX_TXN9

P_GFX_TXN9

W4

C_GFX_TXP10

P_GFX_TXP10

W5

C_GFX_TXN10

P_GFX_TXN10

V2

C_GFX_TXP11

P_GFX_TXP11

V3

C_GFX_TXN11

P_GFX_TXN11

U2

C_GFX_TXP12

P_GFX_TXP12

U1

C_GFX_TXN12

P_GFX_TXN12

U4

C_GFX_TXP13

P_GFX_TXP13

U5

C_GFX_TXN13

P_GFX_TXN13

T2

C_GFX_TXP14

P_GFX_TXP14

T3

C_GFX_TXN14

P_GFX_TXN14

R2

C_GFX_TXP15

P_GFX_TXP15

R1

C_GFX_TXN15

P_GFX_TXN15

AH2

P_GPP_TXP0

AH3

P_GPP_TXN0

AG2

P_GPP_TXP1

AG1

P_GPP_TXN1

GPP GRAPHICS

GPP GRAPHICS

UMI_LINK

UMI_LINK

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

AG4

AG5

AF2

AF3

AK8

AK9

AL7

AL8

AK5

AK6

AJ7

AJ8

J6

C_UMI_TXP0

C_UMI_TXN0

C_UMI_TXP1

C_UMI_TXN1

C_UMI_TXP2

C_UMI_TXN2

C_UMI_TXP3

C_UMI_TXN3

C1 0.1uF

C1 0.1uF

C2 0.1uF

C2 0.1uF

C3 0.1uF

C3 0.1uF

C4 0.1uF

C4 0.1uF

C5 0.1uF

C5 0.1uF

C6 0.1uF

C6 0.1uF

C7 0.1uF

C7 0.1uF

C8 0.1uF

C8 0.1uF

C9 0.1uF

C9 0.1uF

C10 0.1uF

C10 0.1uF

C11 0.1uF

C11 0.1uF

C12 0.1uF

C12 0.1uF

C13 0.1uF

C13 0.1uF

C14 0.1uF

C14 0.1uF

C15 0.1uF

C15 0.1uF

C16 0.1uF

C16 0.1uF

C17 0.1uF

C17 0.1uF

C18 0.1uF

C18 0.1uF

C19 0.1uF

C19 0.1uF

C20 0.1uF

C20 0.1uF

C21 0.1uF

C21 0.1uF

C22 0.1uF

C22 0.1uF

C23 0.1uF

C23 0.1uF

C24 0.1uF

C24 0.1uF

C25 0.1uF

C25 0.1uF

C26 0.1uF

C26 0.1uF

C27 0.1uF

C27 0.1uF

C28 0.1uF

C28 0.1uF

C29 0.1uF

C29 0.1uF

C30 0.1uF

C30 0.1uF

C31 0.1uF

C31 0.1uF

C32 0.1uF

C32 0.1uF

C37 0.1uF

C37 0.1uF

C38 0.1uF

C38 0.1uF

C39 0.1uF

C39 0.1uF

C40 0.1uF

C40 0.1uF

C41 0.1uF

C41 0.1uF

C42 0.1uF

C42 0.1uF

C43 0.1uF

C43 0.1uF

C44 0.1uF

C44 0.1uF

R2 196

R2 196

AF8

AF9

AE7

AE8

AD5

AD6

AD8

AD9

AC7

AC8

AB5

AB6

AB8

AB9

AA7

AA8

Y5

Y6

Y8

Y9

W7

W8

V5

V6

V8

V9

U7

U8

T5

T6

T8

T9

AH5

AH6

AH8

AH9

AG7

AG8

AF5

AF6

AL5

AL4

AK3

AK2

AJ2

AJ1

AJ4

AJ5

J7

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

*

*

+/-1%

+/-1%

*

*

GFX_TXP0 20

GFX_TXN0 20

GFX_TXP1 20

GFX_TXN1 20

GFX_TXP2 20

GFX_TXN2 20

GFX_TXP3 20

GFX_TXN3 20

GFX_TXP4 20

GFX_TXN4 20

GFX_TXP5 20

GFX_TXN5 20

GFX_TXP6 20

GFX_TXN6 20

GFX_TXP7 20

GFX_TXN7 20

GFX_TXP8 20

GFX_TXN8 20

GFX_TXP9 20

GFX_TXN9 20

GFX_TXP10 20

GFX_TXN10 20

GFX_TXP11 20

GFX_TXN11 20

GFX_TXP12 20

GFX_TXN12 20

GFX_TXP13 20

GFX_TXN13 20

GFX_TXP14 20

GFX_TXN14 20

GFX_TXP15 20

GFX_TXN15 20

UMI_TXP0 13

UMI_TXN0 13

UMI_TXP1 13

UMI_TXN1 13

UMI_TXP2 13

UMI_TXN2 13

UMI_TXP3 13

UMI_TXN3 13

APU_VDD_RUN APU_VDD_RUN APU_VDD_RUN

C234

*

*

C234

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

C236

C236

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

C237

C237

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

CPUHS1

CPUHS1

HEATSINK_SOCKET_FM1

HEATSINK_SOCKET_FM1

APU_VDD_RUN APU_VDD_RUN

C570

C570

0.1uF

0.1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Place across each APU_VDD_RUN--GND plane seam

*

*

C569

C569

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

FM1 PCIE I/F

FM1 PCIE I/F

FM1 PCIE I/F

A75M02

A75M02

A75M02

6

6

6

of

39

of

39

of

39

1.0

1.0

1.0

Page 7

MEM_MA_ADD[0..15]10

MEM_MA_BANK[0..2]10

MEM_MA_DM[0..7]10

APU_M_VREF_SUS

APU_VDDIO_SUS

APU_VDDIO_SUS

MEM_MA_DQSP010

MEM_MA_DQSN010

MEM_MA_DQSP110

MEM_MA_DQSN110

MEM_MA_DQSP210

MEM_MA_DQSN210

MEM_MA_DQSP310

MEM_MA_DQSN310

MEM_MA_DQSP410

MEM_MA_DQSN410

MEM_MA_DQSP510

MEM_MA_DQSN510

MEM_MA_DQSP610

MEM_MA_DQSN610

MEM_MA_DQSP710

MEM_MA_DQSN710

MEM_MA_CLKP110

MEM_MA_CLKN110

MEM_MA_CLKP210

MEM_MA_CLKN210

MEM_MA_CKE010

MEM_MA_CKE110

MEM_MA0_ODT010

MEM_MA0_ODT110

MEM_MA0_CSJ010

MEM_MA0_CSJ110

MEM_MA_RASJ10

MEM_MA_CASJ10

MEM_MA_WEJ10

MEM_MA_RSTJ10

MEM_MA_HOTJ10

R3 39.2

R3 39.2

*

*

PLACE WITHIN 1.5" OF APU

R302 1K

R302 1K

*

*

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_HOTJ

+/-1%

+/-1%

+/-5%

+/-5%

M_ZVDDIO

MEM_MA_HOTJ

AF29

AE25

AG21

AF17

AE28

AE29

AG24

AG25

AF20

AF21

AE16

AD16

AA24

AC27

AA25

AC26

AB26

AB25

U1A

U1A

MEMORY CHANNEL A

MEMORY CHANNEL A

V27

MA_ADD0

P27

MA_ADD1

R25

MA_ADD2

P26

MA_ADD3

R24

MA_ADD4

P24

MA_ADD5

P23

MA_ADD6

N26

MA_ADD7

N23

MA_ADD8

M25

MA_ADD9

V24

MA_ADD10

N25

MA_ADD11

M24

MA_ADD12

Y23

MA_ADD13

L27

MA_ADD14

L24

MA_ADD15

W26

MA_BANK0

V25

MA_BANK1

L26

MA_BANK2

H12

MA_DM0

E17

MA_DM1

H21

MA_DM2

F25

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

G29

MA_DM8

G13

MA_DQS_H0

F13

MA_DQS_L0

H17

MA_DQS_H1

G17

MA_DQS_L1

F21

MA_DQS_H2

E21

MA_DQS_L2

G26

MA_DQS_H3

G25

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

F30

MA_DQS_H8

E30

MA_DQS_L8

U27

MA_CLK_H0

U26

MA_CLK_L0

T23

MA_CLK_H1

U23

MA_CLK_L1

T25

MA_CLK_H2

T26

MA_CLK_L2

R27

MA_CLK_H3

R28

MA_CLK_L3

L23

MA_CKE0

K26

MA_CKE1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

Y27

MA0_CS_L0

MA0_CS_L1

W23

MA1_CS_L0

MA1_CS_L1

W25

MA_RAS_L

Y24

MA_CAS_L

Y26

MA_WE_L

J25

MA_RESET_L

U24

MA_EVENT_L

K22

M_VREF

J24

M_ZVDDIO

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_CHECK0

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

E12

F12

H14

E15

G11

H11

E14

G14

F16

G16

H18

F19

F15

H15

E18

F18

G20

H20

E23

G23

G19

E20

F22

G22

F24

H24

E27

F27

H23

E24

E26

H26

AD30

AF30

AG27

AF27

AD31

AE31

AG28

AD28

AF26

AD25

AF23

AE23

AD27

AE26

AF24

AD24

AG22

AD21

AE19

AG19

AD22

AE22

AE20

AD19

AG18

AE17

AF15

AG15

AD18

AF18

AG16

AD15

F28

E29

G31

H30

H27

G28

F31

H29

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DATA[0..63] 10

MEM_MB_ADD[0..15]12

MEM_MB_BANK[0..2]12

MEM_MB_DM[0..7]12

MEM_MB_DQSP012

MEM_MB_DQSN012

MEM_MB_DQSP112

MEM_MB_DQSN112

MEM_MB_DQSP212

MEM_MB_DQSN212

MEM_MB_DQSP312

MEM_MB_DQSN312

MEM_MB_DQSP412

MEM_MB_DQSN412

MEM_MB_DQSP512

MEM_MB_DQSN512

MEM_MB_DQSP612

MEM_MB_DQSN612

MEM_MB_DQSP712

MEM_MB_DQSN712

MEM_MB_CLKP112

MEM_MB_CLKN112

MEM_MB_CLKP212

MEM_MB_CLKN212

MEM_MB_CKE012

MEM_MB_CKE112

MEM_MB0_ODT012

MEM_MB0_ODT112

MEM_MB0_CSJ012

MEM_MB0_CSJ112

MEM_MB_RASJ12

MEM_MB_CASJ12

MEM_MB_WEJ12

MEM_MB_RSTJ12

MEM_MB_HOTJ12

APU_VDDIO_SUS

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_HOTJ

R312 1K

R312 1K

*

*

M30

M31

M28

M27

W31

AB28

W29

AL29

AH25

AK21

AJ17

AJ29

AH29

AK25

AL25

AJ20

AJ21

AL16

AL17

AA30

AC30

AA31

AC29

AB29

AB31

W28

AA27

AA28

+/-5%

+/-5%

V31

N28

P29

N29

N31

L30

L29

K28

K31

J31

V30

K29

B12

D16

B20

A25

D29

D13

C13

A17

B17

B21

C21

D25

C25

B29

A29

U30

U29

T29

T28

R31

T31

P30

R30

J30

J28

Y29

Y30

J27

V28

MEM_MB_HOTJ

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DM8

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_DQS_H8

MB_DQS_L8

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB_CKE0

MB_CKE1

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB1_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

MEMORY CHANNEL B

MEMORY CHANNEL B

U1B

U1B

D11

C12

A14

B14

B11

A11

A13

D14

A16

C16

B18

A19

C15

B15

D17

C18

D20

A20

D22

D23

C19

D19

A22

C22

C24

B24

B26

C27

A23

B23

D26

A26

AJ30

AK30

AH28

AJ27

AG30

AH31

AK28

AL28

AJ26

AH26

AH23

AJ23

AK27

AL26

AJ24

AK24

AK22

AH22

AL19

AK19

AL23

AL22

AH20

AL20

AJ18

AH17

AJ15

AK15

AH19

AK18

AK16

AH16

A28

D28

C30

D31

B27

C28

B30

C31

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

MEM_MB_DATA[0..63] 12

APU_VDDIO_SUS

C45

C45

R4

R4

*

*

0.1uF

0.1uF

1K

1K

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

+/-1%

+/-1%

Dummy

Dummy

APU_M_VREF_SUS

R5

R5

*

*

1K

1K

+/-1%

+/-1%

*

*

C46

C46

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

C47

C47

1nF

1nF

50V, X7R, +/-10%

50V, X7R, +/-10%

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

FM1 DDR3 MEM I/F

FM1 DDR3 MEM I/F

FM1 DDR3 MEM I/F

A75M02

A75M02

A75M02

7

7

7

of

39

of

39

of

39

1.0

1.0

1.0

Page 8

APU_SIC

APU_SID

APU_VDDIO_SUS

APU_ALERTJ

APU_THERMTRIPJ

642

135

*

*

APU_VDDIO_SUS

R9

R9

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

Q1

Q1

FDV301N

FDV301N

G

Dummy

Dummy

1 2

APU_VDDIO_SUS

R11

R11

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

Q2

Q2

FDV301N

FDV301N

G

Dummy

Dummy

1 2

E C

Q3

Q3

MMBT3904-7-F

MMBT3904-7-F

E C

Q4

Q4

MMBT3904-7-F

MMBT3904-7-F

7 8

135

B

B

APU_VDDIO_SUS

R52

R52

R53

R53

*

*

*

RN10

RN10

1K

1K

+/-5%

+/-5%

DS

DS

642

*

*

7 8

3D3V_ALW

3D3V_ALW

3D3V_ALW

RN72

RN72

10K

10K

+/-5%

+/-5%

FM1R1

*

*

*

*

135

*

*

R8

R8

4.7K

4.7K

+/-5%

+/-5%

Dummy

Dummy

R12

R12

4.7K

4.7K

+/-5%

+/-5%

Dummy

Dummy

RN9

RN9

642

300

300

+/-5%

+/-5%

7 8

*

1K

1K

1K

1K

+/-5%

+/-5%

+/-5%

+/-5%

APU_SVC_R

APU_SVD_R

FCH_APU_RSTJ

APU_VDDIO_PG

APU_PROCHOTJ

APU_THERMTRIPJ

APU_ALERTJ

APU_SIC

APU_SID

FCH_APU_SIC 14

SIO_APU_SIC 28

FCH_APU_SID 14

SIO_APU_SID 28

ALERTJ 15

FCH_APU_THERMTRIPJ 14

APU_VDDIO_SUS

R34

R34

300

300

+/-5%

+/-5%

*

*

RN13

RN13

1K Ohm

1K Ohm

1

3

5

7 8

2

4

6

*

*

APU_VDD_RUN APU_VDD_RUN

ML_VGA_LP015

ML_VGA_LN015

ML_VGA_LP115

ML_VGA_LN115

ML_VGA_LP215

ML_VGA_LN215

ML_VGA_LP315

ML_VGA_LN315

APU_CLKP13

APU_CLKN13

APU_SVC34

APU_SVD34

+/-5%

+/-5%

APU_TRSTJ

APU_TDI

APU_TMS

APU_TCK

need check it

APU_VDDP_FB_H36

APU_VDDNB_FB_H34

APU_VDDIO_FB_H33

APU_VDD_FB_H34

APU_VDD_FB_L34

*

*

C235

C235

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

DP0_TXP018

DP0_TXN018

DP0_TXP118

DP0_TXN118

DP0_TXP218

DP0_TXN218

DP0_TXP318

DP0_TXN318

APU_DISP_CLKP13

APU_DISP_CLKN13

FCH_APU_RSTJ13

APU_VDDIO_PG13

APU_PROCHOTJ13,14

C277 0.1uF

C277 0.1uF

C278 0.1uF

C278 0.1uF

C279 0.1uF

C279 0.1uF

C280 0.1uF

C280 0.1uF

C285 0.1uF

C285 0.1uF

C286 0.1uF

C286 0.1uF

C287 0.1uF

C287 0.1uF

C288 0.1uF

C288 0.1uF

1 2

1 2

R39 0

R39 0

*

*

1 2

1 2

C639

C639

0.1uF

0.1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

U1C

U1C

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

M2

DP0_TXP0

M3

DP0_TXN0

L2

DP0_TXP1

L1

DP0_TXN1

L4

DP0_TXP2

L5

DP0_TXN2

K2

DP0_TXP3

K3

AL12

AK12

AH12

AG12

AF10

AG10

AJ13

AG11

AL14

AK14

AD10

AF13

DP0_TXN3

R4

DP1_TXP0

R5

DP1_TXN0

P2

DP1_TXP1

P3

DP1_TXN1

N2

DP1_TXP2

N1

DP1_TXN2

N4

DP1_TXP3

N5

DP1_TXN3

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

A8

SVC

B8

SVD

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

E9

TDI

G10

TDO

E8

TCK

D8

TMS

F10

TRST_L

D7

DBRDY

F8

DBREQ_L

E11

RSVD_1

H9

RSVD_2

K23

RSVD_3

K25

RSVD_4

RSVD_5

B5

VDDP_SENSE

A6

VDDNB_SENSE

B6

VDDIO_SENSE

C7

VDD_SENSE

A5

VDDR_SENSE

C6

VSS_SENSE

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXP0

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXN0

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXP1

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXN1

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXP2

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXN2

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXP3

16V, X7R, +/-10%

16V, X7R, +/-10%

DP1_TXN3

APU_SVC_R

APU_SVD_R

APU_SIC

APU_SID

FCH_APU_RSTJ

APU_VDDIO_PG

APU_PROCHOTJ

APU_THERMTRIPJ

APU_ALERTJ

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRSTJ

APU_DBRDY

APU_DBREQJ

APU_VDDP_SENSE

APU_VDDNB_SENSE

APU_VDDIO_SENSE APU_TEST35

APU_VDDR_SENSE

TP42TP42

TP43TP43

*

*

*

*

*

*

*

*

*

*

*

*

*

*

+/-5%

+/-5%

TP41TP41

TP9TP9

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT MISC.

DISPLAY PORT MISC.

DISPLAY PORT 1

DISPLAY PORT 1

CLK

CLK

CTRL SER.

CTRL SER.

TEST

TEST

JTAG

JTAG

SENSE RSVD

SENSE RSVD

APU_VDD_RUN

C668

C668

0.1uF

0.1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

+/ -1%

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

THERMDA

THERMDC

TEST10

TEST12

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST21

TEST22

TEST23

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

DMAACTIVE_L

TEST2

TEST3

TEST6

TEST9

FM1R1

J9

R6 150

R6 150

G9

G7

H8

K6

K8

L7

DP1_AUXP_C

L8

DP1_AUXN_C

R7

R8

P8

P9

N7

N8

M8

M9

K9

K5

P5

R15 100K

R15 100K

P6

R16 100K

R16 100K

M5

R17 100K

R17 100K

M6

R18 100K

R18 100K

AH14

APU_THERMDA

AG14

APU_THERMDC

AB23

AC24

AG13

D10

APU_TEST9

C10

F6

APU_TEST12

D9

APU_TEST14

C9

APU_TEST15

B9

APU_TEST16

A9

APU_TEST17

E4

APU_TEST18

F5

APU_TEST19

D4

APU_TEST20

D5

APU_TEST21

E5

APU_TEST22

F7

E6

APU_TEST24

AE11

APU_TEST25_H

AD11

APU_TEST25_L

G5

G6

AD14

APU_TEST30_H

AE14

APU_TEST30_L

AG31

APU_TEST31

AE13

APU_TEST32_H

AD13

APU_TEST32_L

A7

AC12

FM1R1

AF11

DP1_HPD_C

*

*

C202 0.1uF

C202 0.1uF

C203 0.1uF

C203 0.1uF

*

*

*

*

*

*

*

*

+/ -1%

DP0_AUXP_C 18

DP0_AUXN_C 18

*

*

*

*

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

TP27TP27

TP28TP28

R23 0

R23 0

TP1TP1

TP2TP2

TP3TP3

TP4TP4

R36 511 Ohm

R36 511 Ohm

R37 511 Ohm

R37 511 Ohm

TP5TP5

TP6TP6

R38 39.2

R38 39.2

TP7TP7

R182 300

R182 300

TP8TP8

R42 300

R42 300

R46 1K

R46 1K

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

DP0_HPD_C 18

RN17 1K Ohm

RN17 1K Ohm

*

*

1

3

5

7 8

RN19 1K Ohm

RN19 1K Ohm

*

*

1

3

5

7 8

2011-07-07: Change R182 from 1k to 300 ohm

*

*

*

*

*

*

*

*

*

*

*

*

*

*

2

4

6

2

4

6

+/-5%Dummy

+/-5%Dummy

+/-5%

+/-5%

+/-5%

+/-5%

+/-1%

+/-1%

+/-5%

+/-5%

+/-5%Dummy

+/-5%Dummy

+/-5%

+/-5%

AUX_VGA_CH_P 15

AUX_VGA_CH_N 15

APU_VDDP_RUN

+/-1%

+/-1%

+/-1%

+/-1%

FM1R1 37

FCH_DMA_ACTIVEJ 13

APU_VDDIO_SUS

APU_VDDIO_SUS

APU_VDDIO_SUS 3D3V_ALW

R187

R187

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

Q7

Q7

B

MMBT3904-7-F

MMBT3904-7-F

Dummy

Dummy

APU_VDDIO_PG

2011-07-07: For ISL6328_POWOK_R Dummy R187, Q7, R207,

stuff R43 following CRB

E C

R43 0

R43 0

*

*

+/-5%

+/-5%

R188

R188

*

*

4.7K

4.7K

+/-5%

+/-5%

Dummy

Dummy

APU_VDDIO_SUS

R207

R207

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

ISL6328_PWROK_R 34

APU_VDDIO_SUS

+/-1%

+/-1%

R203 10K

R203 10K

*

ML_VGA_HPD15

*

B

Q17

Q17

MMBT3904-7-F

MMBT3904-7-F

E C

R204

R204

*

*

1K

1K

+/-1%

+/-1%

DP1_HPD_C

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

FM1 DISPLAY & MISC

FM1 DISPLAY & MISC

FM1 DISPLAY & MISC

A75M02

A75M02

A75M02

8

8

8

of

39

of

39

of

39

1.0

1.0

1.0

Page 9

PROCESSOR POWER AND GROUND

VDD = Variable per VID VDDIO = 1.25V/1.35V/1.5V (DDR3)

APU_VDD_RUN APU_VDD_RUN APU_VDDIO_SUS

U1D

U1D

VDD

M12

P12

H10

U19

K10

K12

K14

K16

K18

K20

W19

N19

M10

W13

M16

M18

M20

U21

N11

N21

P10

P20

R11

R21

T10

T12

T20

VDD

VDD

VDD

VDD

H6

VDD

VDD

J11

VDD

J13

VDD

J15

VDD

J17

VDD

J19

VDD

J21

VDD

J5

VDD

VDD

VDD

VDD

VDD

VDD

VDD

K4

VDD

L11

VDD

VDD

L15

VDD

L17

VDD

VDD

L21

VDD

L3

VDD

L6

VDD

M1

VDD

VDD

VDD

VDD

VDD

VDD

VDD

M4

VDD

M7

VDD

VDD

VDD

P1

VDD

VDD

VDD

VDD

VDD

R3

VDD

R6

VDD

T1

VDD

VDD

VDD

VDD

T4

VDD

T7

VDD

U11

VDD

U13

VDD

V1

VDD

V10

VDD

V12

VDD

V20

VDD

W11

VDD

W21

VDD

W3

VDD

W6

VDD

Y1

VDD

Y10

VDD

Y12

VDD

Y14

VDD

Y16

VDD

Y18

VDD

Y20

VDD

Y4

VDD

Y7

VDD

AA11

VDD

AA13

VDD

AA15

VDD

AA17

VDD

AA19

VDD

AA21

VDD

AB1

VDD

AB10

VDD

R13

VDD

AB14

VDD

AB16

VDD

AB18

VDD

R19

VDD

AC11

VDD

AC13

VDD

AC15

VDD

AC17

VDD

AC19

VDD

AC21

VDD

AC3

VDD

AC6

VDD

AD1

VDD

AD4

VDD

AD7

VDD

AF1

VDD

AG3

VDD

AG6

VDD

AH1

VDD

AH4

VDD

AH7

VDD

AK4

VDD

AK7

VDD

AA23

AA26

AA29

AB22

AB24

AB27

AB30

AC23

AC25

AC28

AC31

U1G

AA10

AA14

AA16

AA18

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AC10

AC14

AC16

AC18

AC20

AC22

AD17

AD20

AD23

AD26

AD29

AE10

AE15

AE18

AE21

AE24

AE27

U1G

VSS

VSS

T11

VSS

T21

VSS

U10

VSS

U12

VSS

U20

VSS

U22

VSS

U3

VSS

U6

VSS

U9

VSS

V11

VSS

V21

VSS

V4

VSS

V7

VSS

W10

VSS

W12

VSS

W20

VSS

W22

VSS

W9

VSS

Y11

VSS

Y13

VSS

Y15

VSS

Y17

VSS

Y19

VSS

Y21

VSS

VSS

VSS

VSS

VSS

VSS

AA3

VSS

AA6

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB4

VSS

AB7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE3

VSS

AE30

VSS

AE6

VSS

AE9

VSS

AF12

VSS

AF14

VSS

AF16

VSS

AF19

VSS

AF22

VSS

AF25

VSS

AF28

VSS

AF31

VSS

AF4

VSS

AF7

VSS

AG17

VSS

AG20

VSS

AG23

VSS

AG26

VSS

AG29

VSS

AG9

VSS

AH13

VSS

AH15

VSS

AH18

VSS

AH21

VSS

AH24

VSS

AH27

VSS

AH30

VSS

AJ12

VSS

AJ14

VSS

AJ16

VSS

AJ19

VSS

AJ22

VSS

AJ25

VSS

AJ28

VSS

AJ3

VSS

AJ31

VSS

AJ6

VSS

AJ9

VSS

AK13

VSS

AK17

VSS

AK20

VSS

AK23

VSS

AK26

VSS

AK29

VSS

AL13

VSS

AL15

VSS

AL18

VSS

AL21

VSS

AL24

VSS

AL27

VSS

AL3

VSS

AL6

VSS

M19

VSS

P13

VSS

P19

VSS

T13

VSS

T19

VSS

U1F

U1F

VSS

VSS

A10

VSS_1

A12

VSS_2

A15

VSS_3

A18

VSS_4

A21

VSS_5

A24

VSS_6

A27

U1E

U1E

POWER

POWER

J26

VDDIO

J29

VDDIO

K24

VDDIO

K27

VDDIO

K30

VDDIO

L25

VDDIO

L28

VDDIO

L31

VDDIO

M23

VDDIO

M26

VDDIO

M29

VDDIO

N24

VDDIO

N27

VDDIO

N30

VDDIO

P22

VDDIO

P25

VDDIO

P28

VDDIO

P31

VDDIO

R23

VDDIO

R26

VDDIO

R29

VDDIO

T22

VDDIO

T24

VDDIO

T27

VDDIO

T30

VDDIO

U25

VDDIO

U28

VDDIO

U31

VDDIO

V22

VDDIO

V23

VDDIO

V26

VDDIO

V29

VDDIO

W24

VDDIO

W27

VDDIO

W30

VDDIO

Y22

VDDIO

Y25

VDDIO

Y28

VDDIO

Y31

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

M22

VDDIO

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB_CAP_1

VDDNB_CAP_2

VDDP_A_1

VDDP_A_2

VDDP_A_3

VDDP_A_4

VDDP_B_1

VDDP_B_2

VDDP_B_3

VDDP_B_4

VDDA

VDDA

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

APU_VDDA_RUN

AD12

AE12

A3

A4

B3

B4

C1

C2

C3

C4

C5

D1

D2

D3

E1

E2

E3

F1

F2

F3

Place close pin M14 and N13 inside the backplate cavity opening

F4

M14

N13

APU_VDDP_RUN

AH10

AJ10

AK10

AL10

APU_VDDR_RUN

AH11

AJ11

AK11

AL11

J1

J2

J3

J4

*

*

H1

H2

H3

H4

*

*

C62 22uF

C62 22uF

C63 22uF

C63 22uF

C69

C69

10uF

10uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

C74

C74

10uF

10uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

APU_VDDNB_RUN

*

*

*

*

C70

C70

4.7uF

4.7uF

*

*

+/-10%

+/-10%

C75

C75

4.7uF

4.7uF

*

*

+/-10%

+/-10%

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C71

C71

12

220nF

220nF

*

*

+/-10%

+/-10%

C76

C76

4.7uF

4.7uF

*

*

+/-10%

+/-10%

APU_VDDP_RUN

APU_VDDR_RUN

C72

C72

1nF

1nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C77

C77

12

220nF

220nF

*

*

+/-10%

+/-10%

C56

C56

10uF

10uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

C64

C64

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

APU_VDDP_B_RUN

*

*

*

*

C73

C73

1nF

1nF

50V, X7R, +/-10%

50V, X7R, +/-10%

C78

C78

12

220nF

220nF

+/-10%

+/-10%

C57

C57

10uF

10uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

C65

C65

4.7uF

4.7uF

*

*

+/-10%

+/-10%

APU_VDDR_B_RUN

C60

C58

C58

4.7uF

4.7uF

*

*

*

*

+/-10%

+/-10%

C67

C67

C66

C66

12

220nF

220nF

4.7uF

4.7uF

*

*

*

*

+/-10%

+/-10%

+/-10%

+/-10%

C60

C59

C59

12

1nF

1nF

220nF

220nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

+/-10%

+/-10%

C68

C68

12

220nF

220nF

*

*

+/-10%

+/-10%

*

*

C61

C61

1nF

1nF

50V, X7R, +/-10%

50V, X7R, +/-10%

VSS_7

AL9

VSS_8

B10

VSS_9

B13

VSS_10

B16

VSS_11

B19

VSS_12

B22

VSS_13

B25

VSS_14

B28

VSS_15

B7

VSS_16

C11

VSS_17

C14

VSS_18

C17

VSS_19

C20

VSS_20

C23

VSS_21

C26

VSS_22

C29

VSS_23

C8

VSS_24

D12

VSS_25

D15

VSS_26

D18

VSS_27

D21

VSS_28

D24

VSS_29

D27

VSS_30

D30

VSS_31

D6

VSS_32

E10

VSS_33

E13

VSS_34

E16

VSS_35

E19

VSS_36

E22

VSS_37

E25

VSS_38

E28

VSS_39

E31

VSS_40

E7

VSS_41

F11

VSS_42

F14

VSS_43

F17

VSS_44

F20

VSS_45

F23

VSS_46

F26

VSS_47

F29

VSS_48

F9

VSS_49

G1

VSS_50

G12

VSS_51

G15

VSS_52

G18

VSS_53

G2

VSS_54

G21

VSS_55

G24

VSS_56

G27

VSS_57

G3

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

G30

G4

G8

H13

H16

H19

H22

H25

H28

H31

H5

H7

J10

J12

J14

J16

J18

J20

J22

J23

J8

K1

K11

V13

K15

K17

V19

K21

K7

L10

L12

L14

L16

L18

L20

L22

L9

M11

M13

M15

M17

M21

N10

N12

N20

N22

N3

N6

N9

P11

P21

P4

P7

R10

R12

R20

R22

R9

APU_VDD_RUN

C651

C651

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

APU_VDD_RUN

C92

C92

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

APU_VDD_RUN

C108

C108

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

APU_VDDNB_RUN

C122

C122

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

APU_VDDIO_SUS

C137

C137

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C654

*

*

C654

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

*

*

C294

C294

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

BOTTOM SIDE DECOUPLING

C93

*

*

*

*

*

*

*

*

C93

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C109

C109

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C123

C123

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C138

C138

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

*

*

*

*

*

*

*

*

C94

C94

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C110

C110

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

@MLCC

@MLCC

C124

C124

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C139

C139

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

*

*

*

*

*

*

*

*

*

*

C653

C653

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C95

C95

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

@MLCC

@MLCC

C111

C111

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C125

C125

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C140

C140

10uF

10uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

*

*

*

*

*

*

*

*

*

*

C293

C293

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C96

C96

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

@MLCC

@MLCC

C112

C112

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C126

C126

4.7uF

4.7uF

+/-10%

+/-10%

C141

C141

4.7uF

4.7uF

+/-10%

+/-10%

*

*

*

*

*

*

12

*

*

*

*

C652

C652

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C97

C97

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C113

C113

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

@MLCC

@MLCC

C127

C127

220nF

220nF

+/-10%

+/-10%

C142

C142

4.7uF

4.7uF

+/-10%

+/-10%

12

*

*

C82

C82

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

EMC Caps On Bottom

APU_VDDNB_RUN APU_VDDP_RUN APU_VDDR_RUN APU_VDDP_B_RUN APU_VDDR_B_RUN

APU_VDD_RUN

C79

C79

12

180pF

180pF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

12

*

*

C80

C80

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

12

*

*

C81

C81

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

2011-07-23: EC57 CO-LAY C95,C96,C98,C110,C113,C114

C99

*

*

*

*

12

*

*

*

*

C98

C98

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

@MLCC

@MLCC

C114

C114

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

@MLCC

@MLCC

C128

C128

220nF

220nF

+/-10%

+/-10%

C143

C143

4.7uF

4.7uF

+/-10%

+/-10%

*

*

*

*

*

*

C99

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C115

C115

4.7uF

4.7uF

+/-10%

+/-10%

C144

C144

4.7uF

4.7uF

+/-10%

+/-10%

C100

C100

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C116

C116

4.7uF

4.7uF

*

*

+/-10%

+/-10%

APU_VDD_RUN

C129

C129

10nF

10nF

*

*

+/-10%

+/-10%

C145

C145

12

220nF

220nF

*

*

+/-10%

+/-10%

*

*

*

*

*

*

12

*

*

C101

C101

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C118

C118

4.7uF

4.7uF

+/-10%

+/-10%

Dummy

Dummy

C130

C130

10nF

10nF

+/-10%

+/-10%

C146

C146

220nF

220nF

+/-10%

+/-10%

*

*

*

*

*

*

APU_VDDNB_RUN

*

*

12

*

*

C102

C102

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C119

C119

4.7uF

4.7uF

+/-10%

+/-10%

Dummy

Dummy

C131

C131

10nF

10nF

+/-10%

+/-10%

Dummy

Dummy

C657

C657

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C83

C83

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

12

*

*

*

*

*

*

*

*

*

*

C120

C120

220nF

220nF

+/-10%

+/-10%

Dummy

Dummy

C132

C132

10nF

10nF

+/-10%

+/-10%

Dummy

Dummy

C656

C656

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C84

C84

12

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

EC57

EC57

330uF

330uF

@NO_MLCC

@NO_MLCC

*

*

12

*

*

C121

C121

220nF

220nF

+/-10%

+/-10%

C655

C655

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

12

*

*

C85

C85

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

3D3V_RUN

*

*

C658

C658

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C86

12

*

*

C103

C103

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C86

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

C87

C87

12

180pF

180pF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

1

R64

R64

2.26K

2.26K

+/-1%

+/-1%

Dummy

Dummy

2

R65

R65

*

*

0

0

+/-5%

+/-5%

APU_VDDIO_SUS APU_VDDIO_SUS

C133

C133

12

220nF

220nF

*

+/-10%

+/-10%

*

*

*

Place across each VDDIO-GND plane seam

C88

C88

12

180pF

180pF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

U2

U2

3

VIN

2

VOUT

1

GND

AP2114H-2.5TRG1

AP2114H-2.5TRG1

C134

C134

12

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

VOUT1

4

*

*

12

*

*

C135

C135

12

220nF

220nF

+/-10%

+/-10%

Dummy

Dummy

C89

C89

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

*

*

*

*

12

*

*

C90

C90

12

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

C117

C117

1uF

1uF

+/-10%

+/-10%

C136

C136

180pF

180pF

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

C91

C91

12

180pF

180pF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

2D5V_VDDA_RUN

C104

C104

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

FB1

FB1

21

FB 30Ohm

FB 30Ohm

APU_VDDIO_SUS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Tuesday, April 24, 2012

Date: Sheet

Date: Sheet

Date: Sheet

APU_VDDA_RUN

C106

C106

C105

C105

12

220nF

220nF

4.7uF

4.7uF

*

*

*

*

FM1 POWER & GND

FM1 POWER & GND

FM1 POWER & GND

A75M02

A75M02

A75M02

+/-10%

+/-10%

+/-10%

+/-10%

C444

C444

22uF

22uF

*

*

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

C107

C107

3.3nF

3.3nF

*

*

+/-10%

+/-10%

1.0

1.0

1.0

of

9

39

of

9

39

of

9

39

Page 10

APU_VDDIO_SUS

R66

R66

*

*

1K

1K

+/-1%

+/-1%

R67

R67

*

*

1K

1K

+/-1%

+/-1%

APU_VDDIO_SUS

R68

R68

*

*

1K

1K

+/-1%

+/-1%

R69

R69

*

*

1K

1K

+/-1%

+/-1%

Device

DIMMA0

DIMMB0

C147

C147

0.1uF

0.1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

C150

C150

0.1uF

0.1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

SMBus 0

8-bit Address (hex)

*

*

*

*

A0

A2

C148

C148

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C151

C151

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

MEM_VREF_CA

*

*

MEM_VREF_DQ

*

*

C149

C149

1nF

1nF

50V, X7R, +/-10%

50V, X7R, +/-10%

C152

C152

1nF

1nF

50V, X7R, +/-10%

50V, X7R, +/-10%

*

*

C153

C153

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

SMB0_CLK12,14

SMB0_DATA12,14

MEM_MA_BANK[2..0]7

MEM_MA_ADD[0..15]7

DIMM1

DIMM1

198

FREE4

MEM_MA_HOTJ7

MEM_VREF_CAMEM_VREF_DQ

APU_VDDIO_SUS

3D3V_RUN

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE17

MEM_MA_CKE07

MEM_MA0_CSJ17

MEM_MA0_CSJ07

MEM_MA_CLKN27

MEM_MA_CLKP27

MEM_MA_CLKN17

MEM_MA_CLKP17

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_RSTJ7

MEM_MA_CASJ7

MEM_MA_RASJ7

MEM_MA_WEJ7

APU_VTT_SUS

187

FREE3

49

FREE2

48

FREE1

240

VTT

120

VTT

239

VSS

235

VSS

232

VSS

229

VSS

226

VSS

223

VSS

220

VSS

217

VSS

214

VSS

211

VSS

208

VSS

205

VSS

202

VSS

199

VSS

166

VSS

163

VSS

160

VSS

157

VSS

154

VSS

151

VSS

148

VSS

145

VSS

142

VSS

139

VSS

136

VSS

133

VSS

130

VSS

127

VSS

124

VSS

121

VSS

119

VSS

116

VSS

113

VSS

110

VSS

107

VSS

104

VSS

101

VSS

98

VSS

95

VSS

92

VSS

89

VSS

86

VSS

83

VSS

80

VSS

47

VSS

44

VSS

41

VSS

38

VSS

35

VSS

32

VSS

29

VSS

26

VSS

23

VSS

20

VSS

17

VSS

14

VSS

11

VSS

8

VSS

5

VSS

2

VSS

197

VDDQ

194

VDDQ

191

VDDQ

189

VDDQ

186

VDDQ

183

VDDQ

182

VDDQ

179

VDDQ

176

VDDQ

173

VDDQ

170

VDDQ

78

VDD

75

VDD

72

VDD

69

VDD

66

VDD

65

VDD

62

VDD

60

VDD

57

VDD

54

VDD

51

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1_L

193

S0_L

64

CK1/NU_L

63

CK1/NU

185

CK0_L

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET_L

74

CAS_L

192

RAS_L

73

WE_L

DDR III

DDR III

DDRIII

DDRIII

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

CB<0>

CB<1>

CB<2>

CB<3>

CB<4>

CB<5>

CB<6>

CB<7>

DQS_H<0>

DQS_L<0>

DQS_H<1>

DQS_L<1>

DQS_H<2>

DQS_L<2>

DQS_H<3>

DQS_L<3>

DQS_H<4>

DQS_L<4>

DQS_H<5>

DQS_L<5>

DQS_H<6>

DQS_L<6>

DQS_H<7>

DQS_L<7>

DQS_H<8>

DQS_L<8>

DM0/DQS9_H

DQS9_L

DM1/DQS10_H

DQS10_L

DM2/DQS11_H

DQS11_L

DM3/DQS12_H

DQS12_L

DM4/DQS13_H

DQS13_L

DM5/DQS14_H

DQS14_L

DM6/DQS15_H

DQS15_L

DM7/DQS16_H

NC/DQS16_L

DM8/DQS17_H

DQS17_L

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQ<8>

DQ<9>

DQ<10>

DQ<11>

DQ<12>

DQ<13>

DQ<14>

DQ<15>

DQ<16>

DQ<17>