Page 1

5

D D

2D6V_STR

BC598

BC597

BC597

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC598

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

*

*

4

BC599

BC599

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC600

BC600

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC601

BC601

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC602

BC602

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

3

BC603

BC603

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

2

1

C C

B B

2D6V_STR

BC604

BC604

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC605

BC605

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC606

BC606

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC607

BC607

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC608

BC608

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

BC609

BC609

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

A A

TECHNOLOGY CORP.

TECHNOLOGY CORP.

Title:

Title:

Title:

Document Number:

Document Number:

Document Number:

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

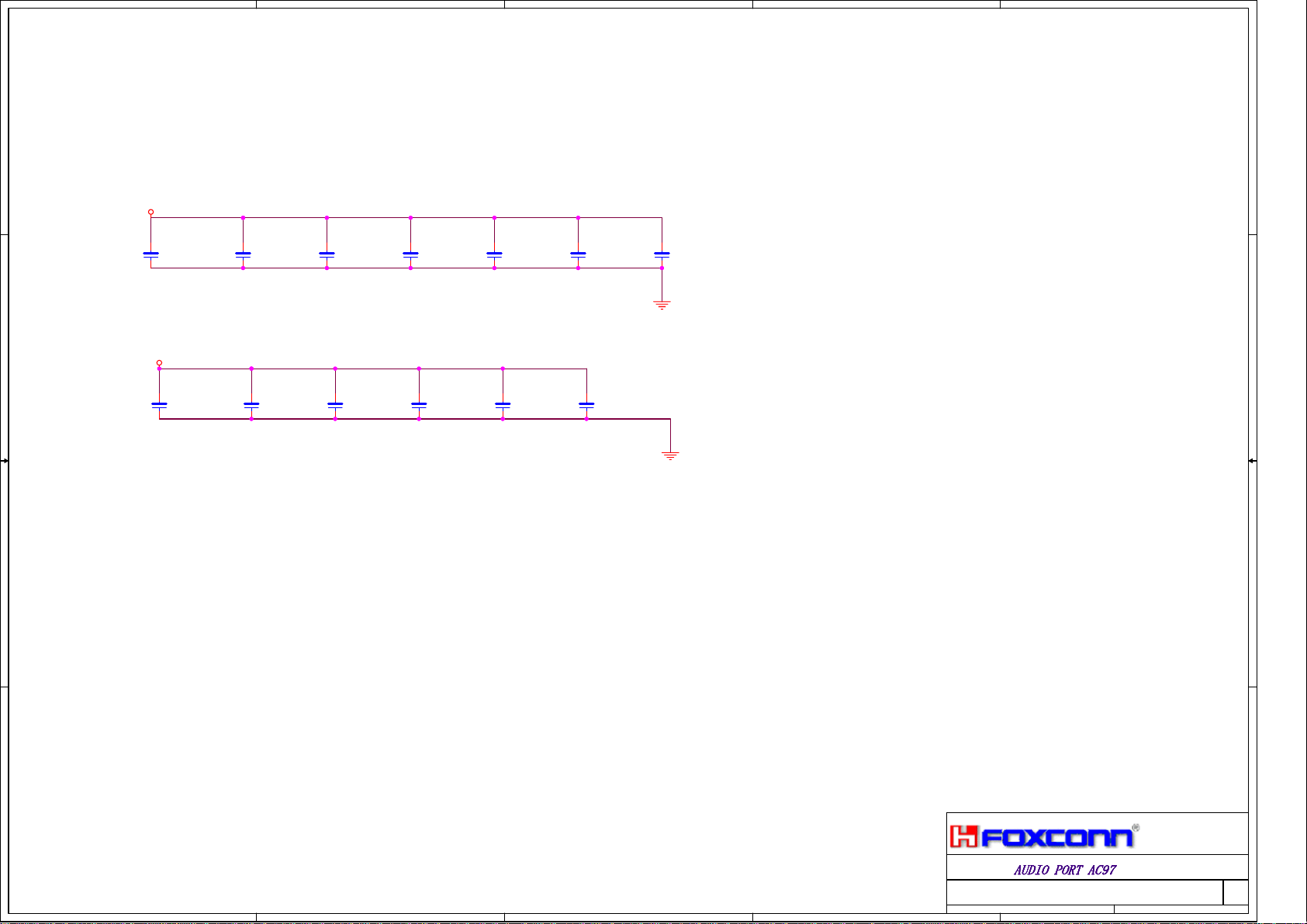

AUDIO PORT AC97

AUDIO PORT AC97

AUDIO PORT AC97

915M12

915M12

915M12

TECHNOLOGY CORP.

of

143Friday, June 17, 2005

of

143Friday, June 17, 2005

of

143Friday, June 17, 2005

1

Rev

Rev

Rev

1.0

1.0

1.0

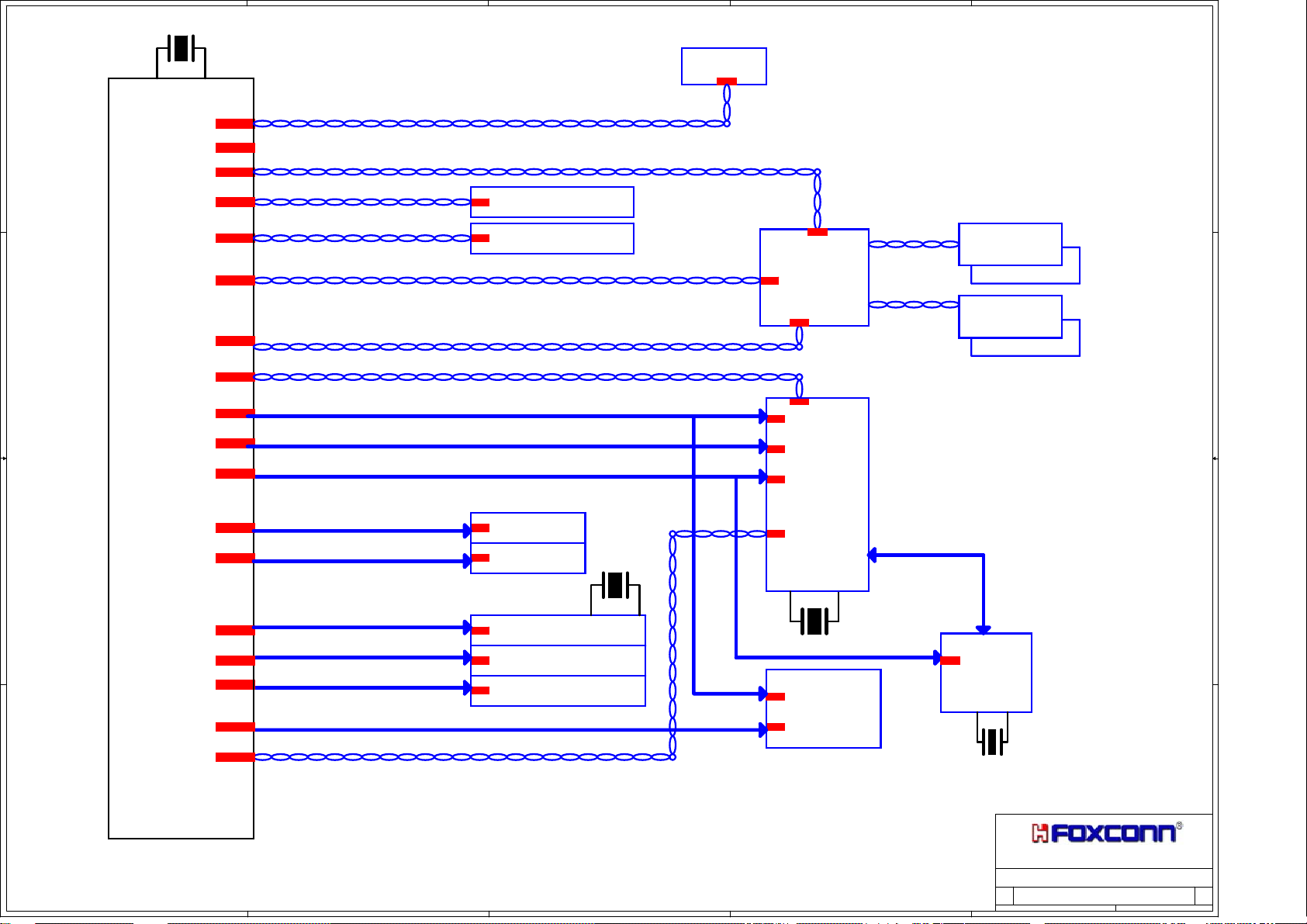

Page 2

5

4

3

2

1

Foxconn Precision Co. Inc.

D D

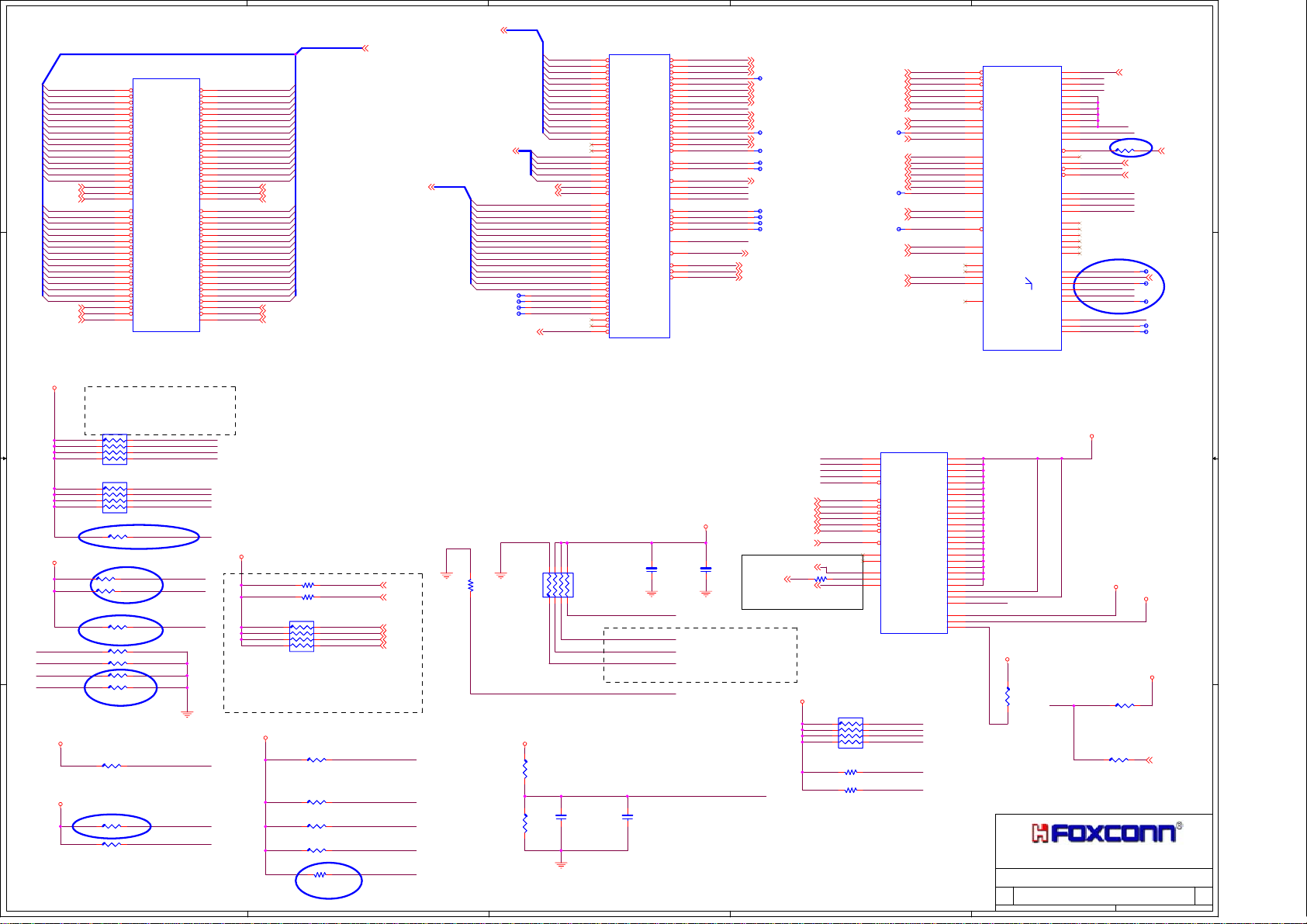

915M12 Schematic

Fab.A

Data: 2005/04/16

Page Index

01. Index Page

02. Topology

03. Reset Map

04. Clock Distribution

C C

05. Power Delivery Map

06. Power Sequence

07. CK410 ClockGen

08. Voltage Regulator Down 10.1

09. VRM INPUT AND OUTPUT

10. Power DDR &1.5V

11. 1D5V_SYS/FSB_VTT/2D5V-MCH

12. LGA775 -1

13. LGA775 -2 35. HW Monitor

14. Grantsdale -GMCH -1

B B

15. Grantsdale -GMCH -2

16. Grantsdale -GMCH -3

17. Grantsdale -GMCH -4

18. Channel A,DIMM 1&2

19. Channel B,DIMM 1&2

20.DIMM Power & Termination

21. PCI Express x16 Gfx Slot

22. ICH6-1

23. ICH6-2

24. ICH6-3

25. LAN_RTL8100C

26. LAN_RTL8100C Power

27. LAN Port:100M

28. IDE RAID ITE8212

29. USB Connector

30. FWH

31. Power/MISC Connectors

32. PCI Slot 1,2

33. PCI Slot 3

34. Super I/O_IT8712F

36. Keyboard / Mouse / Fan

37. Serial / Parallel

38. AUDIO AC97 655

39. AUDIO PORT 655

40. VGA Connector

41. GPIO / IRQ / IDSEL Map

42. Jumper Setting / Option Table

43. Modify List

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Index Page

Index Page

Index Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

915M12

915M12

915M12

1

143Friday, June 17, 2005

143Friday, June 17, 2005

143Friday, June 17, 2005

CC

CC

CC

of

of

of

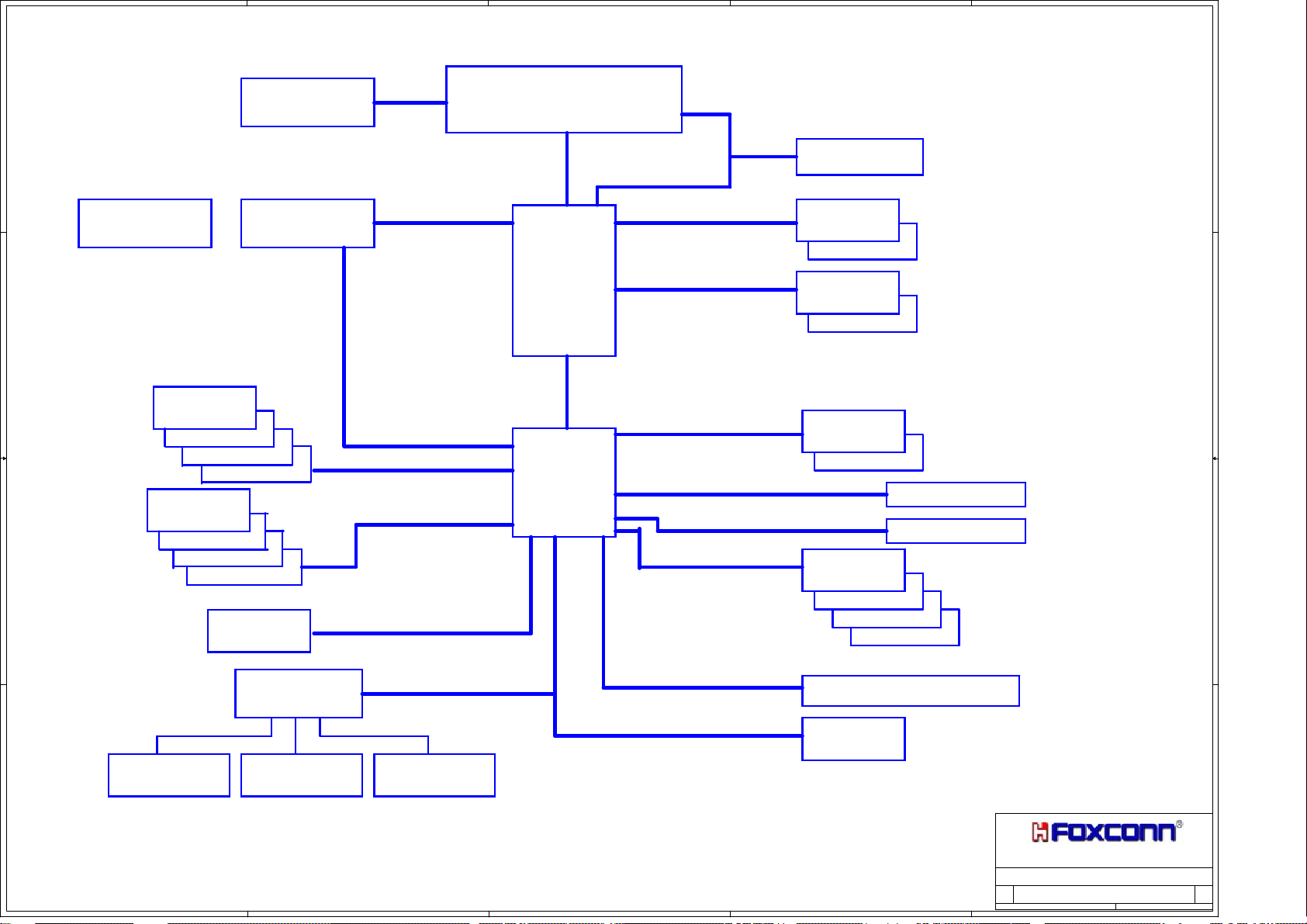

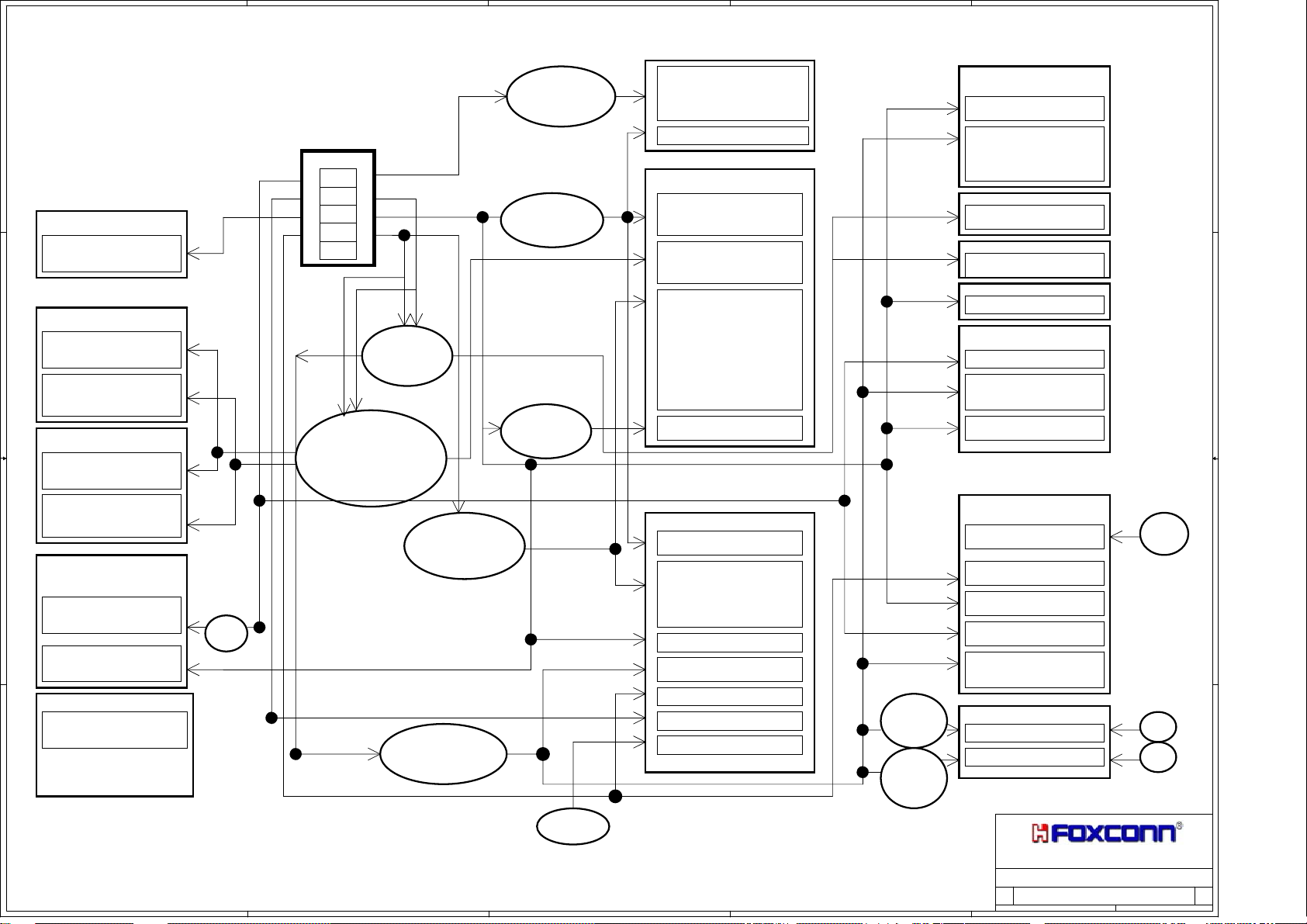

Page 3

5

VRD 10.1

D D

3 Phase PWM

4

Prescott, Tejas

3

2

1

- LGA775 processor

Socket T

Intel SDVO Card

PCI Express x 16

External Graphics

or

PCI Express x16 Port

800/533 FSB

DDR I 333/400

CK-410 Clock

DIMM1

Card

DIMM2

GMCH

GrantsDale

DDR2 400/533

DIMM1

DIMM2

C C

4 Lanes

Back Panel

USB2.0 Port 1

USB2.0 Port 2

PCI Express x4 Port

USB2.0 Port 3

USB2.0 Port 4

Front Panel

USB2.0 Port 5

USB2.0 Port 6

USB2.0 Port 7

B B

USB2.0 Port 8

ATA100

IDE CONN 1

Direct Media Interface (DMI)

ICH6

PCI Interface

PCI Interface

PCI Interface

uATX Form Factor

PCI Slot 1

PCI Slot 2,3

Serial ATA

SATA Connector 1

SATA Connector 2

SATA Connector 3

SATA Connector 4

LAN

REALTEK 8100C

IDE CONTRLOR

ITE 8212

Super I/O

IT 8712F

LPC I/F

AC 97 2.3

Realtek ALC655

Firmware HUB

4Mb

PS2

Keyboard / Mouse

A A

5

Parallel

Serial

4

Floppy

Drive Connector

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Topology

Topology

Topology

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

FOXCONN PCEG

915M12

915M12

915M12

1

243Friday, June 17, 2005

243Friday, June 17, 2005

243Friday, June 17, 2005

CC

CC

CC

of

of

of

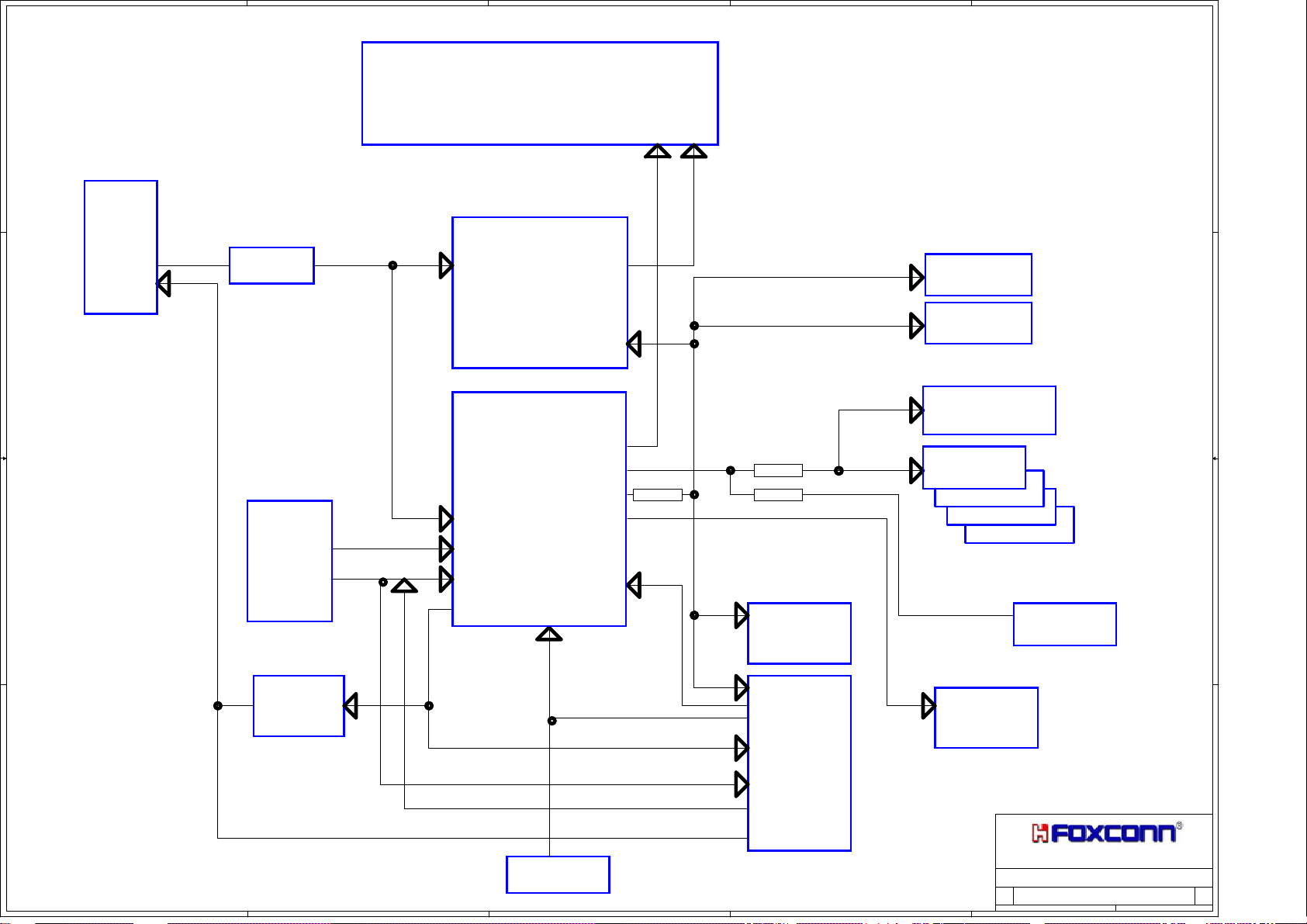

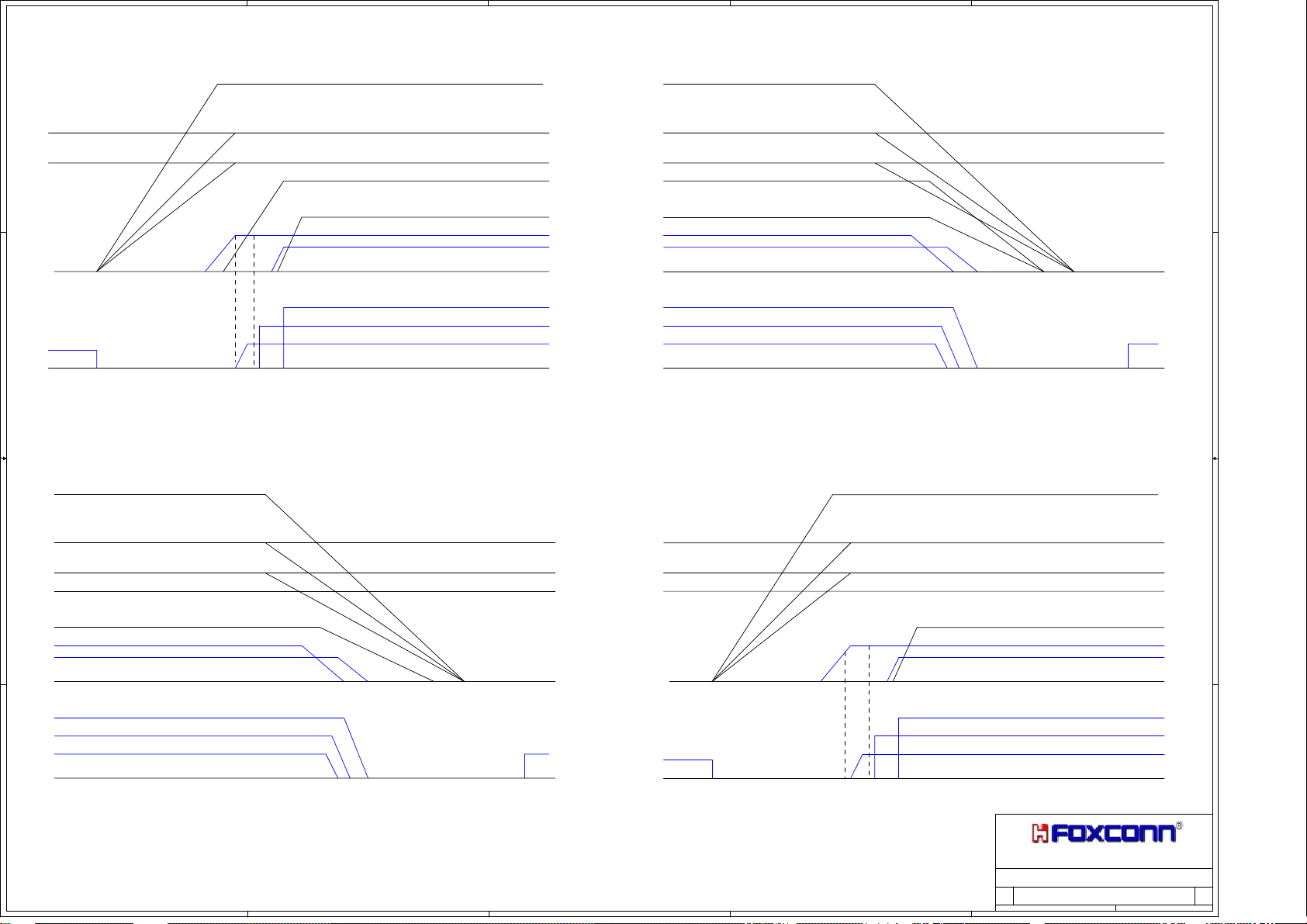

Page 4

5

4

3

2

1

CPU (Tejas / Prescott)

D D

ATX

Power

PWRGD_PS PWROK

PS_ON#

C C

Translation

Circuitry

PWRGD_3V

Front Panel

FR_RST

B B

SW_ON

LGA775 processor

CPURST#

GMCH

GrantsDale

RSTIN#

ICH6

ICH_PWRGD

PCIRST#

PLTRST#

PWROK

SYS_RESET#

PWRBTN#

SLP_S3#

AC_RST#

RCIN#

RSMRST#

CPU_PWRGD

Buffer

CPURST#

Buffer

Buffer

RST#

FWH

PCI Express x16

PCI Express x4

LRESET#

uATX Form Factor

RST#

TPM

PCI Slot 1

PCI Slot 2

LAN

ITE 8212

ATA100

IDE CONN 1

Power on/off

circuit

KBRST

RSMRST#

Super IO

RST#

Audio

PSIN

PANSWH#

RST#

A A

PWRON#

PSON#

FOXCONN PCEG

FOXCONN PCEG

Title

Title

RSMRST circuit

5

4

3

2

Title

Reset Map

Reset Map

Reset Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

915M12

915M12

915M12

1

343Friday, June 17, 2005

343Friday, June 17, 2005

343Friday, June 17, 2005

CC

CC

CC

of

of

of

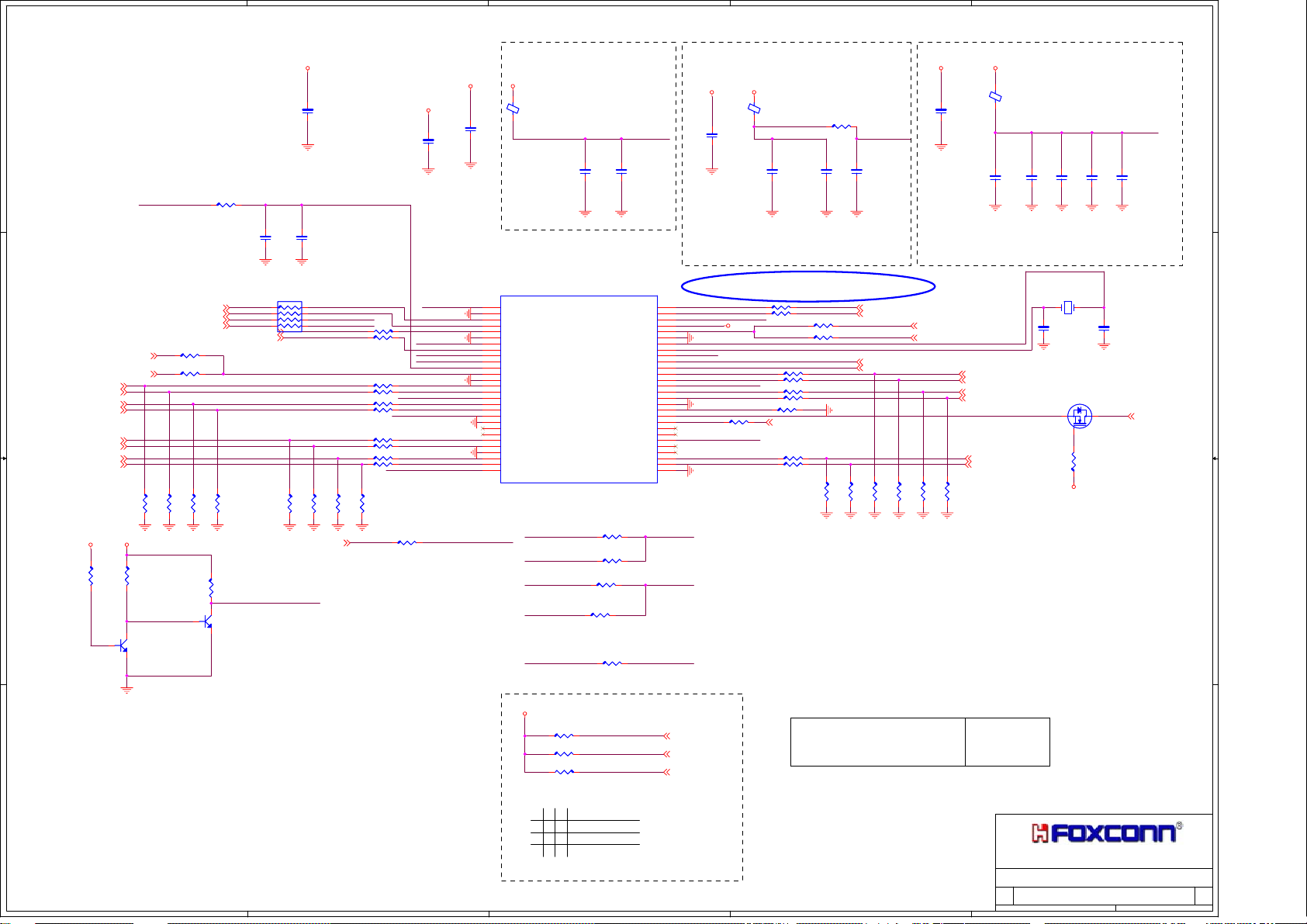

Page 5

5

14.318MHz

4

3

2

1

CPU

D D

CPU 133/200 MHz Diff Pair

MCH 133/200 MHz Diff Pair

PCI Express 100 MHz Diff Pair

PCI Express 100 MHz Diff Pair

DOT 96 MHz Diff Pair

PCI Express x4

PCI Express x16 Gfx

GMCH

GrantsDale

DDR1

DIMM1

DIMM2

915

910

C C

CK-410

PCI Express/DMI 100 MHz Diff Pair

PCI Express/DMI 100 MHz Diff Pair

USB/SIO 48 MHz

ICH 33 MHz

REF 14 MHz

DDRII

DIMM1

DIMM2

ICH6

LAN 33 MHz

FWH 33 MHz

B B

LAN

ITE 8212

AC97/HDA Bit Clock

25MHz

PCI 33 MHz

PCI 33 MHz

PCI 33 MHz

PCI Slot 1

PCI Slot 2

PCI Slot 3

32.768KHz

AC'97

Super I/O

SIO 33 MHz

SATA 100 MHz Diff Pair

24.576MHz

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

CLOCK Distribution

CLOCK Distribution

CLOCK Distribution

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

915M12

915M12

915M12

1

443Friday, June 17, 2005

443Friday, June 17, 2005

443Friday, June 17, 2005

CC

CC

CC

of

of

of

Page 6

5

4

3

2

1

Proceessor

VRD 10.1

Switching

D D

Three Phase

Vccp (CPU Vcore)

Voltage=0.8375~1.6V

Icc(Max)=119A (2004

Performance FMB B)

1.2V FSB

Vtt-tbdA

ATX P/S

12V

CK 410

Vdd (Core)

3.3V

Ivdd(Max)=560mA

5VSB

3.3V

5V

-12V

Linear 3.3V

to 1.2V

5A

DDR Channel A

Vdd (Core)

C C

2.6V

Ivdd(Max)=3A(per channel)

Vtt (Core)

1.3V

Ivterm(Max)=900mA

(per channel)

Single Phase Switch

DDR Channel B

Vdd (Core)

2.6V

Ivdd(Max)=3A(per channel)

Vtt (Core)

1.3V

Ivterm(Max)=900mA

(per channel)

AC'97 2.3/

B B

5V to 2.6V

Ivdd(Max)=11.5A

Ivdd(Max)=500mA(S3)

LDO

2.6V to 1.3V

Ivterm(Max)=1.8A

5VDUAL

Icc(Max)=

4.345A(S0,S1)

22mA(S3)

V_1p5_core

1.5V

Switching=12A

2.5V DAC

regulator

V_2p5_DAC

100mA

Azalia Codec

Vcc

5V

Icc(Max)=48mA

Vcc

3.3V

Icc(Max)=20mA

LDO

12V to 5V

1394(chip)

3.3VSB

Icc(Max)=156mA(S0)

Icc(Max)=0.8mA(suspend)

1394 2 ports

A A

5

LDO

5V_dual to 3.3SB

Icc(Max)=1.5A

4

RTC

Battery

3

Grantsdale GMCH

FSB_Vtt

1.2V FSB Vtt

Icc(Max)=1.2A

2.6V DDR1 I/O=5.5A(S0,S1)

2.6V DDR1 I/O=250mA(S3)

Vcore (Core Logic)

1.5V

Icc(Max)=9.6A(Integrated)

Icc(Max)=7.5A(Discrete)

*1.5V

PCIexpress(X16)=1A

*1.5V

PCIexpress(X1)=0.06A

*1.5V SDVO=tbdA

*1.5V DMI=0.25A

*2.5V DAC=0.07A

2.5V HV=tbdA

ICH6

1.2V VCC_CPU-tbdmA

1.5V Core=1.88A

*1.5V PCI Express=270mA

*1.5V DMI=290mA

1.5V SATA=430mA

3.3V=180mA

3.3V VccSus

Icc(Max)=330mA

5VRef=tbduA

5VrefSus=tbduA

RTC=5uA

*Power derived through filter

2

1.0V

Lan Core

V_1p0_ctrl

1.8V

Lan Phy

V_1p8_ctrl

Super I/O

3.3V

Icc(Max)=50mA

3.3SBV

Icc(Max)=50mA(S0)

3.3SBV

Icc(Max)=38mA(S3)

USB 8 Ports

+5V DUAL=4A(S0, S1)

+5V DUAL=20mA(S3)

PS2

+5V DUAL=345mA(S0, S1)

+5V DUAL=2mA(S3)

FWH

3.3V=107mA(S0, S1)

PCI Express

X16 slot (1)

+12V=4.4A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

+3.3V=3A

PCI Per Slot (3)

-12V

Icc(Max)=0.1A

5V

Icc(Max)=5A

3.3V

Icc(Max)=7.6A

12V

Icc(Max)=0.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

Northway

+1.0=tbdA

+1.8V=tbdA

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Power Delivery Map

Power Delivery Map

Power Delivery Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

915M12

915M12

915M12

1

LDO

LDO

543Friday, June 17, 2005

543Friday, June 17, 2005

543Friday, June 17, 2005

-12V

CC

CC

CC

of

of

of

Page 7

5

4

3

2

1

S5->S0

D D

+5V_DUAL

+3D3V_DUAL

+12V_SYS

+5V_SYS

+3D3V_SYS

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

1ms to 10ms

Vcc_PWRGD

VRM_OUTEN

C C

PS_ONJ

S0->S3

+12V_SYS

VIDPWRGD

S0->S5

+12V_SYS

+5V_SYS

+3D3V_SYS

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

S3->S0

+5V_DUAL

+3D3V_DUAL

PS_ONJ

+12V_SYS

+5V_SYS

B B

+3D3V_SYS

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

A A

5

4

+5V_DUAL

+3D3V_DUAL

+2D6V_STR

PS_ONJ

+5V_DUAL

+3D3V_DUAL

+2D6V_STR

+5V_SYS

+3D3V_SYS

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

1ms to 10ms

Vcc_PWRGD

VRM_OUTEN

PS_ONJ

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

VIDPWRGD

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

915M12

915M12

915M12

1

643Friday, June 17, 2005

643Friday, June 17, 2005

643Friday, June 17, 2005

CC

CC

CC

of

of

of

Page 8

5

4

3

2

1

BC4

BC4

0.1uF

0.1uF

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

CK_200M_P_GMCH 14

CK_200M_N_GMCH 14

CK_200M_P_CPU 12

CK_200M_N_CPU 12

CK_PE_100M_P_ICH 22

CK_PE_100M_N_ICH 22

R42

R42

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

3D3V_SYS

FB1

FB1

FB L0805 300 Ohm

FB L0805 300 Ohm

2 1

+/-25%

+/-25%

0805

0805

BC12

BC12

4.7uF

4.7uF

*

*

C1206

C1206

reserved

reserved

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

high frequency decoupling caps. placed one 10nF cap.

per power pin

*

*

BC8

BC8

10nF

10nF

*

*

C0603

C0603

reserved

reserved

50V, X7R, +/-10%

50V, X7R, +/-10%

1 2

BC18

BC18

33pF

33pF

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

C0603

C0603

VDD_CPU/VDD_SRC FilterVDD_PCI/VDD_REF Filter

3D3V_CLK_CPU_SRC

BC13

BC13

10nF

10nF

*

*

C0603

C0603

50V, X7R, +/-10%

50V, X7R, +/-10%

X1

X1

XTAL-14.318MHz

XTAL-14.318MHz

+/-30PPM

+/-30PPM

X2O

X2O

G

R43

R43

4.7K

4.7K

*

*

+/-5%

+/-5%

R0603

R0603

5V_SYS

BC14

BC14

10nF

10nF

C0603

C0603

reserved

reserved

50V, X7R, +/-10%

50V, X7R, +/-10%

*

*

Q1 2N7002

Q1 2N7002

DS

BC15

BC15

10nF

10nF

*

*

C0603

C0603

50V, X7R, +/-10%

50V, X7R, +/-10%

BC19

BC19

33pF

33pF

50V, NPO, +/-5%

50V, NPO, +/-5%

C0603

C0603

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

SOT23_GSD

SOT23_GSD

ICH_SYS_RSTJ 12,22,31

3D3V_SYS

3D3V_SYS3D3V_SYS

BC1

BC1

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

VDD_48 Filter

BC16

BC16

4.7uF

4.7uF

*

*

C1206

C1206

reserved

reserved

C0603

reserved

reserved

BC17

BC17

10nF

10nF

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

this cap. placed

close to power pin

D D

3D3V_CLK_PCI 3D3V_CLK_48

R2

R0805

R2

R0805

2.2 +/-5%

2.2 +/-5%

*

*

*

*

Near Pin53

3D3V_SB

*

*

BC55

BC55

0.1uF

0.1uF

C0603

C0603

Reserved

Reserved

FB2

FB2

FB L0805 300 Ohm

BC2

BC2

0.1uF

0.1uF

*

*

C0603

C0603

dummy

dummy

FB L0805 300 Ohm

+/-25%

+/-25%

2 1

0805

0805

3D3V_CLK_CPU_SRC 3D3V_CLK_REF

BC10

BC10

BC9

BC9

10nF

10nF

4.7uF

4.7uF

*

*

*

*

C1206

C1206

reserved

reserved

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

3D3V_SYS 3D3V_SYS

2 1

BC3

BC3

0.1uF

0.1uF

*

*

C0603

C0603

BC5

BC5

4.7uF

4.7uF

C1206

C1206

*

*

reserved

reserved

FB3

FB3

FB L0805 300 Ohm

FB L0805 300 Ohm

+/-25%

+/-25%

R1

R1

0805

0805

2.2

2.2

*

3D3V_CLK_PCI

*

BC11

BC11

10nF

10nF

*

*

*

*

C0603

C0603

50V, X7R, +/-10%

placed each 10nF cap. per power pin

50V, X7R, +/-10%

+/-5%R0805

+/-5%R0805

BC7

BC7

10nF

10nF

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

3D3V_SYS

*

*

dummy

dummy

9/8 Reserved for 1394 debug.

RN133 8P4R0603+/-5%*RN133 8P4R0603+/-5%

1

2

*

3

CK_33M_PCI232

CK_33M_SIO34

CK_33M_ICH24

R11

R11

R0603

C C

CK_PE_100M_P_16PORT21

CK_PE_100M_N_16PORT21

CK_PE_100M_P_GMCH14

CK_PE_100M_N_GMCH14

CK_SATA_100M_P_ICH23

CK_SATA_100M_N_ICH23

CK_48M_SIO34

CK_48M_ICH22

CK_96M_P_GMCH14

CK_96M_N_GMCH14

R0603

*

*

R12

R12

*

*

R29

R29

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

R31

R31

R30

R30

*

*

*

*

49.9

49.9

49.9

49.9

+/-1%

+/-1%

+/-1%

+/-1%

R0603

R0603

R0603

R0603

TURBO1J34

CK_33M_PCI333

22+/-5%

22+/-5%

22

22

+/-5%R0603

+/-5%R0603

R32

R32

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

3D3V_SYSVCCP

R48

R48

R47

R47

*

*

*

B B

*

330

330

dummy

dummy

10K

10K

dummy

dummy

Q3

Q3

B

MMBT3904

MMBT3904

dummy

dummy

E C

R49

R49

1K

1K

*

*

dummy

dummy

CLK_VTT_PWRGDJ

Q2

Q2

B

MMBT3904

MMBT3904

SOT23_BEC

SOT23_BEC

E C

dummy

dummy

4

5

6

33M_ICH 33M_PCI2

7 8

R33

R33

*

*

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

VRD_PWRD8

R7 0

R7 0

R9 33+/-5% R0603

R9 33+/-5% R0603

R14 33+/-5% R0603

R14 33+/-5% R0603

R16 33+/-5% R0603

R16 33+/-5% R0603

R18 33+/-5% R0603

R18 33+/-5% R0603

R20 33+/-5% R0603

R20 33+/-5% R0603

R24 33+/-5% R0603

R24 33+/-5% R0603

R23 33+/-5% R0603

R23 33+/-5% R0603

R26 33+/-5% R0603

R26 33+/-5% R0603

R27 33+/-5% R0603

R27 33+/-5% R0603

R35

R35

R34

R34

*

*

49.9

49.9

49.9

49.9

+/-1%

+/-1%

+/-1%

+/-1%

R0603

R0603

R0603

R0603

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

R36

R36

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

R44 33

R44 33

*

*

*

*

3D3V_CLK_PCI

33M_SIO

33M_ICH

FS1-CV115-24

96M_DOT_P

96M_DOT_N

CLK_VTT_PWRGDJ

PE_100M_P_16PORT

PE_100M_N_16PORT

3D3V_CLK_CPU_SRC

PE_100M_P_GMCH

PE_100M_N_GMCH

SATA_100M_P_ICH

SATA_100M_N_ICH

3D3V_CLK_CPU_SRC

CLK_VTT_PWRGDJ

+/-5%R0603

+/-5%R0603

U1

1

VDD_PCI

2

VSS_PCI

3

PCI2

4

PCI3

5

PCI4/Turbo1

6

VSS_PCI

7

VDD_PCI

8

PCIF_0/ITP_EN

9

PCIF

10

PCIF2

11

VDD_48

12

FS_B/48MHZ

13

VSS_48

14

DOTT_96MHz

15

DOTC_96MHz

16

(VTT_PwrGd/PD#)

17

SRC_1

18

SRC_1#

19

VDDSRC

20

VSS

21

SRC_2

22

SRC_2#

23

SRC_3

24

SRC_3#

25

VSS_GND

26

SATA

27

SATA#

28

VDD_SRC

IDTCV115-2U1IDTCV115-2

FS_A/(REF1/PCI5)

CPU_2_ITP/ SRC_7

CPU_2_ITP#/ SRC_7#

SMBus Address :1101-0010

FS2-CV115-24 FSBSEL2

FS2-CV115

FS1-CV115

R45 2.2K

R45 2.2K

*

*

R46 2.2K

R46 2.2K

*

*

R50 2.2K

R50 2.2K

+/-5%

+/-5%

*

*

R51 2.2K

R51 2.2K

+/-5%

+/-5%

*

*

R52 2.2K

R52 2.2K

*

*

VDD_suspend

FS_C/REF0

VSS_REF

XTAL_OUT

VDD_REF

VDD_CPU

VSS_CPU

VDD_SRC

VSS_SRC

R0603

R0603

+/-5%

+/-5%

R0603

R0603

+/-5%

+/-5%

R0603

R0603

R0603

R0603

dummy

dummy

+/-5%

+/-5%

PCI_1

PCI_0

XTAL_IN

CPU_0

CPU_0#

CPU_1

CPU_1#

IREF

RESET#

Turbo2

SRC_6

SRC_6#

SRC_5

SRC_5#

dummy

dummy

R0603

R0603

33M_LAN3D3V_CLK_PCI

R4 33 +/-5%R0603

56

55

54

53

FS2-CV115-24

52

51

50

49

3D3V_CLK_REF

48

47

SCL

46

SDA

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

FSBSEL1FS1-CV115-24

FSBSEL0FS0

R4 33 +/-5%R0603

33M_FWH

R6 33 +/-5%R0603

R6 33 +/-5%R0603

FS033M_SIO

3D3V_SB

200M_P_GMCH

200M_N_GMCH

3D3V_CLK_CPU_SRC

200M_P_CPU

200M_N_CPU

CLK_IREF

FS1-CV115

FS2-CV115

R22 0 +/-5%

R22 0 +/-5%

*

*

3D3V_CLK_CPU_SRC

PE_100M_P_ICH

PE_100M_N_ICH

R13 33 +/-5%R0603

R13 33 +/-5%R0603

R15 33 +/-5%R0603

R15 33 +/-5%R0603

R17 33 +/-5%R0603

R17 33 +/-5%R0603

R19 33 +/-5%R0603

R19 33 +/-5%R0603

R21 475 +/-1%R0603

R21 475 +/-1%R0603

R0603

R0603

R28 33 +/-5%R0603

R28 33 +/-5%R0603

R25 33 +/-5%R0603

R25 33 +/-5%R0603

*

*

*

*

R8 22 +/-5%R0603

R8 22 +/-5%R0603

*

*

R10 22 +/-5%R0603

R10 22 +/-5%R0603

*

*

*

*

*

*

*

*

*

*

*

*

TURBO2J 34

*

*

*

*

*

*

R37

R37

49.9

49.9

+/-1%

+/-1%

R0603

R0603

R38

R38

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

CK_33M_LAN 25CK_33M_PCI132

CK_33M_FWH 30

SMB_CLK_MAIN 18,19,36

SMB_DATA_MAIN 18,19,36

*

*

R39

R39

49.9

49.9

+/-1%

+/-1%

R0603

R0603

R40

R40

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

CK_14M_AUDIO 38

CK_14M_ICH 22

*

*

R41

R41

49.9

49.9

+/-1%

+/-1%

R0603

R0603

FSB_VTT

R53 470

R53 470

*

*

R54 470

R54 470

*

*

*

*

+/-5% R0603

+/-5% R0603

A A

5

4

BSEL TABLE

210

000

001

010

FSB Frequency

266

133MHz(533)

200MHz(800)

FSBSEL0

+/-5%R0603

+/-5%R0603

FSBSEL1

+/-5%R0603

+/-5%R0603

FSBSEL2

R55470

R55470

3

FSBSEL0 12,14

FSBSEL1 12,14

FSBSEL2 12,14

FSB800 / 1066 CPU FSBSEL0 = 0

FSB533 CPU FSBSEL0 = 1

2

BS0 BS1

0 1 200

1 0 133

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

CK410 ClockGen

CK410 ClockGen

CK410 ClockGen

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

915M12

915M12

915M12

1

743Friday, June 17, 2005

743Friday, June 17, 2005

743Friday, June 17, 2005

CC

CC

CC

of

of

of

Page 9

5

4

3

2

1

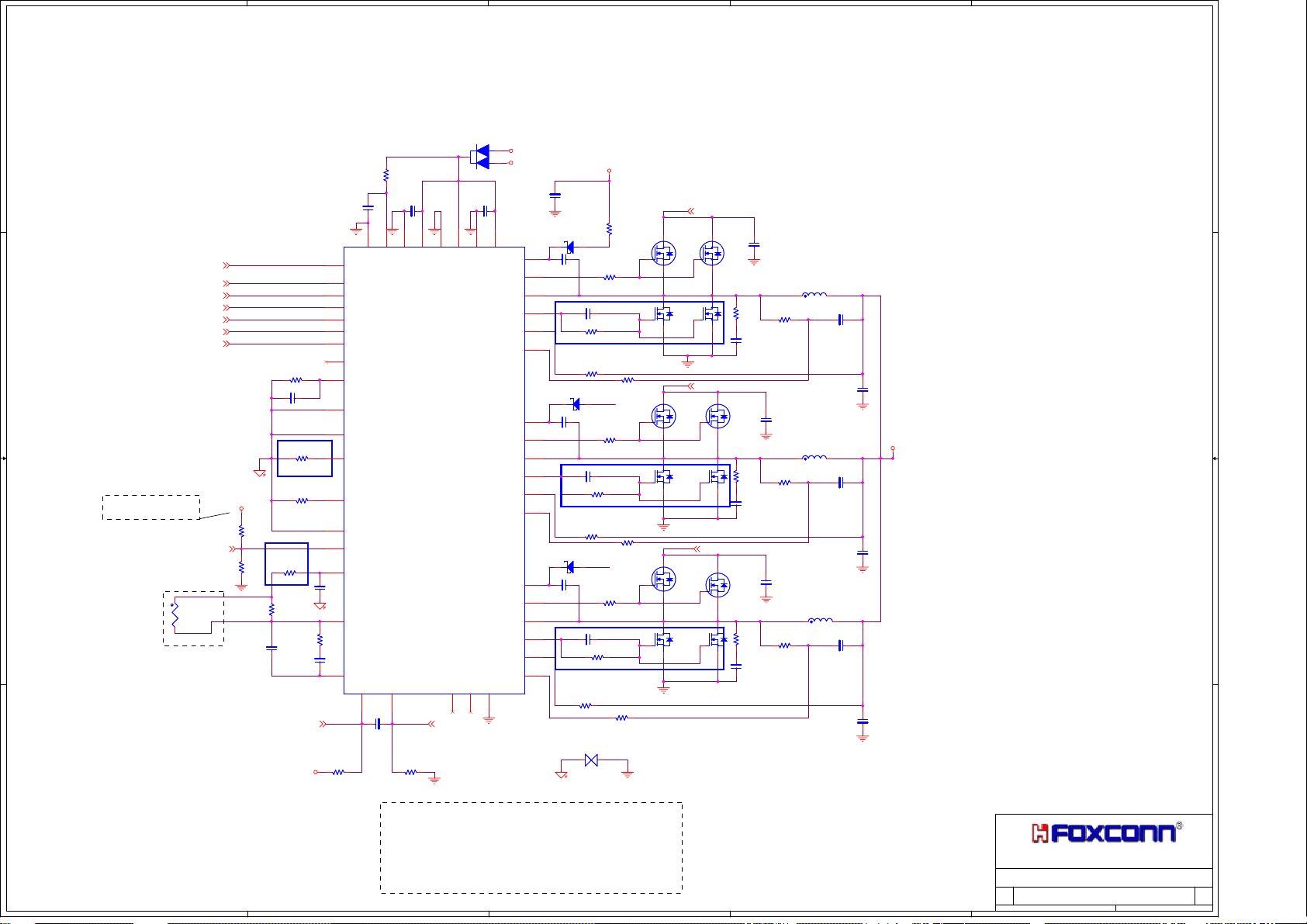

PWM Controller and Driver schematics

D D

D2

12V_VRM

2

3

1

R56

R56

*

*

10

10

+/-5%

+/-5%

R0805

R0805

BC21

BC21

BC20

BC20

1uF

1uF

1uF

1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

C0805

C0805

5

4

U2

U2

VRM_EN

VRM_EN9,12

VID_OUT0

VID_OUT034

VID_OUT1

VID_OUT134

VID_OUT2

VID_OUT234

VID_OUT3

VID_OUT334

VID_OUT4

VID_OUT434

VID_OUT5

C C

Select pull high

voltage by chipset

B B

A A

20050524 A.1 update !

Place close to MOSFET

VID_OUT534

20050524 A.1 update !

3D3V_SYS

*

*

VRD_PWRD7

*

*

RT2

RT2

T

T

100K

100K

+/-1%

+/-1%

R0603

R0603

Dummy

Dummy

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

100K

100K

BC29

BC29

10nF 25V, X7R, +/-10%

10nF 25V, X7R, +/-10%

R66 120K

R66 120K

R71

R71

8.2K

8.2K

+/-5%

+/-5%

R0603

R0603

R74

R74

8.2K

8.2K

+/-5%

+/-5%

R0603

R0603

Dummy

Dummy

50V, X7R, +/-10%

50V, X7R, +/-10%

R489

R489

*

*

0

0

+/-5%

+/-5%

R0603

R0603

BC40

BC40

47pF

47pF

*

*

C0603

C0603

R62

R62

R67

R67

150K

150K

R75

R75

*

*

C0603

C0603

Dummy

Dummy

*

*

*

*

C0603

C0603

R0603

R0603

Dummy

Dummy

+/-1%

+/-1%

*

*

R0603+/-1%

R0603+/-1%

R0603

R0603

*

*

+/-1%

+/-1%

R0603

R0603

5.11K

+/-1%

5.11K

+/-1%

*

*

18K

18K

+/-1%*R77

+/-1%

R0603

R0603

*

*

VCCP

13

24

25

26

27

28

23

29

9

20

21

6

22

31

30

10

BC37470pF

BC37470pF

8

*

R77

BC43

BC43

4.7nF

4.7nF

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

7

R82

R82

*

*

0

0

R0603

R0603

+/-5%

+/-5%

Dummy

Dummy

OUTEN

VID0

VID1

VID2

VID3

VID4

VID5

VID_SEL

OVP

TC

CS_SEL

OFFSET

OSC/FAULT

SGND

SS_END

VSEN

FB

COMP

35

VCC

SGND

PGND3

L6711TR

L6711TR

FBR

FBG

11

12

BC45

BC45

*

*

0.1uF

0.1uF

C0603

C0603

R84

R84

*

*

0

0

R0603

R0603

+/-5%

+/-5%

Dummy

Dummy

This module schematics design base

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

41

38

39

PGND2

VCCDR2

VCCDR3

NC484849

VSS_SENSE 12VCC_SENSE12

BAT54CD2BAT54C

BC22

BC22

1uF

1uF

C0805

C0805

3

NC37

37

5V_SB_SYS

*

*

*

*

1

BOOT1

PGND1

VCCDR1

UGATE1

PHASE1

LGATE1

BOOT2

UGATE2

PHASE2

LGATE2

BOOT3

UGATE3

PHASE3

LGATE3

49

CS1+

CS2+

CS3+

2 1

BC24 0.1uF

BC24 0.1uF

45

46

47

2

14

CS1-

15

BC31 0.1uF

BC31 0.1uF

44

43

42

40

16

CS2-

17

2 1

BC38 0.1uF

BC38 0.1uF

34

33

32

36

18

CS3-

19

12V_VRM

BC23

BC23

1uF

1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

R57

D3

1N4148WD31N4148W

25V, Y5V, +80%/-20%C0603

25V, Y5V, +80%/-20%C0603

*

*

C0603 25V, X7R, +/-10%

C0603 25V, X7R, +/-10%

Dummy

Dummy

R63 3K +/-1%

R63 3K +/-1%

D4

1N4148WD41N4148W

2 1

25V, Y5V, +80%/-20%C0603

25V, Y5V, +80%/-20%C0603

*

*

C0603 25V, X7R, +/-10%

C0603 25V, X7R, +/-10%

Dummy

Dummy

R72 3K +/-1%

R72 3K +/-1%

D5

1N4148WD51N4148W

25V, Y5V, +80%/-20%C0603

25V, Y5V, +80%/-20%C0603

*

*

C0603 25V, X7R, +/-10%

C0603 25V, X7R, +/-10%

Dummy

Dummy

R81 3K R0603+/-1%

R81 3K R0603+/-1%

JS1 SHORTJS1 SHORT

*

*

VBOOT

R58 2.2

R58 2.2

*

*

R0805 +/-5%

R0805 +/-5%

BC2647nF

BC2647nF

*

*

R61

R61

2.2

2.2

*

*

+/-5%

+/-5%

R0805

R0805

*

*

VBOOT

R65 2.2

R65 2.2

*

*

R0805 +/-5%

R0805 +/-5%

BC3347nF

BC3347nF

*

*

R68

R68

2.2

2.2

*

*

+/-5%

+/-5%

R0805

R0805

*

*

VBOOT

R76 2.2

R76 2.2

*

*

R0805 +/-5%

R0805 +/-5%

BC4147nF

BC4147nF

*

*

R78

R78

2.2

2.2

*

*

+/-5%

+/-5%

R0805

R0805

*

*

12

R57

2.2

2.2

R0805

R0805

+/-5%

+/-5%

1.2K

1.2K

R0603

R0603

+/-1%

+/-1%

R64

R64

1.2K

1.2K

R0603

R0603

+/-1%

+/-1%

R73

R73

1.2K

1.2K

R0603

R0603

+/-1%

+/-1%

*

*

phase1

*

*

*

*

R83

R83

phase2

phase3

12V_VIN

12V_VIN 9

BC25

Q4

AOD436Q4AOD436

AOD438Q6AOD438

Q8

AOD436Q8AOD436

AOD438

AOD438

Q12

Q12

AOD436

AOD436

AOD438

AOD438

G

Q6

G

12V_VIN 9

G

Q11

Q11

G

G

Q14

Q14

G

DS

DS

12V_VIN 9

DS

G

DS

G

12V_VIN

DS

G

DS

G

12V_VIN

DS

G

DS

G

Q5

Q5

AOD436

AOD436

reserved

reserved

AOD438Q7AOD438

DS

DS

DS

DS

R59

R59

2.2

2.2

R0805

R0805

*

*

Q7

+/-5%

+/-5%

BC28

BC28

1.5nF

1.5nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

Q9

Q9

AOD436

AOD436

reserved

reserved

R69

R69

2.2

2.2

R0805

R0805

*

*

+/-5%

+/-5%

Q10

Q10

AOD438

AOD438

BC35

BC35

1.5nF

1.5nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

Q13

Q13

AOD436

AOD436

reserved

reserved

R79

R79

2.2

2.2

R0805

R0805

*

*

Q15

Q15

+/-5%

+/-5%

AOD438

AOD438

BC44

BC44

1.5nF

1.5nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

BC25

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

R60 1.8K

R60 1.8K

*

*

R0603+/-1%

R0603+/-1%

BC32

BC32

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

R70 1.8K

R70 1.8K

*

*

R0603+/-1%

R0603+/-1%

BC39

BC39

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

R80

R80

1.8K

1.8K

*

*

R0603+/-1%

R0603+/-1%

L1

L1

*

*

0.6uH

0.6uH

BC27 0.33uF

BC27 0.33uF

16V, X7R, +/-10%

16V, X7R, +/-10%

L2

L2

*

*

0.6uH

0.6uH

BC34 0.33uF

BC34 0.33uF

16V, X7R, +/-10%

16V, X7R, +/-10%

L3

L3

*

*

0.6uH

0.6uH

BC42 0.33uF

BC42 0.33uF

16V, X7R, +/-10%

16V, X7R, +/-10%

0.33uF

0.33uF

C0805

C0805

Dummy

Dummy

0.33uF

0.33uF

C0805

C0805

Dummy

Dummy

0.33uF

0.33uF

C0805

C0805

Dummy

Dummy

BC30

BC30

BC36

BC36

BC46

BC46

16V, X7R, +/-10%C0805

16V, X7R, +/-10%C0805

*

*

*

*

VCCP

16V, X7R, +/-10%C0805

16V, X7R, +/-10%C0805

*

*

*

*

16V, X7R, +/-10%C0805

16V, X7R, +/-10%C0805

*

*

*

*

on Intel P4 platform that use

socket 775 package. Support Intel

04B spec.

Title

Title

Title

VRM PWM and Driver Controller

VRM PWM and Driver Controller

VRM PWM and Driver Controller

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

915M12

915M12

915M12

1

843Friday, June 17, 2005

843Friday, June 17, 2005

843Friday, June 17, 2005

A

A

A

of

of

of

Page 10

5

4

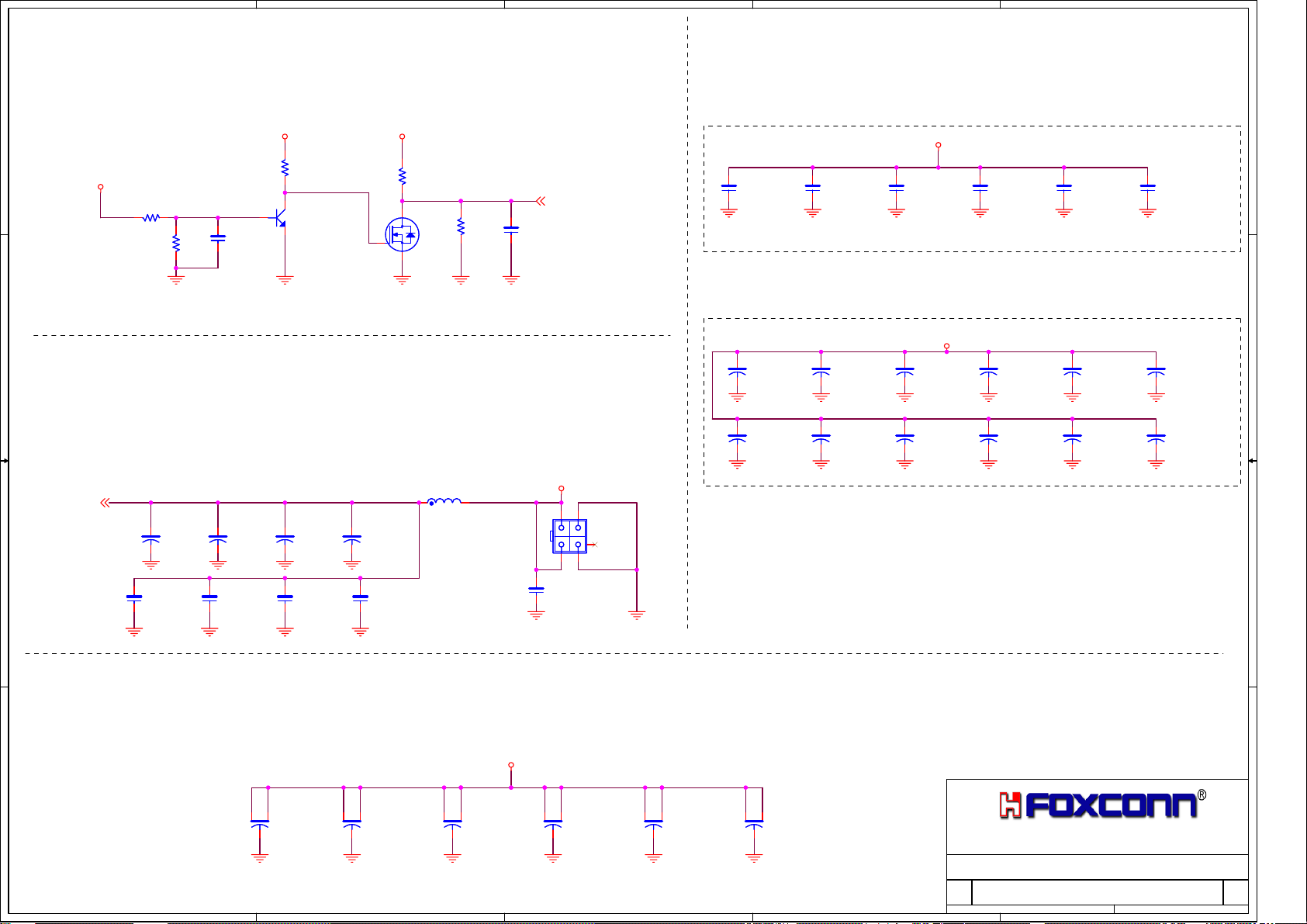

PWM Controller Enable schematics

3

2

1

D D

R85

R85

*

*

10K

10K

+/-5%

B

Dummy

Dummy

+/-5%

R0603

R0603

Dummy

Dummy

Q16

Q16

MMBT3904

MMBT3904

SOT23_BEC

SOT23_BEC

E C

VTT_OUT_RIGHT

R86

R86

*

*

4.7K

4.7K

*

*

R0603

R0603

+/-5%

+/-5%

Dummy

Dummy

C C

R88

R88

22.1K

22.1K

+/-1%

+/-1%

R0603

R0603

Dummy

Dummy

BC52

BC52

1uF

1uF

*

*

C0805

C0805

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

VRM Input LC schematics

12V_VIN8

B B

12V_VIN

*

*

BC96

BC96

12

10uF

10uF

*

*

16V, X5R, +/-10%

16V, X5R, +/-10%

C1206H10

C1206H10

Dummy

Dummy

EC11

EC11

1500uF

1500uF

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

*

*

EC12

EC12

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

BC100

BC100

12

10uF

10uF

16V, X5R, +/-10%

16V, X5R, +/-10%

C1206H10

C1206H10

Dummy

Dummy

EC13

EC13

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

BC109

BC109

12

10uF

10uF

*

*

16V, X5R, +/-10%

16V, X5R, +/-10%

C1206H10

C1206H10

Dummy

Dummy

*

*

G

EC14

EC14

1500uF

1500uF

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

BC111

BC111

12

10uF

10uF

*

*

16V, X5R, +/-10%

16V, X5R, +/-10%

C1206H10

C1206H10

Dummy

Dummy

12V_VRM5V_SB_SYS

*

*

DS

Dummy

Dummy

Dummy

Dummy

L4

L4

R87

R87

10K

10K

+/-5%

+/-5%

R0603

R0603

Q17

Q17

2N7002

2N7002

*

*

Choke Coil 1.2uH

Choke Coil 1.2uH

*

*

Dummy

Dummy

R89

R89

4.7K

4.7K

+/-5%

+/-5%

R0603

R0603

VRM_EN

BC54

BC54

1nF

1nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

Dummy

Dummy

VRM_EN 8,12

12V_VRM

3

4

BC525

BC525

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

PWR2

PWR2

1

ATX12V_P1_2X2

ATX12V_P1_2X2

PWR4NWP1

PWR4NWP1

5

2

BC47

BC47

10uF

10uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

EC1

EC1

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

EC7

EC7

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

BC53

BC53

10uF

10uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

*

*

*

*

VRM Output MLCC

VCCP

BC48

BC48

10uF

10uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

place in socket

VCCP

EC2

EC2

560uF

560uF

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

EC8

EC8

560uF

560uF

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

EC3

EC3

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

EC9

EC9

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

BC49

BC49

10uF

10uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

EC4

EC4

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

EC10

EC10

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

BC50

BC50

10uF

10uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

EC5

EC5

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

TC1

TC1

100uF

100uF

*

*

2V, +/-20%

2V, +/-20%

ctdh16

ctdh16

reserved

reserved

BC51

BC51

10uF

10uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

EC6

EC6

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H200

CE35D80H200

Dummy

Dummy

TC2

TC2

100uF

100uF

*

*

2V, +/-20%

2V, +/-20%

ctdh16

ctdh16

Dummy

Dummy

VRM Output filter schematics

VCCP

A A

5

EC15

EC15

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

EC16

EC16

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

EC19

**

**

3

EC19

3300uF

3300uF

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

EC20

EC20

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

VRM Input and Output

VRM Input and Output

VRM Input and Output

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

915M12

915M12

915M12

943Friday, June 17, 2005

943Friday, June 17, 2005

943Friday, June 17, 2005

of

of

1

of

A

A

A

EC18

EC17

EC17

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

4

EC18

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

Page 11

5

4

3

2

1

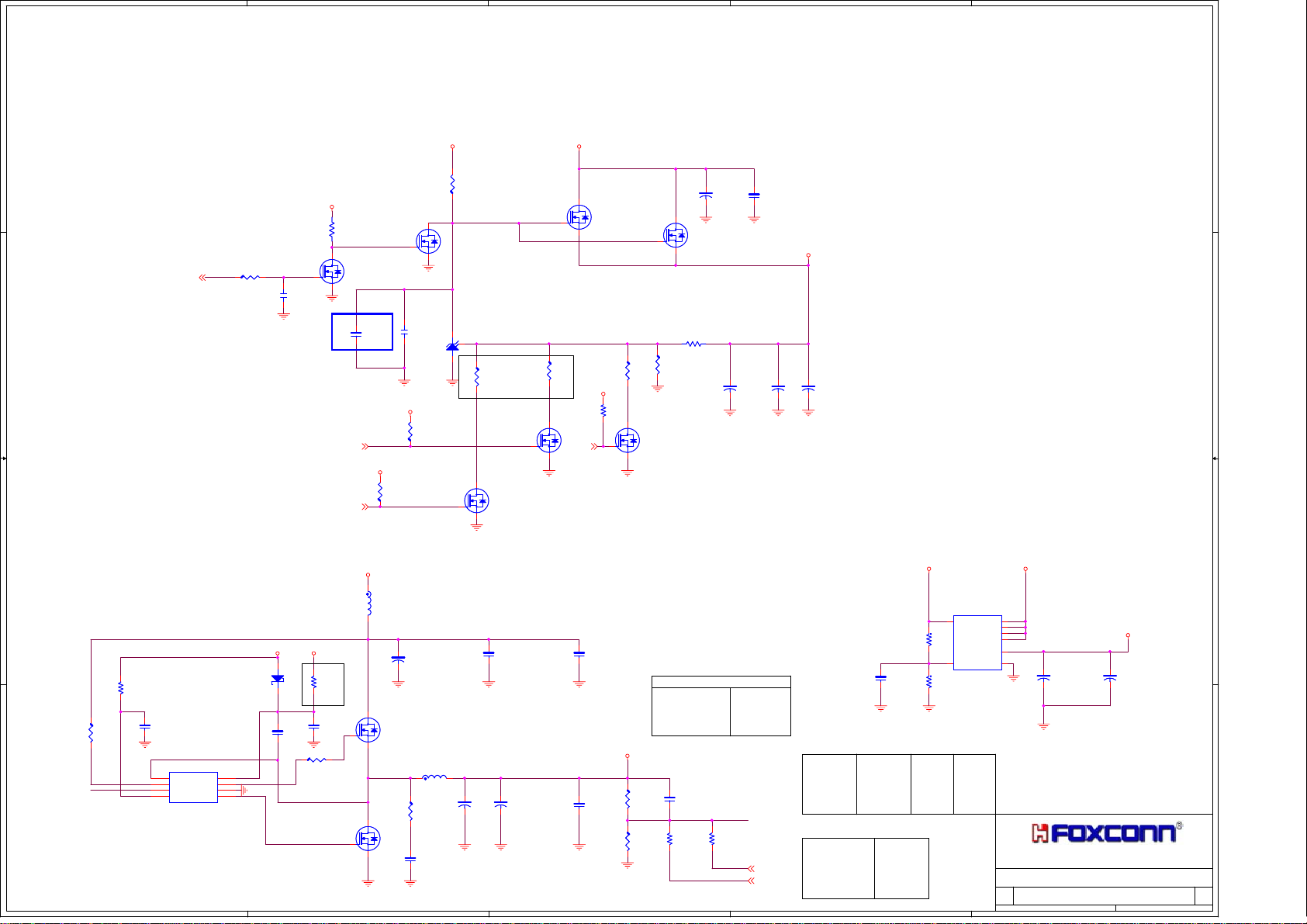

MEM_VDD

MEM_STR

D D

5V_DUAL 3D3V_DUAL

R546

R546

1K

1K

+/-5%

+/-5%

*

*

R0603

DS

R582

R582

1K

1K

+/-5%

+/-5%

*

*

R0603

R0603

dummy

dummy

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

SOT23_GSD

SOT23_GSD

R0603

DRV_2.6V

Q54

Q54

U32

U32

1

AP432N

AP432N

3 2

+

R578

R578

*

*

1.25V

200

200

-

+/-1%

+/-1%

R0603

R0603

dummy

dummy

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

SOT23_GSD

SOT23_GSD

dummy

dummy

DS

Q582N7002

Q582N7002

dummy

dummy

G

5V_DUAL

R547

R547

10K

10K

R0603

R0603

+/-5%

+/-5%

2N7002

2N7002

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

BC113

BC113

4.7uF

4.7uF

C0805

C0805

dummy

dummy

3D3V_DUAL

SOT23_GSD

SOT23_GSD

3D3V_DUAL

R583

R583

1K

1K

+/-5%

+/-5%

*

*

R0603

R0603

dummy

dummy

G

12

BC596

BC596

0.1uF

0.1uF

C0603

C0603

1 2

UNNAMED_45_CAP_I193_A

BC595

BC595

4.7uF

4.7uF

C1206

C1206

DS

Q552N7002

Q552N7002

G

*

*

GPIO_DDR_122

GPIO_DDR_222

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

SOT23_GSD

SOT23_GSD

R548

R548

SLP_S4J22

C C

SLP_S4J

100K

100K

*

*

12

Q19

Q19

AP9916H

AP9916H

TO263_252

TO263_252

25m Ohm@Vgs=4.5V

25m Ohm@Vgs=4.5V

*

*

DS

Q572N7002

Q572N7002

G

G

R579

R579

200

200

+/-1%

+/-1%

R0603

R0603

dummy

dummy

DDR2_DETECT

DS

14,15,18,19

25m Ohm@Vgs=4.5V

25m Ohm@Vgs=4.5V

5V_DUAL

R581

R581

*

*

1K

1K

+/-5%

+/-5%

R0603

R0603

Q56

Q56

G

*

*

DS

Q20

Q20

AP9916H

AP9916H

TO263_252

TO263_252

G

*

*

R550

R550

180

180

+/-1%

+/-1%

R0603

R0603

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

SOT23_GSD

SOT23_GSD

2N7002

2N7002

R551

R551

280

280

+/-1%

+/-1%

R0603

R0603

*

*

DS

R549

R0603

R549

R0603

1 2

130

+/-1%

130

+/-1%

EC21

EC21

1000uF

1000uF

CE35D80H125

CE35D80H125

CE35D80H200

CE35D80H200

20050618

R550 change to 169ohm!

BC56

BC56

0.1uF

0.1uF

*

*

2D6V_STR

EC27

EC27

EC26

*

*

CE35D80H200

CE35D80H200

EC26

1500uF

1500uF

1500uF

1500uF

*

*

CE35D80H200

CE35D80H200

EC25

EC25

*

*

1500uF

1500uF

dummy

dummy

20050524 A.1 update !

3D3V_SYS2D6V_STR

8

VCNTL

7

VCNTL

6

VCNTL

5

VCNTL

4

VOUT

2

GND

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

EC23

EC23

100uF

100uF

*

*

16V, +/-20%

16V, +/-20%

CE20D50H110

CE20D50H110

DUMMY

DUMMY

DDR1 2.6V/1.3V 5VDUAL

DDR1 2.6V/1.3V 5VDUAL

DDR1 2.6V/1.3V 5VDUAL

VTT_DDR

EC24

EC24

1000uF

1000uF

*

*

6.3V, +/-20%

6.3V, +/-20%

CE35D80H125

CE35D80H125

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

915M12

915M12

915M12

1

10 43Saturday, June 18, 2005

10 43Saturday, June 18, 2005

10 43Saturday, June 18, 2005

CC

CC

CC

of

of

of

R109

R109

10

10

+/-5%

+/-5%

R0805

R0805

BC69

BC69

1uF

1uF

+/-5%

+/-5%

R0805

R0805

5V_SYS

12

*

*

L5

L5

Choke Coil 0.9uH

Choke Coil 0.9uH

BC63

BC62

*

*

BC62

*

*

0.1uF

0.1uF

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

dummy

dummy

EC29

EC29

1000uF

1000uF

*

*

6.3V, +/-20%

6.3V, +/-20%

CE35D80H125

CE35D80H125

reserved

reserved

EC30

EC30

1000uF

1000uF

6.3V, +/-20%

6.3V, +/-20%

CE35D80H125

CE35D80H125

reserved

reserved

EC28

EC28

1000uF

1000uF

*

*

6.3V, +/-20%

6.3V, +/-20%

CE35D80H125

CE35D80H125

DS

Q21

Q21

G

NTD60N02R

NTD60N02R

L6

L6

*

*

1.4uH

1.4uH

*

*

R103 2.2

R103 2.2

+/-5%

Q22

Q22

NTD80N02

NTD80N02

+/-5%

R0603

R0603

BC68

BC68

4.7nF

4.7nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

DS

G

4

BC63

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

Dummy

Dummy

BC66

BC66

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

3

1D5V_CORE

R104

R104

*

*

100

100

+/-1%

+/-1%

R0603

R0603

R105

R105

*

*

110

110

+/-1%

+/-1%

R0603

R0603

R476

R476

*

*

1K

1K

+/-1%

+/-1%

R0603

R0603

Dummy

Dummy

V_1D5V_2

V_1D5V_1

ICH6

GPIO20

GPIO28

GPIO24

GPIO_1D5V_1 GPIO19

GPIO_1D5V_2

GPIO_DDR_1

GPIO_DDR_2

1= HIGH 0= LOW

BC67

BC67

10nF

10nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

1D5V_FB

R475

R475

*

*

2.2K

2.2K

+/-1%

+/-1%

R0603

R0603

Dummy

Dummy

GPIO_1D5V_2 22

GPIO_1D5V_1 22

BC59

BC59

1uF

1uF

*

*

C0805

C0805

GPIO_DDR_1 GPIO_DDR_2

11

0

10

00

1= HIGH 0= LOW

GPIO_1D5V_1 GPIO_1D5V_2

1.5V

1.55V

1.6V

1.65V

1

11

01

10

00

2

R95

R95

10K

10K

+/-1%

+/-1%

R0603

R0603

R97

R97

10K

10K

+/-1%

+/-1%

R0603

R0603

DDR(2.6V)

2.70V

2.67V

2.63V 1.85V

2.6V 1.8V

U4

1

VIN

3

REFEN

RT9173U4RT9173

DDR(1.8V)

1.93V

1.9V

B B

12V_SYS

5V_SYS

D6

D6

*

R100

R100

*

*

10

10

+/-5%

+/-5%

R0805

R0805

BC64

BC64

Dummy

Dummy

1uF

1D5V_FB

5

1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

25V, Y5V, +80%/-20%C0603

25V, Y5V, +80%/-20%C0603

U5

U5

BOOT

UGATE

GND

LGATE

RT9202

RT9202

SOP8JA

SOP8JA

1

2

3

4

8

PHASE

7

OCSET

6

FB

5

VCC

R101

R101

*

*

10K

10K

+/-1%

+/-1%

R0603

R0603

A A

SD103AW

SD103AW

2 1

Dummy

Dummy

*

*

Dummy

Dummy

BC65

BC65

0.1uF

0.1uF

R102 0

R102 0

*

Reserved

Reserved

*

*

*

*

Page 12

5

3D3V_SB

4

3

2

1

D D

BC108

BC108

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

dummy

dummy

C0603

C0603

C C

B B

2.5V

5V_DUAL 3D3V_SB

BC75

BC75

1uF

1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

dummy

dummy

Vout=Vref(1+R2/R1)+IadjR2

R1 is Up Resistor.

Iadj=50uA

Vref=1.25V

When Stuff D11

Change R187 from 324 +/-1% Ohm to 62 +/-1% Ohm

Q23

Q23

2N7002

2N7002

Dummy

Dummy

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

R107

R107

*

U7

U7

VIN3VOUT

Adjust

AMS1085

AMS1085

1

TO252_123

TO252_123

*

*

*

845

845

+/-1%

+/-1%

R0603

R0603

R110

R110

487

487

+/-1%

+/-1%

R0603

R0603

1.2V

R108

R108

*

*

1.02K

1.02K

+/-1%

+/-1%

R0603

R0603

Dummy

Dummy

BC71

BC71

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

dummy

dummy

2

R114

R114

*

*

301

301

+/-1%

+/-1%

R0603

R0603

*

*

R116

R116

*

*

499

499

+/-1%

+/-1%

R0603

R0603

DS

G

GTLREF_SEL 13

9/10 for P4 EE function need.

12V_SYS

84

3

+

+

2

-

-

-12V_SYS

output current 1.5A

EC34

EC34

470uF

470uF

16V, +/-20%

16V, +/-20%

CE35D80H200

CE35D80H200

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

G

1

U6A

U6A

LM358M

LM358M

SOP8JA

SOP8JA

FOR EMI ISSUE USB6,USB7 TRANSFER LAYER

BC77

BC77

0.1uF

0.1uF

C0603

C0603

dummy

dummy

3D3V_SYS

*

*

*

*

R111

R111

1K

1K

+/-5%

+/-5%

R0603

R0603

**

**

1D5V_CORE

DS

Q25

Q25

AP9916H

AP9916H

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

EC33

EC33

3300uF

3300uF

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

BC72

BC72

4.7uF

4.7uF

*

*

BC70

BC70

0.1uF

0.1uF

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

FSB_VTT

*

*

*

*

*

*

BC73

BC73

0.1uF

0.1uF

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

EC31

EC31

1000uF

1000uF

6.3V, +/-20%

6.3V, +/-20%

CE35D80H125

CE35D80H125

reserved

reserved

3D3V_SB 3D3V_SYS

3D3V_SB

*

*

R113

R113

*

*

150

150

+/-1%

+/-1%

R0603

R0603

R115

R115

+/-1%

+/-1%

475

475

R0603

R0603

D7

D7

1

BAT54C

BAT54C

SOT23_123

SOT23_123

BC74

BC74

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

dummy

dummy

3

*

*

3D3V_SB3D3V_DUAL

2

12V_SYS

placed near the LM358M pin 8

BC76

BC76

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

2D5V_MCH1D5V_CORE

BC78

BC78

1uF

1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

12V_SYS

5

+

+

6

-

-

-12V_SYS

3D3V_SB

R117

R117

1K

1K

R0603

R0603

+/-5%

+/-5%

DS

Q27

Q27

2N7002

2N7002

G

SOT23_GSD

SOT23_GSD

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

2D5V_MCH

*

*

BC79

BC79

4.7uF

4.7uF

*

*

C1206

C1206

dummy

dummy

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

84

7

U6B

U6B

LM358M

LM358M

SOP8JA

SOP8JA

5V_DUAL

for 3D3V_SB / Front panel USB

5V_SB_SYS5V_SYS

AO4600

AO4600

1

8

S2G2S1G1

S2G2S1G1

2

7

3

6

45

D1 D1 D2 D2

D1 D1 D2 D2

Q53

Q53

A A

EC35

EC35

1000uF

1000uF

*

*

6.3V, +/-20%

6.3V, +/-20%

CE35D80H125

CE35D80H125

5

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

PWOK+

Q30

Q30

2N7002

2N7002

SOT23_GSD

SOT23_GSD

12V_SYS

R118

R118

*

*

1K

1K

+/-5%

+/-5%

R0603

R0603

PWOK+ 29,36

DS

G

7.5 Ohm Vgs=5V

7.5 Ohm Vgs=5V

4

PWOKJ

SOT23_GSD

SOT23_GSD

2N7002

2N7002

Q31

Q31

5V_SB_SYS

R119

R119

1K

1K

+/-5%

+/-5%

*

*

R0603

R0603

DS

G

PWRG_ATX

PWRG_ATX 31,34

5V level

3

1A

1A

PWOK+

PWOK+

PWOK+

PWOK+

3D3V_SYS3D3V_SB

200 mils

200 mils

Q28

Q28

1

S2 G2 S1 G1

S2 G2 S1 G1

2

3

4 5

AO4600

AO4600

Q32

Q32

1

S2 G2 S1 G1

S2 G2 S1 G1

2

3

4 5

AO4600

AO4600

reserved

reserved

8

7

6

D1D1D2D2

D1D1D2D2

8

7

6

D1D1D2D2

D1D1D2D2

2

D8

D8

2 1

B120

B120

dummy

dummy

5A

200 mils

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

DDR1 2.6V/1.3V 5VDUAL

DDR1 2.6V/1.3V 5VDUAL

DDR1 2.6V/1.3V 5VDUAL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

915M12

915M12

915M12

1

11 43Friday, June 17, 2005

11 43Friday, June 17, 2005

11 43Friday, June 17, 2005

of

of

of

CC

CC

CC

Page 13

5

HDJ[63..0]

2 OF 7

2 OF 7

U8B

HDJ0

HDJ1

HDJ2

HDJ3

HDJ4

D D

C C

B B

A A

HDJ5

HDJ6

HDJ7

HDJ8

HDJ9

HDJ10

HDJ11

HDJ12

HDJ13

HDJ14

HDJ15

HDBIJ014

HDSTBNJ014

HDSTBPJ014

HDJ16

HDJ17

HDJ18

HDJ19

HDJ20

HDJ21

HDJ22

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

HDJ30

HDJ31

HDBIJ114

HDSTBNJ114

HDSTBPJ114

VTT_OUT_LEFT

R241 62

R241 62

VTT_OUT_LEFT

R126 100

R126 100

R128 100

R128 100

15 mils width, 7 mils spacing

max. 1200 mils

R254 60.4

R254 60.4

HCOMP0

R135 60.4

R135 60.4

HCOMP1

R136 60.4

R136 60.4

HCOMP2

R260 60.4

R260 60.4

HCOMP3

R255 60.4

R255 60.4

15 mils width, 7 mils spacing

max. 1200 mils

VTT_OUT_LEFT

R139 62

R139 62

FSB_VTT

R146 62

R146 62

R149 62

R149 62

U8B

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

D15#

HDBIJ0

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

HDBIJ1 HDBIJ3

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1#

CPU Prescott_Socket_LGA775_Rev1.0

CPU Prescott_Socket_LGA775_Rev1.0

CPU_LGA775

CPU_LGA775

Place at CPU end of route

Place at CPU end of route

RN80

RN80

1

2

*

*

3

4

5

6

7 8

62 8P4R0603

62 8P4R0603

+/-5%

+/-5%

RN2

RN2

1

2

*

*

3

4

5

6

7 8

62 8P4R0603

62 8P4R0603

+/-5%

+/-5%

*

*

dummy

dummy

+/-1%R0603

+/-1%R0603

*

*

dummy

dummy

+/-1%R0603

+/-1%R0603

*

*

*

*

*

*

*

*

*

*

*

*

+/-5%R0603

+/-5%R0603

*

*

dummy

dummy

+/-5%R0603

+/-5%R0603

*

*

+/-5%R0603

+/-5%R0603

*

*

5

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

CPU_PWRG

TESTHI_1

TESTHI_11

TESTHI_12

HBR0J

TESTHI_8

TESTHI_9

TESTHI_10

TESTHI_13

+/-5%R0603

+/-5%R0603

HCOMP2

HCOMP3

HCOMP4

+/-1%R0603

+/-1%R0603

+/-1%R0603

+/-1%R0603

+/-1%R0603

+/-1%R0603

+/-1%R0603

+/-1%R0603

+/-1%R0603

+/-1%R0603

RSVD_G6

TESTHI_0

TESTHI_2_7

HDJ32

G16

HDJ33

E15

HDJ34

E16

HDJ35

G18

HDJ36

G17

HDJ37

F17

HDJ38

F18

HDJ39

E18

HDJ40

E19

HDJ41

F20

HDJ42

E21

HDJ43

F21

HDJ44

G21

HDJ45

E22

HDJ46

D22

HDJ47

G22

HDBIJ2

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

HDBIJ2 14

HDSTBNJ2 14

HDSTBPJ2 14

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

HDJ62

HDJ63

HDBIJ3 14

HDSTBNJ3 14

HDSTBPJ3 14

VTT_OUT_RIGHT

1

*

*

3

5

7 8

Place BPM termination near CPU

VTT_OUT_RIGHT

R140 62

R140 62

R144 1K

R144 1K

R147 62

R147 62

R150 62

R150 62

R130

R130

*

*

56 R0603 +/-5%

56 R0603 +/-5%

R131

R131

*

*

56 R0603+/-5%

56 R0603+/-5%

RN3

RN3

2

4

6

56

56

*

*

Place at CPU end of route

*

*

*

*

*

*

*

*

HBPM5J

HBPM4J

+/-5%

+/-5%

8P4R0603

8P4R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

+/-5%R0603

dummy

dummy

+/-5%R0603

+/-5%R0603

dummy

dummy

+/-5%R0603

+/-5%R0603

R242

R242

130

130

+/-5%

+/-5%

R0603

R0603

HBPM3J

HBPM2J

HBPM1J

HBPM0J

4

HDJ[63..0] 14

HAJ[31..3]14

HBPM5J

HBPM4J

HBPM3J

HBPM2J

HBPM1J

HBPM0J

HCPURSTJ

CPU_BOOT

RSVD_AK6

HIERRJ

PROCHOTJ

4

HAJ[31..3]

3

HAJ[31..3]

HAJ[31..3]14

U8A

U8A

HAJ3

L5

A03#

HAJ4

P6

A04#

HAJ5

M5

A05#

HAJ6

L4

A06#

HAJ7

M4

A07#

HAJ8

R4

A08#

HAJ9

T5

A09#

HAJ10

U6

A10#

HAJ11

T4

A11#

HAJ12

U5

A12#

HAJ13

U4

A13#

HAJ14

V5

A14#

HAJ15

V4

A15#

HAJ16

W5

A16#

N4

RSVD1

HREQJ[4..0]14

HADSTBJ014

HPCREQJ14

HAJ17

HAJ18

HAJ19

HAJ20

HAJ21

HAJ22

HAJ24

HAJ25

HAJ26

HAJ27

HAJ28

HAJ29

HAJ30

HAJ31

TP_LAG775_PIN_AH4

TP15TP15

TP_LAG775_PIN_AH5

TP16TP16

TP_LAG775_PIN_AJ5

TP21TP21

TP_LAG775_PIN_AJ6

TP20TP20

HADSTBJ114

R129

R129

*

*

56

56

+/-5%

+/-5%

R0603

R0603

VTT_OUT_LEFT

R141

R141

*

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

R148

R148

*

*

100

100

+/-1%

+/-1%

R0603

R0603

*

*

135

P5

HREQJ0

HREQJ1

HREQJ2

HREQJ3

HREQJ4

642

GTLREF voltage should be 0.67*FSB_VTT

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin

caps should be placed near CPU pin

*

*

RSVD2

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

G5

PCREQ#

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

AC4

RSVD3

AE4

RSVD4

AD5

ADSTB1#

CPU Prescott_Socket_LGA775_Rev1.0

CPU Prescott_Socket_LGA775_Rev1.0

CPU_LGA775

CPU_LGA775

RN81

RN81

56

56

8P4R0603

8P4R0603

+/-5%

+/-5%

7 8

HTDO

HTDI

place TCK/TDI/TMS terminations near CPU within 1.5 inch

place TRSTJ termination anywhere on route

BC82

BC82

1uF

1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

*

*

Dummy

Dummy

3

D2

ADS#

C2

BNR#

D4

HIT#

H4

RSP#

G8

BPRI#

B2

DBSY#

C1

DRDY#

E4

HITM#

AB2

IERR#

P3

INIT#

C3

LOCK#

E3

TRDY#

AD3

BINIT#

G7

DEFER#

F2

EDRDY#

AB3

MCERR#

U2

AP0#

U3

AP1#

F3

BR0#

G3

TESTHI08

G4

TESTHI09

H5

TESTHI10

J16

DP0#

H15

DP1#

H16

DP2#

J17

DP3#

H1

GTLREF

RESET#

*

*

HTMS

HTCK

HTRSTJ

BC83

BC83

220pF

220pF

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

new land name: GTLREF0

G23

B3

RS0#

F5

RS1#

A3

RS2#

1 OF 7

1 OF 7

VTT_OUT_RIGHT

BC81

BC81

0.1uF

0.1uF

*

*

C0603

C0603

place TDO termination near XDP connector

HGTLREF

TP_RSPJ

HIERRJ

TP_BINITJ

TP_MCERRJ

TP_APJ0

TP_APJ1

HBR0J

TESTHI_8

TESTHI_9

TESTHI_10

TP_DPJ0

TP_DPJ1

TP_DPJ2

TP_DPJ3

HGTLREFHAJ23

BC80

BC80

0.1uF

0.1uF

C0603

C0603

HADSJ 14

HBNRJ 14

HITJ 14

TP1TP1

HBPRIJ 14

HDBSYJ 14

HDRDYJ 14

HITMJ 14

INITJ 22

HLOCKJ 14

HTRDYJ 14

TP2TP2

HDEFERJ 14

HEDRDYJ 14

TP6TP6

TP7TP7

TP8TP8

HBR0J 14

TP9TP9

TP10TP10

TP4TP4

TP11TP11

HCPURSTJ 14

HRSJ0 14

HRSJ1 14

HRSJ2 14

HBPM0J

HBPM1J

HBPM2J

HBPM3J

HBPM4J

HBPM5J

ICH_SYS_RSTJ7,22,31

FSBSEL07,14

R584 DUMMY

R584 DUMMY

FSBSEL17,14

FSBSEL27,14

TO support FSB1066 , R584 must dummy

20050608

VTT_OUT_RIGHT

2

HVCCIOPLL13

VID_IN034

VID_IN134

VID_IN234

VID_IN334

VID_IN434

VID_IN534

CK_200M_P_CPU7

CK_200M_N_CPU7

10 mils width, 10 mils spacing

VCC_SENSE8

VSS_SENSE8

HTCK

AE1

HTDI

AD1

HTDO

AF1

HTMS

AC1

HTRSTJ

AG1

HBPM0J

AJ2

HBPM1J

AJ1

HBPM2J

AD2

HBPM3J

AG2

HBPM4J

AF2

HBPM5J

AG3

ICH_SYS_RSTJ

AC2

AK3

AJ3

FSBSEL0

G29

H30

*

*

FSBSEL2

G30

RN4

RN4

1

2

*

*

3

4

5

6

7 8

1K

1K

+/-5%

+/-5%

R142

R142

8P4R0603

8P4R0603

*

*

R145

R145

1K R0603+/-5%

1K R0603+/-5%

*

*

1K R0603+/-5%

1K R0603+/-5%

2

SMIJ22

A20MJ22

FERRJ22

INTR22

NMI22

IGNNEJ22

STPCLKJ22

HVCCA13

HVSSA13

TP_VCCPLL

TP5TP5

VID_IN0

VID_IN1

VID_IN2

VID_IN3

VID_IN4

VID_IN5

TP_VID6

TP3TP3

new land name

TP50TP50

THERMDA35

THERMDC35

U8D

U8D

4 OF 7

4 OF 7

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLKOUT0

ITPCLKOUT1

BSEL0

BSEL1

BSEL2

CPU Prescott_Socket_LGA775_Rev1.0

CPU Prescott_Socket_LGA775_Rev1.0

CPU_LGA775

CPU_LGA775

VID_IN0

VID_IN1

VID_IN2

VID_IN3

VID_IN4

VID_IN5

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTTPWRGD

VTT_OUT1

VTT_OUT2

VTT_SEL

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

1

3 OF 7

3 OF 7

U8C

U8C

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

D23

RSVD5

C23

VCCIOPLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

RSVD6

F28

BCLK0

G28

BCLK1

AE8

SKTOCC#

AL1

THERMDA

AK1

THERMDC

AN3

VCCSENSE

AN4

VSSSENSE

AN5

VCC_MB_REG

AN6

VSS_MB_REG

Changed pin name

Changed pin name

from RSV

from RSV

F29

RSVD9

CPU Prescott_Socket_LGA775_Rev1.0

CPU Prescott_Socket_LGA775_Rev1.0

CPU_LGA775

CPU_LGA775

TPEV_VCCFUSEPRG

TPEV_VIDFUSEPRG

CPU_PWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

PWRGOOD

PROCHOT#

THERMTRIP#

BOOTSELECT

new land name

new land name

3D3V_SYS

R137

R137

*

*

1K

1K

+/-5%

+/-5%

R0603

R0603

dummy

dummy

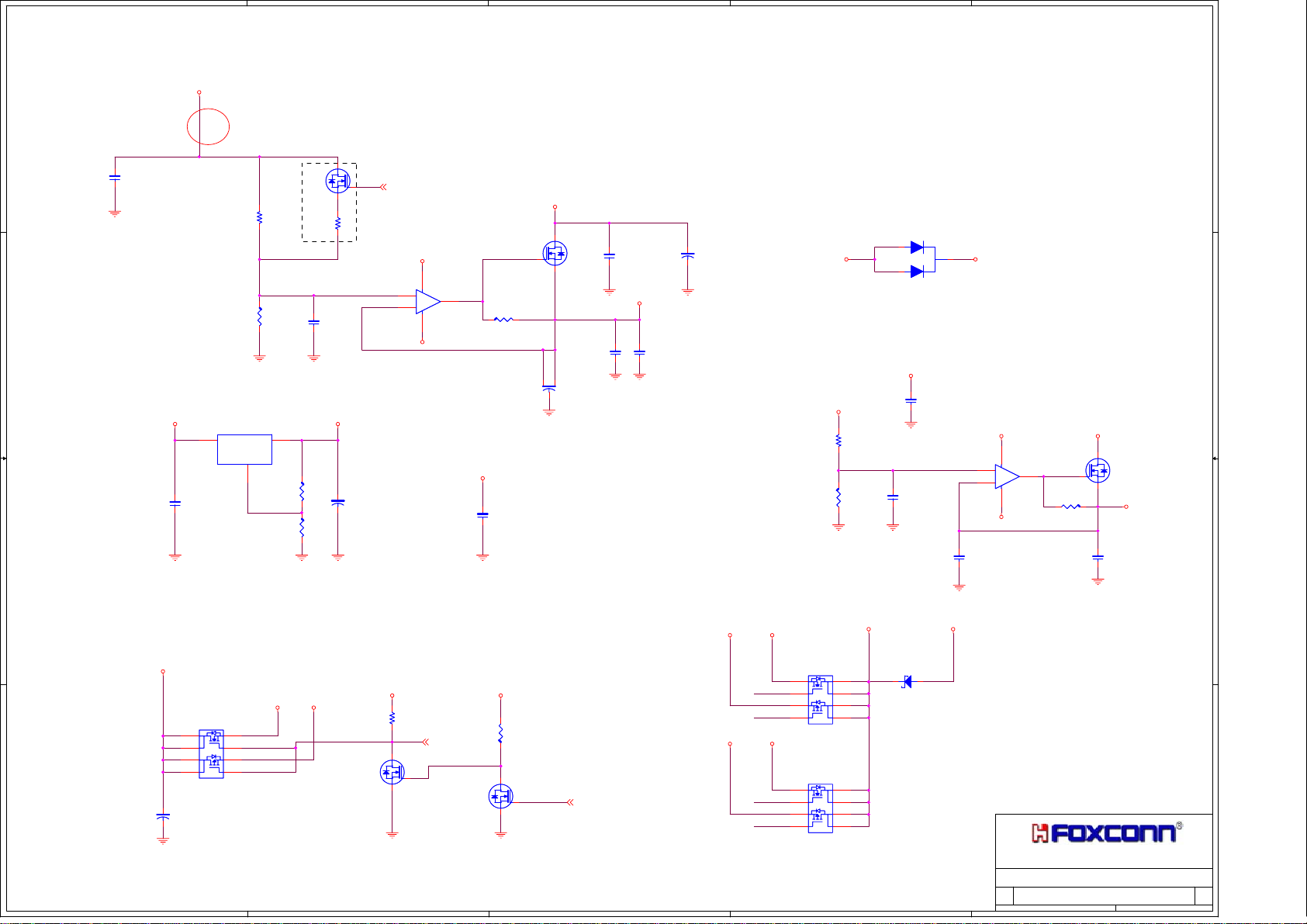

Title

Title

Title

LGA775 -1

LGA775 -1

LGA775 -1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

TESTHI_0

F26

TESTHI_1

W3

TESTHI_11

P1

TESTHI_12

W2

F25

G25

G27

G26

G24

F24

AK6

RSVD10

G6

RSVD11

TESTHI_13

L2

SLP#

AH2

RSVD12

N1

AL2

M2

A13

COMP0

T1

COMP1

G2

COMP2

R1

COMP3

N5

RSVD13

AE6

RSVD14

C9

RSVD15

G10

RSVD16

D16

RSVD17

A20

RSVD18

E23

RSVD19

E24

RSVD20

F23

RSVD21

H2

RSVD22

J2

RSVD23

J3

RSVD24

Y1

V2

LL_ID0

AA2

LL_ID1

FSB_VTT

CPU_PWRGD

R143

R143

0

0

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

915M12

915M12

915M12

TESTHI_0 13

TESTHI_2_7

RSVD_AK6

RSVD_G6

R201 0

R201 0

*

*

PROCHOTJ

HCOMP0

HCOMP1

HCOMP2

HCOMP3

TP_RSVD_CPU_N5

TP_RSVD_CPU_C9

HGTLREF

HCOMP4

TP_RSVD_CPU_A20

CPU_BOOT

LL_ID0

TP_LL_ID1

VTT_OUT_RIGHT

R138

R138

620

620

*

*

Reserved

Reserved

*

*

1

CPU_PWRG 22

THERMTRIPJ 22

VTT_OUT_RIGHT

R0603

R0603

+/-5%

+/-5%

R0603

R0603

+/-5%

+/-5%

dummy

dummy

TP13TP13

MCH_GTLREF 13,14

TP14TP14

TP19TP19

TP49TP49

TP22TP22

VTT_OUT_LEFT

VRM_EN 8,9

12 43Friday, June 17, 2005

12 43Friday, June 17, 2005

12 43Friday, June 17, 2005

CPUSLPJ 22

of

of

of

CC

CC

CC

Page 14

5

VCCP VCCPVCCP

D D

C C

B B

A A

U8E

U8E

5 OF 7

AG22

AM26

AE12

AE11

AL18

AC25

AN14

AD28

AC29

AC27

AM18

AM19

AC26

AF15

AE14

AC24