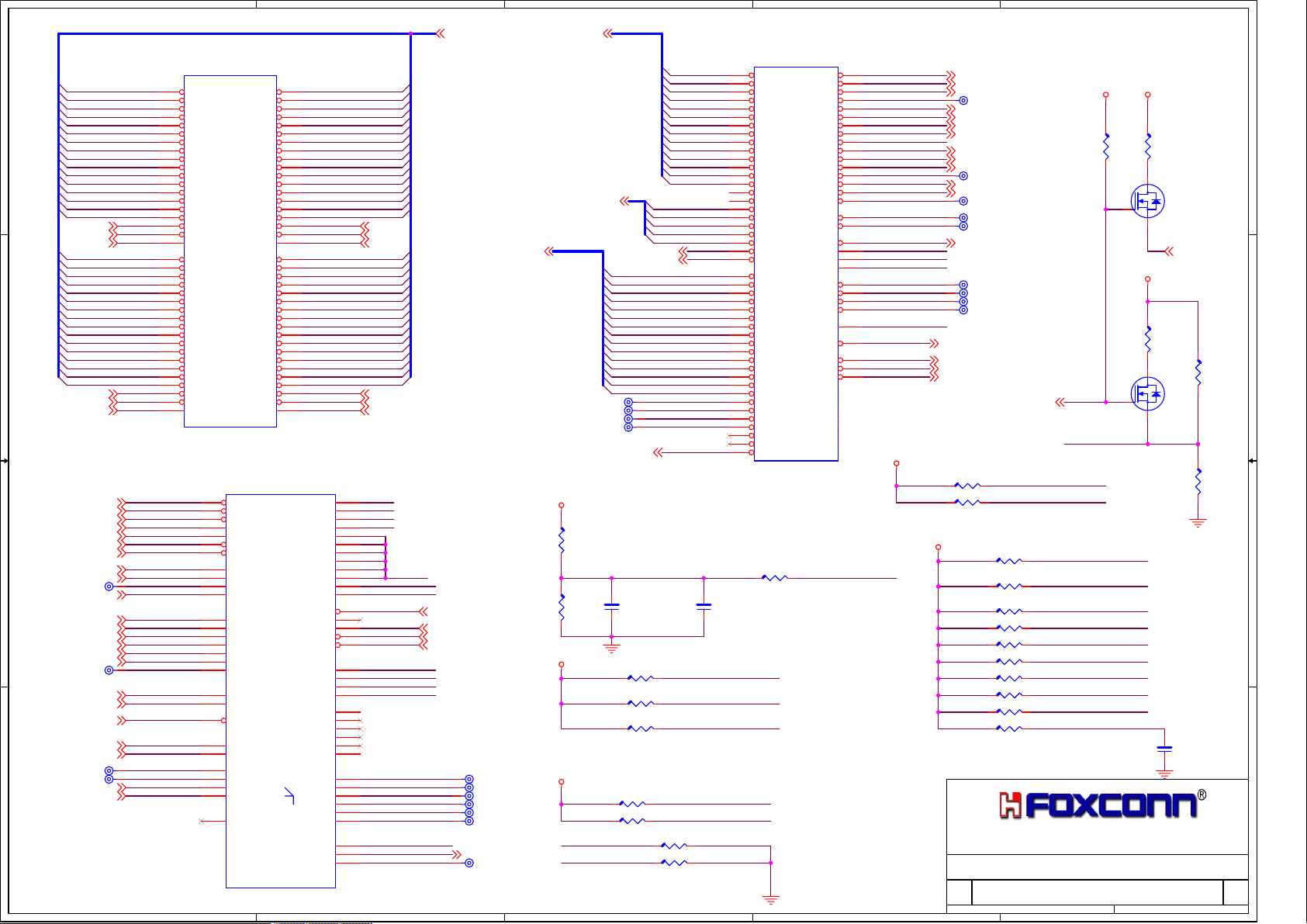

Foxconn 915A01 Schematic

5

4

3

2

1

Foxconn Precision Co. Inc.

915A01 Schematic

Fab.B Date: 2004/05/01

D D

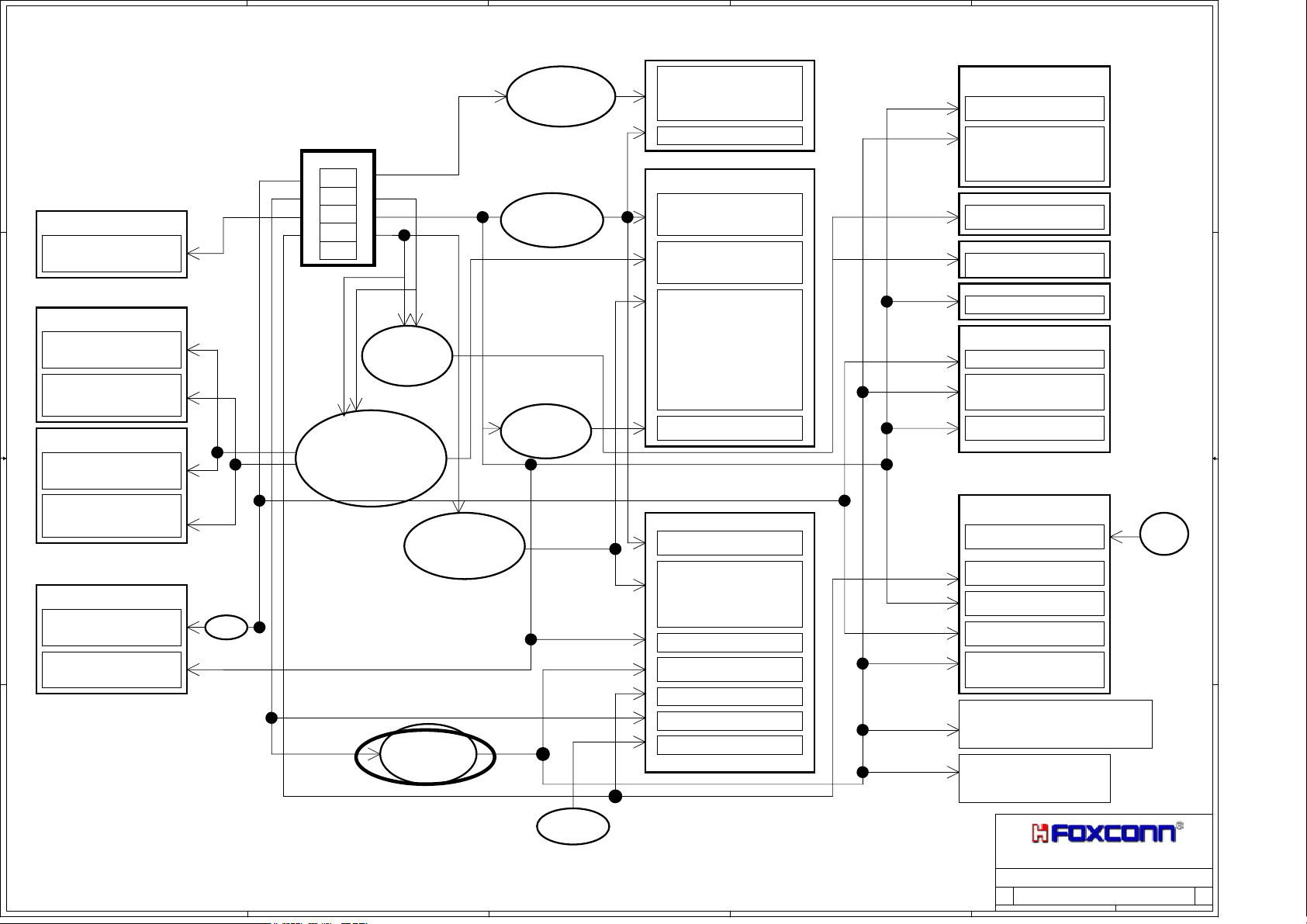

Page Index

01. Index Page

02. Topology

03. Rest Map

04. Clock Distribution

05. Power Delivery Map

06. Power Sequence

07. CK410 ClockGen

C C

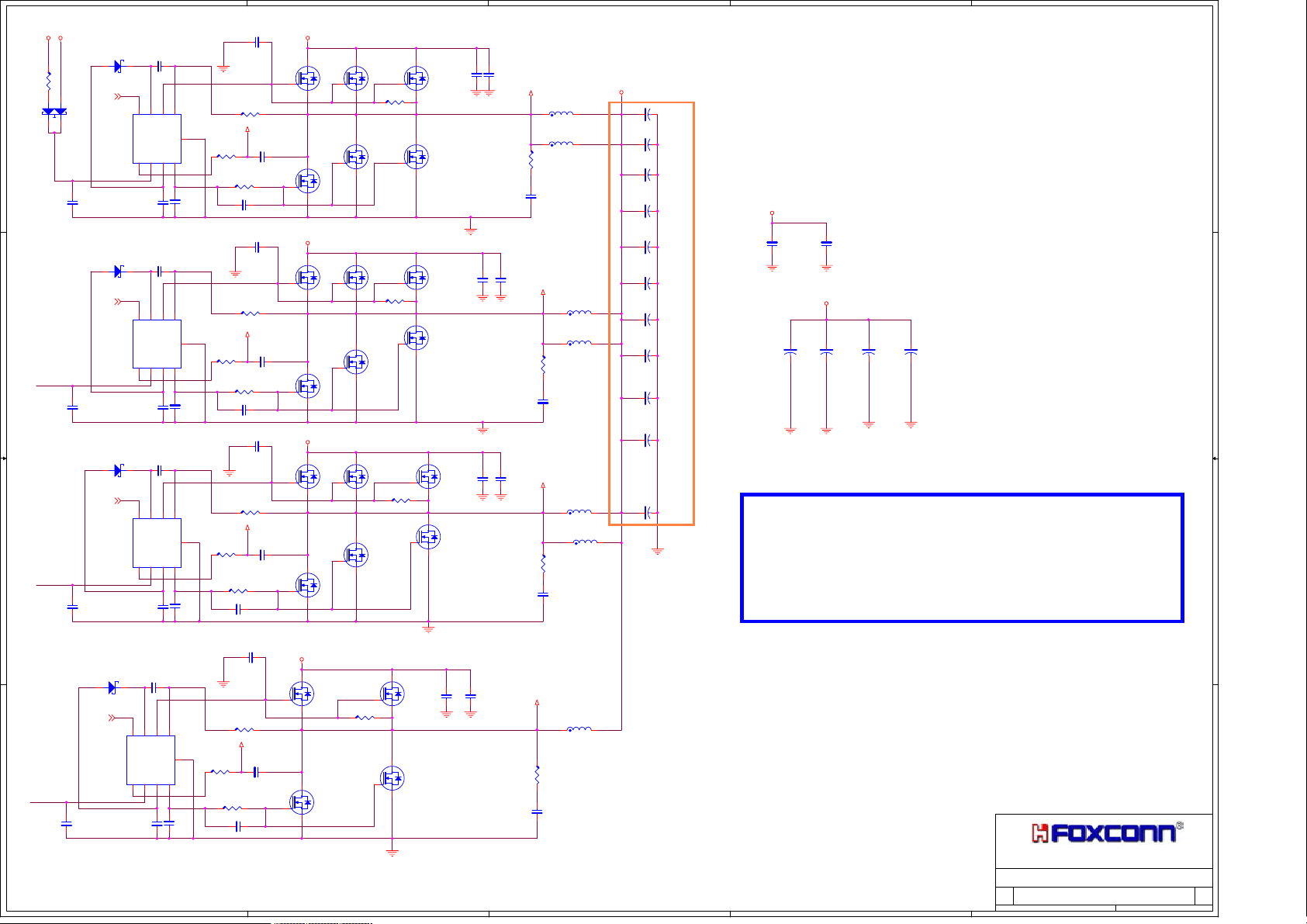

08. VRD10.1 (SC2646, 3P)

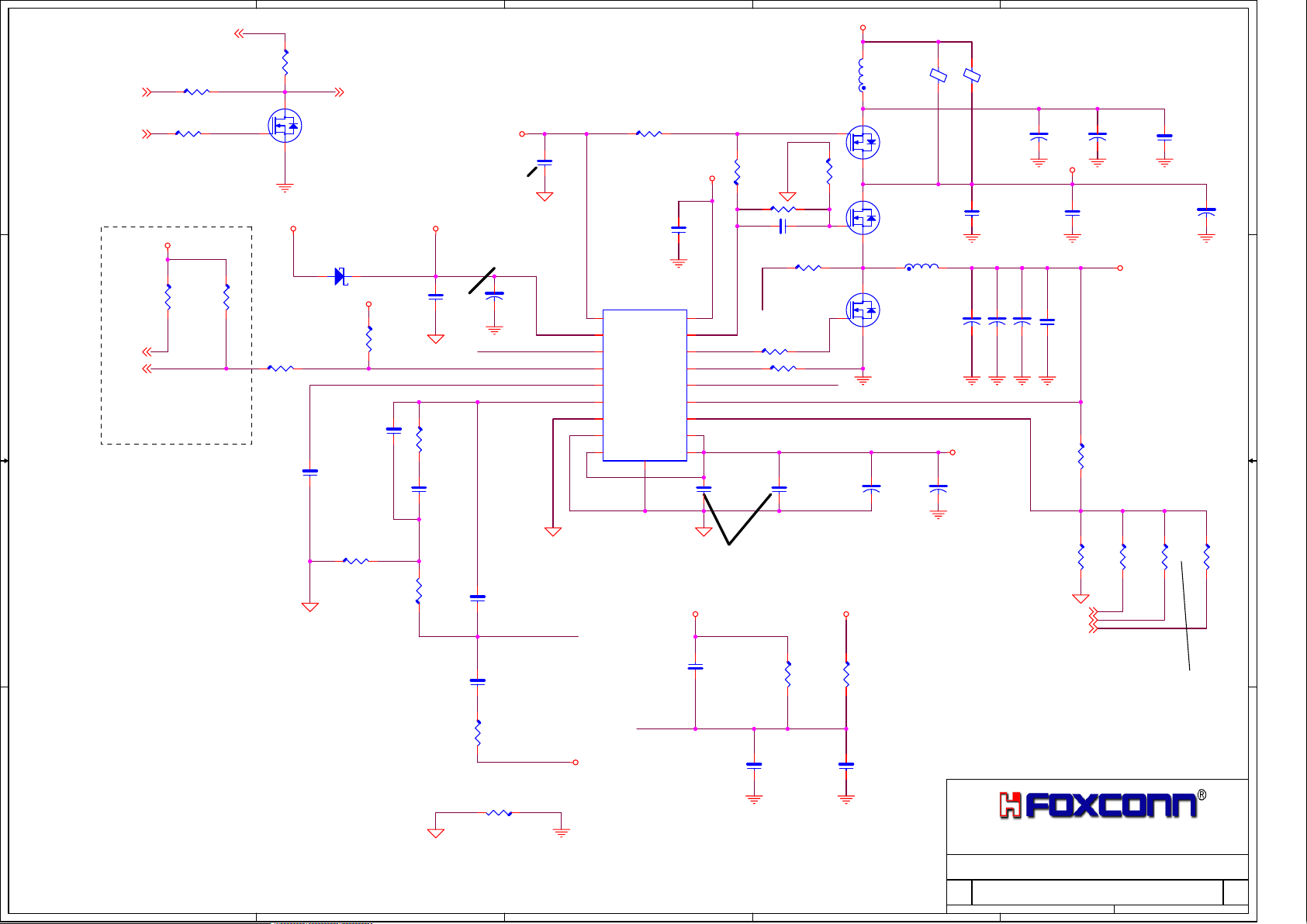

09. VRD10.1 (SC1211)

10. DDR2 POWER

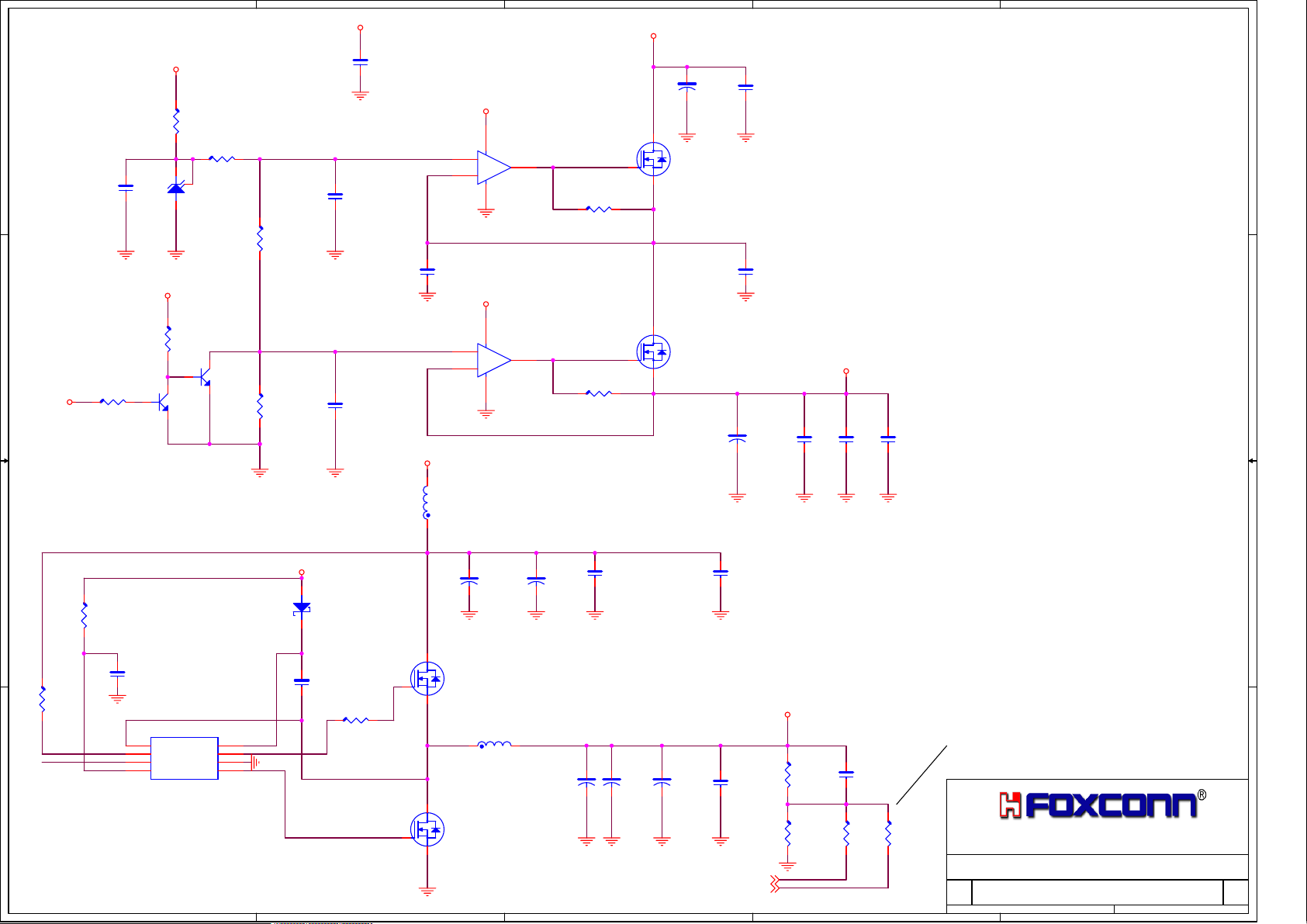

11. Power 1.5V/1.2V

12. 2.5V_MCH

13. LGA775 -1

14. LGA775 -2

15. Grantsdale -GMCH -1

16. Grantsdale -GMCH -2

B B

17. Grantsdale -GMCH -3

18. DDR2 Channel A Term.

19. DDR2 Channel A DIMM1, 2

20. DDR2 Channel B Term.

21. DDR2 Channel B DIMM1, 2

22. PCI Express x16 Gfx Slot

23. VGA Connector

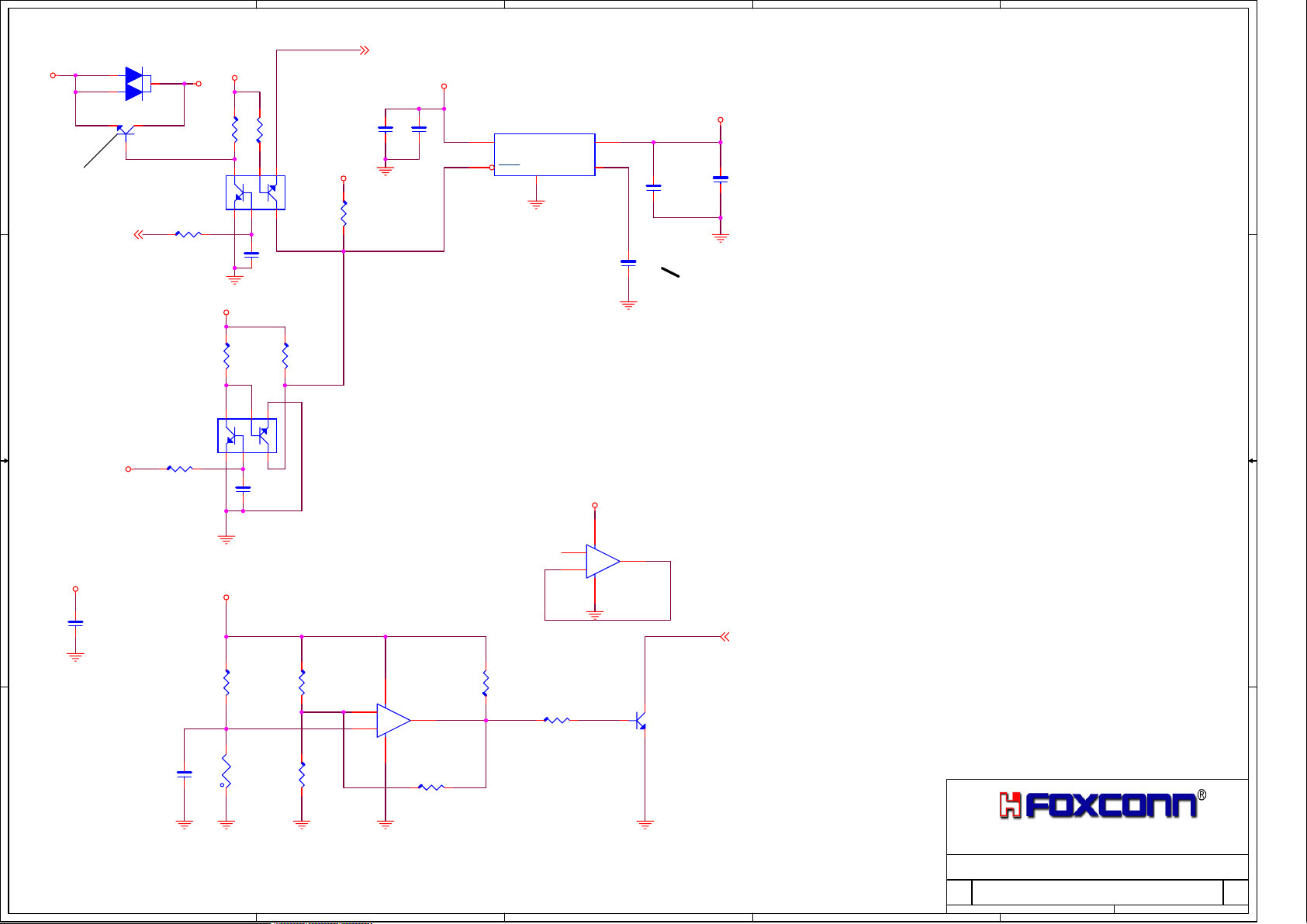

24. ICH6-1

25. ICH6-2

A A

26. ICH6-3

27. LAN RTL8110S

28. RT8110S/C-POWER

29. LAN Connectors

30.SATA Controller/Regulator

31. AC' 97 2.3/Azalia Codec

32. FWH

33. USB Connectors

34. Power Conn. / 3V_SB/FAN

35. Front Panel / MISC Conn.

36. PCI Express x1 Slot 1

37. PCI Express x1 Slot 2

38.PCI Express x1 Slot3]

39. PCI Slots 1

40.PCI Slot 2

41.PCI Slot 3

42. Super I/O

43. HW Monitor

44. Keyboard / Mouse

45. Serial / Parallel

46. VT6307_1394

47. 1394 CON

48. TPM

49. VID Controller

50. GPIO / IRQ / IDSEL Map

51. Jumper Setting Table

52. Modify List

FOXCONN PCEG

Title

Index Page

Size Document Number Re v

5

4

3

2

Date: Sheet

915A01 DDR2

152Tuesd ay, May 18, 2004

1

of

B

5

4

3

2

1

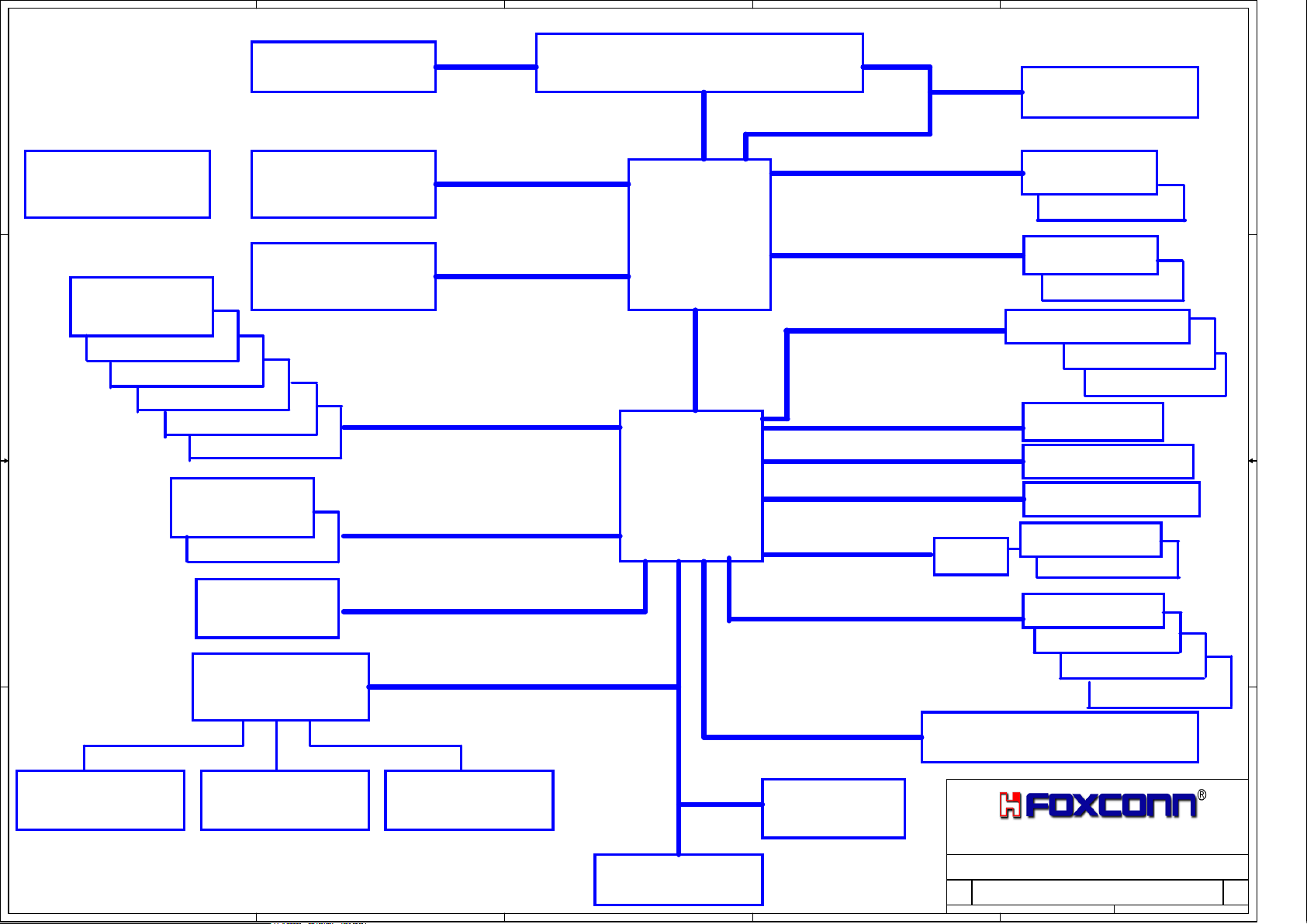

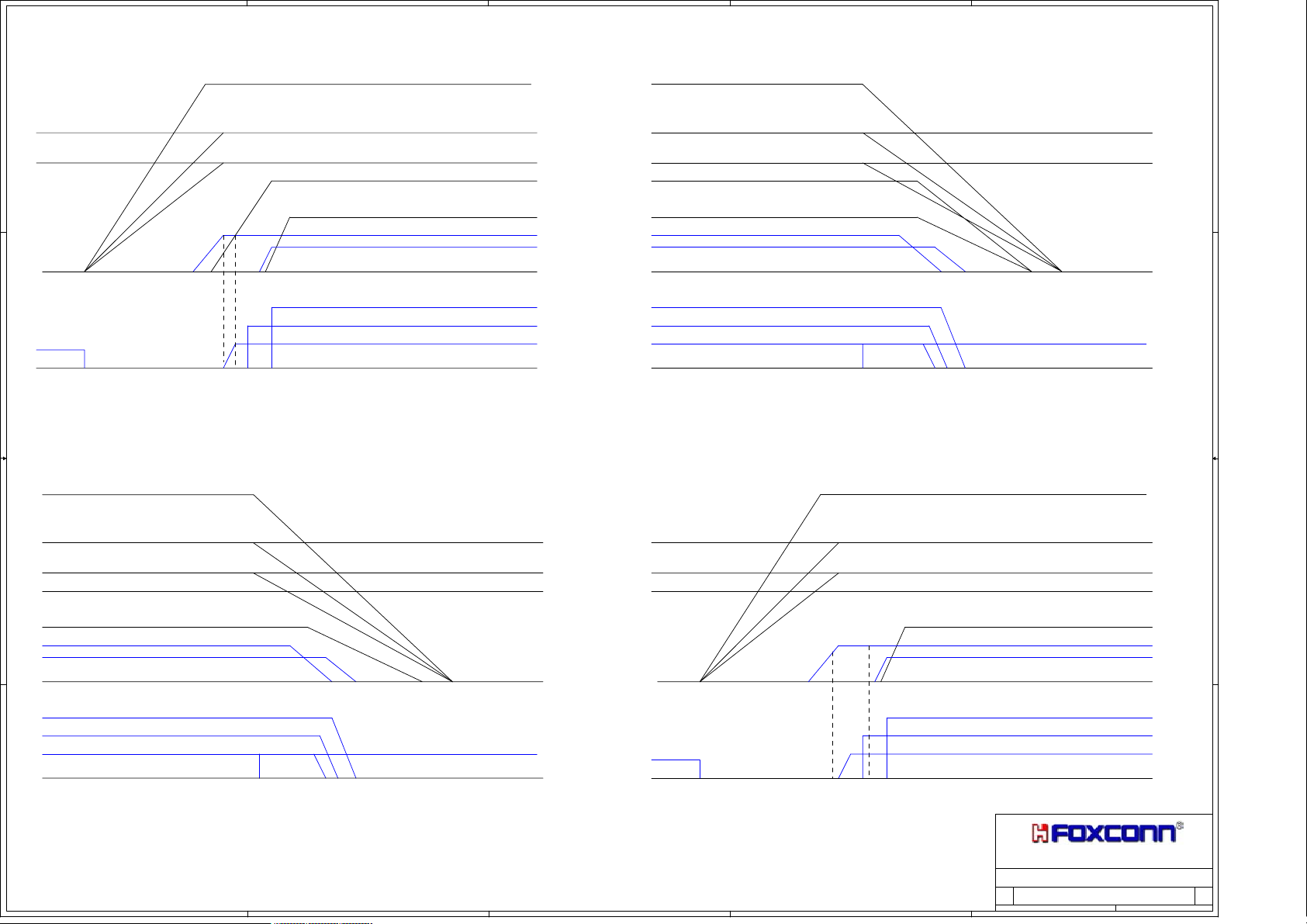

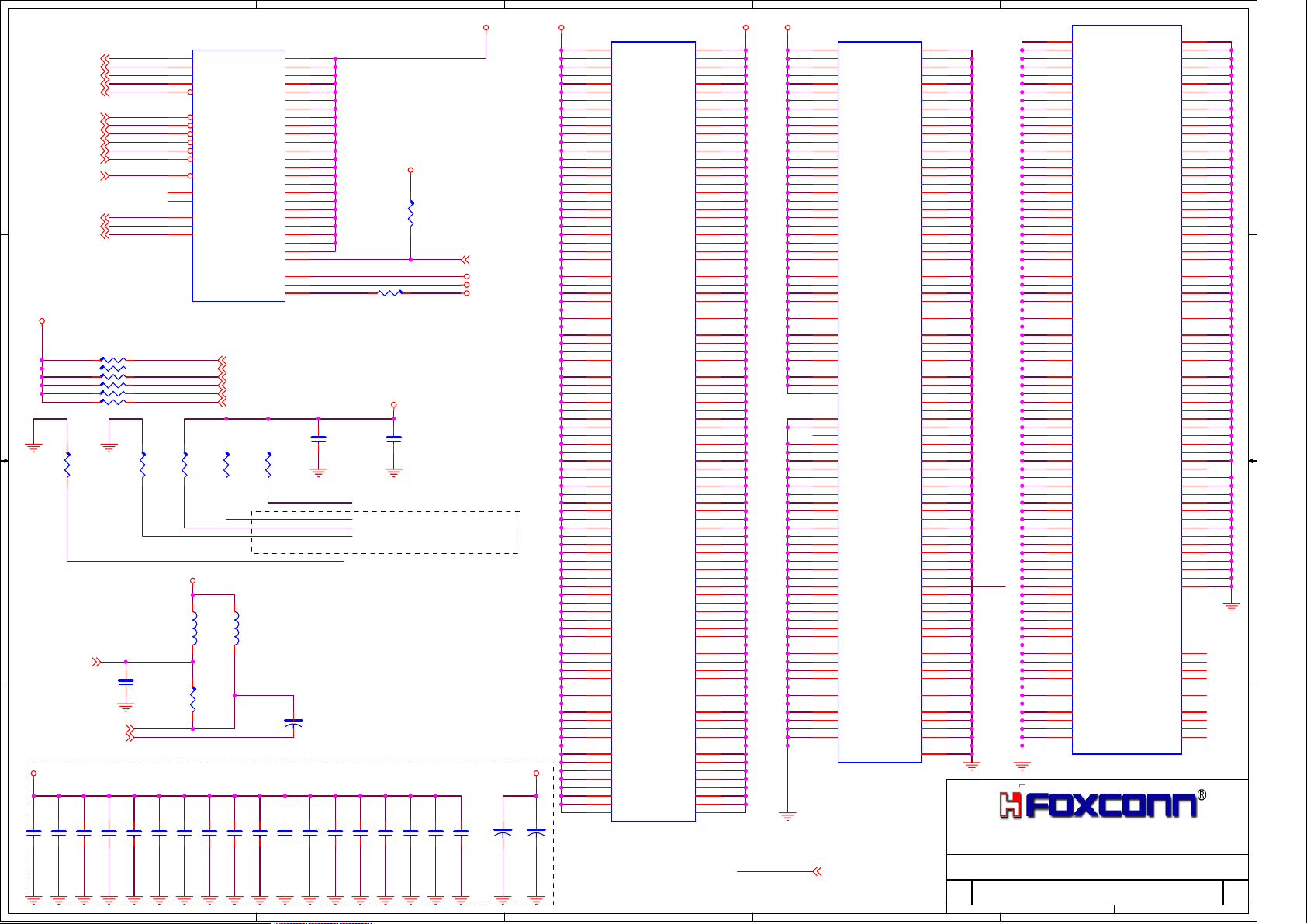

VRD 10.1

3 Phase PWM

D D

Intel SDVO Card

or

PCI Express x 16

External Graphics

PCI Express x16 Port

Card

VGA Connector

Back Panel

USB2.0 Port 1

C C

USB2.0 Port 2

USB2.0 Port 3

Direct Media Interface (DMI)

USB2.0 Port 4

USB2.0 Port 5

USB2.0 Port 6

Front Panel

USB2.0 Port 7

USB2.0 Port 8

B B

ATA100

IDE CONN 1

- LGA775 processor

Socket T

800/533 FSB

GMCH

GrantsDale

4 Lanes

ICH6

DDR2 533/400

DDR2 533/400

PCI Express x1 Interface

PCI Interface

PCI Interface

PCI Interface

PCI Interface

Sil3112A

CK-410 Clock

Channel A DDR2

DIMM1

DIMM2

Channel B DDR2

DIMM1

DIMM2

PCI-E Slot 1

PCI-E Slot 2

PCI-E Slot 3

uATX Form Factor

PCI Slot 1,2,3

LAN

REALTEK 8100C/8110S

1394

VIA VT6307

Serial ATA

SATA Connector 5

SATA Connector 6

Serial ATA

SATA Connector 1

SATA Connector 2

Prescott, Tejas

Super I/O

ITE IT8712F

LPC I/F

SATA Connector 3

SATA Connector 4

AC 97 2.3/Azalia Header

Realtek ALC203/ALC650/ALC655

A A

PS2

Keyboard / Mouse

Parallel

Serial

Floppy

Drive Connector

Firmware HUB

4Mb or 8Mb

FOXCONN PCEG

Title

TPM TCPA1.2

(HEADER)

5

4

3

2

Topology

Size Document Number Re v

Date: Sheet

915A01 DDR2

252Tuesd ay, May 18, 2004

1

of

B

5

4

3

2

1

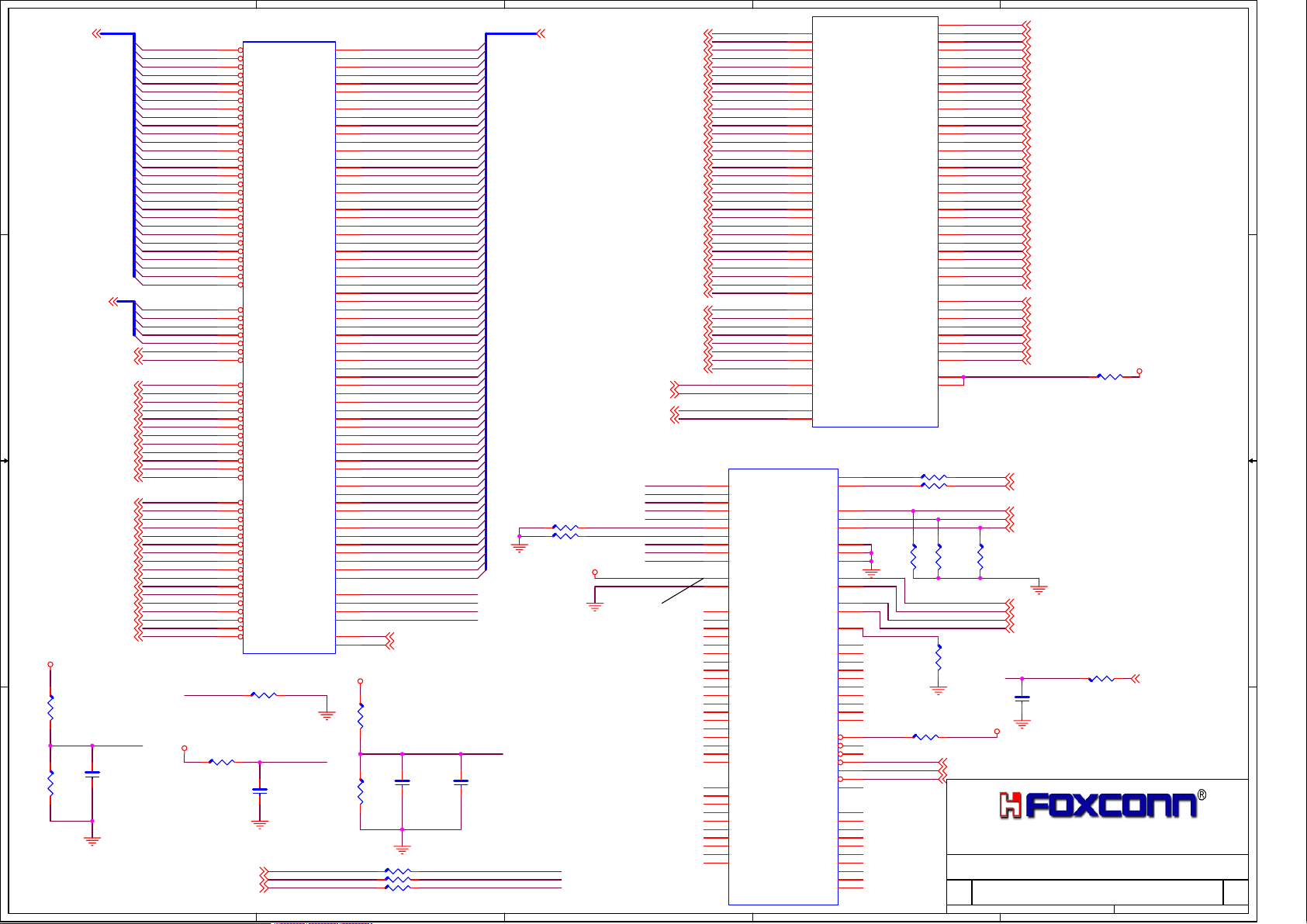

CPU (Tejas / Prescott)

ATX

Power

D D

PWRGD_PS

PS_ON#

Translation

Circuitry

PWRGD_3V

LGA775 processor

PWROK

CPURST#

CPU_PWRGD

CPURST#

GMCH

PCI Express x16

GrantsDale

RSTIN#

C C

ICH_PWRGD

LRESET#

PCIRST#

Buffer

uATX Form Factor

RST#

Buffer

RST#

FWH

Front Panel

PWROK

ICH6

PLTRST#

AC_RST#

Buffer

TPM

PCI Slot 1

LAN RST#

1394 RST#

ATA100

IDE CONN 1

B B

FR_RST

SW_ON

SYS_RESET#

PWRBTN#

SLP_S3#

RST#

RCIN#

KBRST

Super IO

RSMRST#

RST#

Power on/off

circuit

RSMRST#

PSIN

Audio

PWRON#

A A

RSMRST circuit

5

4

3

PSOUT#

FOXCONN PCEG

Title

Reset Map

Size Document Number Re v

2

Date: Sheet

915A01 DDR2

352Tuesd ay, May 18, 2004

1

of

B

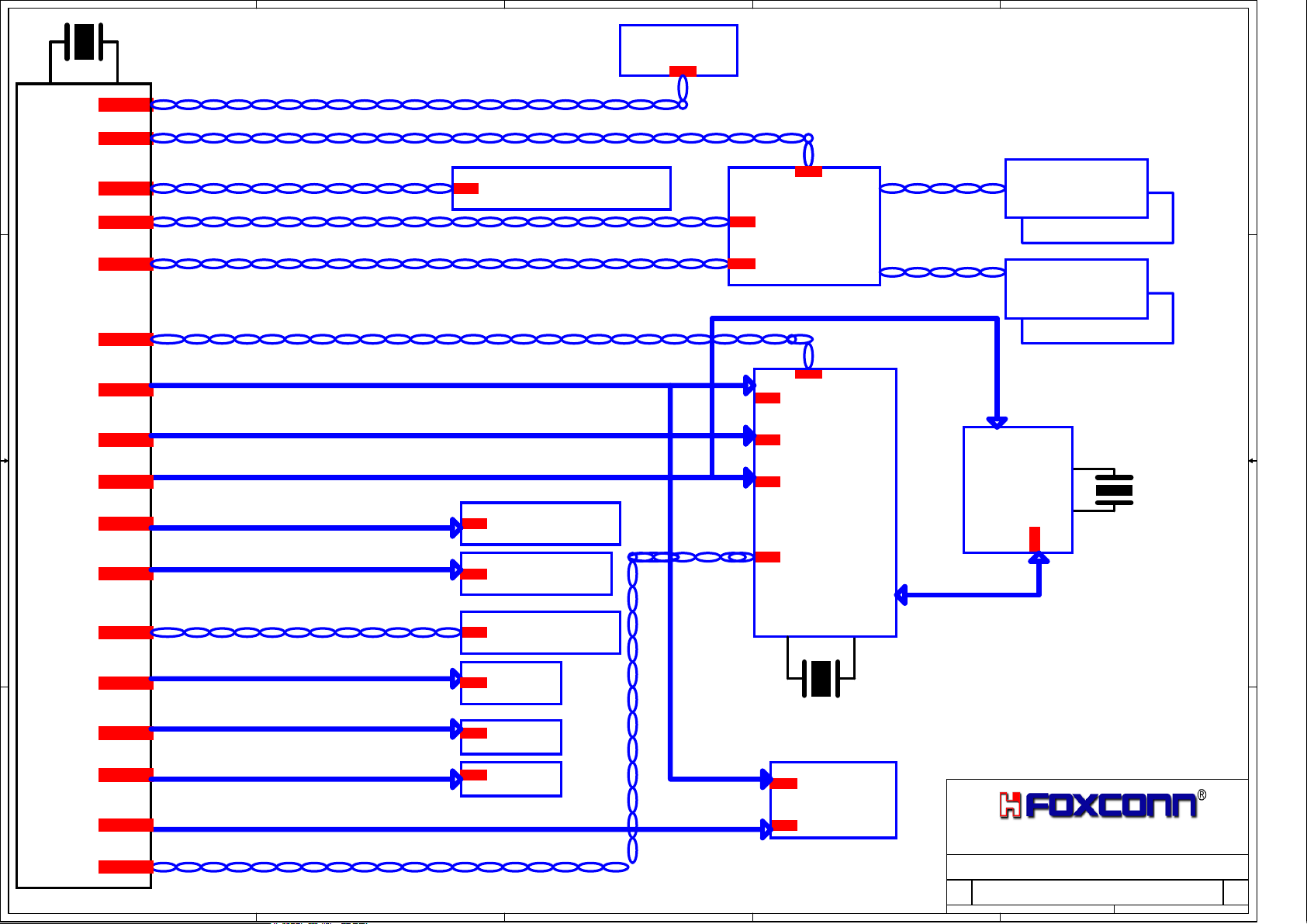

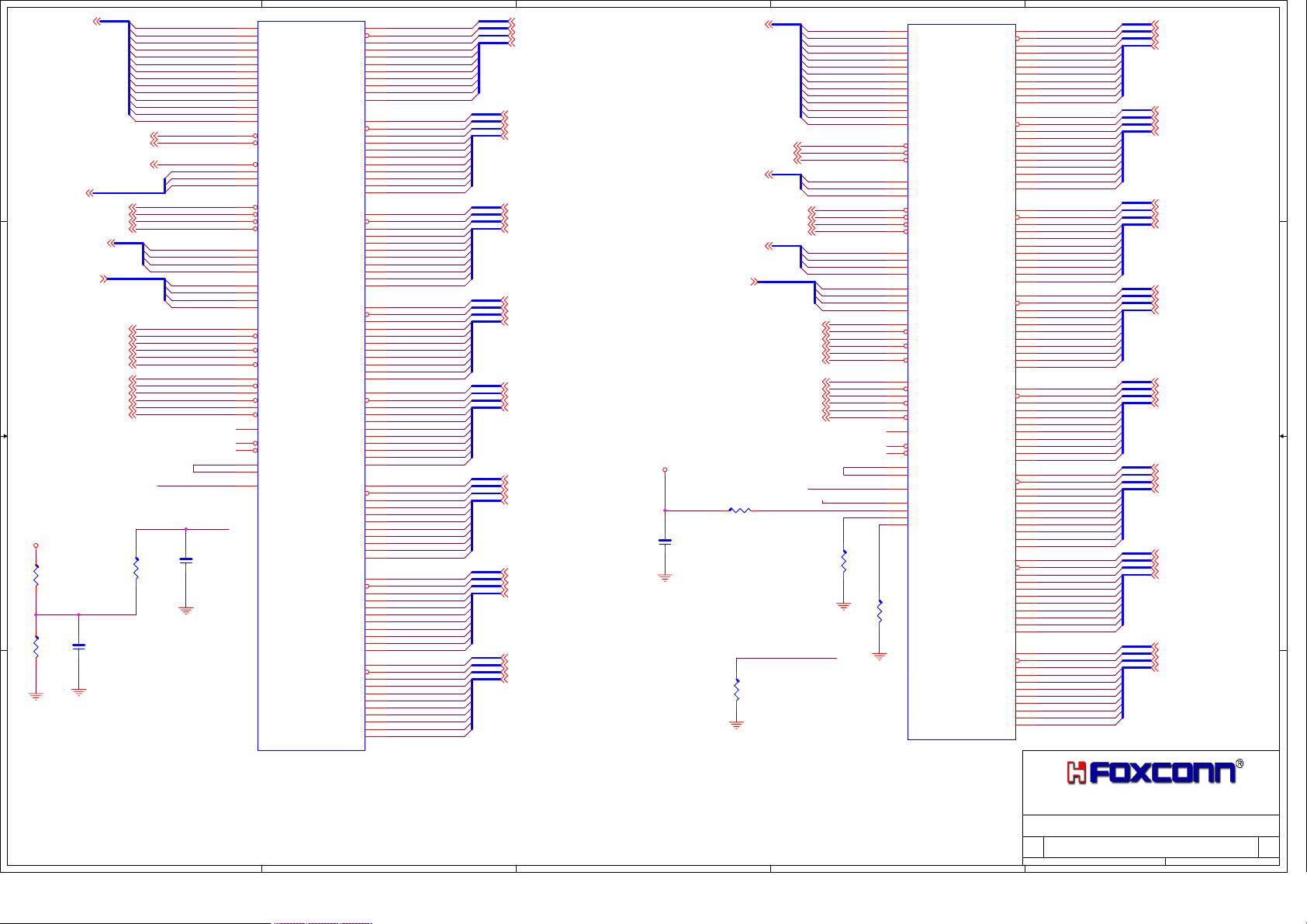

14.318MHz

5

4

3

2

1

CPU

CPU 133/200 MHz Diff Pair

D D

MCH 133/200 MHz Diff Pair

DDR 4 Slots 12 Diff CLKs

PCI Express 100 MHz Diff Pair

DOT 96 MHz Diff Pair

PCI Express x16 Gfx

GMCH

GrantsDale

PCI Express/DMI 100 MHz Diff Pair

PCI Express/DMI 100 MHz Diff Pair

C C

CK-410

USB/SIO 48 MHz

ICH 33 MHz

REF 14 MHz

Channel A DDR2

DIMM1

DIMM2

Channel B DDR2

DIMM1

DIMM2

AC'97

FWH 33 MHz

PCI 33 MHz

B B

FWH

PCI Slot 1,2,3

ICH6

AC97 Bit Clock

24.576MHz

PCI Express 100 MHz Diff Pair

LAN 33 MHz

PCI-E SLOT1,2,3

LAN

TPM 33 MHz

32.768KHz

TPM

1394 33 MHz

1394

A A

SIO 33 MHz

SATA 100 MHz Diff Pair

5

4

3

Super I/O

FOXCONN PCEG

Title

CLOCK Distribution

Size Document Number Re v

2

Date: Sheet

915A01 DDR2

452Tuesd ay, May 18, 2004

1

of

B

5

4

3

2

1

Proceessor

VRD 10.1

Switching

D D

Four Phase

Vccp (CPU Vcore)

Voltage=0.8375~1.6V

Icc(Max)=110A

(Tejas FMB1)

1.2V FSB

Vtt-tbdA

ATX P/S

12V

CK 410

Vdd (Core)

3.3V

Ivdd(Max)=560mA

5VSB

3.3V

5V

-12V

Linear 3.3V

to 1.2V

5A

DDR2 Channel A

Vdd (Core)

C C

1.8V

Ivdd(Max)=4A(per channel)

Vtt (Core)

0.9V

Ivterm(Max)=600mA

(per channel)

Single Phase Switch

DDR Channel B

Vdd (Core)

1.8V

Ivdd(Max)=4A(per channel)

Vtt (Core)

0.9V

Ivterm(Max)=600mA

(per channel)

B B

5V to 2.6V

Ivdd(Max)=11.5A

Ivdd(Max)=500mA(S3)

LDO

2.6V to 1.3V

Ivterm(Max)=1.8A

5VDUAL

Icc(Max)=

4.345A(S0,S1)

22mA(S3)

V_1p5_core

1.5V

Switching=12A

2.5V DAC

regulator

V_2p5_DAC

100mA

AC'97 2.3 Codec

Vcc

5V

Icc(Max)=48mA

Vcc

3.3V

Icc(Max)=20mA

A A

5

LDO

12V to 5V

LDO

5VSB to 3.3SB

Icc(Max)=1.5A

4

RTC

Battery

3

Grantsdale GMCH

FSB_Vtt

1.2V FSB Vtt

Icc(Max)=1.2A

2.6V DDR1 I/O=5.5A(S0,S1)

2.6V DDR1 I/O=250mA(S3)

Vcore (Core Logic)

1.5V

Icc(Max)=9.6A(Integrated)

Icc(Max)=7.5A(Discrete)

*1.5V

PCIexpress(X16)=1A

*1.5V

PCIexpress(X1)=0.06A

*1.5V SDVO=tbdA

*1.5V DMI=0.25A

*2.5V DAC=0.07A

2.5V HV=tbdA

ICH6

1.2V VCC_CPU-tbdmA

1.5V Core=1.88A

*1.5V PCI Express=270mA

*1.5V DMI=290mA

1.5V SATA=430mA

3.3V=180mA

3.3V VccSus

Icc(Max)=330mA

5VRef=tbduA

5VrefSus=tbduA

RTC=5uA

*Power derived through filter

2

Super I/O

3.3V

Icc(Max)=50mA

3.3SBV

Icc(Max)=50mA(S0)

3.3SBV

Icc(Max)=38mA(S3)

USB 8 Ports

+5V DUAL=4A(S0, S1)

+5V DUAL=20mA(S3)

PS2

+5V DUAL=345mA(S0, S1)

+5V DUAL=2mA(S3)

FWH

3.3V=107mA(S0, S1)

PCI Express

X16 slot (1)

+12V=4.4A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

+3.3V=3A

PCI Slot 1

-12V

Icc(Max)=0.1A

5V

Icc(Max)=5A

3.3V

Icc(Max)=7.6A

12V

Icc(Max)=0.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

PCI LAN (REALTEK 8100C/8110S)

3.3VSB/3.3V_SYS

P(Max)=2W(Gb),

P(Max)=.622W(100Mb),

P(Max)=.512W(10Mb)

PCI 1394 (VIAVT6307)

3.3V_SYS

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

Title

Power Delivery Map

Size Docum ent Num ber Re v

Date: Sheet

FOXCONN PCEG

915A01 DDR2

1

552Tuesday, M ay 18, 2004

-12V

BC

of

5

4

3

2

1

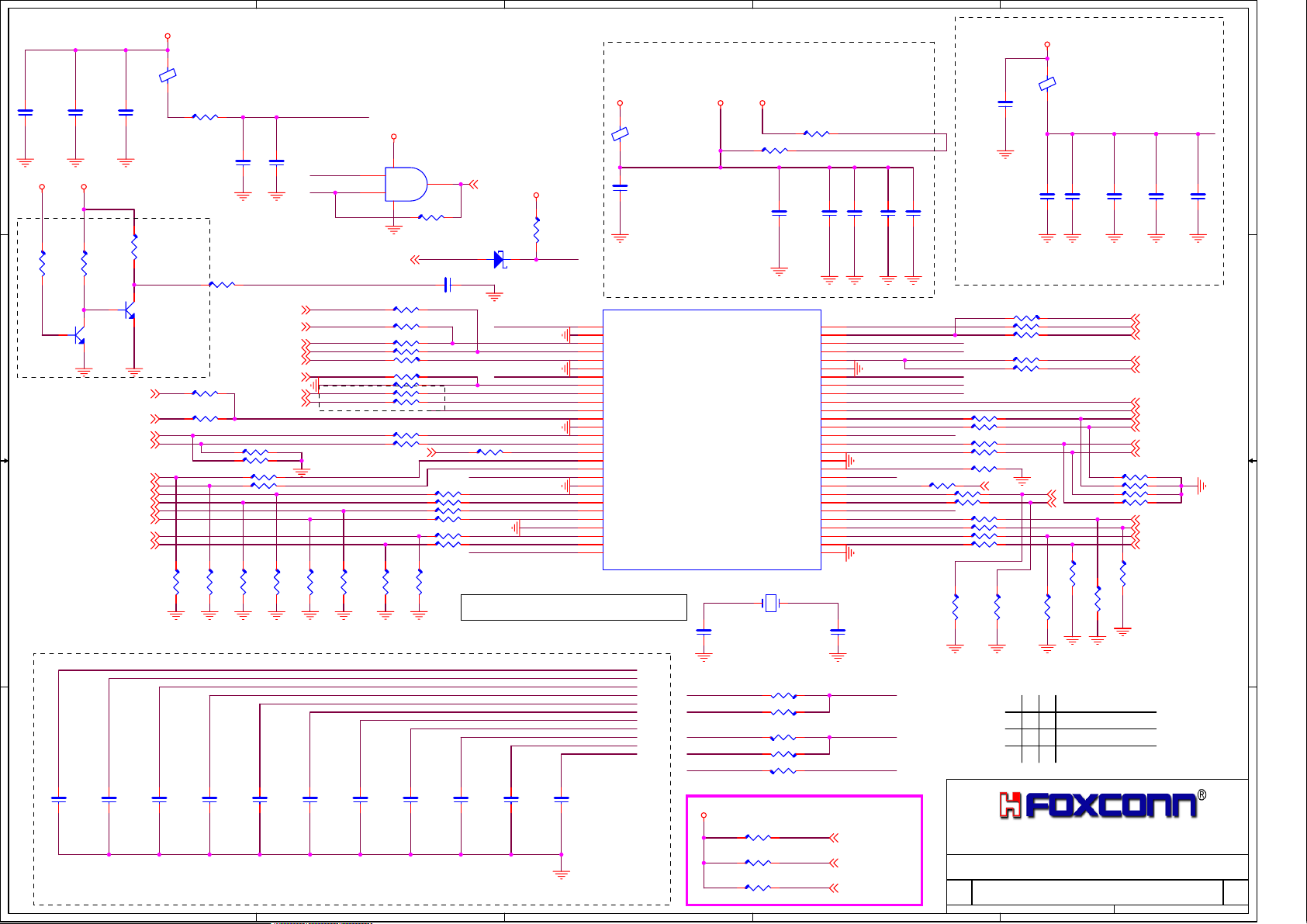

S5->S0

D D

+5V_DUAL

+12V_SYS

+5V_SYS

+3D3V_SYS+3D3V_DUAL

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

1ms to 10ms

Vcc_PWRGD

VRM_OUTEN

PS_ONJ

C C

S0->S3

+12V_SYS

VIDPWRGD

S0->S5

+12V_SYS

+5V_SYS

+3D3V_SYS

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

S3->S0

+5V_DUAL

+3D3V_DUAL

PS_ONJ

+12V_SYS

+5V_SYS

+3D3V_SYS

B B

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

A A

5

4

+5V_DUAL

+3D3V_DUAL

+2D6V_STR

PS_ONJ

+5V_DUAL

+3D3V_DUAL

+2D6V_STR

+5V_SYS

+3D3V_SYS

+2D6V_STR

VTT_DDR

VTT_VR

Vcc

1ms to 10ms

Vcc_PWRGD

VRM_OUTEN

PS_ONJ

Title

Power Sequence

Size Docum ent Num ber Re v

3

2

Date: Sheet

VIDPWRGD

FOXCONN PCEG

915A01 DDR2

1

652Tuesday, M ay 18, 2004

BC

of

5

3D3V_SYS

Note :

1. When CV115, Pin 54 is FSA. When CV115-2/-4, Pin 54 is FSA/REF1.

2. When CV115, Pin 38 is FSB. When CV115-2/-4, Pin 38 is RESET output and Pin 12 is FSB/48Mhz.

4

3

VDD_PCI Filter

2

3D3V_SYS

1

VDD_CPU/VDD_SRC Filter

3. When CV115, Pin 37 is FSC. When CV115-2/-4, Pin 37 is TURBO2 input and Pin 52 is FSC/REF0.

C1206

BC186

10uF

*

10V, Y5V, +80%/-20%

D D

VCCP

BC150

0.1uF

*

25V, X7R, +/-10%

C0603

*

25V, X7R, +/-10%

3D3V_CLK_PCI

BC153

0.1uF

C0603

*

R219

R220

*

*

C C

B B

A A

220

+/-5%

R0603

Dummy

B

CK_PE_100M_P_16PORT22

CK_PE_100M_N_16PORT22

CK_PE_100M_P_1PORT136

CK_PE_100M_N_1PORT136

CK_PE_100M_P_GMCH15

CK_PE_100M_N_GMCH15

CK_SATA_100M_P_ICH25

CK_SATA_100M_N_ICH25

*

50V,NPO,+/-5%

BC170

10pF

C0603

Dummy

10K

+/-5%

R0603

Dummy

Q43

MMBT3904

Dummy

E C

CK_96M_P_GMCH15

CK_96M_N_GMCH15

B

E C

CK_48M_SIO42

CK_48M_ICH24

BC175

10pF

*

C0603

Dummy

50V,NPO,+/-5%

5

FB25

FB L0805 300 Ohm

2 1

R119 2.2

+/-5%

*

R0603

this cap. placed

close to power pin

ONLY POP WHEN CV115 POPED

R204

10K

+/-5%

R0603

Dummy

R205 4.7K

R0603 +/-5%

Q28

MMBT3904

Dummy

R143 22

R147 22

*

50V,NPO,+/-5%

*

R0603+/-5%

*

*

R160 49.9 +/-1%

R1537 49.9 +/-1%

R166 33R0603 +/-5%

R168 33R0603 +/-5%

R165

*

*

49.9

+/-1%

R0603

BC157

10pF

*

C0603

Dummy

50V,NPO,+/-5%

4. Pin 5 of CV115-2/-4 is either TURBO1 or PCI4.

5. When CV115-4, Pin 14 and Pin 15 are SRC_0 and SRC_0#.

10uF

R0603

R167

49.9

+/-1%

R0603

BC154

10pF

C0603

Dummy

VDD_48 Filter

C1206

BC148

10V, Y5V, +80%/-20%

10nF

*

Dummy

CK_33M_PCI240

CK_33M_139446

CK_33M_PCI139

CK_33M_TPM48

TRUBO1J42

CK_33M_Sil3112A30

CK_33M_SIO42

CK_33M_ICH26

+/-5%

*

*

*

*

R178

*

49.9

+/-1%

R0603

*

50V,NPO,+/-5%

3D3V_CLK_48

C0603

BC179

50V, X7R, +/-10%

*

CLK_VTT_PWRGDJ

*

BC161

10pF

C0603

Dummy

PWRGD_3V

FS1-CV115

R12400 33R0603 +/-5%

R128 33R0603 +/-5%

R124 33R0603 +/-5%

R130 33R0603 +/-5%

R685 0 Dummy

R146 4.7KR0603 +/-5%

R132 33R0603 +/-5%

R135 33R0603 +/-5%

Change R from 43OHM to 33OHM

R154 33 +/-5%R0603

R161 33R0603 +/-5%

PE_100M_P_16PORT

PE_100M_N_16PORT

R174

R184

*

49.9

+/-1%

R0603

*

49.9

+/-1%

R0603

BC164

10pF

*

C0603

Dummy

50V,NPO,+/-5%

3D3V_SB

U31 NC7SZ08

53

1

2

ICH_SYS_RSTJ14,24,35,49

Dummy

4

R580 0

*

Dummy

ICH_SYS_RSTJ FS1-CV115

BC586 10nF

*

*

*

*

*

*

R1438 33 R0603+/-5%

R175 33 +/-5%R0603

R179 33 +/-5%R0603

R181 33R0603 +/-5%

R185 33R0603 +/-5%

R190 33R0603 +/-5%

R198 33R0603 +/-5%

R180

49.9

+/-1%

R0603

BC165

10pF

*

C0603

Dummy

50V,NPO,+/-5%

*

*

*

*

*

R208 33

*

PWRGD_3V10,15,24,32,34 CK_200M_N_GMCH 15

*

*

*

*

*

*

R189

R197

*

*

49.9

+/-1%

R0603

*

50V,NPO,+/-5%

49.9

+/-1%

R0603

BC152

10pF

C0603

Dummy

EMI CAPS.

4

3D3V_SYS

2 1

BC187

PWRGD_3V_ACT 15,24

+/-5%

R0603

D11

1N4148W

C0603

50V, X7R, +/-10%

33M_PCI1

XDP_EN

33M_SIO

33M_ICH

3D3V_CLK_48

FS1-CV115-24

96M_DOT_P

96M_DOT_N

*

3D3V_CLK_CPU_SRC

3D3V_CLK_CPU_SRC

3D3V_SB

R222

*

10K

+/-5%

R0603

Dummy

21

3D3V_CLK_PCI

3D3V_CLK_PCI

CLK_VTT_PWRGDJ

PE_100M_P1

PE_100M_N1

PE_100M_P_GMCH

PE_100M_N_GMCH

SATA_100M_P_ICH

SATA_100M_N_ICH

*

U12

1

VDD_PCI

2

VSS_PCI

3

PCI2

4

PCI3

5

PCI4/Turbo1

6

VSS_PCI

7

VDD_PCI

8

PCIF_0/ITP_EN

9

PCIF

10

PCIF2

11

VDD_48

12

FS_B/48MHZ

13

VSS_48

14

DOTT_96MHz

15

DOTC_96MHz

16

(VTT_PwrGd/PD#)

17

SRC_1

18

SRC_1#

19

VDDSRC

20

VSS

21

SRC_2

22

SRC_2#

23

SRC_3

24

SRC_3#

25

VSS_GND

26

SATA

27

SATA#

28

VDD_SRC

IDTCV115-2

0.1uF

25V, X7R, +/-10%

C0603

SM Bus Address :1101-0010

CK_48M_SIO

CK_48M_ICH

CK_33M_PCI1

CK_33M_LAN

CK_33M_1394

CK_33M_SIO

CK_33M_ICH

CK_33M_FWH

CK_33M_TPM

CK_14M_AUDIO

CK_14M_ICH

BC158

10pF

*

C0603

Dummy

50V,NPO,+/-5%

BC169

10pF

*

C0603

Dummy

50V,NPO,+/-5%

BC162

10pF

*

C0603

Dummy

50V,NPO,+/-5%

3

3D3V_CLK_PCI

FB24

FB L0805 300 Ohm

this cap. placed

close to power pin

FS2-CV115-24 FSBSEL2

FS2-CV115

FS1-CV115

FSB_VTT

3D3V_SB

R23 0 R0603+/-5%

this cap. placed

close to power pin

FS_A/(REF1/PCI5)

CPU_2_ITP/ SRC_7

CPU_2_ITP#/ SRC_7#

XTAL-14.318MHz

BC171

10pF

*

50V, NPO, +/-5%

C0603

R133 2.2K+/-5%

R686 2.2K+/-5%

R164 2.2K

R687 2.2K+/-5%

R171 2.2K

R213 470 +/-5%

*

R214 470 +/-5%

*

R131 470 +/-5%

*

R27 0 R0603+/-5% Dummy

*

C1206

BC147

10uF

*

10V, Y5V, +80%/-20%

PCI_1

PCI_0

VDD_suspend

FS_C/REF0

VSS_REF

XTAL_IN

XTAL_OUT

VDD_REF

CPU_0

CPU_0#

VDD_CPU

CPU_1

CPU_1#

VSS_CPU

RESET#

Turbo2

VDD_SRC

SRC_6

SRC_6#

SRC_5

SRC_5#

VSS_SRC

X3

CLK_OSC1CLK_OSC2

12

SCL

SDA

IREF

*

0.1uF C0603

3D3V_CLK_PCI

BC163

*

*

0.1uF C0603

25V, X7R, +/-10%

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

FS1-CV115

38

FS2-CV115

37

PE_100M_P3

36

PE_100M_N3

35

3D3V_CLK_CPU_SRC

34

33

32

31

30

29

BC166

10pF

*

50V, NPO, +/-5%

C0603

3D3V_CLK_PCI_SB

BC168

*

0.1uF C0603

25V, X7R, +/-10%

33M_LAN

33M_FWH

FS0

3D3V_CLK_PCI_SB

FS2-CV115-24

CLK_OSC1

CLK_OSC2

3D3V_CLK_PCI

200M_P_CPU

200M_N_CPU

3D3V_CLK_CPU_SRC

200M_P_GMCH

200M_N_GMCH

CLK_IREF

PE_100M_P2

PE_100M_N2

PE_100M_P_ICH

PE_100M_N_ICH

*

*

Dummy

FSBSEL1FS1-CV115-24

*

*

R0603

*

Dummy

R0603

FSBSEL0FS0

+/-5%

FSBSEL0 14,15

FSBSEL1 14,15

FSBSEL2 14,15

2

BC541

BC542

*

0.1uF C0603

25V, X7R, +/-10%

25V, X7R, +/-10%

R172 475+/-1%

R435 0

R1547 33

R0603 +/-5%

R1697 33

R182 33 +/-5%

R186 33 +/-5%

R191 33 +/-5%

R195 33 +/-5%

FB29

BC208

0.1uF

*

C0603

25V, X7R, +/-10%

high frequency decoupling caps. placed

close to power pins

R12401 33 R0603+/-5%

R121 33 R0603+/-5%

R126 33 R0603+/-5%

*

*

R142 22 R0603+/-5%

R134 22 R0603+/-5%

*

*

*

*

*

*

*

*

*

*

R1609

49.9

+/-1%

R0603

*

*

*

*

TRUBO2J 42

R153

*

49.9

+/-1%

R0603

*

FB L0805 300 Ohm

2 1

Change decoupling caps from 10nf to 0.1uf

3D3V_CLK_CPU_SRC

BC189

BC182

C1206

BC200

10uF

*

*

10V, Y5V, +80%/-20%

0.1uF C0603

25V, X7R, +/-10%

*

R16233+/-5%

R16933+/-5%

R15133+/-5%

R15833+/-5%

R170 49.9 +/-1%

R163 49.9 +/-1%

R159 49.9 +/-1%

CK_PE_100M_P_1PORT3 38

R152 49.9 +/-1%

CK_PE_100M_N_1PORT3 38

R196

*

49.9

+/-1%

R0603

*

R192

*

49.9

+/-1%

R0603

*

0.1uF C0603

R183

49.9

+/-1%

R0603

BC188

*

0.1uF C0603

25V, X7R, +/-10%

25V, X7R, +/-10%

CK_33M_PCI3 41

CK_33M_LAN 27

CK_33M_FWH 32

CK_14M_AUDIO 31

CK_14M_ICH 24

SMB_CLK_MAIN 19,21,4 4

SMB_DATA_MAIN 19,21,44

CK_200M_P_CPU 13

CK_200M_N_CPU 13

CK_200M_P_GMCH 15

*

*

*

*

CK_PE_100M_P_1PORT2 37

CK_PE_100M_N_1PORT2 37

CK_PE_100M_P_ICH 24

CK_PE_100M_N_ICH 24

R187

*

49.9

+/-1%

R0603

0.1uF C0603

*

BSEL TABLE

FSB Frequency

A

CB

000

001

010

266MHz

133MHz(533)

200MHz(800)

FOXCONN PCEG

Title

CK410 ClockGen

Size Document Number Re v

Date: Sheet

915A01 DDR2

752Tuesd ay, May 18, 2004

1

of

BC195

25V, X7R, +/-10%

B

5

BC358

*

8.2nF

C0603

50V,X7R,+/-10%

R391

+/-1%

20K

*

R0603

BC373

*

470pF

C0603

50V,NPO,+/-5%

AUX1 AUX3AUX2

*

R292

24.9K

+/-1%

R0603

*

R373

150K

+/-1%

R0603

BC365

1uF

*

16V,Y5V,+80%/-20%

C0603

R409 10

*

*

BC349

*

8.2nF

C0603

50V,X7R,+/-10%

+/-5%R0603

*

PVID0

PVID049

PVID1

PVID149

PVID2

PVID249

PVID3

PVID349

PVID4

PVID449

PVID5

PVID549

R109

24.9K

+/-1%

R0603

R352

150K

+/-1%

R0603

VRM_SYS

16V,Y5V,+80%/-20%

AUX4

D D

VRM_SYS

R365

*

3.6K

+/-1%

*

R0603

Dummy

Dummy

*

R354

30

+/-1%

R0603

C C

VRM_SYS

R406

20K

+/-1%

R0603

DUMMY

B B

*

*

*

BC3582

8.2nF

C0603

50V,X7R,+/-10%

R392

+/-1%

20K

*

R0603

DUMMY

12V_VRM

R2921

24.9K

+/-1%

R0603

Dummy

R3733

150K

+/-1%

R0603

Dummy

VTT_PWRGD

BC367

15pF

*

C0603

50V,NPO,+/-5%

*

*

*

BC350

8.2nF

C0603

50V,X7R,+/-10%

MSENSE

BC372

1uF

*

C0603

4

R122

24.9K

+/-1%

R0603

R353

150K

+/-1%

R0603

R155

R1557

*

*

1

1

+/-1%

+/-1%

R0603

R0603

Dummy

1

2

3

4

5

6

7

8

9

10

11

12

R284 0 R0603+/-5%

VRM_FB

R283 0 R0603+/-5%

VCCP

R149

R270

*

*

1

1

+/-1%

+/-1%

R0603

BC346

0.22uF

C0603

R0603

16V, Y5V, +80%/-20%

NONE

Pop only if 3 phase design is used

U24

OS3

OS2

OS1

BGOUT

ERROUT

GNDSEN

FB

OFFSET/MSENSE

VCC

VID4

VID3

VID2

SC2646

OS4

OUTSEN

OUT4

OUT3

OUT2

OUT1

AGND

OSCREF

PGOOD

VID5

VID0

VID1

*

*

R367

R156

*

10K

+/-1%

R0603

*

RT2 47K/NTC

*

T

R0603 +/-1%

R3656 0

24

VRM_SENSE

23

22

21

20

19

18

R397

17

*

R0603

16

15

14

13

VSS_SENSE 13

VCC_SENSE 13

0 R0603 +/-5%

3

PN2 PN1PN3

R148

*

10K

+/-1%

R0603

R341 25.5K

*

OUT4

OUT3

OUT2

OUT1

+/-5%

150K

R273

*

10K

+/-1%

R0603

BC353

C0603

*

150pF

R0603+/-1%

*

R370 60.4K

BC344 1.5nF

C0603

50V,X7R,+/-10%

+/-5%

R0603

VTT_OUT_LEFT

PN4

MSENSE

R2739

*

10K

+/-1%

R0603

Dummy

50V, NPO, +/-5%

*

R371

20K

+/-1%

R0603

*

R0603+/-1%

*

R385

1.5K R0603

*

OUT3 9

OUT2 9

OUT1 9

*

DS

G

Q45

2N7002

Dummy

+/-5%

Dummy

OUT4 9

R3657

0

R0603

+/-5%

Pop only if 3 phase design is used

VRM_SYS

R396 0

*

R0603

+/-5%

Dummy

R395

2.74K

*

R0603

+/-1%

LOAD_LINE_SELECT

VTT_PWRGD

R411

*

22.1K

+/-1%

R0603

2

LL_ID013

12V_VRM

2

4

5

ATX12V_P1_2X2

1

3

VTT_PWRGD 14

B

BC374

1uF

*

16V, Y5V, +80%/-20%

C0603

CN11

Q46

MMBT3904

SOT23_BEC

E C

BC381

0.1uF

25V, X7R, +/-10%

C0603

Dummy

BC375

0.1uF

25V, X7R, +/-10%

C0603

Dummy

R412

15K

R0603

+/-5%

Dummy

L7

*

Choke Coil 1.2uH

EC14

1800uF

CE50D100H300

16V,+/-20%

5V_SB_SYS

R415

*

10K

+/-5%

R0603

G

5V_SB_SYS

*

R414

2.7K

R0603

*

+/-5%

Dummy

R416

10K

+/-5%

*

*

*

*

R410 300

DS

*

R0603

Dummy

5

1 6

2

R417

10K

+/-5%

R0603

Dummy

BC160

0.1uF

25V, X7R, +/-10%

C0603

EC9

EC7

1800uF

1800uF

*

16V,+/-20%

CE50D100H300

*

Q47

2N7002

43

Q49

MMDT3946

Dummy

LOAD_LINE_SELECT

BC380

0.1uF

*

25V, X7R, +/-10%

*

C0603

Dummy

EC2

1800uF

*

*

16V,+/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

VTT_PWRGD

+/-5%R0603

1

VIN

BC133

4.7uF

*

16V,Y5V,+80%/-20%

C1206

VTT_PWRGD 14

*

A A

FOXCONN PCEG

Title

Voltage Regulator Down 10.1

Size Document Number Re v

5

4

3

2

Date: Sheet

915A01 DDR2

852Tuesd ay, May 18, 2004

1

of

B

5

4

3

2

1

VIN

5V_SB_SYS

D34

B120B

*

*

*

*

D21

1N4148W

OUT18

1211_VIN

16V,Y5V,+80%/-20%

D6

1N4148W

OUT28

1211_VIN

16V,Y5V,+80%/-20%

D8

1N4148W

OUT38

1211_VIN

16V,Y5V,+80%/-20%

D88

1N4148W

Dummy

OUT48

1211_VIN

16V,Y5V,+80%/-20%

R303

*

1

+/-5%

R0805

D33

B120B

D D

16V,Y5V,+80%/-20%

C C

16V,Y5V,+80%/-20%

B B

16V,Y5V,+80%/-20%

A A

16V,Y5V,+80%/-20%

Dummy

Dummy

Dummy

Dummy

0.47uF

C0603

2 1

BC320

0.47uF

C0603

BC124

0.47uF

C0603

BC141

0.47uF

C0603

BC1418

2 1

OUT1

OUT2

OUT3

21

OUT4

5

BC311

21

1uF

C0805

25V,Y5V,+80%/-20%

3

4

CO

BST

VPN5VIN6VREG7BG

BC322

1uF

C0805

BC130

21

1uF

C0805

25V,Y5V,+80%/-20%

3

4

CO

BST

VPN5VIN6VREG7BG

BC119

1uF

C0805

BC139

21

1uF

C0805

25V,Y5V,+80%/-20%

3

4

CO

BST

VPN5VIN6VREG7BG

BC138

1uF

C0805

BC1599

*

1uF

C0805

25V,Y5V,+80%/-20%

3

2

4

CO

BST

PGND

VPN5VIN6VREG7BG

BC1382

1uF

C0805

Dummy

*

2

PGND

*

2

PGND

*

2

PGND

TG

*

*

Dummy

TG

*

*

TG

*

*

TG

*

*

1

8

1

DRN

8

1

DRN

8

1

DRN

8

Dummy

DRN

BC1362

2.2nF

16V,NPO,+/-5%

C0603

U20

SC1211

9

BC321

2.2nF

16V,NPO,+/-5%

C0603

U8

SC1211

9

BC109

2.2nF

16V,NPO,+/-5%

C0603

U10

SC1211

9

BC136

2.2nF

16V,NPO,+/-5%

C0603

U901

SC1211

Dummy

9

BC5111

1nFC0603

50V,X7R,+/-10%

Dummy

R287 2.2 +/-5%

*

AUX1

R293 100

R0603

*

+/-5%

R39

*

BC594

BC5112

1nFC0603

50V,X7R,+/-10%

Dummy

R106 2.2 +/-5%

*

AUX2

R107

+/-5%

*

100

R0603

R40

*

BC596

BC5113

1nFC0603

50V,X7R,+/-10%

Dummy

R112

2.2

*

AUX3

R118

+/-5%

*

100

R0603

R41

*

BC592

*

BC5114

1nFC0603

50V,X7R,+/-10%

Dummy

R2682

2.2

*

AUX4

R1181

AUX4

+/-5%

*

100

R0603

Dummy

R99 0

*

BC593

*

AUX1AUX3

*

AUX2

47nF

C0603

*

25V, X7R, +/-10%

Dummy

0

R0805

+/-5%

47nF

C0603

25V, X7R, +/-10%

Dummy

*

Dummy

Dummy

Dummy

R0805

+/-5%

47nF

C0603

25V, X7R, +/-10%

Dummy

*

R0603

BC314

1nF C0603

50V,X7R,+/-10%

*

0

R0805

+/-5%

47nF

C0603

25V, X7R, +/-10%

Dummy

*

R0603

BC135

C0603

*

50V,X7R,+/-10%

0

R0805

+/-5%

*

+/-5%

R0603

BC149

C0603

*

50V,X7R,+/-10%

G

+/-5%

R0603

BC1492

C0603

*

50V,X7R,+/-10%

G

G

G

G

G

G

G

1nF

VIN

VIN

1nF

VIN

1nF

VIN

DS

DS

DS

Q37

NTD60N02R

DS

Q39

NTD110N02R-1

DS

Q9

NTD60N02R

DS

Q16

NTD110N02R-1

DS

Q13

NTD60N02R

Dummy

DS

Q19

NTD110N02R-1

Q131

NTD60N02R

Dummy

Q199

NTD110N02R-1

Dummy

R29

R30

G

G

R31

10K

R0603

+/-5%

*

*

*

DS

DS

DS

25V, X7R, +/-10%

G

10K

R0603

+/-5%

DS

G

DS

G

25V, X7R, +/-10%

10K

Dummy

R0603

+/-5%

DS

G

G

10K

R0603

+/-5%

G

BC5526

Q121

0.1uF

C0603

NTD60N02R

25V, X7R, +/-10%

Dummy

Dummy

Q200

NTD110N02R-1

Dummy

BC5523

Q36

0.1uF

C0603

NTD60N02R

Dummy

Dummy

Q40

NTD110N02R-1

Q11

NTD60N02R

Dummy

Q15

NTD110N02R-1

DS

Q14

NTD60N02R

25V, X7R, +/-10%

Dummy

DS

Q17

NTD110N02R-1

*

BC204

4.7uF

*

*

16V,Y5V,+80%/-20%

C1206

PN1

PN1

L18

*

IND Coil 400nH

CK165S135

+/-20%

L301

*

R263

*

IND Coil 280nH

1

CK127S110

+/-5%

+/-20%

R0603

400nH and 280nH choke co-lay

*

*

BC1342

4.7uF

*

16V,Y5V,+80%/-20%

C1206

Dummy

BC108

4.7uF

*

16V,Y5V,+80%/-20%

C1206

16V,Y5V,+80%/-20%

BC134

4.7uF

*

C1206

BC5524

0.1uF

C0603

BC5525

0.1uF

C0603

BC273

2.2nF

*

16V,NPO,+/-5%

C0603

PN2

PN2

R111

*

1

+/-5%

R0603

BC146

2.2nF

*

16V,NPO,+/-5%

C0603

PN3

PN3

R114

*

1

+/-5%

R0603

BC145

2.2nF

*

16V,NPO,+/-5%

C0603

PN4

PN4

R1143

*

1

+/-5%

R0603

Dummy

BC1854

2.2nF

*

16V,NPO,+/-5%

C0603

Dummy

Dummy

*

IND Coil 400nH

CK165S135

+/-20%

*

*

IND Coil 400nH

CK165S135

+/-20%

*

L304

*

IND Coil 280nH

CK127S110

+/-20%

Dummy

IND Coil 280nH

CK127S110

+/-20%

Dummy

VCCP

L8

L302

L9

L303

IND Coil 280nH

CK127S110

+/-20%

Dummy

3

UNDER HEATSINK

EC43 560uF

4V, +/-20%

*

CE35D80H200

EC45 560uF

4V,+/-20%

*

CE35D80H200

EC47 560uF

4V,+/-20%

*

CE35D80H200

EC26 560uF

4V,+/-20%

*

CE35D80H200

EC31 560uF

4V,+/-20%

*

CE35D80H200

EC30 560uF

4V,+/-20%

*

CE35D80H200

EC29 560uF

4V,+/-20%

*

CE35D80H200

EC28 560uF

4V,+/-20%

*

CE35D80H200

EC27 560uF

4V,+/-20%

*

CE35D80H200

C2 56 0uF

4V,+/-20%

*

CE35D80H200

Dummy

C1 56 0uF

4V,+/-20%

*

CE35D80H200

VCCP

BC194

68pF

*

50V,NPO,+/-5%

C0603

820uF/1500uF co-layout

*

BC193

68pF

*

50V, NPO, +/-5%

C0603

VCCP

EC37

820uF

*

Dummy

CE35D80H200

6.3V,+/-20%

6.3V,+/-20%

EC24

1500uF

Dummy

CE50D100H300

EC23

EC16

1500uF

Dummy

CE50D100H300

1500uF

*

Dummy

CE50D100H300

6.3V,+/-20%

*

6.3V,+/-20%

De-pop if 4 phase design is used.

--------------------------------Q37, Q29, Q39, Q9, Q11, Q15, Q12,

Q14, Q20, Q121

Title

Voltage Regulator Down 10.1

Size Docum ent Num ber Re v

2

Date: Sheet

FOXCONN PCEG

915A01 DDR2

1

952Tuesday, M ay 18, 2004

B

of

DS

Q29

G

NTD60N02R

DS

Q38

G

NTD110N02R-1

Dummy

DS

Q10

G

NTD60N02R

DS

Q21

G

NTD110N02R-1

Dummy

DS

Q12

G

NTD60N02R

DS

Q20

G

NTD110N02R-1

Dummy

R35

*

4

5

SLP_S45J24,42

Only pop for SC2616

SLP_S3J12,24,34,42

D D

C C

PWRGD_3V7,15,24,32,34

SLP_S3J12,24,34,42

SLP_S45J24,42

R523 0

R0603 +/-5%

R521 100 +/-5%

*

3D3V_SB

R522

*

10K

+/-5%

R0603

Dummy

*

R0603

*

R571

10K

+/-5%

R0603

R532

*

10K

+/-5%

R0603

ACPI_S3

DS

Q55

G

2N7002

D29 1N4148W

R568

0 R0603+/-5%

Dummy

*

These two resistors are

necessary. S3# and S5#

must be tied to 5Vstb to

prevent them floating.

BC520

0.22uF

*

16V, Y5V, +80%/-20%

C0603

4

ACPI_S3

1" from controller

5V_SB_SYS5V_SYS

0.5'' from Controller

21

Dummy

5V_SB_SYS

*

BC524

0.1uF

C0603

Dummy

R572

10K

+/-5%

R0603

*

25V, X7R, +/-10%

*

R570

*

30K

+/-1%

R0603

BC513

1nF

*

50V,X7R,+/-10%

C0603

BC511

1.0uF

C0603

16V,Y5V,+80%/-20%

EC66

100uF

*

16V, +/-20%

CE20D50H110

VDDQEN

VDDQCOMP

12V_SYS

ACPI_S3

BC525

1uF

*

16V,Y5V,+80%/-20%

C0805

3

R545 4.7K

*

Dummy

16V,Y5V,+80%/-20%

Close to PIN9

of SC2616

U33

16

12VCC

4

5VSBY

11

S3#

10

S5#

18

17

12

3

VDDQSBY

SS/EN

COMP

AGND

LGND

VTTSN2VTTO1

NCP5201

19

BC516

1uF

C0805

VDDQIN

THPAD

R0603

5VCC

SGND

VTTO

*

TG

BG

FB

+/-5%

VDDR_IN

9

15

14

13

7

8

1

6

5

*

DDR_PN

VDDQSBY

R5457

0

R0603

*

+/-5%

R520 0 R0805

BC598 0.1uF

DDR_PN

R519 0

R559

VDDQFB

BC508

0.1uF

25V, X7R, +/-10%

C0603

2

5V_SYS

L26

Choke Coil 1.2uH

*

FB L1806 60 Ohm

Q58

G

R530

*

2K

+/-5%

R0603

Dummy

+/-5%

*

C0603

Dummy

*

25V, X7R, +/-10%

R546 0 R0603

*

*

*

+/-5%

R0603

R0603

0

+/-5%

+/-5%

Dummy

NTD60N02R

D S

VDDR_IN

DS

Q57

G

NTD40N03R

*

Choke Coil 2.6uH

DS

Q56

G

NTD40N03R

6.3V, +/-20%

CE50D100H300

Only pop for SC2616

BC509

4.7uF

*

6.3V,X5R,+/-10%

C0805

EC63

1500uF

*

6.3V, +/-20%

CE35D80H200

L3

2 1

Dummy

L27

EC67

3300uF

EC56

470uF

*

16V, +/-20%

CE35D80H200

L4

FB L1806 60 Ohm

Dummy

2 1

BC512

1uF

*

16V,Y5V,+80%/-20%

C0805

16V, +/-20% CE35D80H200

*

*

VTT_DDR

EC68 470uF

10V,+/-20% ce20d50h110

*

*

EC65 22uF

*

EC61

100uF

16V, +/-20%

CE20D50H110

VDDR_IN

BC514

4.7uF

*

16V, Y5V, +80%/-20%

C1206

BC517

4.7uF

6.3V,X5R,+/-10%

C0805

*

EC62

100uF

*

16V, +/-20%

CE20D50H110

R537

470

+/-1%

R0603

1

1D8V_STR

BC501

1uF

*

16V,Y5V,+80%/-20%

C0805

EC64

2200uF

*

6.3V, +/-20%

CE50D100H300

Only pop for SC2616

R560 0

B B

+/-5%

R0603

*

Dummy

*

R553

0

R0603

+/-5%

BC521

10nF

*

50V, X7R, +/-10%

C0603

VDDQFB

Only pop for NCP5201

BC515

0.1uF

*

25V, X7R, +/-10%

C0603

R538

*

16

+/-1%

R0603

A A

R533 0

*

+/-5%

R0603

Place less than

0.25" from Controller

Only pop for NCP5201

VDDR_IN

*

BC504

0.1uF

C0603

25V, X7R, +/-10%

VDDQSBY

Trace to PIN7 must be able to carry 2A

Only pop for SC2616

1D8V_STR

Place close to PIN8 of SC2616

*

BC507

4.7uF

*

10V, Y5V, +80%/-20%

C0805

Dummy

R525

62K

+/-1%

R0603

1D8V_STRVDDR_IN

*

R536

0

R1206

+/-1%

Dummy

BC510

1uF

*

10V, Y5V, +80%/-20%

C0603

Dummy

SUPERGPIO049

SUPERGPIO149

SUPERGPIO249

Value should be tuned

R541

1.2K

+/-1%

R0603

R662

*

*

1.2K

+/-1%

R0603

Dummy

*

R663

1.2K

+/-1%

R0603

Dummy

R664

*

1.2K

+/-1%

R0603

Dummy

FOXCONN PCEG

Title

DDR1 2.6V/1.3V

Size Document Number Re v

5

4

3

2

Date: Sheet

915A01 DDR2

10 52Tuesd ay, May 18, 2004

1

of

B

5

3D3V_SB

R200

*

62

B

3D3V_SB

*

E C

+/-1%

R0603

D14

R

LM431ACM3

A C

R229

499

+/-1%

R0603

B

Q7

MMBT2222A

R199

*

121

R0603

+/-1%

Q34

MMBT2222A

E C

R207

*

402

+/-1%

R0603

R210

*

487

+/-1%

R0603

D D

BC196

22uF

*

C1206

10V,Y5V,+80%/-20%

C C

1D5V_CORE

R230 1K

+/-5%

*

R0603

placed near the LM358M pin 8

2.2V2.5V

*

1.2V

*

4

12V_SYS

BC218

0.1uF

*

25V, X7R, +/-10%

C0603

BC207

0.1uF

25V, X7R, +/-10%

C0603

BC216

0.1uF

25V, X7R, +/-10%

C0603

BC212

0.1uF

*

25V, X7R, +/-10%

C0603

5V_SYS

3

2

5

6

12V_SYS

84

+

-

12V_SYS

84

+

-

U14A

1

LM358M

SOP8JA

U14B

7

LM358M

SOP8JA

3

3D3V_SYS

G

R193 1K +/-5%

R0603

*

G

R227

1K

+/-5%

*

R0603

DS

Q25

IPD09N03LA

DS

Q27

IPD09N03LA

EC25

220uF

*

10V, +/-20%

CE25D60H110

BC192

0.1uF

*

25V, X7R, +/-10%

C0603

BC205

2.2uF

*

16V,Y5V,+80%/-20%

C0805

EC38

*

1000uF

6.3V, +/-20%

CE35D80H200

2

FSB_VTT

BC248

BC228

*

*

4.7uF

C0805

10V, Y5V, +80%/-20%

0.1uF

C0603

25V, X7R, +/-10%

BC229

*

33pF

50V,NPO,+/-5%

C0603

1

L31

Choke COIL 1uH +/-20%

*

BC313

B B

R288

*

0

+/-5%

R0603

BC308

1uF

*

16V, Y5V, +80%/-20%

1D5V_FB

C0603

5

U18

8

PHASE

7

OCSET

6

FB

5

VCC

BOOT

UGATE

GND

LGATE

RT9202

SOP8JA

1

2

3

4

R279

*

5.62K

+/-1%

R0603

A A

5V_SYS

D20

SD103AW

2 1

*

BC302

0.1uF

25V, X7R, +/-10%

C0603

R282 0

*

+/-5%

R0603

4

DS

G

DS

G

EC46

1000uF

*

6.3V, +/-20%

CE35D80H200

Q41

NTD60N02R

L20 Choke Coil 5uH

*

Q42

NTD80N02

EC73

1000uF

*

6.3V, +/-20%

CE35D80H200

Dummy

CK80D160

6.3V, +/-20%

CE50D100H300

Dummy

EC74

1800uF

BC303

*

0.1uF

25V, X7R, +/-10%

C0603

*

*

EC49

1000uF

*

6.3V, +/-20%

CE35D80H200

3

EC53

1000uF

6.3V, +/-20%

CE35D80H200

4.7uF

*

16V,Y5V,+80%/-20%

C0805

BC326

4.7uF

*

16V,Y5V,+80%/-20%

C0805

SUPERGPIO449

SUPERGPIO349

1D5V_CORE

R285

*

105

+/-1%

R0603

1D5V_FB

R281

*

118

+/-1%

R0603

SUPERGPIO4

SUPERGPIO3

Value should be tuned

BC305

10nF

*

50V,X7R,+/-10%

C0603

R665

118

+/-1%

R0603

Dummy

R666

*

118

+/-1%

R0603

Dummy

2

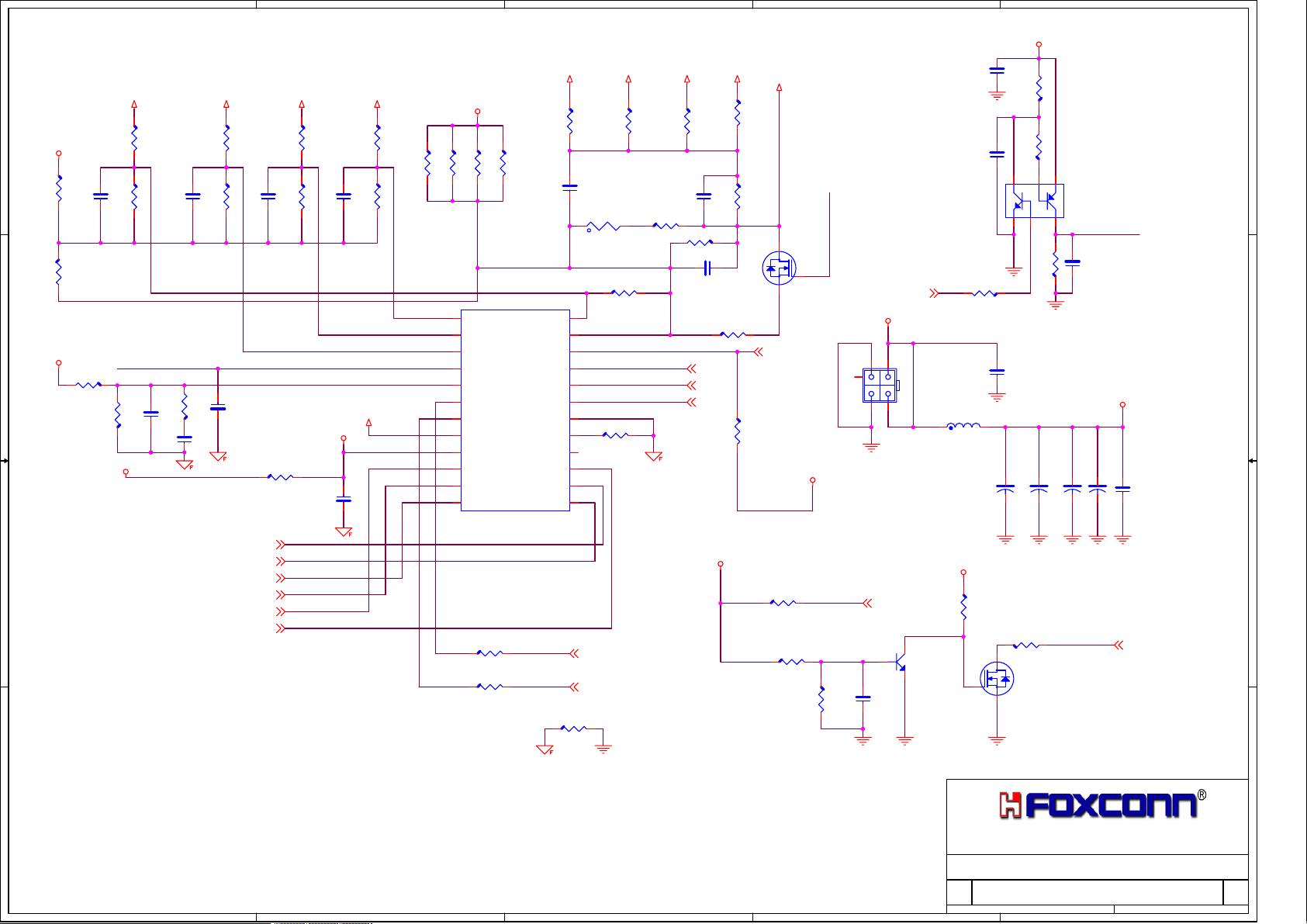

Title

Power 1.5V 1.2V

Size Document Number Re v

Date: Sheet

*

FOXCONN PCEG

915A01 DDR2

11 52Tuesd ay, May 18, 2004

1

B

of

5

4

3

2

1

1D5V_CORE

D D

Changed from 3904 to 2222

by Goldstar 9/15/2003

C C

1

2

E C

SLP_S3J10,24,34,42

1D5V_CORE

D16

3

BAT54C

Q32

MMBT2222A

B

Dummy

R241 3.3K

R226 10K

*

3D3V_SB2D5V_MCH

R235

R231

*

10K

100

R0603

+/-5%

+/-5%

R0603

Dummy

Dummy

1 6

2

+/-5%

*

R0603

*

Dummy

3D3V_SB

R211

*

47K

+/-5%

R0603

Dummy

5

1 6

2

+/-5%

R0603

Dummy

BC215

1uF

*

10V,Y5V,+80%/-20%

C0603

Dummy

16V,Y5V,+80%/-20%

*

43

5

BC224

1uF

C0603

10V,Y5V,+80%/-20%

Dummy

43

Q35

MMDT5551

Dummy

*

Q30

R202

10K

+/-5%

R0603

Dummy

3D3V_SYS

MMDT5551

Dummy

SLP_S3J 10,24,34,42

BC201

4.7uF

*

C1206

R321

*

100

+/-5%

R0603

3D3V_SYS

BC199

0.1uF

*

C0603

25V, X7R, +/-10%

U13 MIC5 205-2.5BM5

1

VIN

3

SHDN

BYPASS/ADJ

GND

2

VOUT

5V_SYS

5

4

*

BC210

0.1uF

*

25V, X7R, +/-10%

C0603

Dummy

2D5V_MCH

2.5V/100mA

BC267

0.1uF

25V, X7R, +/-10%

C0603

BC209

*

4.7uF

C1206

16V,Y5V,+80%/-20%

Add by Goldstar 9/15/2003

U11A

84

LM393

3

B B

A A

5V_SYS

BC177

0.1uF

*

25V, X7R, +/-10%

C0603

Dummy

placed near the LM393 pin 8

25V, X7R, +/-10%

BC181

0.1uF

C0603

Dummy

5V_SYS

7.5K

R0603

+/-1%

Dummy

R144

680

+/-1%

*

R0603

Dummy

R145 130

R157

*

1K

+/-1%

R0603

Dummy

RT1

*

6.8K

T

+/-1%

*

R0603

Dummy

R173

*

1K

+/-1%

R0603

Dummy

R177

*

499

+/-1%

R0603

Dummy

5

6

U11B

84

LM393

Dummy

+

7

-

R176

*

2

R0603

*

+/-1%

Dummy

Dummy

+

1

-

PROCHOTJ 13

Q22

B

MMBT3904

Dummy

E C

FOXCONN PCEG

VR Thermal Monitor Circuit

5

4

3

2

Title

2.5V_MCH

Size Document Number Re v

Date: Sheet

915A01 DDR2

12 52Tuesd ay, May 18, 2004

1

of

B

5

U16B

HDJ0

HDJ1

HDJ2

HDJ3

D D

C C

TBD

Pin D23

CRB 0.7: test point TP_VCCPLL

Pin AM5

CRB 0.7: test point TP_VID6

B B

A A

HDJ4

HDJ5

HDJ6

HDJ7

HDJ8

HDJ9

HDJ10

HDJ11

HDJ12

HDJ13

HDJ14

HDJ15

HDBIJ015

HDSTBNJ015

HDSTBPJ015

HDJ16

HDJ17

HDJ18

HDJ19

HDJ20

HDJ21

HDJ22

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

HDJ30

HDJ31

HDBIJ115

HDSTBNJ115

HDSTBPJ115

SMIJ24

A20MJ24

FERRJ24

INTR24

NMI24

IGNNEJ24

STPCLKJ24

HVCCA14

HVSSA14

TP33

HVCCIOPLL14

VID042,49

VID142,49

VID242,49

VID342,49

VID442,49

VID542,49

TP4

CK_200M_P_CPU7

CK_200M_N_CPU7

SKTOCCJ34,49

THERMDA43

THERMDC43

TP3

TP2

VCC_SENSE8

VSS_SENSE8

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

HDBIJ0

HDBIJ1 HDBIJ3

TP_VCCPLL

1

TP_VID6

1

SKTOCCJ

TP_VCCSENSE

1

TP_VSSSENSE

1

5

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1#

CPU Prescott_Socket_LGA775_Rev1.0

VID0

VID1

VID2

VID3

VID4

VID5

2 OF 7

G16

D32#

E15

D33#

E16

D34#

G18

D35#

G17

D36#

F17

D37#

F18

D38#

E18

D39#

E19

D40#

F20

D41#

E21

D42#

F21

D43#

G21

D44#

E22

D45#

D22

D46#

G22

D47#

D19

DBI2#

G20

DSTBN2#

G19

DSTBP2#

D20

D48#

D17

D49#

A14

D50#

C15

D51#

C14

D52#

B15

D53#

C18

D54#

B16

D55#

A17

D56#

B18

D57#

C21

D58#

B21

D59#

B19

D60#

A19

D61#

A22

D62#

B22

D63#

C20

DBI3#

A16

DSTBN3#

C17

DSTBP3#

3 OF 7

U16C

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

D23

RSVD5

C23

VCCIOPLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

VID6

F28

BCLK0

G28

BCLK1

AE8

SKTOCC#

AL1

THERMDA

AK1

THERMDC

AN3

VCCSENSE

AN4

VSSSENSE

AN5

VCC_MB_REG

AN6

VSS_MB_REG

Changed pin name

from RSV

F29

RSVD9

CPU Prescott_Socket_LGA775_Rev1.0

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

RSVD10

RSVD11

RSVD12

PWRGOOD

PROCHOT#

THERMTRIP#

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

GTLREF1

RSVD24

BOOTSELECT

SLP#

COMP0

COMP1

COMP2

COMP3

COMP4

LL_ID0

LL_ID1

HDJ32

HDJ33

HDJ34

HDJ35

HDJ36

HDJ37

HDJ38

HDJ39

HDJ40

HDJ41

HDJ42

HDJ43

HDJ44

HDJ45

HDJ46

HDJ47

HDBIJ2

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

HDJ62

HDJ63

4

HDJ[63..0]

HDBIJ2 15

HDSTBNJ2 15

HDSTBPJ2 15

HDBIJ3 15

HDSTBNJ3 15

HDSTBPJ3 15

TBD

Pin AL2 PROCHOT#

CRB 0.7: pull up to VTT_OUT_RIGHT

DG/611A: example VR thermal monitor circuit

TESTHI_0

F26

TESTHI_1

W3

TESTHI_11

P1

TESTHI_12

W2

F25

G25

G27

G26

G24

TESTHI_2_7

F24

RSVD_AK6

AK6

RSVD_G6

G6

L2

AH2

N1

AL2

M2

HCOMP0

A13

HCOMP1

T1

HCOMP2

G2

HCOMP3

R1

N5

AE6

TBD

C9

Pin N5 ~ Pin J3

G10

CRB 0.7: connections ok?

D16

A20

TP_RSVD_CPU_N5

E23

TP_RSVD_CPU_AE6

E24

TP_RSVD_CPU_C9

F23

TP_RSVD_CPU_G10

H2

TP_RSVD_CPU_ D16

J2

TP_RSVD_CPU_A20

J3

CPU_BOOT

Y1

LL_ID0

V2

TP_LL_ID1

AA2

4

HDJ[63..0] 15

TBD

Pin AK6, G6

refer to CRB 0.7

CPUSLPJ 24

CPU_PWRG 24

PROCHOTJ 12

THERMTRIPJ 24

TP35

1

TP34

1

TP32

1

TP13

1

TP14

1

TP11

1

LL_ID0 8

1

TP8

HAJ[31..3]15

HAJ[31..3]15

HREQJ[4..0]15

HAJ[31..3]

VTT_OUT_RIGHT

R325

*

49.9

+/-1%

R0603

R326

*

100

+/-1%

R0603

VTT_OUT_RIGHT

VTT_OUT_LEFT

HCOMP0

HCOMP1

3

HAJ[31..3]

HAJ3

HAJ4

HAJ5

HAJ6

HAJ7

HAJ8

HAJ9

HAJ10

HAJ11

HAJ12

HAJ13

HAJ14

HAJ15

HAJ16

HREQJ0

HREQJ1

HREQJ2

HREQJ3

HADSTBJ015

HPCREQJ15

HAJ17

HAJ18

HAJ19

HAJ20

HAJ21

HAJ22

HAJ23

HAJ24

HAJ25

HAJ26

HAJ27

HAJ28

HAJ29

HAJ30

HAJ31

TP17

TP12

TP9

TP1

HADSTBJ115

GTLREF voltage should be 0.67*FSB_VTT

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin

caps should be placed near CPU pin

BC341

*

1.0uF

10V,Y5V,+80%/-20%

C0603

R340 62

*

R319 1K

*

R332 62

*

10 mils width

7 mils spacing

R312 100

*

R330 100

*

R268 60.4 +/-1%R0603

R331 60.4 +/-1%R0603

3

HREQJ4

TP_LAG775_PIN_AH4

1

TP_LAG775_PIN_AH5

1

TP_LAG775_PIN_AJ5

1

TP_LAG775_PIN_AJ6

1

BC340

*

220pF

50V, X7R, +/-20%

C0603

Place at CPU end of route

R0603

+/-5%

R0603

+/-5%

Dummy

R0603

+/-5%

Dummy

HCOMP2

R0603

+/-1%

+/-1%

R0603

HCOMP3

*

*

10 mils width

7 mils spacing

U16A

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

N4

RSVD1

P5

RSVD2

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

G5

PCREQ#

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

AC4

RSVD3

AE4

RSVD4

AD5

ADSTB1#

CPU Prescott_Socket_LGA775_Rev1.0

R315 0 R0603

*

HIERRJ

CPU_BOOT

RSVD_AK6

TESTHI08

TESTHI09

TESTHI10

+/-5%

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

EDRDY#

MCERR#

AP0#

AP1#

BR0#

DP0#

DP1#

DP2#

DP3#

GTLREF

RESET#

RS0#

RS1#

RS2#

1 OF 7

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

F2

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

G23

B3

F5

A3

1

1

2

2

3

3

4

4

HGTLREF

2

TP_RSPJ

HIERRJ

TP_BINITJ

TP_MCERRJ

TP_APJ0

TP_APJ1

HBR0J

TESTHI_8

TESTHI_9

TESTHI_10

TP_DPJ0

TP_DPJ1

TP_DPJ2

TP_DPJ3

HGTLREF

HBR0J

TBD

CRB 0.7: 220 ohm, 5%

DG 0.51: 62 ohm, 5%

FSB_VTT

2

1

HADSJ 15

HBNRJ 15

HITJ 15

1

TP15

HBPRIJ 15

HDBSYJ 15

HDRDYJ 15

HITMJ 15

INITJ 24

HLOCKJ 15

HTRDYJ 15

1

TP7

HDEFERJ 15

HEDRDYJ 15

1

TP16

1

TP6

1

TP10

HBR0J 15

1

TP31

1

TP29

1

TP30

1

TP28

HCPURSTJ 15

HRSJ0 15

HRSJ1 15

HRSJ2 15

R209 62

*

R223 62

*

VTT_OUT_LEFT

R310 62

Place at CPU end of route

R328 100 R0603+/-5%

R317 62

R313 62

R311 62

R316 62

R329 62

R318 62

R314 62

R357 62

GTLREF_SEL14

TESTHI_0

R0603

+/-5%

+/-5%

Place at CPU end of route

*

R0603

TESTHI_2_7

+/-5%

*

+/-5%

*

+/-5%

*

+/-5%

*

+/-5%

*

+/-5%

*

+/-5%

*

+/-5%

*

+/-5%

*

R0603

R0603

R0603

R0603

R0603

R0603

R0603

R0603

Dummy

R0603

TESTHI_0

HBR0J

CPU_PWRG

TESTHI_1

TESTHI_8

TESTHI_9

TESTHI_10

TESTHI_11

TESTHI_12

RSVD_G6

HCPURSTJ

VIN

VCCP

R228

10K

+/-5%

R0603

Dummy

G

G

*

DS

3D3V_SYS

*

DS

R248

619

+/-1%

R0603

Dummy

Q8

2N7002

Dummy

MCH_GTLREF

R289

249

+/-1%

R0603

Dummy

Q31

2N7002

Dummy

BC342

22pF

*

50V,NPO,+/-5%

C0603

*

FOXCONN PCEG

Title

CPU-HOST

Size Document Number Re v

Date: Sheet

915A01 DDR2

13 52Tuesd ay, May 18, 2004

1

R588

*

110

+/-1%

R0603

Dummy

R590

*

62

+/-1%

R0603

Dummy

B

of

5

U16D

HTCK

HTCK

HTDI

HTDO

HTMS

HTRSTJ

D D

C C

B B

HBPM0J

HBPM1J

HBPM2J

HBPM3J

HBPM4J

HBPM5J

ICH_SYS_RSTJ7,24,35,49

FSBSEL07,15

FSBSEL17,15

FSBSEL27,15

VTT_OUT_RIGHT

*

HVCCIOPLL13

ICH_SYS_RSTJ

Place BPM termination near CPU

R336 49.9 +/-1%

R363 49.9 +/-1%

*

R334 49.9 +/-1%

*

R359 49.9 +/-1%

*

R338 49.9 +/-1%

*

R337 49.9 +/-1%

*

*

R335

49.9

+/-1%

R0603

place TRSTJ termination anywhere on route

L0805 10uH +/-10%

HVCCIOPLL

*

HVCCA13

HVSSA13

VCCP VCCP

BC254 10uF

C1206 6.3V,X5R,+/-10%

BC245 10uF

C1206 6.3V,X5R,+/-10%

A A

*

*

BC271 10uF

C1206 6.3V,X5R,+/-10%

C1206 6.3V,X5R,+/-10%

BC262 10uF

C1206 6.3V,X5R,+/-10%

*

*

*

AE1

HTDI

AD1

HTDO

AF1

HTMS

AC1

HTRSTJ

AG1

HBPM0J

HBPM1J

HBPM2J

HBPM3J

HBPM4J

HBPM5J

FSBSEL0

FSBSEL1

FSBSEL2

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

R361

*

*

49.9

+/-1%

R0603

FSB_VTT

L11

0805

+/-10%

BC211

1uF

16V, Y5V, +80%/-20%

C0603

BC278 10uF

5

HVCCA

HVSSA

C1206 6.3V,X5R,+/-10%

*

BC291 10uF

*

C1206 6.3V,X5R,+/-10%

*

HBPM5J

HBPM4J

HBPM3J

HBPM2J

HBPM1J

HBPM0J

BC244 10uF

4 OF 7

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLKOUT0

ITPCLKOUT1

BSEL0

BSEL1

BSEL2

VTTPWRGD

VTT_OUT1

VTT_OUT2

CPU Prescott_Socket_LGA775_Rev1.0

HBPM5J

HBPM4J

HBPM3J

HBPM2J

HBPM1J

HBPM0J

R360

R358

*

49.9

49.9

+/-1%

+/-1%

R0603

R0603

PLL Supply Filter

12

12

Notes:

1. Cap. should be within 600 mils of the VCCA and VSSA pins

2. VCCA route should be parallel and next to VSSA route

3. Min. 12 mils trace from the filter to the processor pins

4. The inductors should be close to the cap.

R221

0

+/-5%

R0603

Place these caps. inside CPU socket

10uF/SDK caps. co-layout

BC261 10uF

C1206 6.3V,X5R,+/-10%

BC253 10uF

C1206 6.3V,X5R,+/-10%

*

*

A29

VTT1

B25

VTT2

B29

VTT3

B30

VTT4

C29

VTT5

A26

VTT6

B27

VTT7

C28

VTT8

A25

VTT9

A28

VTT10

A27

VTT11

C30

VTT12

A30

VTT13

C25

VTT14

C26

VTT15

C27

VTT16

B26

VTT17

D27

VTT18

D28

VTT19

D25

VTT20

D26

VTT21

B28

VTT22

D29

VTT23

D30

VTT24

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

VTT_SEL

BC348

0.1uF

*

25V, X7R, +/-10%

R362

*

49.9

+/-1%

R0603

place TCK/TDI/TMS terminations near CPU within 1.5 inch

HTRSTJ

125mA125mA

L10

L0805 10uH +/-10%

0805

+/-10%

ESL <= 5 nH, ESR < 0.3 ohm

C1206 6.3V,X5R,+/-10%

BC270 10uF

C1206 6.3V,X5R,+/-10%

*

C0603

place TDO termination near XDP connector

HTDO

HTDI

HTMS

HTCK

EC34

33uF

*

35V, +/-20%

CE20D50H110

C1206 6.3V,X5R,+/-10%

BC290 10uF

C1206 6.3V,X5R,+/-10%*BC277 10uF

*

*

4

VTT_OUT_RIGHT

R203 1K

VTT_OUT_RIGHT

*

BC243 10uF

BC252 10uF

C1206 6.3V,X5R,+/-10%

BC260 10uF

C1206 6.3V,X5R,+/-10%

*

*

4

R320

*

0

+/-5%

R0603

Dummy

*

R0603

Dummy

BC347

0.1uF

25V, X7R, +/-10%

C0603

BC269 10uF

C1206 6.3V,X5R,+/-10%

BC276 10uF

C1206 6.3V,X5R,+/-10%

*

*

+/-5%

C1206 6.3V,X5R,+/-10%

BC289 10uF

*

FSB_VTT

VTT_PWRGD 8

VTT_OUT_RIGHT

VTT_OUT_LEFT

3D3V_SYS

TC2

100uF

*

CTD

2.5V,+/-20%

3

VCCP VCCP VCCP

TC1

100uF

*

CTD

Dummy

Dummy

2.5V,+/-20%

U16E

AG22

VCCP1

K29

VCCP2

AM26

VCCP3

AL8

VCCP4

AE12

VCCP5

AE11

VCCP6

W23

VCCP7

W24

VCCP8

W25

VCCP9

T25

VCCP10

Y28

VCCP11

AL18

VCCP12

AC25

VCCP13

W30

VCCP14

Y30

VCCP15

AN14

VCCP16

AD28

VCCP17

Y26

VCCP18

AC29

VCCP19

M29

VCCP20

U24

VCCP21

J23

VCCP22

AC27

VCCP23

AM18

VCCP24

AM19

VCCP25

AB8

VCCP26

AC26

VCCP27

J8

VCCP28

J28

VCCP29

T30

VCCP30

AM9

VCCP31

AF15

VCCP32

AC8

VCCP33

AE14

VCCP34

N23

VCCP35

W29

VCCP36

U29

VCCP37

AC24

VCCP38

AC23

VCCP39

Y23

VCCP40

AN26

VCCP41

AN25

VCCP42

AN11

VCCP43

AN18

VCCP44

Y27

VCCP45

Y25

VCCP46

AD24

VCCP47

AE23

VCCP48

AE22

VCCP49

AN19

VCCP50

V8

VCCP51

K8

VCCP52

AE21

VCCP53

AM30

VCCP54

AE19

VCCP55

AC30

VCCP56

AE15

VCCP57

M30

VCCP58

K27

VCCP59

M24

VCCP60

AN21

VCCP61

T8

VCCP62

AC28

VCCP63

N25

VCCP64

AE18

VCCP65

W26

VCCP66

AD25

VCCP67

M8

VCCP68

N30

VCCP69

AD26

VCCP70

AJ26

VCCP71

AM29

VCCP72

M25

VCCP73

M26

VCCP74

L8

VCCP75

U25

VCCP76

Y8

VCCP77

AJ12

VCCP78

AD27

VCCP79

U23

VCCP80

M23

VCCP81

AG29

VCCP82

N27

VCCP83

AM22

VCCP84

U28

VCCP85

K28

VCCP86

U8

VCCP87

AK18

VCCP88

AD8

VCCP89

K24

VCCP90

AH28

VCCP91

AH21

VCCP92

CPU Prescott_Socket_LGA775_Rev1.0

5 OF 7

AK12

VCCP93

AH22

VCCP94

T29

VCCP95

AM14

VCCP96

AM25

VCCP97

AE9

VCCP98

Y29

VCCP99

AK25

VCCP100

AK19

VCCP101

AG15

VCCP102

J22

VCCP103

T24

VCCP104

AG21

VCCP105

AM21

VCCP106

J25

VCCP107

U30

VCCP108

AL21

VCCP109

AG25

VCCP110

AJ18

VCCP111

J19

VCCP112

AH30

VCCP113

J15

VCCP114

AG12

VCCP115

AJ22

VCCP116

J20

VCCP117

AH18

VCCP118

AH26

VCCP119

W27

VCCP120

AL25

VCCP121

AN8

VCCP122

AH14

VCCP123

U27

VCCP124

T23

VCCP125

R8

VCCP126

AK22

VCCP127

AN29

VCCP128

AG11

VCCP129

AK26

VCCP130

J10

VCCP131

AJ15

VCCP132

AG26

VCCP133

AN9

VCCP134

AH15

VCCP135

AF18

VCCP136

AL15

VCCP137

J26

VCCP138

J18

VCCP139

J21

VCCP140

AG27

VCCP141

AK15

VCCP142

AF11

VCCP143

AD23

VCCP144

AM15

VCCP145

AF8

VCCP146

AK21

VCCP147

AG30

VCCP148

AJ21

VCCP149

AM11

VCCP150

AL11

VCCP151

AJ11

VCCP152

K30

VCCP153

AL14

VCCP154

AN30

VCCP155

AH25

VCCP156

AL12

VCCP157

AJ9

VCCP158

AK11

VCCP159

AG14

VCCP160

N29

VCCP161

AL30

VCCP162

AJ25

VCCP163

AH9

VCCP164

J29

VCCP165

J11

VCCP166

K25

VCCP167

P8

VCCP168

K23

VCCP169

AL19

VCCP170

AM8

VCCP171

T26

VCCP172

N28

VCCP173

AH12

VCCP174

AL22

VCCP175

AN15

VCCP176

AJ8

VCCP177

U26

VCCP178

AJ19

VCCP179

T27

VCCP180

AK8

VCCP181

AN12

VCCP182

AG9

VCCP183

N26

VCCP184

3

GTLREF_SEL

2

U16F

AF9

VCCP185

AF22

VCCP186

AH11

VCCP187

AJ14

VCCP188

AH19

VCCP189

AH29

VCCP190

AH27

VCCP191

AG28

VCCP192

AL26

VCCP193

AM12

VCCP194

J24

VCCP195

J13

VCCP196

T28

VCCP197

W28

VCCP198

J12

VCCP199

J27

VCCP200

AG19

VCCP201

AL9

VCCP202

AD30

VCCP203

AF21

VCCP204

Y24

VCCP205

AK14

VCCP206

J9

VCCP207

M27

VCCP208

AF14

VCCP209

J30

VCCP210

AG18

VCCP211

AA8

VCCP212

AG8

VCCP213

AL29

VCCP214

AD29

VCCP215

W8

VCCP216

AH8

VCCP217

N24

VCCP218

AN22

VCCP219

J14

VCCP220

K26

VCCP221

AF19

VCCP222

N8

VCCP223

AF12

VCCP224

M28

VCCP225

AK9

VCCP226

C10

VSS1

D12

VSS2

AM7

VID7

C24

VSS4

K2

VSS5

C22

VSS6

AN1

VSS7

B14

VSS8

K7

VSS9

AE16

VSS10

B11

VSS11

AL10

VSS12

AK23

VSS13

H12

VSS14

AF7

VSS15

AK7

VSS16

H7

VSS17

E14

VSS18

L28

VSS19

Y5

VSS20

E11

VSS21

AL16

VSS22

AL24

VSS23

AK13

VSS24

AL3

VSS25

D21

VSS26

AL20

VSS27

D18

VSS28

AN2

VSS29

AK16

VSS30

AK20

VSS31

AM27

VSS32

AM1

VSS33

AL13

VSS34

AL17

VSS35

C19

VSS36

E28

VSS37

AH7

VSS38

AK30

VSS39

D24

VSS40

CPU Prescott_Socket_LGA775_Rev1.0

GTLREF_SEL 13

6 OF 7

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

GTLREF_SEL

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

2

AL23

A12

L25

J7

AE28

AE29

K5

J4

AE30

AN20

AF10

AE24

AM24

AN23

H9

H8

H13

AC6

AC7

AH6

C16

AM16

AE25

AE27

AJ28

AJ7

F19

AH13

AD7

AH16

AK17

E17

AH17

AH20

AE5

AH23

AE7

AM13

AH24

AJ30

AJ10

AF3

AK5

AJ16

AF6

AK29

AJ17

F22

AH3

AK10

AM10

F16

AJ23

F13

AG7

F10

L26

AD4

H11

L24

L23

AM23

A15

AH10

H29

B24

L3

H27

A21

AE2

AJ29

A24

AK27

AK28

B20

AM20

H26

B17

H25

H24

AA3

AA7

H23

AA6

H10

1

GTLREF_SEL

U16G

H22

VSS126

H21

VSS127

H20

VSS128

H19

VSS129

H18

VSS130

AB7

VSS131

H17

VSS132

AJ24

VSS133

AM17

VSS134

AC3

VSS135

H14

VSS136

P28

VSS137

V6

VSS138

AK2

VSS139

P27

VSS140

P26

VSS141

AM28

VSS142

AJ13

VSS143

W4

VSS144

P25

VSS145

AJ20

VSS146

W7

VSS147

P23

VSS148

AG13

VSS149

AG16

VSS150

AG17

VSS151

C7

VSS152

Y2

VSS153

L30

VSS154

L29

VSS155

D15

VSS156

AL27

VSS157

Y7

VSS158

L27

VSS159

AA29

VSS160

N6

VSS161

N7

VSS162

AA28

VSS163

AN13

VSS164

AA27

VSS165

AA26

VSS166

P4

VSS167

AA25

VSS168

AA24

VSS169

P7

VSS170

E26

VSS171

V30

VSS172

R2

VSS173

V29

VSS174

V28

VSS175

R5

VSS176

V27

VSS177

R7

VSS178

E20

VSS179

AN10

VSS180

V25

VSS181

T3

VSS182

V24

VSS183

V23

VSS184

T6

VSS185

AL7

VSS186

E25

VSS187

U1

VSS188

R29

VSS189

R28

VSS190

R27

VSS191

R26

VSS192

R25

VSS193

U7

VSS194

R24

VSS195

R23

VSS196

P30

VSS197

V3

VSS198

P29

VSS199

AF16

VSS200

AE10

VSS201

AF13

VSS202

H6

VSS203

A18

VSS204

A2

VSS205

E2

VSS206

D9

VSS207

C4

VSS208

A6

VSS209

D6

VSS210

CPU Prescott_Socket_LGA775_Rev1.0

7 OF 7

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VID_SELECT

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

RSVD25

RSVD26

COMP5

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

D5

A9

D3

B1

B5

B8

AJ4

AE26

AH1

E29

V7

C13

AK24

AB30

L6

L7

AB29

M1

AB28

E8

AG20

AN17

AB27

AB26

AN16

M7

AB25

AB24

AB23

N3

AA30

F4

AG10

AE13

AF30

H28

F7

AF29

AF28

G1

AF27

AF26

AF25

AN28

AN27

AF24

AF23

AG24

AF17

AN24

H3

AN7

P24

AE20

AE17

E27

T7

R30

AJ27

AB1

AM4

V26

AA23

AL28

AF20

AG23

V1

F6

T2

Y3

AE3

W1

E7

B13

D14

E6

D1

E5

FOXCONN PCEG

Title

LGA775 -2

Size Document Number Re v

Date: Sheet

915A01 DDR2

14 52Tuesd ay, May 18, 2004

1

of

B

5

HAJ[31..3]13

D D

HREQJ[4..0]13

C C

B B