Formenti f19 schematic

F 19 SERVICE MANUAL

THIS DOCUMENT IS A PROPERTY

OF INDUSTRIE FORMENTI ITALIA

NO AUTHORIZED MODIFICATIONS

ARE PERMITTED.

CREATED BY E.G.

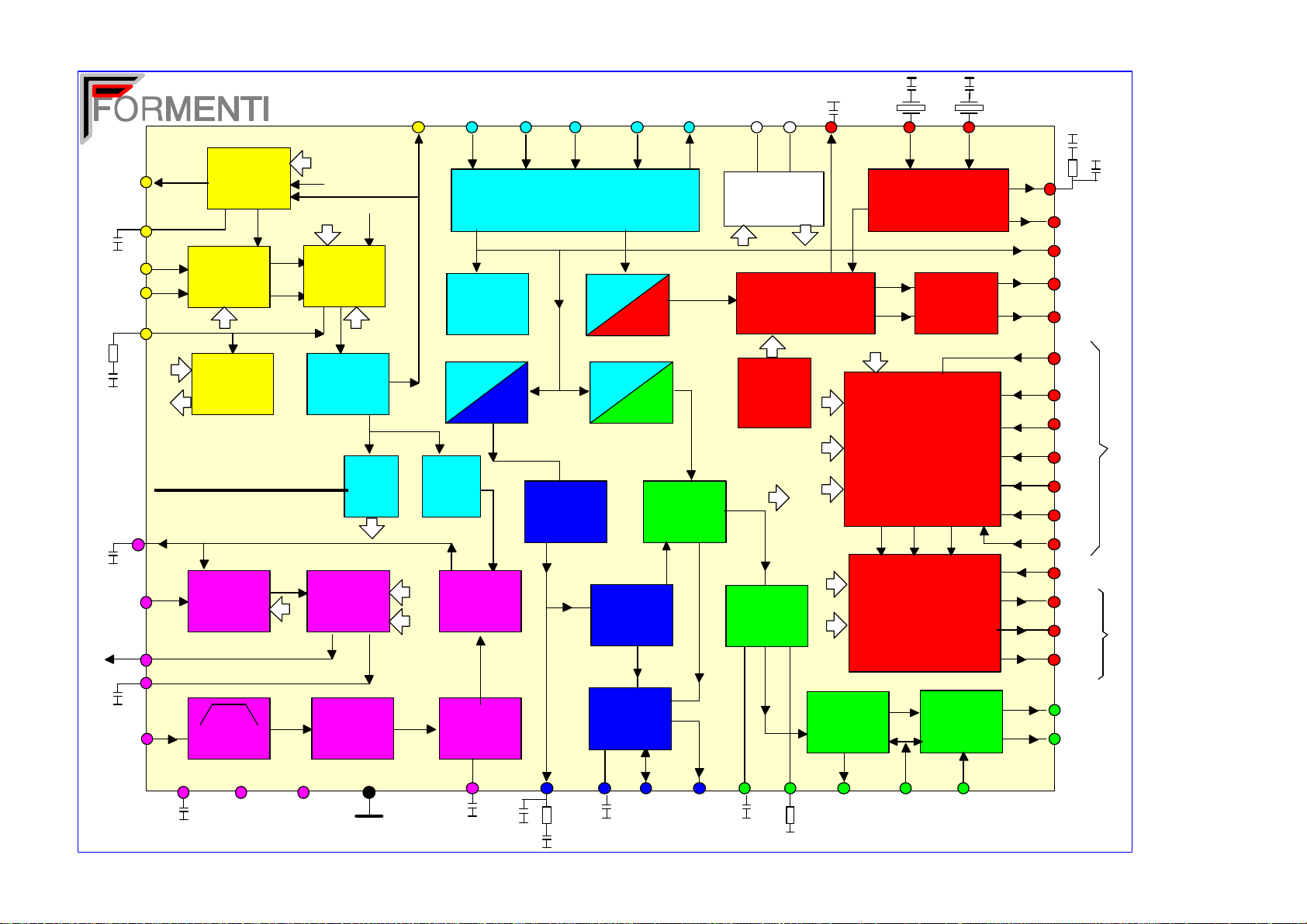

There are two different types of F19 chassis that are equipped with two

From the point of view of the application on the F19 chassis the two type of

Even if the two devices are non interchangeable the two chassis

As the specifications of the two devices are the same and the first version of

different microcontroller.

These microcontroller are known as ETT having a code SAA5297A and

PAINTER with a code number SAA5553.

microcontroller are substantially having the same performances, the same pinout , the same firmware but they are not interchangeable as the power supply

are different.

In case of SAA5297A the power supply is 5 V for the SAA5553 is 3.3 V.

can be interchanged as the in/out interface are exactly the same.

the chassis was equipped with the SAA5297A , in this document the

characteristics of it are very much detailed meanwhile there is a very short

description (as an addendum at the end) for the SAA5553.

F19 CHASSIS DESCRIPTION

Summary

The F19 is a chassis suitable to drive CRT having both 4 by 3 and 16 to 9 aspect

ratio and dimension from 25" up to 34".

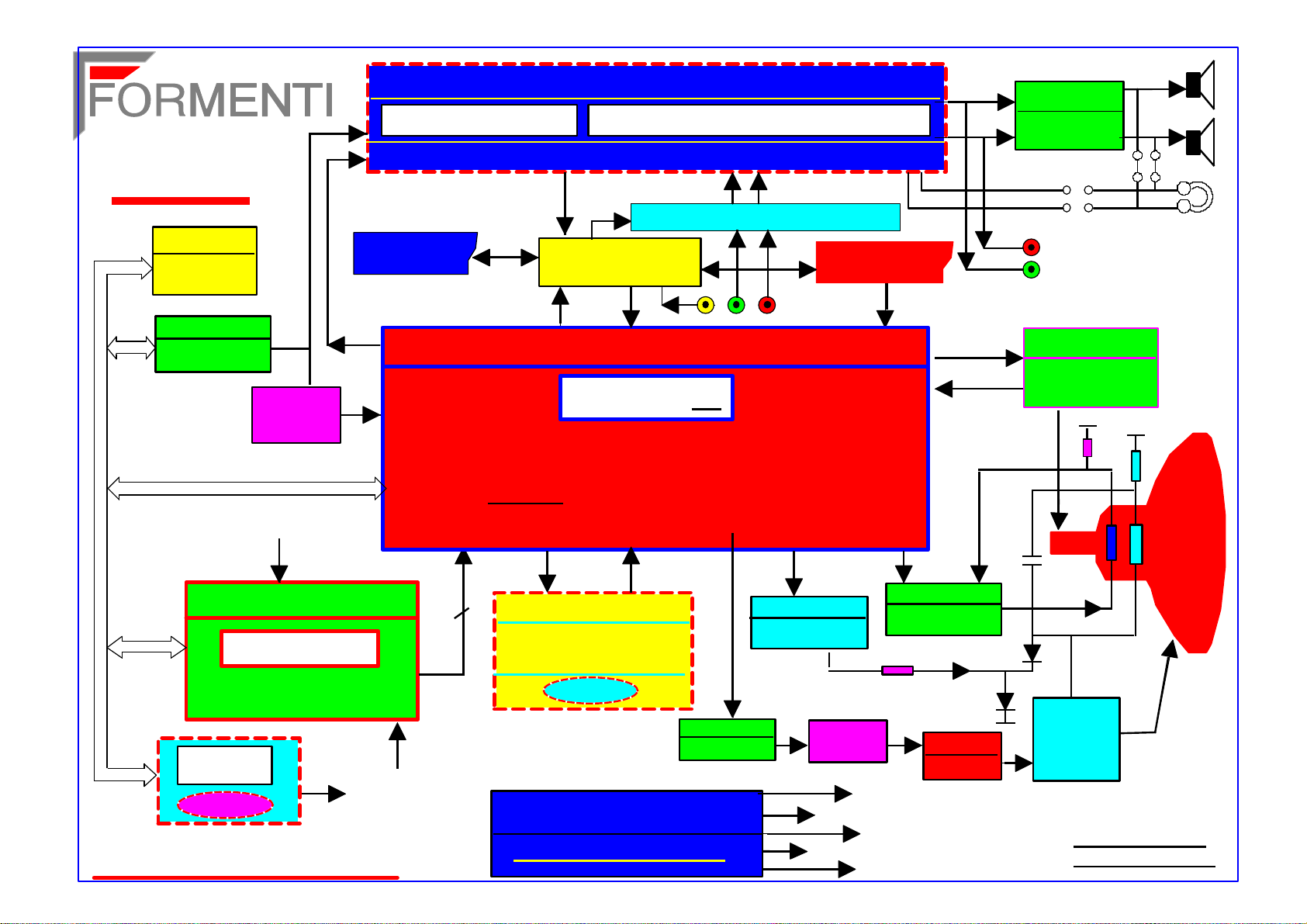

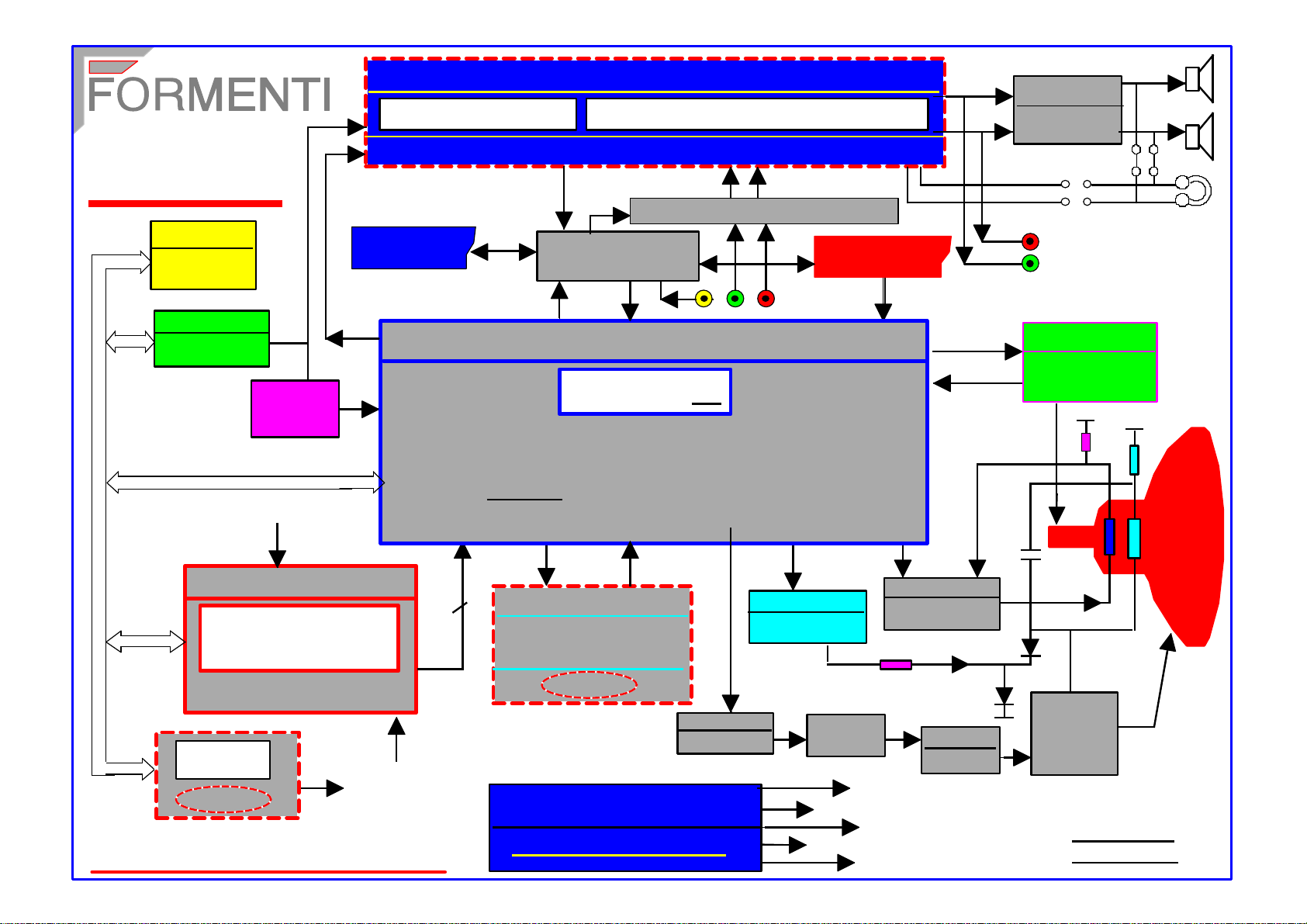

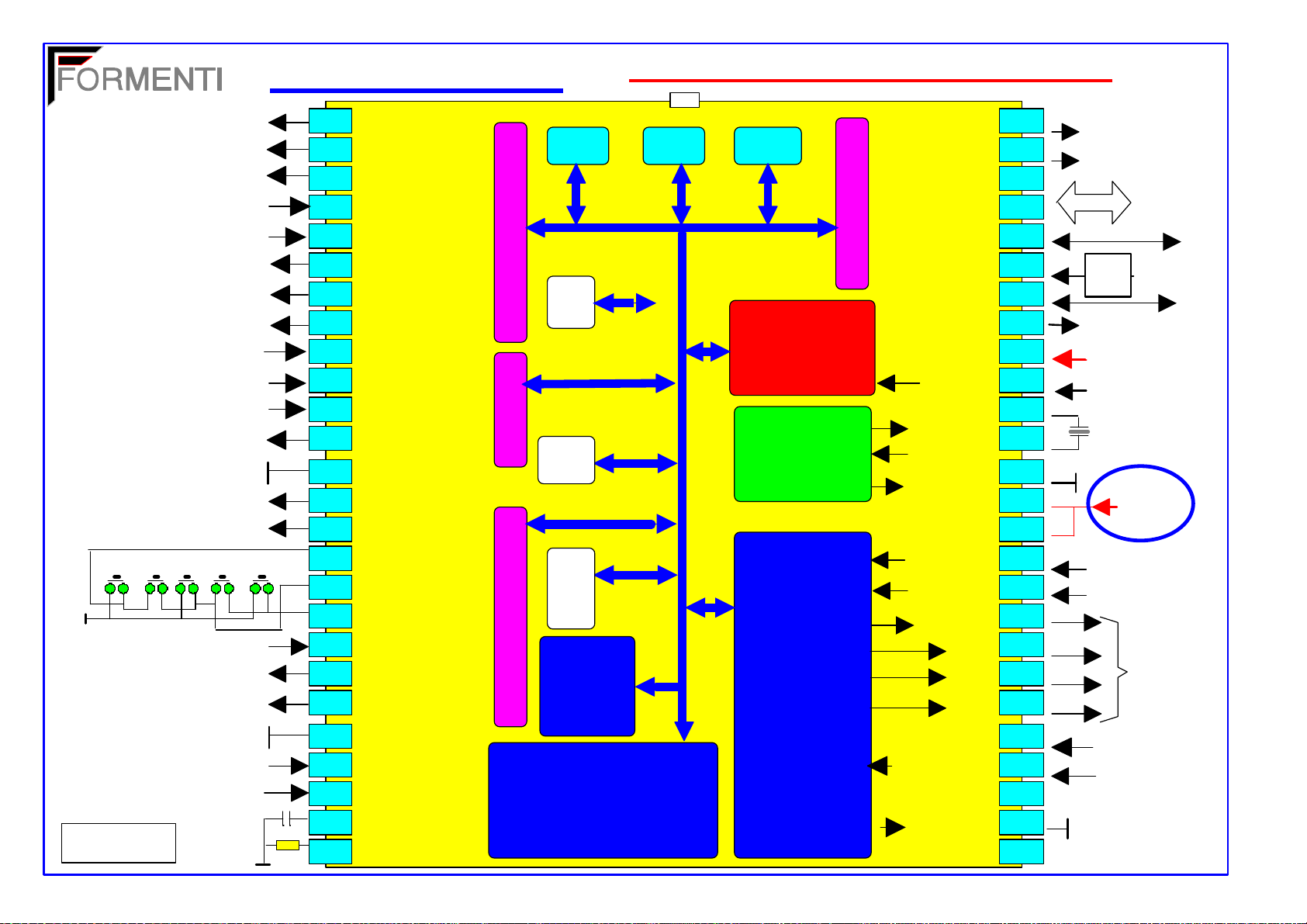

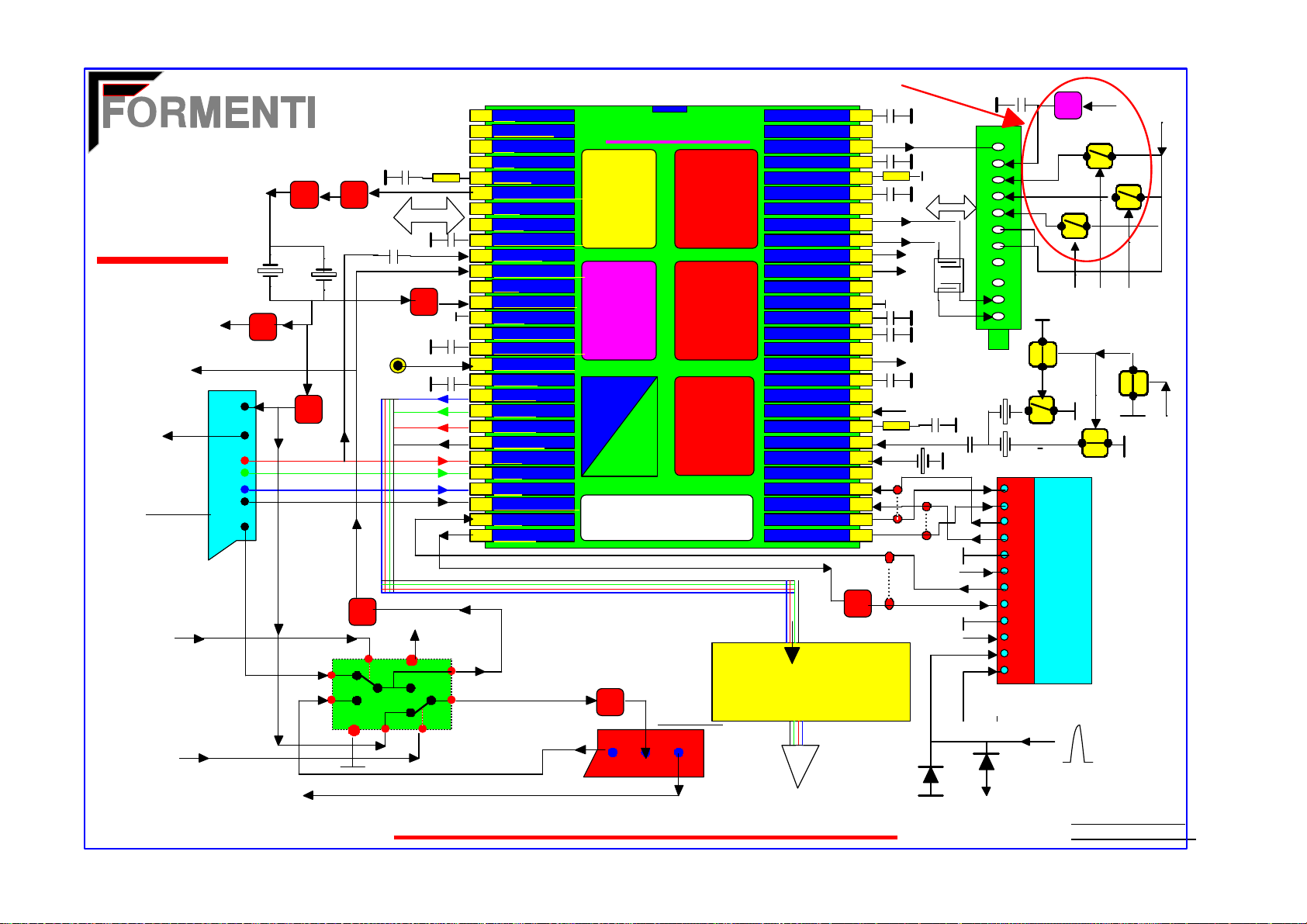

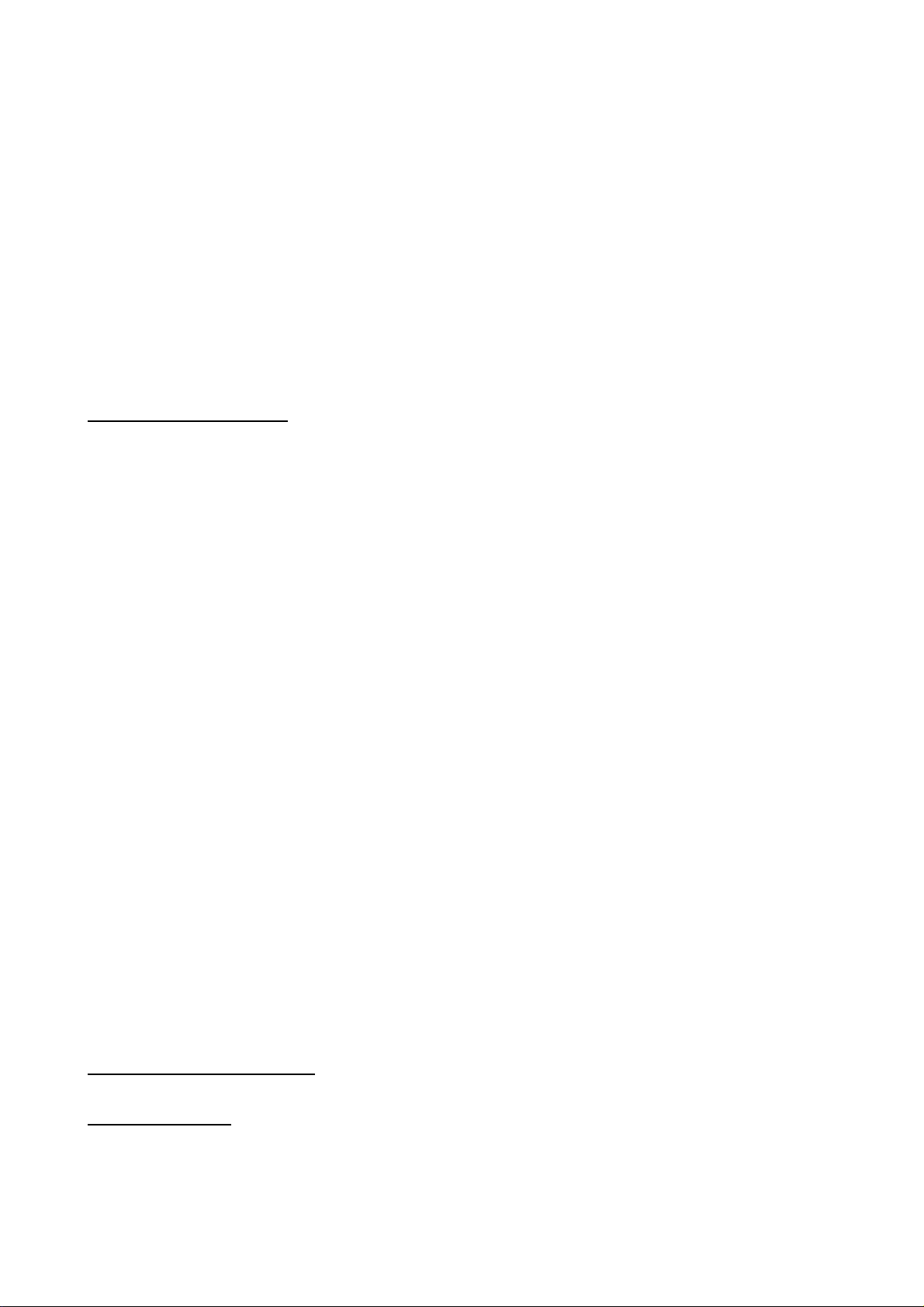

As we can see from the block diagram the chassis is equipped with the most recent

Integrated Circuit like the one chip TV processor TDA884x that does include all the low

level signal processing including Video, Audio, synchronisation process, and chroma

decoder . (see more detail at the "TDA884x FAMILY SPECIFICATION" paragraph), and

the Sound Processor TDA9875A that perform all sound function including digital decoding

of NICAM signals. (see more detail at the " TDA9870A & tda9875A MAIN

CHARACTERISTICS" paragraph).

The above mentioned devices are driven by an Integrated Circuit that does include

the microcontroller function with 64 K ROM and the TELETEXT acquisition and 8 pages

RAM. (SAA5297A)

In the F19 chassis there are, besides the stereo one, two possible module that are

performing "FEATURES" like PIP (picture in picture) and / or CTI (colour transients

improvement) and 4 by 3 to 16 by 9 signal processing. One further module is dedicated to

the so called "Zero Power Stand By"

A 26 Key Remote Control is performing the full control for the end- used but can

also be used in " SERVICE MODE" to control and adjust, without open the back cover of

the TV set all the necessary functions.

With the 5 "LOCAL KEY BOARD" button all the end user function can also be

performed

When the TV set is equipped with a PLL tuner the microcontroller recognise it and

the tuning method became a frequency synthesis system if not it work as a voltage tuning

system (provided all necessary components are mounted)

The TV make use of a multilevel MENU (activated both by the Remote Control and

Local Keyboard) using five selectable languages ( Italian, German, English, France, end

Spanish) with which it is possible to control sequentially all video and sound value, to

adjust several parameter like picture format, sound response, sleep timer etc., and to set

others important parameter like standard, select country for automatic tuning and sort etc.

Here below a list of the characteristics of the TV se

E.G.Data creazione 31/10/99 15.38 1 / 7 f19intro

TV SET CHARACTERISTICS (MONO & STEREO )

PICTURE TUBE SIZE :

• 4 : 3 ASPECT RATIO

• 16 : 9 ASPECT RATIO

• STANDARD

• R.F. (ANTENNA) (FOR FREQ. SYNTH.)

• VIDEO (SCART & CINCH)

• COLOUR (MAX. THREE STANDARDS)

• SOUND STANDARD:

∗ MONO

∗ STEREO

TUNING SYSTEM SELECTABLE :

FREQUENCY SYTHETIZER

• TOTAL AVAILABLE CHANNEL NUMBER

• CHANNEL IN ONE RF STANDARD UP TO

• NUMBER OF PROGRAM

• DIRECT PROGRAM & CHANNEL CALL WITH

• PROGRAM & CHANNEL STEP UP AND DOWN

• VOLTAGE SYNTHESISER

• CABLE & HYPERBAND CHANNEL

• SWITCHABLE AFC

• AUTOMATIC SEARCH TUNING

• A S T WITH AUTO SORT

AUDIO SECTION

POWER

• MONO

• STEREO

EXTERNAL CONNECTION

• HEADPHONE

• LOUDSPEAKERS

A / V INPUT / OUTPUT

• FRONT PANEL CINCH

• I FULL SCART (CVBS, STEREO, RBA)

• SCART (CVBS & STEREO IN / OUT)

• SCART A TO SCART B LOOP THROUGH

TXT PANEUROPEAN CHARACTER SET

• LEVEL 1

• LEVEL 1,5 (FASTEXT)

FEATURES

• CTI (COLOUR TRANSIENT IMPROVEMENT)

• 16:9 TO 4:3 VIDEO COMPRESSION

• VERTICAL ZOOM OUT

• MENU DRIVEN SYSTEM

• EASY TO USE REMOTE CONTROL

• REMOTE CONTROL WITH “SERVICE” USE

• PIP

21” / 25” / 28” / 29” / 34”

28 “ / 32”

CCIR ( B / G/ L / L’ / D / K / I )

B / G/ L / L’ / D / K / I / M / N

PAL / SECAM / NTSC

B / G/ L / L’ / D / K / I

AM & FM

A2 OR NICAM

FACTORY OPTION

200

100

100

1, OR 2 OR 3 DIGIT

YES

YES

YES

YES

YES

6 W RMS.

2 x 6 W RMS.

STEREO SET ONLY

INTERNAL L.S. SWITCHED

A / V INPUT

MULTIMEDIA INPUT OUTPUT

VCR, HI.FI, SATELLITE, ETC

FOR PROGRAMS DUBBING

8 PAGES

7 PAGES

OPTION

ONLY FOR 16:9 TV SET

3 LEVEL

NOT ACCESSIBLE TO END USER

OPTION

E.G.Data creazione 31/10/99 15.38 2 / 7 f19intro

A U D I O

AUDIO

EEPROM

PCF8582

TUNER

PLL

IIC bus

MICRO

PCA84C841/210

TXT

SAA5281/....

SAA5297A

T.O.P.

PHILIPS

PIP

SIEMENS

THIS MODULE IS PRESENT ONLY FOR STEREO SET

2ND SCART

SAW

FILTER

AUDIO

TDA9875

VIDEO PROCESSOR

AUDIO

VIDEO

&

AUDIO

A/V INA /V OUTA/V IN/OUT

TDA 8362A

S E C A M D.L. CROMA

TDA4661TDA8395

TDA844X

TXT & OSD

R B G

H. DRIVER

BC 639

POWER SUPPLY

TDA 4605 & STH7N80F

PIP (RGB)

FULL SCARTSCART INTER.

RGB

VERTICAL

TDA3654

E.W. GEN.

TDA4950

L.O.T.

BU 508 D

140 V

26 V

15 V

12 V

8 V

RGB

RGB

(OSD)

VIDEO AMPL.

CUT-OFF

TDA1521

TDA5112

V.

RGB

E H T

TRAFO

F16UPF19.DRW

E.G. 2/02/99

110°

H.

EAT

F16

UPDATED

F19

BLOCK DIAGRAM

AUDIO STEREO (NICAM) PROCESSOR

2 x 7 W

AUDIO POWER

TDA 9811 (nicam) TDA 9870A (TDA9875A (nicam)

V

I

D

E

I

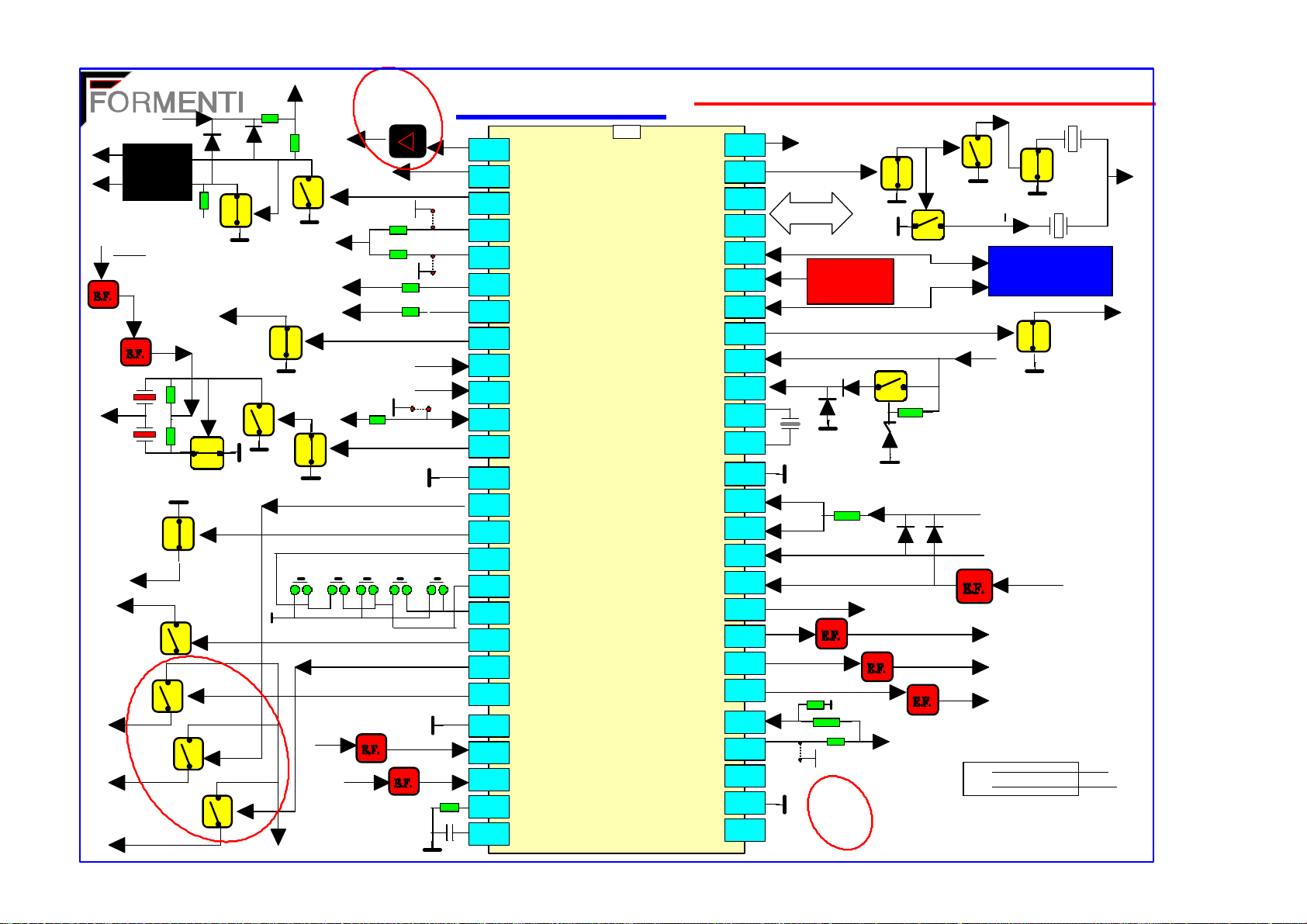

F 19

EEPROM

PCF8584 /

ST2404CB

TUNER

PLL

IIC bus

IIC bus

LOCAL KEY BOARD

O

A

U

D

I

O

I.

F.

SAW

FILTER

N

T

E

R

VIDEO & AUDIO

C

A

R

2ND SCART

R

I

E

R

IIC BUS ONE CHIP VIDEO PROCESSOR

*IF VIDEO & PLL DEM

*AGC & AFC, MUTE

*AUDIO PLL DEM

*PAL/NTSC (SECAM) DEC.

*B.B CHROMA DELAY LINE

*FULL SCART INTERFACE.

E T T

SAA5297A

IIC bus

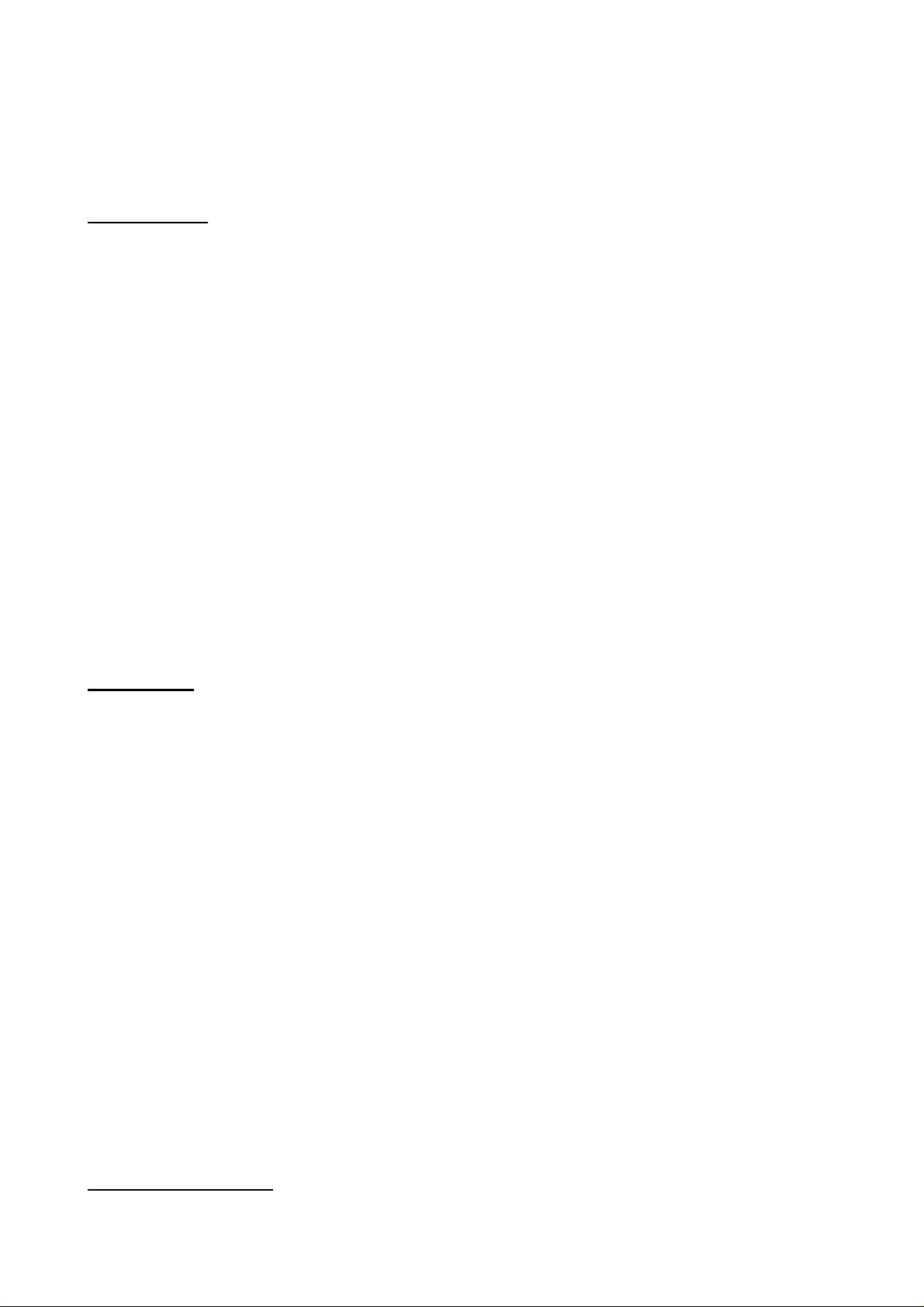

F19 BLOCK DIAGRAM

MICROCONTROLLER

& TELETEX 8 PAGES

PIP

OPTION

PIP (RGB)

I.R. INPUT

THIS MODULE IS PRESENT ONLY FOR STEREO SET

AUDIO

A/V IN/OUT

A /V OUT

AUDIO

AUDIO SCART SWITCH HEF4053

VIDEOSCART

SWITCH LA7955

A/V IN

FULL SCART

A/V/ CINCH

(OPTION)

TDA 8843(4)

*H & V SYNC PROCESSIG

*FULL IIC BUS CONTROLL FOR:

*AUTO CUT-OFF

*ALL ANALOGUE FUCTIONS

*GEOMETRY CORRECTION

*FEATURES INTERFACE

E-W-

E-W POWER

BUK474200A

DRIVER

TRAFO

26 V

8 VTDA 4605 & STH7N90F1

4

TXT

& OSD

R B G

U V

FEATURES MODULE

TDA4566 (CTI)

SAA4981 (16:9 TO 4:3)

OPTION

POWER SUPPLY

H DRIVE

H. DRIVER

BC 338

RGB

VERTICAL

TDA8351

E-W DRIVE COIL

BU 508 D

150 V

12 V

5 V

RGB

CUT-OFF

VERTICAL

FEEDBACK

L.O.T.

TDA1521

LINE OUT

(OPTION)

VIDEO AMPL.

TDA5112

RGB

V.

H.

H. DEFL.

& E H T

TRAFO

F19BLDIA.DRW

E.G. 17 / 7 / 99

HEADPHONE

E-W LOAD COIL

CRT

110°

EAT

AUDIO STEREO (NICAM) PROCESSOR

2 x 7 W

AUDIO POWER

TDA 9811 (nicam) TDA 9870A (TDA9875A (nicam)

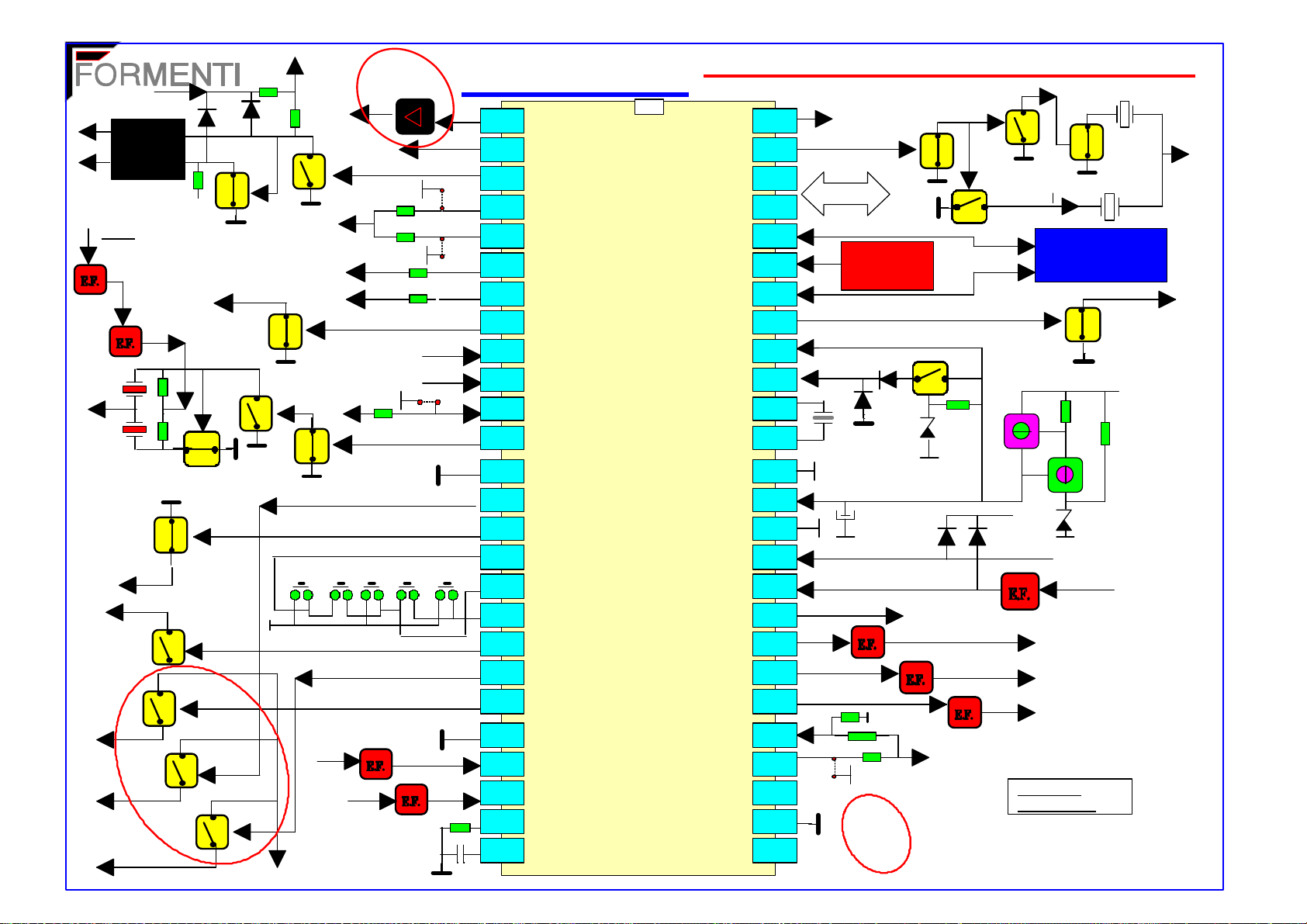

V

I

D

E

I

O

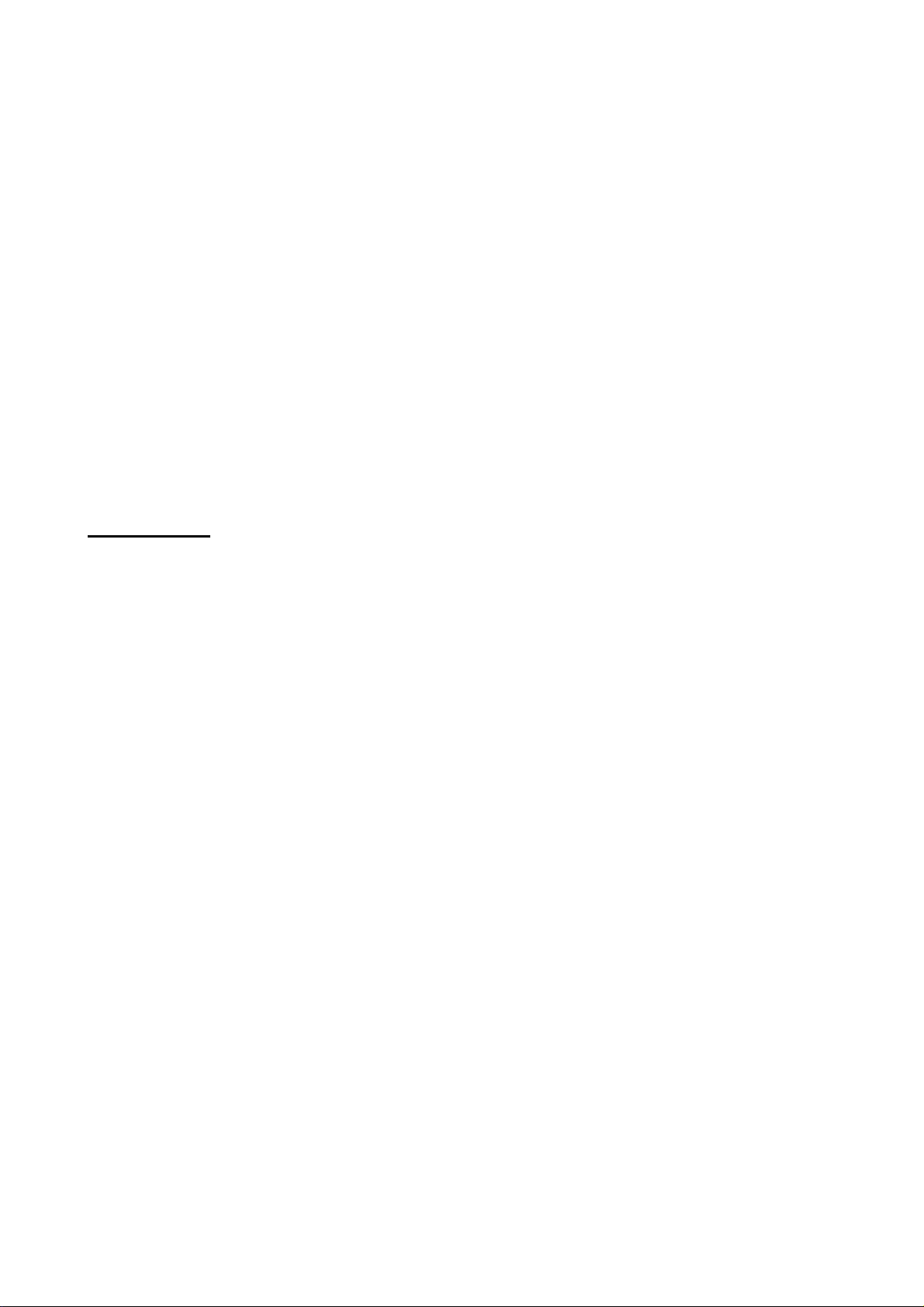

F 19.1

EEPROM

PCF8584 /

ST2404CB

TUNER

PLL

IIC bus

SAW

FILTER

IIC bus

LOCAL KEY BOARD

N

T

A

E

U

D

I

O

I.

F.

VIDEO & AUDIO

R

C

A

2ND SCART

R

R

I

E

R

IIC BUS ONE CHIP VIDEO PROCESSOR

*IF VIDEO & PLL DEM

*AGC & AFC, MUTE

*AUDIO PLL DEM

*PAL/NTSC (SECAM) DEC.

*B.B CHROMA DELAY LINE

*FULL SCART INTERFACE.

E T T

SAA5297A or

SAA5553M3

IIC bus

F19.1 BLOCK DIAGRAM

MICROCONTROLLER

& 8 PAGES TELETEXT

PIP

OPTION

PIP (RGB)

I.R. INPUT

THIS MODULE IS PRESENT ONLY FOR STEREO SET

AUDIO

A/V IN/OUT

A /V OUT

AUDIO

AUDIO SCART SWITCH HEF4053

VIDEOSCART

SWITCH LA7955

A/V IN

FULL SCART

A/V/ CINCH

(OPTION)

TDA 8843(4)

*H & V SYNC PROCESSIG

*FULL IIC BUS CONTROLL FOR:

*AUTO CUT-OFF

*ALL ANALOGUE FUCTIONS

*GEOMETRY CORRECTION

*FEATURES INTERFACE

E-W-

E-W POWER

BUK474200A

DRIVER

TRAFO

26 V

8 VTDA 4605 & STH7N90F1

4

TXT

& OSD

R B G

U V

FEATURES MODULE

TDA4566 (CTI)

SAA4981 (16:9 TO 4:3)

OPTION

POWER SUPPLY

H DRIVE

H. DRIVER

BC 338

RGB

VERTICAL

TDA8351

E-W DRIVE COIL

BU 508 D

150 V

12 V

5 V

RGB

CUT-OFF

VERTICAL

FEEDBACK

L.O.T.

TDA1521

LINE OUT

(OPTION)

VIDEO AMPL.

TDA5112

RGB

V.

H.

H. DEFL.

& E H T

TRAFO

F19BDE&P.DRW

E.G. 22/04/2000

HEADPHONE

E-W LOAD COIL

CRT

110°

EAT

F19 TUNINGF19 TUNING

&&

TELETEXTTELETEXT

SAA529XA FAMILY MAIN CHARACTERISTICS

FEATURES

General

• Single chip microcontroller with integrated teletext decoder

• Single +5 V power supply

• Single crystal oscillator for teletext decoder, display and microcontroller

• Teletext function can be powered-down independent of microcontroller function for

reduced power consumption in standby

• Pin compatibility throughout family.

Microcontroller

• 80C51 microcontroller core

• 16/32/64 kbyte mask programmed ROM

• 256/768/1280 bytes of microcontroller RAM

• Eight 6-bit Pulse Width Modulator (PWM) outputs for control of TV analog signals

• One 14-bit PWM for Voltage Synthesis Tuner control

• Four 8-bit Analog-to-Digital converters

• 2 high current open-drain outputs for directly driving LEDs etc.

• I 2 C-bus interface

• External ROM and RAM capability on QFP80 package version.

Teletext acquisition

• 1 page and 10 page Teletext version

• Acquisition of 525-line and 625-line World System Teletext, with automatic selection

• Acquisition and decoding of VPS data (PDC system A)

• Page clearing in under 64 s (1 TV line)

• Separate storage of extension packets (SAA5296/7, SAA5296/7A and SAA5496/7)

• Inventory of transmitted Teletext pages stored in the Transmitted Page Table (TPT)

end Subtitle Page Table (SPT) (SAA5296/7, SAA5296/7A and SAA5496/7)

• Automatic detection of FASTEXT transmission

E.G.Data creazione 01/11/99 17.27 8 / 30 F19MANU.doc

TO CURRENT INTEGRATOR

VOLTAGE SINTESYS ONLY

FRANCE STD. SWITCH

CTI DETECTOR

16 : 9 DETECTOR

SCART1 / SCART2 SWITCH

SCART 1 / TV

TO SCART 2 SWITCH

FRONT CINCH / SCART1

SWITCH

SCART 1 INPUT DETECTOR

SCART 2 INPUT DETECTOR

HEAD PHONES DETECTOR

STANDARD SWITCH

UHF SUPPLY

(VOLTAGE SINTESYS ONLY)

TV / AV SWITCH

MENU V - V + P - P +

LOCAL KEY BOARD

TV ON / OFF SWITCH

TUNER SUPPLY (V.S. ONLY)

TUNER SUPPLY(V.S. ONLY)

CVBS FROM ANTENNA

CVBS FROM SCART

SAA5297A.DRW

E.G . 17 / 10 / 99

DATA

SLICER

REF.PIN

TO X13

SAA5297A

1

V TUN.

2

DSC

3

SWT. L/L'

4

CTI STS.

5

16:9 STS

6

SWT. S1/S2

7

COPY SWT.

8

SWT. CI/S1

9

AV1 STS.

10

AV2 STS.

11

H.P. STS.

12

SYSTEM

13

VSS M+T

14

UHF

15

TV / AV

16

P0.3

17

P0.4

18

P0.5

19

ON / OFF

20

VHF H

21

VHF L

22

VSSA

23

CVBS0

24

CVBS1

25

BLACK

26

IREF

P

O

R

T

2

P

O

R

T

3

P

O

R

T

0

T X T DATA

SLICER &

ACQUISITION

MICRO & TXT Block Diagram

ROM RAM TIMER

A/ D

8051

CORE

B

U

PWM

S

TXT

INT

PAGE

RAM

OSCILLATOR

DISPLAY

DISPLAY

P

O

R

T

1

TIMING

SWT 16:9

OSC. SWT.

MSDA

MSCL

SDA 1

INTO

SCL 1

AM/FM

VDDM

RESET

OSCOUT

OSCIN

OSCGND

VDDT

VDDA

VSYNC

HSYNC

BLK

RGBREF

PIP STS

INT. TEST

FRAME

R

G

B

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

TO CHANGE

ASPECT RATIO

TO SWITCH S.C.

FROM 4.43

TO 3.58 MHz

MAIN

IIC BUS

IIC BUS

FOR

I.R.

EEPROM

SOUND STANDARD

SWITCH

5 V from ST-BY

FROM

RESESET CIRCUIT

QZ100

12 MHz

5 V

VERTICAL

FLYBACK

HORIZONTAL

FLYBACK PULSE

TO

TDA884X

RGB REFERENCE

VOLTAGE

2,5 V

PIP DETECTOR

NOT CONNECTED

NOT CONNECTED

TO CURRENT INTEGRATOR

VOLTAGE SINTESYS ONLY

TO X13

FRANCE STD. SWITCH

CTI DETECTOR

16 : 9 DETECTOR

SCART1 / SCART2 SWITCH

SCART 1 / TV

TO SCART 2 SWITCH

FRONT CINCH / SCART1

SWITCH

SCART 1 INPUT DETECTOR

SCART 2 INPUT DETECTOR

HEAD PHONES DETECTOR

STANDARD SWITCH

UHF SUPPLY

(VOLTAGE SINTESYS ONLY)

TV / AV SWITCH

MENU V - V + P - P +

LOCAL KEY BOARD

TV ON / OFF SWITCH

TUNER SUPPLY (V.S. ONLY)

TUNER SUPPLY(V.S. ONLY)

CVBS FROM ANTENNA

CVBS FROM SCART

DATA

SAA5553.DRW

E.G 22/ 04 / 2000

SLICER

REF.PIN

SAA5553M3

1

V TUN.

DSC

2

3

SWT. L/L'

CTI STS.

4

5

16:9 STS

SWT. S1/S2

6

7

COPY SWT.

SWT. CI/S1

8

9

AV1 STS.

AV2 STS.

10

11

H.P. STS.

SYSTEM

12

13

VSS M+T

UHF

14

15

TV / AV

P0.3

16

17

P0.4

P0.5

18

19

ON / OFF

VHF H

20

21

VHF L

VSSA

22

CVBS0

23

CVBS1

24

BLACK

25

IREF

26

P

O

R

T

2

P

O

R

T

3

PWM

P

O

R

T

0

PAGE

RAM

T X T DATA

SLICER &

ACQUISITION

MICRO & TXT Block Diagram

ROM RAM TIMER

A/ D

8051

CORE

B

U

S

TXT

INT

OSCILLATOR

DISPLAY

TIMING

DISPLAY

SWT 16:9

P

OSC. SWT.

O

R

T

1

AM/FM

RESET

OSCOUT

OSCGND

VSYNC

HSYNC

RGBREF

PIP STS

INT. TEST

FRAME

MSDA

MSCL

SDA 1

INTO

SCL 1

VDDM

OSCIN

VDDT

VDDA

BLK

R

G

B

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

TO CHANGE

ASPECT RATIO

TO SWITCH S.C.

FROM 4.43

TO 3.58 MHz

MAIN

IIC BUS

IIC BUS

I.R.

FOR

EEPROM

SOUND STANDARD

SWITCH

5 V from ST-BY

FROM

RESESET CIRCUIT

QZ100

12 MHz

3 V

VERTICAL

FLYBACK

HORIZONTAL

FLYBACK PULSE

TO

TDA884X

RGB REFERENCE

VOLTAGE

2,5 V

PIP DETECTOR

NOT CONNECTED

NOT CONNECTED

• Real-time packet 26 engine for processing accented (and other) characters

• Comprehensive Teletext language coverage

• Video signal quality detector.

Teletext Display

• 525-line and 625-line display

• 12 10 character matrix

• Double height, width and size On-Screen Display (OSD)

• Definable border colour

• Enhanced display features including meshing and shadowing

• 260 characters in mask programmed ROM

• Automatic FRAME output control with manual override

• RGB push-pull output to standard decoder ICs

• Stable display via slave synchronisation to horizontal sync and vertical sync.

Additional features of SAA529xA devices

• Wide Screen Signalling (WSS) bit decoding (line 23).

2 GENERAL DESCRIPTION

The SAA529x, SAA529xA and SAA549x family of microcontrollers are a derivative of the

Philips’ industry-standard 80C51 microcontroller and are intended for use as the central

control mechanism in a television receiver. They provide control functions for the television

system and include an integrated teletext function.

The teletext hardware has the capability of decoding and displaying both 525-line and 625line World System Teletext. The same display hardware is used both for Teletext and OnScreen Display, which means that the display features give greater flexibility to

differentiate the TV set.

The family offers both 1 page and 10 page Teletext capability, in a range of ROM sizes.

Increasing display capability is offered from the SAA5290 to the SAA5497.

TELETEXT DECODER

Data slicer

E.G.Data creazione 01/11/99 17.27 9 / 30 F19MANU.doc

The data slicer extracts the digital teletext data from the incoming analog waveform. This

is performed by sampling the CVBS waveform and processing the samples to extract the

teletext data and clock.

Acquisition timing

The acquisition timing is generated from a logic level positive-going composite sync signal

VCS. This signal is generated by a sync separator circuit which adaptively slices the sync

pulses. The acquisition clocking and timing are locked to the VCS signal using a digital

phase-locked-loop. The phase error in the acquisition phase-locked-loop is detected by a

signal quality circuit which disables acquisition if poor signal quality is detected.

Teletext acquisition

This family is capable of acquiring 625-line and 525-line World System Teletext see “World

System Teletext and Data Broadcasting System”. Teletext pages are identified by seven

numbers: magazine (page hundreds), page tens, page units, hours tens, hours units,

minutes tens and minutes units. The last four digits, hours and minutes, are known as the

subcode, and were originally intended to be time related, hence their names.

For the ten page device, each packet can only be written into one place in the teletext

RAM so if a page matches more than one of the page requests the data is written into

the area of memory corresponding to the lowest numbered matching page request.

At power-up each page request defaults to any page, hold on and error check Mode 0.

Rolling headers and time

When a new page has been requested it is conventional for the decoder to turn the header

row of the display green and to display each page header as it arrives until the correct

page has been found.

Error checking

Before teletext packets are written into the page memory they are error checked. The error

checking carried out depends on the packet number, the byte number, the error check

mode bits in the page request data and the TXT1.8 BIT bit. If an uncorrectable error

occurs in one of the Hamming checked addressing and control bytes in the page header

or in the Hamming checked bytes in packet 8/30, bit 4 of the byte written into the memory

is set, to act as an error flag to the software. If uncorrectable errors are detected in any

other Hamming checked data the byte is not written into the memory.

E.G.Data creazione 01/11/99 17.27 10 / 30 F19MANU.doc

Packet 26 processing

One of the uses of packet 26 is to transmit characters which are not in the basic teletext

character set. The family automatically decodes packet 26 data and, if a character

corresponding to that being transmitted is available in the character set, automatically

writes the appropriate character code into the correct location in the teletext memory. This

is not a full implementation of the packet 26 specification allowed for in level 2 teletext, and

so is often referred to as level 1.5.

By convention, the packets 26 for a page are transmitted before the normal packets. To

prevent the default character data overwriting the packet 26 data the device incorporates a

mechanism which prevents packet 26 data from being overwritten.

Fastext detection

When a packet 27, designation code 0 is detected, whether or not it is acquired, the

TXT13.FASTEXT bit is set. If the device is receiving 525-line teletext, a packet X/0/27/0 is

required to set the flag. The flag can be reset by writing a logic 0 into the SFR bit.

When a packet 8/30 is detected, or a packet 4/30 when the device is receiving a 525-line

transmission, the TXT13.Pkt 8/30 is set. The flag can be reset by writing a logic 0 into the

SFR bit.

THE DISPLAY

Introduction

The capabilities of the display are based on the requirements of level 1 teletext, with some

enhancements for use with locally generated on screen displays. The display consists of

25 rows each of 40 characters, with the characters displayed being those from rows 0 to

24 of the basic page memory. If the TXT7.STATUS ROW TOP bit is set row 24 is

displayed at the top of the screen, followed by row 0, but normally memory rows are

displayed in numerical order. The teletext memory stores 8 bit character codes which

correspond to a number of displayable characters and control characters, which are

normally displayed as spaces. The character set of the device is described in more detail

below.

E.G.Data creazione 01/11/99 17.27 11 / 30 F19MANU.doc

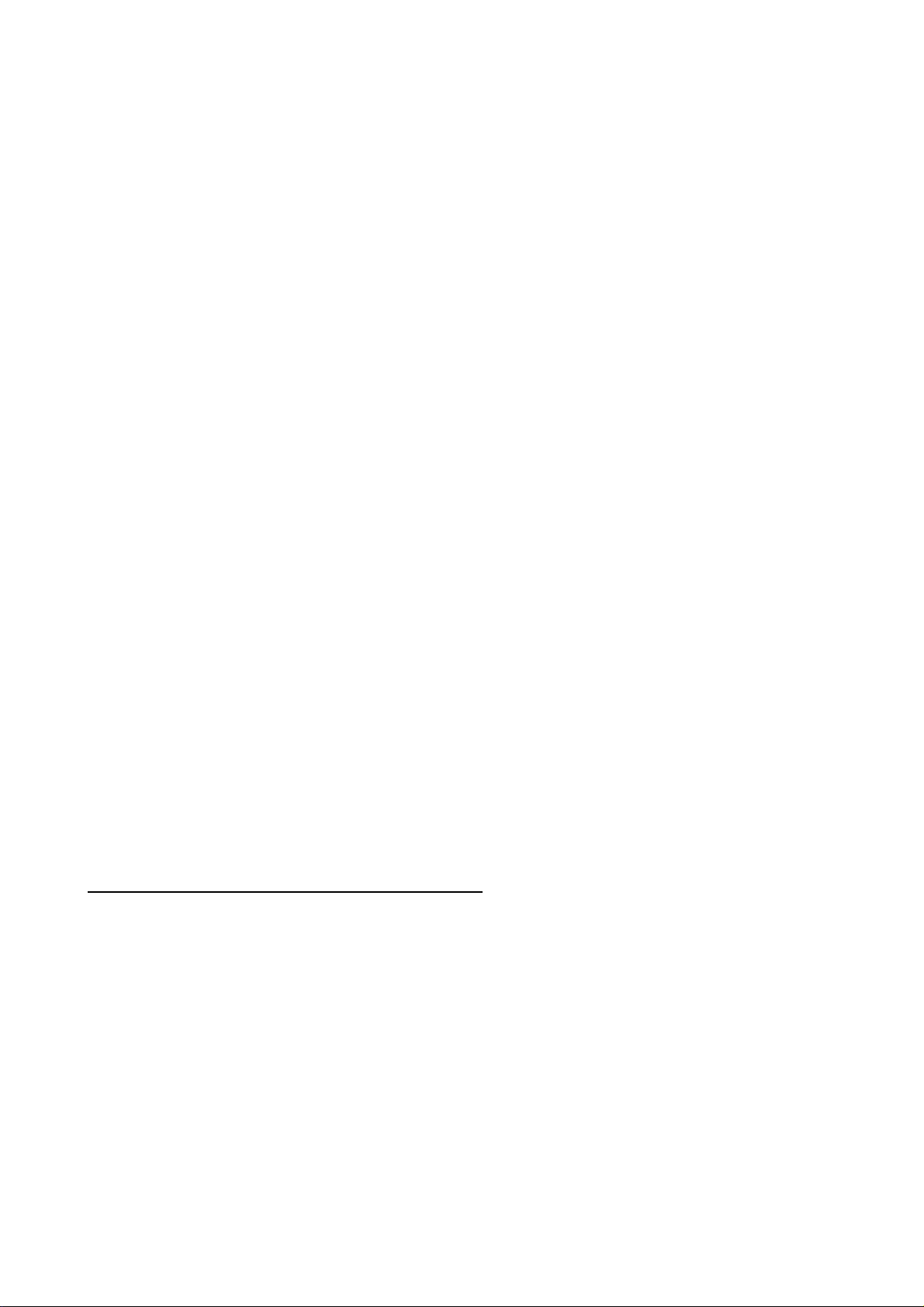

WEST EUROPE

CHARACTER SET

NATIONAL OPTION FOR:

ENGLISH

GERMAN

SWEDISH

ITALIAN

FREANCH

SPANISH

TURKISH

WEST EAST

(OPTION BYTE 1

BIT 3 SETTED TO 0

EAST EUROPE

CHARACTER SET

NATIONAL OPTION FOR:

POLISH

GERMAN

ESTONIAN

SERBO-CROAT

CZECH

SLOVAKIA

RUMANIAN

D

PL

CZ

A

H

R

Y

(OPTION BYTE 1

BIT 6 SETTED TO 1

F19 E&WCS.DRW

E.G. 7/11/99

Character matrix

Each character is defined by a matrix 12 pixels wide and 10 pixels high. When displayed,

each pixel is 1 12 s wide and 1 TV line, in each field, high.

East/West selection

In common with their predecessors, these devices store teletext pages as a series of 8 bit

character codes which are interpreted as either control codes (to change colour, invoke

flashing etc.) or displayable characters. When the control characters are excluded, this

gives an addressable set of 212 characters at any given time.

National option characters

The meanings of some character codes between 20H and 7FH depend on the C12 to C14

language control bits from the teletext page header.

The interpretation of the C12 to C14 language control bits is dependent on the East/West

bit.

On-Screen Display characters

Character codes 80H to 9FH are not addressed by the teletext decoding hardware. An

editor is available to allow these characters to be redefined by the customer. The

alternative character shapes in columns 8a and 9a (SAA549x only) can be displayed when

the ‘graphics’ serial attribute is set. This increases the number of customer definable

characters to 64.

Clock generator

The oscillator circuit is a single-stage inverting amplifier in a Pierce oscillator configuration.

The circuitry between XTALIN and XTALOUT is basically an inverter biased to the transfer

point. A crystal must be used as the feedback element to complete the oscillator circuitry.

It is operated in parallel resonance. XTALIN is the high gain amplifier input and XTALOUT

is the output. To drive the device externally XTALIN is driven from an external source and

XTALOUT is left open-circuit.

E.G.Data creazione 01/11/99 17.27 12 / 30 F19MANU.doc

SOUND I.F.

CVBS

IC 204

TR200

TR201

F575

TO PIN 1

IC 204

TR107

TO STEREO

NICAM

MODULE

TO PIN 4

IC 10

PIN 5

T

O

PIN 3

T

U

N

E

R

PIN 4

AM

SOUND

FILTER

F204

PIN 6

F576

12V

TO PIN

10, 11

IC 200

TR210

TR2

TR 502

TR110

TR 501

12 V

TUNUNG

VOLTAGE

TO PIN 2

TUNER

TO X13

TR219

TR218

TO PIN 4 IC 201

TO PIN 8 IC 201

TR209

TR503

5V

FRON PIN 8 SCART 1

FROM PIN 8 SCART 2

5V

TR111

TO SWITC INT/EX SOUND

MENU V - V + P - P +

TV ON / OFF

CVBS FROM

ANTENNA

CVBS

FROM SCART

5V

R174

R128

R140

R146

TR500

TR203

TR211

SAA5297A

R141

V TUN.

1

2

DSC

SWT. L/L'

3

4

CTI STS.

16:9 STS

5

6

SWT. S1/S2

COPY SWT.

7

8

SWT. CI/S1

AV1 STS.

9

10

AV2 STS.

H.P. STS.

11

12

SYSTEM

VSS M+T

13

14

UHF

TV / AV

15

P0.3

16

P0.4

17

P0.5

18

ON / OFF

19

VHF H

20

VHF L

21

VSSA

22

CVBS0

23

CVBS1

24

BLACK

25

IREF

26

SWT 16:9

OSC. SWT.

OSCGND

INT. TEST

MICRO & TXT PERIPHERALS

MSDA

MSCL

SDA 1

INTO

SCL 1

AM/FM

VDDM

RESET

OSCOUT

OSCIN

VDDT

VDDA

VSYNC

HSYNC

BLK

R

G

B

RGBREF

PIP STS

COR

FRAME

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

TO CTI &

16:9 MOULE

IIC BUS

TR 109

IRR100

SOUND STDANDARD SWITCH

TR 108

QZ100

D 105

12 MHz

R 106

D 108

TR 101

TR 102

TR 103

R167

5V

FOR VOLTAGE

SISTETIZER ONLY

IIC BUS

TR206

TR 205

5V ST-BY

D 102

TR 208

3.58MHz

EEPROM

IC 101

TO PIN 10

IC 102

TR 105

5 V

FLYBACK PULSE

FROM EHT

VERTICAL

BLANKING

FROM PIN 8

IC 5

TO PIN

23, 24, 25

IC 204

F19MTPER.DRW

E.G. 24 /10 /99

4.43 MHz

TO

PIN 35

IC 204

SOUND I.F.

CVBS

IC 204

TR200

TR201

F575

TO PIN 1

IC 204

F576

TR107

TO STEREO

NICAM

MODULE

TO PIN 4

IC 10

PIN 5

T

O

PIN 3

T

U

N

E

PIN 4

R

AM

SOUND

FILTER

F204

PIN 6

12V

TO PIN

10, 11

IC 200

TR210

TR2

TR 502

TR 501

TR218

TO PIN 4 IC 201

TO PIN 8 IC 201

TR110

TR209

TR503

12 V

TUNUNG

VOLTAGE

TO PIN 2

TUNER

TO X13

TR219

5V

FRON PIN 8 SCART 1

FROM PIN 8 SCART 2

5V

TR111

TO SWITC INT/EX SOUND

MENU V - V + P - P +

TV ON / OFF

CVBS FROM

ANTENNA

CVBS

FROM SCART

5V

TR500

R174

R128

R140

R146

TR203

TR211

SAA 5553

1

V TUN.

2

R141

DSC

3

SWT. L/L'

4

CTI STS.

5

16:9 STS

6

SWT. S1/S2

COPY SWT.

7

SWT. CI/S1

8

AV1 STS.

9

AV2 STS.

10

H.P. STS.

11

SYSTEM

12

VSS M+T

13

UHF

14

TV / AV

15

P0.3

16

P0.4

17

P0.5

18

ON / OFF

19

VHF H

20

VHF L

21

VSSA

22

CVBS0

23

CVBS1

24

BLACK

25

IREF

26

OSC. SWT.

INT. TEST

MICRO & TXT PERIPHERALS

SWT 16:9

MSDA

MSCL

SDA 1

INTO

SCL 1

AM/FM

VDDM

RESET

OSCOUT

OSCIN

OSCGND

VDDT

VSSA

VSYNC

HSYNC

BLK

R

G

B

RGBREF

PIP STS

COR

FRAME

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

TO CTI &

16:9 MOULE

IIC BUS

IRR100

SOUND STDANDARD SWITCH

TR 108

QZ100

TR 109

IIC BUS

3,3 V

D 105

12 MHz

3,3 V

D 108

D 102

TR 101

TR 102

TR 103

R167

5V

FOR VOLTAGE

SISTETIZER ONLY

TR206

TR 205

EEPROM

IC 101

TR8

TR7

D5

5 V

FLYBACK

FROM EHT

VERTICAL

BLANKING

FROM PIN 8

IC 5

TO PIN

23, 24, 25

IC 204

F19PAPER.DRW

E.G. 22 / 04 /2000

PAINTER

TR 208

3.58MHz

TR 105

R39

2,5V

4.43 MHz

TO

PIN 35

IC 204

TO PIN 10

IC 102

5 V

R40

VIDEO

VIDEO

SIGNAL

SIGNAL

PROCESSING

PROCESSING

F 19

TO PIN 33

IC100

CVBS

FOR TXT

TO PIN 24

IC 100

(CVBS FOR TXT)

TO PIN 9

IC 100

AV1

STATUS

SCART 1

FROM PIN 6

IC100

AV1 / AV2

SWITCH

FROM PIN 7

IC100

AV1 / TV

SWITCH

TO AV2

EF

TR203

19

8

15

11

7

16

20

CVBS IN

TV

CVBS

TO PIN 10

IC 100

AV2 STATUS

TR201

EF

TR204

TR211

1

3

EFEF

TR200

EF

4

FOR VOLTAGE SINTHESIS ONLY

SIF

1

AUDEXT

VIDEO IN

CINCH

7

IIC

TR202

EF

12 V

6

82

2

NC

3

NC

4

PLLIF

5

IFVIDEO OUT

6

SCL

7

SDA

8

DECOUPLING

9

CHR.IN

10

EX.CVBS/Y IN

11

VP1

12

INT CVBS IN

13

GND

14

AUDIO OUT

15

DECOUPLING

16

EX. CVBS IN

17

BLKIN

18

B OUT

19

G OUT

20

R OUT

21

BCL/VG

22

R IN

23

G IN

24

B IN

25

RGB INSERT.

26

Y IN

27

Y OUT

28

5

9

1/3 0F IC201

LA7955

CVBS IN

CVBS OUT

TDA884X

I.F.

VIDEO

AGC

AFC

DEM.

IDENT

SOUND

PROCES.

(MONO)

SYNC

PROCES.

V. & H.

TIME

BASE

TRANSRECEIVER

TR212

EF

20 19

CONTROL

EXT RGB

IIC

SCART 2

8

MSD

PAL

(SECAM)

NTSC

C.D. &

RGB

MATRIX

VIDEO

SWITCH

& RGB

DRIVE

RGB AMPLIFIER

VIDEO SIGNAL PATH

DECOUPLING

DEENPHASIS

AGC OUT

DECOPLING

I REF

VERT. RAMP

EHT PROTEC.

IF IN 2

IF IN 1

V. DRIVE A

V. DRIVE B

E - W OUT

GND 2

PH. 1 FILTER

PH. 2 FILTER

H. IN, S.C. OUT

HOR. OUT

DECOUPLING

CVBS 1 OUT

V P 2

DET FILTER

X TAL 2

X TAL 1

S.C. REF OUT

R - Y IN

B - Y IN

R - Y OUT

B - Y OUT

MODULE

TO CRT

EF

TR500

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

8 V

UV

12 V

1

2

3

4

IIC

5

6

7

8

9

TR208

3.58MHz

3,57MHz

5 V

FROM PIN 52

IC 100 4:3 TO 16:9

SWITCH

10

11

A10

8 V

UHF

VHF H

VHF L

4.43MHz

1

2

3

4

5

6

7

8

9

10

11

12

TR206

C T I

&

4 : 3

TO

16 : 9

FROM PIN 1

∫∫

IC 100

TR501

TR503

TR502

FROM IC 100

PIN 14, 20, 21

BAND SWITCHING

TR105

TR205

FROM EHT

F19VIDEP.DRW

E.G. 14 / 11 / 99

5 V

FROM

PIN 51

IC 100

Reset signal

The externally applied RESET signal (active HIGH) is used to initialize the microcontroller

core, in addition to the teletext decoder. However, the teletext decoder incorporates a

separate internal reset function which is activated on the rising edge of the analog supply

pin, VDDA . The purpose of this internal reset circuit is to initialize the teletext decoder when

returning from the “text standby mode”.

TDA884X FAMILY SPECIFICATION

FEATURES

The following features are available in all IC’s:

• Multi-standard vision IF circuit with an alignment-freePLL demodulator without external

components

• Alignment-free multi-standard FM sound demodulator(4.5 MHz to 6.5 MHz)

• Audio switch

• Flexible source selection with CVBS switch andY(CVBS)/C input so that a comb filter can

be applied

• Integrated chrominance trap circuit

• Integrated luminance delay line

• Asymmetrical peaking in the luminance channel with a(defeatable) noise coring function

• Black stretching of non-standard CVBS or luminancesignals

• Integrated chroma band-pass filter with switchablecentre frequency

• Dynamic skin tone control circuit

• Blue stretch circuit which offsets colours near whitetowards blue

• RGB control circuit with “Continuous CathodeCalibration” and white point adjustment

• Possibility to insert a “blue back” option when no videosignal is available

• Horizontal synchronization with two control loops andalignment-free horizontal

oscillatoroptimised N2 application.Functionally the IC series is split up is 3 categories,

viz:

E.G.Data creazione 01/11/99 17.27 13 / 30 F19MANU.doc

TUNER

AGC

I.F IN

PLL

FILTER

Deenphasis

EXTERNAL

AUDIO IN

54

53

IF &

TUNER

A G C

I.F. value

48

VIDEO IF

AMPLIFIER

49

Sensitivity

5

A

F

W

AFA

AFB

A F C

TDA 8844

55

DEENPHASIS LINE

Internal

Audio

EXTERNAL

2

AUDIO

SWITCH

15A.F.

MONO AUDIO OUTPUT

SWT

TUNER T.O.P

gating

calibration

PLL

DEMOD.

& VCO

VIDEO

AMPLIFIER

VIDEO

IDENT.

AVL

SWITCH &

VOLUME

CVBS OUTPUT

6

MOD

Pos./Neg.

AVL

Volume

CVBS (int) IN

CVBS (ext) IN

CVBS / Y IN

13 17 11 10

CVBS & Y/C

SWITCH

Luma

Y DELAY,

C. TRAP,

Y PEAKING

To Sync

H.

SYNC

SEPARATOR

VIDEO

MUTE

AUDIO PRE

AMPLIFIER

& MUTE

H. sync

PHI 1

DETECTOR

CHROMA IN

Chroma

CHROMA

CLOCHE &

BANDPASS

V. SYNC

SEPARATOR

VERTICAL

DEVIDER

LINE

OSCILL.

CVBS OUT

(comb filter)

38

V. sync

SCL SDA

7 8

IIC

TRANSRECEIVER

IIC

PAL / NTSC

SECAM

DECODER

AUTO

SYSTEM

IDENT.

MANAGER

VERTICAL

SAWTOOTH

GENERATOR

Secam

Decoupling

16

34 35

BURST PHASE

DETECTOR

Subcarrier

GAI

SAT

R-Y & B-Y

MATRIX

MAT

SAT CONTR.

BLACK STRETCH

DSA

SKIN TINT CORR.

RGB SWITCH

CON

RGB CONTROL

AUTO CUT-OFF

& OUTPUT

BRI

Xtal

& VCXO

BASE BAND

CHROMA

DELAY LINE

36

33

28

29

30

27

31

32

23

24

25

26

18

19

20

21

Loop

filter

Phase

Detector

Fsc

Y

B-Y

R-Y

Y

B-Y

R-Y

R

G

B

F.B.

Black

Currente

Input

R

G

B

I

N

P

U

T

O

U

T

P

U

T

AVL

Decoupling

INTERCARRIER

IN

BandGap

Decoupling

(45)

1

1 A 10 MHz

9

B.P.F.

Supply

12

AUDIO

LIMITER

37 14

8 V8 V Main

Supply

Ground

AUDIO

PLL DEM.

56

Sound

Decoupling

PHI 2

LINE OUT

S.C. GENER.

43 41 40

Phi 1

filter

42

Phi 2

filter

Flyback in

Sand

Castle

Out

51 52

Line

Pulse

Vertical

Out

Sawtooth Reference

E - W

GEOMETRY

45

E-W

DRIVE

VERTICAL

DRIVE

50

EHT

Overvoltage

47

46

22

V- Guard &

B.C. limiter

TDA8844BLDIA.DRW

E.G. 17 /10 / 99

Vertical

Drive

Output

• Versions intended to be used in economy TV receiverswith all basic functions (envelope:

S-DIP 56 and QFP 64)

• Versions with additional features like E-W geometrycontrol, H-V zoom function and YUV

interface which are intended for TV receivers with 110° picture tubes(envelope: S-DIP 56)

• Versions which have in addition a second RGB inputwith saturation control and a second

CVBS output (envelope: QFP 64)

• Vertical count-down circuit

• Vertical driver optimised for DC-coupled vertical outputstages

GENERAL DESCRIPTION

The various versions of the TDA 884X/5X series areI 2 C-bus controlled single chip TV

processors which are

intended to be applied in PAL, NTSC, PAL/NTSC and multi-standard television receivers.

The N2 version is pin and application compatible with the N1 version, however,a new

feature has been added which makes the N2 more attractive. The IF PLL demodulator has

been replaced byan alignment-free IF PLL demodulator with internal VCO (no tuned circuit

required). The setting of the variousfrequencies (33.4, 33.9, 38, 38.9, 45,75 and 58.75

MHz) can be made via the I 2 C-bus.

Because of this difference the N2 version is compatiblewith the N1, however, N1 devices

cannot be used in an optimized N2 application

Functionally the IC series is split up is 3 categories, viz:

• Versions intended to be used in economy TV receivers with all basic functions (envelope:

S-DIP 56 and QFP 64)

• Versions with additional features like E-W geometry control, H-V zoom function and YUV

interface which areintended for TV receivers with 110° picture tubes (envelope: S-DIP 56)

• Versions which have in addition a second RGB input with saturation control and a

second CVBS output (envelope: QFP 64)

FUNCTIONAL DESCRIPTION

Vision IF amplifier

The IF-amplifier contains 3 ac-coupled control stages with a total gain control range which

is higher then 66 dB. The sensitivity of the circuit is comparable with that of modern

E.G.Data creazione 01/11/99 17.27 14 / 30 F19MANU.doc

IF-IC’s.

The video signal is demodulated by means of an alignment-free PLL carrier regenerator

with an internalVCO. This VCO is calibrated by means of a digital control circuit which

uses the X-tal frequency of the colour decoder as a reference. The frequency setting for

the various standards (33.4, 33.9, 38, 38.9, 45.75 and 58.75 MHz) is realised via the I 2 Cbus. To get a good performance for phase modulated carrier signals the control speed of

the PLL can be increased by means of the FFI bit.

The AFC output is generated by the digital control circuit of the IF-PLL demodulator and

can be read via the I 2 C-bus.

For fast search tuning systems the window of the AFC can be increased with a factor 3.

The setting is realised with the AFW bit. The AFC data is valid only when the horizontal

PLL is in lock (SL = 1)

Depending on the type the AGC-detector operates on top-sync level (single standard

versions) or on top sync and top white- level (multi standard versions). The demodulation

polarity is switched via the I 2 C-bus. The AGC detector time-constant capacitor is

connected externally. This mainly because of the flexibility of the application. The timeconstant of the AGC system during positive modulation is rather long to avoid visible

variations of the signal amplitude. To improve the speed of the AGC system a circuit has

been included which detects whether the AGC detector is activated every frame period.

When during 3 field periods no action detected the speed of the system is increased. For

signals without peak white information the system switches automatically to a gated black

level AGC. Because a black level clamp pulse is required for this way of operation the

circuit will only switch to black level AGC in the internal mode.

The circuits contain a video identification circuit which is independent of the

synchronisation circuit. Therefore search tuning is possible when the display section of the

receiver is used as a monitor. However, this ident circuit cannot be made as sensitive as

the slower sync ident circuit (SL) and we recommend to use both ident outputs to obtain a

reliable search system. The ident output is supplied to the tuning system via the I 2 C-bus.

The input of the identification circuit is connected to pin 13 (S-DIP 56 devices), the

“internal” CVBS input (see Fig.6).

This has the advantage that the ident circuit can also be made operative when a

scrambled signal is received (descrambler connected between pin 6 (IF video output) and

pin 13). A second advantage is that the ident circuit can be used when the IF amplifier is

not used (e.g. with built-in satellite tuners).

E.G.Data creazione 01/11/99 17.27 15 / 30 F19MANU.doc

The video ident circuit can also be used to identify the selected CBVS or Y/C signal. The

switching between the 2 modes can be realised with the VIM bit.

Video switches

The circuits have two CVBS inputs (internal and external CVBS) and a Y/C input. When

the Y/C input is not required the Y input can be used as third CVBS input. The switch

configuration is given in Fig.6. The selection of the various sources is made via the I 2 Cbus.

For the TDA 884X devices the video switch configuration is identical to the switch of the

TDA 8374/75 series. So the circuit has one CVBS output (amplitude of 2 VP-P for the

TDA884X series) and the I 2 C-bus control is similar to that of the TDA 8374/75. For the

TDA 885X IC’s the video switch circuit has a second output (amplitude of 1 VP-P ) which

can be set independently of the position of the first output. The input signal for the decoder

is also available on the CVBS1-output.

Therefore this signal can be used to drive the Teletext decoder. If S-VHS is selected for

one of the outputs the luminance and chrominance signals are added so that a CVBS

signal is obtained again.

Sound circuit

The sound bandpass and trap filters have to be connected externally. The filtered

intercarrier signal is fed to a limiter circuit and is demodulated by means of a PLL

demodulator. This PLL circuit tunes itself automatically to the incoming carrier signal so

that no adjustment is required.

The volume is controlled via the I 2 C-bus. The deemphasis capacitor has to be connected

externally. The non-controlled audio signal can be obtained from this pin (via a buffer

stage).

The FM demodulator can be muted via the I 2 C-bus. This function can be used to switchoff the sound during a channel change so that high output peaks are prevented.

The TDA 8840/41/42/46 contain an Automatic Volume Levelling (AVL) circuit which

automatically stabilises the audio output signal to a certain level which can be set by the

viewer by means of the volume control. This function prevents big audio output fluctuations

due to variations of the modulation depth of the transmitter. The AVL function can be

activated via the I 2 C-bus.

Synchronisation circuit

E.G.Data creazione 01/11/99 17.27 16 / 30 F19MANU.doc

The sync separator is preceded by a controlled amplifier which adjusts the sync pulse

amplitude to a fixed level. These pulses are fed to the slicing stage which is operating at

50% of the amplitude. The separated sync pulses are fed to the first phase detector and to

the coincidence detector. This coincidence detector is used to detect whether the line

oscillator is synchronised and can also be used for transmitter identification. This circuit

can be made less sensitive by means of the STM bit. This mode can be used during

search tuning to avoid that the tuning system will stop at very weak input signals. The first

PLL has a very high statical steepness so that the phase of the picture is independent of

the line frequency.

The horizontal output signal is generated by means of an oscillator which is running at

twice the line frequency. Its frequency is divided by 2 to lock the first control loop to the

incoming signal. The time-constant of the loop can be forced by the I 2 C-bus (fast or

slow). If required the IC can select the time-constant depending on the noise content of the

incoming video signal.

The free-running frequency of the oscillator is determined by a digital control circuit which

is locked to the reference signal of the colour decoder. When the IC is switched-on the

horizontal output signal is suppressed and the oscillator is calibrated as soon as all subaddress bytes have been sent. When the frequency of the oscillator is correct the

horizontal drive signal is switched-on. To obtain a smooth switching-on and switching-off

behaviour of the horizontal output stage the horizontal output frequency is doubled during

switch-on and switch-off (slow start/stop). During that time the duty cycle of the output

pulse has such a value that maximum safety is obtained for the output stage.

To protect the horizontal output transistor the horizontal drive is immediately switched off

when a power-on-reset is detected. The drive signal is switched-on again when the normal

switch-on procedure is followed, i.e. all sub-address bytes must be sent and after

calibration the horizontal drive signal will be released again via the slow start procedure.

When the coincidence detector indicates an out-of-lock situation the calibration procedure

is repeated.

The circuit has a second control loop to generate the drive pulses for the horizontal driver

stage. The horizontal output is gated with the flyback pulse so that the horizontal output

transistor cannot be switched-on during the flyback time.

Via the I 2 C-bus adjustments can be made of the horizontal and vertical geometry. The

vertical sawtooth generator drives the vertical output drive circuit which has a differential

output current. For the E-W drive a single ended current output is available. A special

E.G.Data creazione 01/11/99 17.27 17 / 30 F19MANU.doc

feature is the zoom function for both the horizontal and vertical deflection and the vertical

scroll function which are available in some versions. When the horizontal scan is reduced

to display 4:3 pictures on a 16:9 picture tube an accurate video blanking can be switched

on to obtain well defined edges on the screen.

Overvoltage conditions (X-ray protection) can be detected via the EHT tracking pin. When

an overvoltage condition is detected the horizontal output drive signal will be switched-off

via the slow stop procedure but it is also possible that the drive is not switched-off and that

just a protection indication is given in the I 2 C-bus output byte.

The choice is made via the input bit PRD. The IC’s have a second protection input on the

ϕ2 filter capacitor pin. When this input is activated the drive signal is switched-off

immediately and switched-on again via the slow start procedure. For this reason this

protection input can be used as “flash protection”.

The drive pulses for the vertical sawtooth generator are obtained from a vertical

countdown circuit. This countdown circuit has various windows depending on the incoming

signal (50 Hz or 60 Hz and standard or non standard). The countdown circuit can be

forced in various modes by means of the I 2 C-bus. During the insertion of RGB signals

the maximum vertical frequency is increased to 72 Hz so that the circuit can also

synchronise on signals with a higher vertical frequency like VGA. To obtain short switching

times of the countdown circuit during a channel change the divider can be forced in the

search window by means of the NCIN bit. The vertical deflection can be set in the deinterlace mode via the I 2 C bus. To avoid damage of the picture tube when the vertical

deflection fails the guard output current of the TDA 8350/51 can be supplied to the beam

current limiting input. When a failure is detected the RGB-outputs are blanked and a bit is

set (NDF) in the status byte of the I 2 C-bus. When no vertical deflection output stage is

connected thisguard circuit will also blank the output signals. This can be overruled by

means of the EVG bit.

Chroma and luminance processing

The circuits contain a chroma bandpass and trap circuit. The filters are realised by means

of gyrator circuits and

they are automatically calibrated by comparing the tuning frequency with the X-tal

frequency of the decoder. The luminance delay line and the delay for the peaking circuit

are also realised by means of gyrator circuits. The centre frequency of the chroma

bandpass filter is switchable via the I 2 C-bus so that the performance can be optimised for

E.G.Data creazione 01/11/99 17.27 18 / 30 F19MANU.doc

“front-end” signals and external CVBS signals. During SECAM reception the centre

frequency of the chroma trap is reduced to get a better suppression of the SECAM carrier

frequencies. All IC’s have a black stretcher circuit which corrects the black level for

incoming video signals which have a deviation between the black level and the blanking

level (back porch). The timeconstant for the black stretcher is realised internally.

The resolution of the peaking control DAC has been increased to 6 bits. All IC’s have a

defeatable coringfunction in the peaking circuit. Some of these IC’s have a YUV interface

(see table on page 2) so that picture improvement IC’s like the TDA 9170 (Contrast

improvement), TDA 9177 (Sharpness improvement) and TDA 4556/66 (CTI) can be

applied. When the CTI IC’s are applied it is possible to increase the gain of the luminance

channel by means of the GAI bit in subaddress 03 so that the resulting RGB output signals

are not affected.

Colour decoder

Depending on the IC type the colour decoder can decode PAL, PAL/NTSC or

PAL/NTSC/SECAM signals. The PAL/NTSC decoder contains an alignment-free X-tal

oscillator, a killer circuit and two colour difference demodulators. The 90° phase shift for

the reference signal is made internally.

The IC’s contain an Automatic Colour Limiting (ACL) circuit which is switchable via the I 2

C-bus and which prevents that oversaturation occurs when signals with a high chroma-toburst ratio are received. The ACL circuit is designed such that it only reduces the chroma

signal and not the burst signal. This has the advantage that the colour sensitivity is not

affected by this function. The SECAM decoder contains an auto-calibrating PLL

demodulator which has two references, viz: the 4.4 MHz sub-carrier frequency which is

obtained from the X-tal oscillator which is used to tune the PLL to the desired free-running

frequency and the bandgap reference to obtain the correct absolute value of the output

signal. The VCO of the PLL is calibrated during each vertical blanking period, when the IC

is in search or SECAM mode.

The frequency of the active X-tal is fed to the Fsc output (pin 33) and can be used to tune

an external comb filter (e.g. the SAA 4961).

The base-band delay line (TDA 4665 function) is integrated in the PAL/SECAM IC’s and in

the NTSC IC TDA 8846A. In the latter IC it improves the cross colour performance

(chroma comb filter). The demodulated colour difference signals are internally supplied to

the delay line. The colour difference matrix switches automatically between PAL/SECAM

and NTSC, however, it is also possible to fix the matrix in the PAL standard.

E.G.Data creazione 01/11/99 17.27 19 / 30 F19MANU.doc

The “blue stretch” circuit is intended to shift colour near “white” with sufficient contrast

values towards more blue to obtain a brighter impression of the picture.

Which colour standard the IC’s can decode depends on the external X-tals. The X-tal to be

connected to pin 34 must have a frequency of 3.5 MHz (NTSC-M, PAL-M or PAL-N) and

pin 35 can handle X-tals with a frequency of 4.4 and 3.5 MHz. Because the X-tal frequency

is used to tune the line oscillator the value of the X-tal frequency must be given to the IC

via the I 2 C-bus. It is also possible to use the IC in the so called “Tri-norma” mode for

South America. In that case one X-tal must be connected to pin 34 and the other 2 to pin

35. The switching between the 2 latter X-tals must be done externally. This has the

consequence that the search loop of the decoder must be controlled by the µ-computer.

To prevent calibration problems of the horizontal oscillator the external switching between

the 2 X-tals should be carried out when the oscillator is forced to pin 34. For a reliable

calibration of the horizontal oscillator it is very important that the X-tal indication bits (XA

and XB) are not corrupted. For this reason the X-tal bits can be read in the output bytes so

that the software can check the I 2 C-bus transmission.

Under bad-signal conditions (e.g. VCR-playback in feature mode), it may occur that the

colour killer is activated although the colour PLL is still in lock. When this killing action is

not wanted it is possible to overrule the colour killer by forcing the colour decoder to the

required standard and to activate the FCO-bit (Forced Colour On) in the control-5

subaddress.

The IC’s contain a so-called “Dynamic skin tone (flesh) control” feature. This function is

realised in the YUV domain by detecting the colours near to the skin tone. The correction

angle can be controlled via the I 2 C-bus.

RGB output circuit and black-current stabilisation

The colour-difference signals are matrixed with the luminance signal to obtain the RGBsignals. The TDA 884X devices have one (linear) RGB input. This RGB signal can be

controlled on contrast and brightness (like TDA 8374/75). By means of the IE1 bit the

insertion blanking can be switched on or off. Via the IN1 bit it can be read whether the

insertion pin has a high level or not.

The TDA 885X IC’s have an additional RGB input. This RGB signal can be controlled on

contrast, saturation and brightness. The insertion blanking of this input can be switched-off

by means of the IE2 bit. Via the IN2 bit it can be read whether the insertion pin has a high

level or not.

E.G.Data creazione 01/11/99 17.27 20 / 30 F19MANU.doc

The output signal has an amplitude of about 2 volts black-to-white at nominal input signals

and nominal settings of the controls. To increase the flexibility of the IC it is possible to

insert OSD and/or teletext signals directly at the RGB outputs. This insertion mode is

controlled via the insertion input (pin 26 in the S-DIP 56- and pin 38 in the QFP-64

envelope). This blanking action at the RGB outputs has some delay which must be

compensated externally.

To obtain an accurate biasing of the picture tube a “Continuous Cathode Calibration”

circuit has been developed. This function is realised by means of a 2-point black level

stabilisation circuit. By inserting 2 test levels for each gun and comparing the resulting

cathode currents with 2 different reference currents the influence of the picture tube

parameters like the spread in cut-off voltage can be eliminated.

This 2-point stabilisation is based on the principle that the ratio between the cathode

currents is coupled to the ratio between the drive voltages according to:

[ I

The feedback loop makes the ratio between the cathode currents Ik1 and Ik2 equal to the

ratio between the reference currents (which are internally fixed) by changing the (black)

level and the amplitude of the RGB output signals via 2 converging loops. The system

operates in such a way that the black level of the drive signal is controlled to the cut-off

point of the gun so that a very good grey scale tracking is obtained. The accuracy of the

adjustment of the black level is just dependent on the ratio of internal currents and these

can be made very accurately in integrated circuits. An additional advantage of the 2-point

measurement is that the control system makes the absolute value of Ik1 and Ik2 identical

to the internal reference currents. Because this adjustment is obtained by means of an

adaption of the gain of the RGB control stage this control stabilises the gain of the

complete channel (RGB output stage and cathode characteristic).

As a result variations in the gain figures during life will be compensated by this 2-point

loop.

ki

/ I

k2 ]

= [ V

dr1

/ V

dr2

]

An important property of the 2-point stabilisation is that the off-set as well as the gain of

the RGB path is adjusted by the feedback loop. Hence the maximum drive voltage for the

cathode is fixed by the relation between the test pulses, the reference current and the

relative gain setting of the 3 channels. This has the consequence that the drive level of the

CRT cannot be adjusted by adapting the gain of the RGB output stage. Because different

picture tubes may require different drive levels the typical “cathode drive level” amplitude

can be adjusted by means of an I 2 C-bus setting. Dependent on the chosen cathode drive

E.G.Data creazione 01/11/99 17.27 21 / 30 F19MANU.doc

Loading...

Loading...