Page 1

®

57LFC/AN

March 2004

© 2004 Fluke Corporation, All rights reserved.

All product names are trademarks of their respective companies.

System Calibrator

Service Manual

Page 2

LIMITED WARRANTY AND LIMITATION OF LIABILITY

Each Fluke product is warranted to be free from defects in material and workmanship under normal use and

service. The warranty period is one year and begins on the date of shipment. Parts, product repairs, and

services are warranted for 90 days. This warranty extends only to the original buyer or end-user customer of

a Fluke authorized reseller, and does not apply to fuses, disposable batteries, or to any product which, in

Fluke's opinion, has been misused, altered, neglected, contaminated, or damaged by accident or abnormal

conditions of operation or handling. Fluke warrants that software will operate substantially in accordance

with its functional specifications for 90 days and that it has been properly recorded on non-defective media.

Fluke does not warrant that software will be error free or operate without interruption.

Fluke authorized resellers shall extend this warranty on new and unused products to end-user customers

only but have no authority to extend a greater or different warranty on behalf of Fluke. Warranty support is

available only if product is purchased through a Fluke authorized sales outlet or Buyer has paid the

applicable international price. Fluke reserves the right to invoice Buyer for importation costs of

repair/replacement parts when product purchased in one country is submitted for repair in another country.

Fluke's warranty obligation is limited, at Fluke's option, to refund of the purchase price, free of charge repair,

or replacement of a defective product which is returned to a Fluke authorized service center within the

warranty period.

To obtain warranty service, contact your nearest Fluke authorized service center to obtain return

authorization information, then send the product to that service center, with a description of the difficulty,

postage and insurance prepaid (FOB Destination). Fluke assumes no risk for damage in transit. Following

warranty repair, the product will be returned to Buyer, transportation prepaid (FOB Destination). If Fluke

determines that failure was caused by neglect, misuse, contamination, alteration, accident, or abnormal

condition of operation or handling, including overvoltage failures caused by use outside the product’s

specified rating, or normal wear and tear of mechanical components, Fluke will provide an estimate of repair

costs and obtain authorization before commencing the work. Following repair, the product will be returned to

the Buyer transportation prepaid and the Buyer will be billed for the repair and return transportation charges

(FOB Shipping Point).

THIS WARRANTY IS BUYER'S SOLE AND EXCLUSIVE REMEDY AND IS IN LIEU OF ALL OTHER

WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY

OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. FLUKE SHALL NOT BE LIABLE

FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OR LOSSES,

INCLUDING LOSS OF DATA, ARISING FROM ANY CAUSE OR THEORY.

Since some countries or states do not allow limitation of the term of an implied warranty, or exclusion or

limitation of incidental or consequential damages, the limitations and exclusions of this warranty may not

apply to every buyer. If any provision of this Warranty is held invalid or unenforceable by a court or other

decision-maker of competent jurisdiction, such holding will not affect the validity or enforceability of any other

provision.

Fluke Corporation

P.O. Box 9090

Everett, WA 98206-9090

U.S.A.

Fluke Europe B.V.

P.O. Box 1186

5602 BD Eindhoven

The Netherlands

11/99

To register your product online, visit register.fluke.com

Page 3

Claims

Immediately upon arrival, purchaser shall check the packing container against the enclosed

packing list and shall, within thirty (30) days of arrival, give Fluke notice of shortages or any

nonconformity with the terms of the order. If purchaser fails to five notice, the delivery shall be

deemed to conform with the terms of the order.

The purchaser assumes all risk of loss or damage to instruments upon delivery by Fluke to the

carrier. If an instrument is damaged in transit, PURCHASER MUST FILE ALL CLAIMS FOR

DAMAGE WITH THE CARRIER to obtain compensation. Upon request by purchaser, Fluke will

submit an estimate of the cost to repair shipment damage.

Fluke will be happy to answer all questions to enhance the use of this instrument. Please address

your requests or correspondence to: Fluke Corporation, P.O. Box 9090, Everett, WA 98206-9090.

Interference Information

This equipment generates and uses radio frequency energy and if not installed and used in strict

accordance with the manufacturer’s instructions, may cause interference to radio and television

reception. It has been type tested and found to comply with the limits for a Class A computing

device in accordance with the specifications in Subpart J of Part 15 of FCC Rules, which are

designed to provide reasonable protection against such interference in a residential installation.

However, there is no guarantee that interference will not occur in a particular installation. If this

equipment does cause interference to radio or television reception, which can be determined by

turning the equipment off and on, the user is encouraged to try to correct the interference by one

of more of the following measures:

• Reorient the receiving antenna

• Relocate the equipment with respect to the receiver

• Move the equipment away from the receiver

• Plug the equipment into a different outlet so that the computer and receiver are on different

branch circuits

If necessary, the user should consult the dealer or an experienced radio/television technician for

additional suggestions. The user may find the following booklet prepared by the Federal

Communications Commission helpful: How to Identify and Resolve Radio-TV Interference

Problems. This booklet is available from the U.S. Government Printing Office, Washington, D.C.

20402. Stock No. 004-000-00345-4.

Page 4

OPERATOR SAFETY

SUMMARY

XWWARNING

HIGH VOLTAGE

is used in the operation of this equipment

LETHAL VOLTAGE

may be present on the terminals, observe all safety precautions!

To avoid electrical shock hazard, the operator should not

electrically contact the output hi or sense hi binding posts.

During operation, lethal voltages of up to 2200 V ac or dc may

be present on these terminals.

Whenever the nature of the operation permits, keep one hand

away from equipment to reduce the hazard of current flowing

thought vital organs of the body.

Terms in this Manual

This instrument has been designed and tested in accordance with the safety standards listed in

the General Specifications, which are located in Chapter 1 of this manual. This manual contains

information and warnings which have to be followed by the user to ensure safe operation and to

retain the instrument in safe condition.

XWWARNING statements identify conditions or practices that could result in personal injury or

loss of life.

XWCAUTION statements identify conditions or practices that could result in damage to the

equipment or other property.

Symbols Marked on Equipment

X

.

Q

W

Caution, risk of electric shock.

Protective ground (earth) terminal.

Functional earth terminal.

Caution, risk of danger. Refer to the manual to maintain the safety provided by the

equipment.

Page 5

XWWarning

• Do not operate this calibrator in a position where it is difficult to operate

the power switch.

• Do not operate this calibrator in a manner not specified in the manual or

the protection provided by the equipment may be impaired.

• Do not operate the calibrator if it shows signs of damage or malfunction,

the protection provided by the equipment may be impaired.

• Do not use hook-up wire on the calibrator with an insulation or current

rating of less than the calibrator output.

Power Source

The 57LFC is intended to operate from a power source that will not apply more than 246 V ac

rms between the supply conductors or between either supply conductor and ground. A protective

ground connection by way of the grounding conductor in the power cord is essential for safe

operation.

Use the Proper Fuse

To avoid fire hazard, use only the fuse specified on the line voltage selection switch label, and

which is identical in type voltage rating, and current rating.

Grounding the 57LFC

The 57LFC is Safety Class I (grounded enclosure) instruments as defined in IEC 61010 2nd

Edition. The enclosure is grounded through the grounding conductor of the power cord. To avoid

electrical shock, plug the power cord into a properly wired earth grounded receptacle before

connecting anything to any of the 57LFC terminals. A protective ground connection by way of

the grounding conductor in the power cord is essential for safe operation.

Use the Proper Power Cord

• Use only the power cord and connector appropriate for proper operation of a 57LFC.

• Use only a power cord that is in good condition.

• Refer cord and connector changes to qualified service personnel.

Do Not Operate in Explosive Atmospheres

To avoid explosion, do not operate the 57LFC in an atmosphere of explosive gas.

Do Not Remove Cover

To avoid personal injury, do not remove the cover from the 57LFC. Do not operate the 57LFC

without the cover properly installed. There are no user-serviceable parts inside the 57LFC, so

there is no need for the operator to ever remove the cover.

Page 6

SERVICING SAFETY

SUMMARY

FOR QUALIFIED SERVICE

PERSONNEL ONLY

Also refer to the preceding Operator Safety Summary

Do Not Service Alone

Do not perform internal service or adjustment of this product unless another person

capable of rendering first aid and resuscitation is present.

Use Care When Servicing With Power On

Dangerous voltage exist at many points inside this product. To avoid personal injury, do

not touch exposed connections and components while power is on.

Whenever the nature of the operation permits, keep one hand away from equipment to

reduce the hazard of current flowing through vital organs of the body.

Do not wear a grounded wrist strap while working on this product. A grounded wrist strap

increase the risk of current flowing through the body.

Disconnect power before removing protective panels, soldering, or replacing components.

High voltage may still be present even after disconnecting power.

Page 7

FIRST AID FOR ELECTRIC SHOCK

Free the Victim From the Live Conductor

Shut off high voltage at once and ground the circuit. If high voltage cannot be turned off

quickly, ground the circuit.

If the circuit cannot be broken or grounded, use a board, dry clothing, or other

nonconductor to free the victim.

Get Help!

Yell for help. Call an emergency number. Request medical assistance.

Never Accept Ordinary and General Tests for Death

Symptoms of electric shock may include unconsciousness, failure to breathe, absence of

pulse, pallor, and stiffness, and severe burns.

Treat the Victim

If the victim is not breathing, begin CPR or mouth-to-mouth resuscitation if you are

certified.

Page 8

Page 9

Table of Contents

Chapter Title Page

1 Introduction and Specifications ........................................................ 1-1

Introduction........................................................................................................ 1-3

Service Information ........................................................................................... 1-3

Accessories ........................................................................................................ 1-4

Low Thermal EMF Test Leads...................................................................... 1-4

Rack Mount Kit............................................................................................. 1-4

Shielded IEEE-488 Cables (Y8021, Y8022, and Y8023) ............................. 1-4

Contacting Fluke................................................................................................ 1-5

Specifications..................................................................................................... 1-6

General Specifications................................................................................... 1-6

Accuracy Specifications ................................................................................ 1-7

DC Voltage Accuracy ............................................................................... 1-7

DC Current Accuracy................................................................................ 1-7

Resistance Accuracy ................................................................................. 1-7

AC Voltage Accuracy ............................................................................... 1-8

AC Voltage Distortion .............................................................................. 1-9

AC Current Accuracy................................................................................ 1-10

AC Current Distortion............................................................................... 1-11

2 Theory of Operation ........................................................................... 2-1

Introduction........................................................................................................ 2-3

A1 LED PCA..................................................................................................... 2-5

A3 Motherboard PCA........................................................................................ 2-5

Relay Control and Switch Matrix.................................................................. 2-5

LED Control and Output Cables ................................................................... 2-10

Signal Buses .................................................................................................. 2-10

Low Volt Buffer ............................................................................................ 2-10

In-guard Power Supplies ............................................................................... 2-10

Outguard Power Supplies.............................................................................. 2-11

Miscellaneous Circuits .................................................................................. 2-11

Troubleshooting Test Points.......................................................................... 2-12

List of Fuses .................................................................................................. 2-13

A5 Ohms PCA ................................................................................................... 2-13

Precision Resistor Networks.......................................................................... 2-14

i

Page 10

57LFC/AN

Service Manual

Relay Switch Matrix and Control.................................................................. 2-14

Other Control Circuits................................................................................... 2-26

Guard Circuits ............................................................................................... 2-26

Compensation Circuits .................................................................................. 2-27

Monitor...................................................................................................... 2-27

Diagnostics................................................................................................ 2-29

A6 Digital Synthesis PCA ................................................................................. 2-33

Precision, Dual Tracking, +/-7 V References................................................ 2-33

Precision, 28bit, PWM, Dual DAC's ............................................................. 2-33

DC Voltage Operation................................................................................... 2-34

DDS Waveform Generation .......................................................................... 2-34

AC Voltage Operation................................................................................... 2-35

DC Current Operation ................................................................................... 2-35

AC Current Operation ................................................................................... 2-35

Thermocouple Temperature Measurement.................................................... 2-35

Iso-thermal Block Reference Junction Temperature Measurement .............. 2-36

Thermocouple Voltage Measurement: .......................................................... 2-36

Thermocouple Temperature Simulation........................................................ 2-36

Analog to Digital Converter .......................................................................... 2-36

Fault Detection .............................................................................................. 2-36

Digital Control............................................................................................... 2-37

A7 Current PCA................................................................................................. 2-37

Detailed Hardware Description of DC/AC Current....................................... 2-40

Low Current Output Amplifier...................................................................... 2-40

Mid-Current Output Amplifier ...................................................................... 2-41

High Current Output Amplifier ..................................................................... 2-42

High Current Amplifier Power Supplies (Mongo Supplies) ......................... 2-43

A8 High Voltage PCA ....................................................................................... 2-44

Detailed Hardware Description of the 22 V Amplifier ................................. 2-46

Detailed Description of the 220 V Amplifier ................................................ 2-47

Detailed Hardware Description of the High Voltage Regulator.................... 2-49

Heat Sink Temperature Measurement ........................................................... 2-51

Digital Interface and Control......................................................................... 2-51

A9 Out-Guard CPU PCA................................................................................... 2-52

Real Time Clock Memory............................................................................. 2-52

IEEE-488 Interface........................................................................................ 2-52

3 Calibration and Verification............................................................... 3-1

Calibration ......................................................................................................... 3-3

Procedure Architecture.................................................................................. 3-3

ZERO ........................................................................................................ 3-3

MAIN ........................................................................................................ 3-3

DIAG......................................................................................................... 3-3

Calibration Steps ........................................................................................... 3-3

RUN .......................................................................................................... 3-4

Instruction Step (INS) ............................................................................... 3-4

Reference Step (REF) ............................................................................... 3-4

NOT .......................................................................................................... 3-4

Verification Tests............................................................................................... 3-5

Test Equipment.............................................................................................. 3-5

Calibrator Configuration and Pre-check........................................................ 3-6

DC Voltage Test............................................................................................ 3-7

AC Voltage Tests .......................................................................................... 3-9

AC Voltage Accuracy Test ....................................................................... 3-9

ii

Page 11

Contents (continued)

Frequency Accuracy Test.......................................................................... 3-10

DC Current Test ............................................................................................ 3-14

AC Current Test ............................................................................................ 3-15

Current Output Compliance Test................................................................... 3-17

Voltage Output Compliance Test .................................................................. 3-17

Harmonic Test Levels for AC Volts.............................................................. 3-19

Harmonic AC Current Test ........................................................................... 3-21

External Trigger............................................................................................. 3-21

Verification Test Check List.......................................................................... 3-22

4 Maintenance........................................................................................ 4-1

Introduction........................................................................................................ 4-3

Replacing the Fuse............................................................................................. 4-3

Cleaning the Air Filter....................................................................................... 4-4

Replacing PCA Modules ................................................................................... 4-6

Cleaning the Exterior......................................................................................... 4-7

5 List of Replaceable Parts................................................................... 5-1

Introduction........................................................................................................ 5-3

How to Obtain Parts........................................................................................... 5-3

Service Centers .................................................................................................. 5-4

Parts Lists........................................................................................................... 5-4

6 Schematic Diagrams .......................................................................... 6-1

iii

Page 12

57LFC/AN

Service Manual

iv

Page 13

List of Tables

Table Title Page

1-1. 57LFC Accessories ................................................................................................ 1-4

2-1. Functional Description of A3 Motherboard PCA Relays ...................................... 2-6

2-2. A3 Motherboard PCA Power-up and Fault Relay States....................................... 2-7

2-3. A3 Motherboard PCA Final Relay States by Instrument State .............................. 2-8

2-4. Control Register States by Instrument State........................................................... 2-9

2-5. Functional Description of LED Signals ................................................................. 2-10

2-6. A3 Motherboard PCA Test Points List .................................................................. 2-12

2-7. Functional Description of A5 Ohms PCA Relays.................................................. 2-17

2-8. A5 Ohms PCA Power-up and Fault Relay States .................................................. 2-20

2-9. Final Relay States by Instrument State .................................................................. 2-21

2-10. Functional Description of Signals.......................................................................... 2-26

2-11. Compliance Voltage Thresholds............................................................................ 2-28

2-12. OTEST Register States by Instrument State .......................................................... 2-30

2-13. OCHK Register States by Instrument State ........................................................... 2-30

2-14. Diagnostic Values by Instrument State .................................................................. 2-32

2-15. Supply Values as a Function of Ranges................................................................. 2-47

3-1. Recommended Equipment for Calibration and Verification.................................. 3-6

3-2. DC Volts Measurement Limits .............................................................................. 3-8

3-3. AC Volts Measurement Limits .............................................................................. 3-10

3-4. AC Frequency Values ............................................................................................ 3-11

3-5. 4-Wire Ohm Values ............................................................................................... 3-12

3-6. 2-Wire Ohm Values ............................................................................................... 3-13

3-7. DC Current Readings ............................................................................................. 3-14

3-8. AC Current Limits.................................................................................................. 3-16

3-9. Current Output Compliance Limits........................................................................ 3-17

3-10. Voltage Output Compliance Limits ....................................................................... 3-18

3-11. Harmonic Test Values for AC Volts ...................................................................... 3-20

3-12. Harmonic Test Values for AC Current .................................................................. 3-21

5-1. Final Assembly....................................................................................................... 5-5

5-2. A1 LED PCA ......................................................................................................... 5-9

5-3. A3 Motherboard PCA ............................................................................................ 5-10

5-4. A5 Ohms PCA........................................................................................................ 5-18

5-5. A6 Digital Synthesis PCA...................................................................................... 5-23

v

Page 14

57LFC/AN

Service Manual

5-6. A7 Current PCA..................................................................................................... 5-31

5-7. A8 High Voltage PCA ........................................................................................... 5-39

5-8. A9 Out-Guard CPU PCA ....................................................................................... 5-55

vi

Page 15

List of Figures

Figure Title Page

2-1. 57LFC Block Diagram........................................................................................... 2-4

2-2. Block Diagram of the A5 Ohms PCA.................................................................... 2-13

2-3. A5 Ohms PCA High/Low Output .......................................................................... 2-15

2-4. A5 Ohms PCA High/Low Sense............................................................................ 2-16

2-5. DC Current Functions ............................................................................................ 2-38

2-6. AC Current Functions ............................................................................................ 2-39

2-7. A8 High Voltage PCA 22 V and 220 V Amplifier ................................................ 2-45

3-1. 8508A Connections to the 57LFC for DC Volts Measurement............................. 3-7

3-2. 8508A Connections to the 57LFC for AC Volts Measurement............................. 3-9

3-3. 8508A Connections to the 57LFC for AC Frequency Measurement..................... 3-11

3-4. 8508A Connections to the 57LFC for 4-Wire Ohms ............................................. 3-12

3-5. 8508A Connections to the 57LFC for 2-Wire Compensated Ohms....................... 3-13

3-6. 8508A Connections to the 57LFC for DC Current Measurement.......................... 3-14

3-7. 8508A Connections to the 57LFC for AC Current Measurement.......................... 3-15

3-8. 8508A Connections to the 57LFC for Load Current Compliance Test.................. 3-17

3-9. 8508A Connections to the 57LFC for Voltage Compliance Testing ..................... 3-18

3-10. Harmonic Test Setup.............................................................................................. 3-19

4-1. Replacing the Fuse ................................................................................................. 4-4

4-2. Accessing the Air Filter.......................................................................................... 4-5

4-3. Exploded View of the Calibrator ........................................................................... 4-6

5-1. Final Assembly....................................................................................................... 5-7

5-2. A1 LED PCA ......................................................................................................... 5-9

5-3. A3 Motherboard PCA ............................................................................................ 5-17

5-4. A5 Ohms PCA........................................................................................................ 5-22

5-5. A6 Digital Synthesis PCA...................................................................................... 5-30

5-6. A7 Current PCA..................................................................................................... 5-38

5-7. A8 High Voltage PCA ........................................................................................... 5-54

5-8. A9 Out-Guard PCA................................................................................................ 5-59

6-1. A1 LED PCA......................................................................................................... 6-3

6-2. A3 Motherboard PCA............................................................................................ 6-5

6-3. A5 Ohms PCA........................................................................................................ 6-11

6-4. A6 Digital Synthesis PCA...................................................................................... 6-17

6-5. A7 Current PCA..................................................................................................... 6-26

6-6. A8 High Voltage PCA........................................................................................... 6-32

6-7. A9 Out-Guard CPU PCA ....................................................................................... 6-37

vii

Page 16

57LFC/AN

Service Manual

viii

Page 17

Chapter 1

Introduction and Specifications

Title Page

Introduction........................................................................................................ 1-3

Service Information ........................................................................................... 1-3

Accessories ........................................................................................................ 1-4

Low Thermal EMF Test Leads...................................................................... 1-4

Rack Mount Kit............................................................................................. 1-4

Shielded IEEE-488 Cables (Y8021, Y8022, and Y8023) ............................. 1-4

Contacting Fluke................................................................................................ 1-5

Specifications..................................................................................................... 1-6

General Specifications................................................................................... 1-6

Accuracy Specifications ................................................................................ 1-7

DC Voltage Accuracy ............................................................................... 1-7

DC Current Accuracy................................................................................ 1-7

Resistance Accuracy ................................................................................. 1-7

AC Voltage Accuracy ............................................................................... 1-8

AC Voltage Distortion .............................................................................. 1-9

AC Current Accuracy................................................................................ 1-10

AC Current Distortion............................................................................... 1-11

1-1

Page 18

57LFC/AN

Service Manual

1-2

Page 19

Introduction and Specifications

Introduction 1

Introduction

The Fluke Model 57LFC System Calibrator (hereafter called the Calibrator) is a precise

instrument that calibrates a wide variety of electrical measuring instruments. This

calibrator maintains a high accuracy over a wide ambient temperature range, and is able

to test instruments in harsh environments, eliminating the restriction of calibrating only in

a temperature-controlled standards laboratory. With a 57LFC, you can calibrate precision

multimeters that measure ac or dc voltage, ac or dc current, and resistance. The Calibrator

operates in a similar manner to the 57XXA series calibrators.

Specifications are provided at the end of this chapter. The Calibrator is a fullyprogrammable precision source of the following:

• DC voltage to 220 V.

• AC voltage to 220 V rms, with output available from 10 Hz to 100 kHz.

• AC and DC current to 2.2 A, with AC output available from 10 Hz to 20 kHz.

• Resistance in values from 0 Ω to 19 MΩ in 1 and 1.9x.

Features of the calibrator include the following:

• Automatic meter error calculation obtained through using a simple remote adjust.

• Programmable entry limits used for restricting the levels that can be remotely keyed

into the calibrator, preventing access to levels that may be harmful to equipment or

personnel.

• Real-time clock and calendar.

• Offset and scaling modes that simplify linearity testing of multimeters.

• Standard IEEE-488 (GPIB) interface, complying with ANSI/IEEE Standards 488.1-

1987 and 488.2-1987.

• Internal self-testing and diagnostics of analog and digital functions.

• Status LEDs on front panel to indicate standby (yellow), operate (green), high

voltage (red), and fault (red and yellow).

Service Information

Each calibrator is warranted to the original purchaser for a period of one year beginning

on the date received. The warranty is located at the front of this manual.

Service and technical advice for the calibrator is available at Fluke Service Centers. For a

complete list of Fluke Service Centers, visit www.fluke.com.

A worldwide network of Fluke service centers supports Fluke instruments and assists

customers in many ways. Most service centers have standards and calibration laboratories

certified by local national standards organizations. The following is a partial list of the

services provided by most service centers:

• Repair and certified traceable calibration of all Fluke products.

• Certified traceable calibration of many non-Fluke standards and calibrators.

• Worldwide exchange of calibrator internal modules. Delivery inside the U.S.A. is

typically within 48 hours.

• Service agreements with the flexibility to suit your needs. These can be a simple

warranty extension or an agreement that includes on-site support. Calibration service

agreements are also available in many areas.

1-3

Page 20

57LFC/AN

Service Manual

Accessories

• Training programs and seminars, including laboratory metrology, system

applications, and product maintenance.

• Application help and consulting, including system design, hardware selection,

custom software, site evaluation and installation.

• Replacement parts inventory, including recommended spare parts and module kits.

Visit www.fluke.com for locations and phone numbers of authorized Fluke service

centers.

Table 1-1 summarizes the accessories available for the Calibrator. Following the table is

a brief description of each accessory.

Table 1-1. 57LFC Accessories

Model Description

5440A-7002

5440A-7003

Y8021 IEEE-488 Shielded Interface Cable, 1 Meter

Y8022 IEEE-488 Shielded Interface Cable, 2 Meters

Y5537 Rack Mount Kit for 57LFC and 5500A

Low Thermal EMF Test Lead Set with Banana Plugs:

One 4 ft. cable (122 cm) and two 2 ft. (61 cm) cables.

Low Thermal EMF Test Lead Set with Spade Lugs.

Two 4 ft. (122 cm) cables and One 2 ft. (61 cm) cable.

Low Thermal EMF Test Leads

Two types of low thermal test leads are available. These cables are designed to exhibit

low thermal emfs. The types available are:

• Model 5440A-7002. Low Thermal Test Lead cables with banana plugs.

Set includes one 4 ft. (122 cm) cable and two 2 ft. (61 cm) cables. Each cable

includes two conductors and a shield lead.

• Model 5440A-7003. Low Thermal Test Lead cables with spade lugs.

Set includes two 4 ft. (122 cm) cables and one 2 ft. (61 cm) cable. Each cable

includes two conductors and a shield lead. Shield lead has a banana plug connector.

Rack Mount Kit

The rack mount kit provides all the hardware necessary to mount the 57LFC. Rack mount

instructions are included with each kit.

1-4

Shielded IEEE-488 Cables (Y8021, Y8022, and Y8023)

Shielded IEEE-488 cables are available in two lengths (See Table 1-1). The cables attach

the calibrator to any other IEEE-488 device. Each cable has double 24-pin connectors at

both ends to allow stacking. Metric threaded mounting screws are provided with each

connector. Figure 4-2 in Chapter 4 shows the pinout for the IEEE-488 connector.

Page 21

Introduction and Specifications

Contacting Fluke 1

Contacting Fluke

All Calibrators delivered to the Navy, contractors and subcontractors for the RTCASS

program will be repaired and calibrated at the Fluke Technical Support Center in Everett,

Washington. Contact Fluke Technical Support at 1-888-993-5853 or by sending a fax to

1-425-446-6390. The address for the Fluke Technical Support

Center address is:

Fluke Technical Support Center

1420 75th ST SW

Everett, WA 98203-6256

U. S. A.

Once full production is started the following service centers will also maintain and

calibrate the Calibrator in Europe.

FLUKE NEDERLAND B.V.

Customer Support Services

Science Park Eindhoven 5108

5692 EC Son

Netherlands

and in Asia,

FLUKE DEUTSCHLAND GMBH

Customer Support Services

Heinrich Hertz Straße 11

D-34123 Kassel

Germany

FLUKE SOUTH EAST ASIA PTE LTD.

Service Center

83 Clemenceau Avenue

#15-15/06 Ue Square

239920

Singapore

1-5

Page 22

57LFC/AN

Service Manual

Specifications

General Specifications

Factory set IEEE488 address ....... 4

Warm-up Time ...............................Twice the time since last warmed up, to a maximum of 30 minutes

Temperature Performance............ Operating: 0 to 50 °C

Temperature Coefficient............... Temperature Coefficient for temperatures outside tcal ±5 °C is 10% of

Relative Humidity

Altitude

Safety .............................................Designed to comply with IEC 61010-1 2000-1; ANSI/ISA-S82.01-1994;

Analog Low Isolation .................... 20 V

EMC ................................................Designed to comply with IEC 61326-1 2000-11 (EMC) Class A Criteria

Line Power

Settling Time.................................. ≤ 3 to 10 seconds, similar to 5700A.

Chassis Dimensions, H x W x D ... 178 mm x 432 mm x 457 mm (7 in x 17 in x 18 in) maximum

Weight ............................................ Less than 18.15 kg (40 pounds)

Electrical/Signal Interface............. Fluke 5700A/LP equivalent signal interface, AC Mains, IEEE-488, and

Cooling........................................... 1.42 cubic meters (50 cubic feet) per minute

The 57LFC System Calibrators are verified and calibrated at the factory prior to shipment

to ensure they meet the accuracy standards required for all certified calibration

laboratories. By calibrating to the specifications in this chapter, you can maintain the high

performance level throughout the life of your calibrator.

Specifications are valid after a warm-up period of twice the time the calibrator has been

turned off, up to a maximum of 30 minutes. For example, if the calibrator has been turned

off for five minutes, the warm-up period is ten minutes.

To ensure the validity of the specifications, a dc zeros calibration must be performed at

least every 15 days. If more than 15 days elapse without a dc zeros calibration a warning

message appears. This procedure does not require any external equipment or connections

and takes approximately 5 minutes to complete.

Calibration: 15 to 37.7 °C

Storage: -40 to 75 °C

the 1-year spec per °C.

Operating: ................................... <95% to 43 °C (non-condensing), <40% to 50 °C.

Storage:....................................... <95%, non-condensing

Operating: ...................................3,050 m (10,000 ft) maximum

Non-operating: ........................... 12,200 m (40,000 ft) maximum

CAN/CSA-C22.2 No. 1010.1-92

C

Line Voltage (selectable): ........... 100 V, 120 V, 208 V, and 230 V

Line Frequency: .......................... 47 to 63 Hz

Line Voltage Variation: ................±7% about line voltage setting

Maximum VA: ............................. 200

RS-232 connectors, AC power switch, and Line Voltage selection all on

front panel

1-6

XWCaution

Internal damage may occur if excessive external power is

applied to the binding posts while the instrument is operating in

current, voltage, or ohms. In voltage and current, exceeding

30 V may cause damage. In ohms, do not exceed the maximum

specified current.

Page 23

Introduction and Specifications

Specifications 1

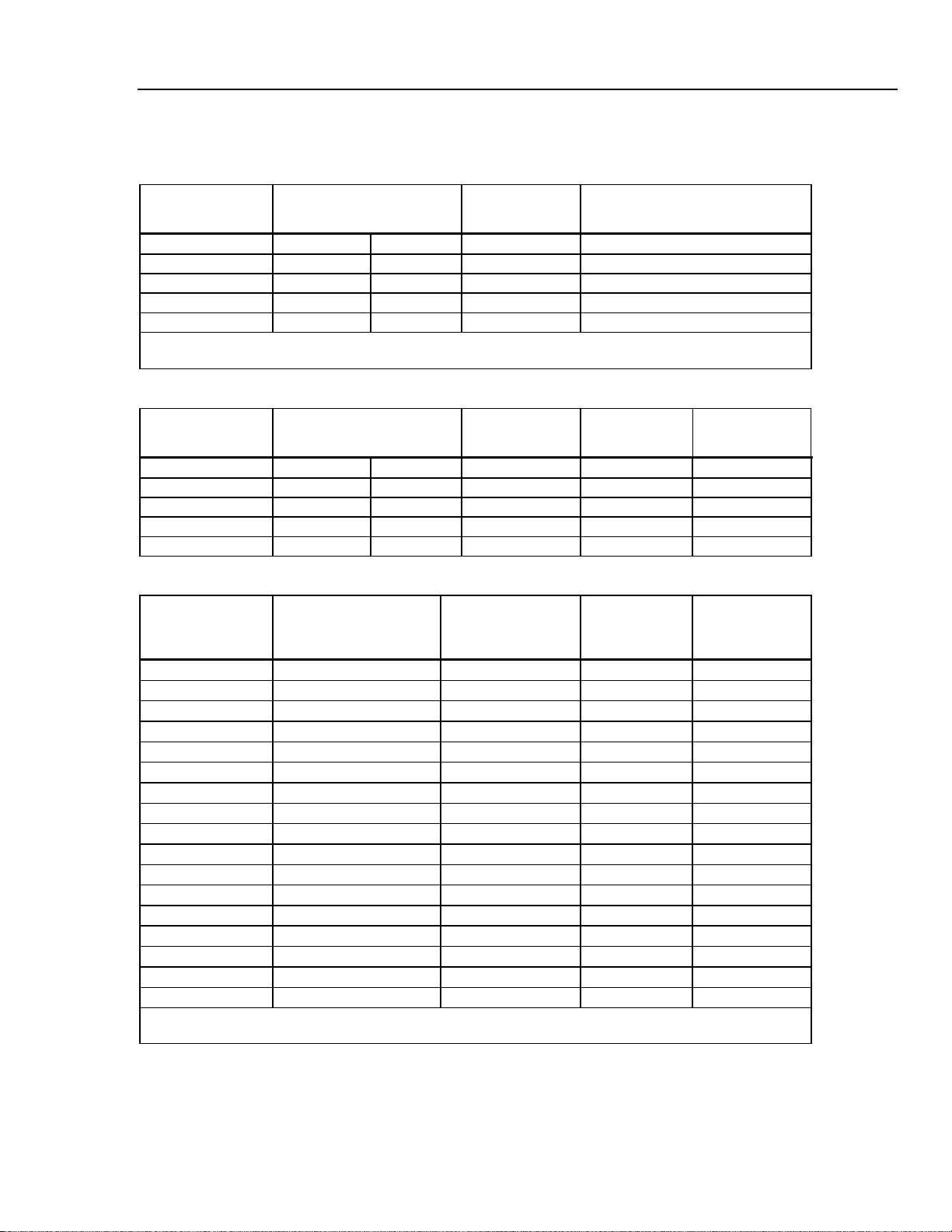

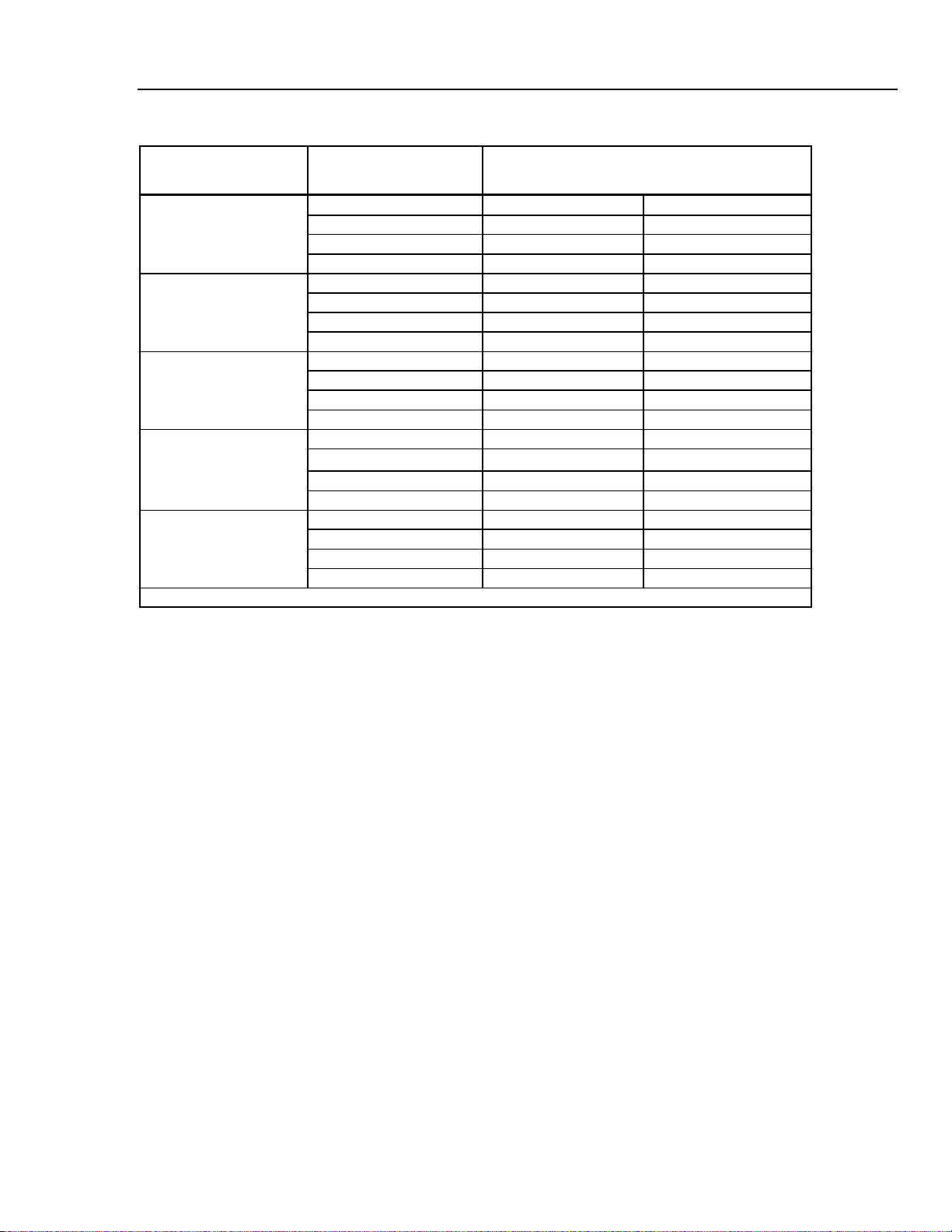

Accuracy Specifications

DC Voltage Accuracy

Ranges

0 mV to 220 mV 0.004% 3 µV 0.1 µV

Absolute Uncertainty,

tcal ±5 °C

±(% output + V) 1 Year

Resolution

50 Ω output impedance

0 V to 2.2 V 0.0025% 3 µV 1 µV 50 mA

0 V to 11 V 0.0025% 30 µV 10 µV 50 mA

0 V to 22 V 0.0025% 30 µV 10 µV 50 mA

0 V to 220 V 0.004% 300 µV 100 µV 20 mA

[1] Remote sensing provided on all but 220 mV range.

Note: minimum output 0 V for all ranges.

Maximum Burden

[1]

DC Current Accuracy

Ranges

0 µA to 220 µA 0.05% 0.02 µA

Absolute Uncertainty,

tcal ±5°C±

(% of output + A) 1 year

Resolution

1 ηA

0 mA to 2.2 mA 0.05% 0.05 µA 0.01 µA 10 V 400 µH

0 mA to 22 mA 0.05% 0.25 µA 0.1 µA 10 V 400 µH

0 mA to 220 mA 0.05% 2.5 µA 1 µA 10 V 400 µH

0 A to 2.2 A 0.07% 40 µA 10 µA 4 V 400 µH

Maximum

Compliance

Voltage

Maximum Inductive

Load

10 V 400 µH

Resistance Accuracy

Absolute Uncertainty of

Nominal Resistance

Value

[1]

0 Ω 0.001 Ω

1 Ω 0.001 Ω

1.9 Ω 0.002 Ω

10 Ω 0.004 Ω

19 Ω 0.008 Ω

100 Ω 0.01 Ω

190 Ω 0.02 Ω

1 kΩ 0.1 Ω

1.9 kΩ 0.2 Ω

10 kΩ 1 Ω

19 kΩ 2 Ω

100 kΩ 10 Ω

190 kΩ 20 Ω

1 MΩ 100 Ω

1.9 MΩ 200 Ω

10 MΩ 4 kΩ

19 MΩ 10 kΩ

[1] Discrete resistors with characterized values stored in non-volatile memory. Specifications apply to the characterized value using 4-wire connections.

[2] Active two-wire compensation may be selected for values up to 190 kΩ. Active compensation is 11 mA load and 2 V burden minimum.

Characterized Value,

tcal ± 5 °C

± (Ω) 1 Year

Full Specification

Current

Maximum Peak

Current

8 mA to 200 mA 220 mA 0.001

8 mA to 100 mA 220 mA 0.001

8 mA to 100 mA 220 mA 0.001

8 mA to 11 mA 220 mA 0.001

8 mA to 11 mA 160 mA 0.001

8 mA to 11 mA 70 mA 0.001

8 mA to 11 mA 50 mA 0.001

1 mA to 2 mA 22 mA 0.010

1 mA to 1.5 mA 16 mA 0.010

0.1 mA to 0.5 mA 3 mA 0.100

0.05 mA to 0.25 mA 1.6 mA 0.200

0.01 mA to 0.1 mA 0.3 mA 1.000

5 µA to 50 µA 0.16 mA 2.000

5 µA to 20 µA 30 µA NA

2.5 µA to 10 µA 16 µA NA

0.5 µA to 2 µA 3 µA NA

0.25 µA to 1 µA 1.6 µA NA

Two-Wire Active

Compensation

Adder (ohms)

[2]

1-7

Page 24

57LFC/AN

Service Manual

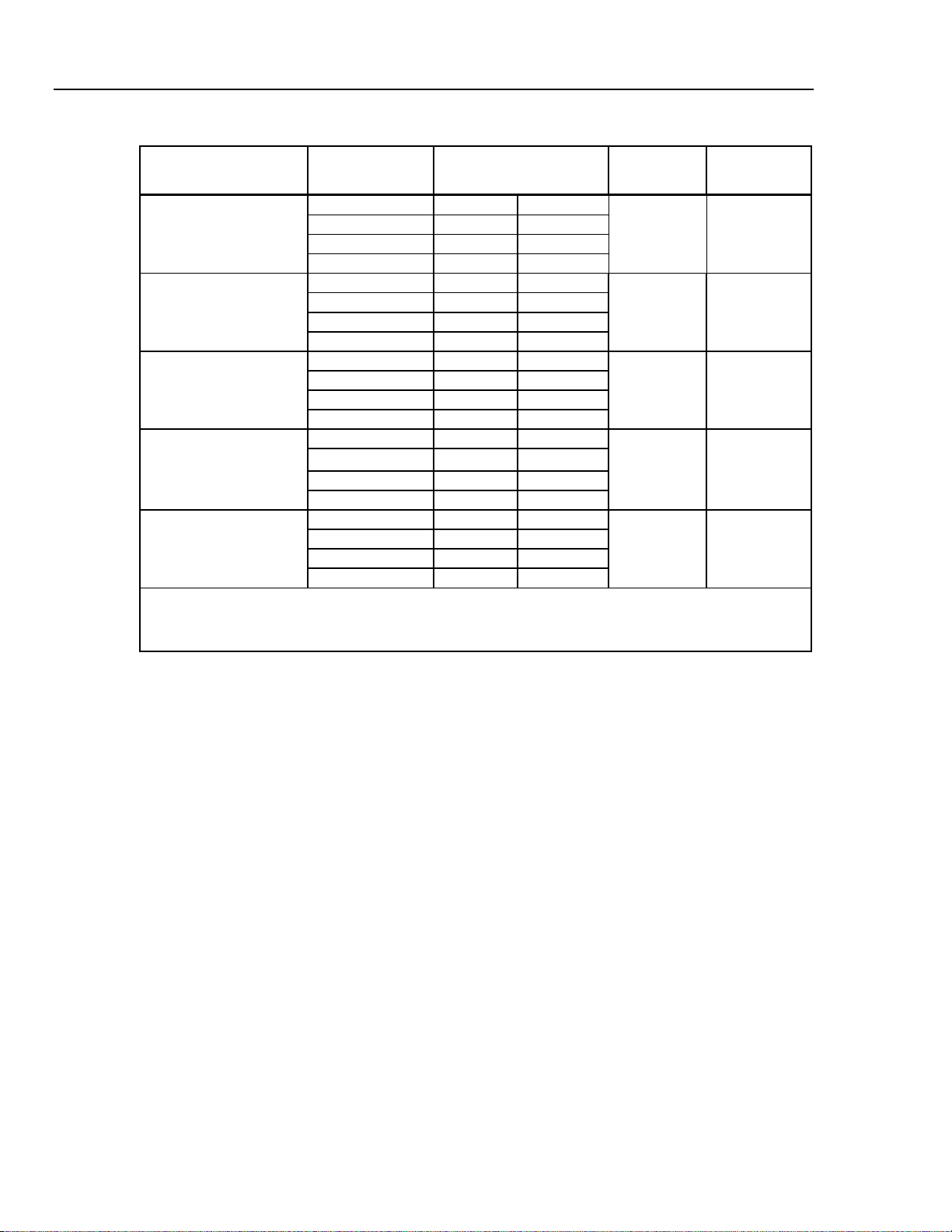

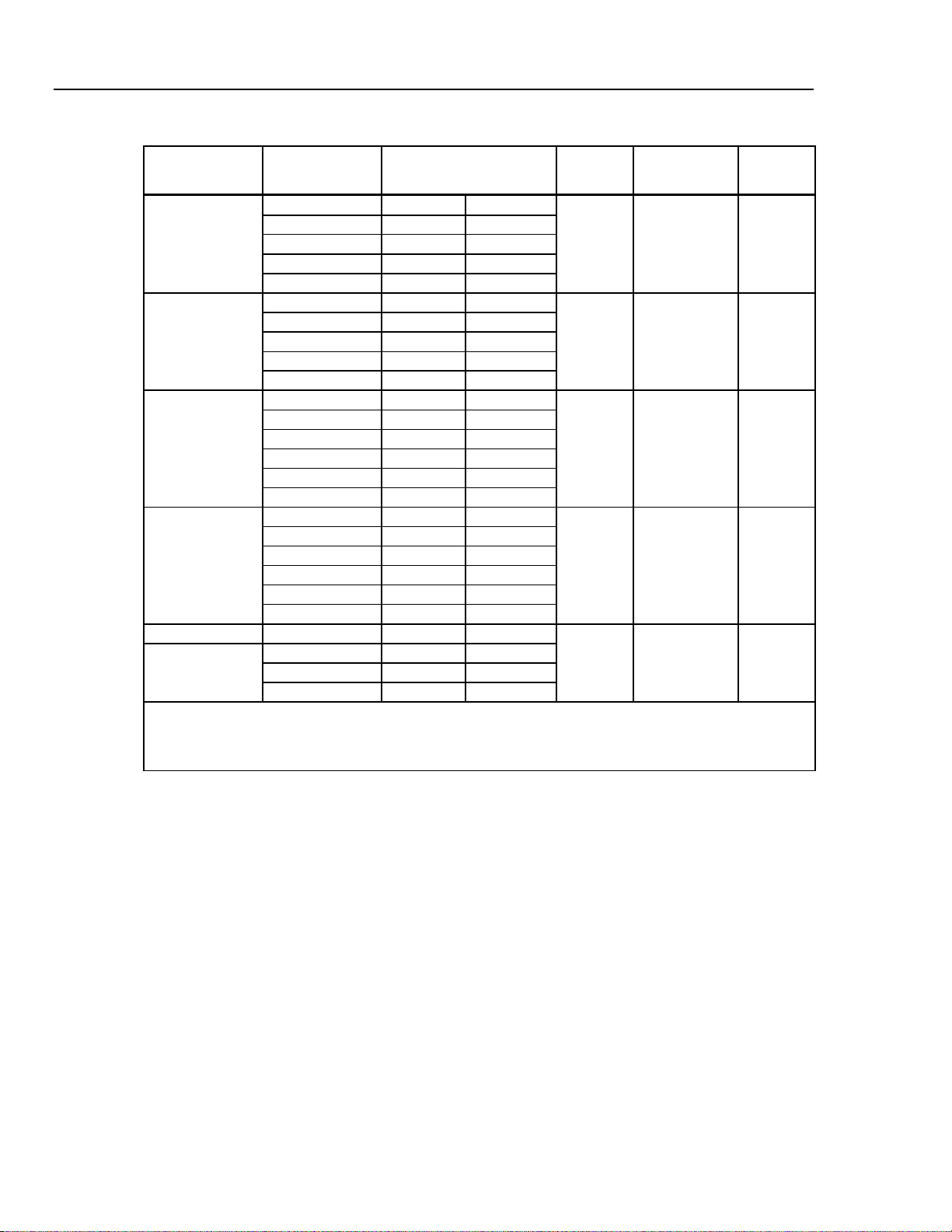

AC Voltage Accuracy

Ranges Frequency

10 mV to 22 mV

10 Hz to 45 Hz 0.15% 20 µV

45 Hz to 20 kHz 0.08% 20 µV

20 kHz to 50 kHz 0.25% 20 µV

Absolute Uncertainty,

tcal ±5 °C

± (% output + V) 1 year

Resolution

1 µV

Maximum

Burden

[1] [2]

50 Ω output

impedance

50 kHz to 100 kHz 0.5% 50 µV

22 mV to 220 mV

10 Hz to 45 Hz 0.15% 50 µV

45 Hz to 20 kHz 0.05% 50 µV

20 kHz to 50 kHz 0.25% 50 µV

1 µV

50 Ω output

impedance

50 kHz to 100 kHz 0.4% 200 µV

0.22 V to 2.2 V

10 Hz to 45 Hz 0.1% 250 µV

45 Hz to 20 kHz 0.05% 100 µV

20 kHz to 50 kHz 0.1% 320 µV

10 µV 50 mA

50 to 100 kHz 0.25% 2000 µV

2.2 V to 22 V

10 Hz to 45 Hz 0.1% 1 mV

45 Hz to 20 kHz 0.05% 1 mV

20 kHz to 50 kHz 0.1% 1 mV

100 µV 50 mA

50 kHz to 100 kHz 0.25% 2 mV

22 V to 220 V

[2]

10 Hz to 45 Hz 0.1% 10 mV

45 Hz to 20 kHz 0.05% 10 mV

20 kHz to 50 kHz 0.25% 20 mV

1 mV 20 mA

50 kHz to 100 kHz 0.5% 50 mV

[1] Remote sensing provided on all but 22 mV and 220 mV ranges. Maximum output current is reduced by 50% above 40 °C. Maximum load capacitance

is 500 pF.

[2] V x Hz limited to 11.8e6.

Note: Frequency uncertainty is specified to be 0.01% of frequency setting.

1-8

Page 25

Introduction and Specifications

Specifications 1

AC Voltage Distortion

Max Distortion and noise

Ranges Frequency

10 mV to 22 mV

22 mV to 220 mV

0.22 V to 2.2 V

2.2 V to 22 V

22 V to 220 V

[1] For larger resistive loads, multiply uncertainty specifications by (actual load/maximum full load for accuracy)2.

10 Hz to 45 Hz 0.15% 90 µV

45 Hz to 20 kHz 0.035% 90 µV

20 kHz to 50 kHz 0.15% 90 µV

50 kHz to 100 kHz 0.25% 90 µV

10 Hz to 45 Hz 0.15% 90 µV

45 Hz to 20 kHz 0.035% 90 µV

20 kHz to 50 kHz 0.15% 90 µV

50 kHz to 100 kHz 0.20% 90 µV

10 Hz to 45 Hz 0.15% 200 µV

45 Hz to 20 kHz 0.035% 200 µV

20 kHz to 50 kHz 0.15% 200 µV

50 kHz to 100 kHz 0.20% 200 µV

10 Hz to 45 Hz 0.15% 2 mV

45 Hz to 20 kHz 0.035% 2 mV

20 kHz to 50 kHz 0.2% 2 mV

50 kHz to 100 kHz 0.5% 2 mV

10 Hz to 45 Hz 0.15% 10 mV

45 Hz to 20 kHz 0.05% 10 mV

20 kHz to 50 kHz 0.8% 10 mV

50 kHz to 100 kHz 1.0% 10 mV

10 Hz to 10 MHz Bandwidth

±(% output + V)

[1]

1-9

Page 26

57LFC/AN

Service Manual

AC Current Accuracy

Ranges

[3]

Frequency

10 Hz to 20 Hz

20 Hz to 45 Hz

30 µA to 220 µA

45 Hz to 1 kHz

1 kHz to 5 kHz

5 kHz to 10 kHz

10 Hz to 20 Hz

20 Hz to 45 Hz

0.22 mA to 2.2 mA

45 Hz to 1 kHz

1 kHz to 5 kHz

5 kHz to 10 kHz

10 Hz to 20 Hz

20 Hz to 45 Hz

2.2 mA to 22 mA

45 Hz to 1 kHz

1 kHz to 5 kHz

5 kHz to 10 kHz

10 kHz to 20 kHz

10 Hz to 20 Hz

20 Hz to 45 Hz

22 mA to 220 mA

45 Hz to 1 kHz

1 kHz to 5 kHz

5 kHz to 10 kHz

10 kHz to 20 kHz

0.22 A to 2.2 A

10 Hz to 45 Hz

45 Hz to 1 kHz

1 kHz to 5 kHz

5 kHz to 10 kHz

[1] 400 µH with inductive compensation ON.

[2] See AC Current Compliance Adder and Distortion Table for impact of compliance voltage on specification.

[3] I-guard, (as on the 5700A rear panel), required when sourcing low-level currents through a long cable.

Note: Frequency uncertainty is specified to be 0.01% of frequency setting.

Absolute Uncertainty,

tcal ±5 °C

±(% of output + A) 1 year

Resolution

0.3% 0.2 µA

0.15% 0.2 µA

0.125% 0.2 µA

0.01 µA 7 V 50 µH

0.4% 0.3 µA

1.5% 0.4 µA

0.2% 0.3 µA

0.15% 0.3 µA

0.1% 0.3 µA

0.1 µA 7 V 50 µH

0.2% 0.3 µA

0.8% 0.5 µA

0.2% 3 µA

0.1% 3 µA

0.1% 3 µA

0.2% 3 µA

1 µA 7 V 50 µH

0.4% 5 µA

0.8% 5 µA

0.18% 30 µA

0.1% 30 µA

0.1% 30 µA

0.3% 50 µA

10 µA 7 V 50 µH

0.4% 100 µA

0.8% 200 µA

0.18% 300 µA 100 µA 4 V 2.5 µH

0.1% 300 µA

1% 3000 µA

5% 5000 µA

Maximum

Compliance

Voltage (rms)

[2]

Maximum

Inductive

[1]

Load

1-10

Page 27

Introduction and Specifications

Specifications 1

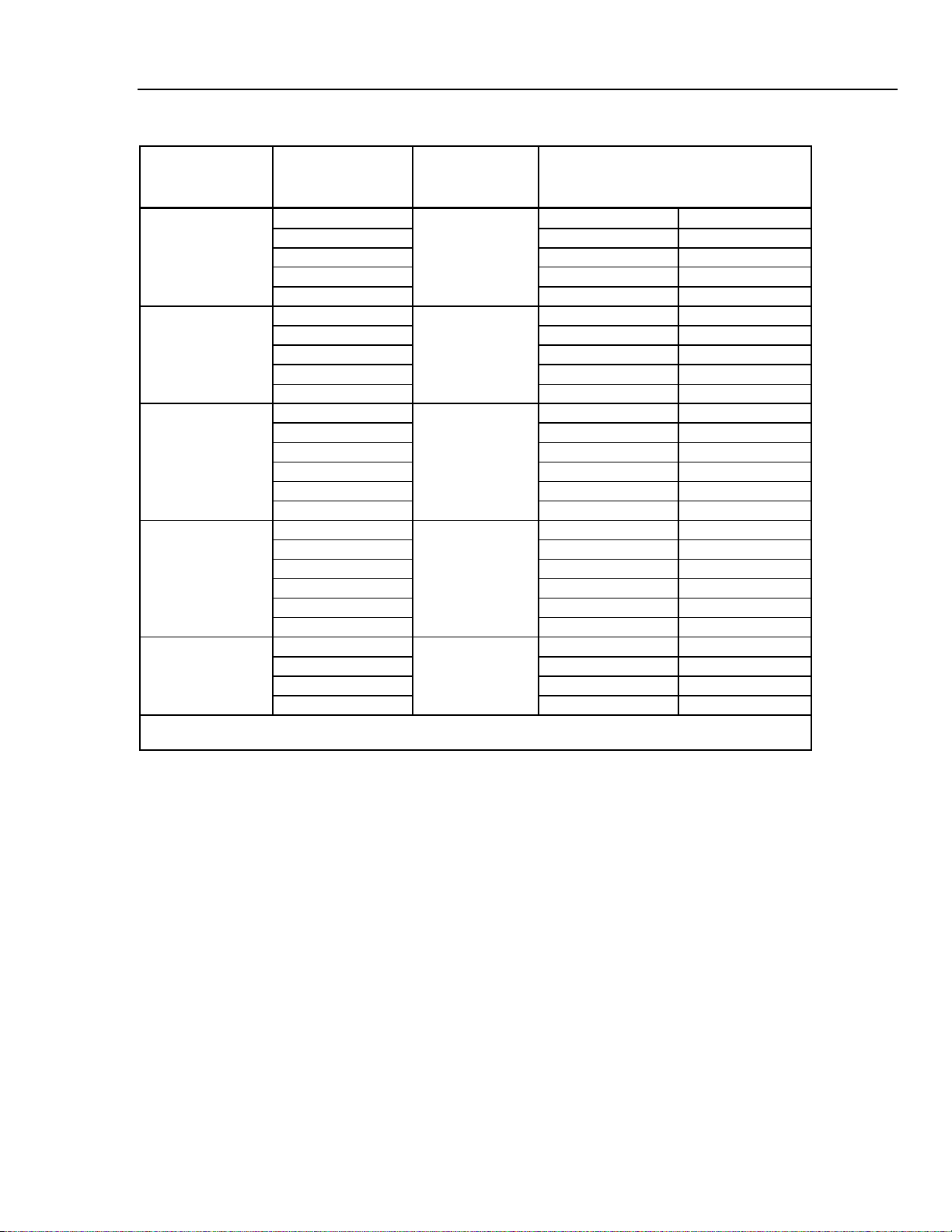

AC Current Distortion

Maximum Resistive

Ranges Frequency

Load For Full

Accuracy Ω

[1]

10 Hz to 20 Hz 0.15% 0.5 µA

20 Hz to 45 Hz 0.1% 0.5 µA

30 µA to 220 µA

45 Hz to 1 kHz 0.05% 0.5 µA

20 kΩ

1 kHz to 5 kHz 0.5% 0.5 µA

5 kHz to 10 kHz

1.0% 0.5 µA

10 Hz to 20 Hz 0.15% 1.5 µA

20 Hz to 45 Hz 0.06% 1.5 µA

10 k

0.22 mA to 2.2 mA

45 Hz to 1 kHz 0.05% 1.5 µA

Ω

1 kHz to 5 kHz 0.5% 1.5 µA

5 kHz to 10 kHz

1.0% 1.5 µA

10 Hz to 20 Hz 0.15% 5 µA

20 Hz to 45 Hz 0.05% 5 µA

2.2 mA to 22 mA

45 Hz to 1 kHz 0.07% 5 µA

1 kHz to 5 kHz 0.3% 5 µA

3.18 k

Ω

5 kHz to 10 kHz 0.7% 5 µA

10 kHz to 20 kHz

1.0% 5 µA

10 Hz to 20 Hz 0.15% 50 µA

20 Hz to 45 Hz 0.05% 50 µA

22 mA to 220 mA

45 Hz to 1 kHz 0.07% 50 µA

1 kHz to 5 kHz 0.30% 50 µA

318

Ω

5 kHz to 10 kHz 0.70% 50 µA

10 kHz to 20 kHz

1.0% 50 µA

10 Hz to 45 Hz 0.2% 500 µA

0.22 A to 2.2 A

[1] For larger resistive loads, multiply uncertainty specifications by actual load/maximum full load for accuracy.

Note: Current times Load cannot exceed the maximum compliance voltage.

45 Hz to 1 kHz 0.07% 500 µA

1 kHz to 5 kHz 1.0% 500 µA

5 Hz to 10 kHz

18 Ω

2.0% 500 µA

Max Distortion & Noise

10 Hz to 50 kHz BW

<0.5V Burden

±(%output + A)

1-11

Page 28

57LFC/AN

Service Manual

1-12 2-1

Page 29

Chapter 2

Theory of Operation

Title Page

Introduction........................................................................................................ 2-3

A1 LED PCA..................................................................................................... 2-5

A3 Motherboard PCA........................................................................................ 2-5

Relay Control and Switch Matrix.................................................................. 2-5

LED Control and Output Cables ................................................................... 2-10

Signal Buses .................................................................................................. 2-10

Low Volt Buffer ............................................................................................ 2-10

In-guard Power Supplies ............................................................................... 2-10

Outguard Power Supplies.............................................................................. 2-11

Miscellaneous Circuits .................................................................................. 2-11

Troubleshooting Test Points.......................................................................... 2-12

List of Fuses .................................................................................................. 2-13

A5 Ohms PCA ................................................................................................... 2-13

Precision Resistor Networks.......................................................................... 2-14

Relay Switch Matrix and Control.................................................................. 2-14

Other Control Circuits................................................................................... 2-26

Guard Circuits ............................................................................................... 2-26

Compensation Circuits .................................................................................. 2-27

Monitor...................................................................................................... 2-27

Diagnostics................................................................................................ 2-29

A6 Digital Synthesis PCA ................................................................................. 2-33

Precision, Dual Tracking, +/-7 V References................................................ 2-33

Precision, 28bit, PWM, Dual DAC's ............................................................. 2-33

DC Voltage Operation................................................................................... 2-34

DDS Waveform Generation .......................................................................... 2-34

AC Voltage Operation................................................................................... 2-35

DC Current Operation ................................................................................... 2-35

AC Current Operation ................................................................................... 2-35

Thermocouple Temperature Measurement.................................................... 2-35

Iso-thermal Block Reference Junction Temperature Measurement .............. 2-36

Thermocouple Voltage Measurement: .......................................................... 2-36

Thermocouple Temperature Simulation........................................................ 2-36

Analog to Digital Converter .......................................................................... 2-36

Fault Detection .............................................................................................. 2-36

Digital Control............................................................................................... 2-37

A7 Current PCA................................................................................................. 2-37

Page 30

57LFC/AN

Service Manual

Detailed Hardware Description of DC/AC Current....................................... 2-40

Low Current Output Amplifier...................................................................... 2-40

Mid-Current Output Amplifier ...................................................................... 2-41

High Current Output Amplifier ..................................................................... 2-42

High Current Amplifier Power Supplies (Mongo Supplies) ......................... 2-43

A8 High Voltage PCA ....................................................................................... 2-44

Detailed Hardware Description of the 22 V Amplifier ................................. 2-46

Detailed Description of the 220 V Amplifier ................................................ 2-47

Detailed Hardware Description of the High Voltage Regulator.................... 2-49

Heat Sink Temperature Measurement ........................................................... 2-51

Digital Interface and Control......................................................................... 2-51

A9 Out-Guard CPU PCA................................................................................... 2-52

Real Time Clock Memory............................................................................. 2-52

IEEE-488 Interface........................................................................................ 2-52

2-2

Page 31

Theory of Operation

Introduction 2

Introduction

This Chapter is intended to provide a detailed description and analysis, where

appropriate, of the printed circuit board assemblies (PCAs) used in the 57LFC System

Calibrator. The Calibrator contains the following PCAs.

• A1 LED PCA

• A3 Motherboard PCA

• A5 Ohms PCA

• A6 Digital Synthesis PCA

• A7 Current PCA

• A8 High Voltage PCA

• A9 Out-Guard CPU PCA

See Figure 2-1 for a block diagram of the 57LFC System Calibrator.

2-3

Page 32

57LFC/AN

Service Manual

A9

Outguard

Controller

IEEE488

RS232

Mains

Transformer

A6

Inguard

Controller

A3

Outguard

Power

±12 V

+5 V

A3

Inguard

Power

±15 V

±5 V

+6 V

A6

Digital

Synthesis &

Reference

0 to ±2.2 V

AC/DC

S

W

I

T

C

H

A3

Output

Switch

A5

OHMS

0 to 19 M

A7

Current

0 to ±2.2 A

AC/DC

Binding

Posts

S

W

I

T

C

H

S

W

I

T

C

H

2-4

A3

High

Voltage

Power

±45 V

±180 V

Figure 2-1. 57LFC Block Diagram

A8

High

Voltage

2 to ±220 V

AC/DC

S

W

I

T

C

H

apv101f.eps

Page 33

Theory of Operation

A1 LED PCA 2

A1 LED PCA

The Calibrator front panel A1 LED PCA provides the only visual indication of the

instrument operation. These LEDs provide a color-coded scheme for the instrument

status.

XWWarning

This instrument is capable of outputting lethal voltages.

Observe all safety precautions.

While the LEDs should provide years of operation, they are

subject to wear out like any other component. Never touch the

binding posts without first checking the output with a

multimeter.

The front panel A1 LED PCA is connected to and controlled by the A3 Motherboard

PCA. A cable is used to connect the A3 Motherboard PCA to the A1 LED PCA. On

power up, the yellow LED will light indicating that the instrument has moved into a

standby state. The green LED is used to indicate that the instrument is in operate and

there may be live voltages on the binding posts. The red LED is used to indicate that the

instrument may be outputting hazardous voltages greater than 30 V rms. If diagnostic

failures occur during power-up, both the yellow and red LEDs light. If all three LEDs are

lit, the instrument is broken and must be sent to a qualified technician for repair.

A3 Motherboard PCA

The following discussion covers the theory of operations for the A3 Motherboard PCA

circuits. This A3 Motherboard PCA generally carries power as well as system signal

buses to the circuit cards. The A3 Motherboard PCA can be divided into several areas: 1)

relay control and switch matrix, 2) LED control and output cables, 3) analog and digital

buses, 4) low volt buffer, 5) in-guard power supplies, 6) out-guard power supplies, 7)

miscellaneous circuits, and 8) list of fuses. Please refer to the A3 Motherboard PCA

schematics for this discussion.

The A3 Motherboard PCA contains lethal voltages. Only

qualified technicians should do troubleshooting.

Relay Control and Switch Matrix

The relay matrix is shown on Sheet 1 of the A3 Motherboard PCA schematic, and the

relay control is shown on Sheet 5. Some of the purposes of the relay matrix are to provide

isolation between the output binding posts and the internal circuitry during standby, and

provide isolation when running zero calibration or diagnostics. The functions of the

relays are shown in Table 2-1. The relay control circuits consist of U3, U5, U6, U8, and

U9. For U3 (74HC138), the IG_CS1 signal is generated on the A6 Digital Synthesis

PCA. U8 selects the driver latch used to set or reset the latching relays.

XWWarning

2-5

Page 34

57LFC/AN

Service Manual

Relay Functional Description

K1 Reset: connect LO’s to the A6 Digital Synthesis PCA; connect OUT_LO to the A6 Digital

K2 Reset: select internal sensing; connect OSNS_HI to IN_SNS_HI and OSNS_LO to

K3 Reset: connect the Digital Synthesis PCA divider; connect IN_SNS_HI to the A6 VDIV

K4 Reset: select VMID for output; connect VMID to OUT_HI

K5 Reset: select external guard; disconnect GUARD from SCOM

Table 2-1. Functional Description of A3 Motherboard PCA Relays

Synthesis PCA RET_LO, and connects IN_SNS_LO to the A6 SNS_LO

Set: disconnect LO’s from the A6 Digital Synthesis PCA; disconnect the A6 Digital

Synthesis PCA RET_LO and SNS_LO from the LO input terminals

IN_SNS_LO

Set: select remote sensing; connect SNS_HI to IN_SNS_HI and SNS_LO to

IN_SNS_LO

Set: disconnect the Digital Synthesis PCA divider; disconnect IN_SNS_HI from VDIV

Set: disconnect VMID from output; disconnect VMID from OUT_HI

Set: select internal guard; connect GUARD to SCOM

K6 Reset: select the 2 V buffer amp; connect V3BUF to VMID for output

Set: disconnect the 2 V buffer amp; disconnect V3BUF from VMID

K7 Reset: disconnect the A8 High Voltage PCA output; disconnect OUT_220V from

OUT_HI

Set: select the A8 High Voltage PCA output; connect OUT_220V to OUT_HI

K8 Reset: disconnect HIGUARD (IGUARD) from GUARD (VGUARD)

Set: connect HIGUARD to GUARD

K9 Reset: connect A6 Digital Synthesis PCA LO return; connect OUT_LO to A6_RET_LO

Set: disconnect the A6 Digital Synthesis PCA LO return, disconnect OUT_LO from

A6_RET_LO

K10 Reset: provide an internal VMID sense path, connect VMID to the A6 VDIV

Set: normal operation; disconnect VMID from VDIV

K11 Reset: provide an internal 220 V sense path; connect OUT_220V to VMID

Set: normal operation; disconnect OUT_220V from VMID

On power up, the relays are forced into a benign setting to protect circuitry and the

customer. Table 2-2 shows the state of the A3 Motherboard PCA relays after power up.

Table 2-3 shows the A3 Motherboard PCA relay states when in several states (power up

and standby). Table 2-4 shows the status of control lines for all modes of A3

Motherboard PCA operation.

2-6

Page 35

Theory of Operation

Table 2-2. A3 Motherboard PCA Power-up and Fault Relay States

Relay State on Power-up or after Fault

K1 Set: disconnect A6 Digital Synthesis PCA LO sense

K2 Reset: select internal sensing

K3 Set: disconnect the A6 Digital Synthesis PCA divider

K4 Set: disconnect VMID from output

K5 Reset: select external guard

K6 Undefined

K7 Reset: disconnect the A8 High Voltage PCA output

K8 Undefined

K9 Set: disconnect the A6 Digital Synthesis PCA LO return

K10 Undefined

K11 Undefined

A3 Motherboard PCA 2

2-7

Page 36

57LFC/AN

Service Manual

Table 2-3. A3 Motherboard PCA Final Relay States by Instrument State

Guard:

Sense:

Relay (Virtual) Register:

Relay:

Instrument State\Bit

Power Up r s s s r s r s s r s 03ad

Dormant r s s s r s r s s r s 03ad

External Guard (mod

mask 0010h)

Internal Guard x x x x x x s x x x x 0010 0010

Internal Sense (mod mast

002h)

External Sense x x x x x x x x x s x 000 2 0002

22 mV A6 Output r s r s r s g r s r r 02a4 02b4 - -

Standby 22 mV A6

Output

220 mV A6 Output r s r s r s g r s r r 02a4 02b4 - -

Standby 220 mV A6

Output

Optt 3.3 V A6 Output

using LO Comp Amp

Opt 3.3 V A6 Output r s r s r s g r r d r 0210 02b0 02a2 02b2

Standby Opt 3.3 A6

Output

2.2 V Buffer Out using LO

Comp Amp

2.2 V Buffer Output r s r s r r g r r d r 0280 0290 0282 0292

Standby 2.2 V Buffer

Output

22 V A8 Output using LO

Comp Amp

22 V A8 Output r s r s r s g r r d r 02a0 02b0 02a2 02b2

Standby 22 V A8 Output r s s s r s r s s r s 03ad

220 V A8 Output Using

LO Comp Amp

220 V A8 Output r s r s s s g s r d r 02e8 02f8 02ea 02fa

Standby 220 V A8 Output r s s s r s r s s r s 03ad

Ohms A5 Output 4-Wire r s s r r s g s s s s - - 032f 033f

Standby Ohms A5 4W r s s r r s r s s r s 032d

Ohms A5 Output 2-Wire r s s r r s g s s r s 032d 033d - -

Standby Ohms A5 2W r s s r r s r s s r s 032d

Ohms A5 Out 2W Comp r s s r r s g s s d s 032d 033d 032f 033f

Standby A5 2W Comp r s s r r s r s s r s 032d

Current A7 Output r s s r r s g s s s s 032f 033f - -

Standby Current A7

Output

TC A10 Output r s s s r s g s s r s 03ad 03bd - -

Standby TC A10 Output r s s s r s r s s r s 03ad

Internal Measure Opt

3.3 V A6 Output

Internal Measure 2.2 V

Buffer Output

Internal Measure 22 V A8

Output

Internal Measure 220 V

A8 Output

Weight:

K11 K10 K9 K8 K7 K6 K5 K4 K3 K2 K1 d=0 d=0 d=1 d=1

4 2 1 8 4 2 1 8 4 2 1 hex hex hex hex

x x x x x x r x x x x 0000 0000

x x x x x x x x x r x 0000 0000

r s s s r s r s s r s 03ad

r s s s r s r s s r s 03ad

r s s s r s g r r d r 03a0 03b0 03a2 03a2

r s s s r s r s s r s 03ad

r s s s r r g r r d r 0380 0390 0382 0392

r s s r r r s s r s 038d

r s s s r s g r r d r 03a0 03b0 03a2 03b2

r s s s s s g s r d r 03e8 03f8 03ea 03fa

r s s r r s r s s r s 032d

r r s s r s r s s r s 01ad

r r s s r r r s s r s 018d

r r s s r s r s s r s 01ad

s r s s r s r s s r s 05ad

MBRLY g=0 g=1 g=0 g=1

ext Int ext int

int int rem rem

Key: x = don’t care, r = reset, s = set, d = reset (0) for internal sense or set (1) for remote sense, g = reset (0) for external

guard or set (1) for internal guard

Notes:

• An over-voltage detection or other serious problem should trip the instrument to the fault state.

• An over-compliance or over-current detection should trip the instrument to the appropriate overload fault.

• A hardware fault causes the instrument to enter the fault state.

2-8

Page 37

Theory of Operation

Table 2-4. Control Register States by Instrument State

Control Register MBSW

Signal: - - CKIT* CKHVCUR* - WARNING* OPERATE* STANDBY*

Instrument State \ Bit

Weight:

Dormant x x H H x H H L 36

Fault x x H H x L H L 32

Standby x x H H x H H L 36

Output Ohms, Current,

I, or V < 30 V

Output V > 30 V x x H H x L L H 31

Output V < 30 V,

Monitor HVCOM

current via SMUX

Output V > 30 V,

Monitor HVCOM

current via SMUX

Output Ohms, I, or V

>30 V, Monitor Internal

Temperature via SMUX

Output V > 30 V,

Monitor Internal

Temperature via SMUX

Key: x = don’t care, H = High (Off), L = Low (On)

8 4 2 1 8 4 2 1 hex

x x H H x H L H 35

x x H L x H L H 25

x x H L x L L H 21

x x L H x H L H 15

x x L H x L L H 11

A3 Motherboard PCA 2

2-9

Page 38

57LFC/AN

Service Manual

LED Control and Output Cables

STANDBY* Turns on the STANDBY LED when asserted Low (YELLOW)

OPERATE* Turns on the OPERATE LED when asserted Low (GREEN)

WARNING* Turns on the WARNING LED when asserted Low (RED)

CKHVCUR* Turns on an analog switch to place the rectified and filtered shunt voltage generated

CKIT* Turns on a switch to connect the output of the temperature to SMUX.

Sheet 5 of the schematic shows the LED control (panel LED's connector). The LEDs are

mounted on their own daughter card with control wires cabled from the A3 Motherboard

PCA. A description of each LED is provided in Table 2-5.

Table 2-5. Functional Description of LED Signals

Signal Functional Description

by the HVCOM current onto the SMUX line when asserted Low

Sheet 1 of the A3 Motherboard PCA schematic shows the connection and wiring for the

output cable from the A3 Motherboard PCA to the front panel binding posts. Note that

there are two guards - IGUARD and GUARD (voltage guard). These guards may be tied

together through K8 when voltage is selected. The other signal leads are OUT_HI,

SNS_HI, OUT_LO, and SNS_LO. The output high and low signals (OUT_HI and

OUT_LO) are used for the main output for volts, current, and ohms. The output sense

signals (SNS_HI and SNS_LO) are used to sense and internally adjust the output signals.

The sense terminals are not used for standard (uncompensated) two wire ohms or ac and

dc current.

Signal Buses

The system analog and digital buses are brought to the circuit cards through the A3

Motherboard PCA connectors J105-108 and J205-208. J105-J108 provides the in-guard

(IG) digital bus signal lines while J205-208 route the in-guard analog signal lines. Guard

is tied to chassis through a set of diodes and MOVs (CR57, CR58, and RV3 and CR69,

CR68, and RV1) and prevents the guard from floating more than 20 V from chassis. The

guard is tied to SCOM through CR55, CR56, RV2, and R86. Note that relay K5 on

Sheet 1 can connect the guard trace directly to SCOM.

Low Volt Buffer

The low voltage buffer circuit is shown on Sheet 4 of the A3 Motherboard PCA

schematic (along the bottom-middle of the Sheet). The V3_3 input signal to U2 comes

from the A6 Digital Synthesis PCA (A6). U2, combined with Q1,2,7 and 8, act to buffer

the V3_3 signal and isolate the output voltage from the A6 card. Q3 and Q4 limit the

output current that may be drawn.

In-guard Power Supplies

The power supplies for the analog circuits, also referred to as in-guard supplies, are

shown on Sheets 2, 3, and 4 of the A3 Motherboard PCA. On Sheet 2 of the A3

Motherboard PCA schematic, the raw transformer secondaries enter at P2. 5AC1, 5AC2,

15AC1 and 15AC2 go to Sheet 3 of the A3 Motherboard PCA schematic along with the

GUARD signal. RT7-10 protects the transformer from large current draws that might

occur if a diode bridge on Sheet 3 of the A3 Motherboard PCA schematic or other

components short.

2-10

Page 39

Theory of Operation

A3 Motherboard PCA 2

The 45 ac, 180 ac, and 360 ac provide the raw voltages that will be used by the A8 High

Voltage and A5 Ohms PCAs. If secondary voltages become too large, TRIAC Q19 will

turn on the limit voltage, open the mains fuse, and prevent damage. CR62 is the full wave

rectifier for the +/-45UNR supply. The +/-45UNR are regulated to become the +/-45V

supplies. MP7 and MP8 are assemblies that contain the heat sinks and the main pairs of

drive transistors for the 45 V regulated supplies. U18 controls the regulation. Q12 with

resistor R48 and R54 and Q13 with resistors R49 and R57 limit the output currents to

~120 mA. CR28 with VR10 and VR11 and CR 26 with VR12 and VR 13 protect against

high voltages damaging the regulation circuits. Note that the HVCOM line caries the

ground return currents for the high voltage supplies back to the center tap of the

transformer.

On Sheet 3 of the A3 Motherboard PCA schematic, CR67 and CR51 rectify the 15 V ac

and 5 V ac (left side of the Sheet), respectively. The resulting +15UNR goes through

U21, a dual regulator., and becomes the guarded +15 V supply. -15UNR goes into U22

and becomes the -15 V supply. VR14 and VR15 limit short term over-voltages to 22 V or

so. The 5 ac signals are regulated to be the power for the relays (+5RLH) and the logic

(+5 V). The +/-15 V supplies are referenced to SCOM, while the +/-5 V supplies are

referenced to DCOM. Note that SCOM and DCOM grounds are kept close to each other

electrically due to the Schottky diodes, CR18 and CR19. CR29 and CR31 limit the

amount that the +/-15 V and +/-5 V power supplies can float from each other. Each

regulator in the design is protected against short-term over voltages occurring at the

regulator output with diodes CR41, CR48, CR35, CR36, and CR34. The 6 turn beads

reduce conducted noise.

Outguard Power Supplies

The connector P1 and the out-guard secondaries labeled 12GAC and 5GAC are shown on

Sheet 2 of the A3 Motherboard PCA schematic. These unregulated supplies including

+5VG_UNR, become the regulated supplies for the outguard controller card (A9) and

include +5VG and +/-12VG. These supply power the A9 Out-Guard CPU PCA through

the connector J1 (found on Sheet five). RT1, and RT3-RT5 protect the transformer from

large current draws that might occur if there is a short down stream. Each regulator in the

design (U20, U25, and U19) is protected against short-term over voltages occurring at the

regulator output with diodes CR42, CR43, and CR59. The 6 turn beads reduce conducted

noise. The regulated +/-12 V supplies also provide power to the 24 V fan located at the

front of the instrument. A second fan connector was added for a future version of the

instrument. GCOM is the reference and is tied through resistors to earth, and tied to

DCOM (the in-guard digital ground) through a 24 V bi-directional Zener, VR17.

Miscellaneous Circuits

On Sheet five of the A3 Motherboard PCA schematic, J1 connects the digital signals

from the A9 Controller card to the A3 Motherboard PCA. The serial data signals form the

communication path to the A6 Digital Synthesis PCA (which also controls the in-guard

digital bus). J6 is used for trouble shooting the circuitry in manufacturing and service

testing. Also on that Sheet is an area marked NOT INSTALLED. These circuits may be

used in a future version of the product.

Sheet 3 of the A3 Motherboard PCA schematic shows U27, a switch used to connect

signals to the SMUX bus line for monitoring the A6 Digital Synthesis PCA.

CKHVCUR* is driven by U7 pin 12 on Sheet 5 of the A3 Motherboard PCA schematic

for connecting the output of the circuit checking the HVCOM current to SMUX. CKIT*

can turn on a switch in U27 to connect the output of the temperature sensor h30 to

SMUX.

2-11

Page 40

57LFC/AN

Service Manual

Troubleshooting Test Points

When a problem occurs with the instrument operation, one likely place to look is the

A3 Motherboard PCA and its power supplies. There are a number of convenient test

points to monitor the supply voltages. The test points are listed in Table 2-6.

The test points can be divided into several groups: general, function unique, out-guard,

and fault. General test points include V3BUF, +/-5UNR, +/-5V, +/-15UNR, and