ft2925

CAVDD

1uF

EN

+

CPVOUT

220uF

VDD

CPVOUT

22uF

Cin

0.22uF

INNR

CVBAT

1uF

INPR

INNL

CPVOUT

0.1uF

CBVDD

0.1uF

CS

22uF

ft2925

2

3

4

5

6

7

8

10

12

13

14 15

16

17

18

9

1

19

20

11

21

22

23

24

25

26

27

28

INNL

INPL

PGND

VOPL

VONL

PVDDL

AVDD

NC

ALC

SDRIVE

EN LX

LX

PGNDB

PGNDB

BVDD

VBAT

PVOUT

PVOUT

VKNEE

PVSNS

PVDDR

VONR

VOPR

PGND

INPR

INNR

AGND

LSL

SPEAKER

INPL

Rin 15K

Cin 0.22uFCin 0.22uF

Rin

15K

Cin

0.22uF

RS2 10Ω

LSR

SPEAKER

CS

0.1uF

D1 SS34

CPVDDR

1uF PVDD

RS1 10Ω

L 3.3uH

VDD

Rin 15K

Rin

15K

PVDD

CPVDDL

1uF

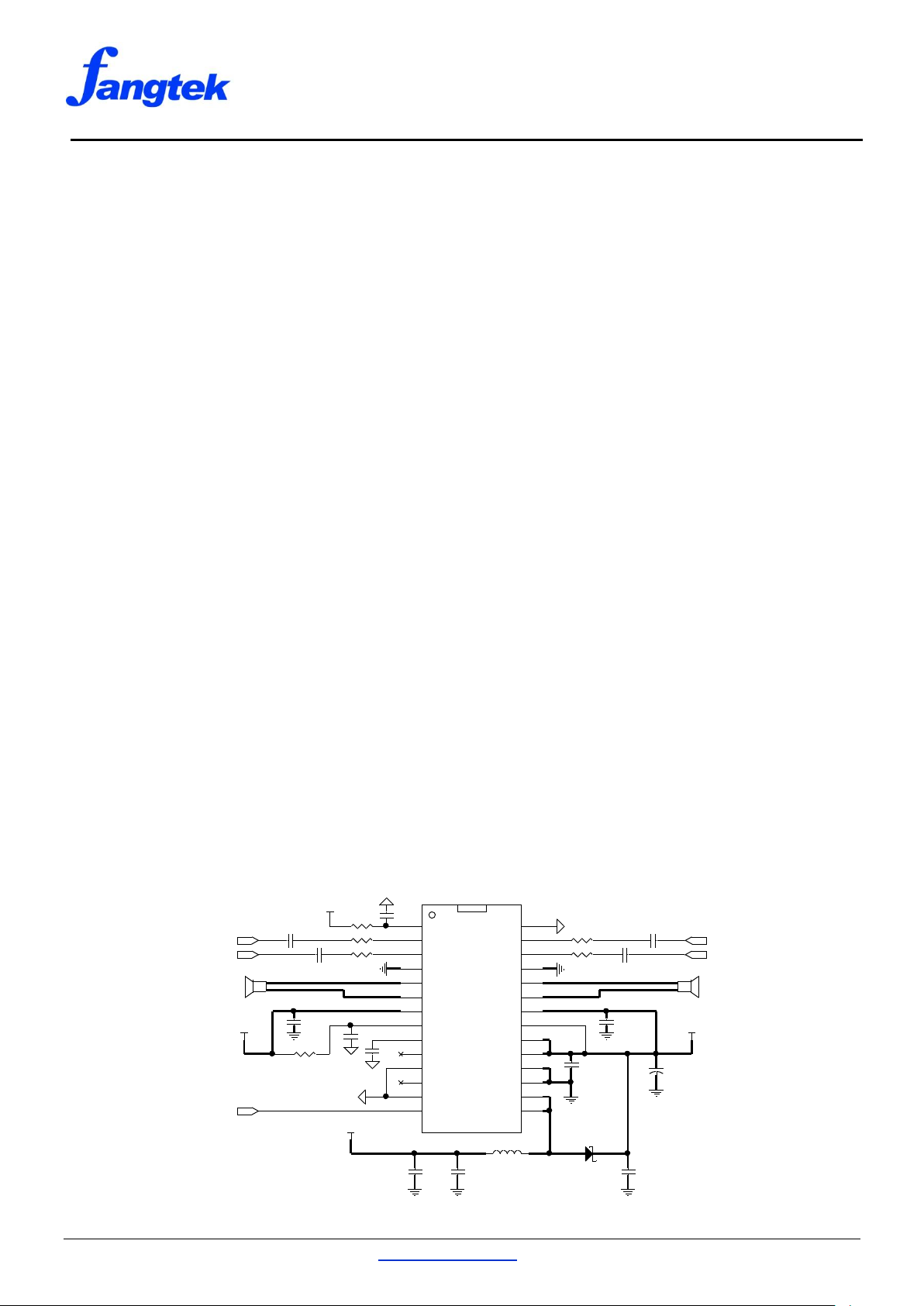

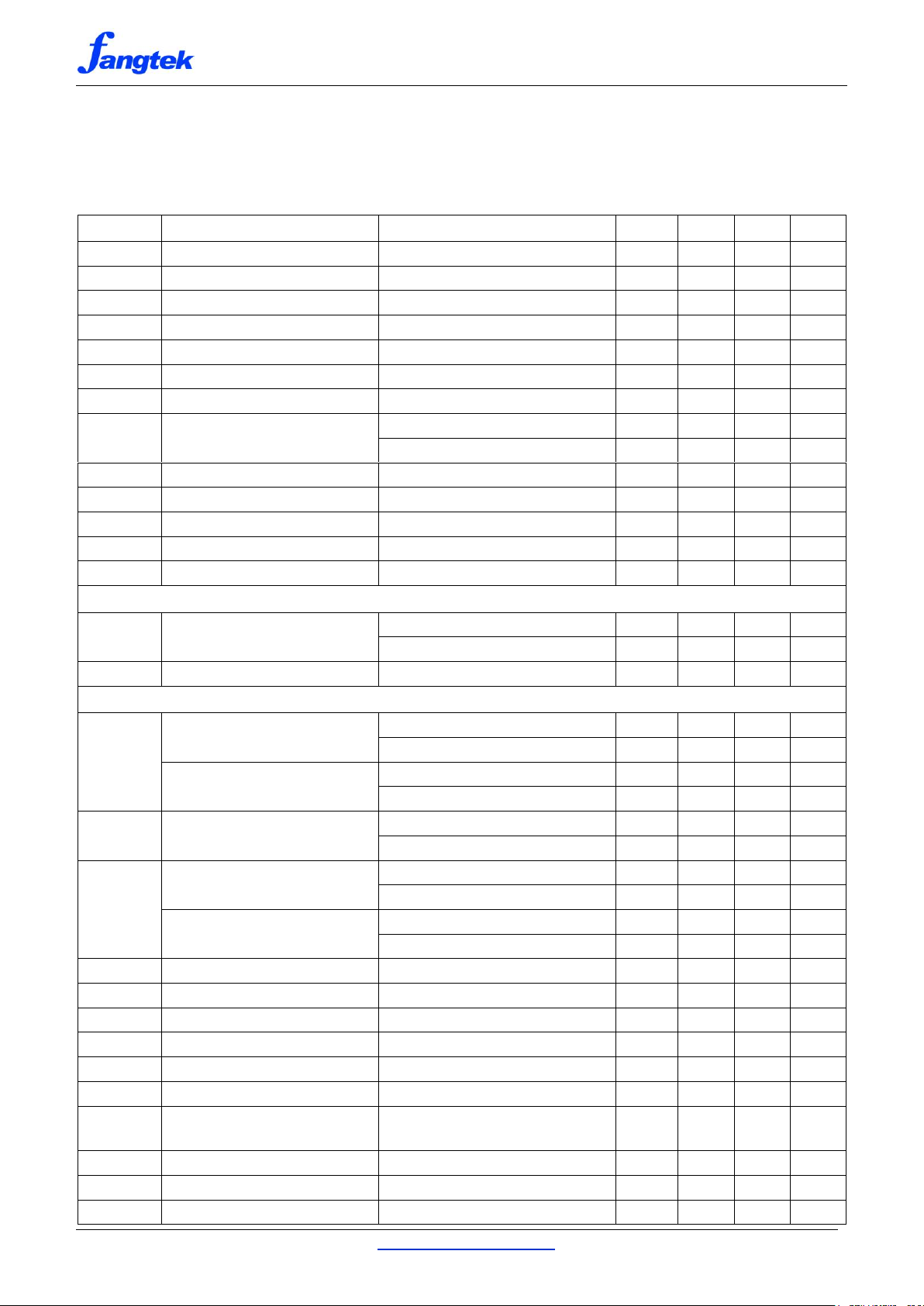

2x6W Class-G Stereo Audio Power Amplifier

with Automatic Level Control & Battery Tracking AGC

GENERAL DESCRIPTION

The ft2925 is a highly efficient 2x6W Class-G stereo

audio power amplifier with automatic level control (ALC)

and battery tracking AGC. It integrates dual filterless

Class-D audio amplifiers with a multi-level Class-G

synchronous boost regulator and operates with a range

of supply voltages from 3V to 5.5V. When operating

with a 3.6V supply voltage, the ft2925 can deliver an

output power of 6W per channel with 10% THD+N, or

an ALC output power of 4.5W per channel with 0.3%

THD+N, into a pair of 4Ω speakers.

In ft2925, the power supply rails of the audio amplifiers’

output stages are internally boosted and regulated by a

synchronous PWM switching regulator with two

integrated power switches. The boost regulator

employs current-mode PWM control with proprietary

multi-level Class-G operation to regulate the boosted

output voltage dynamically in response to the voltage

level of the audio outputs.

The ft2925 features ALC function to constantly monitor

and safeguard the audio outputs against the boosted

supply voltages, preventing output clipping distortion,

excessive power dissipation, and speaker over-load.

Once an over-level condition is detected in either

channel, the ALC lowers the voltage gain of both audio

amplifiers together to limit the peak audio outputs.

In conjunction with ALC, as the battery supply voltage

drops below a prescribed value, the battery tracking

AGC lowers the voltage gain of both audio amplifiers to

limit the peak audio outputs, preventing the collapse of

battery voltage.

FEATURES

Wide range of supply voltages from 3V to 5.5V

Dual filterless Class-D audio amplifiers integrated

with a multi-level Class-G boost regulator

Automatic level control to eliminate output clipping

Battery tracking AGC to prevent battery collapse

Soft drive mode for EMI reduction

Maximum output power (Non-ALC Mode)

(VBAT=3.6V, ALC=High, THD+N=10%)

6.0W/Ch (4Ω Load)

3.5W/Ch (8Ω Load)

ALC output power (ALC Mode)

(VBAT=3.6V, ALC=Low, THD+N=0.3%)

4.5W/Ch (4Ω Load)

2.6W/Ch (8Ω Load)

Wide ALC dynamic range: 12dB

Maximum voltage gain: 30dB

High efficiency: 78%

(VBAT=3.6V, 4Ω Load, Po=2W/Ch, both channels driven)

Volume fade-in and fade-out

Under-voltage lockout protection

Auto-recovering over-current & short-circuit

protection

Thermal over-load protection

Available in TSSOP-28L package

APPLICATIONS

Blue Tooth Speakers

Portable Audio Decks

Consumer Audio Electronics

APPLICATION CIRCUIT

DEC, 2017 www.fangtek.com.cn 1

Figure 1: Typical Application Circuit Diagram of ft2925

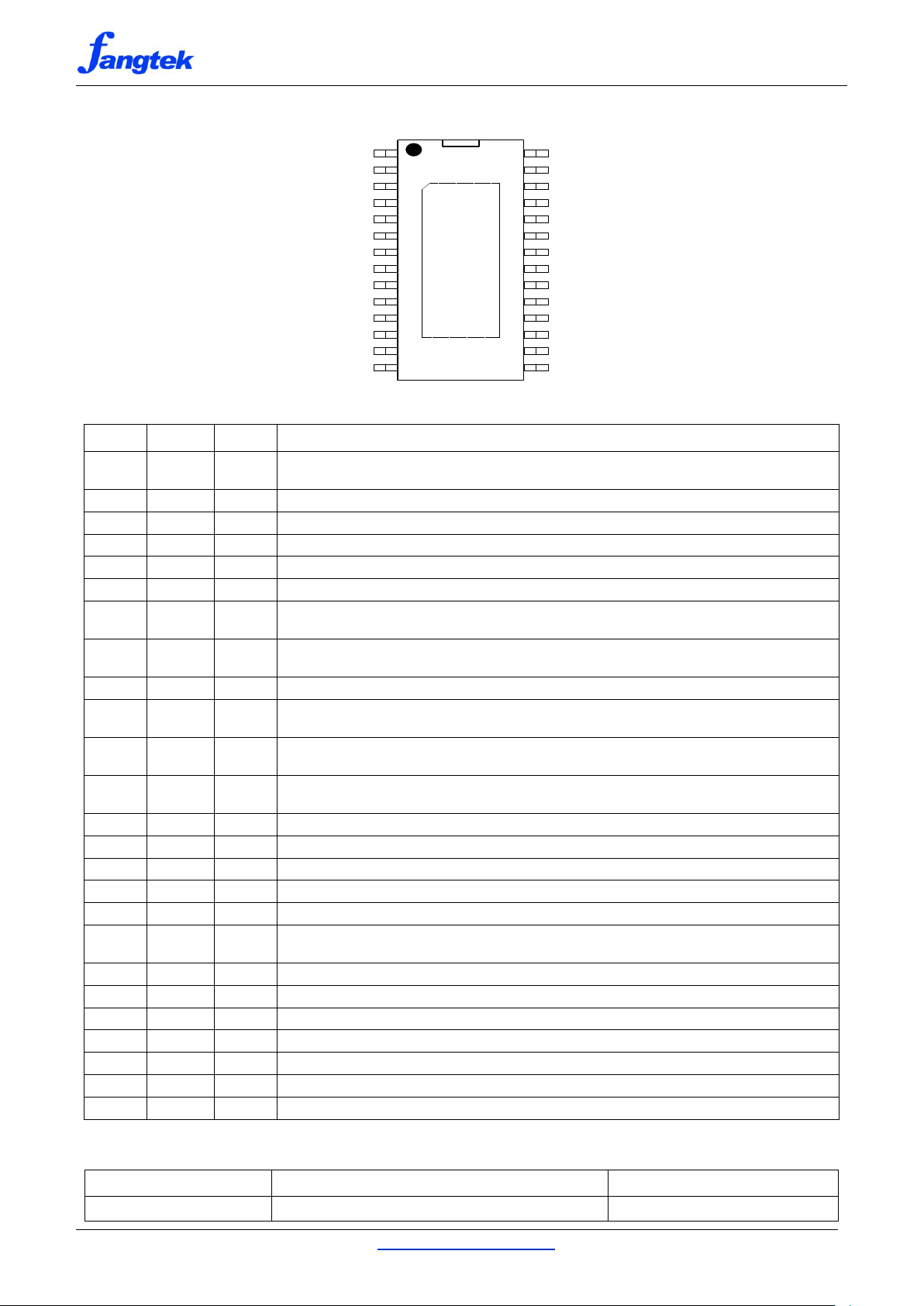

ft2925

NAME

PIN #

TYPE

DESCRIPTION

VBAT 1 P

Supply input voltage. Connect to a 1µF capacitor for decoupling. It is externally connected to

the system supply through a small decoupling resistor of 10Ω.

INNL 2 AI

Left-channel inverting audio input terminal.

INPL 3 AI

Left-channel non-inverting audio input terminal.

PGND 4 G

Power ground for the left-channel audio amplifier’s output stage.

VOPL 5 AO

Left-channel non-inverting audio output terminal.

VONL 6 AO

Left-channel inverting audio output terminal.

PVDDL 7 P

Power supply input for the left-channel audio amplifier’s output stage. Connect directly to the

output capacitor of PVOUT. Also, connect to a 1µF capacitor for decoupling.

AVDD 8 P

Boosted supply input voltage for internal circuitry. Connect it to a 1µF capacitor for decoupling.

Also, place a small decoupling resistor of 10Ω between this pin and PVOUT.

BVDD 9 AO

Internally generated voltage reference. Connect to a 0.1µF capacitor for decoupling.

VKNEE

11

DI

Battery Tracking AGC Control with an internal 300kΩ pullup resistor to VBAT and an internal

300kΩ pulldown resistor to ground.

ALC

12

DI

ALC Mode Control with an internal 300kΩ pullup resistor to VBAT and an internal 300kΩ

pulldown resistor to ground.

SDRIVE

13

DI

Soft Drive Control with an internal 300kΩ pullup resistor to VBAT and an internal 300kΩ

pulldown resistor to ground. When unconnected, the boost regulator is disabled.

EN

14

DI

Chip Enable (Active High) with an internal 300kΩ pulldown resistor to ground.

LX

15, 16

AO

Switch node of the boost regulator.

PGNDB

17, 18

G

Power ground for the boost regulator’s output stage.

PVOUT

19, 20

P

Boosted voltage output.

PVSNS

21

AI

Boosted voltage sense. Connect directly to the output capacitor of PVOUT.

PVDDR

22

P

Power supply input for the right-channel audio amplifier’s output stage. Connect directly to the

output capacitor of PVOUT. Also, connect to a 1µF capacitor for decoupling.

VONR

23

AO

Right-channel inverting audio output terminal.

VOPR

24

AO

Right-channel non-inverting audio output terminal.

PGND

25

G

Power ground for the right-channel audio amplifier’s output stage.

INPR

26

AI

Right-channel non-inverting audio input terminal.

INNR

27

AI

Right-channel inverting audio input terminal.

AGND

28

G

Analog ground.

NC

10

No internal connection.

PART NUMBER

TEMPERATURE RANGE

PACKAGE

ft2925P

-40°C to +85°C

TSSOP-28L

EN

19

18

INPR

22

9

VOPL

26

13

28

5

VBAT

PGNDB

21

LX

AGND

15

LX

7

INNL

4

6

PVSNS

PVDDL

20

INPL

8

3

23

16

PVOUT

1

27

PGNDB

PVDDR

ALC

VONR

12

AVDD

PGND

24 VOPR

10

PVOUT

NC

25

14

INNR

17

VONL

BVDD

VKNEE

SDRIVE

11

2

PGND

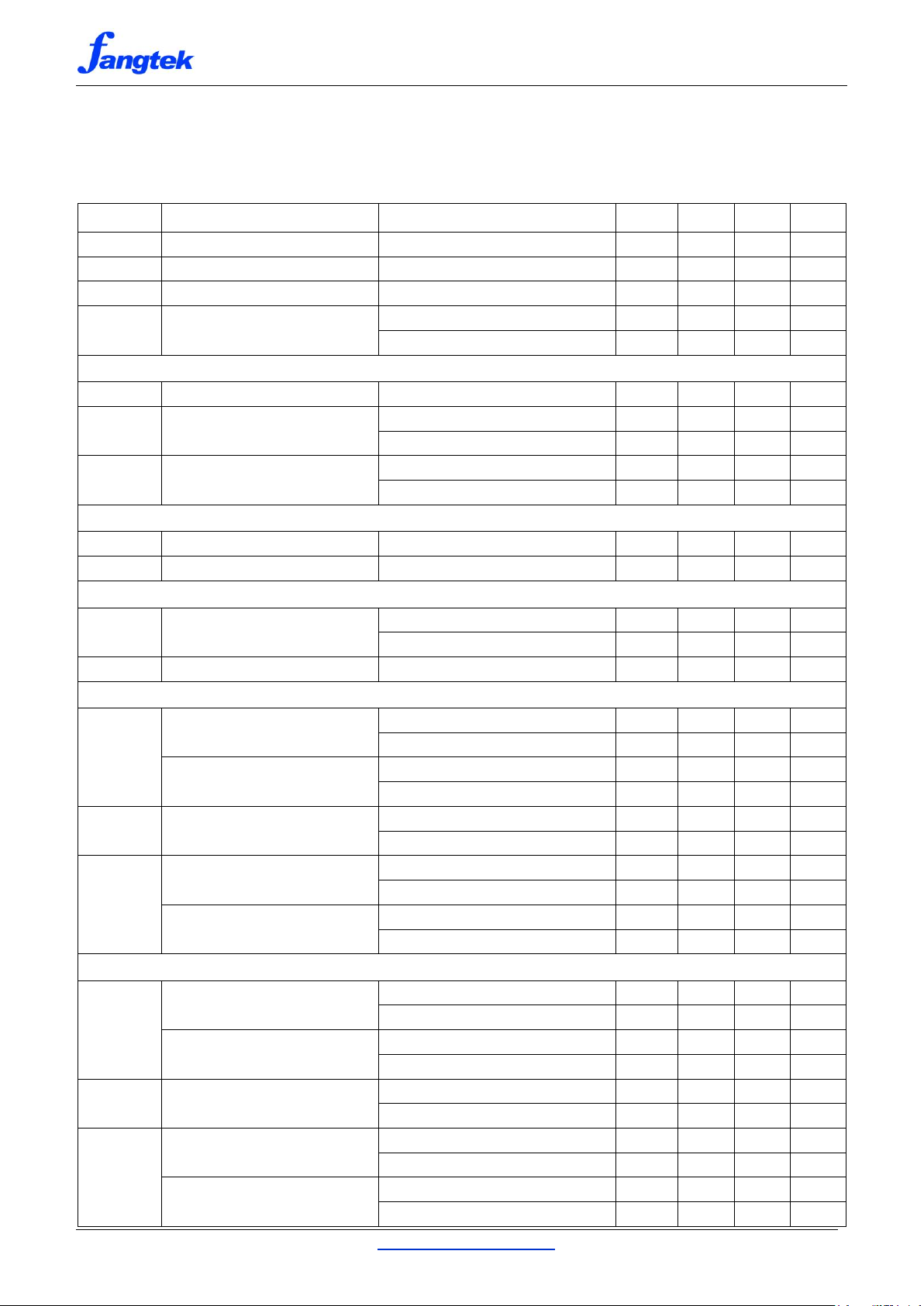

PIN CONFIGURATION AND DESCRIPTION

ft2925P (TOP VIEW)

ORDERING INFORMATION

DEC, 2017 http://www.fangtek.com.cn 2

ft2925

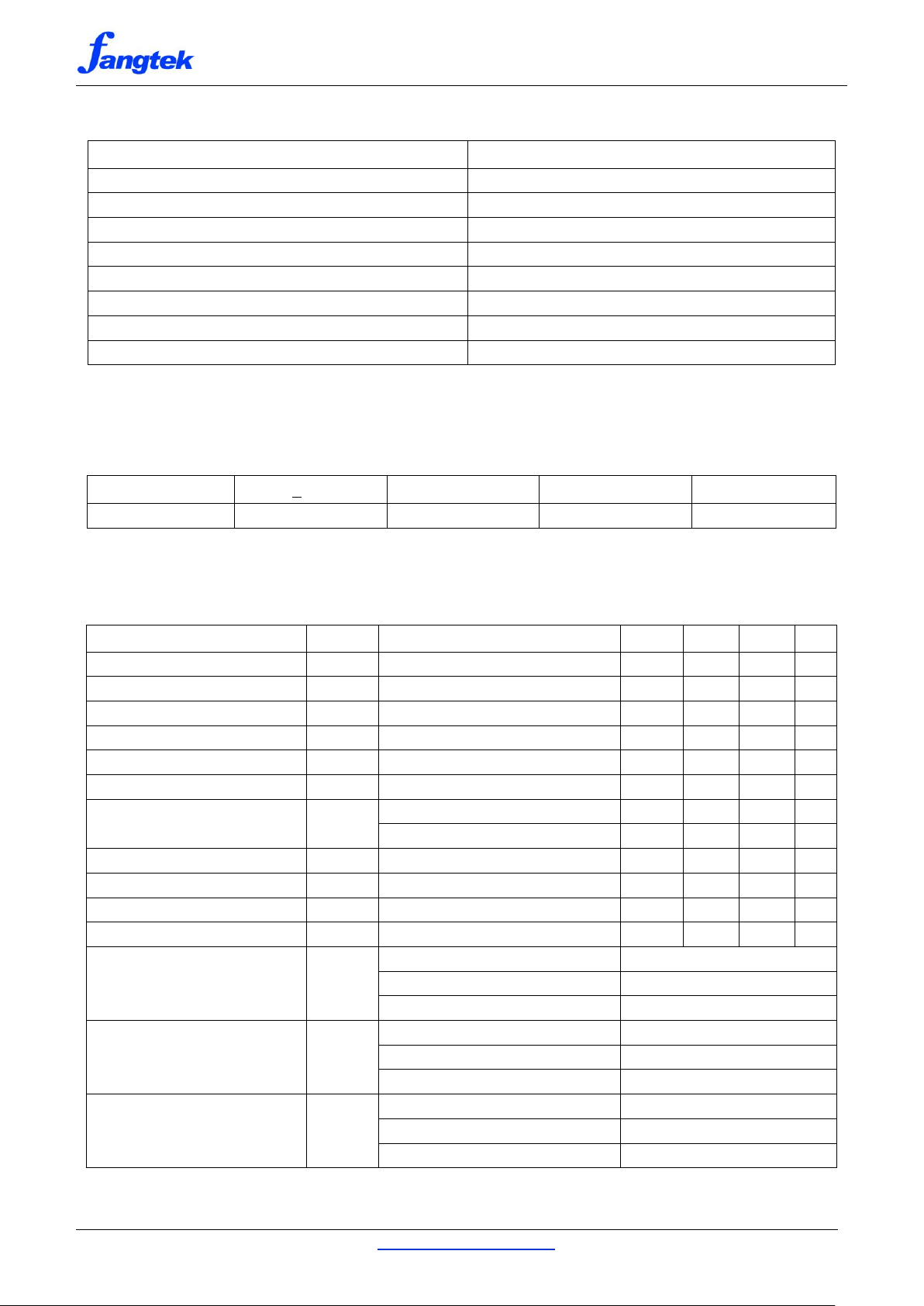

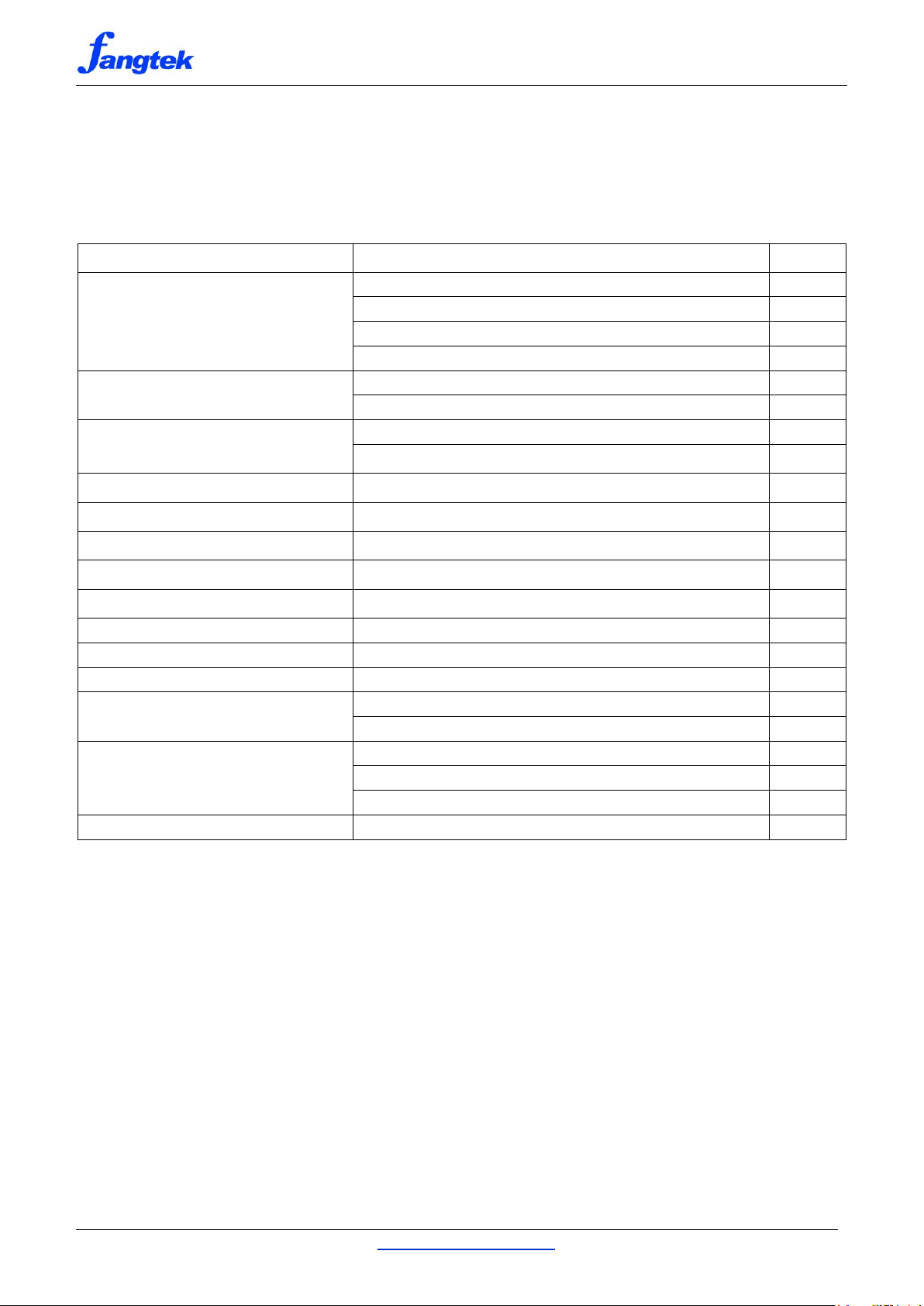

PARAMETER

VALUE

Supply voltage, VBAT

-0.3V to 6V

LX, PVOUT, PVDDL/R, PVSNS, AVDD, VOPL/R, VONL/R

-0.3V to 8V

PGND, PGNDB

-0.3V to 0.3V

All other Pins

-0.3V to VBAT+0.3V

Storage Temperature

-65°C to +150°C

ESD Ratings-Human Body Model (HBM)

4000V

Junction Temperature

150°C

Maximum Soldering Temperature (@10 second duration)

260°C

PACKAGE

TA < +25°C

TA = +70°C

TA = +85°C

ΘJA

TSSOP-28L

4.5W

2.8W

2.3W

28°C/W

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNIT

Supply Voltage

VDD 3.0 5.5

V

Minimum Load Impedance

RL

Across VOPL/R & VONL/R

3.4 4

Ω

Audio Input Resistor

RIN

@ INPL/R, INNL/R

0 56

k

Ω

Audio Input Capacitor

CIN

@ INPL/R, INNL/R

0.1

0.22

1.0

µF

Boost Regulator Inductor

L 2.2

3.3

4.7

µH Boost Regulator Input Capacitor

CS

Ceramic

10

22 µ

F

Boost Regulator Output Capacitor

C

PVOUT

Ceramic

22

44 µF Electrolytic or Tantalum

(Note 4)

100

220 µF

BVDD Output Capacitor

CBVDD

0.1 µF

PVDD Decoupling Capacitors

CPVDDL/R

1 µF

Operating Junction Temperature

TJ -40 125

C

Ambient Temperature

TA -40 85

C

Operating Mode Control

SDRIVE

High η Drive, Boost regulator Enabled

Short to GND

Soft Drive, Boost regulator Disabled

Unconnected

Soft Drive, Boost regulator Enabled

Short to VBAT

ALC Mode Control

ALC

ALC-1

Short to GND

ALC-2

Unconnected

Non-ALC

Short to VBAT

Battery Tracking AGC Control

VKNEE

Battery Tracking AGC Disabled

Short to GND

VKNEE=3.15V

Unconnected

VKNEE=3.40V

Short to VBAT

ABSOLUTE MAXIMUM RATINGS

Note 1: Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at any conditions beyond those indicated under recommended operating conditions is

not implied. Exposure to absolute-maximum-rated conditions for extended periods may also affect device reliability.

(Note1)

POWER DISSIPATION RATINGS

Note 2: The thermal pad of the package must be directly soldered onto a grounded metal island as a thermal sink on the system board.

Note 3: The power dissipation ratings are for a two-side, two-plane printed circuit board (PCB).

(Note 2, 3)

RECOMMENDED OPERATING CONDITIONS

Note 4: A bulk output capacitor (either electrolytic or tantalum) is typically added to facilitate higher voltage margin for higher audio power

at low frequencies. However, be cautious using any bulk output capacitance higher than 220µF as it might adversely slow the boost

regulator’s response to load transients to some extent affecting audio dynamics when playing music.

DEC, 2017 http://www.fangtek.com.cn 3

ft2925

IMPORTANT APPLICATION NOTES

1. It is crucial to place the ft2925 in close proximity to the inductor, Schottky diode, and input/output capacitors

of the boost regulator on the system board, minimizing parasitic resistances and inductances of high-current

traces. Also, these passive components must be placed on the same layer with ft2925 and connected with

wide and short metal lines without vias. Failure to do a proper layout on the system board can result in

significant degradation of maximum output power, efficiency, THD, and EMI performance. It might even

induce excessive ringing at the switch node LX and damage the device permanently.

2. Use wide open areas on the top and bottom layers of the system board as the ground plane (GND) for ft2925.

Place lots of solid vias connecting the top and bottom layers of GND. Furthermore, for proper thermal

dissipation, reserve wide and uninterrupted GND areas along the thermal flow on the top layer, i.e., no wires

cutting through the GND layer and obstructing the thermal flow.

3. The ft2925 is packaged with an exposed thermal pad on the underside of the device. Solder the thermal pad

directly onto a large grounded metal island, as a thermal sink, underneath the package for proper thermal

dissipation. On the grounded metal island, place several rows of solid, equally-spaced vias connecting to the

bottom layer of GND. Failure to do so can severely limit its thermal dissipation capability. It might even cause

the device going into over-temperature shutdown occasionally.

4. All the ground pins (AGND, PGND and PGNDB) are directly connected to the ground plane (GND). The

power supply inputs (PVDDL/R) for the audio amplifiers’ output stages are directly connected to the output

capacitors of the boost regulator with wide and short metal traces.

5. As a high-performance Class-G stereo audio amplifier, the ft2925 requires adequate power supply

decoupling to ensure its high-efficiency, low distortion, and low EMI. Place each decoupling capacitor as

individually close to VBAT, AVDD, BVDD, and PVDDL/R pins as possible.

6. For best noise performance, use differential inputs from the audio sources for ft2925. In single-ended input

applications, the unused inputs of ft2925 should be AC-grounded at the audio source.

7. With an on-chip rectification power switch, the ft2925 requires no external Schottky diode for applications

where speaker load resistances are 8Ω. However, for applications where speaker load resistances are 4Ω or

less, it is required to add an auxiliary Schottky diode across LX and PVOUT pins to improve maximum output

power and overall power efficiency. The added Schottky diode must be rated for a current no less than 3A

and a reverse breakdown voltage no less than 15V.

8. Additional EMI suppression can be achieved using a ferrite bead filter constructed from a ferrite bead and a

capacitor, as shown in Figure 31. Choose a ferrite bead with a rated current no less than 1A for an 8Ω load

and 2A for a 4Ω load. Also, place the ferrite beard filter tightly together and individually close to VOPL/R and

VONL/R pins respectively.

9. Add a simple RC snubber circuit across two audio outputs (VOPL/R and VONL/R) for each channel, as

shown in Figure 32, to prevent the device from accelerated deterioration or abrupt destruction due to

excessive inductive flybacks that are induced on fast output switching or by an over-current condition.

10. The operation of the battery tracking AGC can be highly influenced by the electrical characteristics of the

battery. Place a small decoupling resistor of 10Ω between the battery supply voltage and the VBAT pin,

coupled with a decoupling capacitor of 1µF, mitigating the detrimental effect of high battery current ripples on

the detection of battery voltage.

11. Place a small decoupling resistor of 10Ω between AVDD and PVOUT pins, coupled with a decoupling

capacitor of 1µF, preventing high frequency transients from interfering with the on-chip linear amplifiers.

12. Use direct low-impedance traces for the audio outputs (VOPL/R and VONL/R) to the output filters and to the

speakers.

13. Do not connect any audio outputs (VOPL/R or VONL/R) directly to GND, PVOUT, or PVDDL/R as this might

damage the device permanently.

14. Do not alter the logic state of the SDRIVE pin while the device is in operation. To change the operating mode,

the device must be first placed in shutdown mode for a minimum of 100 milliseconds.

DEC, 2017 http://www.fangtek.com.cn 4

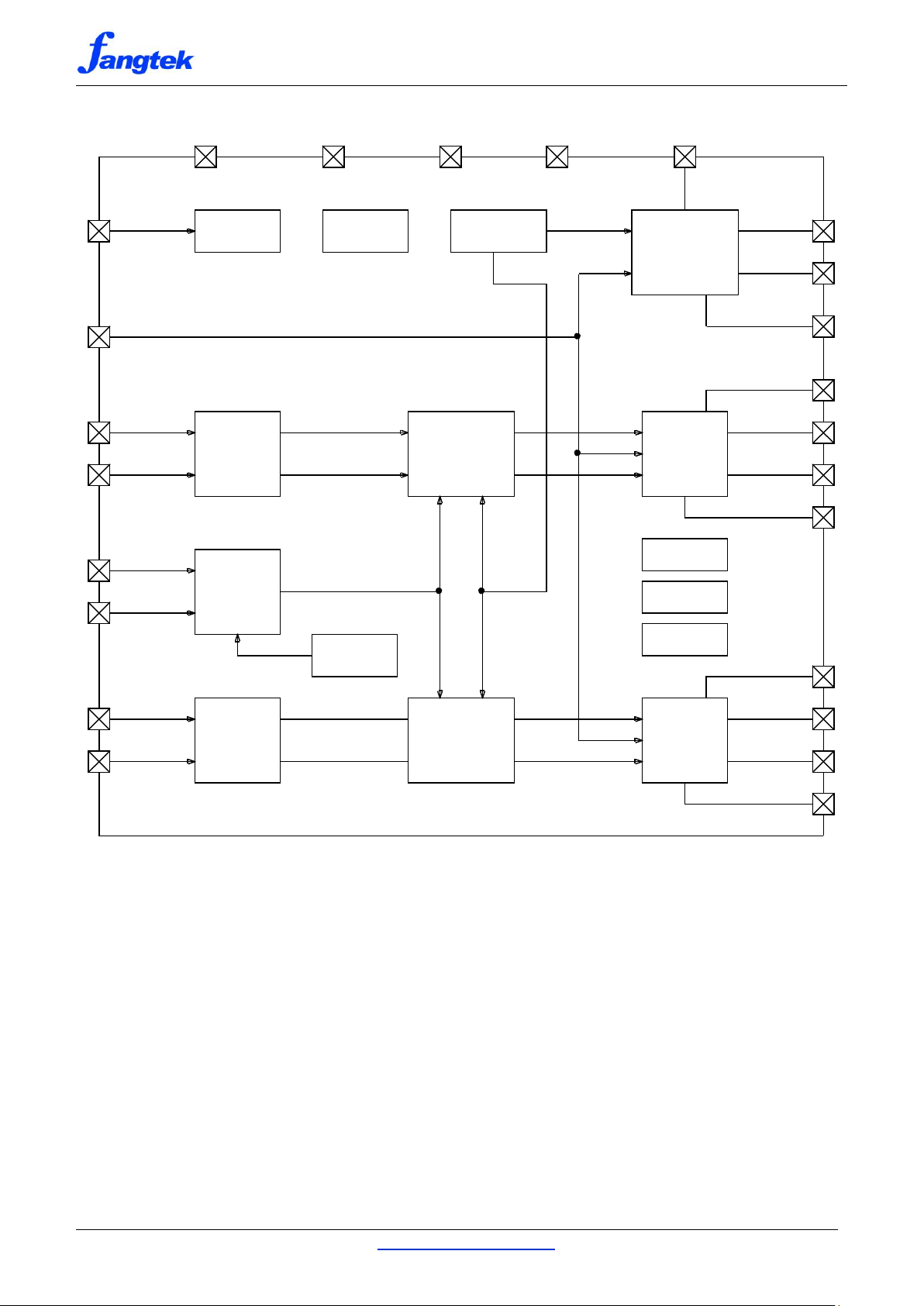

ft2925

INNR

LX

ALC Control

BIAS

VONL

PVDDR

Class-D

Modulator

SDRIVE

Battery

Ttracking

AGND

VOPR

EN

VKNEE

AVDD

PVDDL

OTP

Output

Stage

VBAT

Class-D

Modulator

VONR

INPL

Input

Buffer

ALC

PVSNS

PVOUT

Boost

Battery

Monitor

PGND

PGND

BVDD

Output

Stage

INNL

Oscillator

INPR

PGNDB

OCP

Shutdown

Control

UVLO

VOPL

Input

Buffer

FUNCTIONAL BLOCK DIAGRAM

Figure 2: Simplified Functional Block Diagram of ft2925

DEC, 2017 http://www.fangtek.com.cn 5

ft2925

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNIT

VBAT

Supply Input Voltage

3.0 5.5

V

VUVLOUP

Power-on Threshold Voltage

VBAT from Low to High

2.2 V

VUVLODN

Power-off Threshold Voltage

VBAT from High to Low

2.0 V

IVBAT

Supply Quiescent Current

Inputs AC-Grounded, No Load

7

10

14

mA

IAVDD

Quiescent Current

VIN=0.25VRMS, No Load

6

mA

ISD

Shutdown Current

EN Low 1 µA

BVDD

Voltage Reference

Inputs AC-Grounded, No Load

3.0

3.2

3.4

V

VIH

Digital High Level Input Voltage

EN

1.2 V ALC, SDRIVE, VKNEE

VBAT-0.5

VBAT

V

VIL

Digital Low Level Input Voltage

EN, ALC, SDRIVE, VKNEE

0.4

V

RDOWN

Pulldown Resistor to Ground

EN, ALC, SDRIVE, VKNEE

300 kΩ

RUP

Pullup Resistor to VBAT

ALC, SDRIVE, VKNEE

300 kΩ

TOTSD

Over-Temperature Threshold

160

°C

THYS

Over-Temperature Hysteresis

20

°C

Class-G Boost Regulator

PVOUT

Boosted Voltage

No Load

7.0

7.2

7.4

V

ILOAD=1A

7.0 V

fBOOST

PWM Switching Frequency

800 kHz

Class-D Audio Amplifier with Class-G Boost Regulator (SDRIVE=Low, High Efficiency Drive)

PO, MAX

Maximum Output Power

THD+N=10%

RL=4Ω 6.0

W/Ch

RL=8Ω 3.5

W/Ch

Maximum Output Power

THD+N=1%

RL=4Ω 4.8

W/Ch

RL=8Ω 2.8

W/Ch

PO, ALC

ALC Output Power

RL=4Ω, VIN=0.40VRMS

4.5

W/Ch

RL=8Ω, VIN=0.40VRMS

2.6

W/Ch

THD+N

Total Harmonic Distortion+Noise

(Non-ALC Mode)

RL=4Ω, Po=2W

0.08 %

RL=8Ω, Po=1W

0.08 %

Total Harmonic Distortion+Noise

(ALC Mode)

RL=4Ω, VIN=0.40VRMS

0.3 %

RL=8Ω, VIN=0.40VRMS

0.3 %

AV

Overall Voltage Gain

RIN=15kΩ

25 dB

RIN

Input Resistance

@ INPL/R, INNL/R

20 kΩ

VCOMM

Input Common-Mode Bias

@ INPL/R, INNL/R

1.6 V

ROUT-SD

Output Resistance in Shutdown

@ VOPL/R, VONL/R

3

kΩ

VOS

Output Offset Voltage

Inputs AC-Grounded

±10 mV

VN

Idle-Channel Noise

Inputs AC-Grounded, A-weighted

170

µVRMS

SNR

Signal-to-Noise Ratio

(Non-ALC Mode)

Maximum Output (Vo=4.4VRMS)

RL=4Ω, A-weighted

88 dB

PSRR

Power Supply Rejection Ratio

f=1kHz, Inputs AC-Grounded

70 dB

CMRR

Common Mode Rejection Ratio

f=1kHz, VIN=0.2VRMS

65 dB

XTALK

Crosstalk

RL=4Ω+33µH, Po=2W

80 dB

ELECTRICAL CHARACTERISTICS

(Note 5)

VBAT=3.6V, f=1kHz, Load=4Ω+33µH, L=3.3µH, CIN=0.22µF, RIN=15kΩ (Av=25dB), ALC=NC, VKNEE=Low,

SDRIVE=Low, CS=22µF, CPVOUT=22µF//220µF, CPVDDL/R=1µF, RVBAT=10Ω, CVBAT=1µF, RAVDD=10Ω,

CAVDD=1µF, CBVDD=0.1µF, both channels driven, TA=25°C, unless otherwise specified.

DEC, 2017 http://www.fangtek.com.cn 6

ft2925

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNIT

TSTUP

Startup Time

80 ms

TSD

Shutdown Mode Settling Time

40 ms

fSW

PWM Output Carrier Frequency

400 kHz

ILIMIT

Over-Current Limit

SDRIVE=Low or High

2.6 A/Ch

SDRIVE=Unconnected

1.6 A/Ch

Automatic Level Control (ALC)

AMAX

Maximum ALC Attenuation

12 dB

TATTACK

ALC Attack Time

(VIN=0.24VRMS → 0.75VRMS)

ALC-1 Mode (ALC=Low)

6

ms

ALC-2 Mode (ALC=Unconnected)

48 ms

TRELEASE

ALC Release Time

(VIN=0.75VRMS → 0.24VRMS)

ALC-1 Mode (ALC=Low)

2.0 s

ALC-2 Mode (ALC=Unconnected)

1.0 s

Volume Fade-In & Fade-Out

TFADEIN

Fade-In Time

20 ms

TFADEOUT

Fade-Out Time

20 ms

Battery Tracking AGC

VKNEE

Knee Voltage

VKNEE=High

3.40 V

VKNEE=Unconnected

3.15 V

SATT

Output Attenuation Slope

@ VOPL/R, VONL/R

4

V/V

Class-D Audio Amplifier with Class-G Boost Regulator (SDRIVE=High, Soft Drive)

PO, MAX

Maximum Output Power

THD+N=10%

RL=4Ω 6.0

W/Ch

RL=8Ω 3.5

W/Ch

Maximum Output Power

THD+N=1%

RL=4Ω 4.8

W/Ch

RL=8Ω 2.8

W/Ch

PO, ALC

ALC Output Power

RL=4Ω, VIN=0.40VRMS

4.5

W/Ch

RL=8Ω, VIN=0.40VRMS

2.6

W/Ch

THD+N

Total Harmonic Distortion+Noise

(Non-ALC Mode)

RL=4Ω, Po=2W

0.08 %

RL=8Ω, Po=1W

0.08 %

Total Harmonic Distortion+Noise

(ALC Mode)

RL=4Ω, VIN=0.40VRMS

0.3 %

RL=8Ω, VIN=0.40VRMS

0.3 %

Class-D Audio Amplifier w/o Class-G Boost Regulator (SDRIVE=Unconnected, Soft Drive)

PO, MAX

Maximum Output Power

THD+N=10%

RL=4Ω 1.5

W/Ch

RL=8Ω

0.90

W/Ch

Maximum Output Power

THD+N=1%

RL=4Ω 1.2

W/Ch

RL=8Ω

0.70

W/Ch

PO, ALC

ALC Output Power

RL=4Ω, VIN=0.20VRMS

1.1

W/Ch

RL=8Ω, VIN=0.20VRMS

0.65

W/Ch

THD+N

Total Harmonic Distortion+Noise

(Non-ALC Mode)

RL=4Ω, Po=1W

0.08 %

RL=8Ω, Po=0.5W

0.08 %

Total Harmonic Distortion+Noise

(ALC Mode)

RL=4Ω, VIN=0.20VRMS

0.8 %

RL=8Ω, VIN=0.20VRMS

0.8 %

ELECTRICAL CHARACTERISTICS

(Note 5)

(Cont’d)

VBAT=3.6V, f=1kHz, Load=4Ω+33µH, L=3.3µH, CIN=0.22µF, RIN=15kΩ (Av=25dB), ALC=NC, VKNEE=Low,

SDRIVE=Low, CS=22µF, CPVOUT=22µF//220µF, CPVDDL/R=1µF, RVBAT=10Ω, CVBAT=1µF, RAVDD=10Ω,

CAVDD=1µF, CBVDD=0.1µF, both channels driven, TA=25°C, unless otherwise specified.

DEC, 2017 http://www.fangtek.com.cn 7

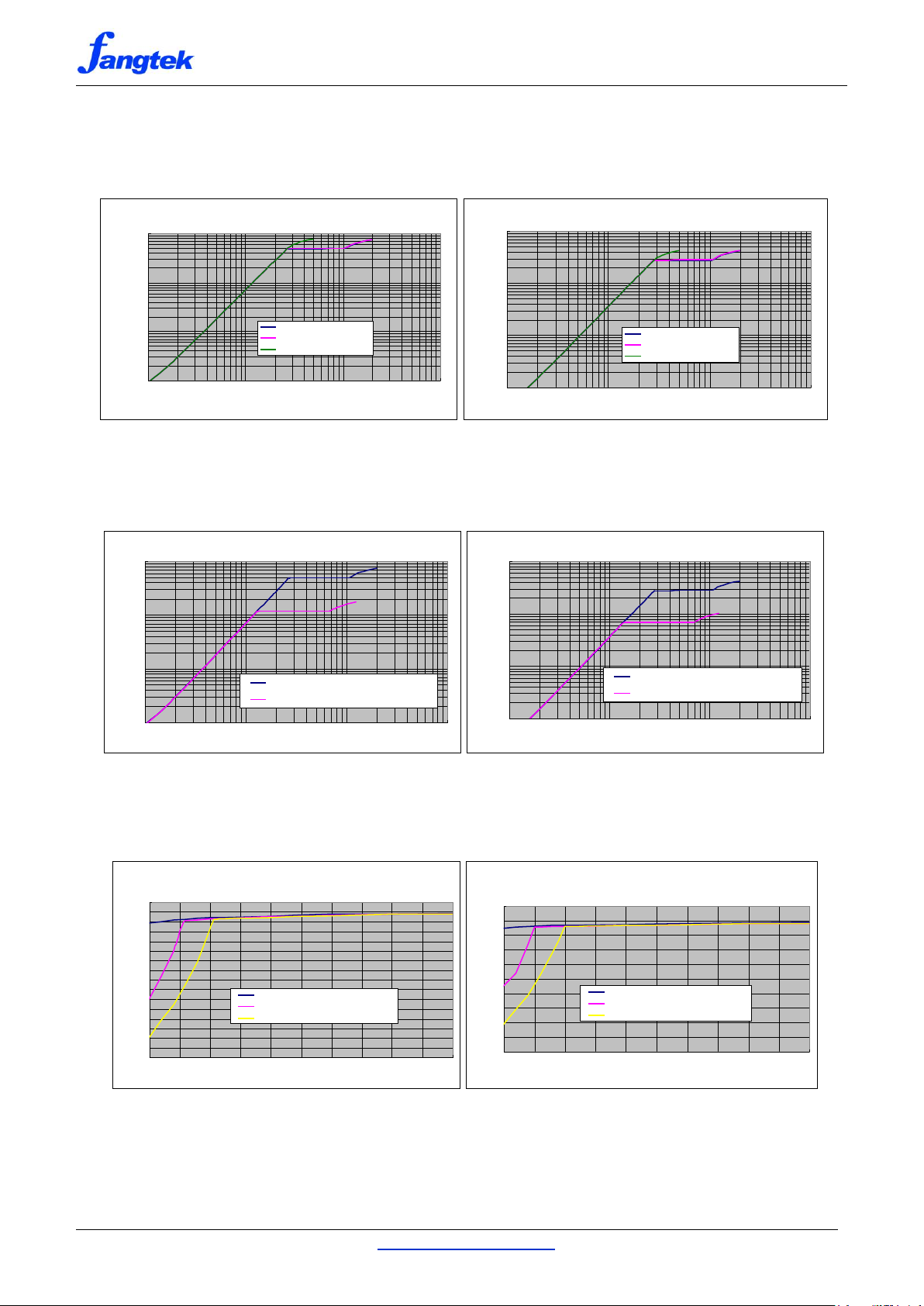

ft2925

DESCRIPTION

CONDITIONS

FIGURE #

Output Power vs. Input Voltage

RL=4Ω+33µH, ALC-1 & ALC-2 & Non-ALC Modes

3

RL=8Ω+33µH, ALC-1 & ALC-2 & Non-ALC Modes

4

RL=4Ω+33µH, ALC-1 Mode, SDRIVE=High/Unconnected

5

RL=8Ω+33µH, ALC-1 Mode, SDRIVE=High/Unconnected

6

Output Power vs. Supply Voltage

VIN=0.40VRMS, RL=4Ω+33µH, VKNEE=High/Unconnected/Low

7

VIN=0.40VRMS, RL=8Ω+33µH, VKNEE=High/Unconnected/Low

8

Overall Efficiency vs. Output Power

RL=4Ω+33µH, Non-ALC Mode, SDRIVE= Low/High

9

RL=8Ω+33µH, Non-ALC Mode, SDRIVE=Low/High

10

THD+N vs. Output Power

RL=4Ω+33µH, Non-ALC Mode

11

THD+N vs. Input Voltage

RL=4Ω+33µH, ALC-1 & ALC-2 Modes

12

THD+N vs. Input Frequency

Po=1W/3W, RL=4Ω+33µH, ALC-1 & ALC-2 Modes

13

Output Power vs. Input Frequency

VIN=0.20VRMS, RL=4Ω+33µH, Non-ALC Mode, f=20Hz ~ 20kHz

14

PSRR vs. Input Frequency

RL=4Ω+33µH, Inputs AC-Grounded

15

Quiescent Current vs. Supply Voltage

Input AC-Grounded, RL=No Load/4Ω+33µH/8Ω+33µH

16

Startup Output Waveforms

VIN=0.1VRMS

17

Shutdown Output Waveforms

VIN=0.1VRMS

18

ALC Release Time

VIN=0.75VRMS → 0.24VRMS, RL=4Ω+33µH, ALC-1 Mode

19

VIN=0.75VRMS → 0.24VRMS, RL=4Ω+33µH, ALC-2 Mode

20

Broadband Output Spectrum

RL=4Ω+33µH, VIN=0.2VRMS, SDRIVE=Low

21

RL=4Ω+33µH, VIN=0.2VRMS, SDRIVE=High

22

RL=4Ω+33µH, VIN=0.2VRMS, SDRIVE=Unconnected

23

Mode Transitions of Boost Regulator

RL=4Ω+33µH, Non-ALC Mode

24

TYPICAL PERFORMANCE CHARACTERISTICS

(Note 5)

VBAT=3.6V, f=1kHz, Load=4Ω+33µH, L=3.3µH, CIN=0.22µF, RIN=15kΩ (Av=25dB), ALC=NC, VKNEE=Low,

SDRIVE=Low, CS=22µF, CPVOUT=22µF//220µF, CPVDDL/R=1µF, RVBAT=10Ω, CVBAT=1µF, RAVDD=10Ω,

CAVDD=1µF, CBVDD=0.1µF, both channels driven, TA=25°C, unless otherwise specified.

List of Typical Performance Characteristics

Note 5: All parameters are measured according to the conditions specified in Electrical and Typical Performance

Characteristics sections with the following notes, unless otherwise specified:

5.1. The two differential inputs are shorted for common-mode input voltage measurement. All other parameters are

taken with input resistors RIN=15Ω and input capacitors CIN=0.22µF, unless otherwise specified.

5.2. The boost regulator’s supply decoupling capacitor CS=22µF is placed close to the inductor.

5.3. The boost regulator’s inductor L=3.3µH and Schottky diode are placed tightly together and close to the LX pins.

5.4. The boost regulator’s output capacitors CPVOUT=22µF//220µF are placed close to the PVOUT pins.

5.5. The audio amplifiers’ supply decoupling capacitors CPVDDL/R=1µF are placed individually close to PVDDL/R pins.

5.6. An output inductor of 33µH is placed in series with the load resistor to emulate a speaker load for all AC and

dynamic parameters.

5.7. A 33kHz lowpass filter is added even if the analyzer has an internal lowpass filter. An RC lowpass filter (100Ω,

47nF) is used on each output for the data sheet graphs.

DEC, 2017 http://www.fangtek.com.cn 8

ft2925

Output Power vs. Input Voltage

0.01

0.1

1

10

0.01 0.1 1 10

Input Voltage (Vrms)

Output Power (W)

ALC-1, RL=4Ω+33uH

ALC-2, RL=4Ω+33uH

Non-ALC, RL=4Ω+33uH

Output Power vs. Input Voltage

0.01

0.1

1

10

0.01 0.1 1 10

Input Voltage (Vrms)

Output Power (W)

ALC-1, RL=8Ω+33uH

ALC-2, RL=8Ω+33uH

Non-ALC, RL=8Ω+33uH

Output Power vs. Input Voltage

0.01

0.1

1

10

0.01 0.1 1 10

Input Voltage (Vrms)

Output Power (W)

ALC Mode, SDRIVE=High, RL=4Ω+33uH

ALC Mode, SDRIVE=NC, RL=4Ω+33uH

Output Power vs. Input Voltage

0.01

0.1

1

10

0.01 0.1 1 10

Input Voltage (Vrms)

Output Power (W)

ALC Mode, SDRIVE=High, RL=8Ω+33uH

ALC Mode, SDRIVE=NC, RL=8Ω+33uH

Output Power vs. Supply Voltage

2.0

2.4

2.8

3.2

3.6

4.0

4.4

4.8

5.2

3 3.5 4 4.5 5 5.5

Supply Voltage (V)

Output Power (W)

RL=4Ω+33uH, VKNEE Low

RL=4Ω+33uH, VKNEE Unconnected

RL=4Ω+33uH, VKNEE High

Output Power vs. Supply Voltage

1.0

1.4

1.8

2.2

2.6

3.0

3 3.5 4 4.5 5 5.5

Supply Voltage (V)

Output Power (W)

RL=8Ω+33uH, VKNEE Low

RL=8Ω+33uH, VKNEE Unconnected

RL=8Ω+33uH, VKNEE High

Figure 7: Output Power vs. Supply Voltage Figure 8: Output Power vs. Supply Voltage

Figure 3: Output Power vs. Input Voltage Figure 4: Output Power vs. Input Voltage

Figure 5: Output Power vs. Input Voltage Figure 6: Output Power vs. Input Voltage

TYPICAL PERFORMANCE CHARACTERISTICS (Cont’d)

DEC, 2017 http://www.fangtek.com.cn 9

Loading...

Loading...