Fairchild Semiconductor TMC2111A, TMC2011A Datasheet

www.fairchildsemi.com

TMC2011A/2111A

Variable-Length Shift Register

Features

• Low power CMOS

• TMC2011A is a pin compatible replacement for the

TDC1011 and TMC2011

• TMC2211A is a pin compatible replacement for the

TMC2111

• Inputs and outputs are TTL compatible

• DC–40MHz clock rate

• Selectable delay lengths (TMC2011A: 3 to 18 stages,

TMC2111A: 1 to 16 stages)

• Special 4-bit wide mixed-delay mode (TMC2011A)

• Available in 24-pin CERDIP and plastic DIP and 28-lead

Plastic Leadless Chip Carrier

Description

The TMC2011A and TMC2111A are high-speed, byte-wide

shift registers with programmable delay lengths.

The TMC2011A can be programmed to any length between

3 and 18 stages. It offers a special split-word mode which

allows for mixed delay lengths. The TMC2011A, constructed in low-power CMOS, is pin and function compatible

with the bipolar TDC1011.

The TMC2111A is a byte-wide shift register that can be programmed to lengths of 1 to 16 stages.

Applications

• Video filtering

• High speed data registers

• Local storage registers

• Digital delay lines

• Television special effects

• Pipeline register

The TMC2011A and TMC2111A are fully synchronous,

with all operations controlled by a single master clock. Input

and output registers are positive-edge triggered D-type flipflops. The length and mode controls are also registered. Both

devices operate with a maximum clock rate of 40 MHz.

Fabricated in a submicron CMOS process, the TMC2011A

and TMC2111A are TTL-compatible, and are available in

24-pin CERDIP and Plastic DIP packages as well as a

28-lead Plastic Leadless Chip Carrier.

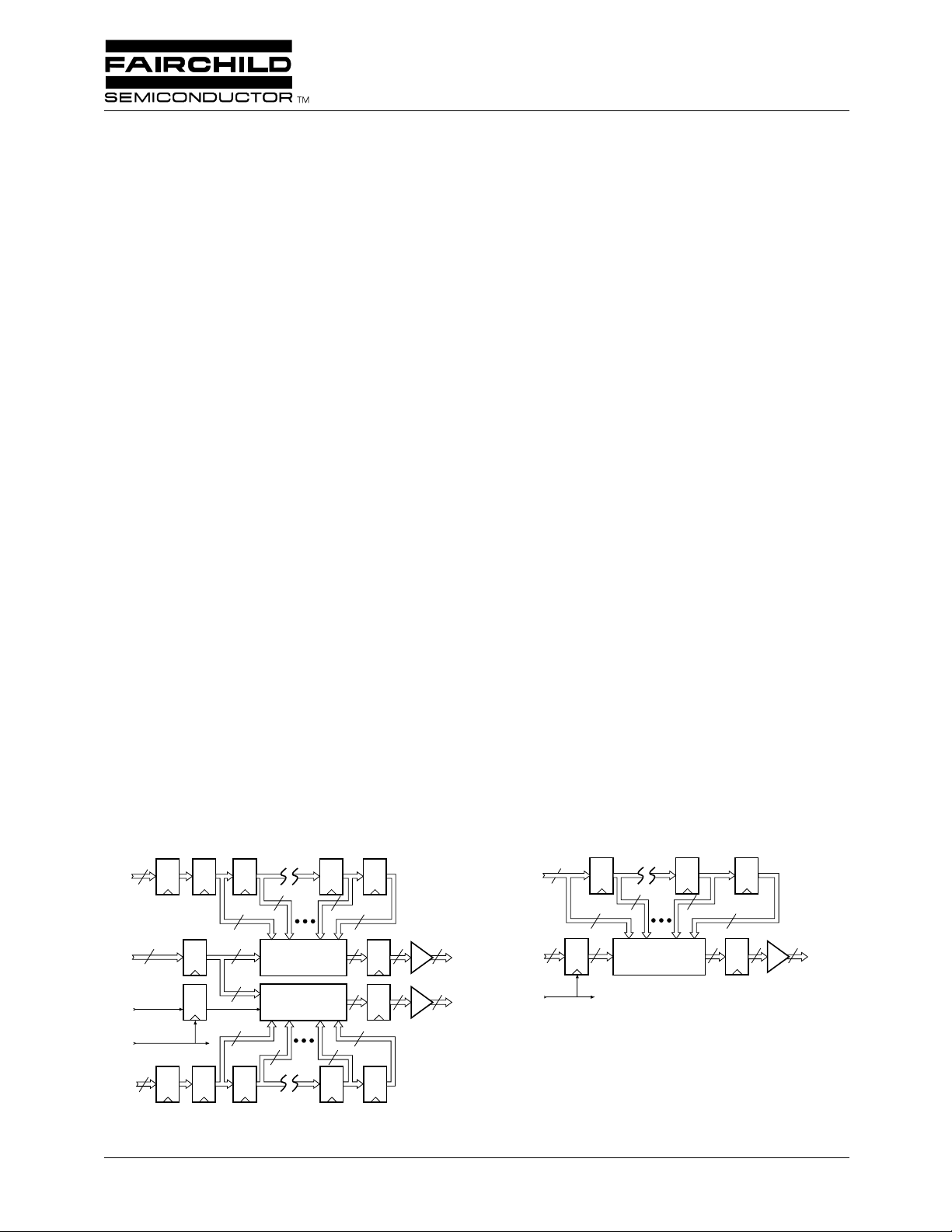

Block Diagrams

TMC2011A TMC2111A

3-0

7-4

DI

CLK

7-0

8

3-0

R

L

4

L

R

DI

3-0

L

3-0

MC

CLK

DI

R

1

R

R

R1R

2

L

I

2

4

44

7-4

4

R

3

44

1 of 16 Selector

4

1 of 16 Selector

4

R

3

R

R

16

17

44

4-Bit Wide

4-Bit Wide

R

R

18

44

R

18

444

44

4

R

16

17

DO

4

DO

65-2011A-01

R

1

88

8

8-Bit Wide

1 of 16 Selector

4

R

14

88

R

15

8

R

16

8

65-2011A-02

DO

7-0

Rev. 1.1.0

TMC2011A/2111A PRODUCT SPECIFICATION

Functional Description

The TMC2011A consists of two 4-bit wide, programmable

length shift registers. The TMC2111A consists of a single

8-bit wide, programmable length shift register. The internal

registers of each device share control signals and a common

clock.

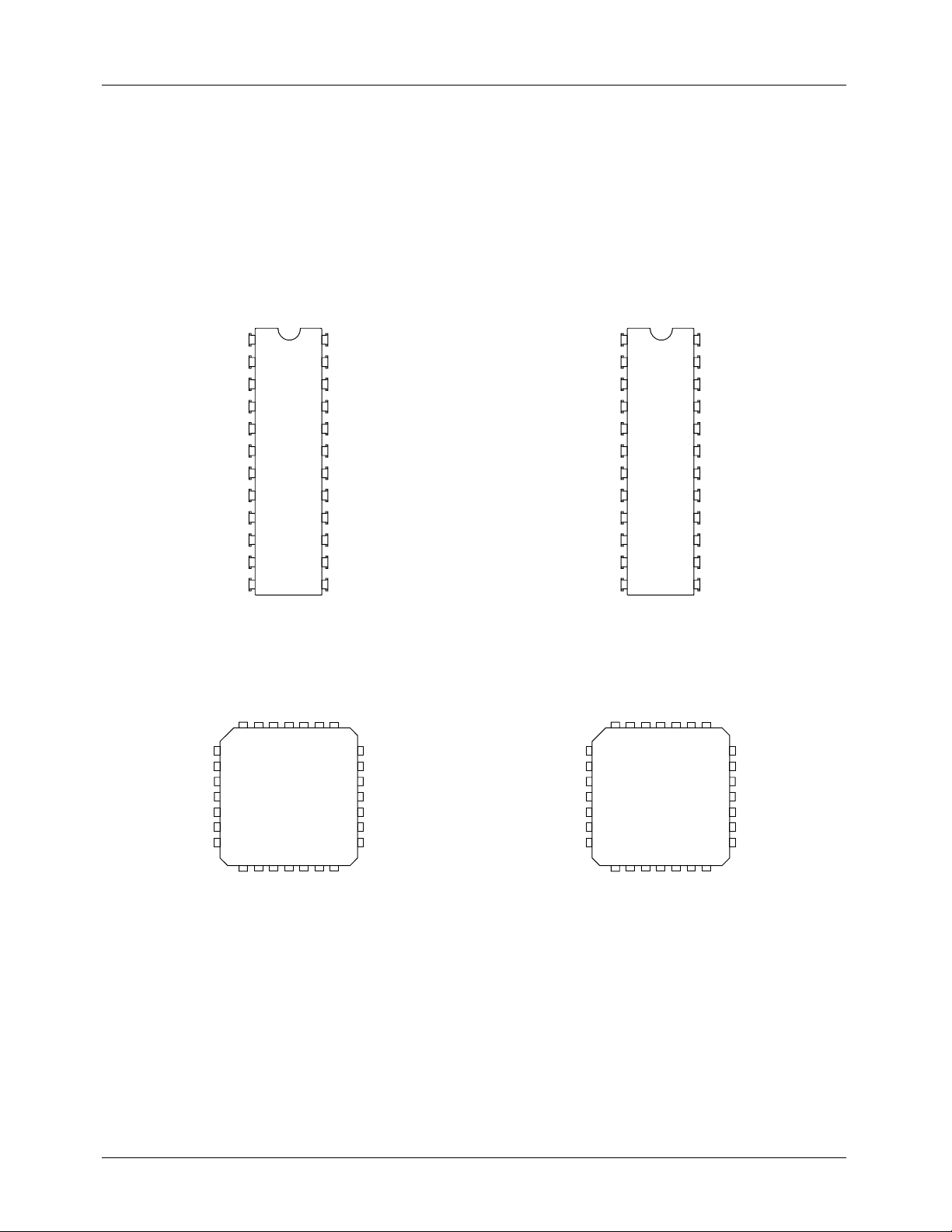

Pin Assignments

24 Lead DIP (B2, N2) Packages

DI

1

0

DI

1

DI

2

DI

3

L

0

L

1

V

DD

CLK

DI

4

DI

5

DI

6

12

DI

7

24

DO

DO

DO

DO

L

L

GND

TMC2011A

MC

DO

DO

DO

13

DO

DI

DI

DI

DI

L

L

V

DD

CLK

DI

DI

DI

DI

1

0

1

2

3

0

1

4

5

6

12

7

0

1

2

3

2

3

4

5

6

7

24

TMC2111A

13

65-2011A-03

DO

DO

DO

DO

L

2

L

3

GND

GND

DO

DO

DO

DO

0

1

2

3

4

5

6

7

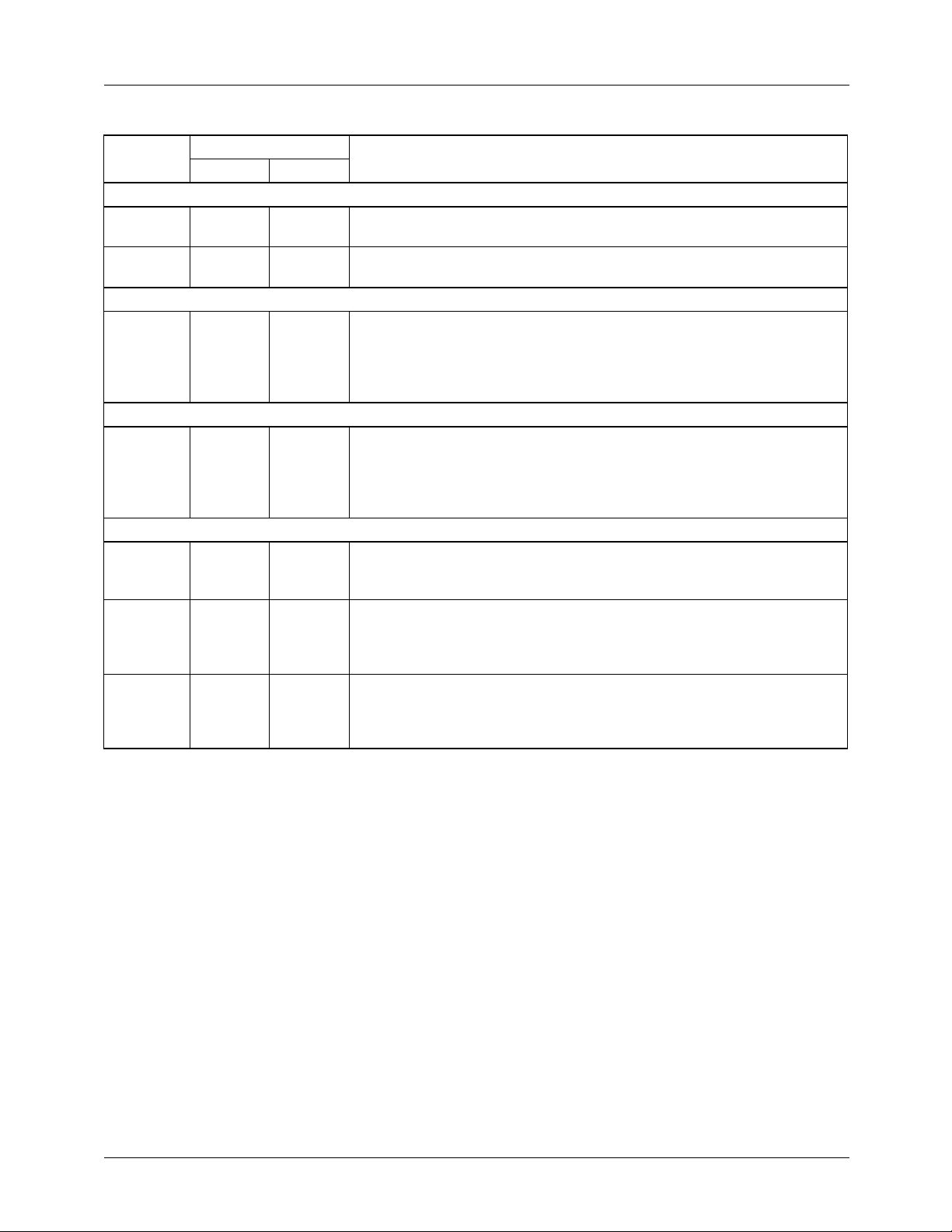

28 Lead PLCC (R3) Package

DI2DI1DI0DO0DO1DO2DO

128

DI

3

L

0

L

1

V

DD

CLK

DI

NC

4

TMC2011A

7

DI5DI6DI

DO7DO6DO5DO

3

DI2DI1DI0DO0DO1DO2DO

128

NC

L

2

L

3

GND

GND

MC

NC

4

DI

V

DD

CLK

DI

NC

3

L

0

L

1

4

TMC2111A

7

DI5DI6DI

DO7DO6DO5DO

3

4

65-2011A-04

NC

L

2

L

3

GND

GND

MC

NC

2

PRODUCT SPECIFICATION TMC2011A/2111A

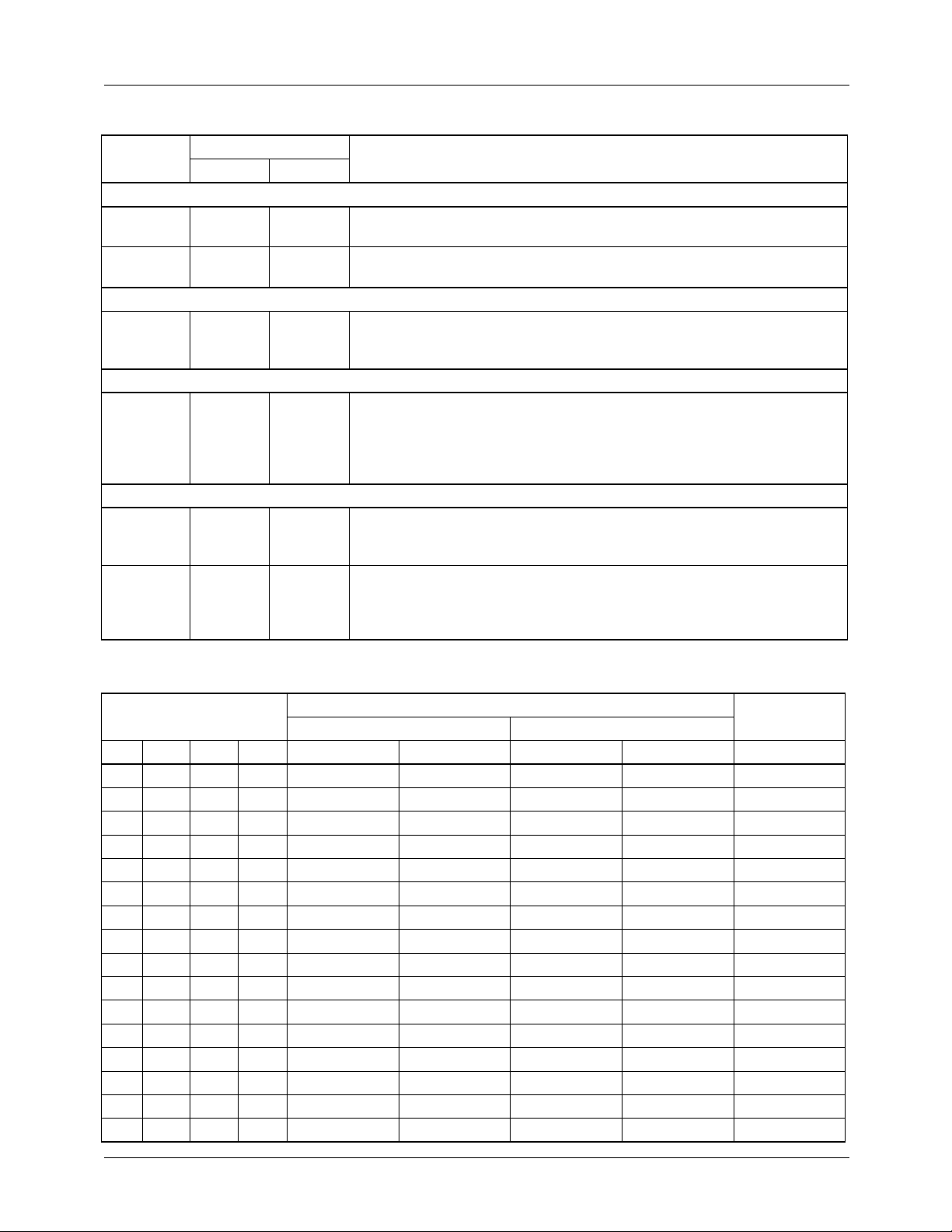

Pin Descriptions – TMC2011A

Pin Number

Pin Name

Power

V

DD

GND 18 21,22 Ground. The TMC2011A operates from a single +5V supply. All power

Data Inputs

DI

7-0

Data Outputs

DO

7-0

Controls

CLK 8 9

L

3-0

MC 17 20

78 Supply Voltage. The TMC2011A and operates from a single +5V supply.

12,11,10,

9,4,3,2,1

13,14,15,

16,21,22,

23,24

19,20,6,5 23,24,7,6 Length Select. The length select input is used to determine the register

14,13,12,

10,5,4,3,2

15,16,17,

18,26,27,

28,1

Pin Function DescriptionDIP PLCC

All power and ground lines must be connected.

and ground lines must be connected.

Data Input. Eight inputs are provided for the data, which pass through the

shift register unchanged. The eight inputs on the TMC2011A are divided

into two groups of four bits to allow mixed delay operation. The lengths of

these two groups are different when the Mode Control (MC) is HIGH (see

Table 1). When MC is LOW both groups have equal delays.

Data Output. The outputs of the shift register are delayed relative to the

input signals. The amount of the delay is programmable (see Table 1).

The outputs remain valid for a minimum of t

leading edge of CLK. This allow the data to be latched into circuits with

non-zero hold time requirements.

Master Clock. All inputs and outputs are synchronous and operate from a

single master clock. All operations occur on the rising edge of the master

clock.

delay of the TMC2011A. This input is registered and affects the output t

after the clock edge after it is input to the device (see Timing Diagram).

Delay lengths are specified in Table 1.

Mode Control. The Mode Control is used to select the special 4-bit wide

split mode. When HIGH, the delay on DO

DO

have the delay specified by the length select. When MC is LOW, all

3-0

eight bits have equal delays as specified by the length select.

nanoseconds after the

HO

is fixed at 18 stages, while

7-4

DO

3

TMC2011A/2111A PRODUCT SPECIFICATION

Pin Descriptions – TMC2111A

Pin Number

Pin Name

Power

V

DD

GND 17,18 20,21,22 Ground. The TMC2111A operates from a single +5V supply. All power

Data Inputs

DI

7-0

Data Outputs

DO

7-0

Controls

CLK 8 9

L

3-0

78 Supply Voltage. The TMC2111A operates from a single +5V supply. All

12,11,10,

9,4,3,2,1

13,14,15,

16,21,22,

23,24

19,20,6,5 23,24,7,6 Length Select. The length select input is used to determine the register

14,13,12,

10,5,4,3,2

15,16,17,

18,26,27,

28,1

Pin Function DescriptionDIP PLCC

power and ground lines must be connected.

and ground lines must be connected.

Data Input. Eight inputs are provided for the data, which pass through the

shift register unchanged. The TMC2111A consists of a single group of

eight bits with all data bits having equal delays.

Data Output. The outputs of the shift register are delayed relative to the

input signals. The amount of the delay is programmable (see Table 1).

The outputs remain valid for a minimum of t

leading edge of CLK. This allow the data to be latched into circuits with

non-zero hold time requirements.

Master Clock. All inputs and outputs are synchronous and operate from a

single master clock. All operations occur on the rising edge of the master

clock.

delay of the TMC2111A. This input is registered and affects the output t

after the clock edge after it is input to the device (see Timing Diagram).

Delay lengths are specified in Table 1.

nanoseconds after the

HO

DO

Table 1. Programming Length Controls

TMC2011A

TMC2111AInput Code Mode (MC) =0 Mode (MC) =1

L

L

3

0000333181

0001444182

0010555183

0011666184

0100777185

0101888186

0110999187

0 1 1 1 10 10 10 18 8

1 0 0 0 11 11 11 18 9

1 0 0 1 12 12 12 18 10

1 0 1 0 13 13 13 18 11

1 0 1 1 14 14 14 18 12

1 1 0 0 15 15 15 18 13

1 1 0 1 16 16 16 18 14

1 1 1 0 17 17 17 18 15

1 1 1 1 18 18 18 18 16

L

2

L

1

DO

0

Length DO

3-0

Length DO

7-4

Length DO

3-0

Length DO

7-4

7-0

Length

4

Loading...

Loading...