Fairchild Semiconductor TMC2072 Datasheet

TMC2072

Genlocking Video Digitizer

www.fairchildsemi.com

Features

• Fully integrated acquisition

• 3-channel video input multiplexer

• Two-stage (analog and digital) video clamp

• Automatic gain adjustment

• Sync detection and separation

• Pixel and subpixel adjustment of video-to-sync output

timing

• Genlock to any NTSC or PAL format, including PAL-M

and PAL-N

• Pixel clock generation

• 8-bit video A/D conversion

• Standard R-bus serial microprocessor interface

• User-selectable line-locked pixel rates include:

– 12.27 MHz NTSC & PAL-M

– 13.5 MHz NTSC & all PAL

– 14.75 MHz PAL (non-M) TMC2072-1 only

– 15.0 MHz PAL (non-M) TMC2072-1 only

• Direct interface to Fairchild Semiconductor video

encoders and decoders

• Built-in circuitry for crystal oscillator

• No tuning or external voltage reference required

• Space-saving 100-lead MQFP package

Applications

• Frame grabber

• Digital videotape recorders

• Desktop video

Description

The TMC2072 Genlocking Video Digitizer samples and

quantizes standard analog baseband composite NTSC

or PAL video into its 8-bit digital equivalent. It extracts

horizontal and vertical sync signals, from which an on-chip

PLL generates a line-locked pixel clock for the on-chip 8-bit

A/D converter and a double-speed register clock to transfer

data to a subsequent video processing subsystem. A second

PLL generates a chroma subcarrier locked to the incoming

chroma burst. The chip reports each line’s color burst phase

and frequency during the next horizontal sync pulse.

The TMC2072 includes a three-channel video input multiplexer, analog clamp, variable gain amplifier, and digital

back porch clamp. The user may provide either an external

20MHz clock or a 20MHz crystal. No external component

changes or tuning are required for PAL or NTSC operation at

either D1 or square pixel VGA pixel rates.

The TMC2072 is fabricated in a submicron CMOS process

and is packaged in a 100-lead MQFP. Its performance is

guaranteed from 0 to 70°C.

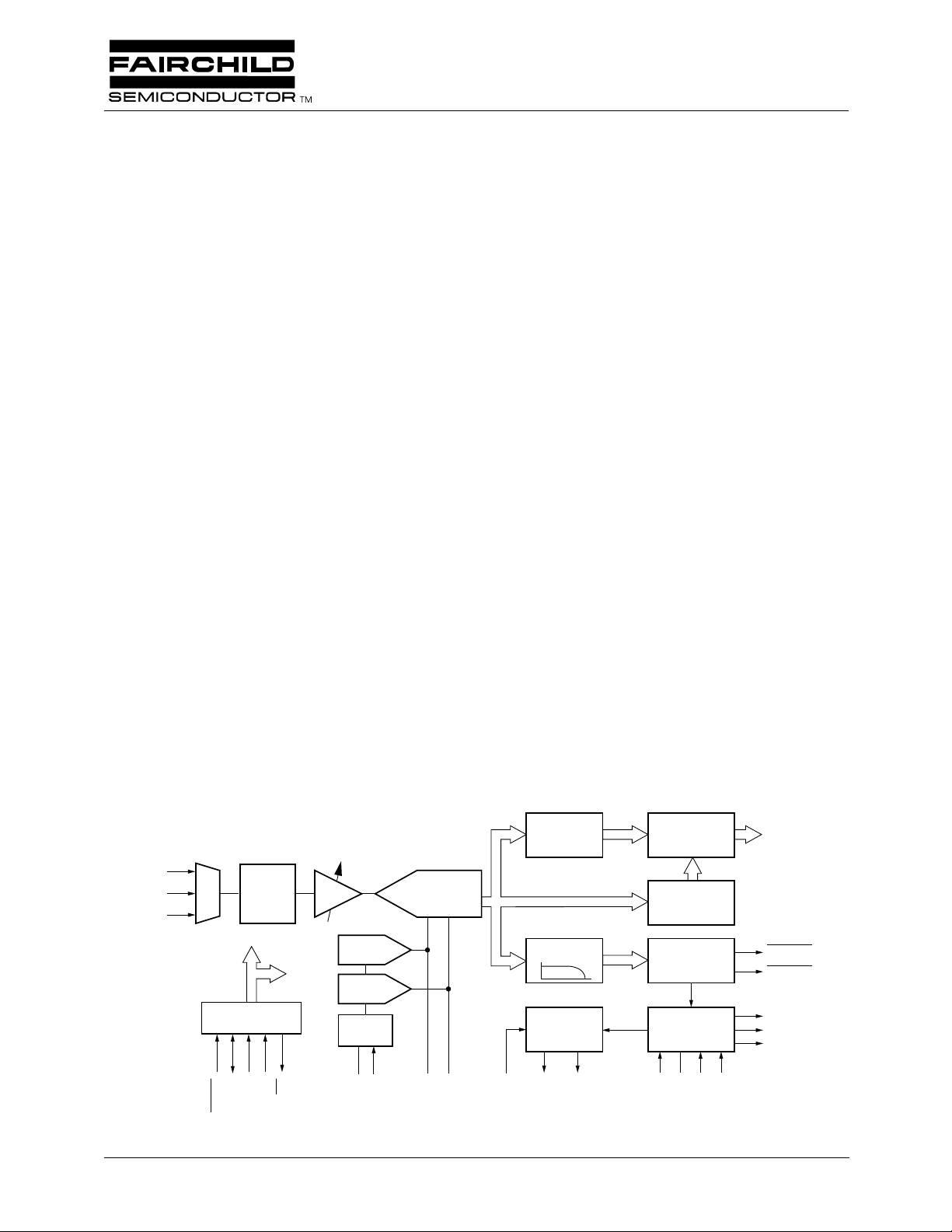

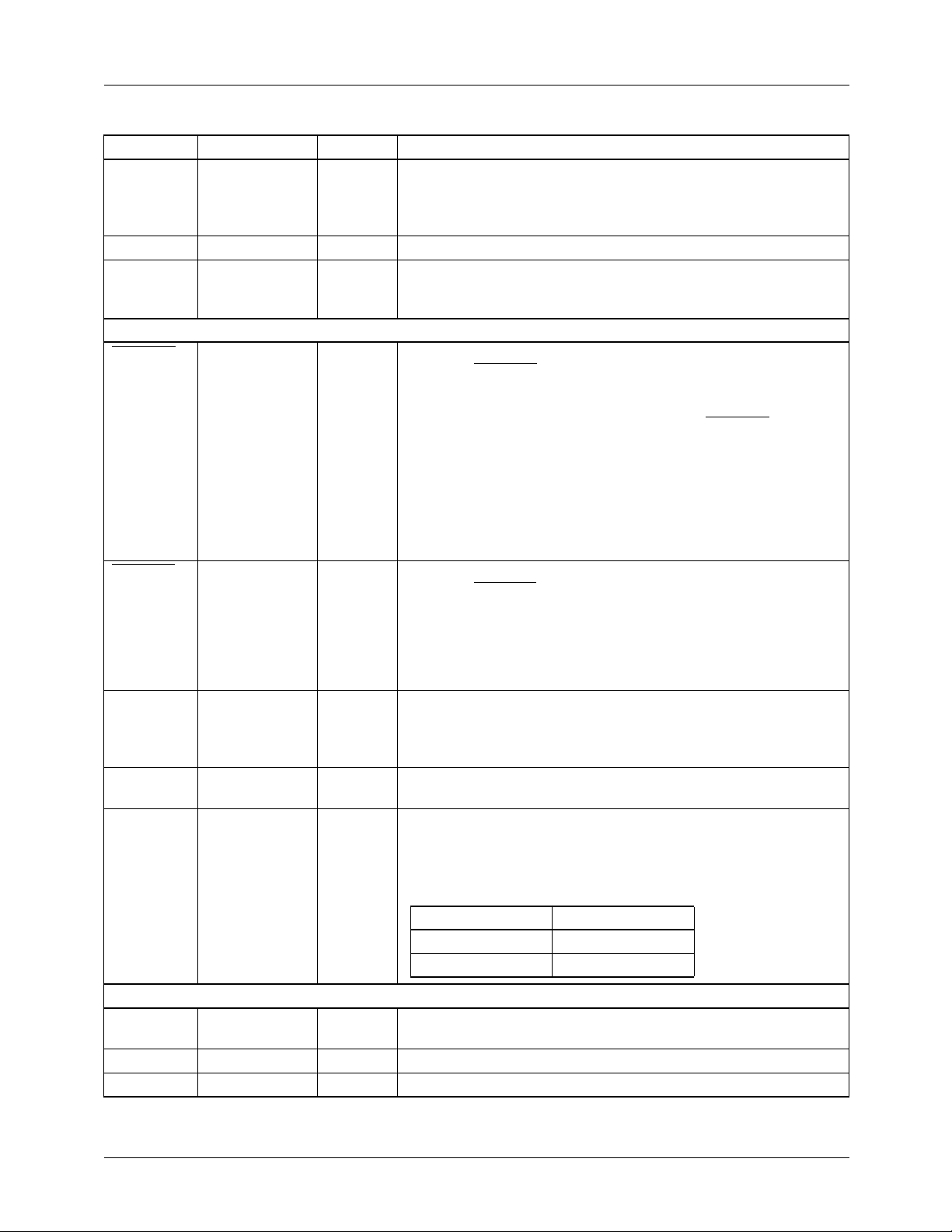

Block Diagram

V

IN1

V

IN2

V

IN3

MUX

CONTROL

RESET

MICROPROCESSOR

INTERFACE

ANALOG

CLAMP

SCL

SDA

SA

2-0

INT

BACK PORCH

CLAMP

GAIN

D/A

D/A

+1.2V

REF

V

COMP

ANALOG INTERFACE DDS/PIXEL CLOCK INTERFACE

A/D

R

LOWPASS

FILTER

DIRECT

DIGITAL

SYNTHESIZER

T

B

R

CLK IN

CLK

OUT

DDS

OUT

DATA

SELECTOR

SUBCARRIER

PHASE-LOCKED

LOOP

SYNC

SEPARATOR

HORIZONTAL

PHASE-LOCKED

LOOP

BYP

C

PFD IN

PXCK SEL

CVBS

7-0

GVSYNC

GHSYNC

PXCK

LDV

VALID

65-2072-01

EXT PXCK

REV. 1.0.4 6/19/01

TMC2072 PRODUCT SPECIFICATION

Functional Description

The TMC2072, a fully integrated self-genlocking video A/D

converter, digitizes NTSC or PAL baseband composite signals. It accepts video on one of three input channels, adjusts

the gain, clamps to the back porch and digitizes the video at

a user-selectable multiple of the horizontal line frequency.

It extracts horizontal and vertical sync, measures the subcarrier frequency and phase, and provides these data with the

digitized composite data over an 8-bit digital video port.

Horizontal and vertical sync outputs are provided, along with

pixel clock (LDV) and twice pixel clock (PXCK).

Operating parameters are set up via a standard two-wire

microprocessor port. The chip can work with either an internal or an external voltage reference.

Fabricated in an advanced CMOS process, the TMC2072 is

housed in a 100 lead metric quad flat package. Its performance is guaranteed from 0 to 70°C and from 4.75 to 5.25

supply volts.

Timing

The TMC2072’s A/D converter and digital signal path

operate from alternate cycles of an internally-synthesized

clock, PXCK. This 24.5 to 30 MHz clock is derived from the

incoming 20 MHz reference clock and phase-locked to the

horizontal sync tips of the incoming analog video stream.

The frequency of PXCK may be set as 1560 (NTSC VGA

square pixel), 1716 (NTSC D1), 1732 (PAL D1), or 1888 or

1920 (PAL VGA) times the incoming video line rate.

Timing of the serial microprocessor interface bus is independent of the pixel clock and is described under the Microprocessor Interface section that follows Functional Description.

Video Input

Via the microprocessor interface, the user can enable one of

the chip’s three analog video input ports. Although each port

normally anticipates a standard video signal level with

286 to 300 mV between sync tip and blank, another control

register bit allows it to be used with half-power (approximately 70% amplitude) signals. Good crosstalk isolation

accommodates active video on all three inputs simultaneously. The user must provide antialias filtering and proper

line termination externally.

Analog Clamp

The front-end analog clamp ensures that the input video falls

within the active range of the A/D converter. The digitized

composite video output can be clamped to the back porch by

a secondary digital clamp.

Automatic Gain Adjustment

To accommodate approximately a ±15% range in video

signal amplitudes, the TMC2072’s on-chip AGC circuit

engages for one video frame following either: 1) initial lock

after reset; 2) loss and recovery of lock while operating; or

3) setting of control bit AGCEN high by the host microprocessor. The AGC operation adjusts the A/D converter’s onchip reference voltages until video blank causes it to output

approximately 1/4 of its full range. The chip then holds this

gain adjustment constant until a new AGC sequence is initiated by AGCEN going high or by loss and recovery of video

lock. The one-frame timeout prevents the gain control from

riding gain and trying to track noise or minor variations in

signal strength.

To handle doubly-terminated and other weak video signals,

the user should set the VGAIN control bit high, thereby

boosting video gain 50% above nominal.

Analog-to-Digital Converter

The TMC2072 contains a high-performance 8-bit A/D

converter. Its gain and offset are automatically set as a part of

the automatic gain adjustment process during initial signal

acquisition, and require no user attention.

The reference voltages to the A/D converter are set up by

internal D/A converters under automatic control during

genlock acquisition. These voltages determine the gain and

offset of the A/D converter with respect to the video level

presented at its input.

Low-Pass Filter

The digitized composite video stream is digitally low-pass

filtered to remove chrominance components from the sync

separator. Filtering provides robust operation by optimizing

the signal-to-noise ratio of the synchronizing/blanking portion of the video, improving the accuracy of the back porch

blanking level detector.

A digital sync separator provides the output sync signals,

GHSYNC and GVSYNC, and times internal operations.

Horizontal Phase-Locked Loop

A phase-locked loop generates PXCK, at twice the pixel

rate. The reference signal for the horizontal phase-locked

loop is generated by the Direct Digital Synthesizer (DDS).

The DDS output is constructed with an internal D/A converter and is output from the TMC2072 via the DDS OUT

pin. This signal is passed through an external LC filter and

input to the horizontal phase-comparator.

The frequency of the DDS output is one ninth of that of

PXCK.

A 20MHz clock is required to drive the DDS. Preferably, this

may be input to the TMC2072 via CMOS levels on the CLK

IN pin. Alternately, a 20MHz crystal may be directly

connected between CLK IN and CLK OUT with tuning

capacitors to activate the internal crystal oscillator circuitry.

2 REV. 1.0.4 6/19/01

PRODUCT SPECIFICATION TMC2072

If incoming video is lost or disconnected after the TMC2072

has locked to it, PXCK and GRS data will continue, but

GVSYNC

and every eighth GHSYNC will cease until lock

is reestablished. The GRS will report the initial subcarrier

frequency set by the Format select bits of the Control

Register. The TMC2072 will relock to incoming video

within two frames after it is restored.

Subcarrier Phase-Locked Loop

A fully-digital phase-locked loop is used to extract the phase

and frequency of the incoming color burst. These frequency

and phase values are output over the CVBS bus during the

horizontal sync period. Fairchild’s video decoder and genlockable encoder chips will accept these data directly.

Back Porch Digital Clamp

A digital back-porch clamp is employed to ensure a constant

blanking level. It digitally offsets the data from the A/D converter to set the back porch level to precisely 3Ch for NTSC

and 40h for PAL. When the digital clamp is enabled, the

CVBS video output data is the A/D conversion result minus

the back porch level plus 3Ch (40h for PAL). The back-porch

level is low-pass filtered to minimize streaking artifacts from

subtle line-to-line variations.

Digitized Video Output

The digitized 8-bit video output is provided over an 8-bit

wide CVBS data port, synchronous with PXCK and LDV.

Subcarrier frequency, subcarrier phase, and Field ID data

(GRS) are transmitted in 4-bit nibbles over CVBS

3-0

during

the horizontal sync tip period at the PXCK rate.

Microprocessor Interface

The TMC2072 is controlled by a standard 2-wire bus. Up to

eight TMC2072 devices may be connected to the 2-wire

serial interface with each device having a unique address.

The 2-wire interface comprises a clock input (SCL) and a

bi-directional data (SDA) pin. The TMC2072 acts as a slave

for receiving and transmitting data over the serial interface.

When the serial interface is not active, the logic levels on

SCL and SDA are pulled HIGH by external pull-up resistors.

Data received or transmitted on the SDA line must be stable

for the duration of the positive-going SCL pulse. Data on

SDA must change only when SCL is LOW. If SDA changes

state while SCL is HIGH, the serial interface interprets that

action as a start or stop sequence.

There are five components to serial bus operation:

• Start signal

• Slave address byte

• Base register address byte

• Data byte to read or write

• Stop signal

When the serial interface is inactive (SCL and SDA are

HIGH) communications are initiated by sending a start signal. The start signal is a HIGH-to-LOW transition on SDA

while SCL is HIGH. This signal alerts all slaved devices that

a data transfer sequence is coming.

The first eight bits of data transferred after a start signal comprise a seven bit slave address and a single R/W bit. The R/W

bit indicates the direction of data transfer, read from or write

to the slave device. If the transmitted slave address matches

the address of the device (set by the state of the SA2:0 input

pins.), the TMC2072 acknowledges by bringing SDA LOW

on the 9th SCL pulse. If the addresses do not match, the

TMC2072 does not acknowledge.

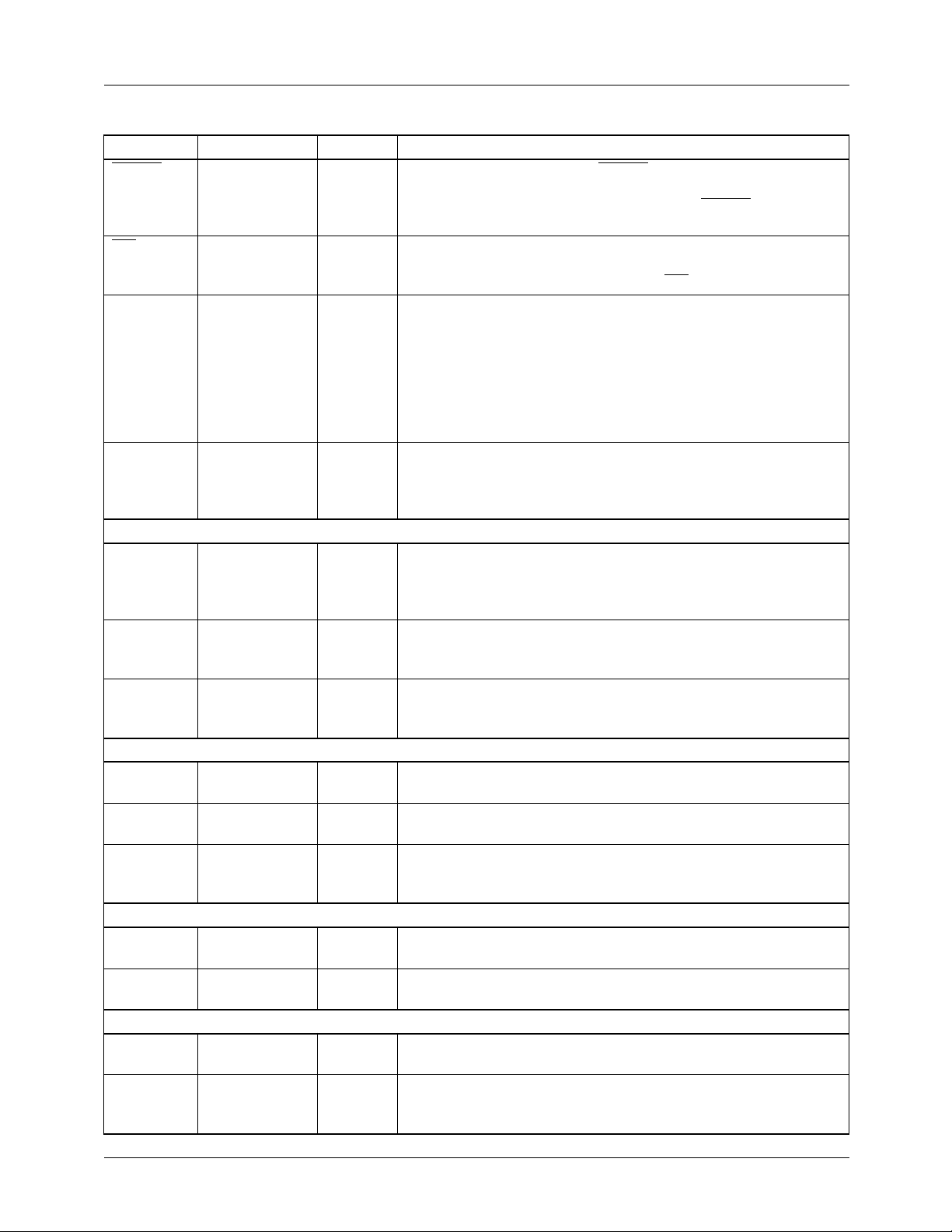

Table 1. Serial Port Addresses

A

1 0 0 0 1/0 1/0 1/0

The address is 1000 SA2 SA1 SA0.

A

6

A

5

A

4

A

3

(SA2)

A

2

(SA1)

A

1

0

(SA0)

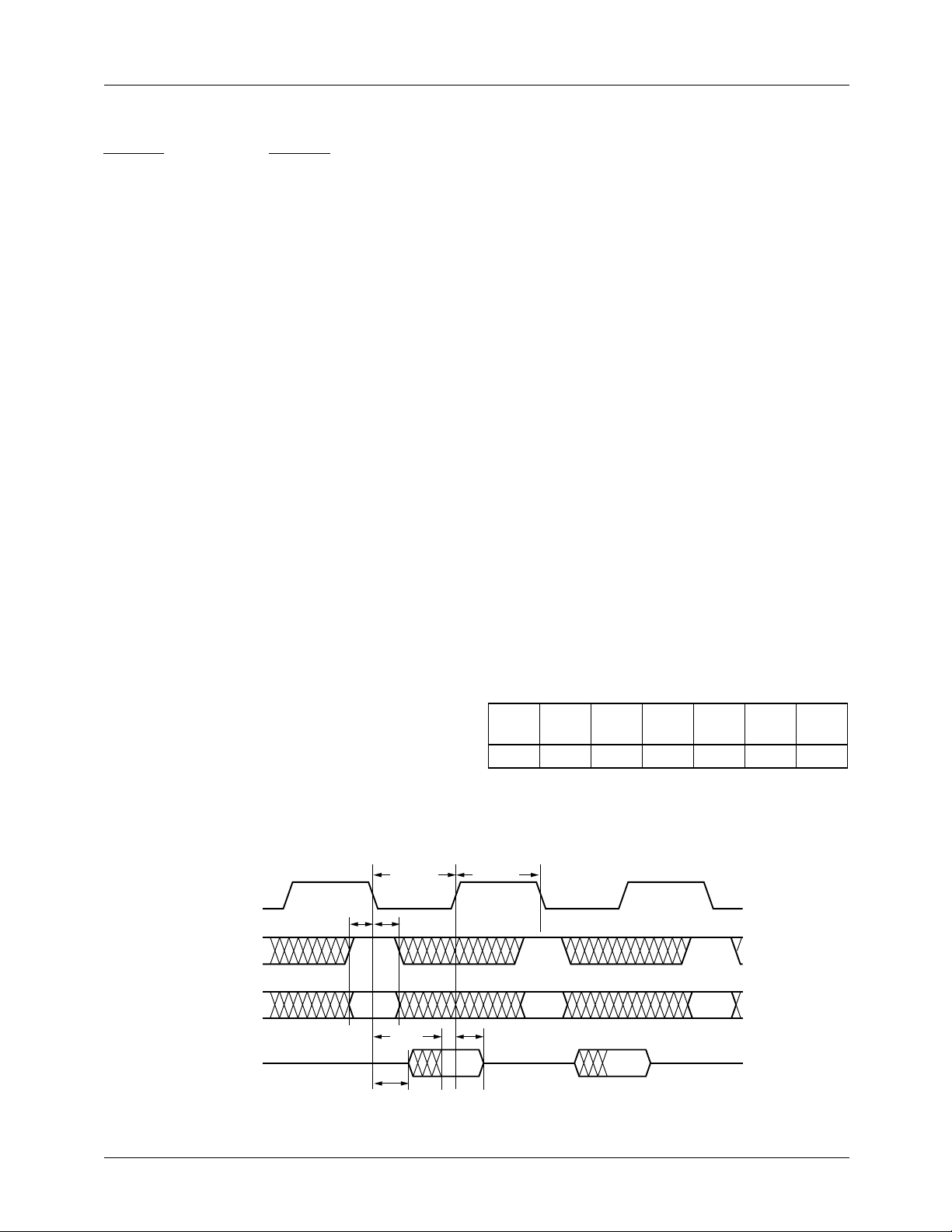

t

PWLCS

SCL

t

SA

SDA

SA

–SA

2

0

D7–D

0

Figure 1. Microprocessor Parallel Port – Read Timing

REV. 1.0.4 6/19/01 3

t

DOZ

t

DOM

t

HA

t

PWHCS

t

DOM

65-2072-02

TMC2072 PRODUCT SPECIFICATION

Data Transfer via Serial Interface

For each byte of data read or written, the MSB is the first bit

of the sequence.

If the TMC2072 does not acknowledge the master device

during a write sequence, the SDA remains HIGH so the master can generate a stop signal. If the master device does not

acknowledge the TMC2072 during a read sequence, the

TMC2072 interprets this as “end of data.” The SDA remains

HIGH so the master can generate a stop signal.

Writing data to specific control registers of the TMC2072

requires that the 8-bit address of the control register of interest be written after the slave address has been established.

This control register address is the base address for subsequent write operations. The base address autoincrements by

one for each byte of data written after the data byte intended

for the base address. If more bytes are transferred than there

are available addresses, the address will not increment and

remain at its maximum value of 10h. Any base address

higher than 10h will not produce an ACKnowledge signal.

If no ACKnowledge is received from the master, the encoder

will automatically stop sending data.

Data are read from the control registers of the TMC2072 in

a similar manner. Reading requires two data transfer

operations:

The base address must be written with the R/W bit of the

slave address byte LOW to set up a sequential read

operation.

Reading (the R/W bit of the slave address byte HIGH)

begins at the previously established base address. The

address of the read register autoincrements after each byte is

transferred.

To terminate a read/write sequence to the TMC2072, a stop

signal must be sent. A stop signal comprises a LOW-toHIGH transition of SDA while SCL is HIGH.

A repeated start signal occurs when the master device driving the serial interface generates a start signal without first

generating a stop signal to terminate the current communication. This is used to change the mode of communication

(read, write) between the slave and master without releasing

the serial interface lines.

Serial Interface Read/Write Examples

Write to one control register

↓ Start signal

↓ Slave Address byte (R/W bit = LOW)

↓ Base Address byte

↓ Data byte to base address

↓ Stop signal

Write to four consecutive control registers

↓ Start signal

↓ Slave Address byte (R/W bit = LOW)

↓ Base Address byte

↓ Data byte to base address

↓ Data byte to (base address + 1)

↓ Data byte to (base address + 2)

↓ Data byte to (base address + 3)

↓ Stop signal

Read from one control register

↓ Start signal

↓ Slave Address byte (R/W bit = LOW)

↓ Base Address byte

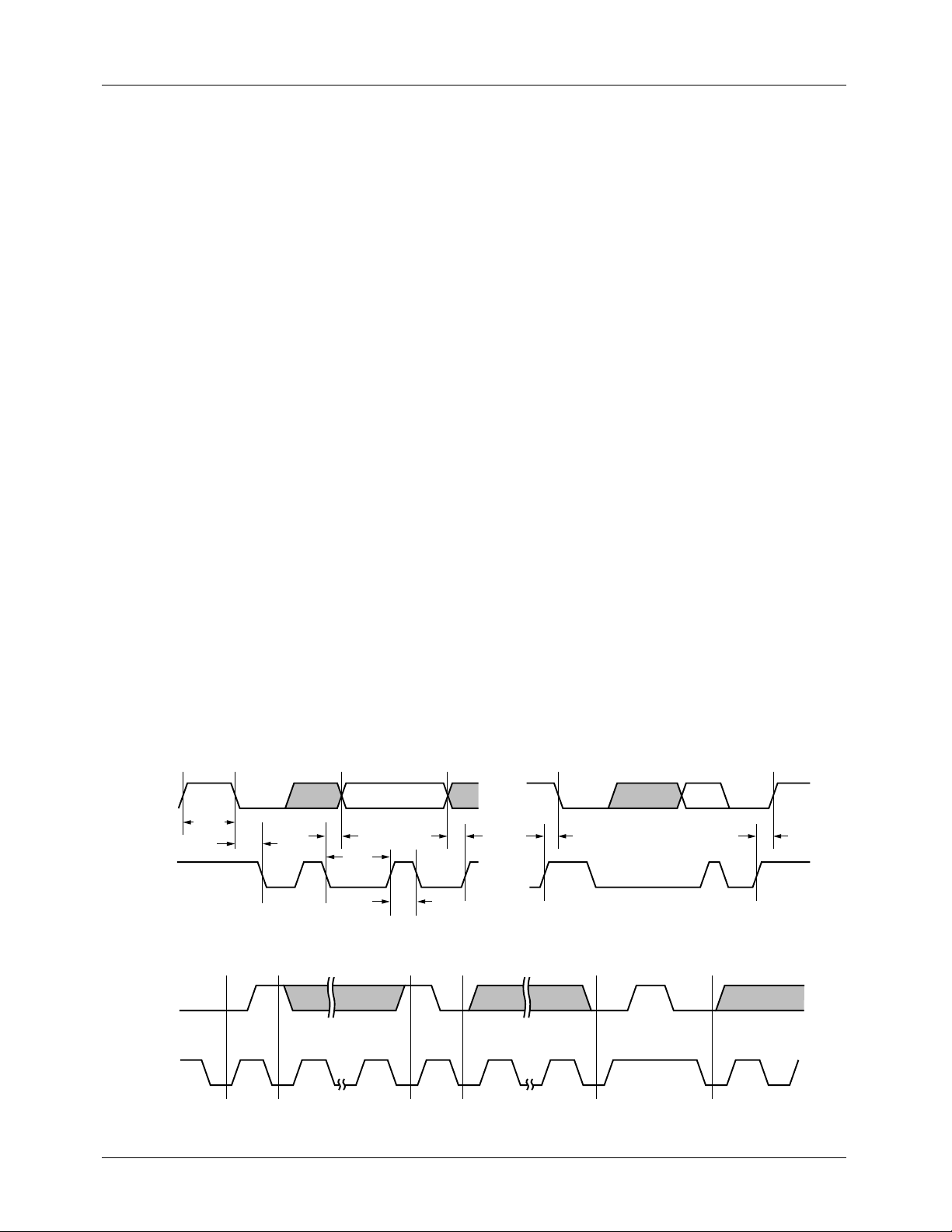

SDA

t

SCL

SDA

SCL

t

STAH

BUFF

STOP

t

DHO

t

DAL

Figure 2. Serial Port Read/Write Timing

Figure 3. Serial Interface – Start/Stop Signal

t

DSU

t

DAH

START STOP START

t

STASU

t

STOSU

65-2072-03

65-2072-04

4 REV. 1.0.4 6/19/01

PRODUCT SPECIFICATION TMC2072

↓ Stop signal

↓ Start signal

↓ Slave Address byte (R/W bit = HIGH)

↓ Data byte from base address

↓ Stop signal

Read from four consecutive control registers

↓ Start signal

↓ Slave Address byte (R/W bit = LOW)

↓ Base Address byte

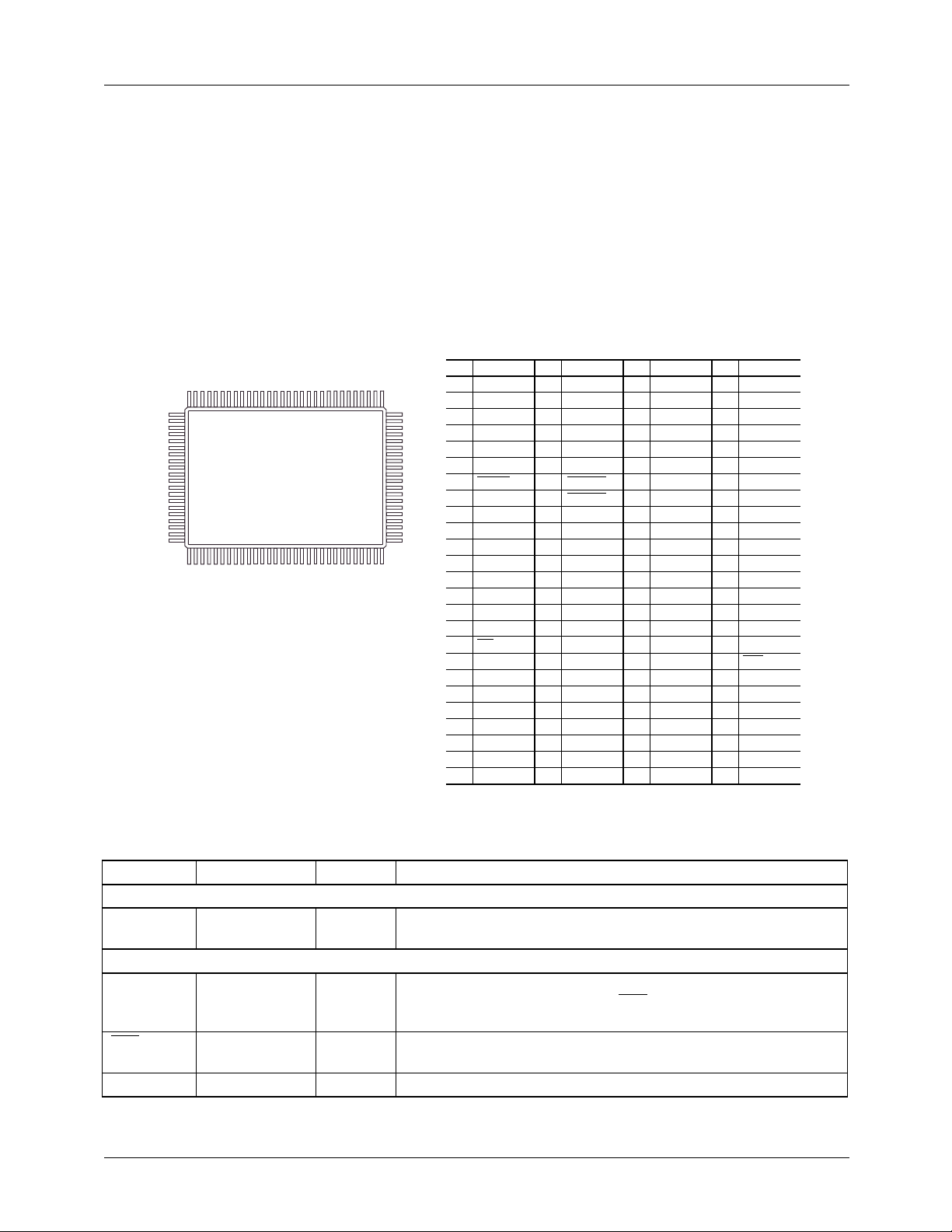

Pin Assignments

81

100

130

Note:

1. NC = No internal connection between package

and IC. Fairchild Semiconductor recommends

leaving these pins open to simplify board

upgrades to potential future genlock chips.

↓ Stop signal

↓ Start signal

↓ Slave Address byte (R/W bit = HIGH)

↓ Data byte from base address

↓ Data byte from (base address + 1)

↓ Data byte from (base address + 2)

↓ Data byte from (base address + 3)

↓ Stop signal

5180

Pin Name Pin Name

SA

1

0

SA

2

50

31

1

SA

3

2

SDA

4

SCL

5

V

6

DD

RESET

7

D

8

GND

NC

9

NC

10

NC

11

NC

12

NC

13

NC

14

NC

15

D

16

GND

INT

17

V

18

DD

NC

19

NC

20

CVBS

21

CVBS

22

CVBS

23

CVBS

24

CVBS

25

V

26

DD

D

27

GND

CVBS

28

CVBS

29

CVBS

30

BURL

31

GHSYNC

32

GVSYNC

33

VALID

34

FID0

35

FID1

36

NC

37

D

38

GND

D

39

GND

LDV

40

D

41

GND

V

42

DD

NC

43

V

44

DD

PXCK

45

D

46

0

1

2

3

4

GND

D

47

GND

V

48

DD

V

49

DDA

A

50

GND

Pin Name Pin Name

V

51

DDA

V

52

DDA

NC

53

5

6

7

NC

54

A

55

GND

NC

56

R

57

B

V

58

IN3

NC

59

V

60

DDA

V

61

IN2

NC

62

A

63

GND

V

64

DDA

V

65

IN1

NC

66

A

67

GND

R

68

T

A

69

GND

V

70

REF

NC

71

A

72

GND

V

73

DDA

A

74

GND

C

75

BYP

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

NC

PFD IN

NC

NC

NC

A

GND

DDS OUT

NC

NC

NC

PXCK SEL

V

DDA

COMP

A

GND

D

GND

CLK IN

V

DD

CLK OUT

EXT PXCK

D

GND

D

GND

D

GND

V

DD

NC

V

DD

65-2072-05

Pin Definitions

Pin Name Pin Number Pin Type Function

Video Input

V

IN1-3

Clocks

CLK IN 91 CMOS 20 MHz DDS clock input. 20 MHz CMOS clock input to DDS. This

CLK OUT 93 CMOS Inverted clock output. Inverted DDS clock output. This pin may

PXCK 45 CMOS 2x Pixel clock output. 2x oversampled line-locked clock output.

REV. 1.0.4 6/19/01 5

65, 61, 58 1.23Vp-p Composite Video Input. Video inputs,1.235 Volts peak-to-peak,

sync tip to peak color

pin may also be used along with CLK OUT for directly connecting

crystals.

also be used along with CLK IN for directly connecting a crystal.

TMC2072 PRODUCT SPECIFICATION

Pin Definitions (continued)

Pin Name Pin Number Pin Type Function

LDV 40 CMOS Pixel clock output. Delayed pixel clock output. LDV runs at 1/2 the

rate of PXCK and its rising edge is useful for transferring CVBS

digital video from the TMC2072 to the TMC22x9x Digital Video

Encoders.

EXT PXCK 94 CMOS External PXCK input. Input for external PXCK clock source.

PXCK SEL 86 CMOS PXCK source select. Select input for internal or external PXCK.

When HIGH, the internally generated line-locked PXCK is selected.

When LOW, the external PXCK source is enabled.

Digital Video

GHSYNC

GVSYNC 33 CMOS Vertical sync output. When the TMC2072 is locked to incoming

CVBS

7-0

FID[0] 35 CMOS Odd/even (“top/bottom”) field flag. LOW denotes the first field of a

FID[1] 36 CMOS Bruch blanking flag. In PAL, LOW denotes a frame with burst

32 CMOS Horizontal sync output. When the TMC2072 is locked to incoming

video, the GHSYNC pin provides a negative-going pulse after the

falling edge of each horizontal sync pulse. When the device is

locked to a stable video signal, there is a fixed number of PXCK

clock cycles between adjacent falling edges of GHSYNC. If no video

signal is present and LEADLAG is less than 4A(hex), the TMC2072

will output normal, evenly-spaced horizontal pulses. If no video

signal is present and LEADLAG exceeds 88(hex), the TMC2072 will

omit every eighth Hsync pulse. As LEADLAG is increased from 49h

to 89h, seven out of every eight Hsyncs will be unaffected, but the

eighth will shrink by one clock cycle per LSB step, until it disappears

entirely at 89h.

video, the GVSYNC pin provides a negative-going edge after the

start of the first vertical sync pulse of a vertical blanking interval. If

no video signal is present on the selected input pin, GVSYNC will

remain continuously at logic high, until a signal is selected and lock

is reestablished. A system designer requiring a free-running vertical

sync may wish to provide this with an external pixel counter.

30-28, 25-21 CMOS Composite output bus. 8-bit composite video data are output on

this bus at 1/2 the PXCK rate. During horizontal sync, field ID,

subcarrier frequency, and subcarrier phase are available on this

bus.

video frame; HIGH, the second.

blanked on line 310, whereas HIGH denotes burst detected on line

310. FID[1] is valid only in PAL and only when FID[0] is high and

should be interpreted as follows:

FID[1:0] PAL Field Number

01 II or VI

11 IV or VIII

µP l/O

SA[2:0] 3-1 R-bus chip address, 3 LSBs. Full 7-bit address = {1, 0, 0, 0, SA[2],

SA[1], SA[0]}

SDA 4 R-bus R-bus bidirectional data line.

SCL 5 R-bus R-bus clock line (input/slave only)

6 REV. 1.0.4 6/19/01

PRODUCT SPECIFICATION TMC2072

Pin Definitions (continued)

Pin Name Pin Number Pin Type Function

RESET

INT

VALID 34 TTL HSYNC locked flag. Hsync locked flag. When high, this output

BURL 31 TTL/

Analog Interface

V

REF

COMP 88 0.1 µF Compensation capacitor. Compensation for DDS D/A converter

RB, RT 57, 68 0.1 µF A/D V

PLL Filter

DDS OUT 82 Internal DDS output. Analog output from the internal Direct Digital

PFD IN 77 Horizontal PLL input. Analog input to the Phase/Frequency

C

BYP

Power Supply

V

DDA

V

DD

Ground

A

GND

D

GND

6, 18, 26, 42, 44,

69, 72, 74, 81, 89

8, 16, 27, 38, 39,

7 TTL Master reset input. Bringing RESET LOW forces the internal state

machines to their starting states, loads the Control Register with

default values, and disables outputs. Bringing RESET

the TMC2072 in its default mode.

17 TTL Interrupt output. This output is LOW if the internal horizontal phase

lock loop is unlocked with respect to incoming video for 128 or more

lines per field. After lock is established, INT

indicates that the most recent incoming horizontal sync has been

detected within ±16 pixels of its expected position. It goes low if no

sync is encountered during this ±16-pixel window, as during a

typical VCR headswitch line. Once the chip has locked to a clean

video source, this flag should remain high continuously. If the chip

has locked to a VCR, this flag will typically go low for one (or

sometimes two) lines at the bottom of each field.

Burst lock flag. When high, this output indicates that the chip’s

CMOS

70 +1.23 V V

75 1 µF Comparator bypass. Decoupling point for the internal comparator

49, 51, 52, 60,

64, 73, 87

48, 92, 98, 100

50, 55, 63, 67,

41, 46, 47, 90,

95-97

+5 V Analog power supply. Positive power supply to analog section.

+5 V Digital power supply. Positive power supply to digital section.

0.0 V Analog ground. Ground for analog section. All pins must be

0.0 V Digital ground. Ground for digital section. All pins must be

internal subcarrier synthesizer is phase-aligned with the current

line’s incoming chroma burst. The flag goes low when the internal

and external phases diverge.

input/output. +1.23 Volt reference. When the internal voltage

REF

reference is used, this pin should be decoupled to A

µF capacitor. An external +1.2 Volt reference may be connected

here, overriding the internal reference source.

circuitry. This pin should be decoupled to V

capacitor.

decoupling. Decoupling points for A/D converter voltage

REF

references. These pins should be decoupled to A

capacitor.

Synthesizer D/A converter, at 1/9 the PXCK frequency.

Detector of the horizontal phase-locked loop.

reference of the Phase/Frequency Detector. This pin should be

decoupled to A

All pins must be connected.

All pins must be connected.

connected.

connected.

with a 0.1 µF capacitor.

GND

goes HIGH.

DDA

HIGH restarts

GND

with a 0.1 µF

GND

with a 0.1

with a 0.1 µF

REV. 1.0.4 6/19/01 7

Loading...

Loading...