Fairchild Semiconductor NDH8504P Datasheet

February 1997

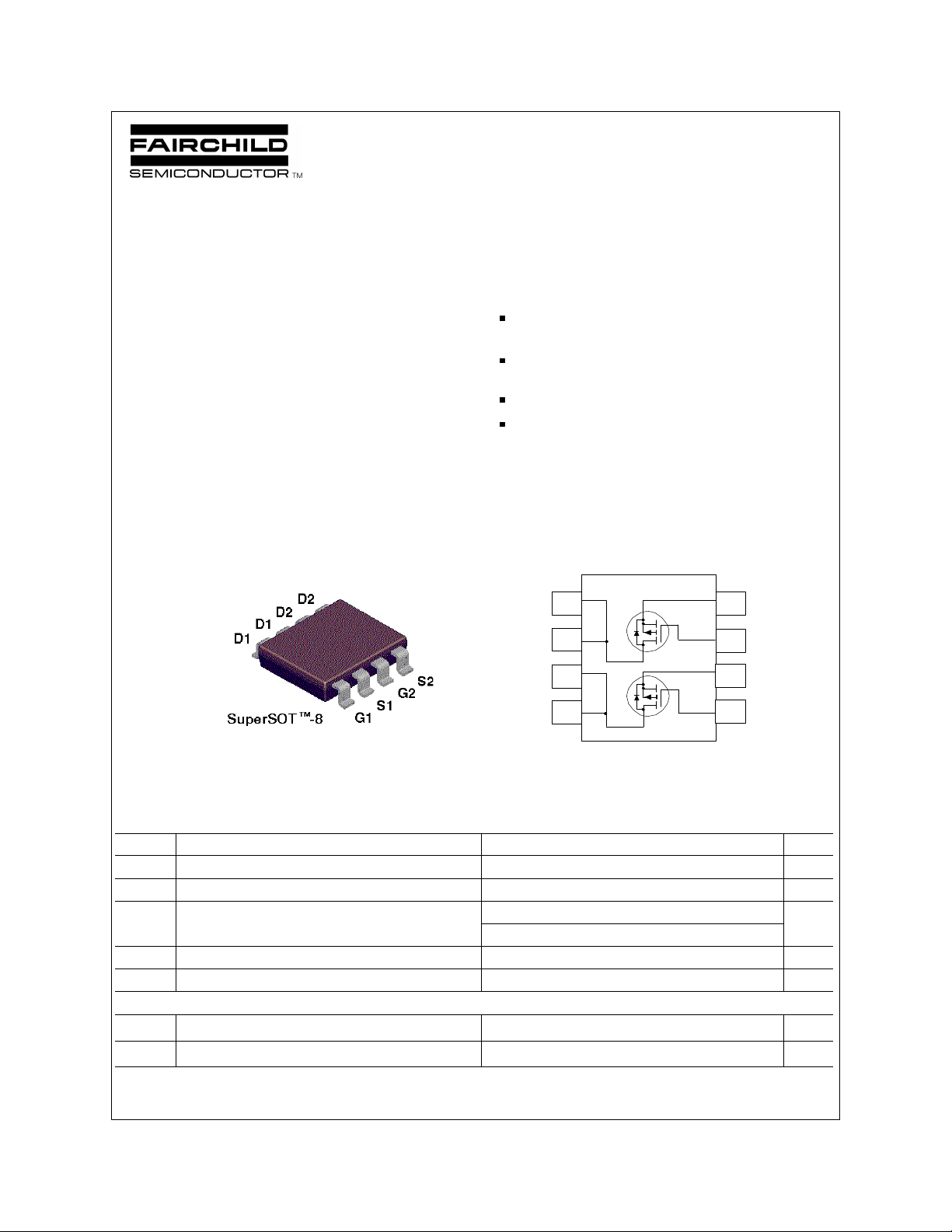

NDH8504P

Dual P-Channel Enhancement Mode Field Effect Transistor

General Description Features

SuperSOTTM-8 P-Channel enhancement mode power field

effect transistors are produced using Fairchild's proprietary,

high cell density, DMOS technology. This very high density

process is especially tailored to minimize on-state resistance.

These devices are particularly suited for low voltage

applications such as notebook computer power management

and other battery powered circuits where fast high-side

switching, and low in-line power loss are needed in a very small

outline surface mount package.

___________________________________________________________________________________________

-2.7 A, -30 V. R

R

= 0.07Ω @ VGS = -10 V

DS(ON)

= 0.115 Ω @ VGS = -4.5 V.

DS(ON)

Proprietary SuperSOTTM-8 package design using copper

lead frame for superior thermal and electrical capabilities.

High density cell design for extremely low R

DS(ON)

.

Exceptional on-resistance and maximum DC current

capability.

5

6

7

8

Absolute Maximum Ratings T

= 25°C unless otherwise noted

A

Symbol Parameter

V

DSS

V

GSS

I

D

Drain-Source Voltage -30 V

Gate-Source Voltage ±20 V

Drain Current - Continuous (Note 1) -2.7 A

- Pulsed -8

P

T

D

J,TSTG

Maximum Power Dissipation (Note 1) 0.8 W

Operating and Storage Temperature Range -55 to 150 °C

THERMAL CHARACTERISTICS

R

JA

θ

R

JC

θ

Thermal Resistance, Junction-to-Ambient (Note 1) 156 °C/W

Thermal Resistance, Junction-to-Case (Note 1) 40 °C/W

4

3

2

1

NDH8504P

Units

© 1997 Fairchild Semiconductor Corporation

NDH8504P Rev.C

ELECTRICAL CHARACTERISTICS (T

= 25°C unless otherwise noted)

A

Symbol Parameter Conditions Min Typ Max Units

OFF CHARACTERISTICS

BV

I

DSS

I

GSSF

I

GSSR

DSS

Drain-Source Breakdown Voltage VGS = 0 V, ID = -250 µA -30 V

Zero Gate Voltage Drain Current

VDS = -24V, V

GS

= 0 V

TJ= 55°C

-1 µA

-10 µA

Gate - Body Leakage, Forward VGS = 20 V, VDS = 0 V 100 nA

Gate - Body Leakage, Reverse

VGS = -20 V, VDS= 0 V

-100 nA

ON CHARACTERISTICS (Note 2)

V

R

I

g

GS(th)

DS(ON)

D(on)

FS

Gate Threshold Voltage VDS = VGS, ID = - 250 µA -1 -1.6 -3 V

TJ= 125°C

-0.8 -1.2 -2.4

Static Drain-Source On-Resistance VGS = -10 V, ID = -2.7 A 0.062 0.07

0.088 0.125

0.102 0.115

-8 A

-3

5.5 S

On-State Drain Current

Forward Transconductance

TJ= 125°C

VGS = -4.5 V, ID = -2.1 A

VGS = -10 V, VDS = -5 V

VGS = -4.5 V, VDS = -5 V

VDS = -10 V, ID = -2.7 A

Ω

DYNAMIC CHARACTERISTICS

C

iss

C

oss

C

rss

Input Capacitance VDS = -15 V, V

Output Capacitance 340 pF

f = 1.0 MHz

GS

= 0 V,

560 pF

Reverse Transfer Capacitance 130 pF

SWITCHING CHARACTERISTICS (Note 2)

t

t

t

t

Q

Q

Q

D(on)

r

D(off)

f

Turn - On Delay Time

Turn - On Rise Time 16 30 ns

VDD = -10 V, ID = -1 A,

VGS = -10 V, R

GEN

= 6 Ω

Turn - Off Delay Time 35 70 ns

Turn - Off Fall Time 40 80 ns

g

gs

gd

Total Gate Charge

Gate-Source Charge 3.8 nC

Gate-Drain Charge 4.7 nC

VDS = -10 V,

ID = -2.7 A, VGS = -10 V

13 25 ns

19 27 nC

NDH8504P Rev.C

ELECTRICAL CHARACTERISTICS (T

= 25°C unless otherwise noted)

A

Symbol Parameter Conditions Min Typ Max Units

DRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS

I

S

V

SD

Notes:

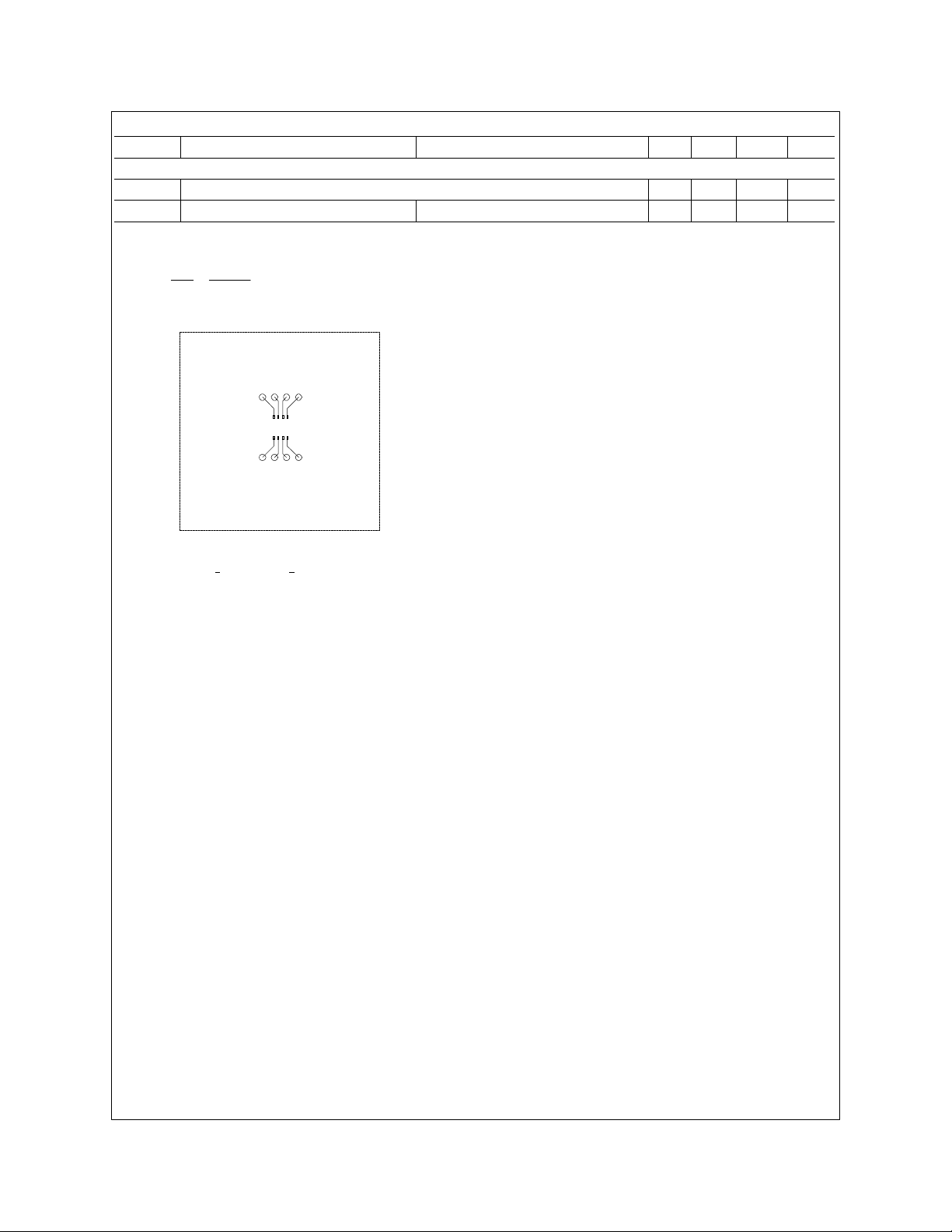

1. R

design while R

P

Typical R

Scale 1 : 1 on letter size paper

2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%.

Maximum Continuous Drain-Source Diode Forward Current -0.67 A

Drain-Source Diode Forward Voltage

is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins. R

JA

θ

D

(t) =

is determined by the user's board design.

CA

θ

T

R

JA

θ

156oC/W when mounted on a 0.0025 in2 pad of 2oz copper.

T

J−TA

θJ A

using the board layouts shown below on 4.5"x5" FR-4 PCB in a still air environment:

J−TA

=

R

(t)

θJ C+RθCA

2

= I

(t) × R

DS(ON)@T

D

(t)

J

VGS = 0 V, IS = -0.67 A (Note 2)

-0.74 -1.2 V

is guaranteed by

JC

θ

NDH8504P Rev.C

Loading...

Loading...