Fairchild Semiconductor HUF76413D3S, HUF76413D3 Datasheet

Data Sheet December 2001

20A, 60V, 0.056 Ohm, N-Channel, Logic

Level UltraFET® Power MOSFET

Packaging

JEDEC TO-251AA JEDEC TO-252AA

DRAIN

(FLANGE)

HUF76413D3

SOURCE

DRAIN

GATE

GATE

SOURCE

HUF76413D3S

DRAIN

(FLANGE)

Symbol

HUF76413D3, HUF76413D3S

Features

• Ultra Low On-Resistance

-r

-r

• Simulation Models

- Temperature Compensated PSPICE® and SABER™

Electrical Models

- Spice and SABER Thermal Impedance Models

- www.fairchildsemi.com

• Peak Cu rrent vs Pulse Width Curve

• UIS Rating Curve

• Switching Time vs R

DS(ON)

DS(ON)

= 0.049Ω, V

= 0.056Ω, V

GS

= 10V

GS

= 5V

GS

Curves

D

G

S

Absolute Maximum Ratings

Drain to Source Voltage (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .V

Drain to Gate Voltage (R

Gate to Source Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .V

Drain Current

Continuous (T

Continuous (TC = 25oC, VGS = 10V) (Figure 2) . . . . . . . . . . . . . . . . . . . . . . . I

Continuous (TC = 100oC, VGS = 5V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

Continuous (TC = 100oC, VGS = 4.5V) (Figure 2) . . . . . . . . . . . . . . . . . . . . . I

Pulsed Drain Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

Pulsed Avalanche Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UIS Figures 6, 17, 18

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . P

Derate Above 25oC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating and Storage Temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s . . . . . . . . . . . . . . . . . . . . . . . . . T

Package Body for 10s, See Techbrief TB334 . . . . . . . . . . . . . . . . . . . . . . . T

NOTES:

= 25oC to 150oC.

1. T

J

CAUTION: Stresses above those listed in “Absolute Maximum Rati ngs” may cause per man ent dama ge to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

= 25oC, VGS = 5V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

C

= 20kΩ) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . V

GS

TC = 25oC, Unless Otherwise Specified

Ordering Information

PART NUMBER PACKAGE BRAND

HUF76413D3 TO-251AA 76413D

HUF76413D3S TO-252AA 76413D

NOTE: When ordering, use the entire part number. Add the suffix T

to obtain the variant in tape and reel, e.g., HUF76413D3ST.

HUF76413D3, HUF76413D3S UNITS

DSS

DGR

GS

D

D

D

D

DM

D

, T

J

STG

L

pkg

60 V

60 V

±16 V

20

20

15

15

Figure 4

60

0.4

-55 to 175

300

260

W/oC

A

A

A

A

W

o

C

o

C

o

C

Product reliability information can be found at http://www.fairchildsemi.com/products/discrete/reliability/index.html

All Fairchild semiconductor products are manufactured, assembled and tested under ISO9000 and QS9000 quality systems certification.

©2001 Fairchild Semiconductor Corpo ration HUF76413D3, HUF76413D3S Rev. B

For severe environments, see our Automotive HUFA series.

HUF76413D3, HUF76413D3S

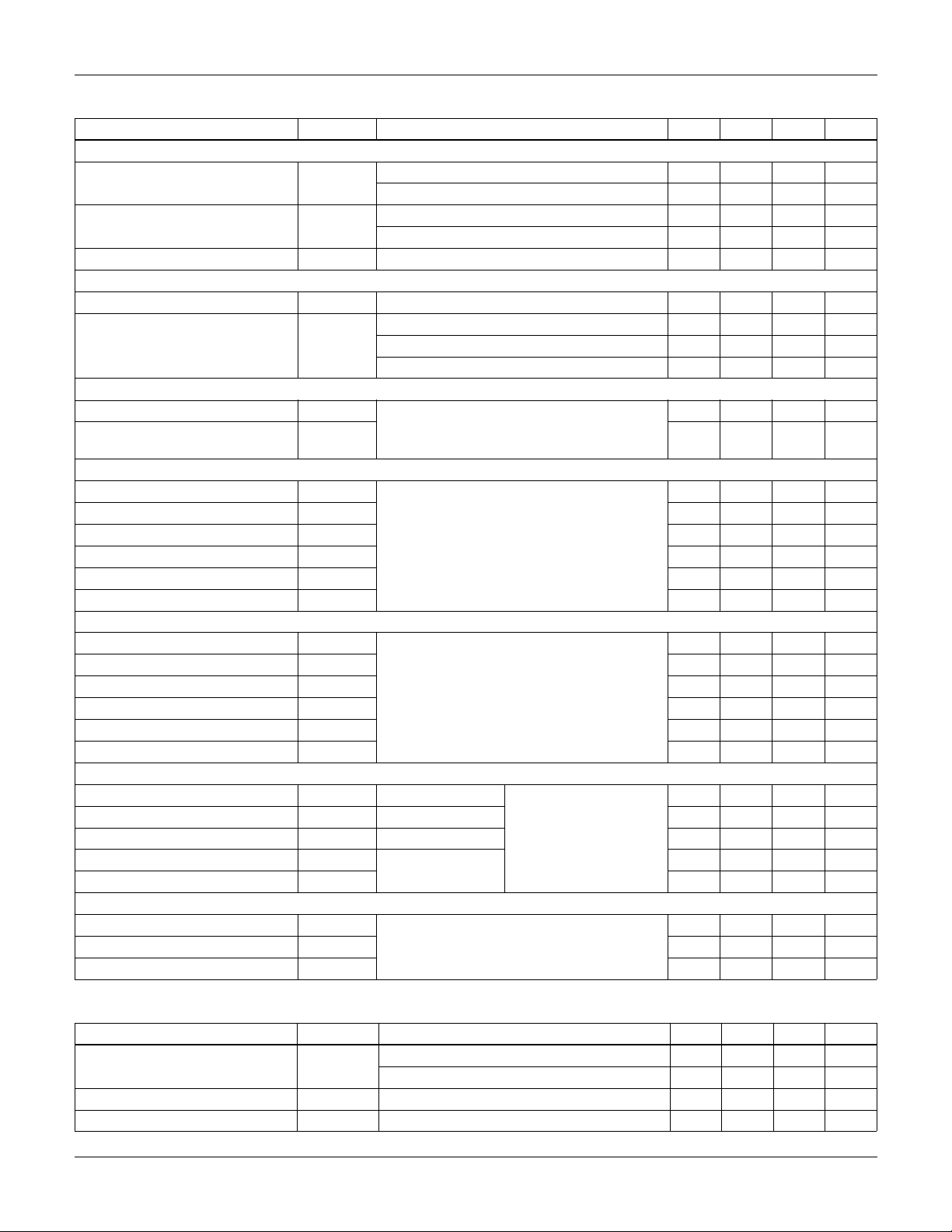

Electrical Specifications

TC = 25oC, Unless Otherwise Specified

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

OFF STATE SPECIFICATIONS

Drain to Source Breakdown Voltage BV

Zero Gate Voltage Drain Current I

Gate to Source Leakage Current I

ON STATE SPECIFICATIONS

Gate to Source Threshold Voltage V

Drain to Source On Resistance r

THERMAL SPECIFICATIONS

Thermal Resistance Junction to Case R

Thermal Resistance Junction to

Ambient

SWITCHING SPECIFICATIONS (V

= 4.5V)

GS

Turn-On Time t

Turn-On Delay Time t

Rise Time t

Turn-Off Delay Time t

Fall Time t

Turn-Off Time t

SWITCHING SPECIFICATIONS (V

GS

= 10V)

Turn-On Time t

Turn-On Delay Time t

Rise Time t

Turn-Off Delay Time t

Fall Time t

Turn-Off Time t

GATE CHARGE SPECIFICATIONS

Total Gate Charge Q

Gate Charge at 5V Q

Threshold Gate Charge Q

Gate to Source Gate Charge Q

Gate to Drain “Miller” Charge Q

CAPACITANCE SPECIFICATIONS

Input Capacitance C

Output Capacitance C

Reverse Transfer Capacitance C

DSSID

I

D

DSS

VDS = 55V, VGS = 0V - - 1 µA

V

GSS

GS(TH)VGS

DS(ON)ID

θJC

R

θJA

ON

d(ON)

d(OFF)

OFF

ON

d(ON)

d(OFF)

OFF

g(TOT)VGS

g(5)

g(TH)

ISS

OSS

RSS

VGS = ±16V - - ±100 nA

I

D

I

D

TO-251 and TO-252 - - 2.5

VDD = 30V, ID = 15A

V

(Figures 15, 21, 22)

r

f

VDD = 30V, ID = 20A

V

R

r

(Figures 16, 21, 22)

f

VGS = 0V to 5V - 9 11 nC

VGS = 0V to 1V - 0.6 0.7 nC

gs

gd

VDS = 25V, VGS = 0V,

f = 1MHz

(Figure 13)

= 250µA, VGS = 0V (Figure 12) 60 - - V

= 250µA, VGS = 0V , TC = -40oC (Figure 12) 55 - - V

= 50V, VGS = 0V, TC = 150oC - - 250 µA

DS

= VDS, ID = 250µA (Figure 11) 1 - 3 V

= 20A, VGS = 10V (Figures 9, 10) - 0.041 0.049 Ω

= 15A, VGS = 5V (Figure 9) - 0.048 0.056 Ω

= 15A, VGS = 4.5V (Figure 9) - 0.051 0.061 Ω

o

- - 100

o

- - 273 ns

= 4.5V, RGS = 16Ω

GS

-10-ns

- 172 - ns

-21-ns

-55-ns

- - 114 ns

- - 63 ns

= 10V,

GS

GS

= 18Ω

-6-ns

-36-ns

-48-ns

-42-ns

- - 135 ns

= 0V to 10V VDD = 30V,

I

= 15A,

D

= 1.0mA

I

g(REF)

-1720nC

(Figures 14, 19, 20)

-2-nC

-5-nC

- 645 - pF

- 190 - pF

-40-pF

C/W

C/W

Source to Drain Diode Specifications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Source to Drain Diode Voltage V

Reverse Recovery Time t

Reverse Recovered Charge Q

©2001 Fairchild Semiconductor Corpo ration HUF76413D3, HUF76413D3S Rev. B

SD

rr

RR

ISD = 15A - - 1.25 V

= 8A - - 1.0 V

I

SD

ISD = 15A, dISD/dt = 100A/µs--72ns

ISD = 15A, dISD/dt = 100A/µs - - 185 nC

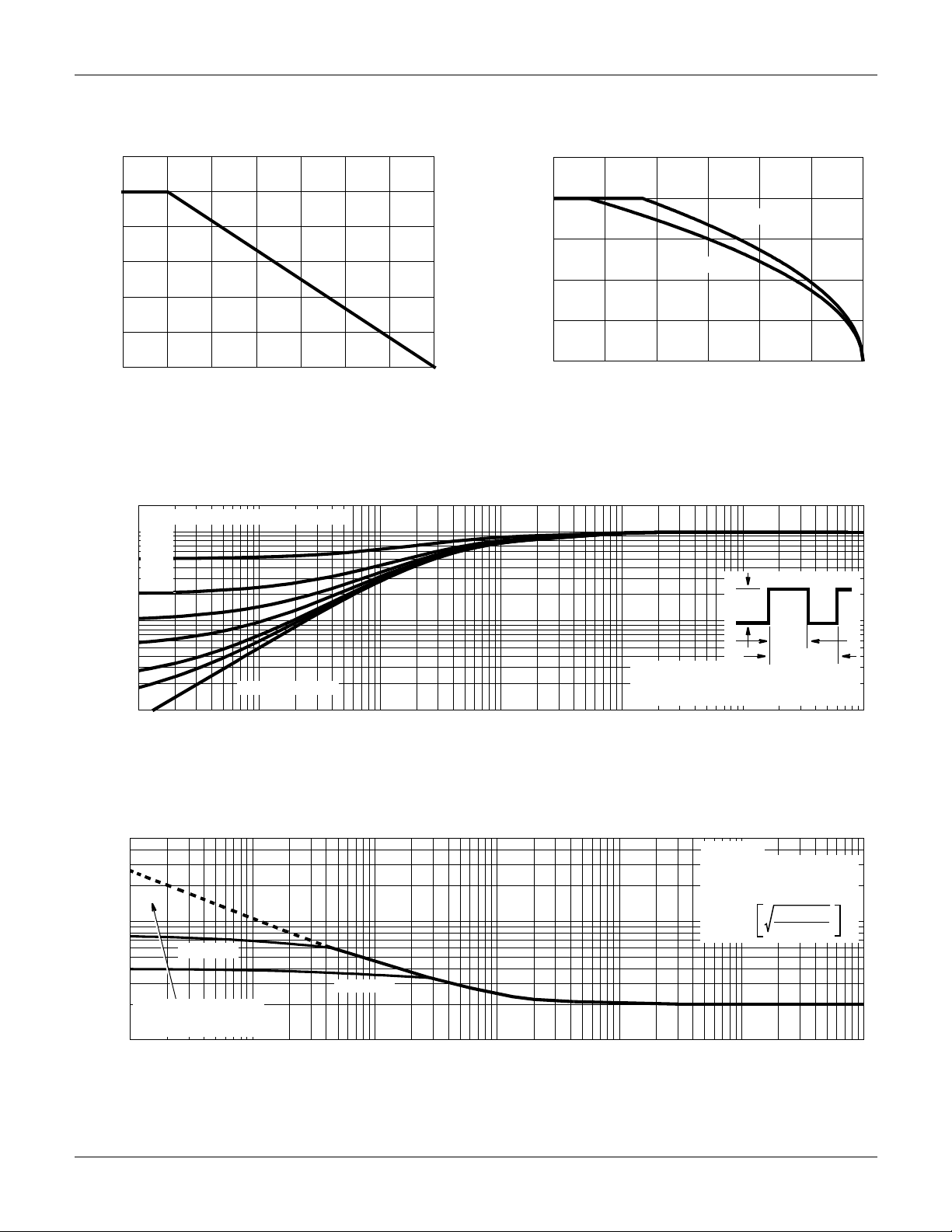

Typical Performance Curves

5

5

HUF76413D3, HUF76413D3S

1.2

1.0

0.8

0.6

0.4

0.2

POWER DISSIPATION MULTIPLIER

0

0 25 50 75 100 17

125

150

TC, CASE TEMPERA TURE (oC)

FIGURE 1. NORMALIZED POWER DISSIP ATION vs CASE

TEMPERATURE

2

DUTY CYCLE - DESCENDING ORDER

0.5

1

0.2

0.1

0.05

0.02

0.01

0.1

, NORMALIZED

θJC

Z

THERMAL IMPEDANCE

SINGLE PULSE

0.01

-5

10

-4

10

-3

10

t, RECTANGULAR PULSE DURATION (s)

25

20

V

= 10V

GS

15

V

= 4.5V

10

, DRAIN CURRENT (A)

D

I

5

GS

0

25 50 75 100 125 150 17

TC, CASE TEMPERATURE (oC)

FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

CASE TEMPERATURE

P

DM

t

NOTES:

DUTY FACTOR: D = t

PEAK TJ = PDM x Z

-2

10

-1

10

θJC

10

1/t2

x R

0

θJC

+ T

1

t

2

C

1

10

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

500

100

, PEAK CURRENT (A)

DM

I

TRANSCONDUCTANCE

MAY LIMIT CURRENT

IN THIS REGION

10

-5

10

VGS = 10V

VGS = 5V

-4

10

-3

10

-2

10

-1

10

t, PULSE WIDTH (s)

TC = 25oC

FOR TEMPERATURES

ABOVE 25

o

C DERATE PEAK

CURRENT AS FOLLOWS:

175 - T

I = I

25

10

0

C

150

10

FIGURE 4. PEAK CURRENT CAPABILITY

©2001 Fairchild Semiconductor Corpo ration HUF76413D3, HUF76413D3S Rev. B

1

Loading...

Loading...