Fairchild Semiconductor FSTD32450 Datasheet

FSTD32450

Configurable 4-Bit to 40-Bit Bus Switch with

Selectable Level Shifting (Preliminary)

Preliminary

FSTD32450 Configurable 4-Bit to 40-Bit Bus Switch with Selectable Level Shifting (Preliminary)

February 2001

Revised August 2001

General Description

The Fairchild Univers al Bus Switch FSTD32450 provides

4-bit, 5-bit, 8-bit, 10 -bit, 16 -bit, 2 0-bit...4 0-bit o f high- speed

CMOS TTL-compatible bus switching. The low On Re sistance of the switch allows inputs to be connect ed to outputs without adding propagation delay or generating

additional ground bounce noise.

The FSTD32450 is designed to allow “customer” configuration control of the en able connections. Th e device can be

organized as eithe r a ten 4-bit, eight 5-bit , four 10-bit, two

20-bit or one 40-bit enable d bus switch. Also achievable

are 8-bit and 16-bit enab led co nfigura tion s (see Fu nctional

Description). The device’s bit configuration is controlled

through select pin logic. (s ee Truth Table). When OE

LOW, Port A

the switch is OPEN.

Another key device feature is the addition of a level shifting

select pin, “S

device behaves as a st andard N-MOS switch. When S

and S5 are HIGH, a diode to VCC is integrated into the circuit allowing for level sh ifting between 5V inputs and 3.3V

outputs.

is connected to Port Bx. When OEx is HIGH,

x

and S5”. When S2 and S5 are LOW, the

2

Features

■ Voltage level shifting

■ 4

Ω switch connection between two ports

■ Minimal propagation delay through the switch

■ Low l

CC

■ Zero bounce in flow-through mode

■ Control inputs compatible with TTL level

■ Packaged in plastic Fine-Pitch Ball Grid Array

(FBGA) (Preliminary)

Applications Note

Select pins S0, S1, S2, S3, S4 and S5 are intended to be

is

x

used as static user confi gurable control pins. The AC p erformance of these pins has not been characterized or

tested. Switching of these select pins during system operation may temporarily disrupt output logic states and/or

enable pin controls.

2

40-bit configuration can be achieved by connecting the

OE

and the OE6 pins to together.

1

Ordering Code:

Order Number Package Number Package Description

FSTD32450GX

(Note 1)

Note 1: BGA package available in Tape and Reel only.

BGA114A

(Preliminary)

114-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide

[Tape and Reel]

UHC is a trademark of Fairchild Semiconductor Corporation.

© 2001 Fairchild Semiconductor Corporation DS500563 www.fairchildsemi.com

Preliminary

Connection Diagram

Pin Assignment for FBGA

FSTD32450

(Top Thru View)

Pin Descriptions

Pin Name Description

OE

, OE2, OE3, OE4, Bus Switch

1

, OE6, OE7, OE8Enables

OE

5

OE

, OE

9

10

1A, 2A, 3A, 4A Bus A

1B, 2B, 3B, 4B Bus B

, S1, S3, S

S

0

S

, S

2

4

5

Bit Configuration Enables

Level Shifting Diode Enables

FBGA Pin Assignments

123456

A 1A

B 1A61A51A11B11B51B

C 1A81A71A31B31B71B

D 1A101A9GND OE51B91B

E 2A22A1S0V

F 2A42A3S

G 2A62A5VCCGND 2B52B

H 2A82A7GND GND 2B72B

J 2A102A9GND GND 2B92B

K OE4OE8GND GND OE9OE

L 3A103A9GND GND 3B93B

M 3A83A7GND GND 3B73B

N 3A63A5GND V

P 3A43A3S

R 3A23A1V

T 4A104A9OE10GND 4B94B

U 4A84A74A34B34B74B

V 4A64A54A14B14B54B

W 4A44A2OE7OE64B24B

1A2OE1OE21B21B

4

CC

S22B32B

1

CC

S43B33B

5

S33B13B

CC

2B12B

3B53B

4

6

8

10

2

4

6

8

10

3

10

8

6

4

2

10

8

6

4

www.fairchildsemi.com 2

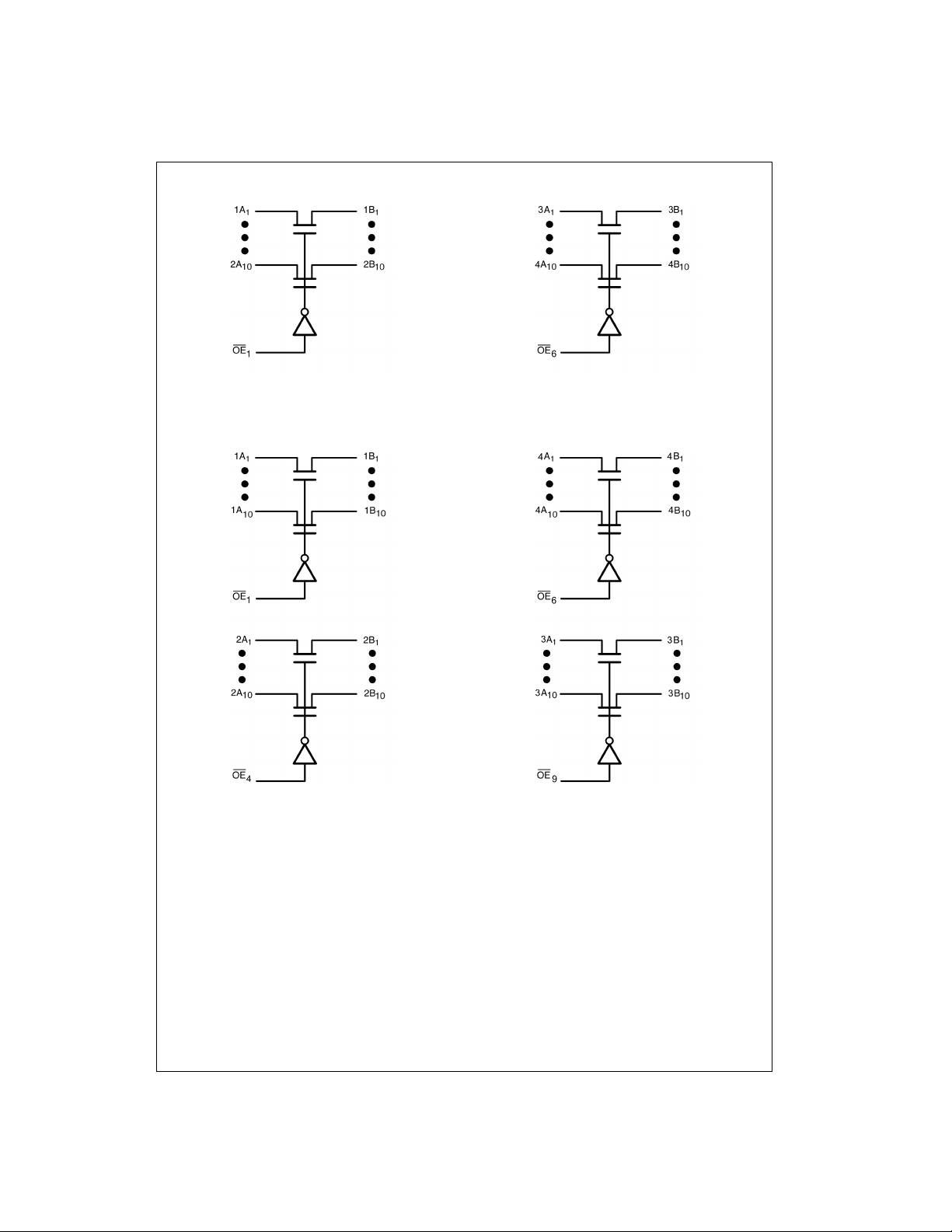

Logic Diagrams

Preliminary

FSTD32450

20-Bit Configuration

10-Bit Configuration

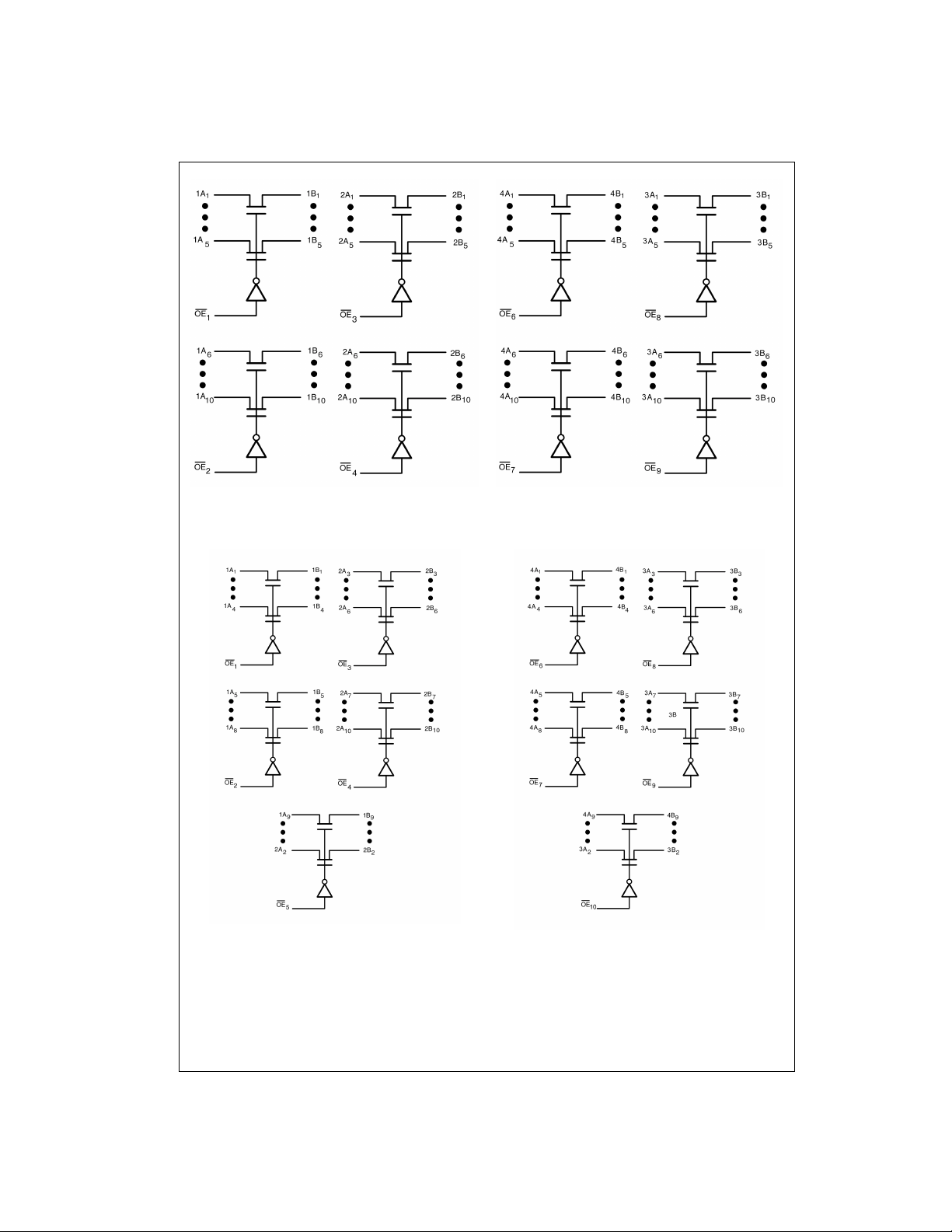

3 www.fairchildsemi.com

FSTD32450

Preliminary

5-Bit Configuration

4-Bit Configuration

www.fairchildsemi.com 4

Loading...

Loading...