Fairchild Semiconductor FMS6502MTC24X, FMS6502 Datasheet

January 2007

FMS6502

8-Input, 6-Output Video Switch Matrix with Output Drivers,

Input Clamp, and Bias Circuitry

FMS6502 8-Input, 6-Output Video Switch Matrix with Output Drivers, Input Clamp, and Bias Circuitry

Features

■ 8 x 6 Crosspoint Switch Matrix

■ Supports SD, PS, and HD 1080i / 1080p Video

■ Input Clamp and Bias Circuitry

■ Doubly Terminated 75Ω Cable Drivers

■ Programmable 0dB or 6dB Gain

■ AC- or DC-Coupled Inputs

■ AC- or DC-Coupled Outputs

■ One-to-One or One-to-Many Input-to-Output

Switching

2CTM

■ I

■ 3.3V or 5V Single Supply Operation

■ Pb-Free TSSOP-24 Package

-Compatible Digital Interface, Standard Mode

Applications

■ Cable and Satellite Set-Top Bo xes

■ TV and HDTV Sets

■ A / V Switchers

■ Personal Video Recorders (PVR)

■ Security and Surveillance

■ Video Distribution

■ Automotive (In-Cabin Entertainment)

Description

The FMS6502 provides eight inputs that can be routed to

any of six outputs. Each input can be routed to one or

more outputs, but only one input may be routed to any

output.

Each input supports an integrated clamp option to set the

output sync tip level of video with sync to ~300mV. Alternatively, the input may be internally biased to center output signals without sync (Chroma, Pb, Pr) at ~1.25V.

All outputs are designed to drive a 150Ω DC-coupled

load. Each output can be programmed to provide either

0dB or 6dB of signal gain.

Input-to-output routing and input bias mode functions are

controlled via an I

2

C-compatible digital interface.

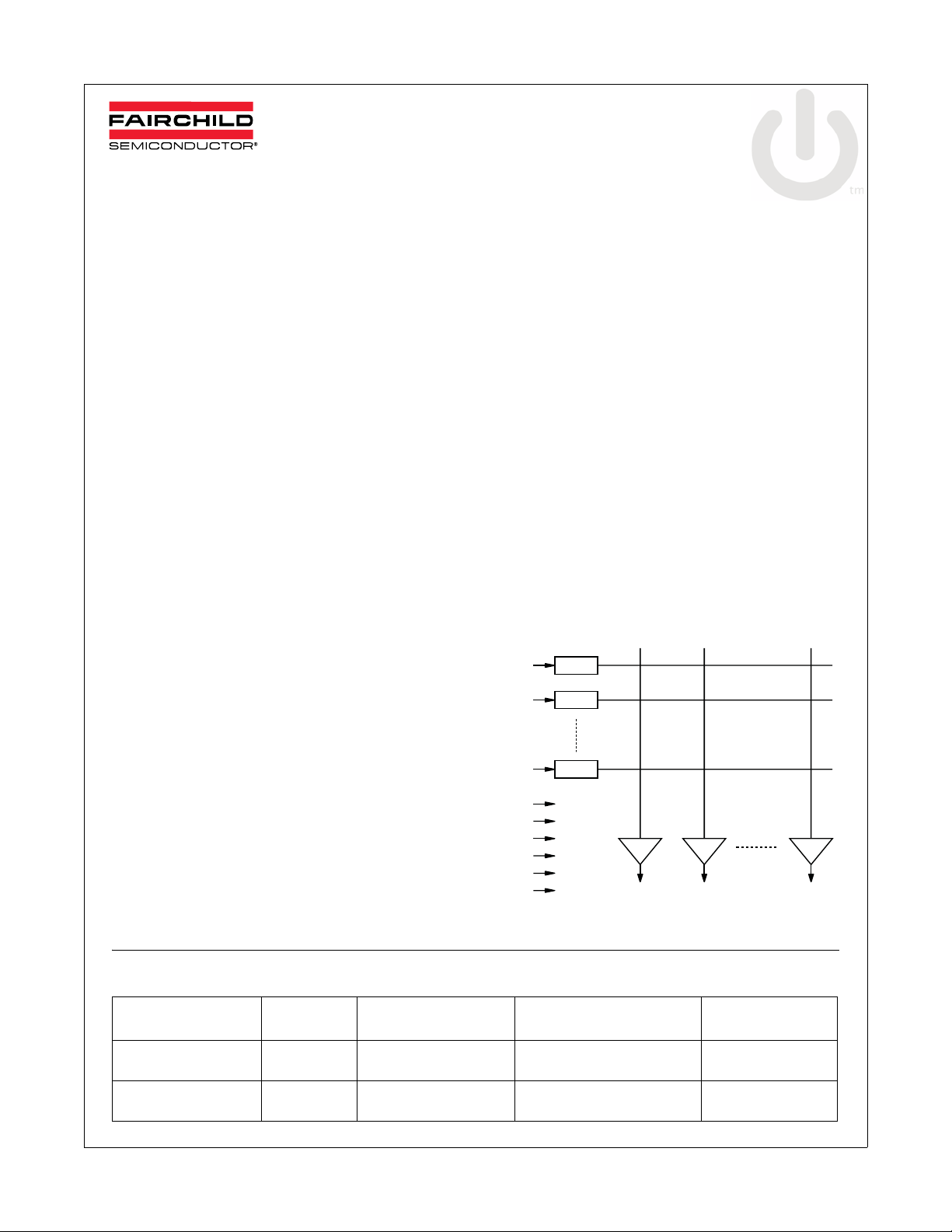

Block Diagram

IN1

IN2

IN8

C / B

C / B

C / B

SDA

SCL

ADDR0

ADDR1

VCC (2)

GND (4)

OUT1 OUT2 OUT6

Figure 1. Block Diagram

Ordering Information

Operating

Part Number Pb-Free

FMS6502MTC24 Yes -40°C to 85°C

FMS6502MTC24X Yes -40°C to 85°C

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.0

Temperature Range Package Packing Method

24-Lead Thin Shrink Small

Ouline Package

24-Lead Thin Shrink Small

Ouline Package

Rail

Reel

FMS6502 8-Input, 6-Output Video Switch Matrix with Output Drivers, Input Clamp, and Bias Circuitry

5

4

2

3

6

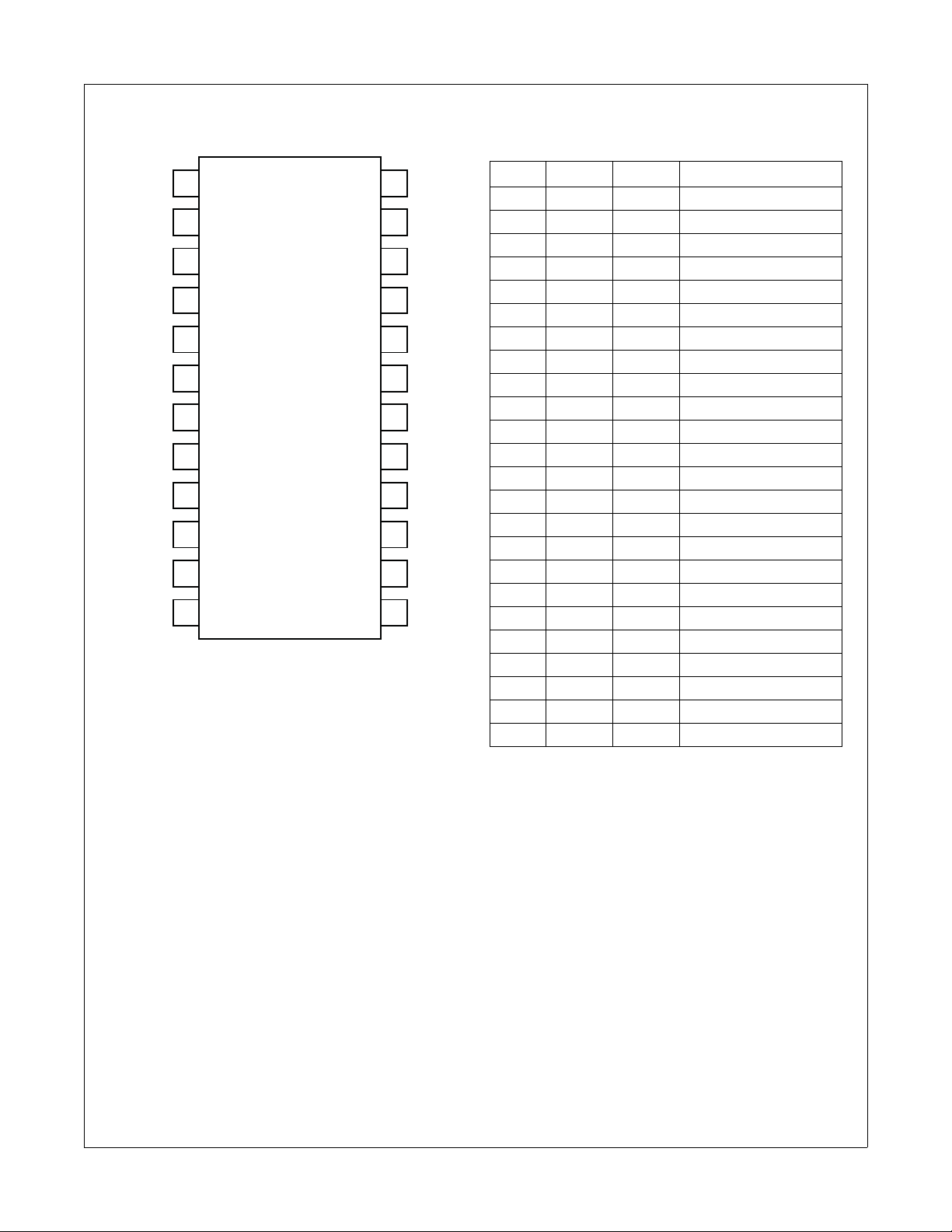

Pin Configuration

1

IN1

IN2

IN3

IN4

IN5

IN6

2

FAIRCHILD

3

FMS6502

4

24L TSSOP

5

6

7

8

9

10

11

12

Figure 2. Pin Configuration

GND

VDD

GND

ADDR1

ADDR0

SCL

Pin Description

GND

24

OUT1

23

22

21

OUT

OUT

VDD

20

OUT

19

18

OUT

17

OUT

16

GND

15

IN8

14

13

SDA

IN7

Pin# Pin Type Description

1 IN1 Input Input, channel 1

2 GND Output Must be tied to ground

3 IN2 Input Input, channel 2

4 VDD Input Positive power supply

5 IN3 Input Input, channel 3

6 GND Output Must be tied to ground

7 IN4 Input Input, channel 4

2

8 ADDR1 Input Selects I

9 IN5 Input Input, channel 5

10 ADDR0 Input Selects I

1 1 IN6 Input Input, channel 6

12 SCL Input Serial clock for I

13 IN7 Input Input, channel 7

14 SDA Input Serial data for I

15 IN8 Input Input, channel 8

16 GND Output Must be tied to ground

17 OUT6 Output Output, channel 6

18 OUT5 Output Output, channel 5

19 OUT4 Output Output, channel 4

20 VDD Input Positive power supply

21 OUT3 Output Output, channel 3

22 OUT2 Output Output, channel 2

23 OUT1 Output Output, channel 1

24 GND Output Must be tied to ground

C address

2

C address

2

2

C port

C port

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FMS6502 Rev. 1.0.0 2

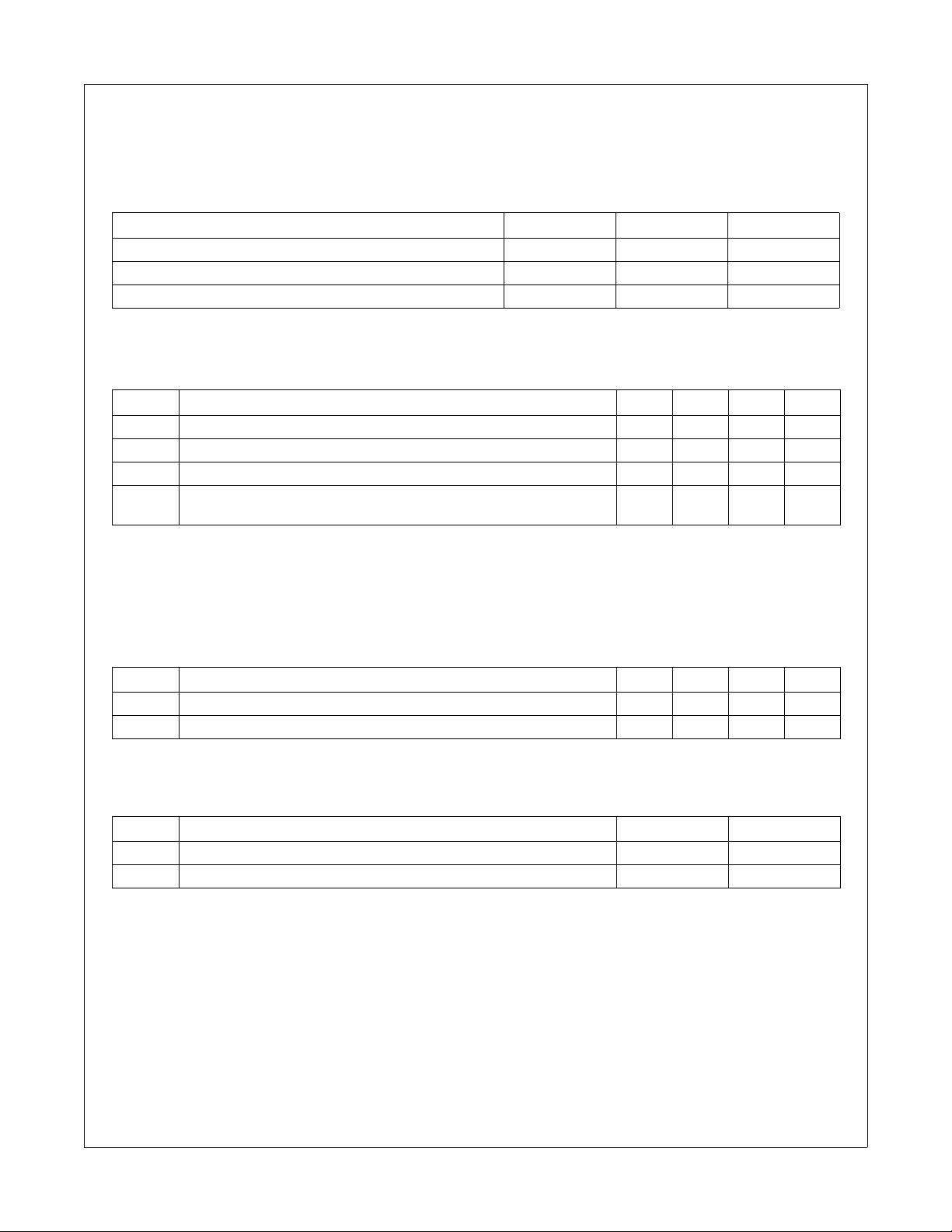

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating cond itions may affect device reliability. The

absolute maximum ratings are stress ratings only.

Parameter Min. Max. Unit

DC Supply Voltage -0.3 6 V

Analog and Digital I/O -0.3 V

Output Current Any One Channel, Do Not Exceed 40 mA

+ 0.3 V

cc

Reliability Information

Symbol Parameter Min. Typ. Max. Unit

T

Junction Temperature 150 °C

J

T

ΘJA

Storage Temperature Range -65 150 °C

STG

Lead Temperature (Soldering, 10s) 300 °C

T

L

Thermal Resistance, JEDEC Standard Multi-Layer Test Boards,

Still Air

84 °C/W

FMS6502 8-Input, 6-Output Video Switch Matrix with Output Drivers, Input Clamp, and Bias Circuitry

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal perfor mance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol Parameter Min. Typ. Max. Unit

T

Operating Temperature Range -40 85 °C

A

V

Supply Voltage Range 3.135 5.0 5.25 V

CC

Electrostatic Discharge Information

Symbol Parameter Value Unit

HBM Human Body Model (JEDEC: JESD22-A114) 10 kV

CDM Charged Device Model (JEDEC: JESD22-A101) 2 kV

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FMS6502 Rev. 1.0.0 3

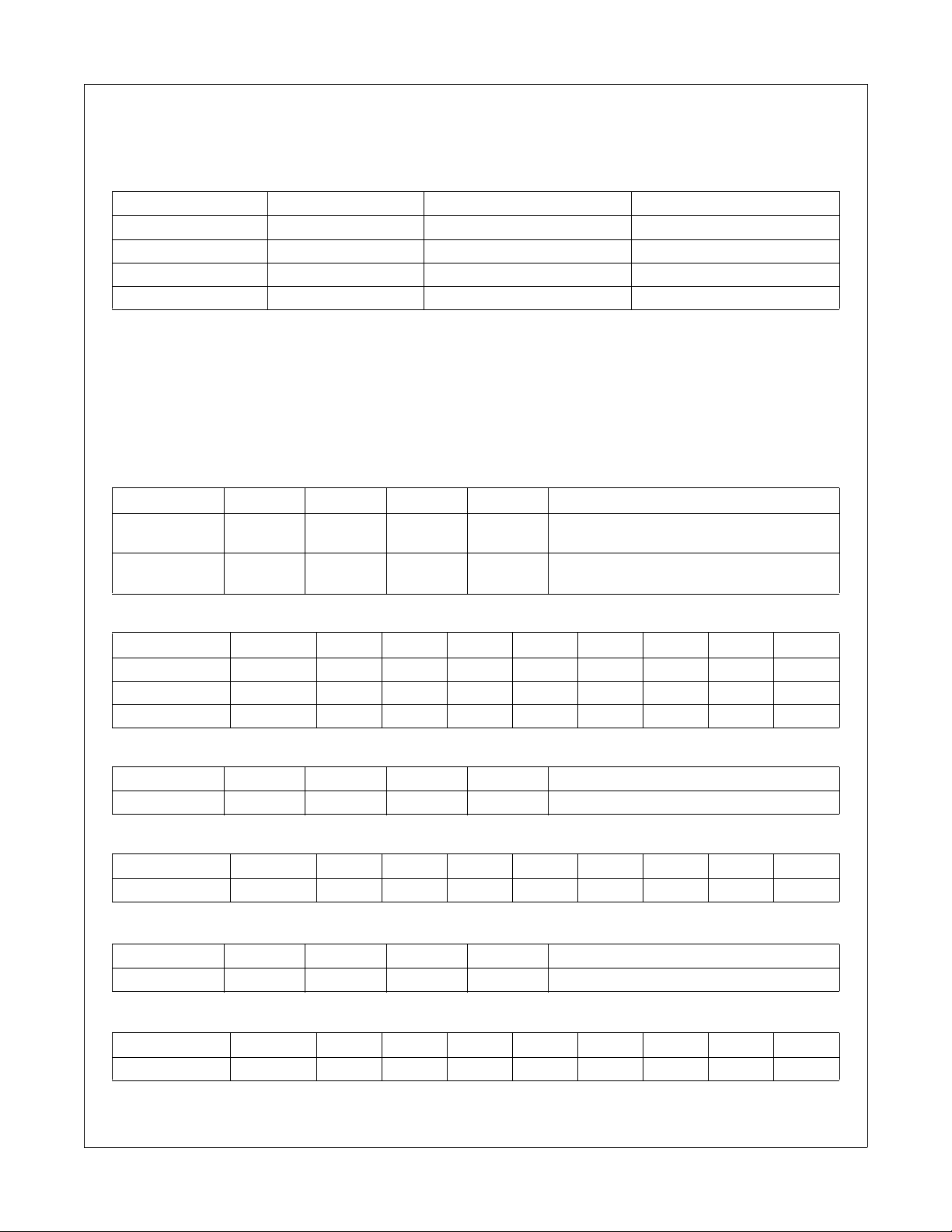

Digital Interface

The I2C-compatibe interface is used to program output

enables, input-to-output routing, and input bias configuration. The I

2

C address of the FMS6502 is 0x06 (0000

ADDR1 ADDR0 Binary Hex

0 0 0000 0110 0x06

0 1 0100 0110 0x46

1 0 1000 0110 0x86

1 1 1100 0110 0xC6

FMS6502 8-Input, 6-Output Video Switch Matrix with Output Drivers, Input Clamp, and Bias Circuitry

0110) with the ability to offset based upon the valu es of

the ADDR0 and ADDR1 inputs. Offset addresses are

defined below:

Data and address data of eight bits each are written to

the FMS6502 I

functions.

For efficiency, a single data register is shared between

two outputs for input selection. More than one output can

select the same input channel for one-to-many routing.

2

C address register to access control

The clamp / bias control bits are written to their own

internal address since they should remain the same

regardless of signal routing. They are set based on the

input signal that is connected to the FMS6502.

All undefined addresses may be written without effect.

Output Control Register Contents and Defaults

Control Name Wid th Type Default Bit(s) Description

In-A 4 bits Write 0 3:0

In-B 4 bits Write 0 7:4

Input selected to drive this output:

0000=OFF

Input selected to drive this output:

0000=OFF

1

, 0001=IN1, 0010=IN2, 1000=IN8

1

, 0001=IN1, 0010=IN2, 1000=IN8

Output Control Register MAP

Name Address Bit 7 Bit 6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

OUT1,2 0x00 B3-Out2 B2-Out2 B1-Out2 B0-Out2 B3-Out1 B2-Out1 B1-Out1 B0-Out1

OUT3,4 0x01 B3-Out4 B2-Out4 B1-Out4 B0-Out4 B3-Out3 B2-Out3 B1-Out3 B0-Out3

OUT5,6 0x02 B3-Out6 B2-Out6 B1-Out6 B0-Out6 B3-Out5 B2-Out5 B1-Out5 B0-Out5

Clamp Control Register Contents and Defaults

Control Name Wid th Type Default Bit(s) Description

Clmp 1 bit Write 0 7:0 Clamp / Bias selection: 1 = Clamp, 0 = Bias

Clamp Control Register Map

Name Address Bit 7 Bit 6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

CLAMP 0x03 Clmp8 Clmp7 Clmp6 Clmp5 Clmp4 Clmp3 Clmp2 Clmp1

Gain Control Register Contents and Defaults

Control Name Wid th Type Default Bit(s) Description

Gain 1 bit Write 0 7:0 Output Gain selection: 0 = 6dB, 1 = 0dB

Gain Control Register Map

Name Address Bit 7 Bit 6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

GAIN 0x04 Unused Unused Gain6 Gain5 Gain4 Gain3 Gain2 Gain1

Note:

1. When the OFF input selection is used, the output amplifier is powered down and enters a high-impedance state.

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FMS6502 Rev. 1.0.0 4

Loading...

Loading...