Fairchild Semiconductor FMS3818 Datasheet

www.fairchildsemi.com

FMS3818

Triple Video D/A Converter

3 x 8 bit, 180 Ms/s

Features

• ±2.5% gain matching

• ±0.5 LSB linearity error

• Internal bandgap voltage reference

• Low glitch energy

• Single 3.3 Volt power supply

Applications

• PC Graphics

• Video signal conversion

– RGB

– YC

C

B

R

– Composite, Y, C

Description

The FMS3818 is a low-cost triple D/A converter, tailored to

fit graphics and video applications where speed is critical.

CMOS-level inputs are converted to analog current outputs

that can drive 25–37.5 Ω loads corresponding to doublyterminated 50–75 Ω loads. A sync current following SYNC

input timing is added to the I

override RGB inputs, setting I

zero when BLANK

applications the internal 1.25V reference voltage can be

overridden by the V

Few external components are required, just the current

reference resistor, current output load resistors, bypass

capacitors and decoupling capacitors.

Package is a 48-lead LQFP. Fabrication technology is

CMOS. Performance is guaranteed from 0 to 70°C.

= L. Although appropriate for many

input.

REF

output. BLANK

OG

, I

OB

and I

OG

will

currents to

OR

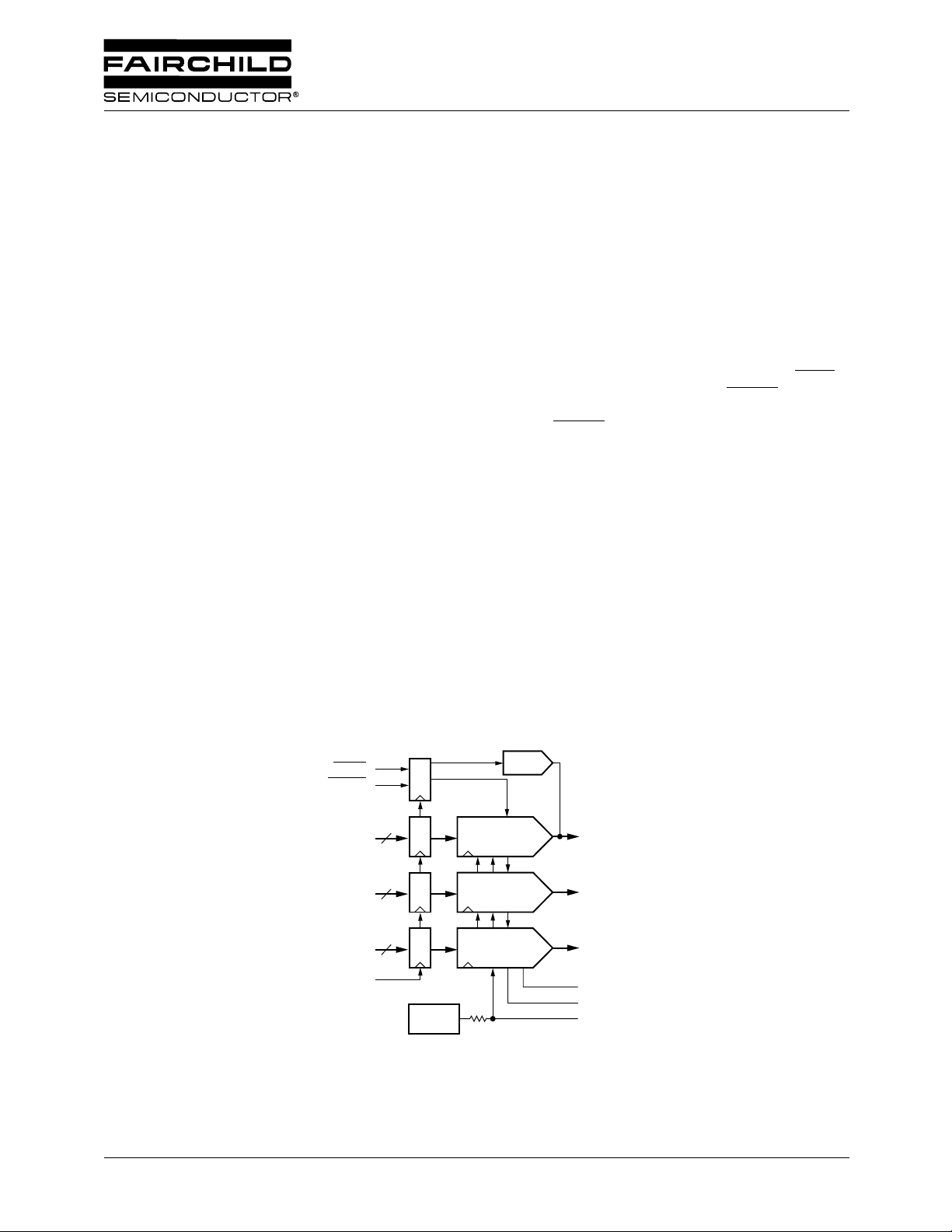

Block Diagram

SYNC

BLANK

G

7-0

B

7-0

R

7-0

CLK

SYNC

8

8

8

+1.25V

Ref

8 bit D/A

Converter

8 bit D/A

Converter

8 bit D/A

Converter

I

OS

IO

G

IO

B

IO

R

COMP

R

REF

V

REF

REV. 1.2.2 11/11/01

FMS3818 PRODUCT SPECIFICATION

Functional Description

Within the FMS3818 are three identical 8-bit D/A

converters, each with a current source output. External loads

are required to convert these currents to voltage outputs.

Data inputs RGB

SYNC = H activates sync current from I

are overridden by the BLANK

7-0

for sync-on-

OS

green video signals.

V

DDA

I

OS

V

SYNC

G

B

R

7-0

7-0

7-0

DDA

V

DDA

V

DDA

input.

BLANK

gates the D/A inputs. If BLANK = H, the D/A

inputs control the output currents to be added to the output

blanking level. If BLANK

= L, data inputs and the pedestal

are disabled.

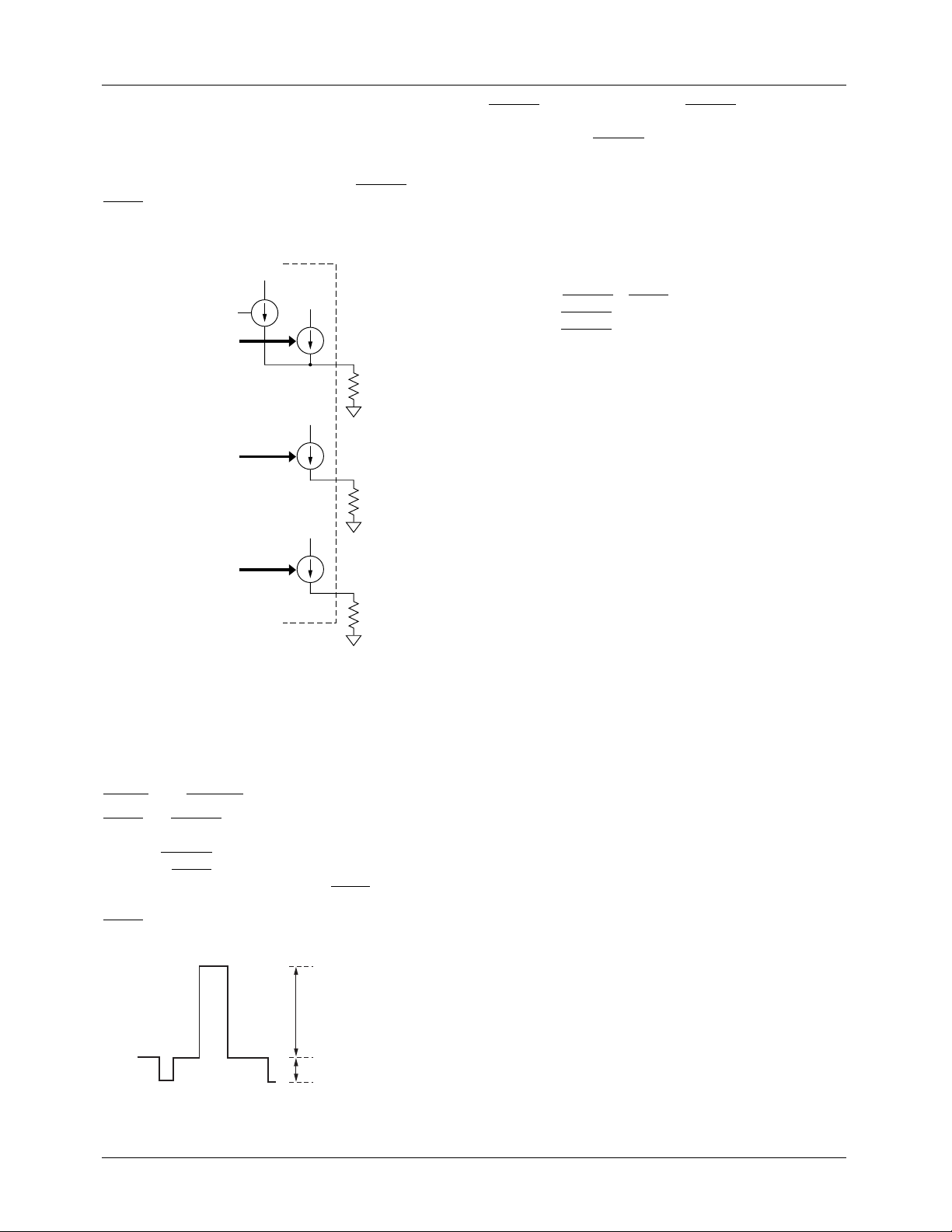

D/A Outputs

Each D/A output is a current source from the V

Expressed in current units, the GBR transformation from

data to current is as

follows:

G = G

B = B

R = R

& BLANK

7-0

& BLANK

7-0

& BLANK

7-0

+ SYNC * 112

Typical LSB current step is 73.2 µA.

To obtain a voltage output, a resistor must be connected to

ground. Output voltage depends upon this external resistor,

the reference voltage, and the value of the gain-setting resistor connected between R

and GND.

REF

To implement a doubly-terminated 75 Ω transmission line, a

shunt 75 Ω resistor should be placed adjacent to the analog

output pin. With a terminated 75 Ω line connected to the

analog output, the load on the FMS3818 current source is

37.5 Ω .

The FMS3818 may also be operated with a single 75 Ohm

terminating resistor. To lower the output voltage swing to the

desired range, the nominal value of the R

REF

be doubled.

supply.

DDA

resistor should

Figure 1. FMS3818 Current Source Structure

Digital Inputs

Incoming GBR data is registered on the rising edge of the

clock input, CLK. Analog outputs follow the rising edge of

CLK after a delay, t

and BLANK

SYNC

and BLANK inputs control the output level (Figure 1

SYNC

and Table 1) of the D/A converters during CRT retrace

intervals. BLANK

level while SYNC

connected to the green D/A converter. SYNC = H adds a

112/256 fraction of full-scale current to the green output.

SYNC = L extinguishes the sync current during the sync tip.

Figure 2. Nominal Output Levels

.

DO

forces the D/A outputs to the blanking

= L turns off a current source, I

data: 700 mV max.

sync: 307 mV

OS

that is

Voltage Reference

Full scale current is a multiple of the current I

external resistor, R

GND. Voltage across R

connected between the R

SET

is the reference voltage, V

SET

which can be derived from either the 1.25 volt internal

bandgap reference or an external voltage reference

connected to V

should be connected between V

I

is mirrored to each of the GBR output current sources.

SET

. To minimize noise, a 0.1µF capacitor

REF

and ground.

REF

To minimize noise, a 0.1µF capacitor should be connected

between the COMP pin and the analog supply voltage V

through an

SET

REF

pin and

,

REF

DDA

Power and Ground

Required power is a single +3.3 Volt supply. To minimize

power supply induced noise, analog +3.3V should be

connected to V

decoupling capacitors placed adjacent to each V

pin pair.

High slew-rate digital data makes capacitive coupling to the

outputs of any D/A converter a potential problem. Since the

digital signals contain high-frequency components of the

CLK signal, as well as the video output signal, the resulting

data feedthrough often looks like harmonic distortion or

reduced signal-to-noise performance. All ground pins should

be connected to a common solid ground plane for best

performance.

DDD

and V

pins with 0.1 and 0.01 µF

DDA

DD

pin or

.

2

REV. 1.2.2 11/11/01

PRODUCT SPECIFICATION FMS3818

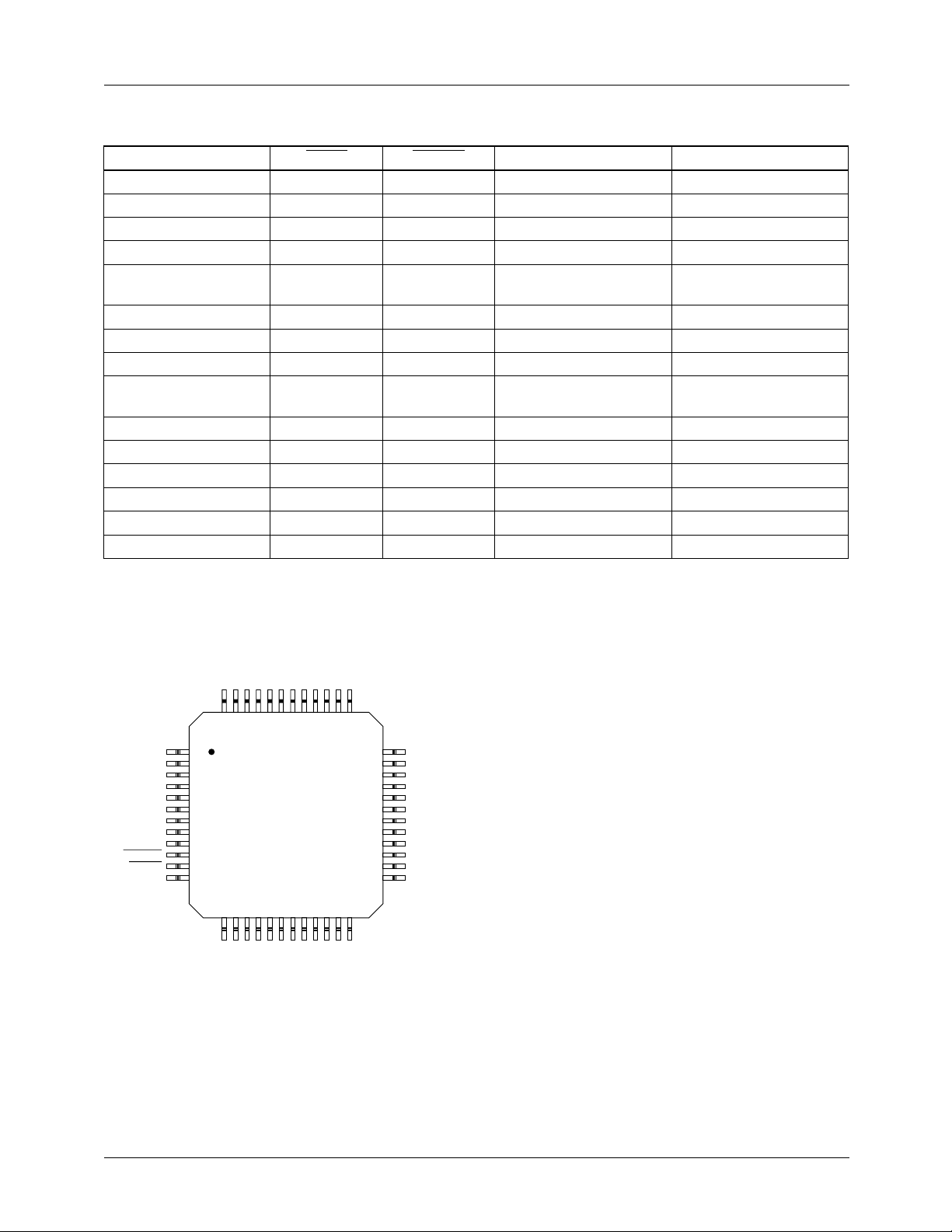

Table 1. Output Voltage Coding

V

= 1.25 V, R

REF

RGB7-0 (MSB…LSB) SYNC BLANK V

1111 1111 1 1 700 1,007

1111 1111 0 1 700 700

1111 1110 1 1 697 1,004

1111 1101 1 1 695 1,001

•

•

1000 0000 1 1 351 658

0111 1111 1 1 349 656

0111 1111 0 1 349 349

•

•

0000 0010 1 1 5 312

0000 0001 1 1 3 310

0000 0000 1 1 0 307

0000 0000 0 1 0 0

XXXX XXXX 1 0 0 307

XXXX XXXX 0 0 0 0

= 348 Ω , R

REF

= 37.5 Ω

L

•

•

•

•

, V

RED

•

•

•

•

(mV) V

BLUE

•

•

•

•

GREEN

•

•

•

•

(mV)

Pin Assignments

LQFP Package

GND

R7R6R5R4R3R2R

484746454443424140

GND

G

G

G

G

G

G

G

G

BLANK

SYNC

V

DDD

1

2

0

3

1

4

2

5

3

6

4

7

5

6

8

7

9

10

11

12

FMS3818

131415161718192021

NC

GND

GND

1

B0B1B2B3B4B6B

R0GND

GND

39

38

22

23

5

7

B

NC

37

24

NC

36

35

34

33

32

31

30

29

28

27

26

25

R

REF

V

REF

COMP

IO

R

IO

G

V

DDA

V

DDA

IO

B

GND

GND

CLK

NC

REV. 1.2.2 11/11/01

3

)

FMS3818 PRODUCT SPECIFICATION

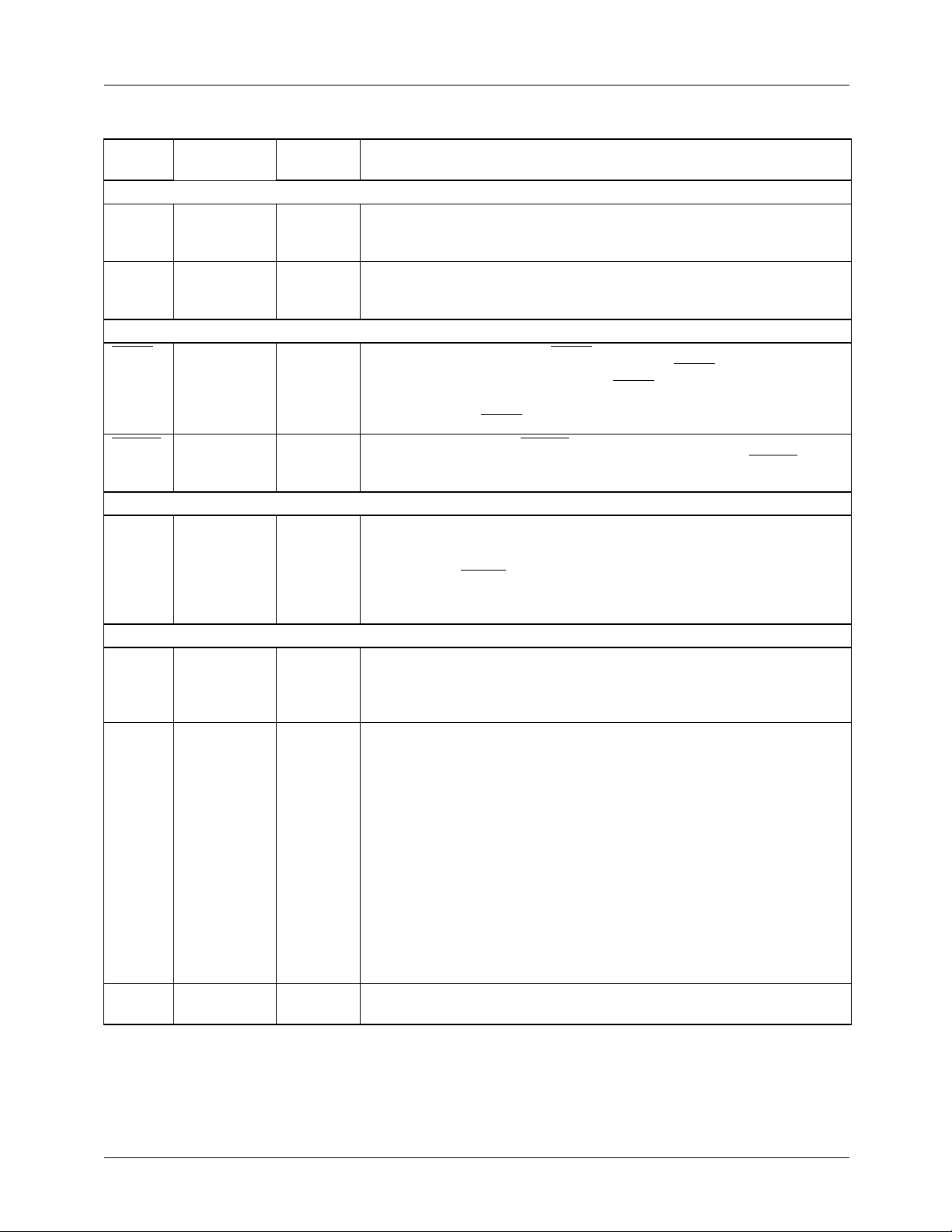

Pin Descriptions

Pin

Name Pin Number Value Pin Function Description

Clock and Data Inputs

CLK 26 CMOS Clock Input. Pixel data is registered on the rising edge of CLK. CLK

should be driven by a dedicated buffer to avoid reflection induced jitter,

overshoot, and undershoot.

R

7-0

G

7-0

B

7-0

47-40

9-2

23-16

CMOS Red, Green, and Blue Pixel Data Inputs. RGB digital inputs are

registered on the rising edge of CLK.

Controls

SYNC 11 CMOS Sync Pulse Input. Bringing SYNC LOW, disables a current source which

superimposes a sync pulse on the I

output. SYNC and pixel data are

OG

registered on the rising edge of CLK. SYNC does not override any other

data and should be used only during the blanking interval. If sync pulses

should be connected to GND.

BLANK

are not required, SYNC

10 CMOS Blanking Input. When BLANK is LOW, pixel data inputs are ignored and

the D/A converter outputs are driven to the blanking level. BLANK is

registered on the rising edge of CLK.

Video Outputs

I

I

I

OR

OG

OB

33

32

29

0.700 V

Red, Green, and Blue Current Outputs. Current source outputs can

p-p

drive VESA VSIS, and RS-343A/SMPTE-170M compatible levels into

doubly-terminated 75 Ohm lines. Sync pulses can be added to the green

output. When SYNC

is HIGH, the current added to I

OG

is:

IO

Voltage Reference

V

R

REF

REF

35 +1.25 V Voltage Reference Input/Output. Internal 1.25V voltage reference is

36 348 Ω

= 2.33 (V

S

available on this pin. An external +1.25 Volt reference may be applied to

this pin to override the internal reference. Decoupling V

a 0.1µF ceramic capacitor is required.

Current-set Resistor Node. Full-scale output current of each D/A

converter is determined by the value of the resistor connected between

R

and GND. Nominal value of R

REF

REF

/ R

REF

is found from:

REF

to GND with

REF

R

= 5.31 (V

REF

where I

is the full-scale output current (amps) from the

FS

D/A converter (without sync). Sync is 0.439 I

REF

/I

)

FS

.

FS

D/A full-scale current may also be calculated from:

I

= V

FS

Where V

/R

FS

L

is the full-scale voltage level and R

FS

is the total resistive load

L

(ohms) on each D/A converter.

COMP 34 0.1 µF Compensation Capacitor Node. A 0.1 µF ceramic capacitor must be

connected between COMP and V

4

to stabilize internal bias circuitry.

DD

REV. 1.2.2 11/11/01

Loading...

Loading...