Fairchild Semiconductor FAN5232 Datasheet

www.fairchildsemi.com

FAN5232

Adjustable PWM Buck Controller for LCD PCs

Features

• Three outputs: Adjustable Buck, 3.3V-Always,

5V-Always

• Adjustable synchronous switcher, 5V – 80% Vin

• 1% internal reference precision

• Current mode with voltage feed-forward

• Precision current limit option

• Charge pump works at all loads

• No shoot-through current

• Independent shutdown pins for ACPI

• Power Good, input UVLO, output OV

• 5.6V to 24V input voltage range

Applications

• LCD PCs

• Notebook PCs and PDAs

• Hand-held portable instruments

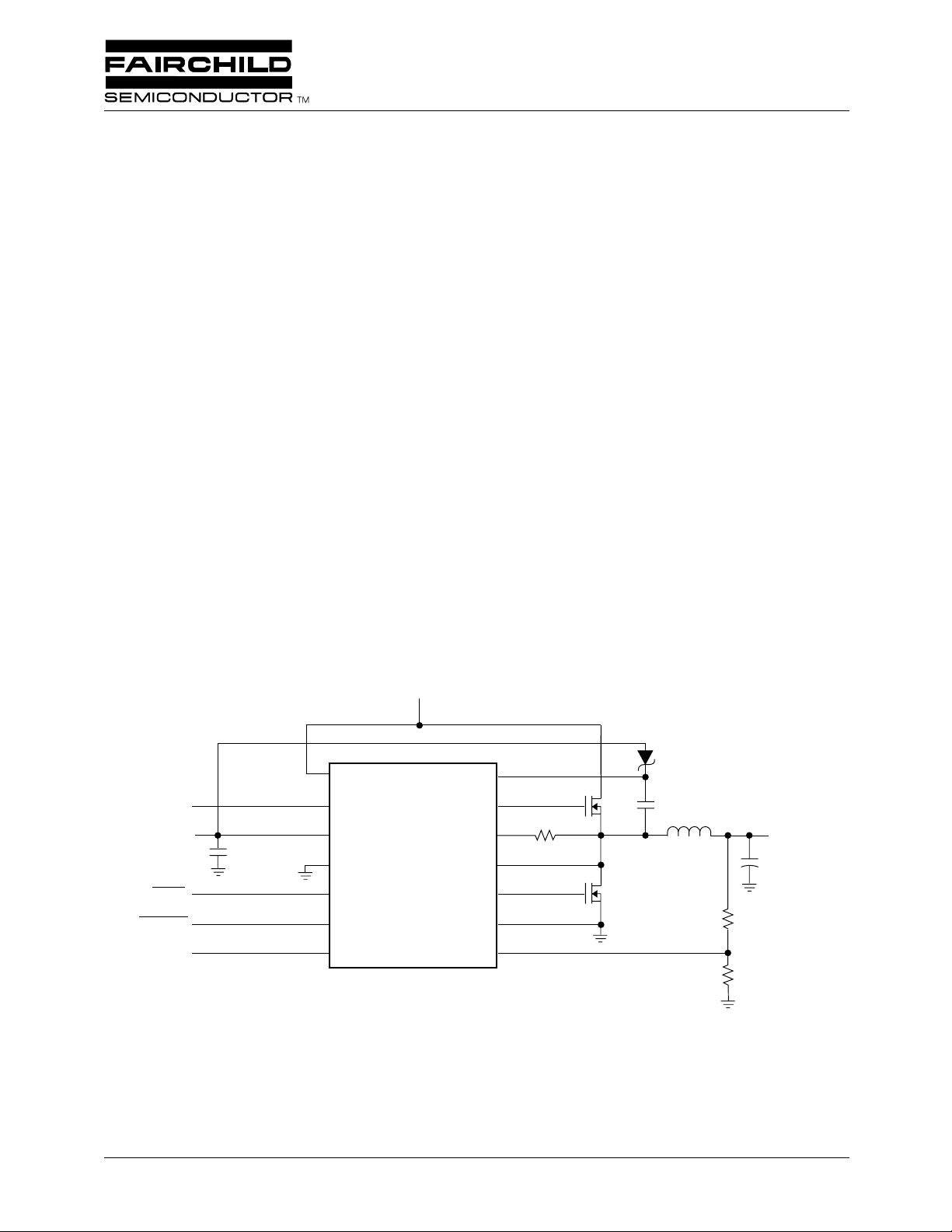

Block Diagram

Vin = 16–22V

Description

The FAN5232 is a high efficiency and high precision DC/DC

controller for PCs. It has a synchronous switcher whose

output can be adjusted from 5V up to 80% of Vin. It also has

two linear regulators for standby, 3.3V and 5V. The PWM

utilizes both input and output voltage feedback in a

current-mode control, allowing for fast and stable loop

response over a wide range of input and output variations.

Synchronous switching provides best efficiency over a wide

range of loads. Current sense based on MOSFET R

gives maximum efficiency, while also permitting use of an

optional sense resistor for high precision.

The FAN5232 is available in a 14 pin TSSOP package.

DS,on

3.3V-Always

5V-Always

SDWN

SDNADJ

PWRGD

1

2

3

4

5

6

7

FAN5232

14

13

12

11

10

12V @ 8A

+

9

8

REV. 1.1.1 10/7/02

2

FAN5232 PRODUCT SPECIFICATION

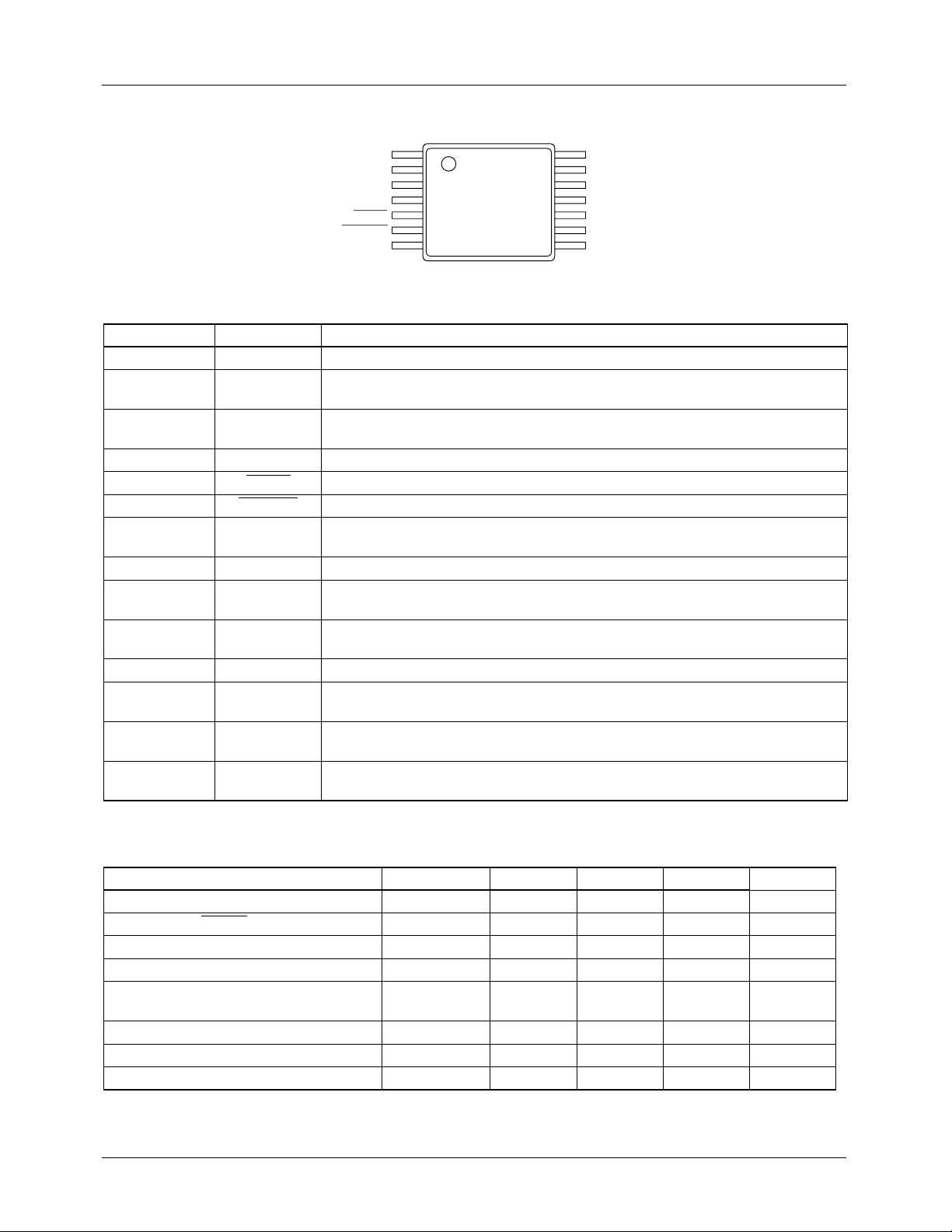

Pin Assignments

VBATT

3V_ALWAYS

5V_ALWAYS

AGND

SDWN

SDNADJ

PWRGD

1

2

3

4

5

6

7

14

13

12

11

10

9

8

Pin Description

Pin Number Pin Name Pin Function Description

1 VBATT

2 3V_ALWAYS 3.3V-ALWAYS Linear Regulator. Total load current on pins 2 and 3 together

3 5V_ALWAYS 5V-ALWAYS Linear Regulator. Total load current on pins 2 and 3 together

4 AGND

5SD

WN

6 SDNADJ

7 PWRGD

8 VFBSW

9 PGND

10 LSD

11 SW

12 ISNS

13 HSD

14 CPUMP

Battery Voltage. Battery voltage sensor.

must not exceed 50mA.

must not exceed 50mA.

Analog Ground.

IC Shutdown. Puts entire chip into shutdown. OFF=0. ON=1.

Shutdown and Softstart for the Switcher. OFF=0. ON=1.

Switcher Output OK. An open collector output that will be low if the switcher

output is out of spec.

Voltage Feedback for the Switcher.

Ground for the Switcher. Connect by the shortest possible path to the source

of the low side MOSFET.

Low Side FET Driver for the Switcher. Connect this pin through a resistor to

the gate of an N-channel MOSFET.

High Side FET Source and Low Side FET Drain Switching Node.

Current Feedback for the Switcher. Connect by the shortest possible path to

a resistor connected to the drain of the low side MOSFET.

High Side FET Driver for the Switcher. Connect this pin through a resistor to

the gate of an N-channel MOSFET.

Charge Pump for the Switcher. Generates gate drive voltage for the high-side

MOSFET.

CPUMP

HSD

ISNS

SW

LSD

PGND

VFB

Absolute Maximum Ratings

1

Parameter Conditions Min. Typ. Max. Units

VBATT Pin -0.3 29 V

PHASE, IFB, SDWN

Pins -5 29 V

CPUMP, HSD Pins -0.3 34 V

All Other Pins -0.3 6.5 V

Thermal Resistance, θ

J-A

θ

J-C

100

32

°C/W

°C/W

Junction Temperature 150 °C

Storage Temperature -65 150 °C

Lead Temperature, Soldering 10 sec. 300 °C

Note:

1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if

Operating Conditions are not exceeded.

REV. 1.1.1 10/7/02

PRODUCT SPECIFICATION FAN5232

Ω

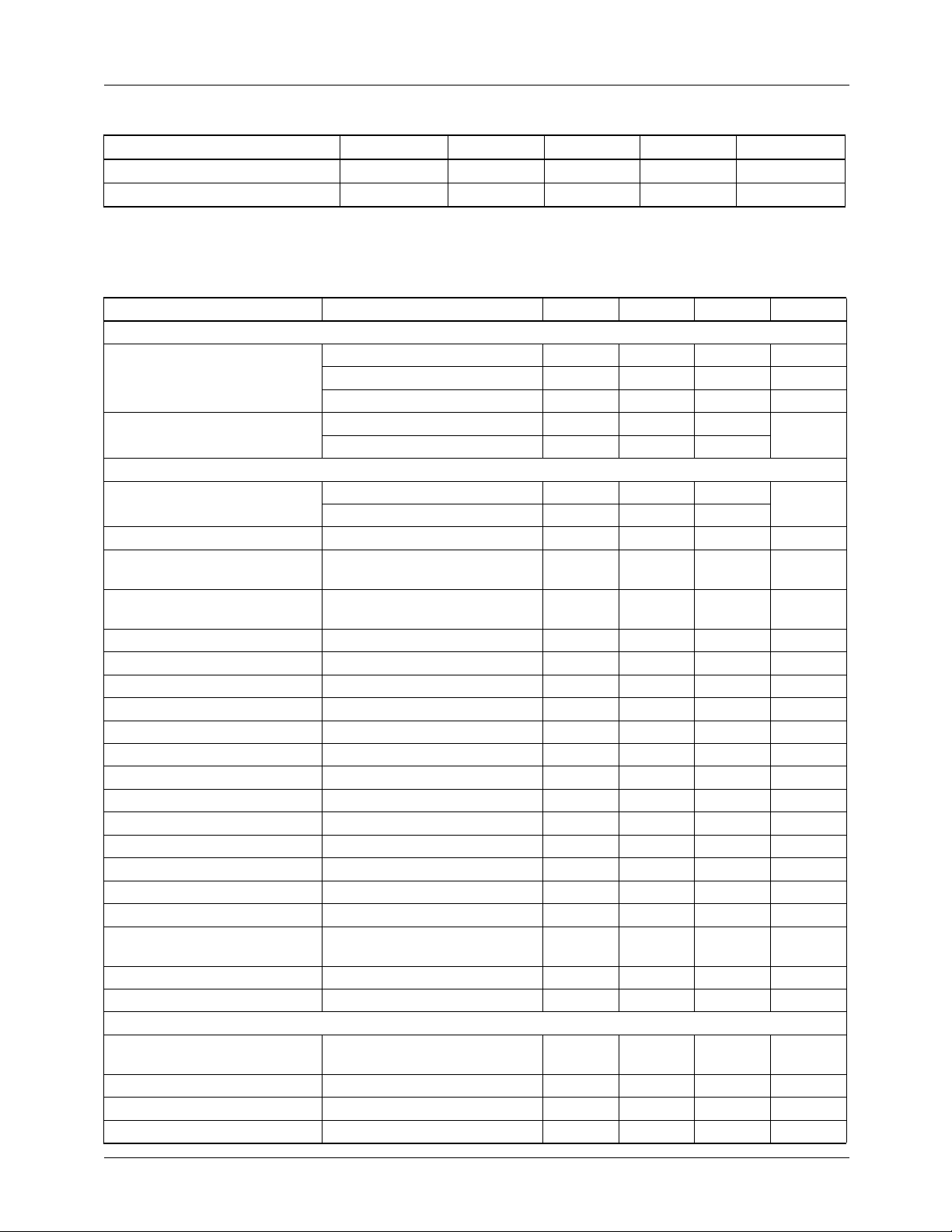

Recommended Operating Conditions

Parameter Conditions Min. Typ. Max. Units

VBATT Voltage 5.6 24 V

Ambient Temperature -20 85 °C

Electrical Specifications

(V

BATT

= 16V, T

= -20 to 85°C, circuit of Figure 1, unless otherwise specified.)

A

Parameter Conditions Min. Typ. Max. Units

Supply

V

Input Quiescent Current

CC

H/LSD

Open 1.4 mA

Stand-by 60 µA

Shut-down 10 µA

V

Input UVLO Threshold Rising 4.3 4.5 5.1 V

CC

Falling 4.0 4.3 4.7

Switcher

Output Voltage Precision, VFB 0.1 ≤ I ≤ 5.5A, 7.2 ≤ VBATT ≤ 24V 4.900 5 5.100 V

I ≤ 100mA, 5.6 ≤ VBATT ≤ 24V 4.900 5 5.100

Oscillator Frequency, f

OSC

Gate Drive On-Resistance for

255 300 345 KHz

612 Ω

all Sources and HSD Sinks

Gate Drive On Resistance for

1.5 8

LSD Sink

HSD On Output, V

HSD Off Output, V

LSD On Output, V

LSD Off Output, V

CPUMP

GS

5V-Always

GS

-V

I = 10µA 100 mV

GS

I = -10µA 100 mV

-V

I = 10µA 100 mV

GS

I = -10µA 100 mV

Ramp Amplitude, pk-pk 2 V

Ramp Offset 0.5 V

Ramp Gain from VBATT 125 mV/V

Error Amplifier GBW 3 MHz

Current Limit Threshold R3 = 1K Ω

135 150 165 mV

Over Voltage Threshold 2µs delay 110 115 120 %V

Under Voltage Threshold 2µs delay 70 75 80 %V

Max Duty Cycle 80 %

Min HSD On-time 200 nsec

VFBSW, ISNS Input Leakage

100 200 nA

Current

SDN/SS Full On Voltage Min. 4.2 V

SDN/SS Full Off Voltage Max. 800 mV

5V and 3.3V Always

Linear Regulator Accuracy 5.6V ≤ VBATT ≤ 22V,

-3.3 2 %

0 ≤ ILOAD ≤ 50mA

Rated Output Current I

3.3

+ I

5

50 mA

Overcurrent Limit 2µs delay 100 180 mA

Undervoltage Threshold 2µs delay 70 75 80 %

O

O

REV. 1.1.1 10/7/02

3

Loading...

Loading...