Fairchild Semiconductor FAN5230 Datasheet

www.fairchildsemi.com

FAN5230

System Electronics Regulator for Mobile PCs

Features

• 5.4V to 24V input voltage range

• Five regulated outputs:

• 5V @ 5A (PWM)

• 3.3V @ 5A (PWM)

• 5V @ 50mA Always On (Linear)

• 3.3V @ 50mA Always On (Linear)

• 12V/Adjustable @ 120mA Boost (PWM)

• >96% efficiency

• Hysteretic mode for light loads

• PWM mode for normal loads

• Main regulators switch out of phase

• 300kHz fixed frequency switching

• RDS(ON) current sense over-current

• Reduced BOM; Max. efficiency

• Optional current sense resistor for precision over-current

detect

• Power Good signal for all voltages

• Input under-voltage lock-out (UVLO)

• Thermal shutdown

• ACPI compliant

• 24-pin QSOP

• 2nd source by Intersil (IPM6220)

Applications

• Notebook PCs

• Web tablets

• Battery-powered instruments

Description

The FAN5230 is a high efficiency and high precision

multiple-output voltage regulator for notebook PC and other

similar battery-powered applications. It integrates three

pulse-width modulated (PWM) switching regulator

controllers and two linear regulators to convert 5.4V-to-24V

notebook battery power into the voltage used by the circuitry

that surrounds the microprocessor in these systems.

The two primary PWM controllers in the FAN5230 use

synchronous-mode rectification to provide 3.3V and 5V at

over 5A each. They switch out-of-phase to minimize input

ripple-current. Utilization of both input and output voltage

feedback in a current-mode control allows for fast and stable

loop response over a wide range of input and output

variations. PWM control in normal operation and hysteretic

control under light load provides efficiency of greater than

95% over a wide range of input and output variations. The

third PWM controller generates 12V at 120mA. A proprietary technology is used for accurate [± 1%] sensing of output current using the RDS(ON) of the external MOSFETs,

eliminating external current sense resistors which saves

board space and reduces BOM cost.

Two integrated linear regulators provide stand-by ALWAYSON power at 3.3V and 5V for light (50mA) loads. Additional

FAN5230 features include over-voltage, under-voltage, and

over-current monitors and thermal shutdow protection.

A single Power-Good signal is issued when soft start is

completed and all outputs are within ± 10% of their settings.

REV. 2.8.5 10/17/01

2

FAN5230

Typical Application

3.3V-ALWAYS@50mA

5V-ALWAYS

Vin = 5.4-24V

FAN5230

1 VIN

2 3.3 ALW

3 CPUMP3.3

CPUMP5 24

HSD5 23

SW5 22

5V-ALWAYS

5V @ 5A

+

3.3V @ 5A

+

Pin Assignments

5V-ALWAYS@ 50mA

PGOOD

SDN3.3

3.3V-ALWAYS

CPUMP3.3

HSD3.3

SW3.3

5V-ALWAYS

LSD3.3

GND3.3

ISEN3.3

VFB3.3

SDN3.3

PGOOD

VIN

4 HSD3.3

5 SW3.3

6 5V-ALW

7 LSD3.3

8 GND3.3

9 ISEN3.3

10 VFB3.3

11 SDN3.3

12 PGOOD

1

2

3

4

5

6

7

8

9

10

11

12

ISEN5 21

LSD5 20

GND5 19

VFB5 18

SDN5 17

SW12 16

VFB12 15

SGND 14

SDWN 13

Top View

24

23

22

21

20

19

18

17

16

15

14

13

SDN5

VFB12

SDWN

CPUMP5

HSD5

SW5

ISEN5

LSD5

GND5

VFB5

SDN5

SW12

VFB12

SGND

SDWN

12V @ 120mA

+

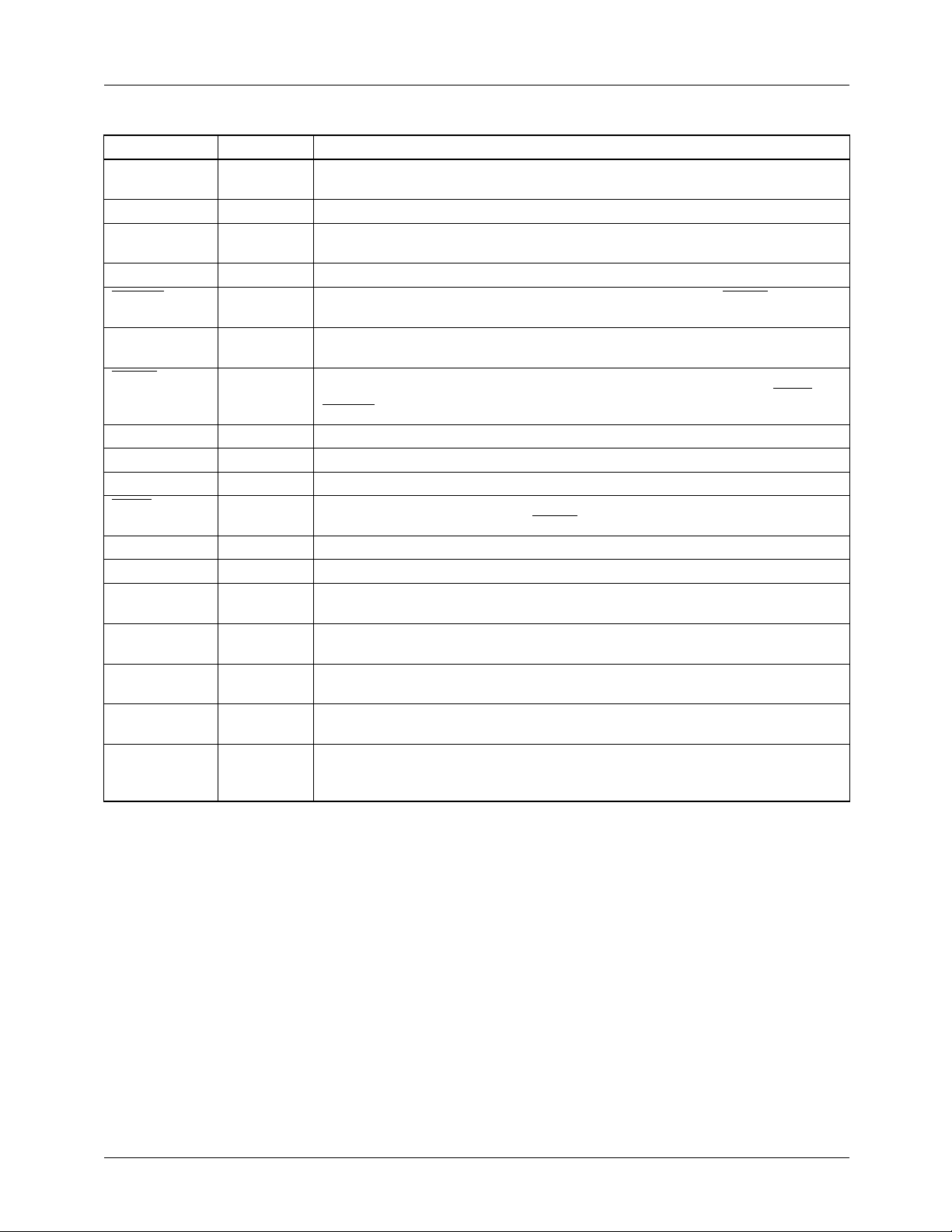

Pin Description

Pin Name Pin Number Pin Function Description

VIN 1

3.3V-ALWAYS 2

CPUMP3.3 3

HSD3.3 4

SW3.3 5

5V-ALWAYS 6

Input power.

3.3V Always on linear regulator. Load current on pins 2 and 6 must not exceed

50mA total. This pin should be decoupled to ground with a 10µF capacitor.

Charge Pump 3.3V. High side Gate drive voltage for 3.3V. This pin is to be

connected to SW3.3 through a 100nF cap. and to 5V-ALWAYS through a diode

High-side gate driver for 3.3V. Connect this pin directly to the gate of an

N-channel MOSFET. The trace from this pin to the MOSFET gate should be < 1".

High side FET Source and Low Side FET Drain Switching Node. Switching

node for 3.3V.

5V Always on linear regulator output. The sum of the load currents on pins 2

and 6 must not exceed 50mA total. This pin should be decoupled to ground with

a 10µF capacitor.

REV. 2.8.5 10/17/01

FAN5230

Pin Description

Pin Name Pin Number Pin Function Description

LSD3.3 7

GND3.3 8

ISEN3.3 9

VFB3.3 10

SDN3.3 11

PGOOD 12

SDWN 13

SGND 14

VFB12 15

SW12 16

SDN5 17

VFB5 18

GND5 19

LSD5 20

ISEN5 21

SW5 22

HSD5 23

CPUMP5 24

(Continued)

Low-side gate driver for 3.3V. Connect this pin directly to the gate of an

N-channel MOSFET. The trace from this pin to the MOSFET gate should be < 1".

Ground for 3.3V MOSFET.

Current sense for 3.3V. This pin should be connected to the Drain of the bottom

Mosfet with an appropriate resistor and an RC filter. See Application Section.

Voltage feedback for 3.3V.

Soft Start and ON/OFF for 3.3V. OFF=GND. ON=open with SDWN=High. Use

open collector device for control.

Power Good Flag. An open collector output that will be logic low if any output

voltage is not above 89% of the nominal output voltage.

Master Shutdown. Shutdown for all power. Off when low. When high

5V/3.3V-ALWAYS are ON while 5V/3.3V-Main are ready to turn on if SDN5,

SDN3.3 go open.

Signal ground.

Voltage feedback for 12V.

FET driver for 12V Boost.

Enable/Soft Start for 5V and 12V. Soft start and ON/OFF for 5V & 12V.

OFF=Grounded. ON=open with SDWN

Voltage feedback for 5V.

Ground for 5V MOSFET.

Low side FET driver for 5V. Connect this pin directly to the gate of an N-channel

MOSFET. The trace from this pin to the MOSFET gate should be < 1".

Current Sense for 5V. This pin should be connected to the drain of the bottom

Mosfet using appropriate resistor and RC filter. See Application Section.

High Side Driver Source and Low Side Driver Drain Switching Node.

Switching node for 5V.

High side FET driver for 5V. Connect this pin directly to the gate of an N-channel

MOSFET. The trace from this pin to the MOSFET gate should be < 1".

Charge Pump 5V. High side Gate drive voltage for 5V. High side Gate drive

voltage for 5V. This pin is to be connected to SW5 through a 100nF cap. and to

5V-ALWAYS through a diode.

=High.

REV. 2.8.5 10/17/01

3

FAN5230

4

Ω

Ω

Ω

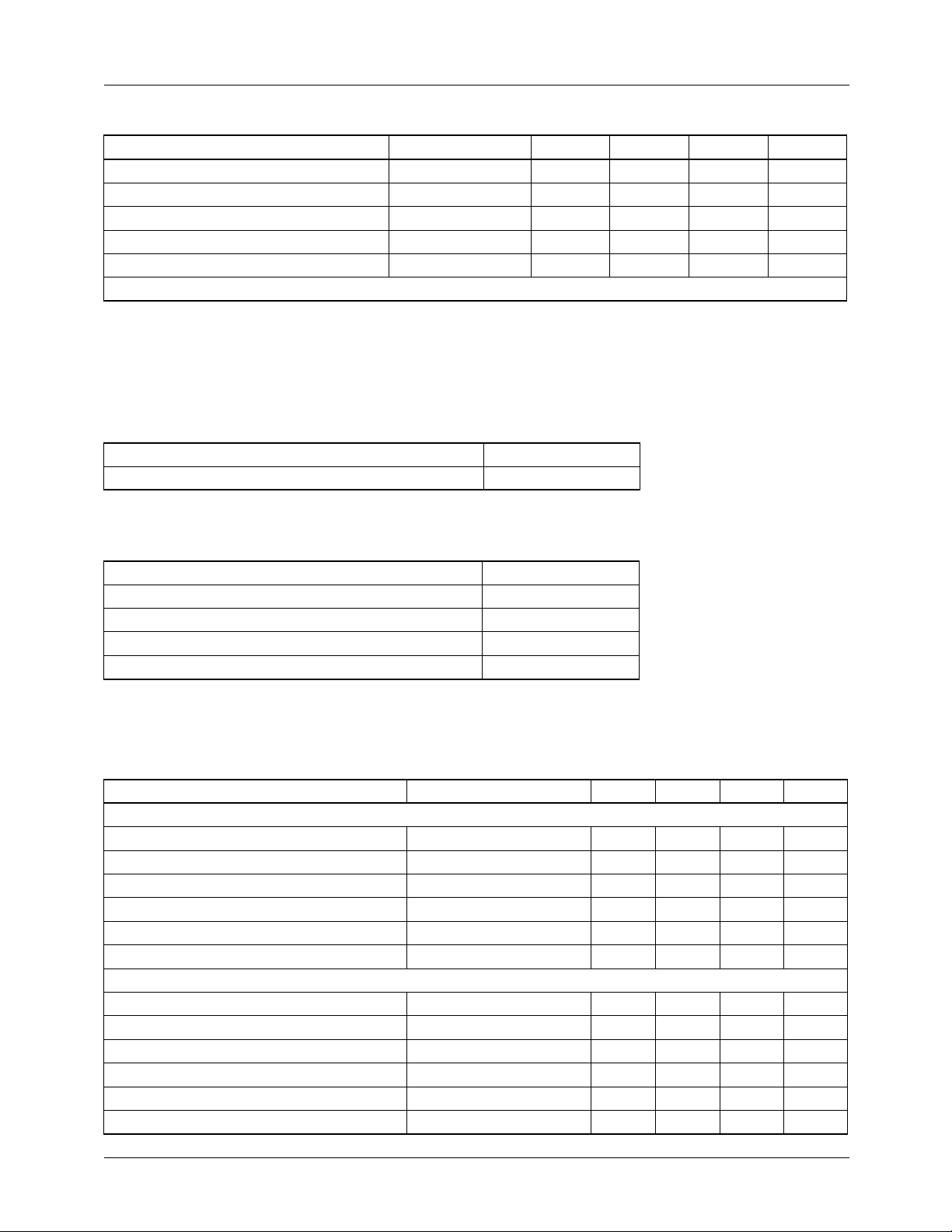

Absolute Maximum Ratings

Parameter Conditions Min. Typ. Max. Units

V

IN

SW, ISEN Pins,SDWN Pin -0.3 27 V

CPUMP, HSD Pins -0.3 33 V

SDN, VFB, V_always pins -0.3 6.5 V

CPUMP to SW pins, and all other pins -0.3 6.5 V

The sum of the load currents on pins 2 and 6 must not exceed 60mA total

Note:

1. Stresses beyond "Absolute Maximum Ratings" may cause permanent device damage. Continuous exposure to absolute

maximum rating conditions may affect device reliability. Functional operation of the device at these or any other conditions

beyond those indicated in the operational sections of the specification is not implied.

1

-0.3 27 V

Recommended Operating Conditions

Input Voltage, V

Ambient Temperature, T

IN

A

+5.4V to 24V

-20°C to 85°C

Thermal Information

Thermal Resistance, RTH

Thermal Resistance, RTH

Maximum Junction Temperature 150°C

Storage Temperature Range -65°C to 150°C

Maximum Lead Temperature, Soldering 10 Sec 300°C

88°C/W

JA

28.5°C/W

JC

ELECTRICAL SPECIFICATIONS

Operating Conditions

Recommended Operating Conditions Unless Noted Refers to Block Diagrams

Parameter Conditions Min. Typ. Max. Units

Supply

V

Input Supply Voltage (DC loading only) Note 1 5.4 24 V

IN

Input Quiescent Current H/LSD Open 1.4 3 mA

Stand-by 300 400 µA

Shut-down <1 5 µA

Input UVLO Threshold Rising Vbat 4.3 4.7 5.1 V

hysteresis 100 mV

5V and 3.3V Main Regulators

Output Voltage Precision 0.1 to 5.5A, 5.4 to 24V -2 +2 %

Oscillator Frequency, f

HSD On-Resistance, pull up 7 12

HSD On Resistance pull down 4 10

LSD On-Resistance, pull up 6 9

LSD On Resistance pull down 5 8

osc

255 300 345 kHz

Ω

REV. 2.8.5 10/17/01

Ω

Ω

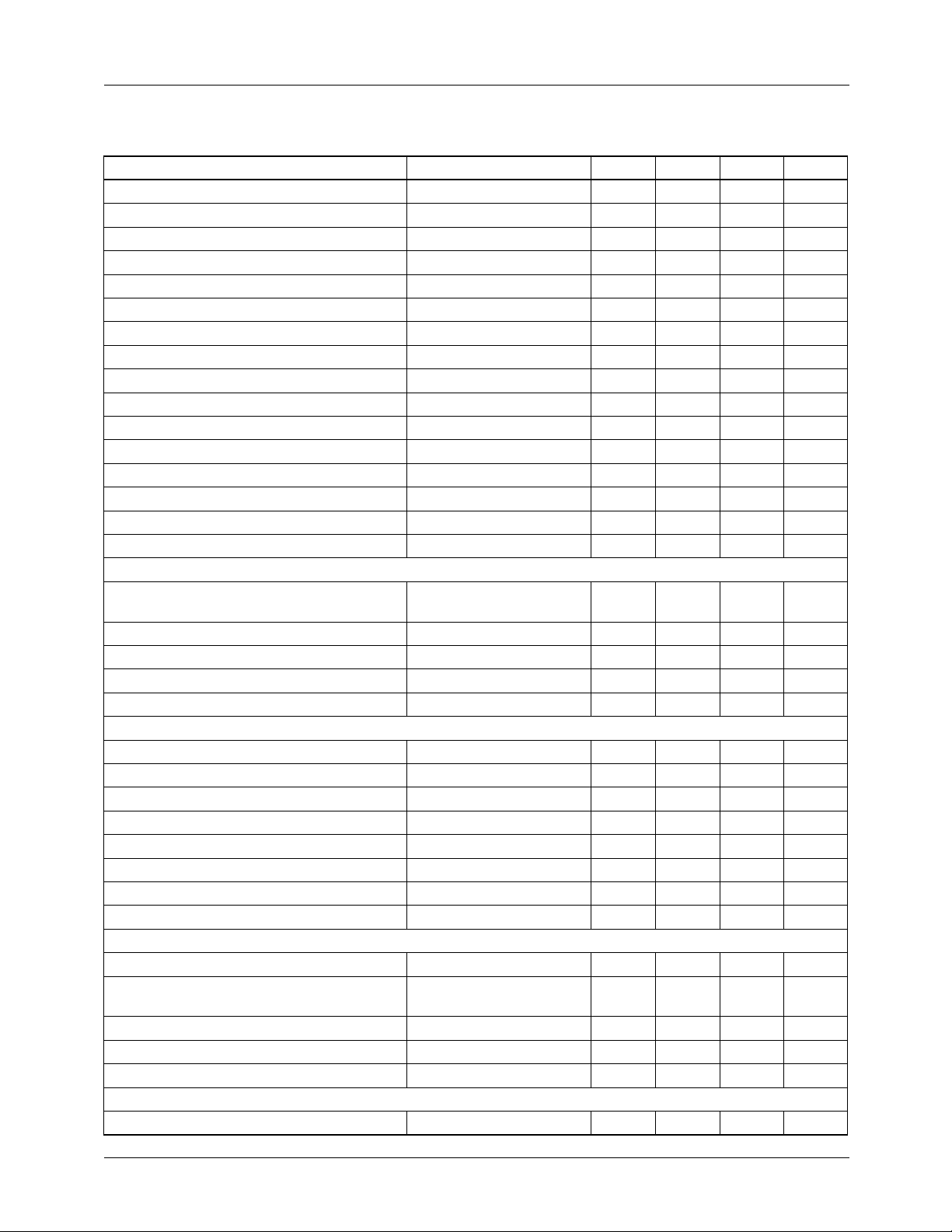

FAN5230

Operating Conditions

(Continued)

Recommended Operating Conditions Unless Noted Refers to Block Diagrams

Parameter Conditions Min. Typ. Max. Units

HSD On Output, V

HSD Off Output, V

LSD On Output, V

LSD Off Output, V

CPUMP

GS

5V-Always

GS

-V

-V

GS

GS

I = 10µA 100 mV

I = 10µA 100 mV

I = 10µA 100 mV

I = 10µA 100 mV

Ramp Amplitude, pk-pk VIN = 16V 2 V

Ramp Offset 0.5 V

Ramp Gain from V

IN

125 mV/V

Error Amplifier GBW 3 MHz

Current Limit Threshold R2, R8 = 1K Ω

90 135 180 µA

Over Voltage Threshold 2µs delay 110 115 120 %VO

Under Voltage Threshold 2µs delay 70 75 80 %VO

SDN/SS Full On Voltage Min. (End of Soft Start) 4.2 V

SDN/SS Full Off Voltage Max. 800 mV

Max Duty Cycle 94 %

Min PWM Time 200 nsec

VFB3.3 Input Leakage Current 40 55 70 µA

12V Regulator

Output Voltage Precision V_5 =4.9 to 5.1V

-2 +2 %

and Io=0 to 150mA

V

FB12

V

Input Current Note 2 100 200 nA

FB12

Oscillator Frequency (f

/3) 85 100 115 kHz

osc

2.472 V

Gate Drive On-Resistance High or Low 6 12

12V Regulator (Continued)

On Output, V

Off Output, V

5V-Always

GS

-V

GS

I = 10µA 100 mV

I = 10µA 100 mV

Ramp Amplitude, pk-pk 2 V

Error Amplifier GBW 1 MHz

Under Voltage Shut Down 2µs delay 70 76 80 %V

Over Voltage Shut Down Measured at VFB

12

115 %V

Min Duty Cycle 0 %

Max Duty Cycle (By design) 32 33 34 %

5V and 3.3V Always

Bypass Switch rdson 1.3 1.5

Linear Regulator Accuracy 5.6 to 24V, 0 to 50mA,

-3.3 2 %

5V Main On or Off

Rated Output Current I

3.3

+ I

5

050mA

Over-current Limit 2µs delay 100 180 mA

Under-voltage Threshold 2µs delay 70 75 80 %

Reference

Internal Reference Accuracy 0-70°C -1 1 %

O

O

REV. 2.8.5 10/17/01

5

Loading...

Loading...