Fairchild Semiconductor 74LVTH652WMX, 74LVTH652WM, 74LVTH652MTCX, 74LVTH652MTC Datasheet

© 2000 Fairchild Semiconductor Corporation DS012018 www.fairchildsemi.com

April 2000

Revised April 2000

74LVTH652 Low Voltage Octal Trans ceiver/Register with 3-STATE Outputs

74LVTH652

Low Voltage Octal Transceiver/Register

with 3-STATE Outputs

General Description

The LVTH652 consists of bus transceiver circui ts with Dtype flip-flops, and control circuitry arranged for multiplexed

transmission of data d irectly from the in put b us or fr om the

internal registers. Data on the A or B bus will be clocked

into the registers as the appropriate clock pin goes to HIGH

logic level. Output Enable pins (OEAB, OEBA

) are provided to control the tr ansceiver function. (See Functio nal

Description).

The LVTH652 data inputs include bush old, eliminati ng the

need for external pull-up resistors to hold unused inputs.

This octal transceiver/register is d esigned for low-voltage

(3.3V) V

CC

applications, but with the capability to provide a

TTL interface to a 5V enviro nment. The LVTH652 is fabricated with an advanced BiCMOS technology to achieve

high speed opera tion similar to 5V ABT while maintaining

low power dissipation.

Features

■ Input and output interface capability to systems at

5V V

CC

■ Bushold data inputs elimina te the nee d for exte rnal pul lup resistors to hold unused inputs

■ Live insertion/extraction per mitt ed

■ Power Up/Down high impedance provides glitch-free

bus loading

■ Outputs source/sink −32 mA/+64 mA

■ Functionally compatible with the 74 series 652

■ Latch-up performance exceeds 500 mA

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending su ffix let te r “X” to the ordering code.

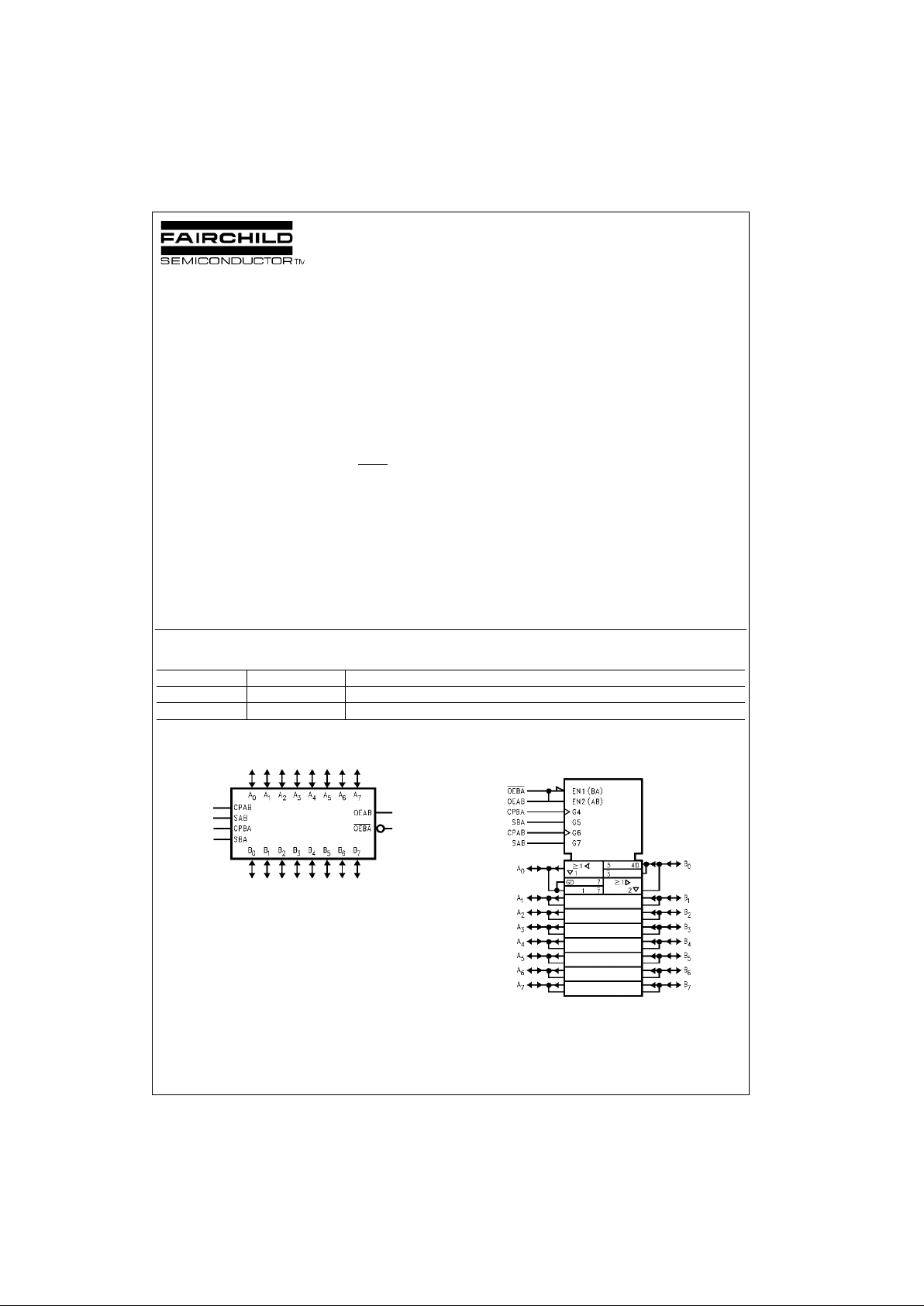

Logic Symbols

IEEE/IEC

Order Number Package Number Package Description

74LVTH652WM M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

74LVTH652MTC MTC24 24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

www.fairchildsemi.com 2

74LVTH652

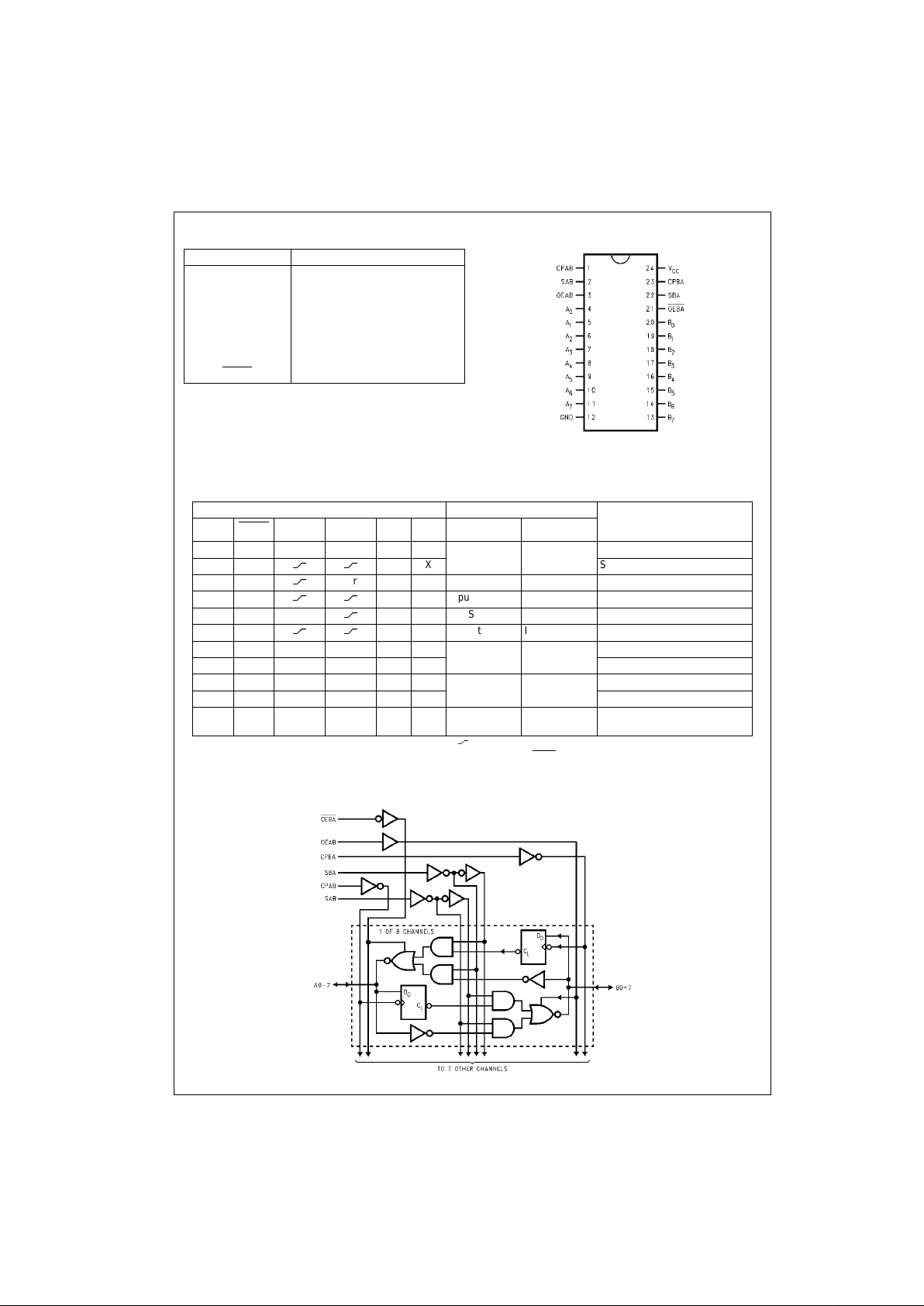

Pin Descriptions Connection Diagram

Truth Table

(Note 1)

H = HIGH Voltage Level L = LOW Voltage Lev el X = Immaterial = LOW to HIGH Clock Transition

Note 1: The data output fu nction s may b e enable d or di sabled b y variou s signa ls at OEA B or O EBA

inputs. Data input function s are a lways e nabled, i.e.,

data at the bus pins w ill be stored on every LOW- to -H I GH t ransition on the clock inp ut s .

Logic Diagram

Please note that this diagram is provided o nly f or t he understanding of lo gic operations and should not be used to estimate propagation delays.

Pin Names Description

A

0–A7

Data Register A Inputs/

3-STATE Outputs

B

0–B7

Data Register B Inputs/

3-STATE Outputs

CPAB, CPBA Clock Pulse Inputs

SAB, SBA Select Inputs

OEAB, OEBA

Output Enable Inputs

Inputs Inputs/Outputs

Operating Mode

OEAB OEBA

CPAB CPBA SAB SBA A0 thru A7B0 thru B

7

L H H or L H or L X X Input Input Isolation

LH

X X Store A and B Data

XH

H or L X X Input Not Specified Store A, Hold B

HH

X X Input Output Store A in Both Registers

LXH or L

X X Not Specified Input Hold A, Store B

LL

X X Output Input Store B in Both Registers

L L X X X L Output Input Real-Time B Data to A Bus

L L X H or L X H Store B Data to A Bus

H H X X L X Input Output Real-Time A Data to B Bus

H H H or L X H X Stored A Data to B Bus

H L H or L H or L H H Output Output

Stored A Data to B Bus and

Stored B Data to A Bus

3 www.fairchildsemi.com

74LVTH652

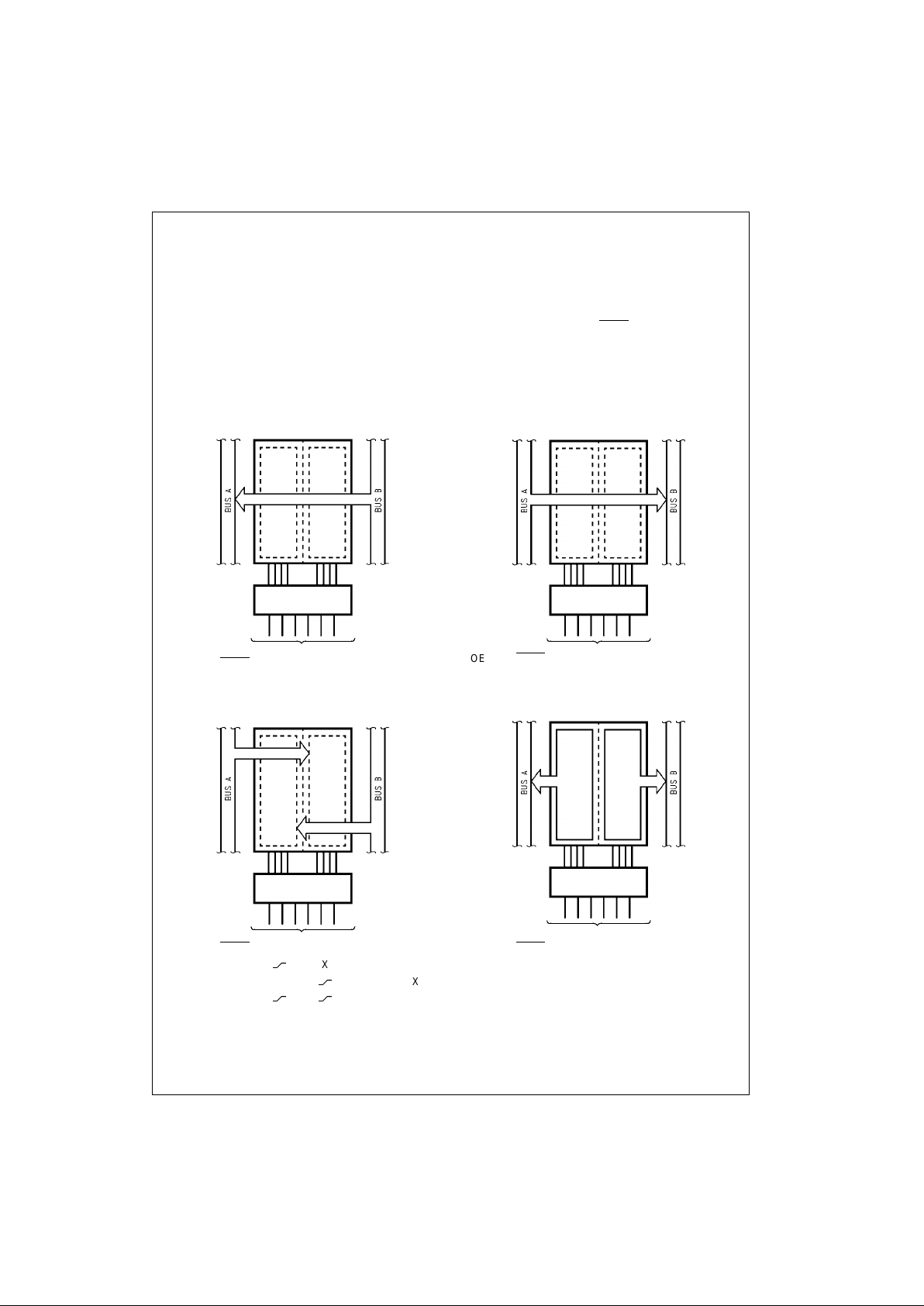

Functional Description

In the transceiver mode , data present a t the HIGH impe dance port may be sto red in either the A or B register or

both.

The select (SAB, SBA) controls can multiplex stored and

real-time.

The examples below demonstrate the four fundamental

bus-management fun cti on s t hat c an be performed wi th t he

LVTH652.

Data on the A or B data bus, or both can be stored in the

internal D-type flip-flop by LOW-to-H IGH transitions at the

appropriate Clock Inp uts (CPAB, CPBA) regardless of the

Select or Output Enable Inputs. When SAB and SBA are in

the real time transfer m od e, it is a lso po ssibl e to sto re d ata

without using the internal D-type flip-flops by simultaneously enabling OEAB and OEBA

. In this configuration

each Output reinforces its Input. Thu s when all other data

sources to the two sets of bus lin es are in a HIGH imp edance state, each set of bus lines will remain at its last state.

Real-Time Transfer

Bus B to Bus A

Storage

Real-Time Transfer

Bus A to Bus B

Transfer Storage

Data to A or B

OEAB OEBA

CPAB CPBA SAB SBA

LLXXXL

OEAB OEBA

CPAB CPBA SAB SBA

XH

XXX

LXX

XX

LH

XX

OEAB OEBA CPAB CPBA SAB SBA

HHXXLX

OEAB OEBA

CPAB CPBA SAB SBA

H L H or L H or L H H

Loading...

Loading...