Fairchild Semiconductor 74F182SJ, 74F182PC Datasheet

74F182

Carry Lookahead Generator

74F182 Carry Lookahead Generator

April 1988

Revised July 1999

General Description

The 74F182 is a high-speed carry lookah ead genera tor. It

is generally used w ith the 74F181 or 74F381 4-bit ari thmetic logic units to provide high-speed lookahead over

word lengths of more than four bits.

Features

■ Provides lookahead carries across a group of four ALUs

■ Multi-level lookahead high-speed arithmetic operation

over long word lengths

Ordering Code:

Order Number Package Number Package Description

74F182SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F182PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

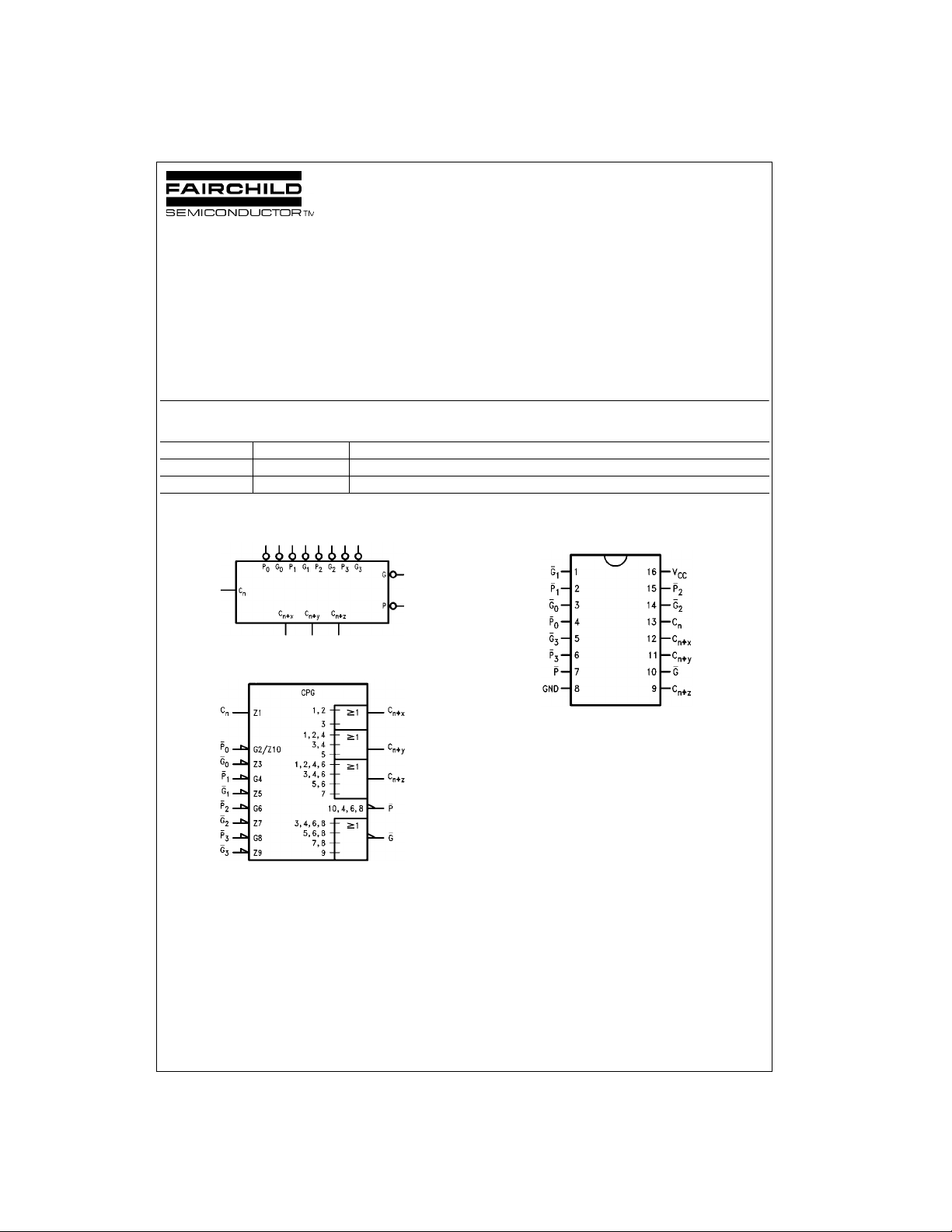

Logic Symbols Connection Diagram

© 1999 Fairchild Semiconductor Corporation DS009492 www.fairchildsemi.com

Unit Loading/Fan Out

74F182

Pin Names Description

C

n

, G

G

0

G

1

G

3

, P

P

0

1

P

2

P

3

− C

C

n+x

G

P

Carry Input 1.0/2.0 20 µA/−1.2 mA

Carry Generate Inputs (Active LOW) 1.0/14.0 20 µA/−8.4 mA

2

Carry Generate Input (Active LOW) 1.0/16.0 20 µA/−9.6 mA

Carry Generate Input (Active LOW) 1.0/8.0 20 µA/−4.8 mA

Carry Propagate Inputs (Active LOW) 1.0/8.0 20 µA/−4.8 mA

Carry Propagate Input (Active LOW) 1.0/6.0 20 µA/−3.6 mA

Carry Propagate Input (Active LOW) 1.0/4.0 20 µA/−2.4 mA

Carry Outputs 50/33.3 −1 mA/20 mA

n+z

Carry Generate Output (Active LOW) 50/33.3 −1 mA/20 mA

Carry Propagate Output (Active LOW) 50/33.3 −1 mA/20 mA

Functional Description

The 74F182 carry lookahe ad generator acce pts up to four

pairs of Active LOW Carry Propagate (P

Generate (G

) and provides anticip ated Active HIGH carries (C

(C

n

, C

C

n+y

) signals and an Active HIGH Carr y input

0–G3

) across four groups of binary adders. The

n+z

74F182 also has Active LOW Carry Propagate (P

Carry Generate (G

) outputs which may be use d for furthe r

levels of lookahead . The logic equations provided at the

outputs are:

= G0 + P0 C

C

n+x

C

= G1 + P1 G0 + P1 P0 C

n+y

C

= G2 + P2 G1 + P2 P1 G0 + P2 P1 P0 C

n+z

n

n

G = G3 + P3 G2 + P3 P2 G1 + P3 P2 P1 G

P = P2 P2 P1 P

0

0–P3

n

0

) and Carry

n + x

) and

U.L.

HIGH/LOW

Input I

Output I

IH/IIL

OH/IOL

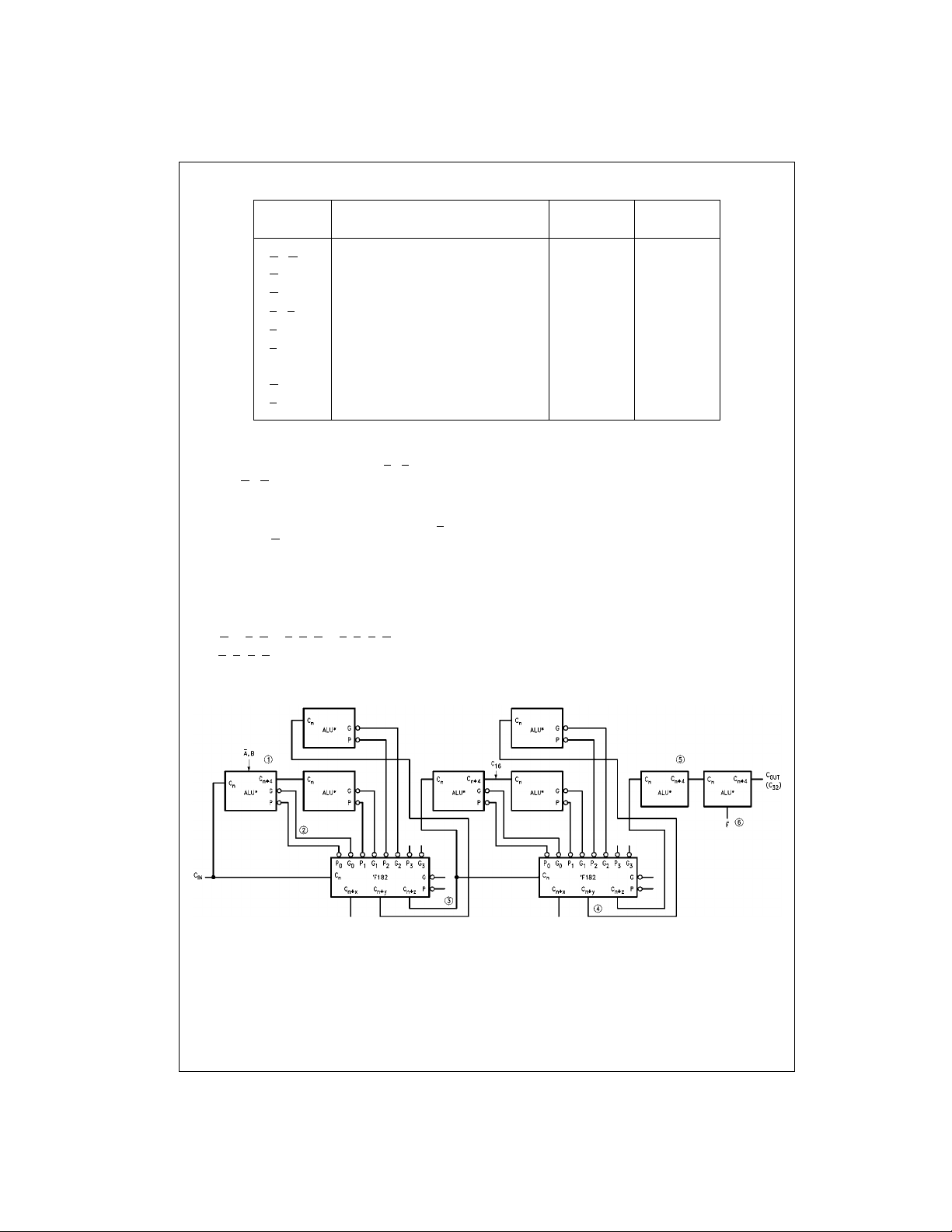

Also, the 74F182 can be used with binary ALUs in an

active LOW or active HIGH input ope rand mode . The connections (Figure 1) to and from the ALU to the carry lookahead generator are identical in both cases. Carries are

,

rippled between lookahea d blocks. Th e critical speed p ath

follows the circled numbers. There are several possible

arrangements for the carry interconnects, but all ach ieve

about the same speed. A 28-bit ALU is formed by dropping

the last 74F181 or 74F381.

*ALUs may be either 74F181 or 74F381

FIGURE 1. 32-Bit ALU with Rippled Carry between 16-Bit Lookahead ALUs

www.fairchildsemi.com 2

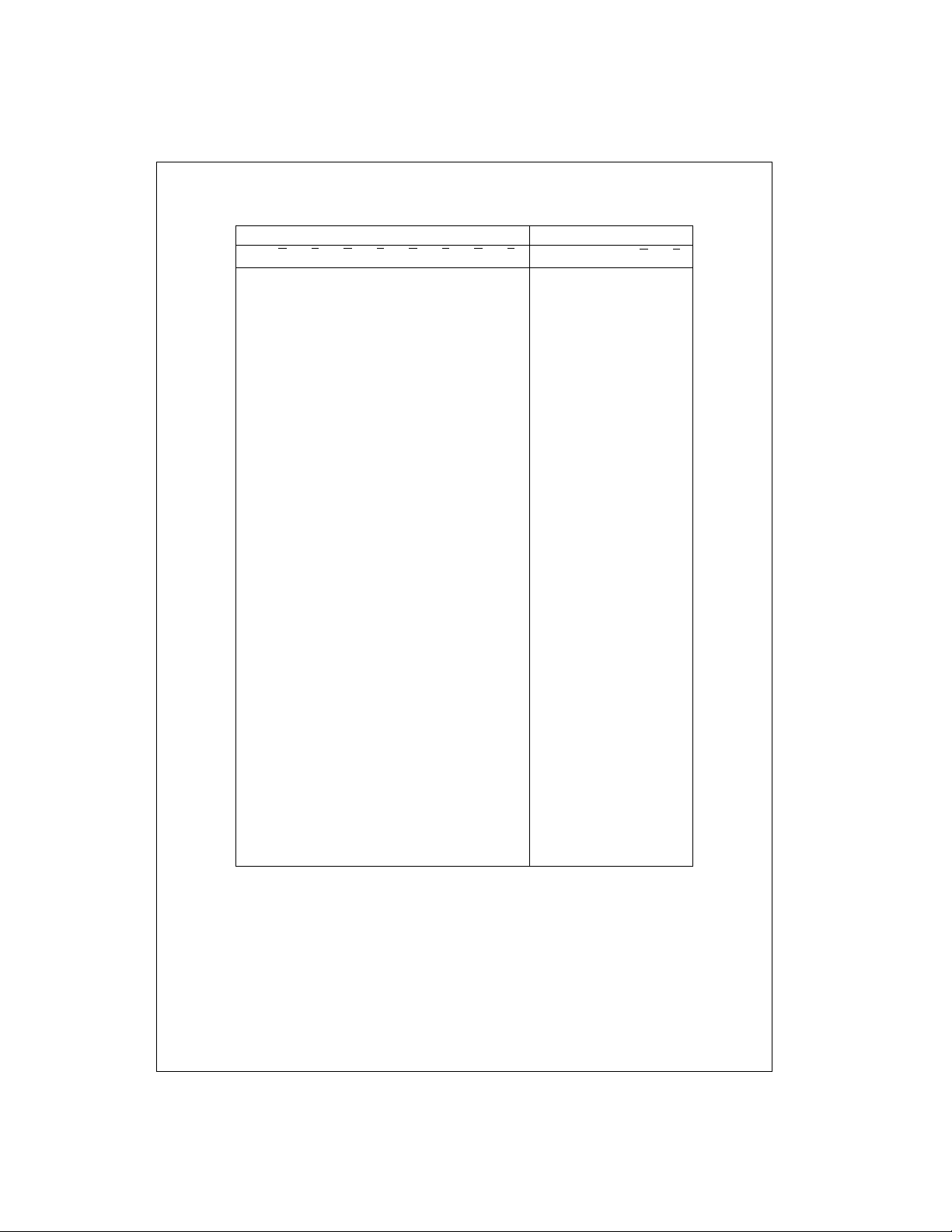

Truth Table

Inputs Outputs

C

nG0P0G1P1G2P2G3P3Cn+xCn+yCn+z

XHH L

LHX L

XLX H

HXL H

XXXHH L

XHHHX L

LHXHX L

XXXLX H

XLXXL H

HXLXL H

XXXXXHH L

XXXHHHX L

XHHHXHX L

LHXHXHX L

XXXXXLX H

XXXLXXL H

XLXXLXL H

HXLXLXL H

74F182

G P

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

X XXXXHH H

X XXHHHX H

X HHHXHX H

H HXHXHX H

X XXXXLX L

XXXLXXL L

XLXXLXL L

L XLXLXL L

HXXX H

XHXX H

XXHX H

XXXH H

LLLL L

3 www.fairchildsemi.com

Loading...

Loading...