Fairchild Semiconductor 74F181SPC, 74F181SCX, 74F181SC, 74F181PC Datasheet

© 1999 Fairchild Semiconductor Corporation DS009491 www.fairchildsemi.com

April 1988

Revised July 1999

74F181 4-Bit Arithmetic Logic Unit

74F181

4-Bit Arithmetic Logic Unit

General Description

The 74F181 is a 4-bit Arithmetic logic Unit (ALU) which can

perform all the po ssible 16 logic operations on two variables and a variety of arithmetic operations. It is 40% faster

than the Schottky ALU and only consu mes 30% as much

power.

Features

■ Full lookahead for high-speed arithmetic operation on

long words

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

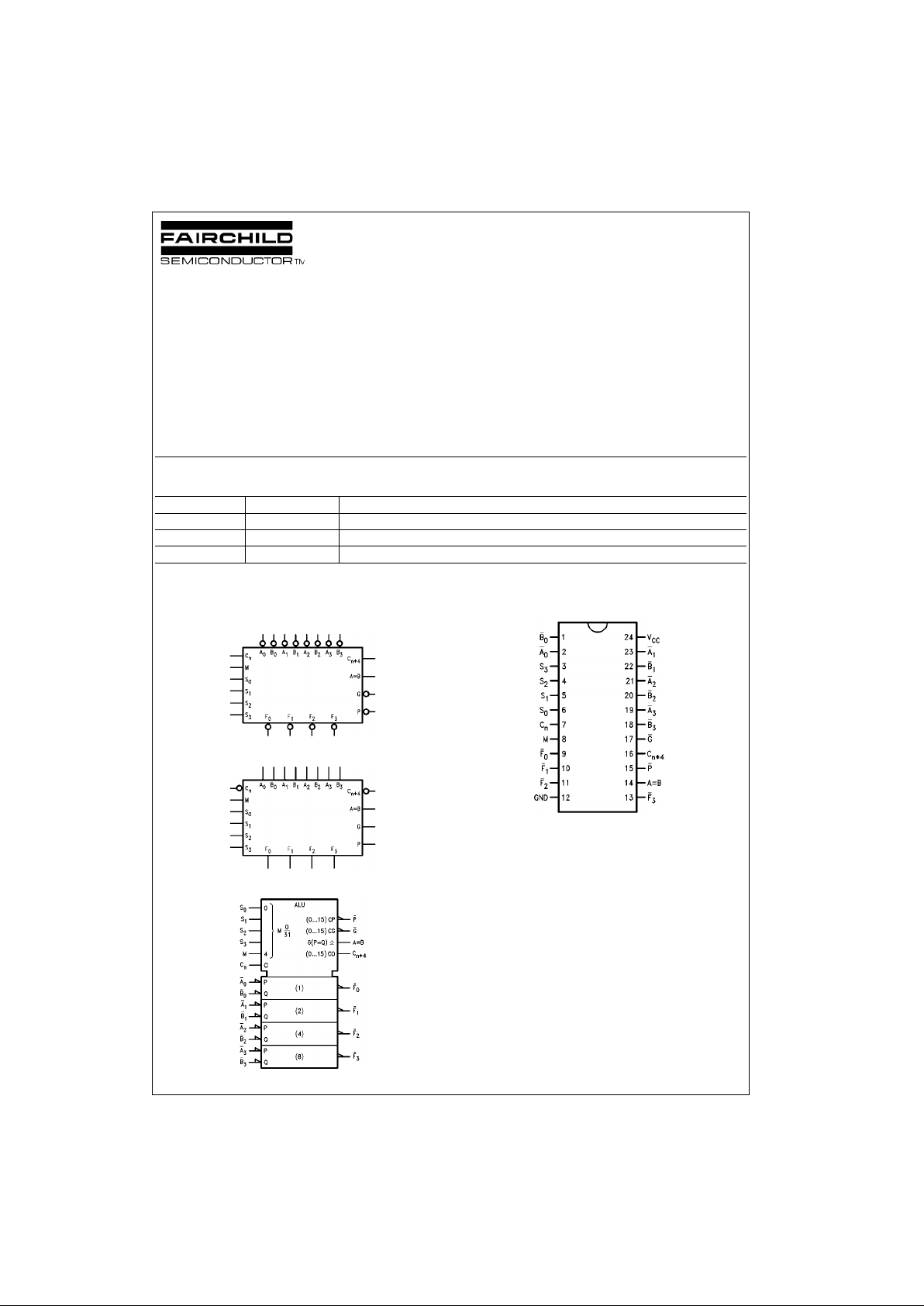

Logic Symbols

Active-HIGH Operands

Active-LOW Operands

IEEE/IEC

Connection Diagram

Order Number Package Number Package Description

74F181SC M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

74F181PC N24A 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600 Wide

74F181SPC N24C 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

www.fairchildsemi.com 2

74F181

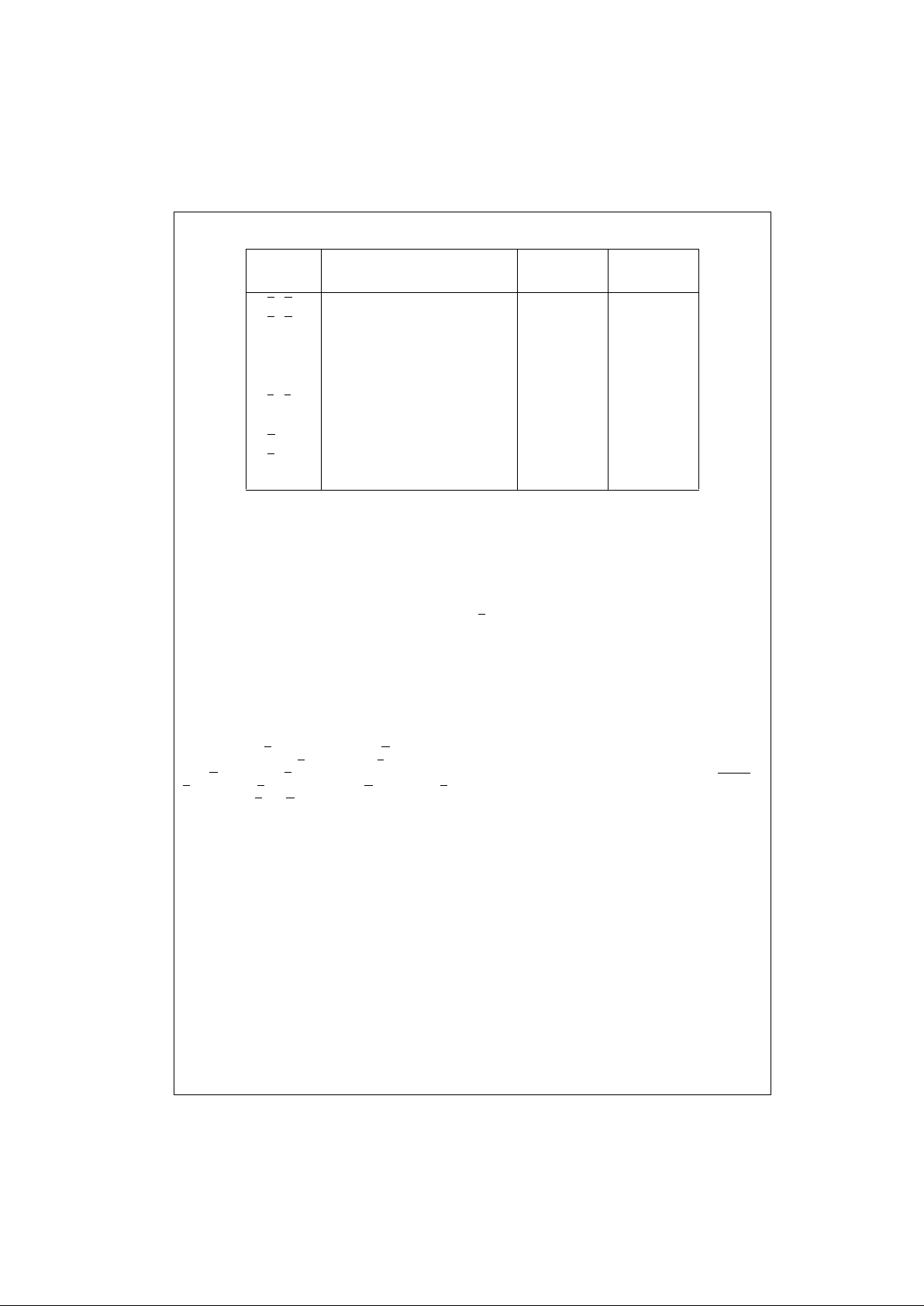

Unit Loading/Fan Out

Note 1: OC-Open C ollector

Functional Description

The 74F181 is a 4-bit high-speed parallel Arithmetic Logic

Unit (ALU). Controlled by the four Function Select inputs

(S

0–S3

) and the Mode Control input (M), it can perform all

the 16 possible log ic operations or 16 different arithmetic

operations on Active HIGH or Active LOW operands. The

Function Table lists these operations.

When the Mode Control input (M) is HIGH, all internal carries are inhibited and the device p erforms l ogic oper ations

on the individual bits as listed. When the Mode Control

input is LOW, the carries are enabled and the dev ice performs arithmetic operations on the two 4-bit words. The

device incorporates full internal carry l ookahead and provides for either ripple carry between devices using the

C

n + 4

output, or for carry lookahead between packages

using the signals P

(Carry Propagate) and G (Carry Gener-

ate). In the Add mode, P

indicates that F is 15 or more,

while G

indicates that F is 16 or more. In the Subtract mode

P

indicates that F is zero or less, while G indicates that F is

less than zero. P

and G are not affected by carry in. When

speed requiremen ts are not stringent , the 74F181 can be

used in a simple Ripple Carry mode by connecting the

Carry output (C

n

+4) signal to the Carry input (Cn) of the

next unit. For h igh speed operation t he device is used in

conjunction with a carry lookahead circuit. One carry lookahead package is requ ired for each group of four 74F181

devices. Carry lookahead can be provided at various levels

and offers high speed capability over extremely long wo rd

lengths.

The A = B output from the device goes HIGH w hen all four

F

outputs are HIGH and can be used to indicate logic

equivalence over four bits when the u nit is in t he Subtract

mode. The A = B output is open collector and can be wired

AND with other A = B outputs to give a comparison for

more than four bits. The A = B signal can also be used with

the C

n+4

signal to indicate A > B and A < B.

The Function Table lists the arithmetic ope rations that are

performed without a carry in. An incoming carry adds a one

to each operation . Thus, select code LHHL gene rates A

minus B minus 1 (2s complem ent no tation) witho ut a ca rry

in and generates A minus B when a carry is applied.

Because subtraction is actual ly performed by co mplementary addition (1s complement), a carry out means borrow

;

thus a carry is gener ated when there is no underflow a nd

no carry is generated when there is underflow. As indicated, this device can be used with either active LOW

inputs producing active LOW outputs or with active HIGH

inputs producing active HIGH outp uts. For either case the

table lists the operatio ns that are performed to the operands labeled inside the logic symbol.

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

A0–A

3

A Operand Inputs (Active LOW) 1.0/3.0 20 µA/−1.8 mA

B

0–B3

B Operand Inputs (Active LOW) 1.0/3.0 20 µA/−1.8 mA

S

0–S3

Function Select Inputs 1.0/4.0 20 µA/−2.4 mA

M Mode Control Input 1.0/1.0 20 µA/−0.6 mA

C

n

Carry Input 1.0/5.0 20 µA/−3.0 mA

F

0–F3

Function Outputs (Active LOW) 50/33.3 −1 mA/20 mA

A = B Comparator Output OC (Note 1)/33.3 (Note 1)/20 mA

G

Carry Generate Output (Active LOW) 50/33.3 −1 mA/20 mA

P

Carry Propagate Output (Active LOW) 50/33.3 −1 mA/20 mA

C

n + 4

Carry Output 50/33.3 −1 mA/20 mA

3 www.fairchildsemi.com

74F181

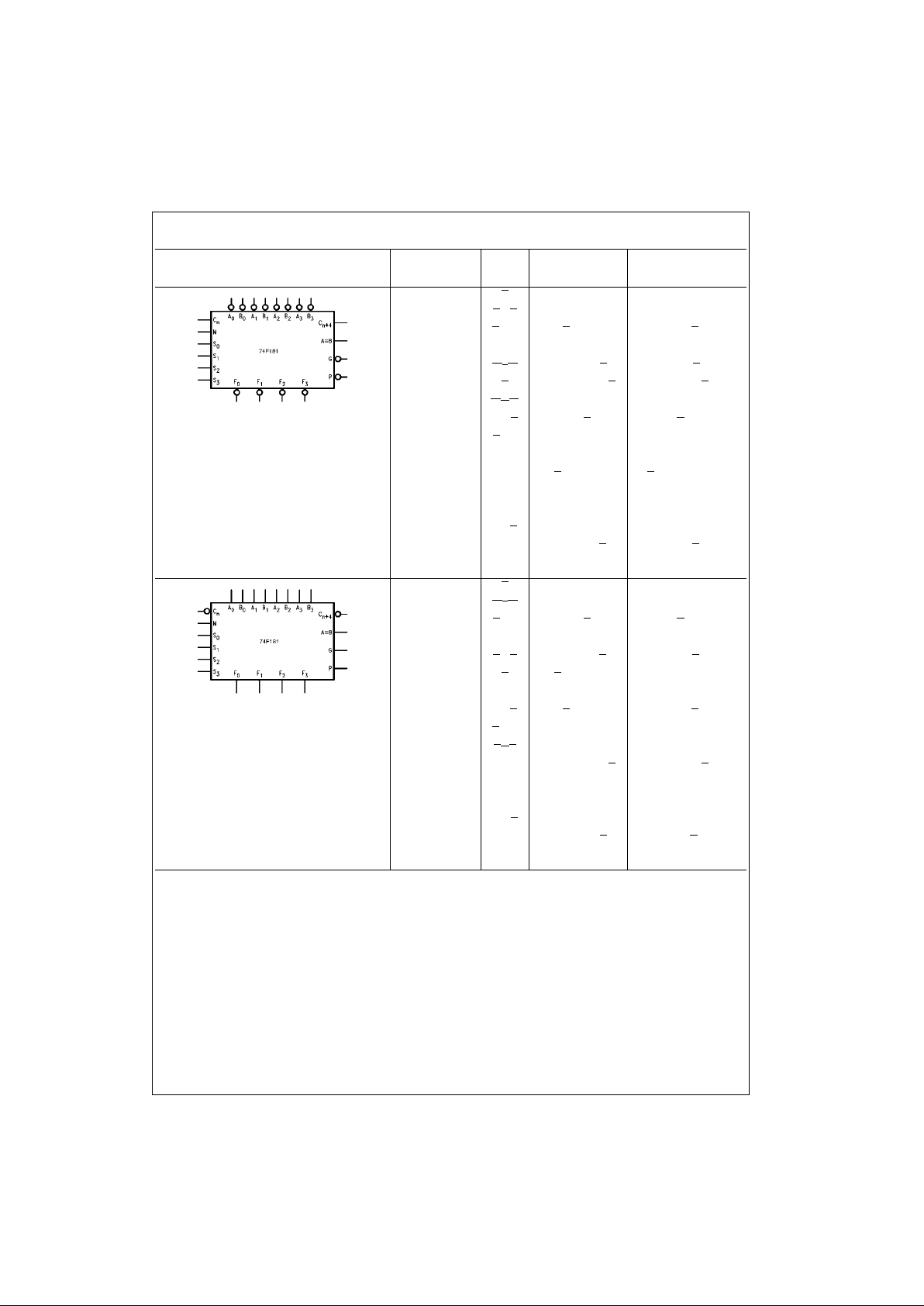

Operation Table

Logic Arithmetic Arithmetic

S

0S1S2S3

(M=H) (M=L, C0=Inactive) (M=L, C0=Active)

a. All Input Data Inverted

LLLL A

A minus 1 A

HLLL A

• B A • B minus 1 A • B

LHLL A

+ BA • B minus 1 A • B

H H L L Logic “1” minus 1 (2s comp.) Zero

LLHL A

+ B A plus (A + B) A plus (A + B) plus 1

HLHL B

A • B plus (A + B) A • B plus (A + B) plus 1

LHHLA

⊕ B A minus B minus 1 A minus B

HHHL A + B

A + B A + B plus 1

LLLHA

• B A plus (A + B) A plus (A + B plus 1

HLLH A⊕B A plus B A plus B plus 1

LHLH B A • B

plus (A + B) A • B plus (A + B) plus 1

HHLH A + BA + BA + B plus 1

L L H H Logic “0” A plus A (2 × A) A plus A (2 × A) plus 1

HLHH A • B

A plus A • B A plus A • B plus 1

L H H H A • B A plus A • B

A plus A • B plus 1

HHHH A A A plus 1

b. All Input Data True

LLLL A

A A plus 1

HLLLA

+ B A + BA + B plus 1

LHLL A

• B A + B A + B plus 1

H H L L Logic “0” minus 1 (2s comp.) Zero

LLHL A

• B A plus (A • B)A plus A • B plus 1

HLHL B

A • B plus (A + B) A • B plus (A + B) plus 1

LHHLA ⊕ B A minus B minus 1 A minus B

HHHL A • B

A • B minus 1 A • B

LLLHA + B A plus A • B A plus A • B plus 1

HLLH A

⊕B A plus B A plus B plus 1

LHLH B A • B plus (A + B

) A • B plus (A + B) plus 1

H H L H A • B A • B minus 1 A • B

L L H H Logic “1” A plus A (2 × A) A plus A (2 × A) plus 1

HLHHA + B

A plus (A + B) A plus (A+B) plus 1

LHHH A + B A plus (A + B

)A plus (A+B) plus 1

HHHH A A minus 1 A

Loading...

Loading...