Fairchild Semiconductor 74F161ASJ, 74F161ASCX, 74F161ASC, 74F161APC, 74F163ASJX Datasheet

...

74F161A • 74F163A

Synchronous Presettable Binary Counter

74F161A • 74F163A Synchronous Presettable Binary Counter

April 1988

Revised July 1999

General Description

The 74F161A and 74F 163A are high-speed synchr onous

modulo-16 binary counte rs. They are synchronously presettable for application in progr ammab le divide rs and have

two types of Count Enable input s plus a Terminal Count

output for versatility in forming synchronous multi-stage

counters. The 74F161A has an asynchronous MasterReset input that overr ides all other inputs and f orces the

outputs LOW. The 74F163A has a Synchronous Reset

input that overrides counting and parallel loading and

allows the outputs to be sim ultaneously reset on the r ising

edge of the clock. The 74 F161A and 74F163A are hig hspeed versions of the 74F161 and 74F163.

Features

■ Synchronous counting and loading

■ High-speed synchronous expan si on

■ Typical count frequency of 120 MHz

Ordering Code:

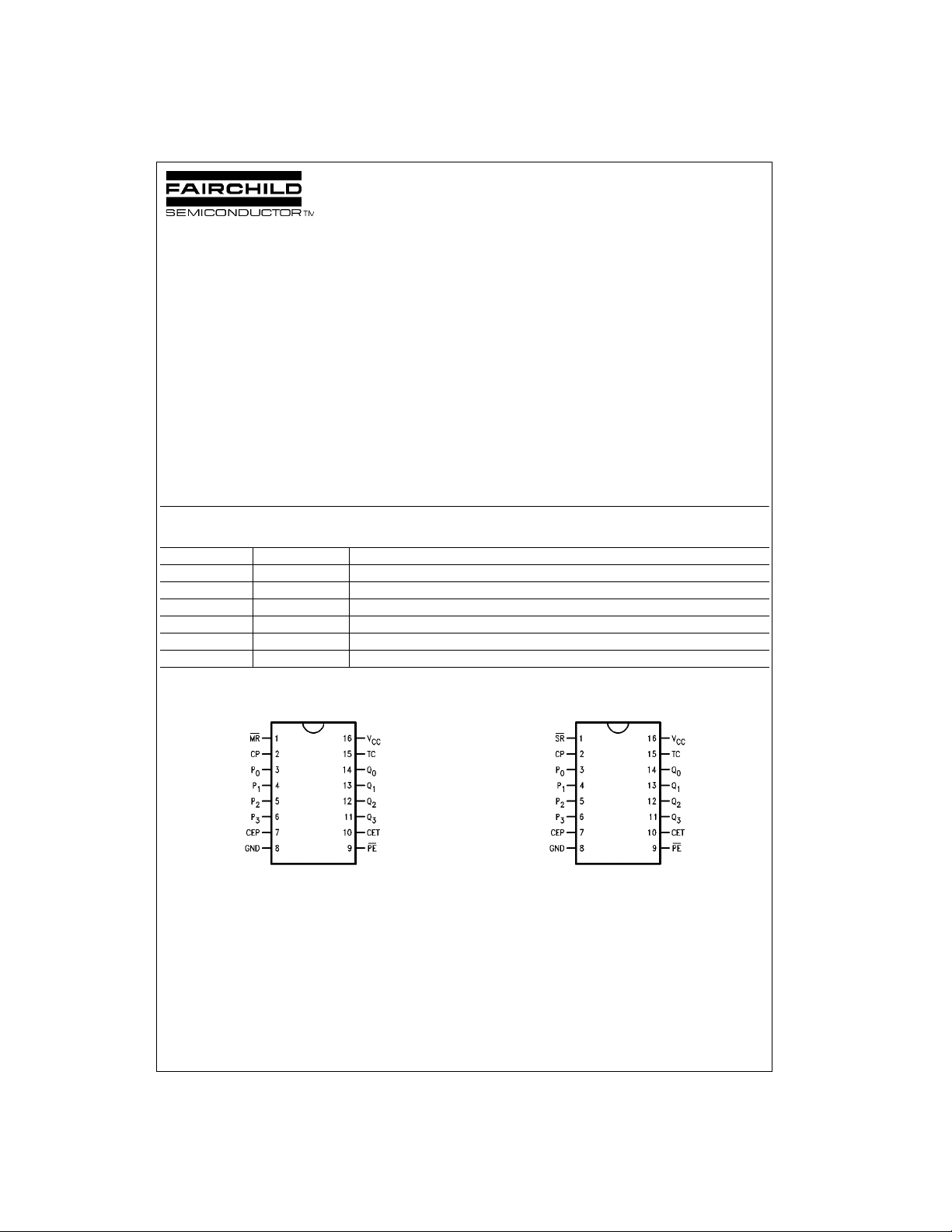

Order Number Package Number Package Description

74F161ASC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F161ASJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F161APC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

74F163ASC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F163ASJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F163APC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

Connection Diagrams

74F161A 74F163A

© 1999 Fairchild Semiconductor Corporation DS009486 www.fairchildsemi.com

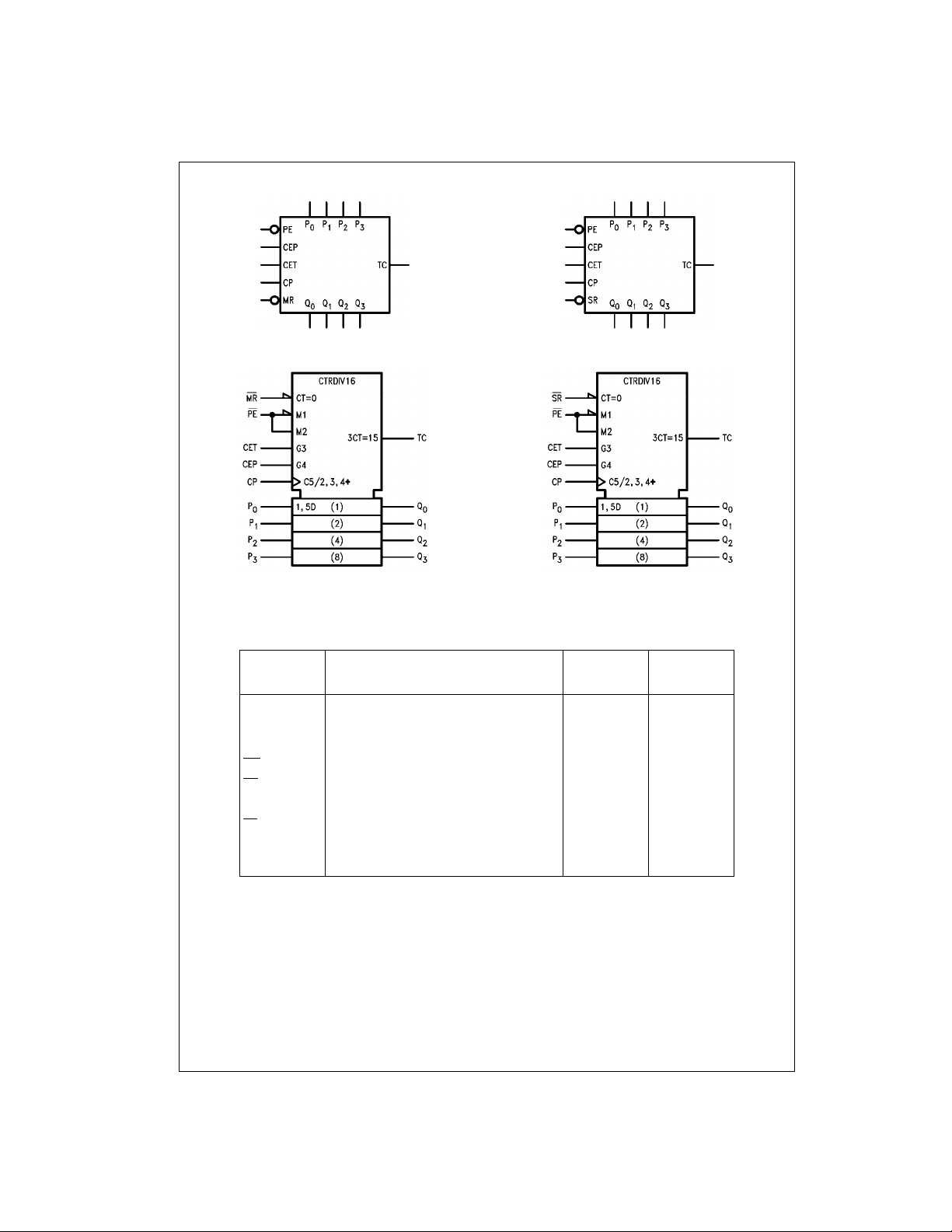

Logic Symbols

74F161A • 74F163A

74F161A

IEEE/IEC

74F163A

IEEE/IEC

74F161A

Unit Loading/Fan Out

Pin Names Description

CEP Count Enable Parallel Input 1.0/1.0 20 µA/−0.6 mA

CET Count Enable Trickle Input 1.0/2.0 20 µA/−1.2 mA

CP Clock Pulse Input (Active Rising Edge) 1.0/1.0 20 µA/−0.6 mA

(74F161A) Asynchronous Master Reset Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

MR

(74F163A) Synchronous Reset Input (Active LOW) 1.0/2.0 20 µA/−1.2 mA

SR

P

0–P3

PE

Q

0–Q3

TC Terminal Count Output 50/33.3 −1 mA/20 mA

Parallel Data Inputs 1.0/1.0 20 µA/−0.6 mA

Parallel Enable Input (Active LOW) 1.0/2.0 20 µA/−1.2 mA

Flip-Flop Outputs 50/33.3 −1 mA/20 mA

74F163A

U.L.

HIGH/LOW

Input I

Output I

IH/IIL

OH/IOL

www.fairchildsemi.com 2

Functional Description

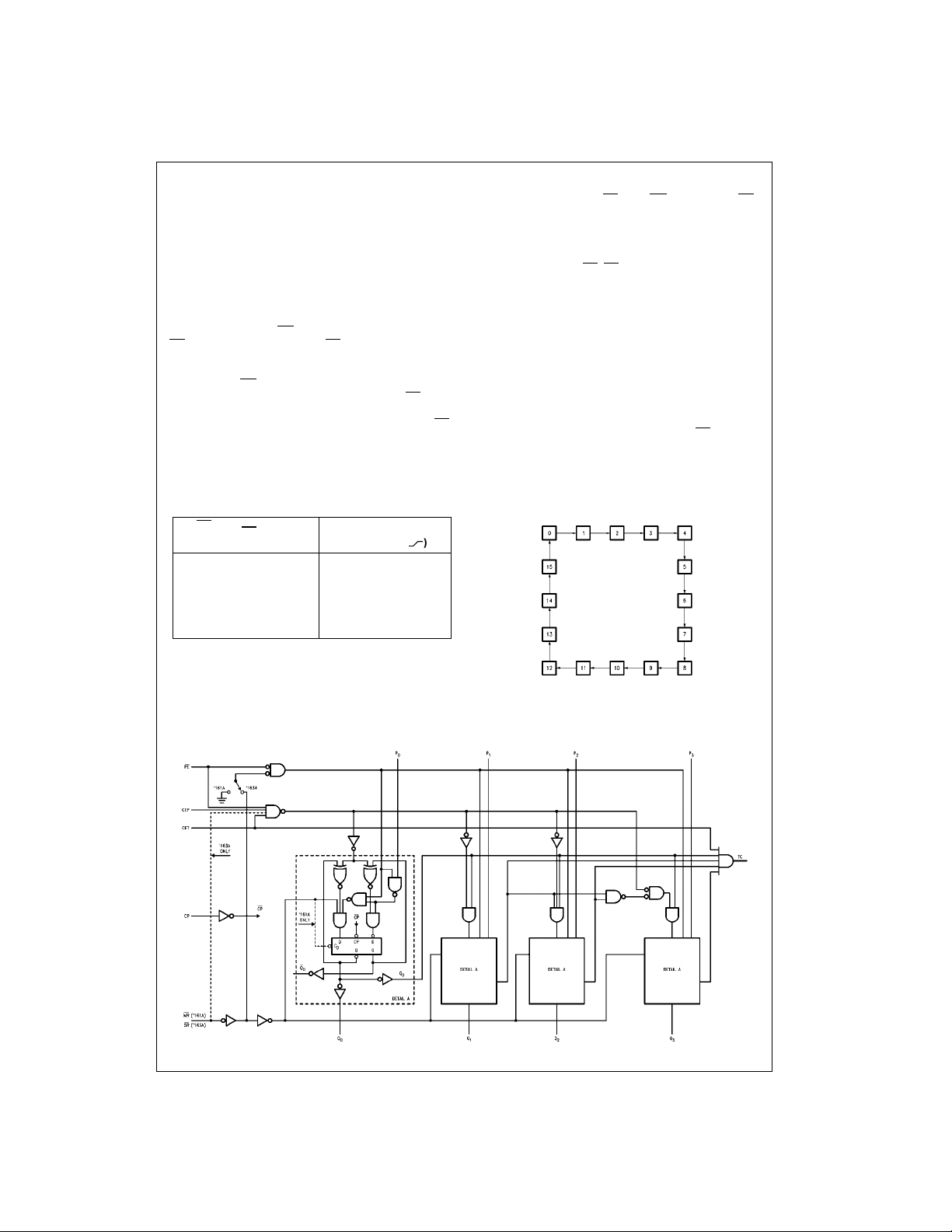

The 74F161A and 74F163A count in modulo-16 binary

sequence. From state 15 (HHHH) they increment to state 0

(LLLL). The clock inputs of all flip-flops are driven in parallel through a clock buffer. Thus all changes of the Q outputs

(except due to Master Rese t of the 74F161A) occur as a

result of, and synchron ous with, the LOW-to-H IGH transition of the CP inpu t signal. The circuits hav e four fundamental modes of operation, in order of precedence:

asynchronous reset (74F161A), synchronous reset

(74F163A), parallel load, count-up and hold. Five control

inputs—Master Reset (MR

, 74F163A), Parallel Enable (PE), Count Enable Paral-

(SR

lel (CEP) and Count Enable Trickle (CET)—determine the

mode of operation, as show n in the Mode Select Table. A

LOW signal on MR

nously forces all out puts LOW. A LOW sign al on SR

rides counting and parallel loading and allows all outputs to

go LOW on the next rising edge of CP. A LOW signal on PE

overrides counting an d allows information on the Parallel

) inputs to be loaded i nto t he flip -flops o n the n ext

Data (P

n

, 74F161A), Synchronous Reset

overrides all other inputs and asynchro-

over-

rising edge of CP. With PE

(74F163A) HIGH, CEP and CET permit counting when

both are HIGH. Conversely, a LOW signal on either CEP or

CET inhibits counting.

The 74F161A and 74F163A use D-type edge triggered flipflops and changing the SR

the CP is in either state does not cause errors, pro vided

that the recommended set up and hold times, wit h respect

to the rising edge of CP, are observed.

The Terminal Count (TC) output is HIGH when CET is

HIGH and th e c o un t er is i n s ta te 15 . To impl em en t sy n chr o nous multi-stage counters, the TC outputs can be used

with the CEP and CET in pu ts in t w o d ifferent w ays. Please

refer to the 74F568 data sheet. The TC output is subject to

decoding spikes due to internal race conditions and is

therefore not recommended for use as a clock or asynchronous reset for flip-flops, counters or registers.

Logic Equations: Count Enable = CEP • CET • PE

and MR ('F161A) or SR

, PE, CEP and CET inputs when

TC = Q0 • Q1 • Q2 • Q3 • CET

74F161A • 74F163A

Mode Select Table

SR

(Note 1)

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Note 1: For 74F163A only

PE

L X X X Reset (Clear)

H L X X Load (P

H H H H Count (Increment)

H H L X No Change (Hold)

H H X L No Change (Hold)

CET

CE

P

Block Diagram

Action on the Rising

Clock Edge (

n→Qn

)

)

State Diagram

3 www.fairchildsemi.com

Loading...

Loading...