Fairchild Semiconductor 74F153SJX, 74F153SJ, 74F153SCX, 74F153SC, 74F153PC Datasheet

© 1999 Fairchild Semiconductor Corporation DS009482 www.fairchildsemi.com

April 1988

Revised July 1999

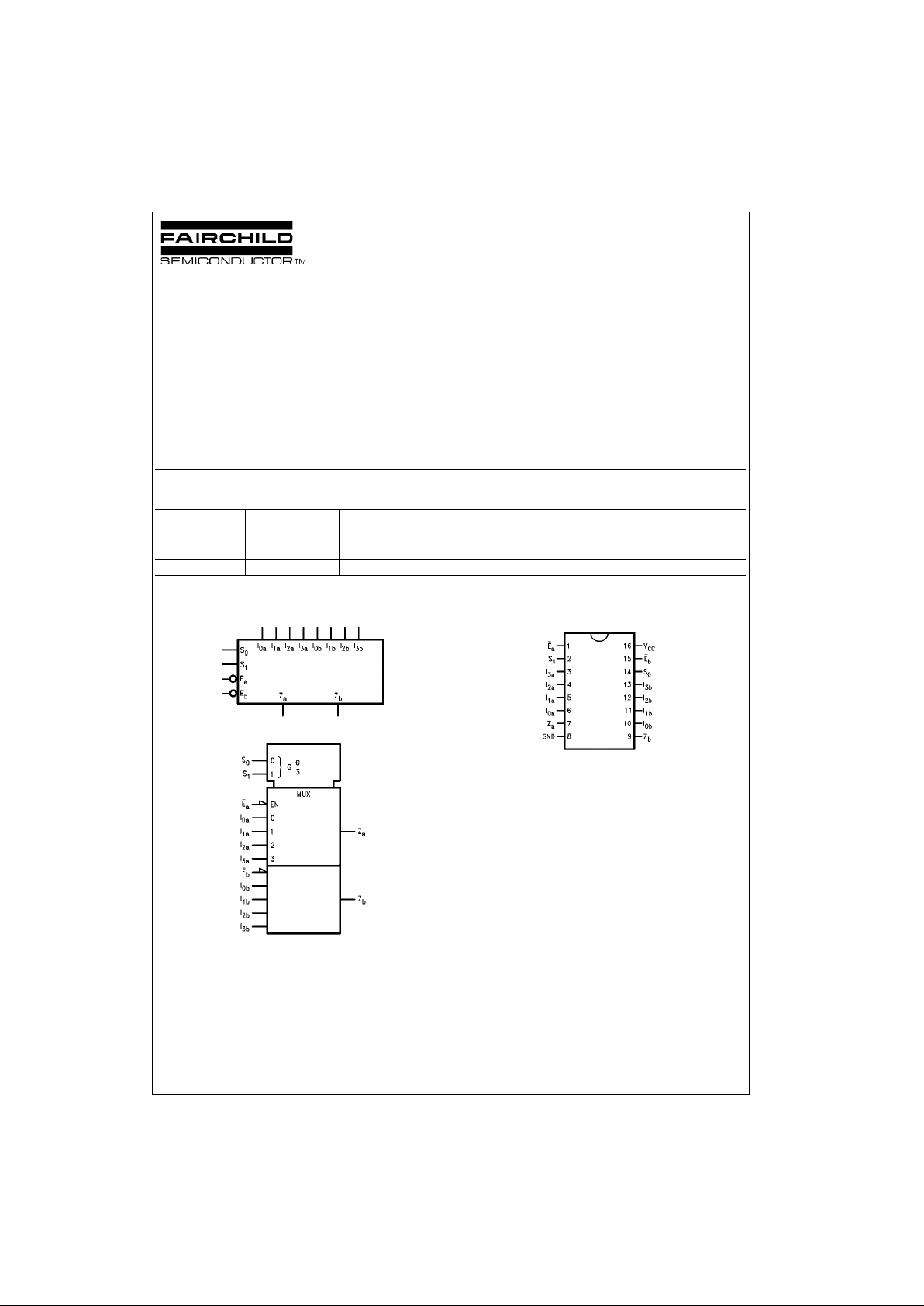

74F153 Dual 4-Input Multiplexer

74F153

Dual 4-Input Multiplexer

General Description

The F153 is a high-speed dual 4-input multiplexer with

common select inputs and individual enable inputs for each

section. It can select two lines of data fro m four sources.

The two buffered outputs present data in the true (noninverted) form. In addition to multiplexer operation, the

F153 can generate any two functions of three variables.

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

Logic Symbols

IEEE/IEC

Connection Diagram

Order Number Package Number Package Description

74F153SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

74F153SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F153PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

74F153

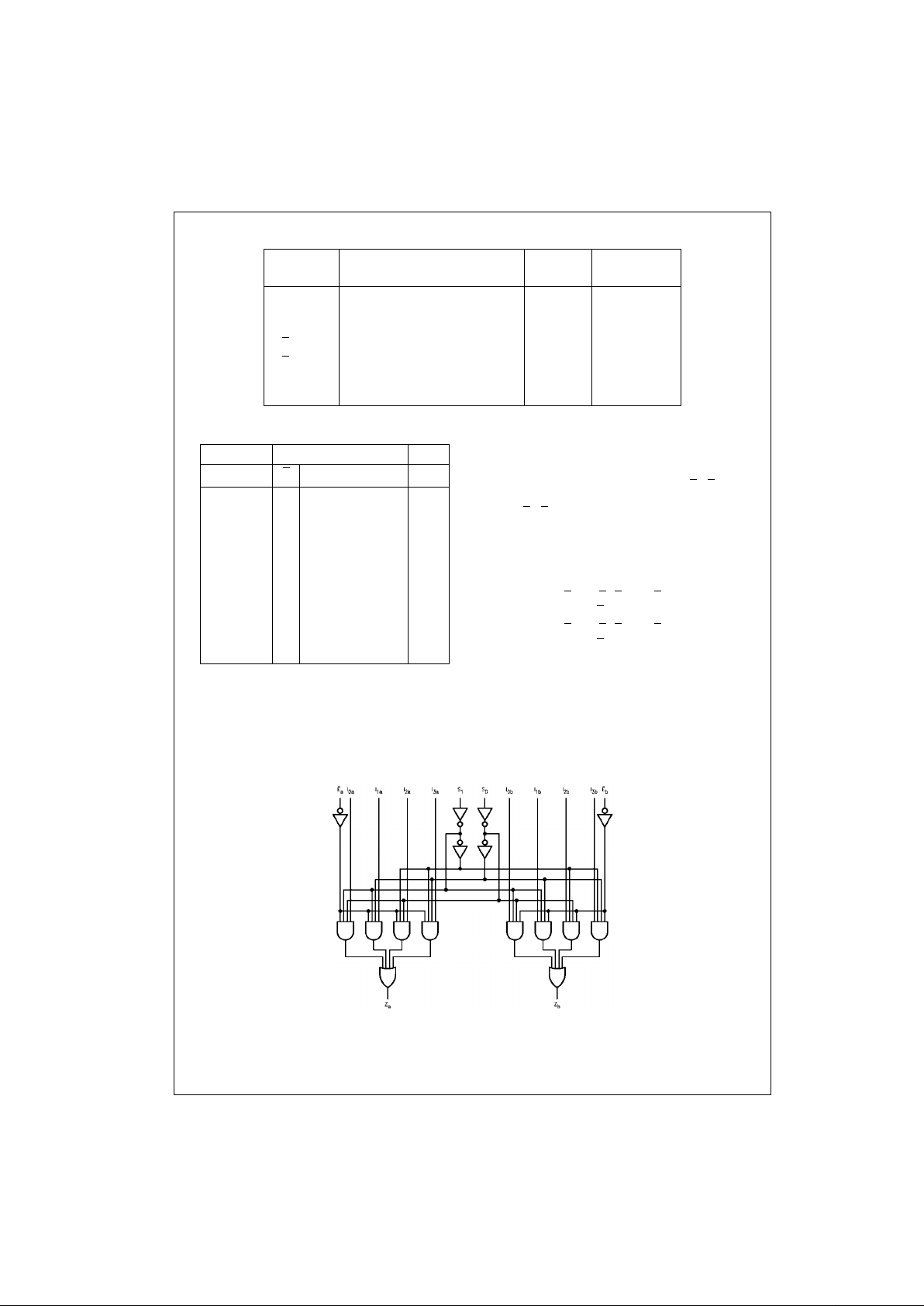

Unit Loading/Fan Out

Truth Table

H = HIGH Voltage Level

L = LOW

X = Immaterial

Functional Description

The F153 is a d ua l 4- in pu t mu ltiplexer. It can se l ect t wo b i t s

of data from up to four so urces under the control of the

common Select inputs (S

0

, S1). The two 4-input multiplexer

circuits have individual active LOW Enables (E

a

, Eb) which

can be used to strobe the outputs independently. When the

Enables (E

a

, Eb) are HIGH, the corresponding outputs (Za,

Z

b

) are forced LOW. The F153 is the logic impleme ntation

of a 2-pole, 4-position switch, where the position of the

switch is determined by the logic levels s upplied to the two

Select inputs. The logic e quations for the outputs are as

follows:

Z

a

= Ea•(I0a•S1•S0 + I1a•S1•S0 +

I

2a•S1•S0

+ I3a•S1•S0)

Z

b

= Eb•(I0b•S1•S0 + I1b•S1•S0 +

I

2b•S1•S0

+ I3b•S1•S0)

The F153 can be used to mo ve da ta fr om a gro up of registers to a common output bus. The particular reg ister from

which the data came would be det ermined by the state of

the Select inputs. A less obvious appl ication is as a function generator. The F153 can generate two functions of

three variables. This is useful for implementing highly irregular random logic.

Logic Diagram

Please note that this diagram is provided o nly f or t he understanding of lo gic operations and should not be used to estimate propagation delays.

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

I0a–I

3a

Side A Data Inputs 1.0/1.0 20 µA/−0.6 mA

I

0b–I3b

Side B Data Inputs 1.0/1.0 20 µA/−0.6 mA

S

0

, S

1

Common Select Inputs 1.0/1.0 20 µA/−0.6 mA

E

a

Side A Enable Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

E

b

Side B Enable Input (Active LOW) 1.0/1.0 20 µA/−0.6 mA

Z

a

Side A Output 50/33.3 −1 mA/20 mA

Z

b

Side B Output 50/33.3 −1 mA/20 mA

Select Inputs Inputs (a or b) Output

S

0

S1E I0I1I2I

3

Z

X X HXXXX L

L L LLXXX L

L L LHXXX H

H L LXLXX L

HLLXHXXH

LHLXXLXL

LHLXXHXH

H H LXXXL L

H H LXXXH H

Loading...

Loading...