Fairchild Semiconductor 74ABT377CSJX, 74ABT377CSJ, 74ABT377CSCX, 74ABT377CMTCX, 74ABT377CMTC Datasheet

...

© 1999 Fairchild Semiconductor Corporation DS011550 www.fairchildsemi.com

January 1993

Revised November 1999

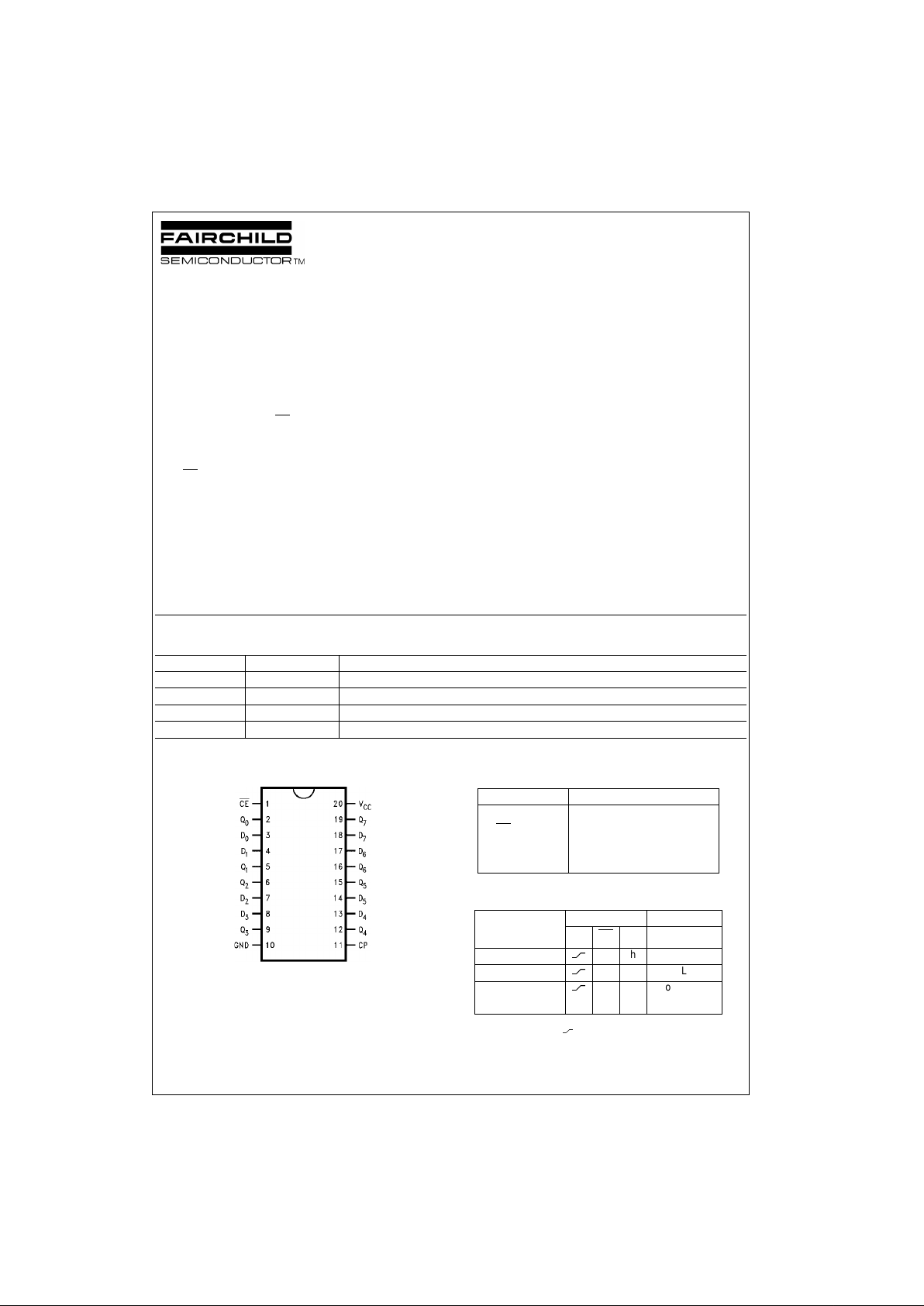

74ABT377 Octal D-Type Flip-Flop with Clock Enable

74ABT377

Octal D-T ype Flip-Flop with Clock Enable

General Description

The ABT377 has eight edge-triggered, D-type flip-flops

with individual D inputs and Q outputs . The common buffered Clock (CP) input loads all flip-flops simultaneously

when the Clock Enable (CE

) is LOW.

The register is fully edge-t riggered. The state of each D

input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop’s Q output.

The CE

input must be stable only one setup time prior to

the LOW-to-HIGH clock transition for predictable operation.

Features

■ Clock enable for address and data synchronization

applications

■ Eight edge-triggered D-typ e flip-fl o ps

■ Buffered common clock

■ See ABT273 for master reset version

■ See ABT373 for transparent latch version

■ See ABT374 for 3-STATE version

■ Output sink capability of 64 mA, source capability

of 32 mA

■ Guarante ed latchup prote ction

■ High impedance glitch free bus loading during entire

power up and power down cycle

■ Non-destructive hot insertion capability

■ Disable time less than enable time to avoid bus

contention

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram Pin Descriptions

Truth Table

H = HIGH Voltage Level L = LOW Voltage Level

X = Immaterial

= LOW-to-HIGH Clock Transition

h = HIGH Voltage Level one setup time prior to the

LOW-to-HIGH Clock Transition

I = LOW Voltage Level one se tu p t im e prior to the

LOW-to-HIGH Clock Transition

Order Number Package Number Package Description

74ABT377CSC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide Body

74ABT377CSJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74ABT377CMSA MSA20 20-Lead Shrink Small Outline Package (SSOP), EIAJ TYPE II, 5.3mm Wide

74ABT377CMTC MTC20 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Pin Names Descriptions

D

0–D7

Data Inputs

CE

Clock Enable (Active LOW)

CP Clock Pulse Input

Q

0–Q7

Data Outputs

Operating Mode Inputs Output

CP

CE

D

n

Q

n

Load “1”

Ih H

Load “0”

II L

Hold

h X No Change

(Do Nothing) X H X No Change

www.fairchildsemi.com 2

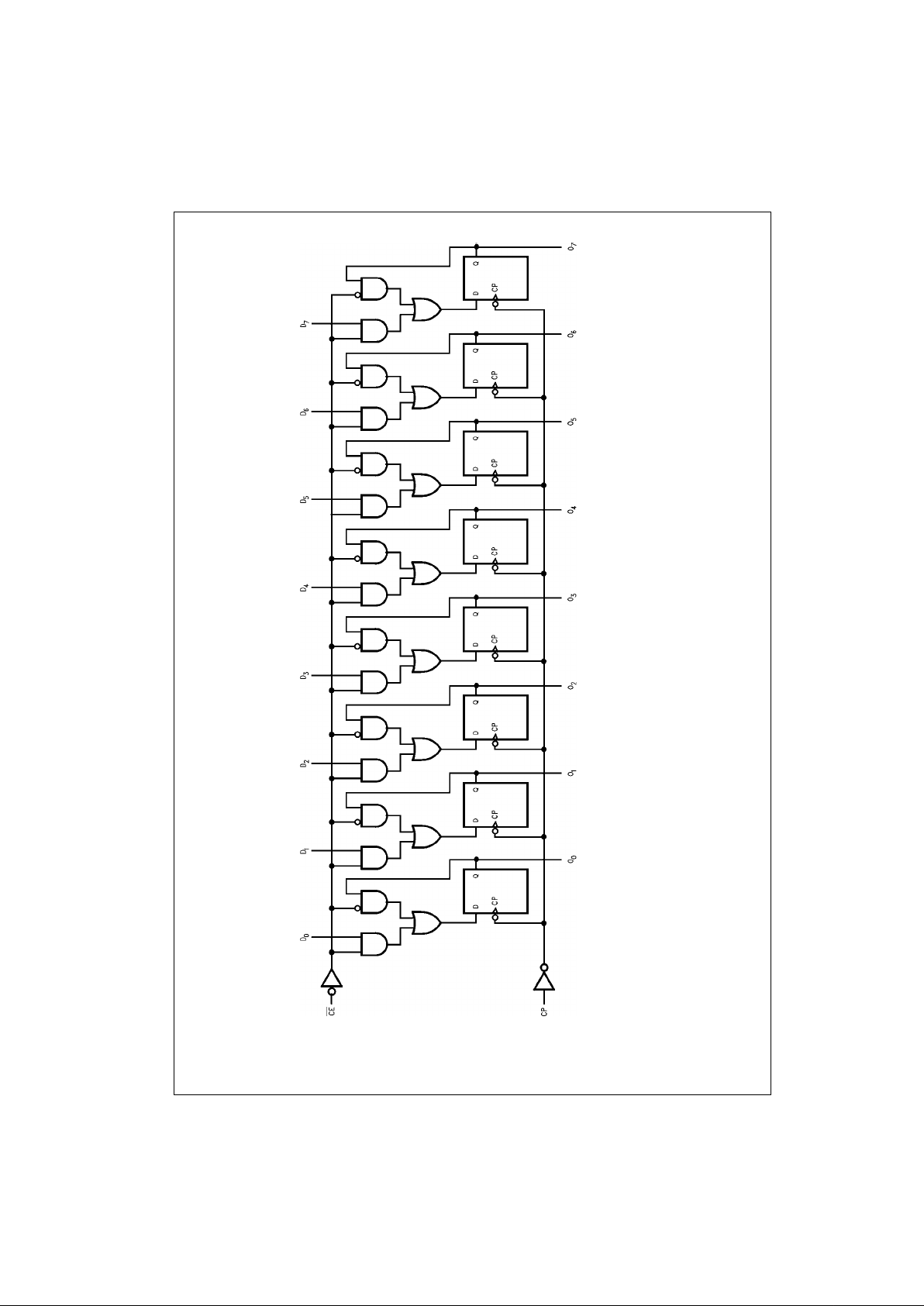

74ABT377

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

3 www.fairchildsemi.com

74ABT377

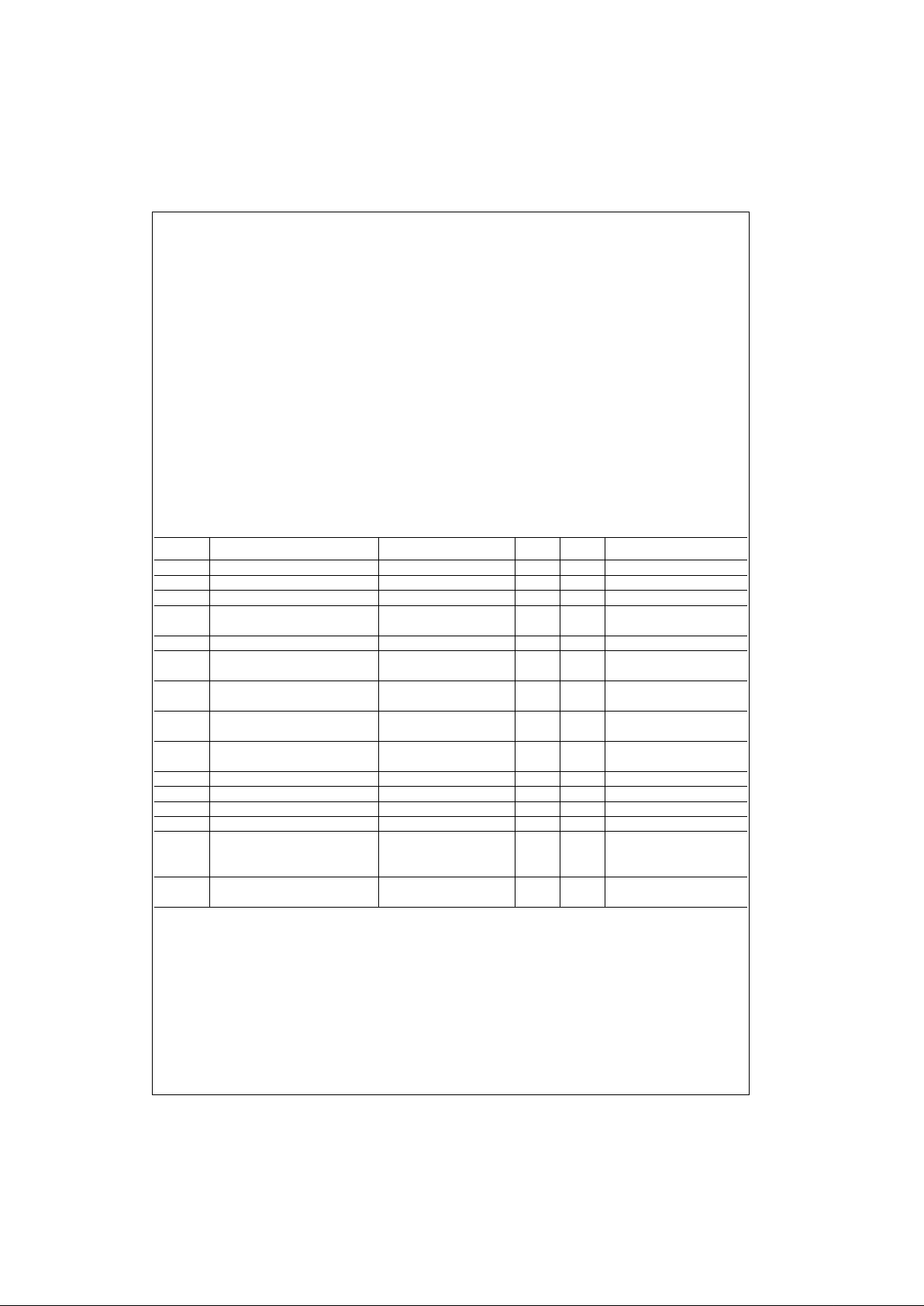

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

Note 1: Absolute maximum ratings are values beyond which the device

may be damaged or have its useful life impaired . Functional operation

under these conditions is not implied.

Note 2: Either voltage lim it or c urrent limit is sufficient to protect inputs

DC Electrical Characteristics

Note 3: Guaranteed but not tested.

Note 4: For 8 bits toggling, I

CCD

< 0.5 mA/MHz.

Storage Temperature −65°C to +150°C

Ambient Temperature under Bias −55°C to +125°C

Junction Temperature under Bias −55°C to +150°C

V

CC

Pin Potential to Ground Pin −0.5V to +7.0V

Input Voltage (Note 2) −0.5V to +7.0V

Input Current (Note 2) −30 mA to +5.0 mA

Voltage Applied to Any Output

in the Disabled or

Power-OFF State −0.5V to +4.75V

in the HIGH State −0.5V to V

CC

Current Applied to Output

in LOW State (Max) Twice the rated I

OL

(mA)

DC Latchup Source Current −500 mA

(Across Comm Operating Range)

Over Voltage Latchup V

CC

+ 4.5V

Free Air Ambient Temperature −40°C to +85°C

Supply Voltage +4.5V to +5.5V

Minimum Input Edge Rate (∆V/∆t)

Data Input 50 mV/ns

Enable Input 20 mV/ns

Symbol Parameter Min Typ Max Units

V

CC

Conditions

V

IH

Input HIGH Voltage 2.0 V Recognized HIGH Signal

V

IL

Input LOW Voltage 0.8 V Recognized LOW Signal

V

CD

Input Clamp Diode Voltage −1.2 V Min IIN = −18 mA

V

OH

Output HIGH Voltage 2.5

VMin

IOH = −3 mA

2.0 IOH = −32 mA

V

OL

Output LOW Voltage 0.55 V Min IOL = 64 mA

I

IH

Input HIGH Current 1

µAMax

VIN = 2.7V (Note 3)

1V

IN

= V

CC

I

BVI

Input HIGH Current

7 µAMaxVIN = 7.0V

Breakdown Test

I

IL

Input LOW Current −1

µAMax

VIN = 0.5V (Note 3)

−1V

IN

= 0.0V

V

ID

Input Leakage Test 4.75 V 0.0 IID = 1.9 µA

All Other Pins Grounded

I

OS

Output Short-Circuit Current −100 −275 mA Max V

OUT

= 0.0V

I

CEX

Output HIGH Leakage Current 50 µAMaxV

OUT

= V

CC

I

CCH

Power Supply Current 50 µA Max All Outputs HIGH

I

CCL

Power Supply Current 30 mA Max All Outputs LOW

I

CCT

Maximum ICC/Input Outputs Enabled VI = VCC − 2.1V

1.5 mA Max Data Input VI = VCC − 2.1V

All Others at VCC or GND

I

CCD

Dynamic I

CC

No Load 0.3 mA/ Max Outputs Open (Note 4)

MHz One bit Toggling, 50% Duty Cycle

Loading...

Loading...