Fairchild FAN5361 service manual

June 2011

FAN5361

6MHz, 600mA / 750mA Synchronous Buck Regulator

FAN5361 — 6MHz, 600mA / 750mA Synchronous Buck Regulator

Features

6MHz Fixed-Frequency Operation

35µA Typical Quiescent Current

Best-in-Class Load Transient Response

Best-in-Class Efficiency

600mA or 750mA Output Current Capability

2.3V to 5.5V Input Voltage Range

1.0 to 1.90V Fixed Output Voltage

Low Ripple Light-Load PFM Mode

Forced PWM and External Clock Synchronization

Internal Soft-Start

Input Under-Voltage Lockout (UVLO)

Thermal Shutdown and Overload Protection

6-bump WLCSP, 0.4mm Pitch

6-pin 2 x 2mm UMLP

Applications

Cell Phones, Smart Phones

Tablets, Netbooks

3G, LTE, WiMAX™, WiBro

Gaming Devices, Digital CamerasDC/DC Micro Modules

®

, Ultra-Mobile PCs

®

, and WiFi® Data Cards

Description

The FAN5361 is a 600mA or 750mA, step-down, switching

voltage regulator that delivers a fixed output from a 2.3V to

5.5V input voltage supply. Using a proprietary architecture

with synchronous rectification, the FAN5361 is capable of

delivering a peak efficiency of 92%, while maintaining

efficiency over 80% at load currents as low as 1mA.

The regulator operates at a nominal fixed frequency of

6MHz, which reduces the value of the external components

to 470nH for the output inductor and 4.7µF for the output

capacitor. The PWM modulator can be synchronized to an

external frequency source.

At moderate and light loads, pulse frequency modulation is

used to operate the device in power-save mode with a

typical quiescent current of 35µA. Even with such a low

quiescent current, the part exhibits excellent transient

response during large load swings. At higher loads, the

system automatically switches to fixed-frequency control,

operating at 6MHz. In shutdown mode, the supply current

drops below 1µA, reducing power consumption. For

applications that require minimum ripple or fixed frequency,

PFM mode can be disabled using the MODE pin.

The FAN5361 is available in 6-bump, 0.4mm pitch, WaferLevel Chip-Scale Package (WLCSP) and a 6-lead 2 x 2mm

ultra-thin MLP package (UMLP).

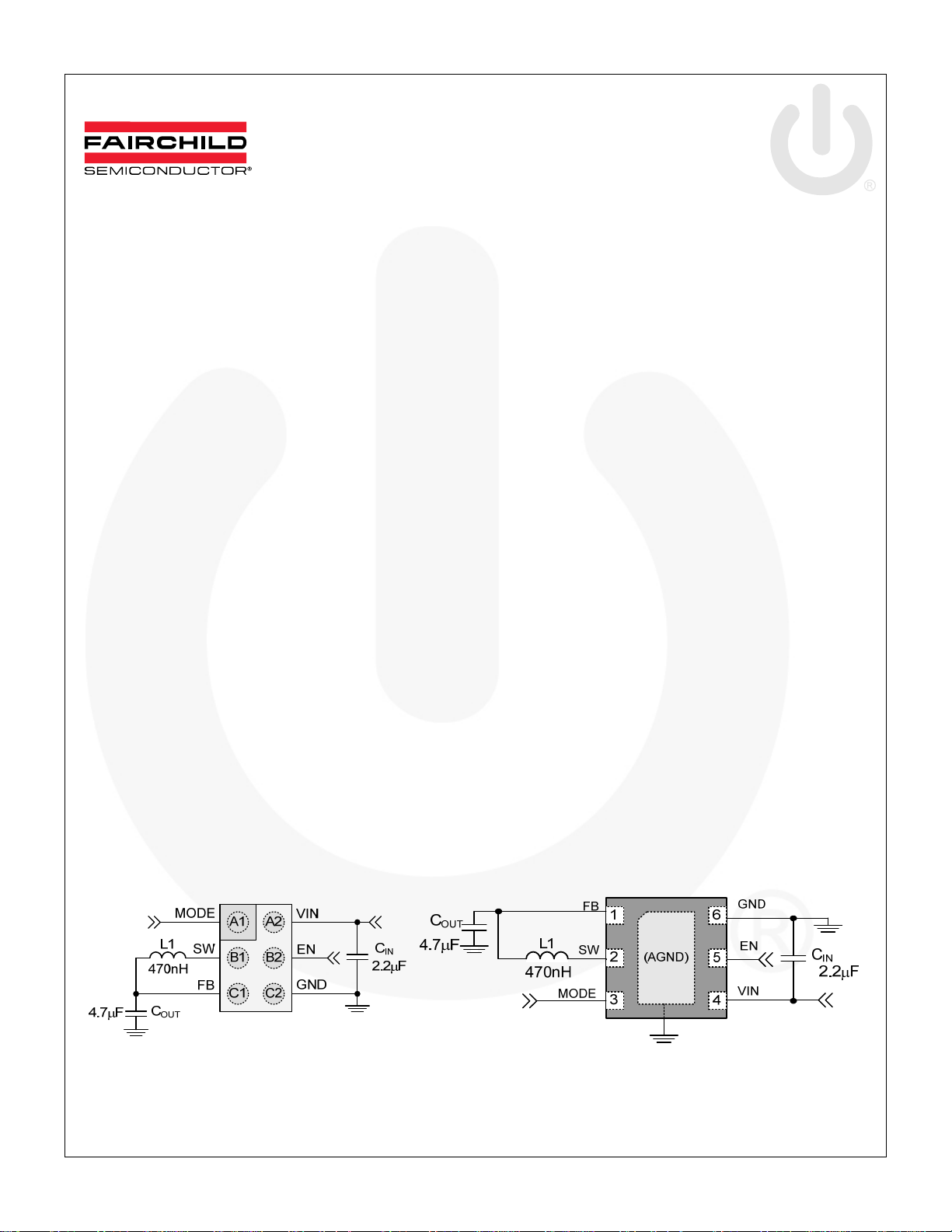

Typical Applications

Figure 1. Typical Applications

All trademarks are the property of their respective owners.

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5361 • Rev. 1.1.2

Ordering Information

FAN5361 — 6MHz, 600mA / 750mA Synchronous Buck Regulator

Part Number

FAN5361UC123X 1.233V

FAN5361UC182X 1.820V

FAN5361UC19X 1.900V

FAN5361UMP123X 1.233V

FAN5361UMP15X 1.500V

FAN5361UMP182X 1.820V

Note:

1. Other voltage options available on request. Contact a Fairchild representative.

Output

Voltage

(1)

Package Temperature Range Packing

WLCSP-6, 0.4mm Pitch

6-Lead, 2 x 2mm UMLP

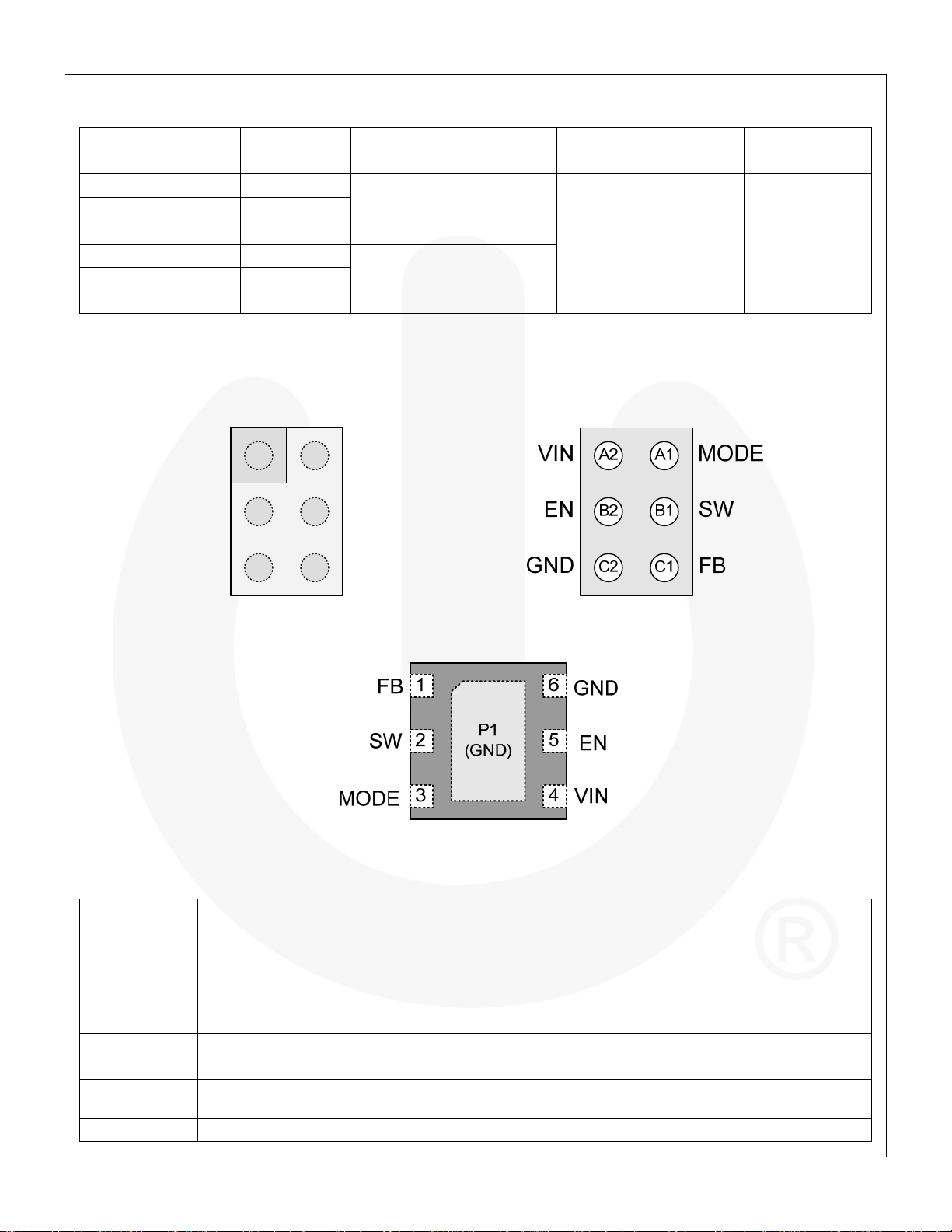

Pin Configurations

MODE

SW

FB

A1

B1

C1

A2

B2

C2

VIN

EN

GND

–40 to +85°C Tape and Reel

Figure 2. WLCSP, Bumps Facing Down Figure 3. WLCSP, Bumps Facing Up

Pin Definitions

Pin #

Name Description

WLCSP UMLP

A1 3 MODE

B1 2 SW

C1 1 FB

C2 6 GND

B2 5 EN

A2 4 VIN

Figure 4. UMLP, Leads Facing Down

MODE. Logic 1 on this pin forces the IC to stay in PWM mode. A logic 0 allows the IC to

automatically switch to PFM during light loads. The regulator also synchronizes its switching

frequency to four times the frequency provided on this pin. Do not leave this pin floating.

Switching Node. Connect to output inductor.

Feedback / V

Ground. Power and IC ground. All signals are referenced to this pin.

Enable. The device is in shutdown mode when voltage to this pin is <0.4V and enabled when

>1.2V. Do not leave this pin floating.

Input Voltage. Connect to input power source.

. Connect to output voltage.

OUT

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5361 • Rev. 1.1.2 2

FAN5361 — 6MHz, 600mA / 750mA Synchronous Buck Regulator

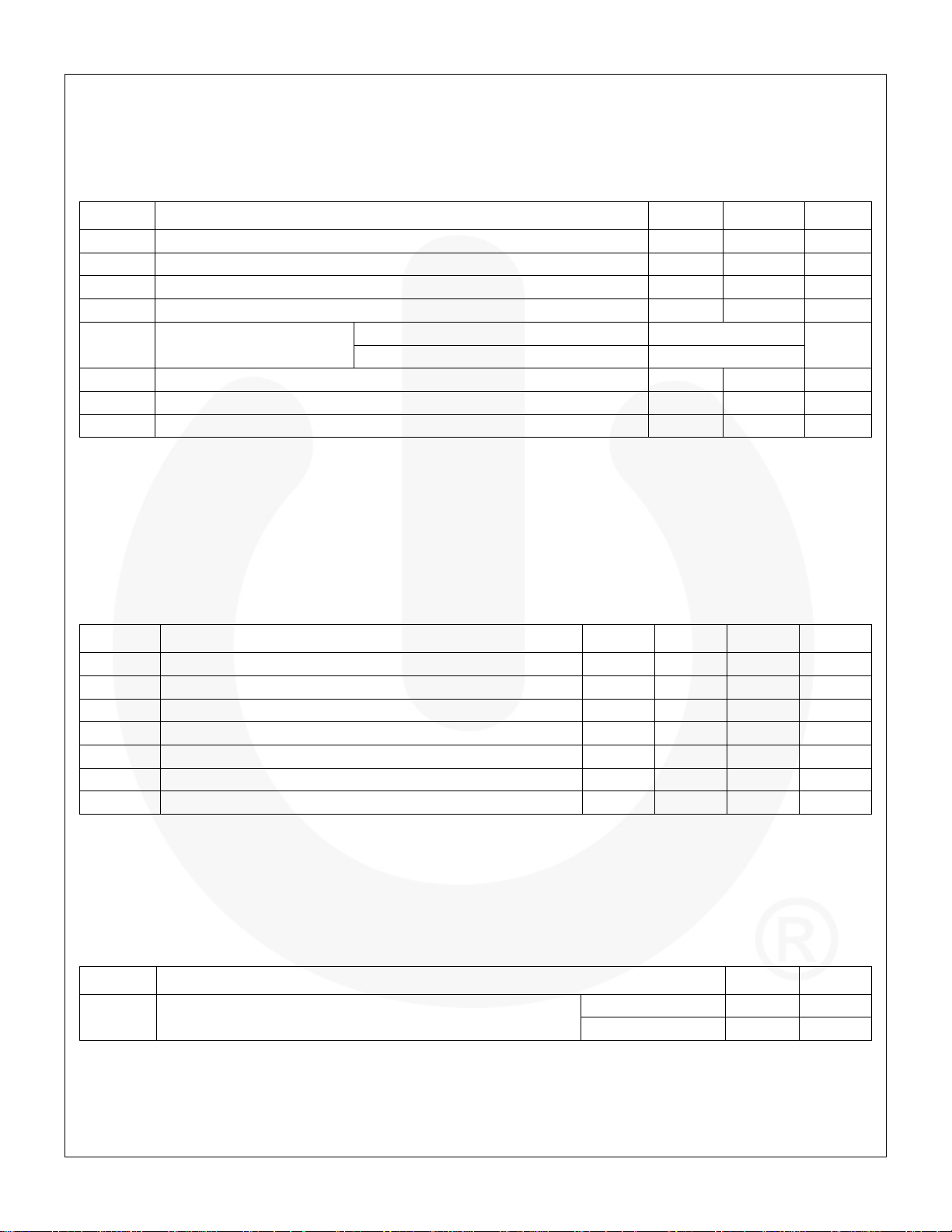

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above

the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended

exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings

are stress ratings only.

Symbol Parameter Min. Max. Unit

VIN Input Voltage –0.3 7.0 V

VSW Voltage on SW Pin –0.3 VIN + 0.3

V

EN and MODE Pin Voltage –0.3 VIN + 0.3

CTRL

Other Pins –0.3 VIN + 0.3

ESD

Electrostatic Discharge

Protection Level

Human Body Model per JESD22-A114 4.0

Charged Device Model per JESD22-C101 1.5

TJ Junction Temperature –40 +150 °C

T

Storage Temperature –65 +150 °C

STG

TL Lead Soldering Temperature, 10 Seconds +260 °C

Note:

2. Lesser of 7V or VIN+0.3V.

(2)

(2)

(2)

V

V

V

kV

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating

conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding

them or designing to Absolute Maximum Ratings.

Symbol Parameter Min. Typ. Max. Unit

VCC Supply Voltage Range 2.3 5.5 V

I

Output Current 0 600 mA

OUT

L Inductor 0.47 µH

CIN Input Capacitor 2.2 µF

C

Output Capacitor 1.6 4.7 12.0 µF

OUT

TA Operating Ambient Temperature –40 +85 °C

TJ Operating Junction Temperature –40 +125 °C

Thermal Properties

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 1s2p

boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature T

given ambient temperate T

.

A

Symbol Parameter Typical Unit

JA

Junction-to-Ambient Thermal Resistance

WLCSP 150 °C/W

UMLP 49 °C/W

J(max)

at a

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5361 • Rev. 1.1.2 3

FAN5361 — 6MHz, 600mA / 750mA Synchronous Buck Regulator

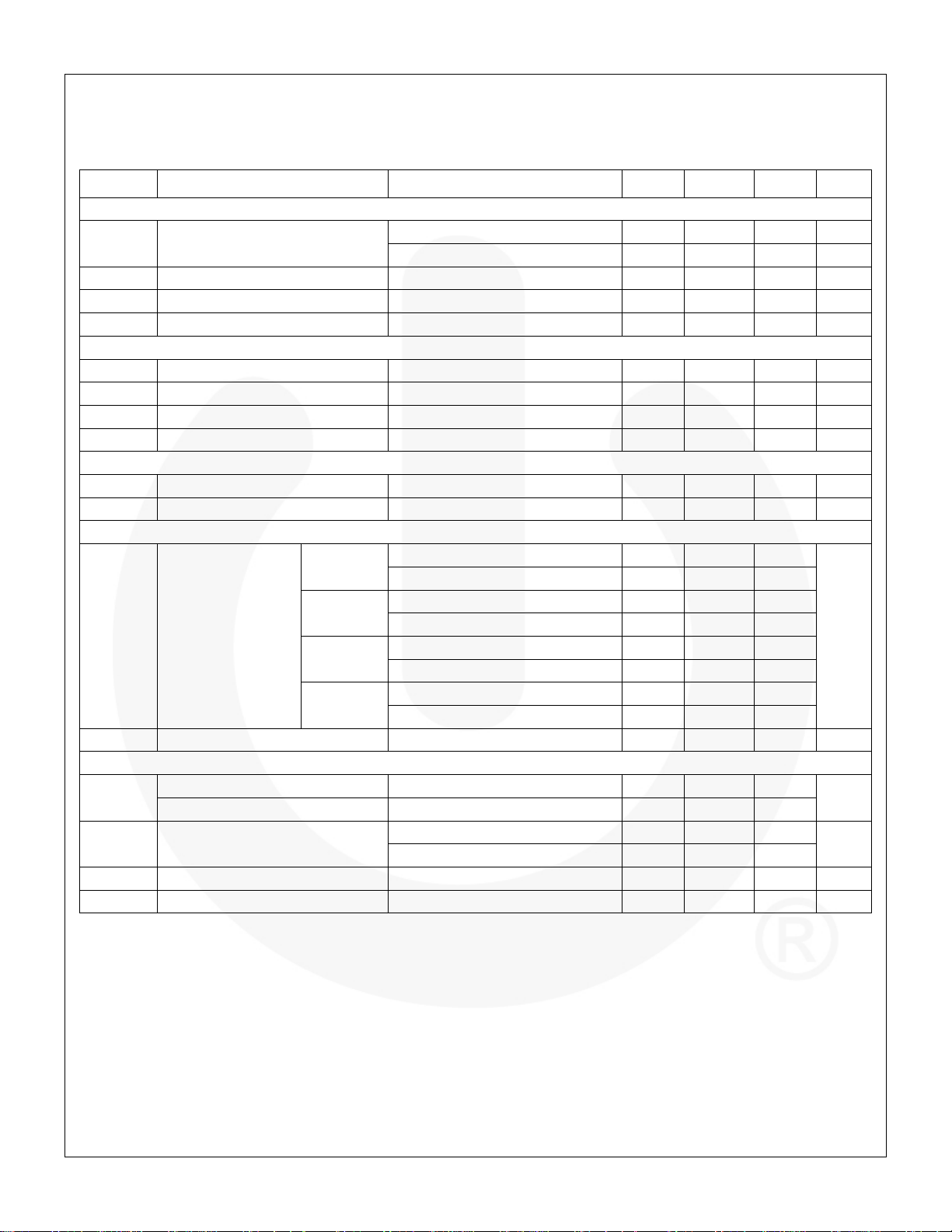

Electrical Characteristics

Minimum and maximum values are at VIN = VEN = 2.3V to 5.5V, V

Figure 1, unless otherwise noted. Typical values are at T

= 25°C, VIN = VEN = 3.6V.

A

Symbol Parameter Conditions Min. Typ. Max. Unit

Power Supplies

IQ Quiescent Current

I

Shutdown Supply Current VIN = 3.6V, EN = GND 0.05 1.00 µA

(SD)

V

Under-Voltage Lockout Threshold Rising VIN 2.15 2.25 V

UVLO

V

Under-Voltage Lockout Hysteresis 150 mV

UVHYST

Logic Inputs: EN and MODE Pins

VIH Enable HIGH-Level Input Voltage 1.2 V

VIL Enable LOW-Level Input Voltage 0.4 V

V

Logic Input Hysteresis Voltage 100 mV

LHYST

IIN Enable Input Leakage Current Pin to VIN or GND 0.01 1.00 µA

Switching and Synchronization

fSW Switching Frequency

f

MODE Synchronization Range

SYNC

(3)

V

Regulation

1.900V

1.820V

VO

Output Voltage

Accuracy

1.500V

1.233V

tSS Soft-Start From EN Rising Edge 180 300 µs

Output Driver

R

DS(on)

I

LIM(OL)

T

TSD

T

HYS

PMOS On Resistance V

NMOS On Resistance VIN = VGS = 3.6V 225

PMOS Open-Loop Peak Current

Limit

(5)

Thermal Shutdown CCM Only 150 °C

Thermal Shutdown Hysteresis 15 °C

Notes:

3. Limited by the effect of t

minimum (see Figure 14 and Figure 15 in Typical Performance Characteristics).

OFF

4. Output voltage accuracy minimum: 1.862V for V

5. Refer to Operation Description and Typical Characteristics for closed-loop data.

No Load, Not Switching 35 55 µA

PWM Mode 6 mA

= 3.6V, TA = 25°C 5.4 6.0 6.6 MHz

(3)

IN

Square Wave at MODE Input 1.3 1.5 1.7 MHz

= 0 to 750mA

I

LOAD

PWM Mode

I

= 0 to 600mA 1.784 1.820 1.875

LOAD

PWM Mode 1.784 1.820 1.856

I

= 0 to 600mA 1.470 1.500 1.545

LOAD

PWM Mode 1.470 1.500 1.530

I

= 0 to 600mA 1.207 1.233 1.272

LOAD

PWM Mode 1.207 1.233 1.259

= VGS = 3.6V 350

IN

= 1.233V, 1.5V, 1.82V 900 1100 1250

V

OUT

V

= 1.9V 1180 1375 1550

OUT

2.7 to 5.5V on 1.9V option.

IN

= 0V (AUTO Mode), TA = -40°C to +85°C; circuit of

MODE

(4)

1.832 1.900 1.957

(4)

1.832 1.900 1.938

V

m

mA

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5361 • Rev. 1.1.2 4

100%

0

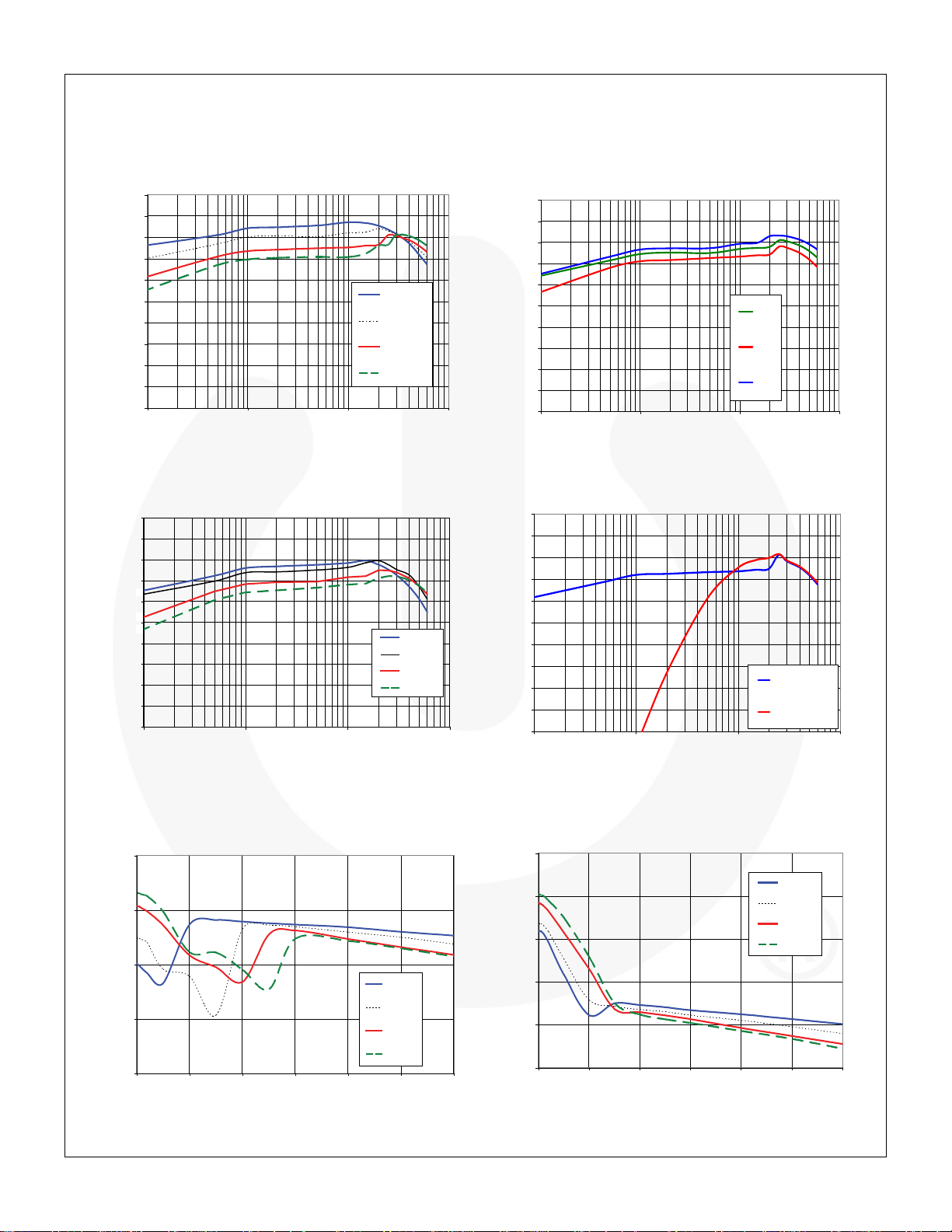

Typical Performance Characteristics

Unless otherwise noted, VIN = VEN = 3.6V, V

= 0V (AUTO Mode), V

MODE

= 1.82V, TA = 25°C.

OUT

FAN5361 — 6MHz, 600mA / 750mA Synchronous Buck Regulator

100%

95%

90%

85%

80%

75%

70%

Efficiency

65%

60%

55%

50%

1 10 100 1000

I

Output Current (mA)

LOAD

Auto 2.3VIN

Auto 2.7VIN

Auto 3.6VIN

Auto 4.2VIN

100%

95%

90%

85%

80%

75%

70%

Efficiency

65%

60%

55%

50%

1 10 100 1000

I

Output Current (mA)

LOAD

25C

85C

-30C

Figure 5. Efficiency vs. Load Current and Input Supply Figure 6. Efficiency vs. Load Current and Temperature

100%

95%

90%

85%

80%

75%

Efficiency

70%

65%

60%

55%

50%

1 10 100 1000

I

Output Current (mA)

LOAD

Figure 7. 1.233V

Efficiency vs. Load Current

OUT

VIN=2.3V

VIN=2.7V

VIN=3.6V

VIN=4.2V

95%

90%

85%

80%

75%

70%

Efficiency

65%

60%

55%

50%

1 10 100 1000

Output Current (mA)

I

LOAD

Auto PFM/PWM

Forced PWM

Figure 8. Efficiency, Auto PWM/PFM vs. Forced PWM

and Supply

1.84

1.83

(V)

1.82

OUT

V

1.81

1.80

0 100 200 300 400 500 60

Load Current (mA)

Figure 9. Load Regulation

VIN=2.3V

VIN=2.7V

VIN=3.6V

VIN=4.2V

1.248

1.243

1.238

(V)

OUT

V

1.233

1.228

1.223

0.00.10.20.30.40.50.6

Figure 10. 1.233V

VIN=2.3V

VIN=2.7V

VIN=3.6V

VIN=4.2V

I

Output Current (A)

LOAD

Load Regulation vs. Input Supply

OUT

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5361 • Rev. 1.1.2 5

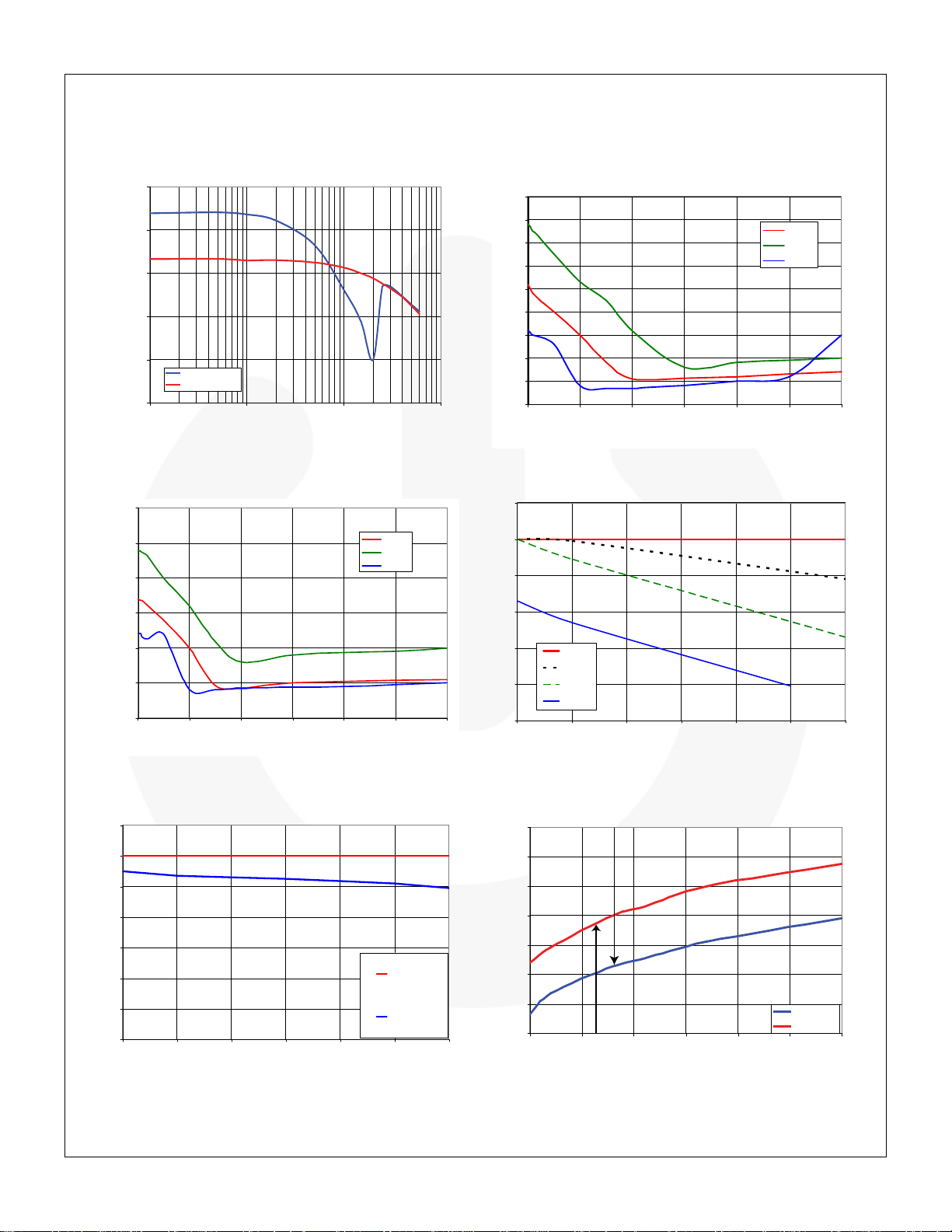

Typical Performance Characteristics (Continued)

Unless otherwise noted, VIN = VEN = 3.6V, V

= 0V (AUTO Mode), V

MODE

= 1.82V, TA = 25°C.

OUT

FAN5361 — 6MHz, 600mA / 750mA Synchronous Buck Regulator

1.830

1.825

1.820

(V)

OUT

V

1.815

1.810

1.805

Auto PWM/PFM

Forced PWM

1 10 100 1,000

I

Output Current (mA)

LOAD

Figure 11. Load Regulation, Auto PFM / PWM and

Forced PWM

30

25

20

15

Vout (mVpp)

10

5

0

0 100 200 300 400 500 600

Load Current (mA)

3.6VIN

5.5VIN

2.5VIN

45

40

35

30

25

20

Vout (mVpp)

15

10

5

0

0 100 200 300 400 500 600

Figure 12. 1.82V

7

FPWM Mode

6

5

4

3

Switching Frequency (MHz)

2

1

0 0.10.20.30.40.50.6

VIN>2.9V

VIN=2.7V

VIN=2.5V

VIN=2.3V

3.6VIN

5.5VIN

2.5VIN

Load Current (mA)

Peak-to-Peak Output Voltage Ripple

OUT

Load Current (A)

Figure 13. 1.233V

7

FPWM Mode

6

5

4

3

2

Switching Frequency (MHz)

1

0

0 0.1 0.2 0.3 0.4 0.5 0.6

Figure 15. 1.233V

Peak-to-Peak Output Voltage

OUT

Ripple

VIN>2.4V

VIN=2.3V

Load Current (A)

Effect of t

OUT

OFF(MIN)

on Reducing

Figure 14. Effect of t

on Reducing Switching

OFF(MIN)

Frequency

350

300

250

200

150

Load Cur rent (mA)

100

Always PWM

The switching mode changes

at these borders

Always PFM

50

0

2.5 3.0 3.5 4.0 4. 5 5.0 5.5

Input Voltage (V)

Figure 16. PFM / PWM Boundaries

PFM border

PWM border

Switching Frequency

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5361 • Rev. 1.1.2 6

Loading...

Loading...