Fairchild FAN5099 service manual

查询FAN5099供应商

FAN5099 Wide Frequency Synchronous Buck

PWM & LDO Controller

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

Decemeber 2006

Features

■ General Purpose PWM Regulator and LDO Controller

■ Input Voltage Range: 3V to 24V

■ Output Voltage Range: 0.8V to 15V

■ V

CC

– 5V

– Shunt Regulator for 12V Operation

■ Support for Ceramic Cap on PWM Output

■ Programmable Current Limit for PWM Output

■ Wide Programmable Switching Frequency Range

(50kHz to 600kHz)

■ R

■ Internal Synchronous Boot Diode

■ Soft-Start for both PWM and LDO

■ Multi-Fault Protection with Optional Auto-restart

■ 16-Pin TSSOP Package

Current Sensing

DS(ON)

Applications

■ High-Efficiency (80+) Computer Power Supplies

■ PC/Server Motherboard Peripherals

– V

_MCH (1.5V), V

CC

V

■ Power Supply for

– FPGA, DSP, Embedded Controllers, Graphic Card

Processor, and Communication Processors

■ High-Power DC-to-DC Converters

TT_GTL

(1.25V)

(1.5V) and

DDQ

Related Application Notes

■ AN-6020 FAN5099 Component Calculation and

Simulation Tools

■ AN-6005 Synchronous Buck MOSFET Loss

Calculations with Excel Model

Description

The FAN5099 combines a high-efficiency pulse-width

modulated (PWM) controller and an LDO (Low DropOut)

linear regulator controller. The PWM controller is

designed to operate over a wide frequency range (50kHz

to 600kHz) to accommodate a variety of applications.

Synchronous rectification provides high efficiency over a

wide range of load currents. Efficiency is further

enhanced by using the low-side MOSFET’s R

sense current. In addition, the capability to operate at low

switching frequencies provides opportunities to boost

power supply efficiency by reducing switching losses and

gain cost savings using low-cost materials, such as powdered iron cores, on the output inductor.

Both the linear and PWM regulator soft-start are controlled by a single external capacitor, to limit in rush current from the supply when the regulators are first

enabled. Current limit for PWM is also programmable.

The FAN5099’s ability to handle wide input voltage

ranges makes this controller suitable for power solutions

in a wide range of applications involving conversion input

voltages from Silver box, battery, and adapters. The

PWM regulator employs a summing-current-mode control with external compensation to achieve fast load transient response and provide system design optimization.

FAN5099 is offered in both industrial temperature grade

(-40°C to +85°C) as well as commercial temperature

grade (-10°C to +85°C).

DS(ON)

to

Ordering Information

Part Number Operating Temp. Range Pb-Free Package Packing Method Qty/Reel

FAN5099MTCX -10°C to +85°C Yes 16-Lead TSSOP Tape and Reel 2500

FAN5099EMTCX -40°C to +85°C Yes 16-Lead TSSOP Tape and Reel 2500

FAN5099MX -10°C to +85°C Yes 16-Lead SOIC Tape and Reel 2500

FAN5099EMX -40°C to +85°C Yes 16-Lead SOIC Tape and Reel 2500

Note: Contact Fairchild sales for availability of other package options.

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3

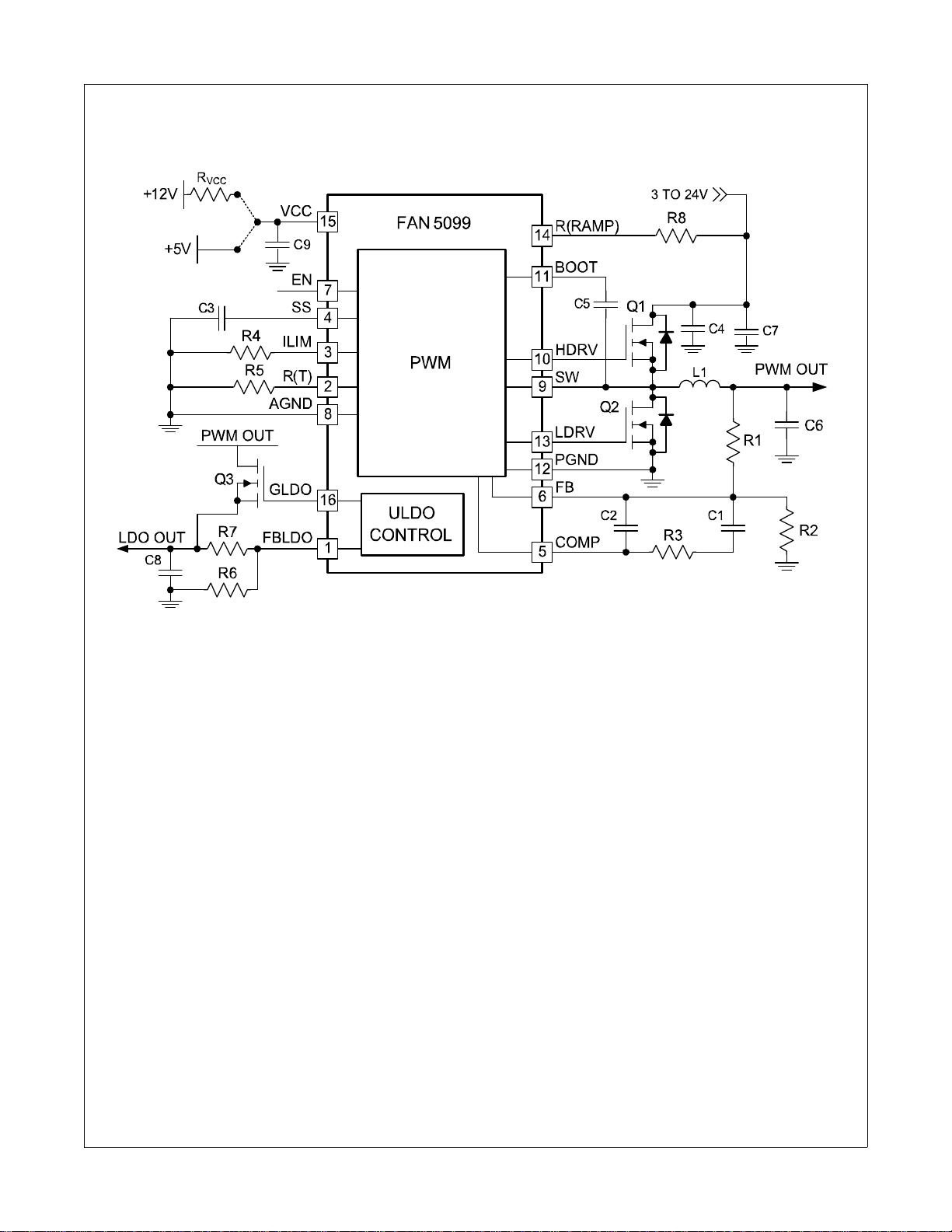

Typical Application

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

Figure 1. Typical Application Diagram

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3 2

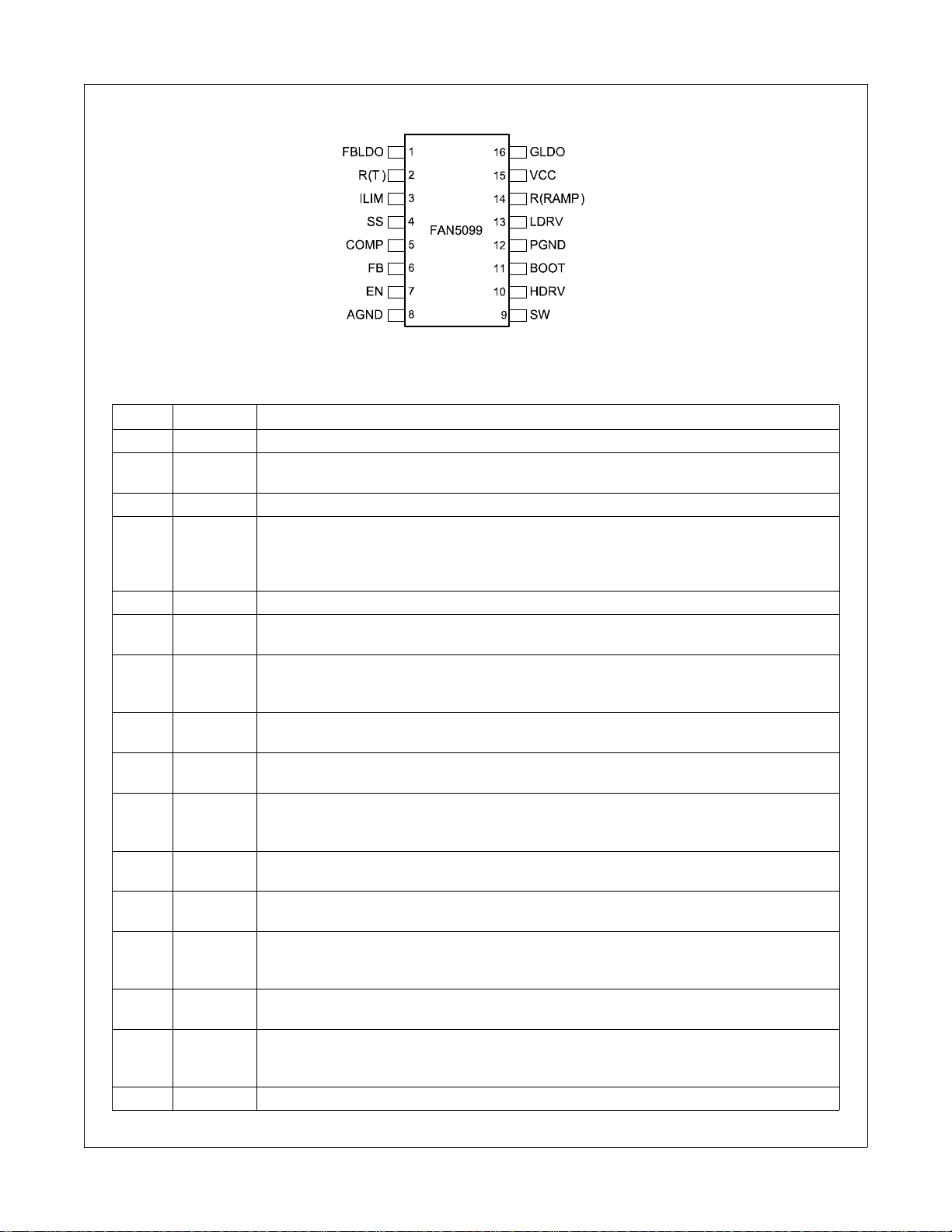

Pin Assignment

Figure 2. Pin Assignment

Pin Description

Pin No. Pin Name Pin Description

1FBLDOLDO Feedback. This node is regulated to V

2R(T)Oscillator Set Resistor. This pin provides oscillator switching frequency adjustment. By plac-

ing a resistor (RT) from this pin to GND, the nominal 50kHz switching frequency is increased.

3ILIMCurrent Limit. A resistor from this pin to GND sets the current limit.

4 SS Soft-Start. A capacitor from this pin to GND programs the slew rate of the converter and the

LDO during initialization. It also sets the time by which the converter delays when restarting

after a fault occurs. SS has to reach 1.2V before fault shutdown feature is enabled. The LDO

is enabled when SS reaches 2.2V.

5COMPCOMP. The output of the error amplifier drives this pin.

6FBFeedback. This pin is the inverting input of the internal error amplifier. Use this pin, in combi-

nation with the COMP pin, to compensate the feedback loop of the converter.

7ENEnable. Enables operation when pulled to logic high. Toggling EN resets the regulator after a

latched fault condition. This is a CMOS input whose state is indeterminate if left open and

needs to be properly biased at all times.

8AGND

9SWSwitching Node. Return for the high-side MOSFET driver and a current sense input. Connect

10 HDRV High-Side Gate Drive Output. Connect to the gate of the high-side power MOSFETs. This

11 BOO T Bootstrap Supply Input. Provides a boosted voltage to the high-side MOSFET driver.

12 PGND Power Ground. The return for the low-side MOSFET driver. Connect to source of low-side

13 LDRV Low-Side Gate Drive Output. Connect to the gate of the low-side power MOSFETs. This pin

14 R(RAMP) Ramp Resistor. A resistor from this pin to VIN sets the ramp amplitude and provides voltage

15 VCC V

16 GLDO Gate Drive for the LDO. Turned off (low) until SS is greater than 2.2V.

Analog Ground.

pin. Tie this pin to the ground island/plane through the lowest impedance connection available.

to source of high-side MOSFET and drain of low-side MOSFET.

pin is also monitored by the adaptive shoot-through protection circuitry to determine when the

high-side MOSFET is turned off.

Connect to bootstrap capacitor as shown in Figure 1.

MOSFET.

is also monitored by the adaptive shoot-through protection circuitry to determine when the

lower MOSFET is turned off.

feed-forward.

. Provides bias power to the IC and the drive voltage for LDRV. Bypass with a ceramic

CC

capacitor as close to this pin as possible. This pin has a shunt regulator which draws current

when the input voltage is above 5.6V.

The signal ground for the IC. All internal control voltages are referred to this

REF

.

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3 3

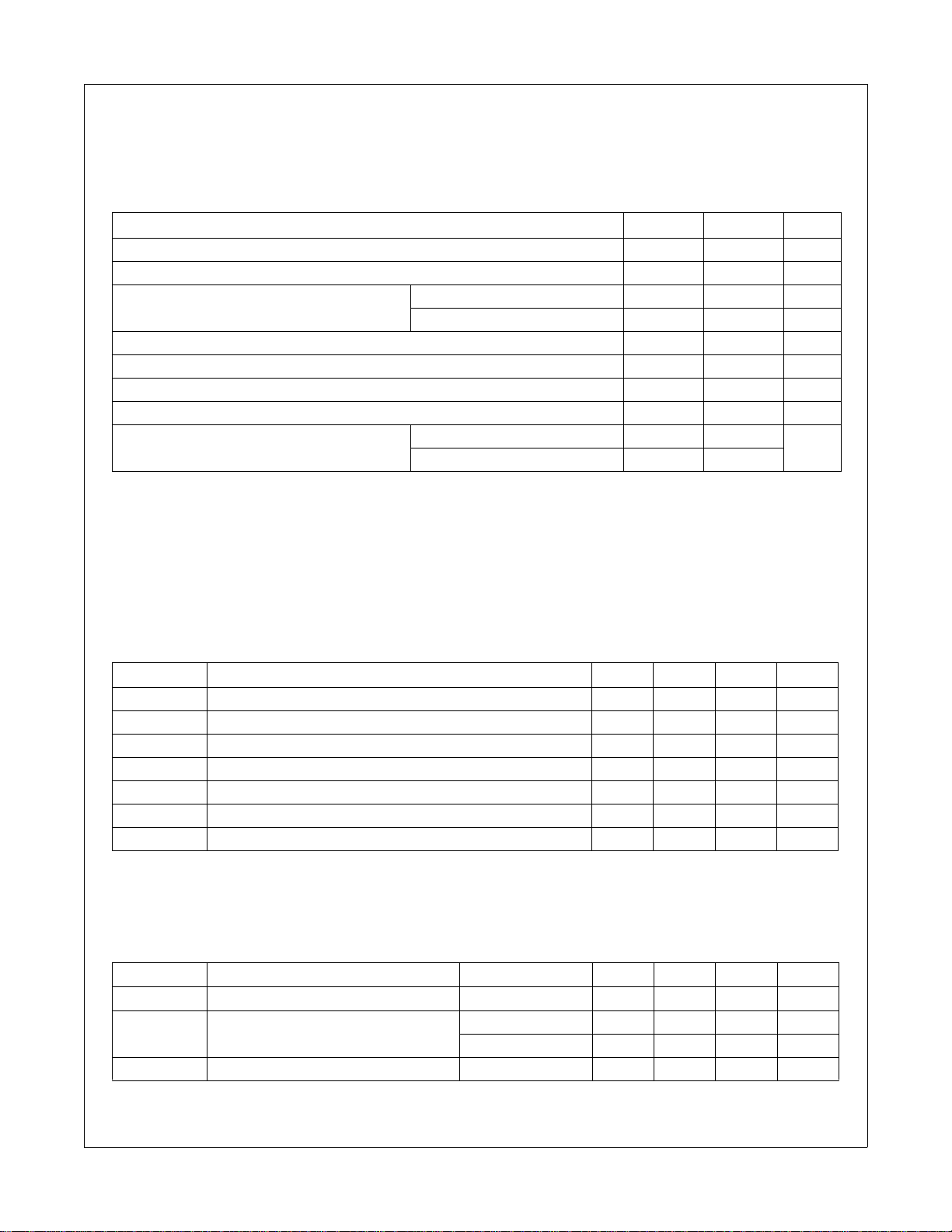

Absolute Maximum Ratings

The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The

device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables

are not guaranteed at the absolute maximum ratings. The “Recommended Operating Conditions” table defines the

conditions for actual device operation.

VCC to PGND 6.0 V

BOOT to PGND 33.0 V

SW to PGND Continuous -0.5 33.0 V

HDRV (V

– VSW) 6.0 V

BOOT

LDRV -0.5 6.0 V

All Other Pins -0.3 V

Maximum Shunt Current for V

Electrostatic Discharge (ESD) Protection

(2)

Level

Notes:

1. Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This

is a stress rating only; functional operation of the device at these or any conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect device reliability. Absolute maximum ratings apply individually only, not in combination. Unless

otherwise specified, all other voltages are referenced to AGND.

2. Using Mil Std. 883E, method 3015.7 (Human Body Model) and EIA/JESD22C101-A (Charge Device Model).

(1)

Parameter Min. Max. Unit

Transient (t < 50ns, f < 500kHz) -3.0 33.0 V

+ 0.3 V

CC

CC

HBM 3.5 kV

CDM 1.8

150 mA

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

Thermal Information

Symbols Parameter Min. Typ. Max. Unit

T

STG

T

L

P

D

θ

JC

θ

JA

3. Junction-to-ambient thermal resistance, θJA, is a strong function of PCB material, board thickness, thickness and

number of copper planes, number of vias used, diameter of vias used, available copper surface, and attached heat

sink characteristics.

Storage Temperature -65 150 °C

Lead Soldering Temperature, 10 Seconds 300 °C

Vapor Phase, 60 Seconds 215 °C

Infrared, 15 Seconds 220 °C

Power Dissipation, TA = 25°C 715 mW

Thermal Resistance – Junction-to-Case 37 °C/W

Thermal Resistance – Junction-to-Ambient

(3)

100 °C/W

Recommended Operating Conditions

Symbols Parameter Conditions Min. Typ. Max. Unit

V

CC

T

A

T

J

Supply Voltage VCC to GND 4.5 5.0 5.5 V

Ambient Temperature

Commercial -10 85 °C

Industrial -40 85 °C

Junction Temperature 125 °C

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3 4

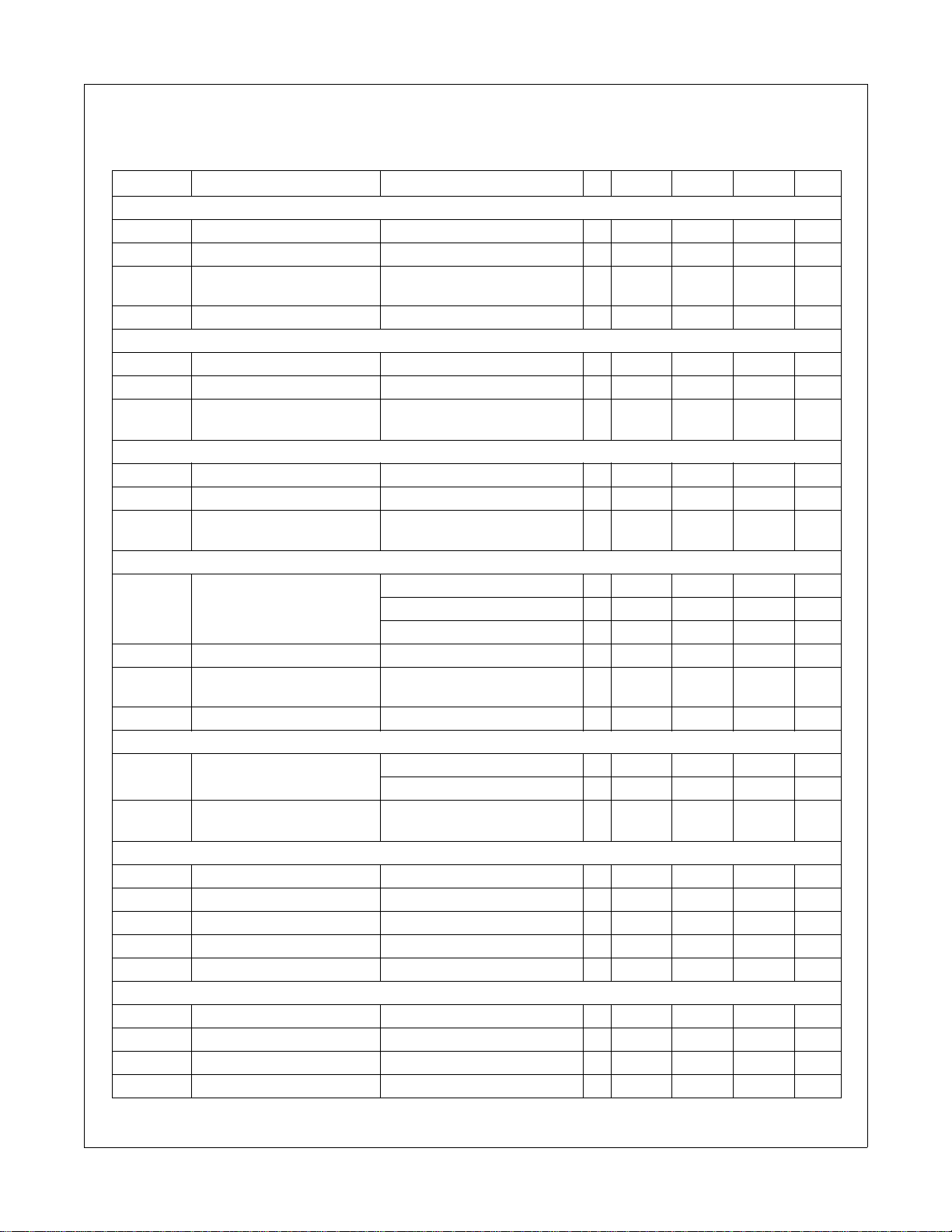

Electrical Characteristics

Unless otherwise noted, VCC = 5V, TA = 25°C, using the circuit in Figure 1. The ‘•’ denotes that the specifications apply

to the full ambient operating temperature range.

Symbol Parameter Conditions Min. Typ. Max. Unit

Supply Current

I

VCC

I

VCC(SD)VCC

I

VCC(OP)VCC

V

SHUNTVCC

Under-Voltage Lockout (UVLO)

UVLO(H) Rising V

UVLO(L) Falling V

Soft-Start

I

SS

V

LDOSTART

V

SSOK

Oscillator

F

OSC

ΔV

RAMP

Reference

V

REF

Error Amplifier

GBWP Gain-BW Product 25 MHz

S/R Slew Rate 10pF across COMP to GND 8 V/μS

I

FB

Gate Drive

R

HUP

R

HDN

R

LUP

R

LDN

VCC Current (Quiescent) HDRV, LDRV Open

Current (Shutdown) EN = 0V, VCC = 5.5V

Current (Operating)

Volta ge

UVLO Threshold

V

CC

(6)

UVLO Threshold

CC

UVLO Threshold

CC

Hysteresis

Current 10 μA

LDO Start Threshold 2.2 V

PWM Protection Enable

Threshold

Frequency

Operating Frequency Range 40 600 kHz

Ramp Amplitude

(Peak-to-Peak)

Minimum On Time f = 200kHz 200 ns

Reference Voltage

(Measured at FB Pin)

Current Amplifier Reference

(at SW node)

DC Gain 80 dB

Output Voltage Swing No Load

FB Pin Source Current μA

HDRV Pull-up Resistor Sourcing

HDRV Pull-down Resistor Sinking

LDRV Pull-up Resistor Sourcing

LDRV Pull-down Resistor Sinking

(4,5)

•

2.6 3.2 3.8 mA

EN = 5V, V

Q

= 20nC, FSW = 200kHz

FET

= 5.0V,

CC

Sinking 1mA to 100mA at VCC Pin

•

5.4 5.9 V

•

4.00 4.25 4.50 V

•

3.60 3.75 4.00 V

200 400 μA

10 15 mA

0.5 V

1.2 V

R(T) = 25.5KΩ ± 1% 240 300 360 kHz

R(T) = 199KΩ ± 1% 60 80 100 kHz

R(T) = Open 50 kHz

R(RAMP) = 330KΩ 0.4 V

TA = 0°C to 70°C

= -40°C to 85°C

T

A

•

790 800 810 mV

•

788 800 812 mV

160 mV

•

0.5 4.0 V

•

•

•

•

1.8 3.0 Ω

1.8 3.0 Ω

1.8 3.0 Ω

1.2 2.0 Ω

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3 5

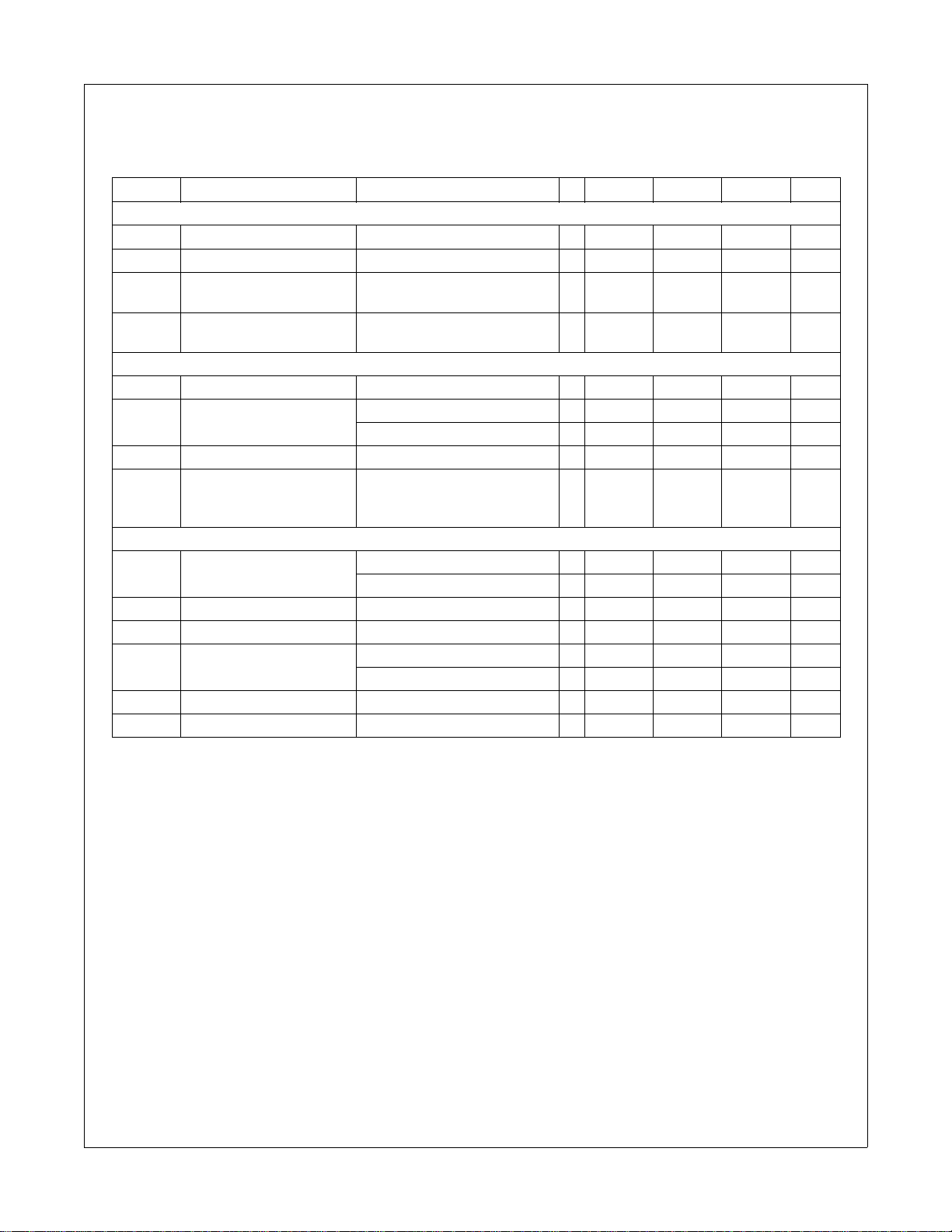

Electrical Characteristics (Continued)

Unless otherwise noted, V

= 5V, T

CC

to the full ambient operating temperature range.

Symbol Parameter Conditions Min. Typ. Max. Unit

Protection/Disable

I

I

SWPD

V

V

Supply Current

TSD Thermal Shutdown 160 °C

V

Low Drop-Out (LDO)

V

LDOREF

V

LDO_DO

ILIMIT Source Current 9 10 11 μA

LIM

SW Pull-down Current SW = 1V, EN = 0V mA

Under-Voltage Threshold

UV

Over-Voltage Threshold

OV

Enable Threshold Voltage

EN

Enable Source Current V

Enable Sink Current

(7)

Reference Voltage

(measured at FBLDO pin)

Regulation 0A ≤ I

Drop-out Voltage I

External Gate Drive

Gate Drive Source Current 1.2 mA

Gate Drive Sink Current 400 μA

= 25°C, using the circuit in Figure 1. The ‘•’ denotes that the specifications apply

A

As % of set point;

2μS noise filter

As % of set point;

2μS noise filter

Enable Condition

Disable Condition

V

(4, 5)

65 75 80 %

•

110 115 120 %

•

•

2.0 V

•

= 5V 50 μA

CC

= 5V and fault conditions

CC

10 μA

0.8 V

(overload, short-circuit,

over-voltage, under-voltage)

TA = 0°C to 70°C

= -40°C to 85°C

T

A

≤ 5A

LOAD

≤ 5A and R

LOAD

= 4.75V

V

CC

= 5.6V

V

CC

< 50mΩ 0.3 V

DS-ON

•

775 800 825 mV

•

770 800 830 mV

•

1.17 1.20 1.23 V

•

•

4.5 V

5.3 V

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

Notes:

4. All limits at operating temperature extremes are guaranteed by design, characterization, and statistical quality control.

5. AC specifications guaranteed by design/characterization (not production tested).

6. For a case when V

is sinking current to keep voltage on V

7. Test Conditions: V

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3 6

is higher than the typical 5V V

CC

LDO_IN

= 1.5V and V

pin constant.

CC

LDO_OUT

voltage observed at VCC pin when the internal shunt regulator

CC,

= 1.2V.

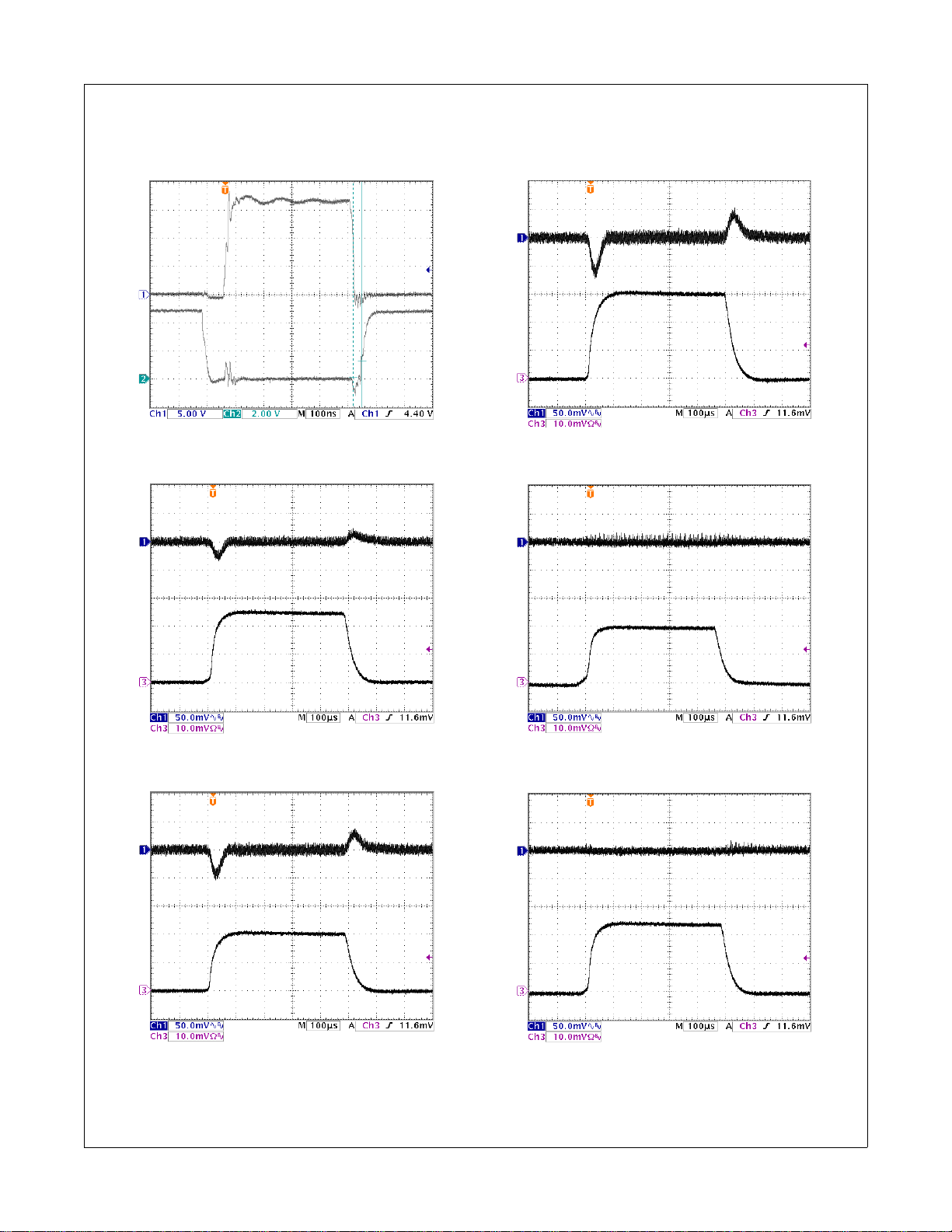

Typical Performance Characteristics

VIN=12V, Vdd=5V, V

OUT

=1.5V, V

=1.2V, I

ldo

load

=5A, I

ldo

=2A, F

= 300kHz, unless otherwise noted.

osc

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

Ch1: HDRV; Ch2: LDRV. Dead times: 62ns, 32ns

Figure 3. Dead Time Waveform

Ch1: V

; Ch3: IL, 2.5A/div

OUT

Figure 4. PWM Load Transient (0 to 5A)

Ch1: V

; Ch3: IL, 5A/div

OUT

Figure 6. PWM Load Transient (0 to 15A)

Ch1: V

OUT_LDO

; Ch3: I

LDO

, 1A/div

Figure 7. LDO Load Transient (0 to 2A)

Ch1: V

; Ch3: IL, 5A/div

OUT

Figure 5. PWM Load Transient (0 to 10A)

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3 7

Ch1: V

Figure 8. LDO Load Transient (0 to 5A)

OUT_LDO

; Ch3: I

LDO

, 2.5A/div

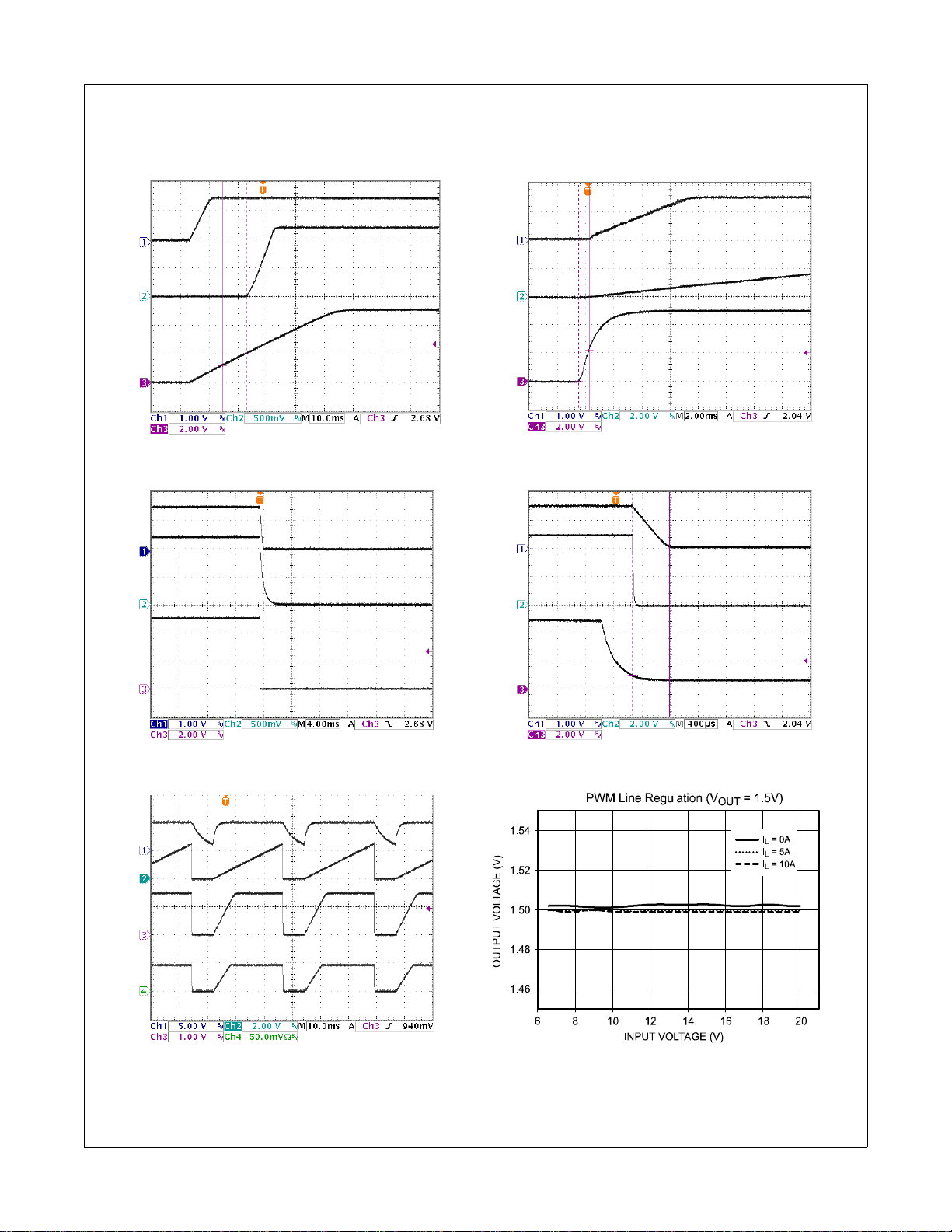

Typical Performance Characteristics (Continued)

VIN=12V, Vdd=5V, V

Ch1: V

; Ch2:V

OUT

OUT

OUT_LDO

=1.5V, V

; Ch3: SS

=1.2V, I

ldo

load

=5A, I

ldo

=2A, F

osc

= 300kHz, unless otherwise noted.

Ch1: V

; Ch2: SS; Ch3: EN

OUT

FAN5099 Wide Frequency Synchronous Buck PWM & LDO Controller

Figure 9. PWM/LDO Power Up

Ch1: V

OUT

; Ch2: V

OUT_LDO

; Ch3: SS

Figure 10. PWM/LDO Power Down

Figure 12. Enable On (I

Ch1: V

; Ch2: SS; Ch3: EN

OUT

Figure 13. Enable Off (I

PWM

PWM

= 5A)

= 5A)

Ch1: EN; Ch2: SS; Ch3: V

Figure 11. Auto Restart

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN5099 Rev. 1.1.3 8

; Ch4: IL, 25A/div

OUT

Figure 14. PWM Line Regulation

Loading...

Loading...