Fairchild FAN4800 service manual

Application Note AN6032

FAN4800 Combo Controller Applications

www.fairchildsemi.com

General Description

This application note shows the step-by-step process to

design a high-performance supply. The equations shown in

this document can also be used for different output voltages

and total power.

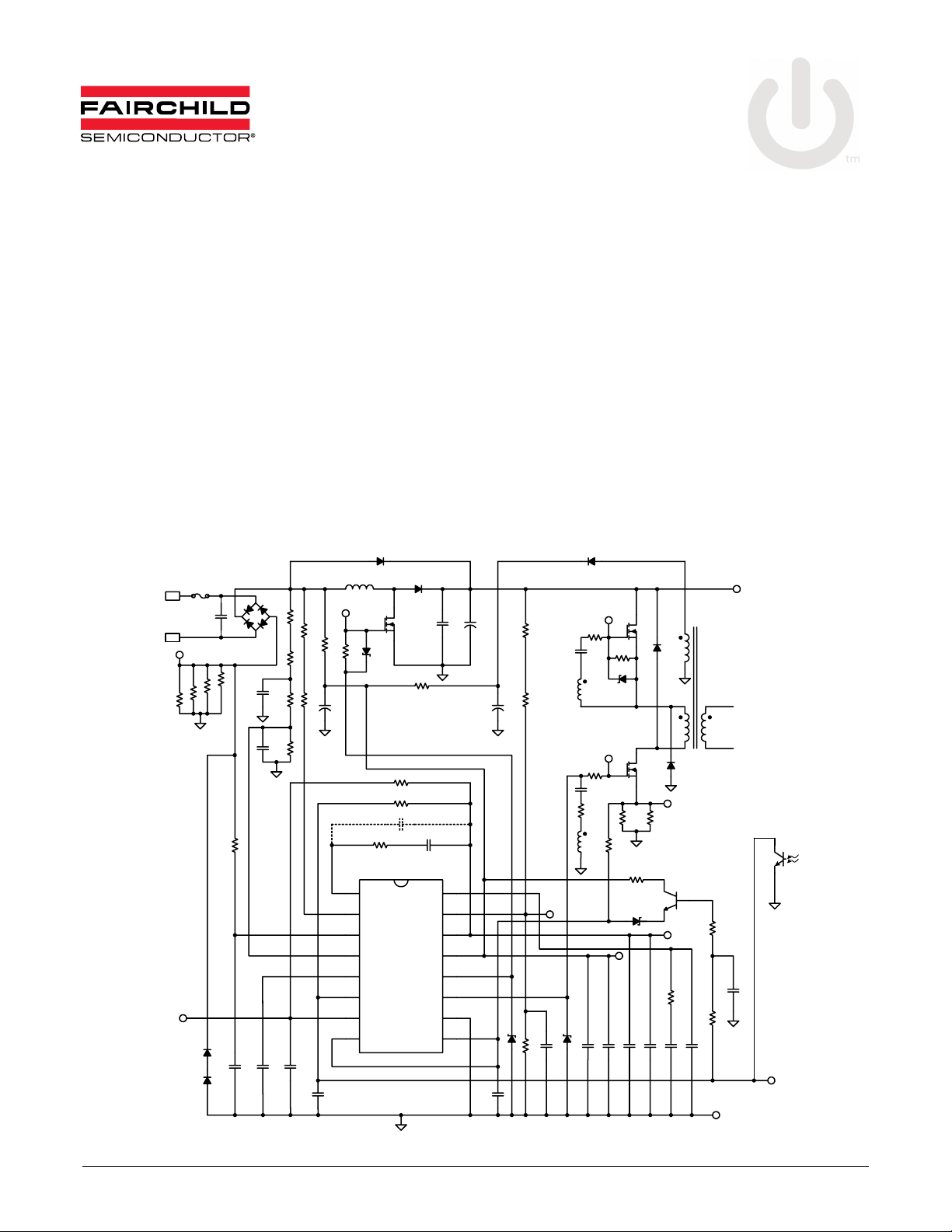

The complete power supply circuits shown in Figures 6 and

7 demonstrate the FAN4800’s ability to manage high output

power while complying with international requirements

regarding AC line quality. The PFC section provides

380V

The output of the converter delivers +12V at up to 8.4 amps.

The circuit operates from 85 to 265V

tions switching at 100kHz.

to a dual-transistor current-mode forward converter.

DC

with both power sec-

AC

D2

D1

1N5406

L1

1

2

3

4

5

6

7

8

D9

MBRS

140

R12

71.5k

IEAO

I

AC

I

SENSE

V

RMS

SS

V

DC

RAMP1

RAMP2

ISL9R460P2

FQPF9N50

NOT USED

U1

FAN4800

PFC OUT

PWM OUT

Q1

41.7k

DC I

R6

R10

6.2k

AC INPUT

85 TO 265Vac

R5A

1.2

RAMP1

R5B

1.2

D12

1N5401

D13

1N5401

I

F1

3.15A

0.68uF

SENSE

R5C

1.2

BR1

4A, 600V

C26

100nF

0.1uF

KBL06

R2A

453k

R2B

453k

C3

R3

110k

C2

0.47uF

R4

15.4k

C19

C18

1uF

470pF

C1

R5D

1.2

R31

100

R1B

500k

R1A

500k

10nF

C11

R27

75k

C30

330uF

25V

R21

Q1G

22

10nF

R28

240

C7

C6

1.5nF

VEAO

V

V

GND

LIMIT

C4

16

15

V

FB

14

REF

13

CC

12

11

10

9

The PFC Stage

Powering the FAN4800

The FAN4800 is initialized once C12 is charged to 13V

through R

age on C

well-regulated 13V for the FAN4800 from its secondary

winding. T

N

SEC

bypassing with low-ESR ceramic or film capacitors on V

and V

is achieved when D

peak AC line voltage before the boost switch Q

on. This ensures the boost inductor current is zero before

100uF

450V

C5

C12

10uF

35V

C17

220pF

D8

MBRS

140

R7A

178k

R7B

178k

and R28. PFC switching action boosts the volt-

27

to 380V via L1’s inductance. T2 then supplies a

5

’s primary-to-secondary turns ratio (N

2

) is 18.8:1. For proper circuit operation, high-frequency

is provided. Orderly PFC operation upon start-up

REF

R8

2.37k

V

FB

MBRS

C31

1nF

quick charges the boost capacitor to the

2

D3

RGF1J

Q2G

R30

4.7k

D7

MMBZ5245B

Q3G

R19

220

MMBZ5245B

V

CC

C16

1uF

R20A

2.2

0.1uF

FQPF

6N50

FQPF6N50

R9

1.1k

D4

C13

Q2

RGF1J

Q3

R20B

2.2

R11

845k

C14

1uF

D5

T2

D6

RGF1J

RAMP2 / DC I

Q4

MMBT3904

V

REF

10nF

C8

68nF

R17

33

C25

0.1uF

T1B

R14

33

C20

1uF

R15

3

T1A

D10

140

C15

10nF

VDC / +380V

LIMIT

R13

10k

C10

15uF

R16

10k

C9

PRI GND

1

V

DC

/

PRI

CC

is turned

Figure 1. The PFC Stage

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN4800 Rev. 1.0.2 • 12/07/06

AN6032 APPLICATION NOTE

(

(

)

(

)3(

)

(

)

η

(

)6(

(

)

(

)

(

(

PFC action begins. The value of the regulated voltage on C

must always be greater than the peak value of the maximum

line voltage delivered to the supply.

>

V2V

C5 in(rms_max)

>×

V 1.414 265

()()

C5

>

V 375V use 380V

C5

1

Because the FAN4800 uses transconductance amplifiers, the

loop compensation networks are returned to ground (see the

FAN4800 datasheet for the error amplifier characteristics/

advantages). This eliminates the interaction of the resistive

divider network with the loop compensation capacitors, permitting a wide choice of divider values chosen to minimize

amplifier offset voltages due to input bias currents. For reliable operation, R

and R7B must have a voltage rating of at

7A

least 400 volts.

Calculate the divider ratio (R

+

RRV

7A 7B C5

R2.5

8

+

R R 380

7A 7B

R2.5

8

+

RR

7A 7B

R

8

7A+R7B

)/R8 by:

=−

1

=−

=

1

151

2

Selecting the Power Components

The FAN4800 PFC section operates with continuous inductor current to minimize peak current and to maximize available power. The boost inductor value found by setting ΔI, the

peak-to-peak value of high-frequency current, is typically

10% to 20% of the peak value of the maximum line current.

2P

in(max)

I

in( peak _ max)

P

in(max)

where I

in(peak_max)

at low line, V

age, P

O(max)

ciency. Value I

is a peak value of input current occurred

in(rms_min)

is the maximum output power, and η is effi-

in(peak_max)

the specified percentage rate. I

mum current.

Δ

IdII

II

L(max) in( peak _ max)

Duty cycle D and switching frequency f

selection.

=

V

in( rms _ min)

P

O(max)

=

η

is RMS value of minimum line volt-

defines value of ΔI, where dI is

is the inductor maxi-

L(max)

=×

in( peak _ max)

Δ

=+

I

2

influence inductor

S

4

5

5

−

V2V

Oin(rms_min)

=

)

The boost diode D

D

=

L

1

=

=

=

3.128mH use 3.0mH

V

O

×

D2V

in( rms _ min)

×

fI

Δ

S

−⋅⋅

V2V V

()

O in( rms _min) in( rms _ min)

⋅⋅⋅

VfdIP

OS O(max)

−⋅⋅⋅

380 1.414 85 85 0.95

()()

{}

380 1 10 0.15 100

()

and switch Q1 are chosen with a reverse

1

5

⋅× ⋅ ⋅

()

()()

2

2

()( )

voltage rating of 500V to safely withstand the 380V boost

potential. The maximum Q

Equation 8 and the maximum Q

RMS current is obtained by

1

peak current is calculated

1

by Equation 9.

42V

=−

I2I

Q1rms in( rms _max)

2P 4 2V

O(max) in( rms _ min)

=−

ηπ

V23V

in( rms _ min) O

1.414 100 4 1.414 85

()()

=−

1.06 A

II

2.025 A

0.95 85 2 3 3.1416 380

()()

=

=+

Q1peak in( peak_ max)

2P

O(max)

=

V

η

in( rms

1.414 100

()()

=+

0.95 85

()()

=

1

23V

1

⋅⋅⋅

⋅⋅⋅

I

Δ

2

V2V 2V

()

+

_min) O S 1

⋅

⋅

in( rms _ min)

π

O

()()

1

()()

−⋅

Oin(rms_min)in(rms_min)

⋅⋅

VfL

−⋅⋅⋅

380 1.414 85 1.414 85

()()

{}

⋅× ⋅×

380 1 10 3 10

()

()( )

()()

53

The boost diode average current can be calculated by:

=

II

D1avg O(max)

P

O(max)

=

V

O

100

==

0.26 A

380

The boost capacitor value is chosen to permit a given output

voltage hold-up time in the event the line voltage is suddenly

removed.

2P t

≥

C

5

O(max) HLD

22

VV

C5(NOM ) C5(MIN )

−

where:

t

= hold-up time (sec)

HLD

V

= minimum voltage on C5 at which the PWM stage

C5(min)

can still deliver full output power

7

)

8

9

−

10

)

11

)

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN4800 Rev. 1.0.2 • 12/07/06 2

AN6032 APPLICATION NOTE

p

(

)12(

(

)

(

)

(

)

(

(

(

)

(

)

A key advantage of using leading/trailing-edge modulation

is that a large portion of the inductor current is "dumped"

directly into the load (PWM stage transformer) and not the

boost capacitor. This relaxes the ESR requirement of the

boost capacitor. For reference, Equation 12 should be used as

a starting point when choosing C

’s maximum ripple current

5

rating (at 120Hz).

I

O( C5 )

=

I

C5_rms

I2I

()

eak C5 _ rms

2

=⋅

12a

3. Select the value of (R

)

multiplier output current without saturating the output.

The maximum output current of the multiplier is

k

M

=

k

2

V

rms

=

kkV

Min(rms_min)

=⋅

0.35 85

()()

=≈

2528.75 2529

1A+R1B

2

2

) that permits the greatest

16

16a

228.57μA.

Selecting the Power Setting Components

The maximum average power delivered by the PFC stage is

set using the following procedure:

1. Find the resistive divider ratio that results in the voltage

at the V

pin being equal to 1.14V at the lowest line

RMS

k 2V V 0.625

+≥

RR

()

1A 1B

+≥

RR

()

1A 1B

+≥

R R 989.38k use 1M

()

1A 1B

in( rms _ min) EAO(max)

0.35 1.414 85 6 0.625

()( )()( )

()

228.57 10

⋅⋅−

228.57 10

ΩΩ

−

−

6

×

−

6

×

17

voltage. The voltage at this pin must be well filtered, yet

able to respond well to transient line voltage changes.

π

R1.14

4

=

R

22V

TOT

⋅

in( rms _ min)

13

The resistor and capacitor values in the typical example

were found empirically to offer the lowest ripple voltage

and still respond well to line voltage changes. Should a

ratio be required that is greatly different from that found

4. Select the value of the current sense resistor to complete

the calculations for the power setting components.

⋅−⋅

R k V 0.625

MULO M EAO( max)

R||R||R||R

5A 5B 5C 5D

R||R||R||R

5A 5B 5C 5D

R || R || R || R 0.452 use 0.3

5A 5B 5C 5D

≤

3.5 10 2529 6 0.625 0.95

()

≤

≤

(

PRR

O(max) 1A 1B

3

×⋅ − ⋅

ΩΩ

+

()

()( )()

100 1 10

()

()

×

η

18

6

in Equation 13, adjust the filter capacitor values according to Equations 14 and 15.

C

=

3

2f R R R R

⋅+⋅+

π

()()

12A2B 34

⎛⎞

1

+

⎜⎟

⎜⎟

RR RR

()()

2A 2B 3 4

⎝⎠

C

=

2

R

TOT

RR

⋅

4TOT

+⋅+

2f R

⋅

π

24

14

15

where:

R

= multiplier output termination resistance (3.5kΩ).

MULO

Voltage Loop Compensation

Maximum transient response of the PFC section, without

instability, is obtained when the open-loop crossover frequency is one-half the line frequency. For this application,

where:

f

= 15Hz, f2 = 23Hz

1

R

= R2A + R2B + R3 + R

TOT

4

the compensation components (pole/zero pair) are chosen so

that the closed loop response decreases at 20dB/decade,

crossing unity gain at 30Hz, then immediately decreasing at

40dB/decade. The error amplifier pole is placed at 30Hz and

an effective zero at one-tenth this frequency, or 3Hz. Find

2. Find the constant of proportionality kM of the multiplier

gain k in Equation 16a. To obtain "brownout" action

the crossover frequency (G

reference, Equation 20 finds the power stage pole and Equation 21 finds the power stage DC gain.

= 1) of the power stage. For

PS

below the lowest input voltage, the maximum gain of the

multiplier must be used when finding k

gain (0.35) occurs when the V

RMS

. The maximum

M

input of the multiplier

is 1.14V. Equation 16 is the general expression for the

multiplier gain versus the line voltage.

)

)

)

© 2006 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN4800 Rev. 1.0.2 • 12/07/06 3

Loading...

Loading...