Fairchild BSS138 service manual

October 2005

BSS138

N-Channel Logic Level Enhancement Mode Field Effect Transistor

General Description

These N-Channel enhancement mode field effect

transistors are produced using Fairchild’s proprietary,

high cell density, DMOS technology. These products

have been designed to minimize on-state resistance

while provide rugged, reliable, and fast switching

performance.These products are particularly suited for

low voltage, low current applications such as small

servo motor control, power MOSFET gate drivers, and

other switching applications.

Features

• 0.22 A, 50 V. R

• High density cell design for extremely low R

• Rugged and Reliable

• Compact industry standard SOT-23 surface mount

package

= 3.5Ω @ VGS = 10 V

DS(ON)

R

= 6.0Ω @ VGS = 4.5 V

DS(ON)

DS(ON)

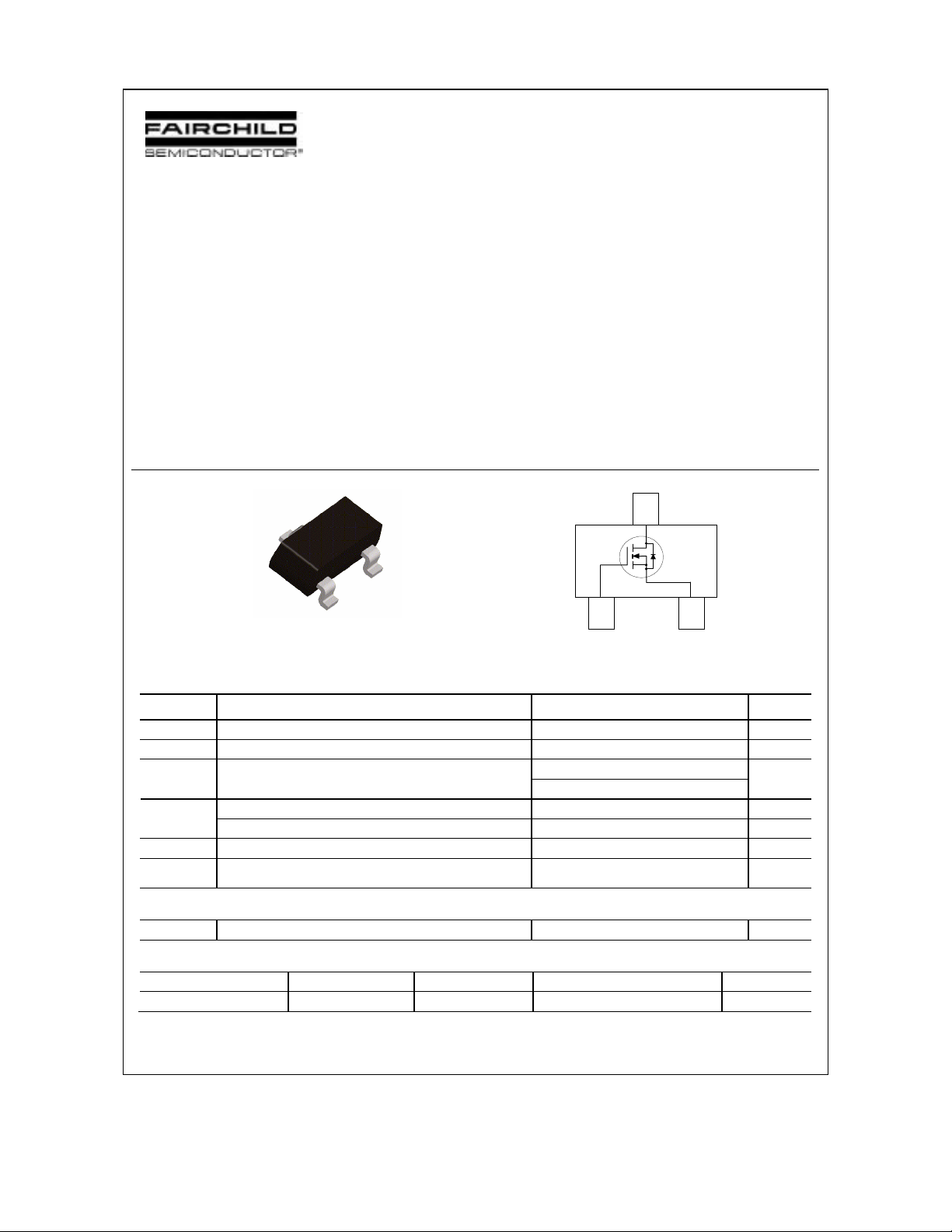

BSS138

D

D

S

G

SOT-23

Absolute Maximum Ratings T

G

o

=25

C unless otherwise noted

A

Symbol Parameter Ratings Units

V

Drain-Source Voltage 50 V

DSS

V

Gate-Source Voltage

GSS

ID Drain Current – Continuous

– Pulsed 0.88

PD

TJ, T

TL

STG

Maximum Power Dissipation

Derate Above 25°C

Operating and Storage Junction Temperature Range

Maximum Lead Temperature for Soldering

Purposes, 1/16” from Case for 10 Seconds

(Note 1)

0.22 A

(Note 1)

0.36

±20

2.8

−55 to +150 °C

300

Thermal Characteristics

R

θJA

Thermal Resistance, Junction-to-Ambient

(Note 1)

350

S

V

W

mW/°C

°C

°C/W

Package Marking and Ordering Information

Device Marking Device Reel Size Tape width Quantity

SS BSS138 7’’ 8mm 3000 units

2005 Fairchild Semiconductor Corporation

BSS138 Rev C(W)

BSS138

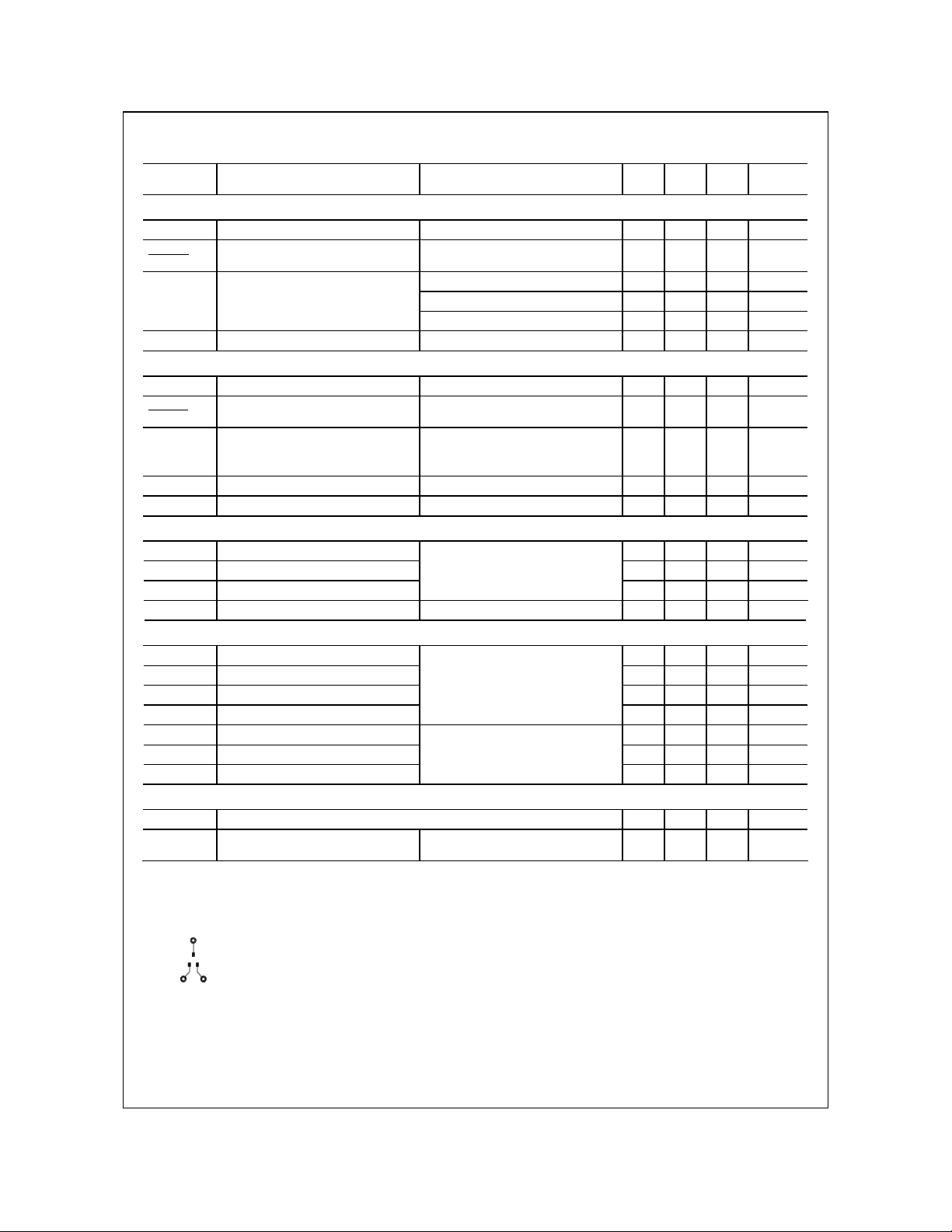

Electrical Characteristics T

= 25°C unless otherwise noted

A

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BV

Drain–Source Breakdown Voltage

DSS

∆BV

DSS

∆T

J

I

Zero Gate Voltage Drain Current VDS = 50 V, VGS = 0 V 0.5

DSS

Breakdown Voltage Temperature

Coefficient

V

I

Gate–Body Leakage.

GSS

On Characteristics

V

Gate Threshold Voltage VDS = VGS, ID = 1 mA 0.8 1.3 1.5 V

GS(th)

∆V

GS(th)

∆TJ

R

DS(on)

Gate Threshold Voltage

Temperature Coefficient

Static Drain–Source

(Note 2)

On–Resistance

I

On–State Drain Current VGS = 10 V, VDS = 5 V 0.2 A

D(on)

= 0 V, ID = 250 µA

V

GS

= 250 µA,Referenced to 25°C

I

D

= 50 V, VGS = 0 V TJ = 125°C

V

DS

= 30 V, VGS = 0 V 100 nA

DS

= ±20 V, VDS = 0 V

V

GS

= 1 mA,Referenced to 25°C

I

D

= 10 V, ID = 0.22 A

V

GS

= 4.5 V, ID = 0.22 A

V

GS

= 10 V, ID = 0.22 A, TJ = 125°C

V

GS

gFS Forward Transconductance VDS = 10V, ID = 0.22 A 0. 12 0.5 S

50 V

72

mV/°C

µA

5

–2

0.7

1.0

1.1

±100

3.5

6.0

5.8

µA

nA

mV/°C

Ω

Dynamic Characteristics

C

Input Capacitance 27 pF

iss

C

Output Capacitance 13 pF

oss

C

Reverse Transfer Capacitance

rss

RG Gate Resistance VGS = 15 mV, f = 1.0 MHz 9

Switching Characteristics

t

Turn–On Delay Time 2.5 5 ns

d(on)

(Note 2)

tr Turn–On Rise Time 9 18 ns

t

Turn–Off Delay Time 20 36 ns

d(off)

tf Turn–Off Fall Time

Qg Total Gate Charge 1.7 2.4 nC

Qgs Gate–Source Charge 0.1 nC

Qgd Gate–Drain Charge

= 25 V, V

V

DS

GS

f = 1.0 MHz

V

= 30 V, ID = 0.29 A,

DD

= 10 V, R

V

GS

V

= 25 V, ID = 0.22 A,

DS

V

= 10 V

GS

GEN

= 0 V,

6 pF

Ω

= 6 Ω

7 14 ns

0.4 nC

Drain–Source Diode Characteristics and Maximum Ratings

IS Maximum Continuous Drain–Source Diode Forward Current 0.22 A

VSD Drain–Source Diode Forward

VGS = 0 V, IS = 0.44 A

(Note 2)

0.8 1.4 V

Voltage

Notes:

1. R

is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of

θJA

the drain pins. R

is guaranteed by design while R

θJC

a) 350°C/W when mounted on a

minimum pad..

is determined by the user's board design.

θCA

Scale 1 : 1 on letter size paper

2. Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

BSS138 Rev C(W)

Loading...

Loading...