Fairchild 74ABT16374 service manual

查询74ABT16374供应商

74ABT16374

16-Bit D-Type Flip-Flop with 3-STATE Outputs

74ABT16374 16-Bit D-Type Flip-Flop with 3-STATE Outputs

March 1994

Revised May 2005

General Description

The ABT16374 contains sixteen non-inverting D-t ype flipflops with 3-STAT E outputs and is intended for bus oriented

applications. The device is byte controlled. A buffered clock

(CP) and Output E nable (OE

and can be shorted together for full 16-bit operation.

) are common to each byte

Features

■ Separate control logic for each byte

■ 16-bit version of the ABT374

■ Edge-triggered D-type inputs

■ Buffered Positive edge-triggered clock

■ High impedance glitch free bus loading during entire

power up and power down cycle

■ Non-destructive hot insertion capability

■ Guaranteed latch-up protection

Ordering Code:

Order Number Package Number Package Description

74ABT16374CSSC MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

74ABT16374CMTD MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Devices also availab l e in Tape and Reel. Specify by appending suffix lette r “X” to the ordering code.

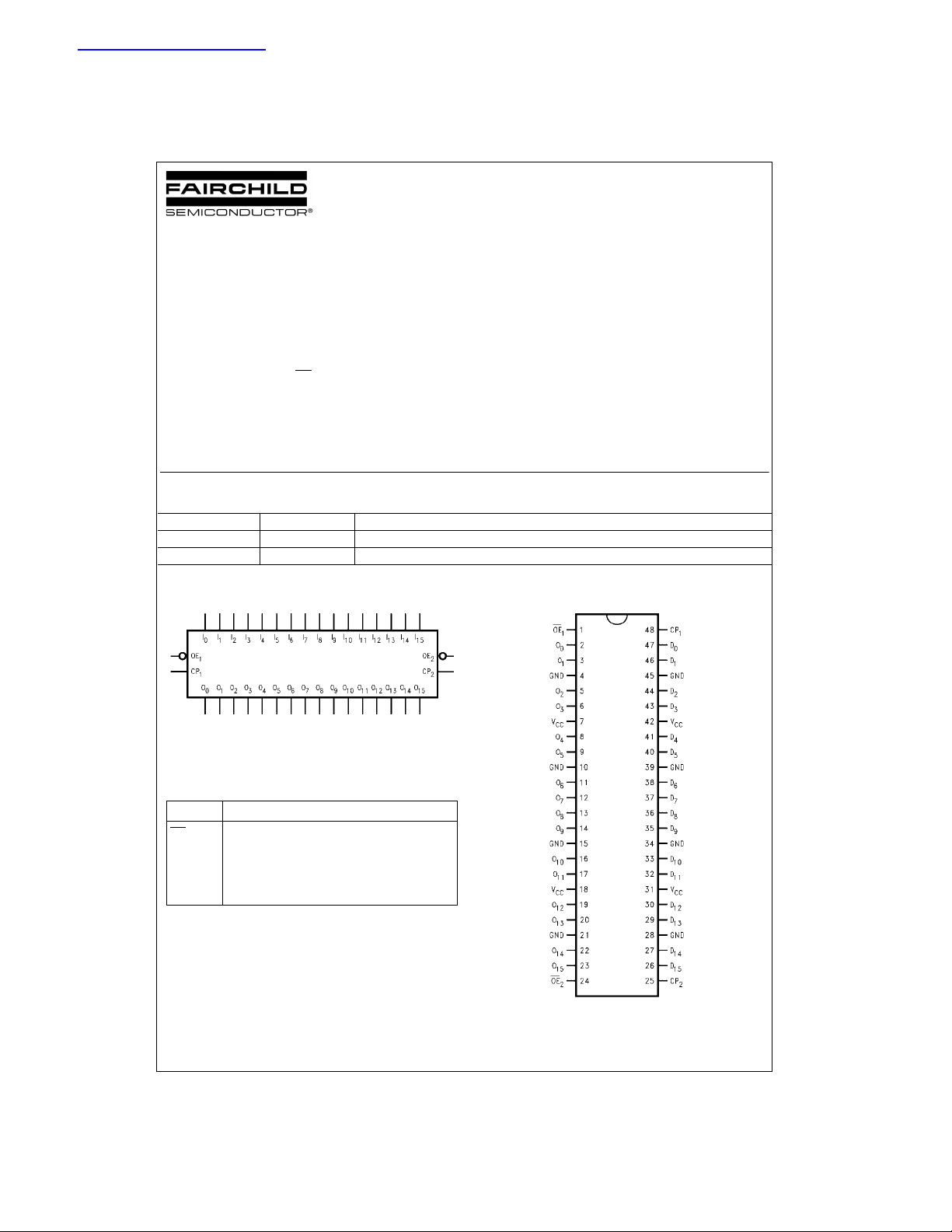

Logic Symbol

Connection Diagram

Pin Descriptions

Pin Name Description

OE

CP

D

0–D15

O

0–O15

© 2005 Fairchild Semiconductor Corporation DS011668 www.fairchildsemi.com

3-STATE Output Enable Input (Active LOW)

n

Clock Pulse Input (Active Rising Edge)

n

Data Inputs

3-STATE Outputs

Functional Description

The ABT16374 consists of sixteen edge -tr igge red fl ip -fl ops

with individual D-type inputs and 3-STATE true outputs.

The device is byte controlled with each byte functioning

identically, but independent of the ot her. The control pins

can be shorted together to obtain full 16-bit operation. Each

74ABT16374

byte has a buffered clock and buffered Output Enable common to all flip-flops within th at byte. The descri ption which

follows applies to each byte. Each flip-flop will store the

state of their indivi dual D inputs that meet th e setup and

hold time requirem ents on the LOW-to-HIGH Clock (CP

transition. With the Output Enable (OE

) LOW, the con-

n

tents of the flip-flops ar e available at the outputs. When

is HIGH, the outputs go to the high i mpedance state.

OE

n

Operation of the OE

flip-flops.

input does not affect the state of the

n

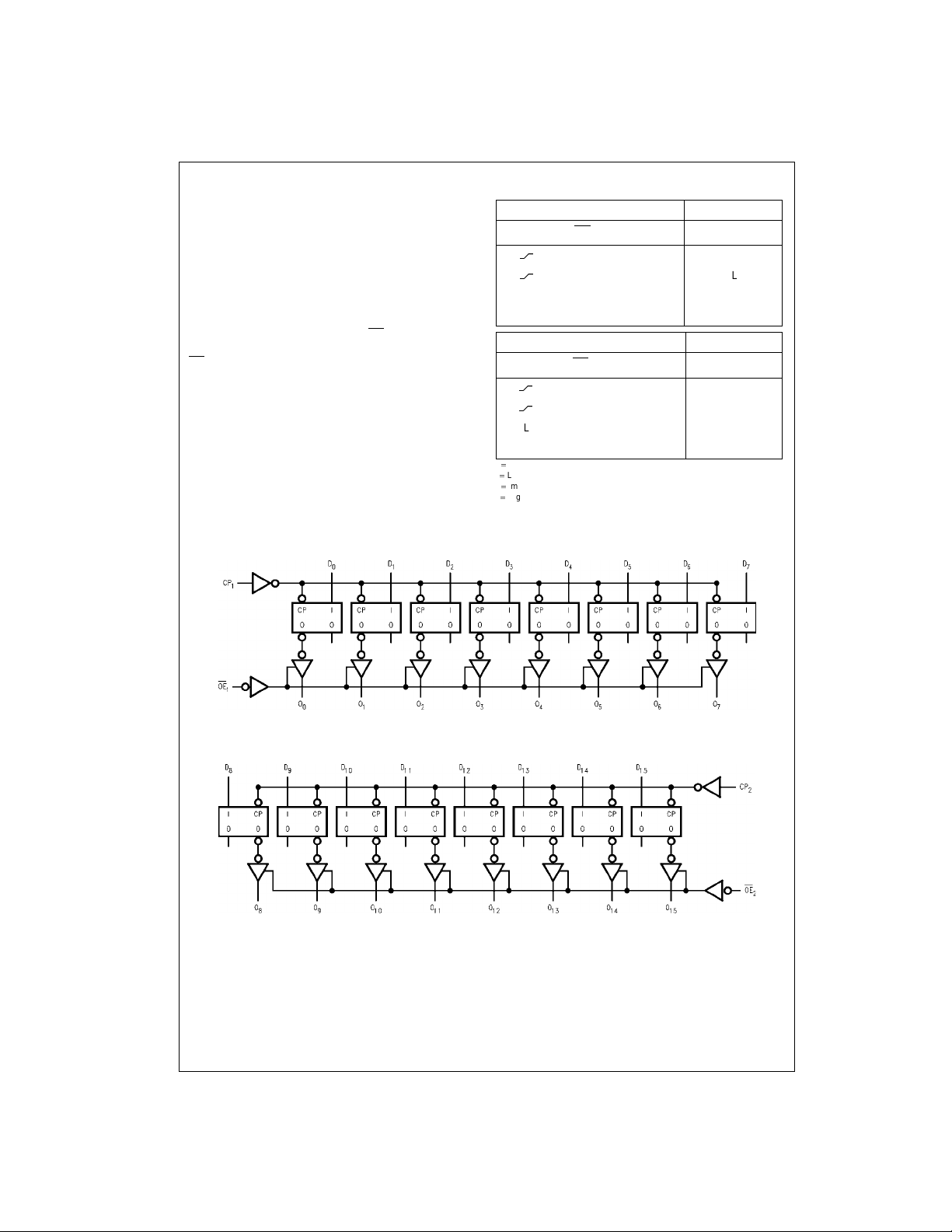

Logic Diagrams

Truth Tables

)

n

H HIGH Voltage Level

L

X

Z

Byte 1 (0:7)

Inputs Outputs

CP

OE

1

D0–D

1

7

O0–O

L H H

L L L

L L X (Previous)

X H X Z

Inputs Outputs

CP

OE

2

L H H

L L L

D8–D

2

15

O8–O

L L X (Previous)

X H X Z

LOW Voltage Level

Immaterial

High Impedance

7

15

Byte 2 (8:15)

www.fairchildsemi.com 2

Loading...

Loading...