Page 1

MF855-03

CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

S1C63000

Core CPU Manual

Page 2

NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko

Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any

liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or

circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such

as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there

is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright

infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic

products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from

the Ministry of International Trade and Industry or other approval from another government agency.

© SEIKO EPSON CORPORATION 2001 All rights reserved.

Page 3

The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1,

2001 please use the new product number. For further information, please contact Epson sales

representative.

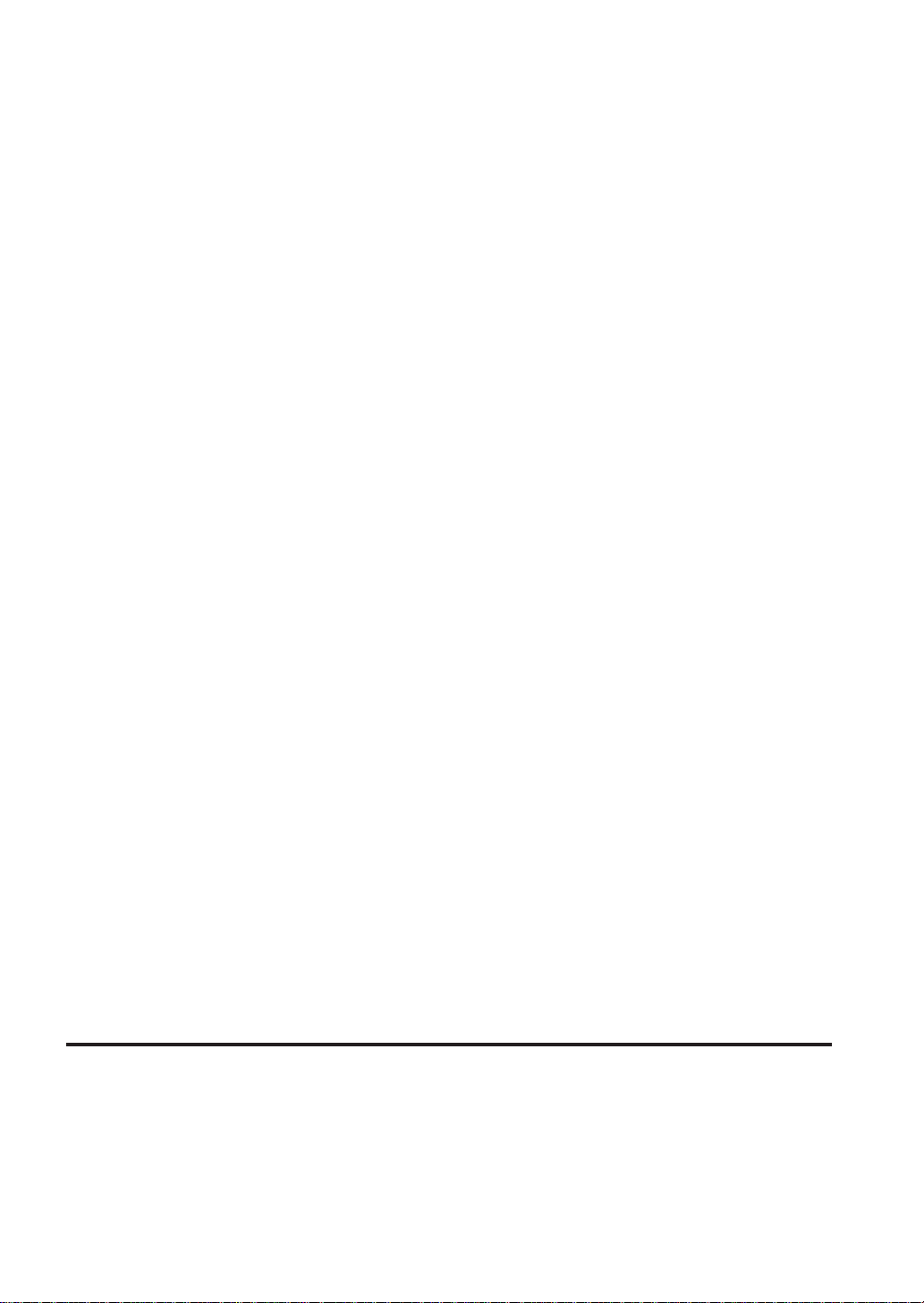

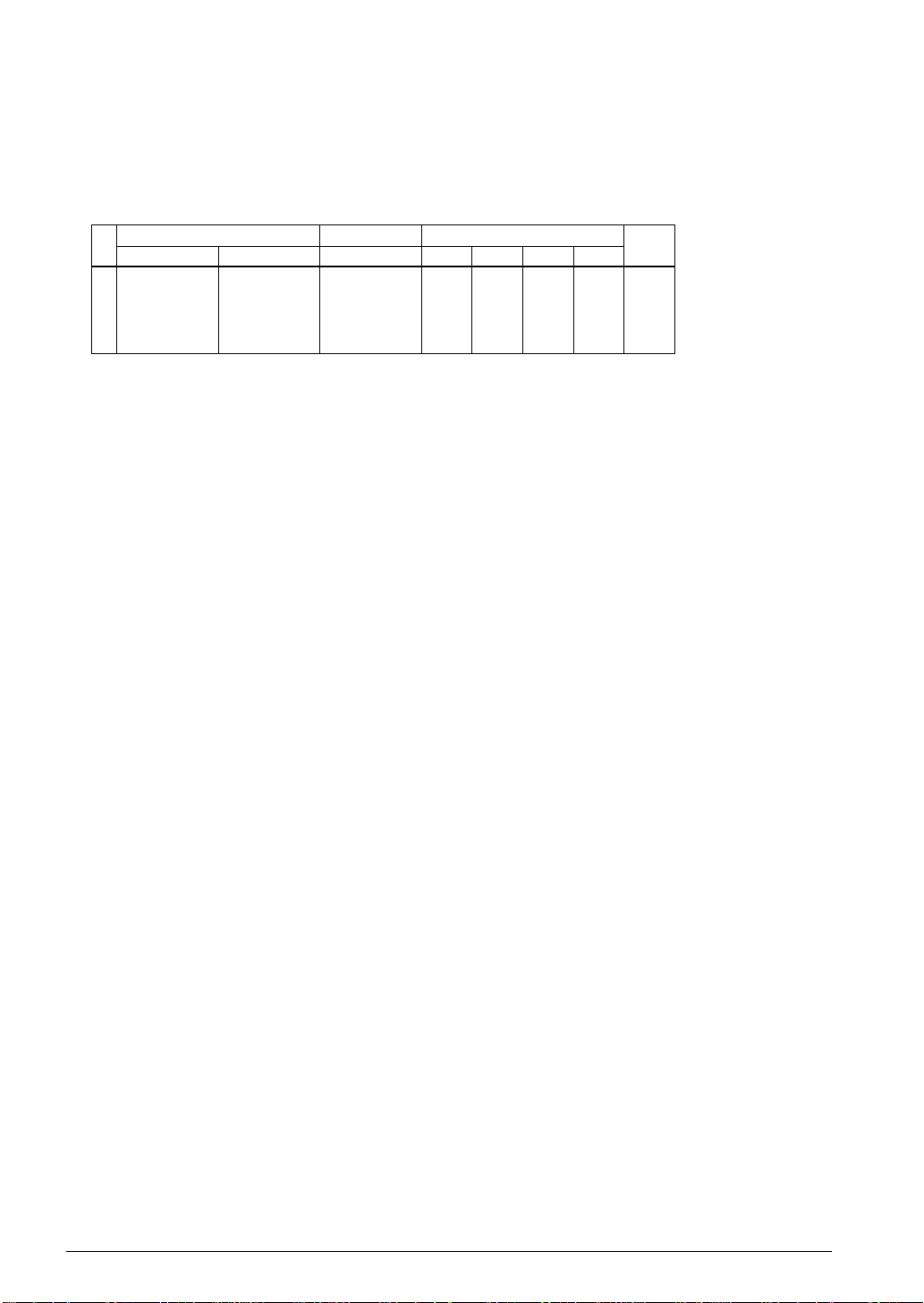

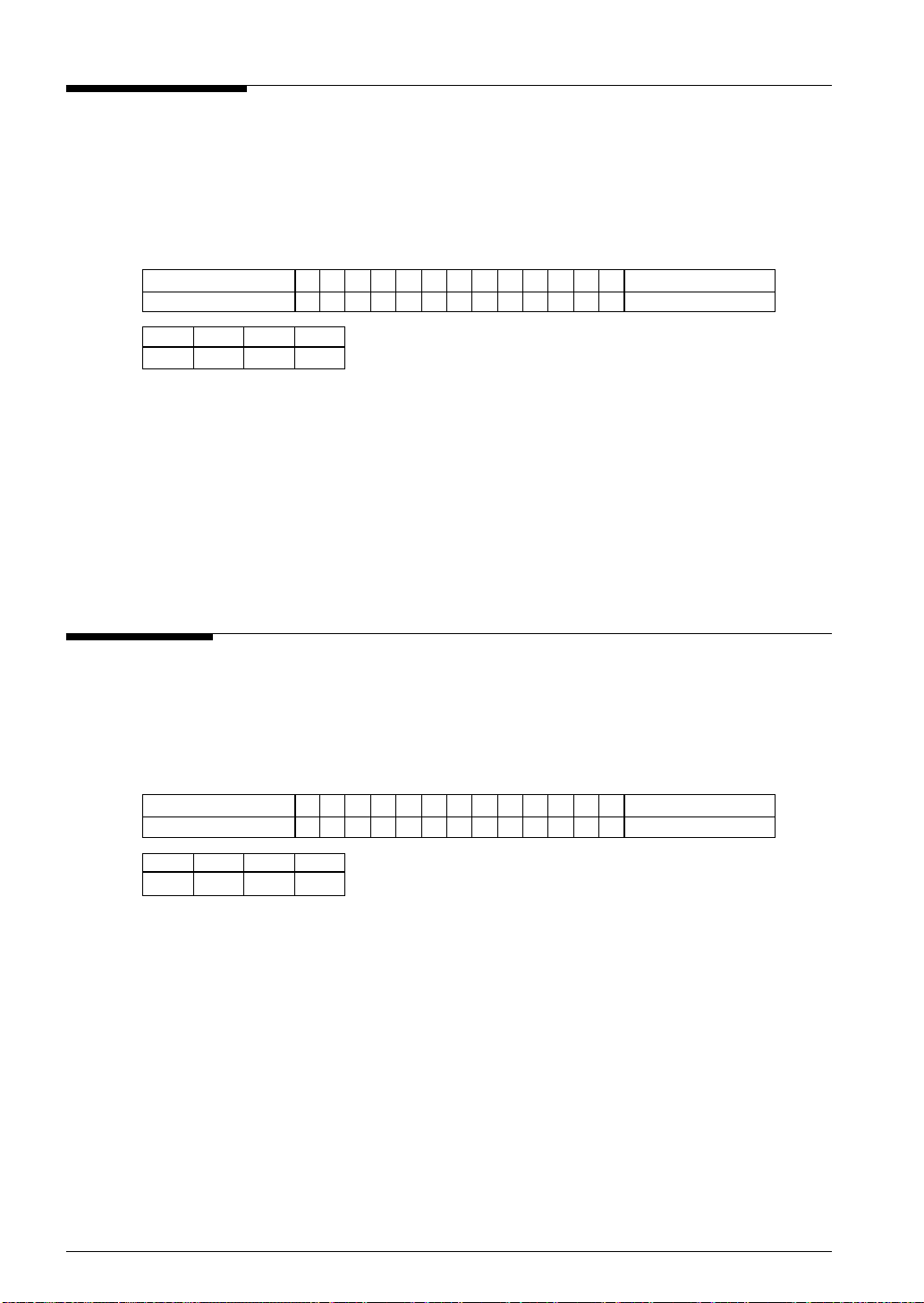

Configuration of product number

Devices

S1 C 63158 F 0A01

Development tools

S5U1

∗1: For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

∗2: Actual versions are not written in the manuals.

C 63000 A1 1

00

Packing specification

Specification

Package (D: die form; F: QFP)

Model number

Model name (C: microcomputer, digital products)

Product classification (S1: semiconductor)

00

Packing specification

Version (1: Version 1 ∗2)

Tool type (A1: Assembler Package ∗1)

Corresponding model number

(63000: common to S1C63 Family)

Tool classification (C: microcomputer use)

Product classification

(S5U1: development tool for semiconductor products)

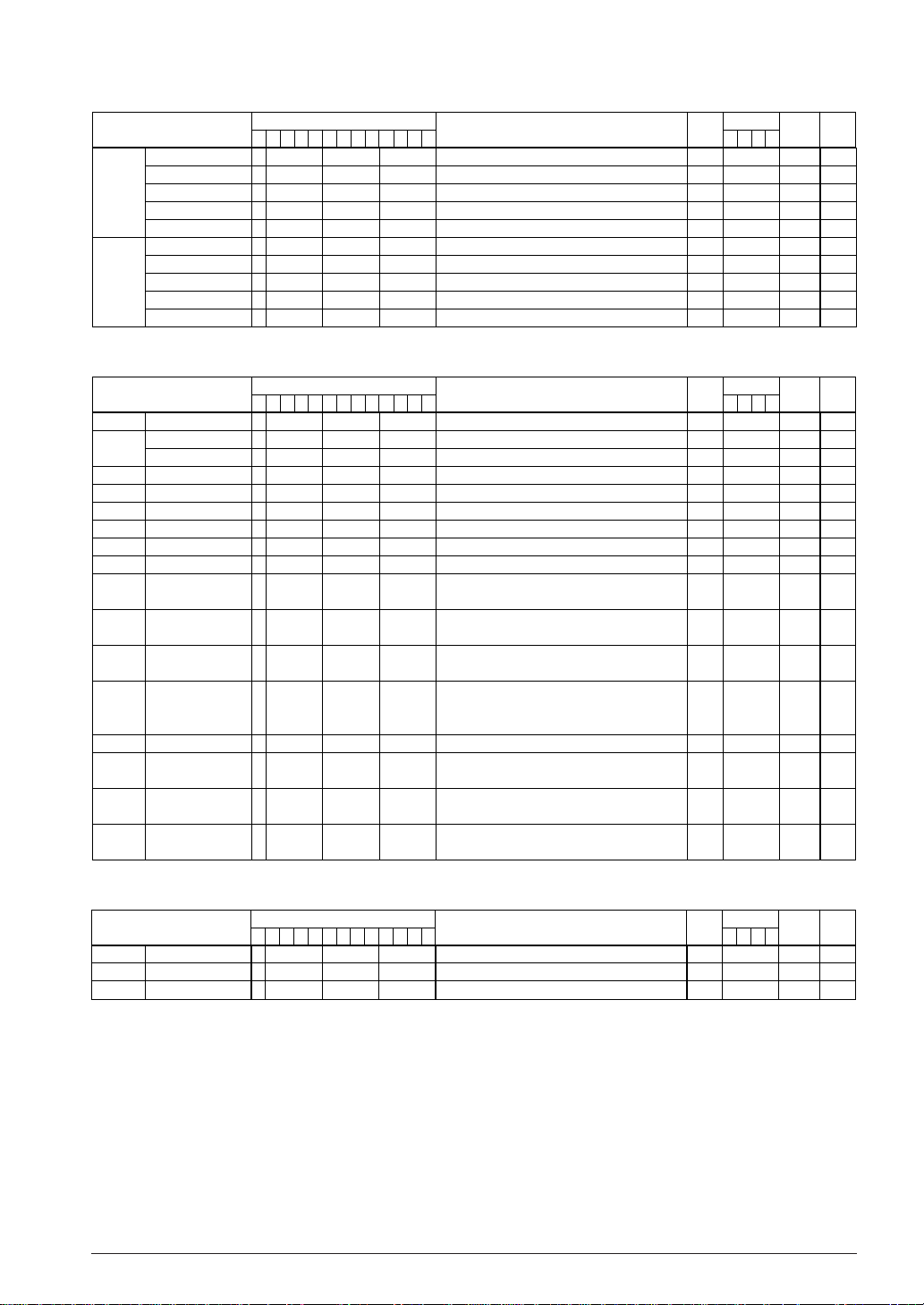

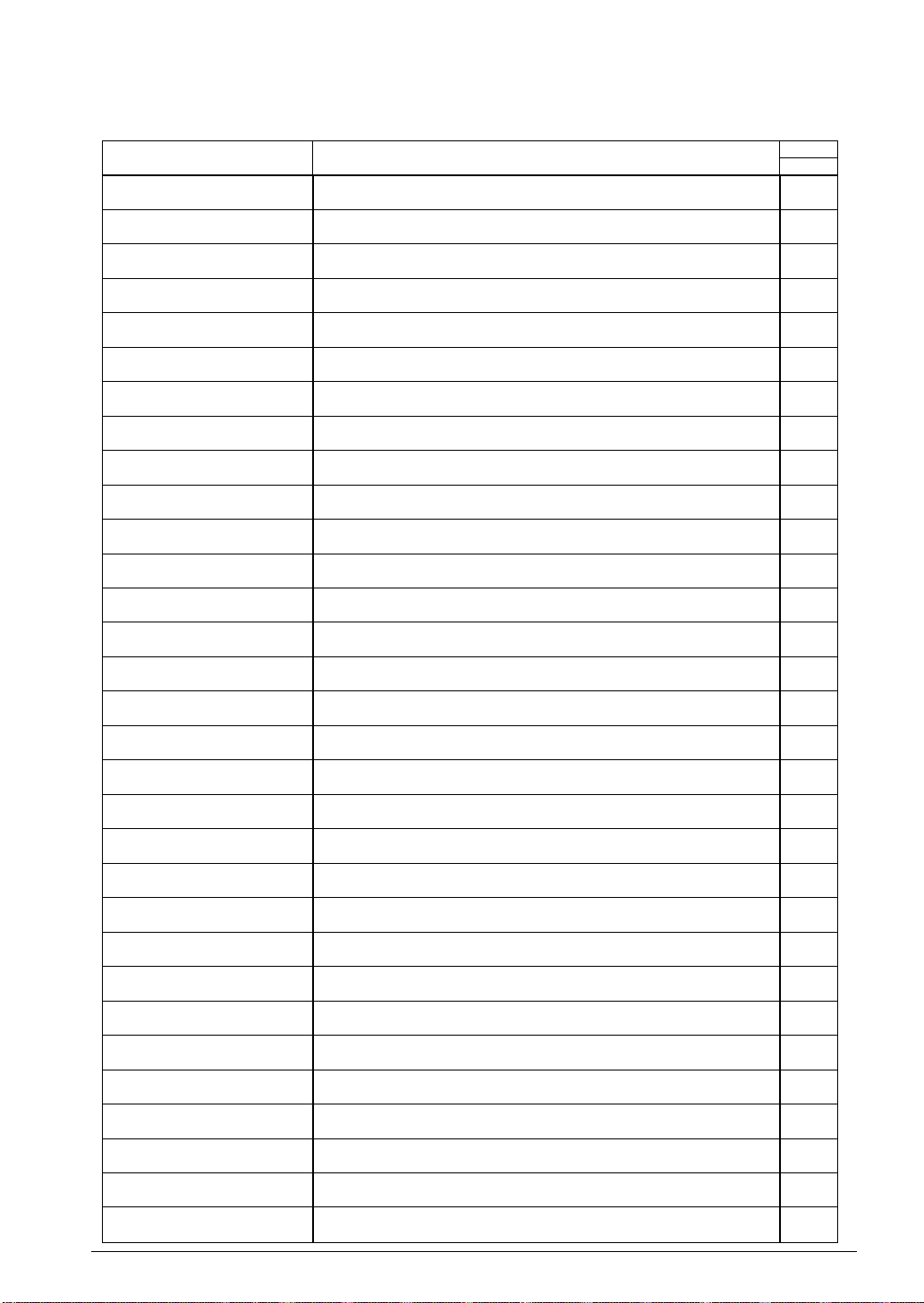

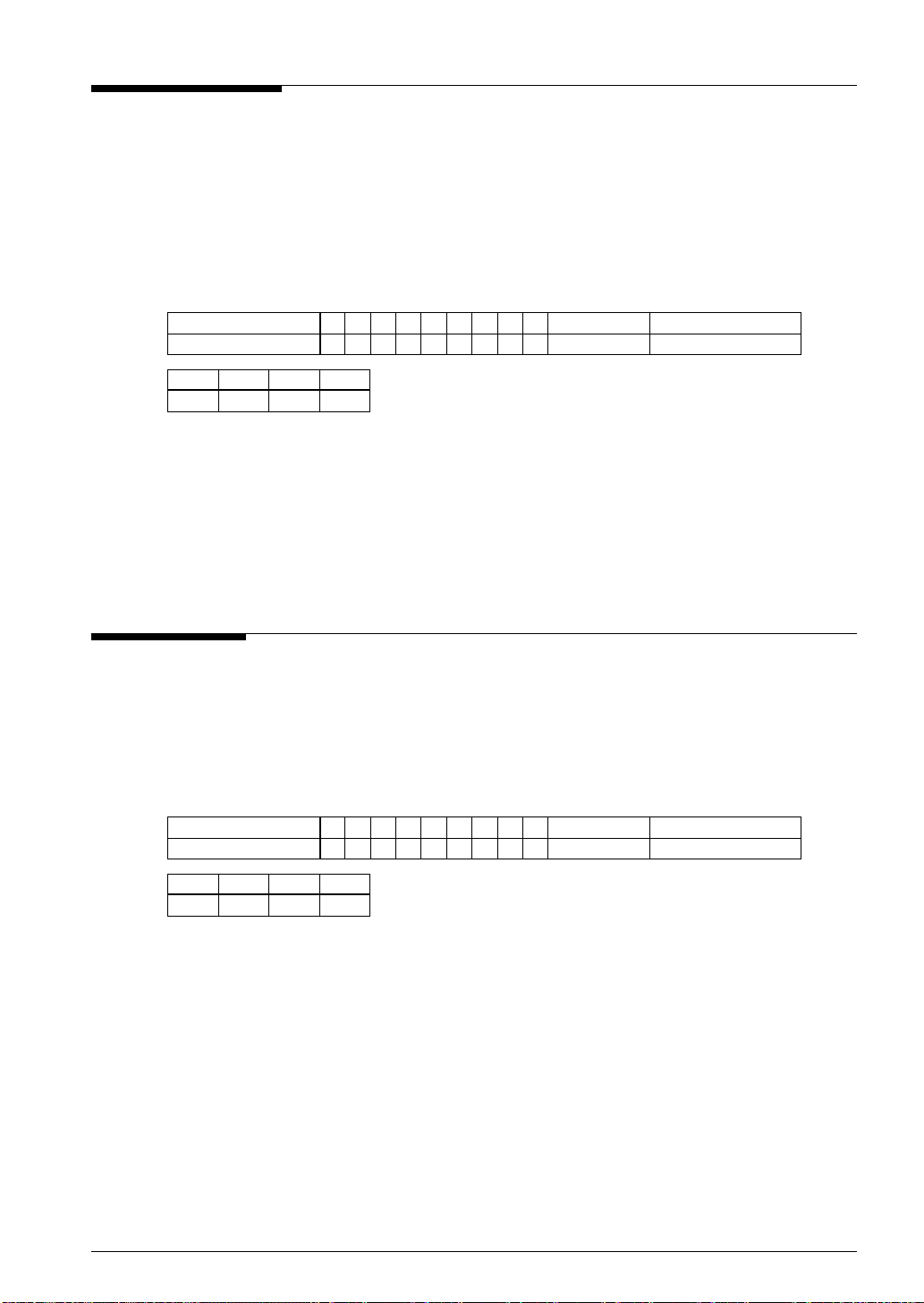

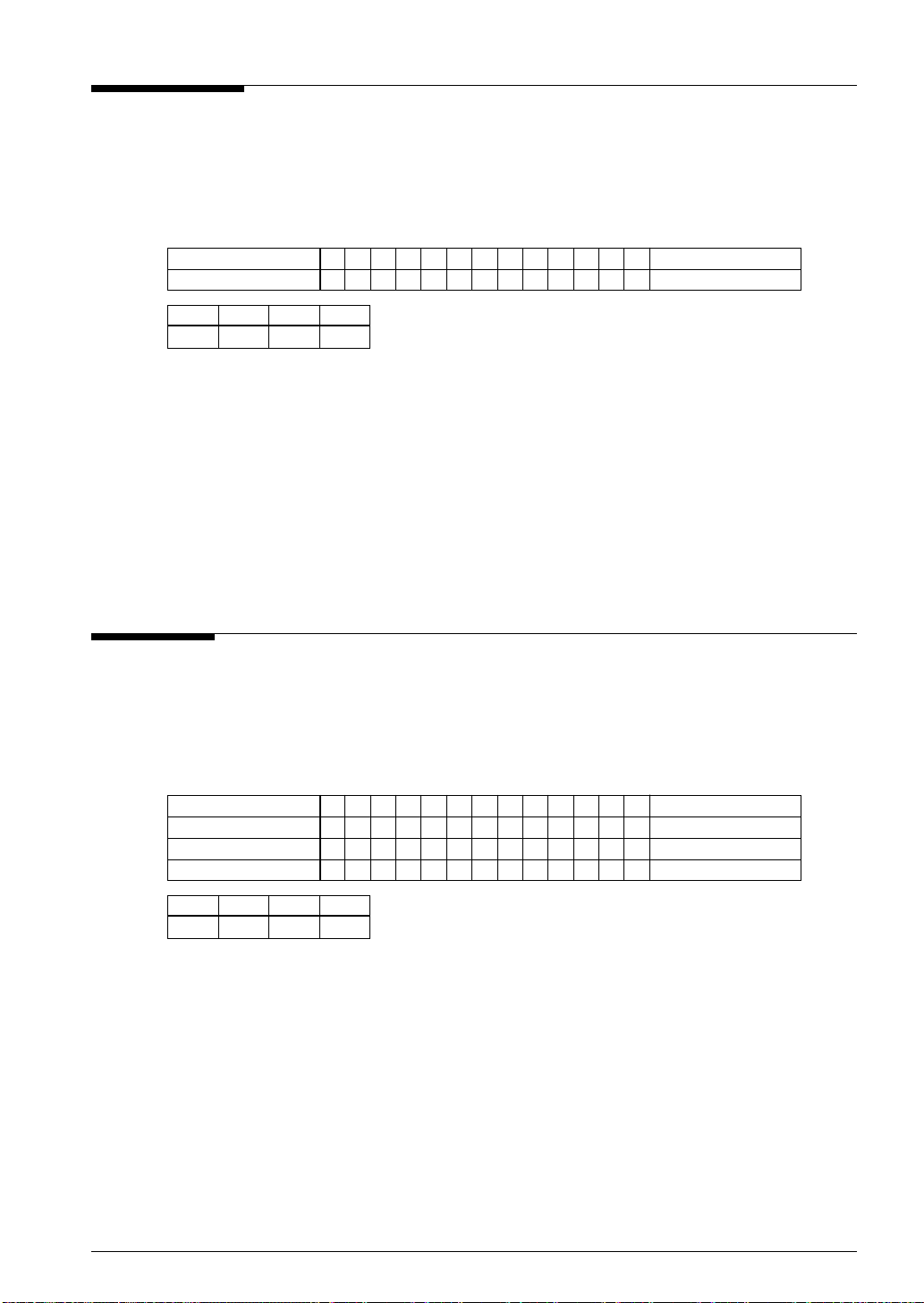

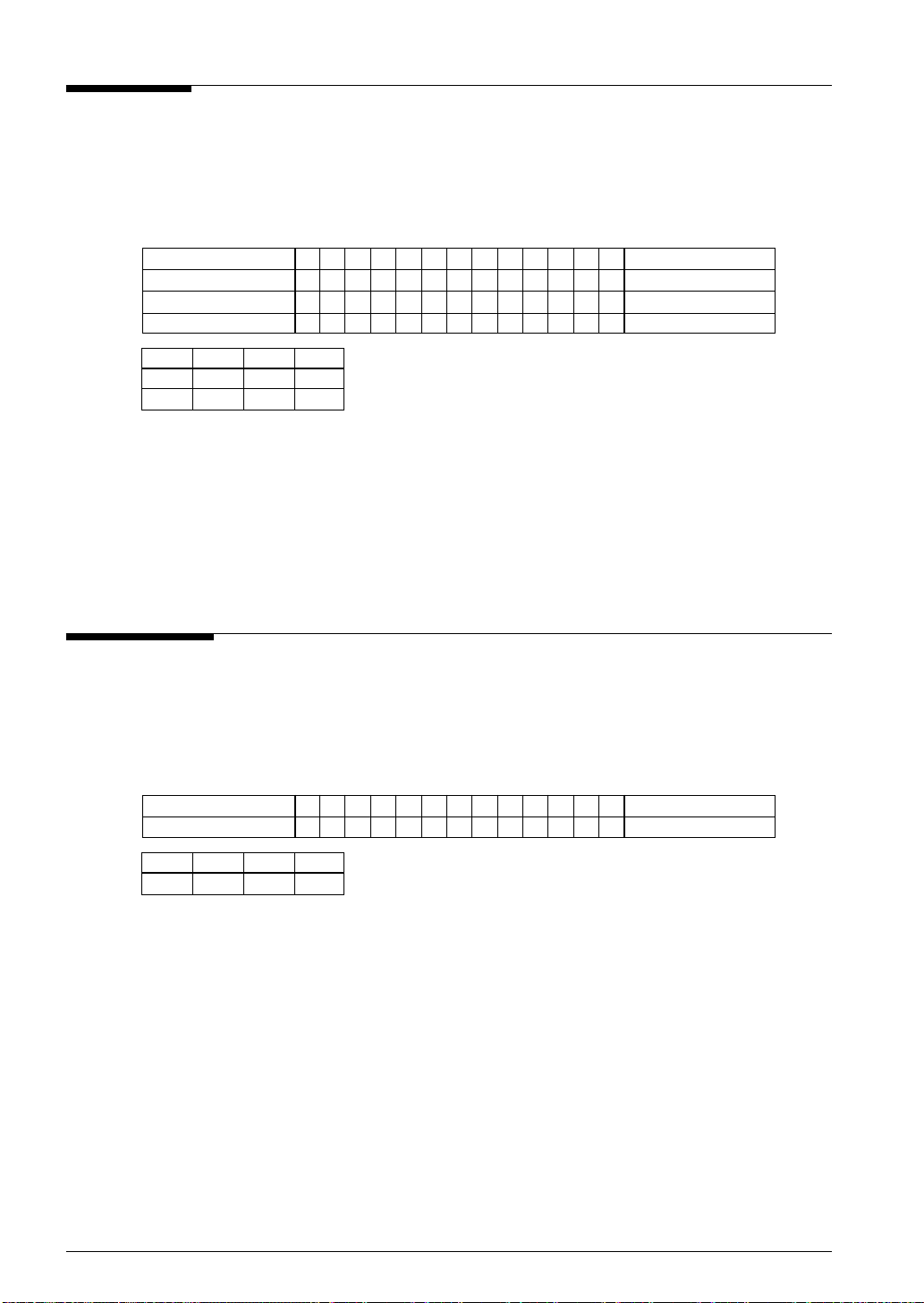

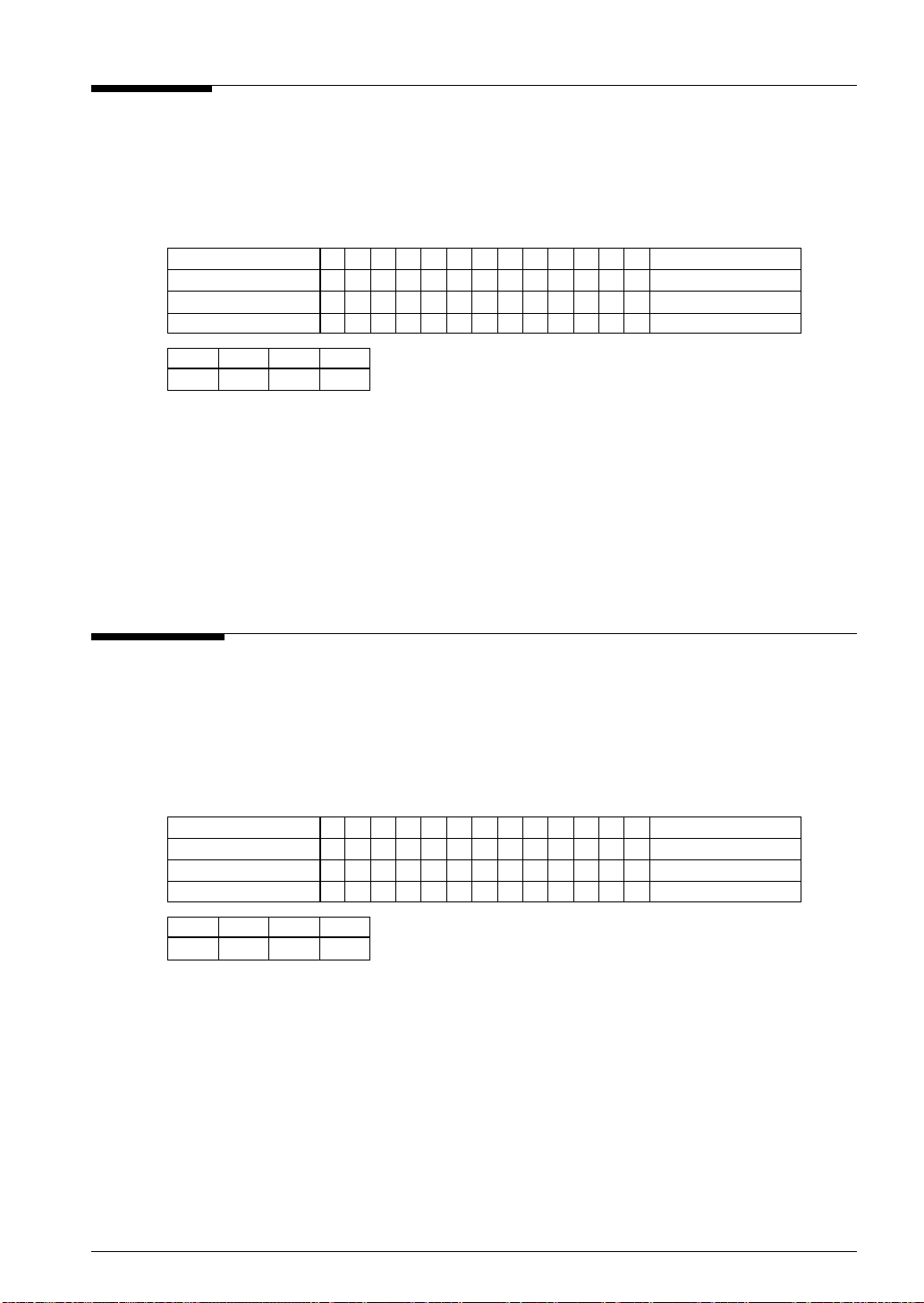

Comparison table between new and previous number

S1C63 Family processors

Previous No.

E0C63158

E0C63256

E0C63358

E0C63P366

E0C63404

E0C63406

E0C63408

E0C63F408

E0C63454

E0C63455

E0C63458

E0C63466

E0C63P466

New No.

S1C63158

S1C63256

S1C63358

S1C6P366

S1C63404

S1C63406

S1C63408

S1C6F408

S1C63454

S1C63455

S1C63458

S1C63466

S1C6P466

Previous No.

E0C63467

E0C63557

E0C63558

E0C63567

E0C63F567

E0C63658

E0C63666

E0C63F666

E0C63A08

E0C63B07

E0C63B08

E0C63B58

New No.

S1C63467

S1C63557

S1C63558

S1C63567

S1C6F567

S1C63658

S1C63666

S1C6F666

S1C63A08

S1C63B07

S1C63B08

S1C63B58

S1C63 Family peripheral products

Previous No.

E0C5250

E0C5251

New No.

S1C05250

S1C05251

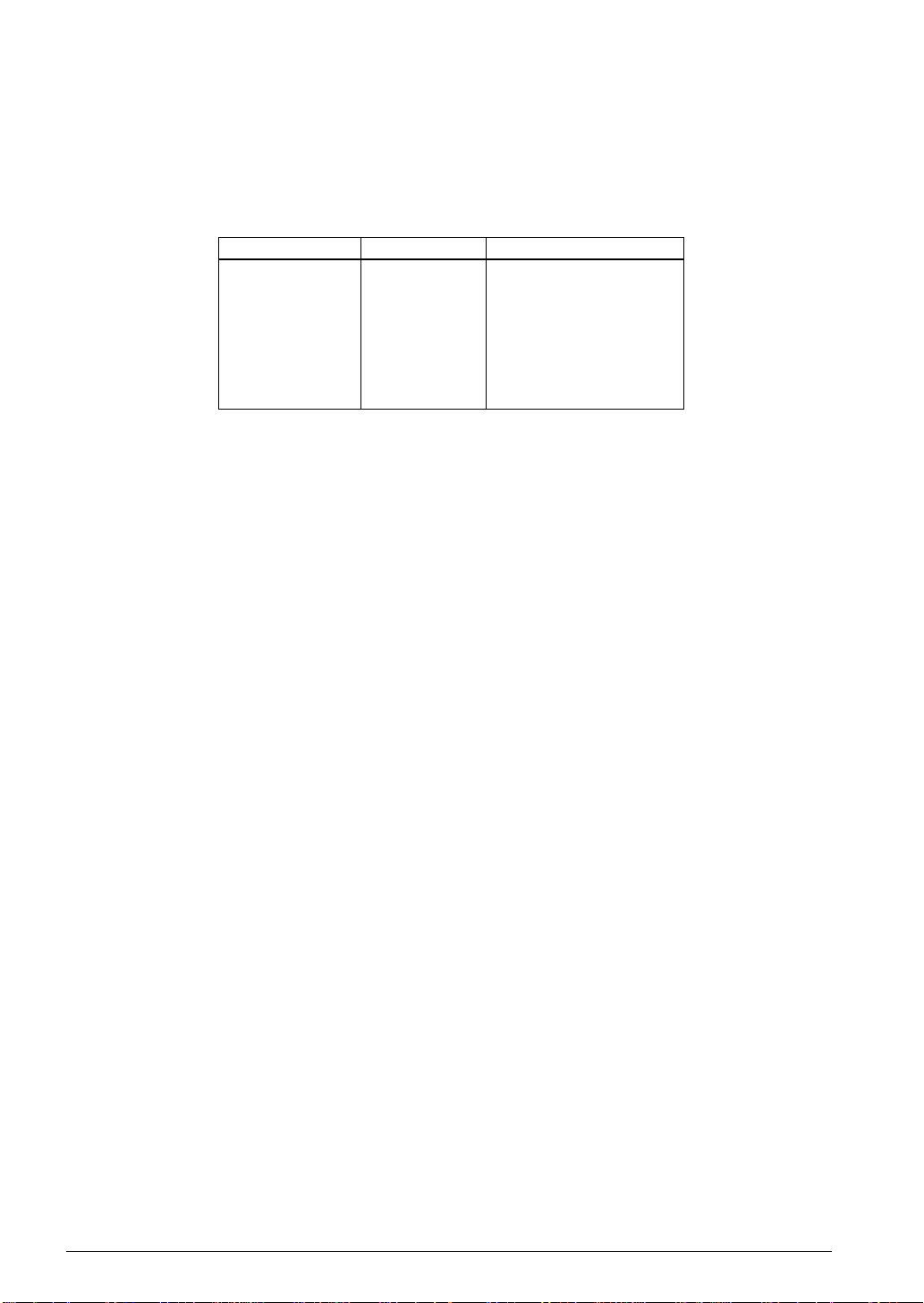

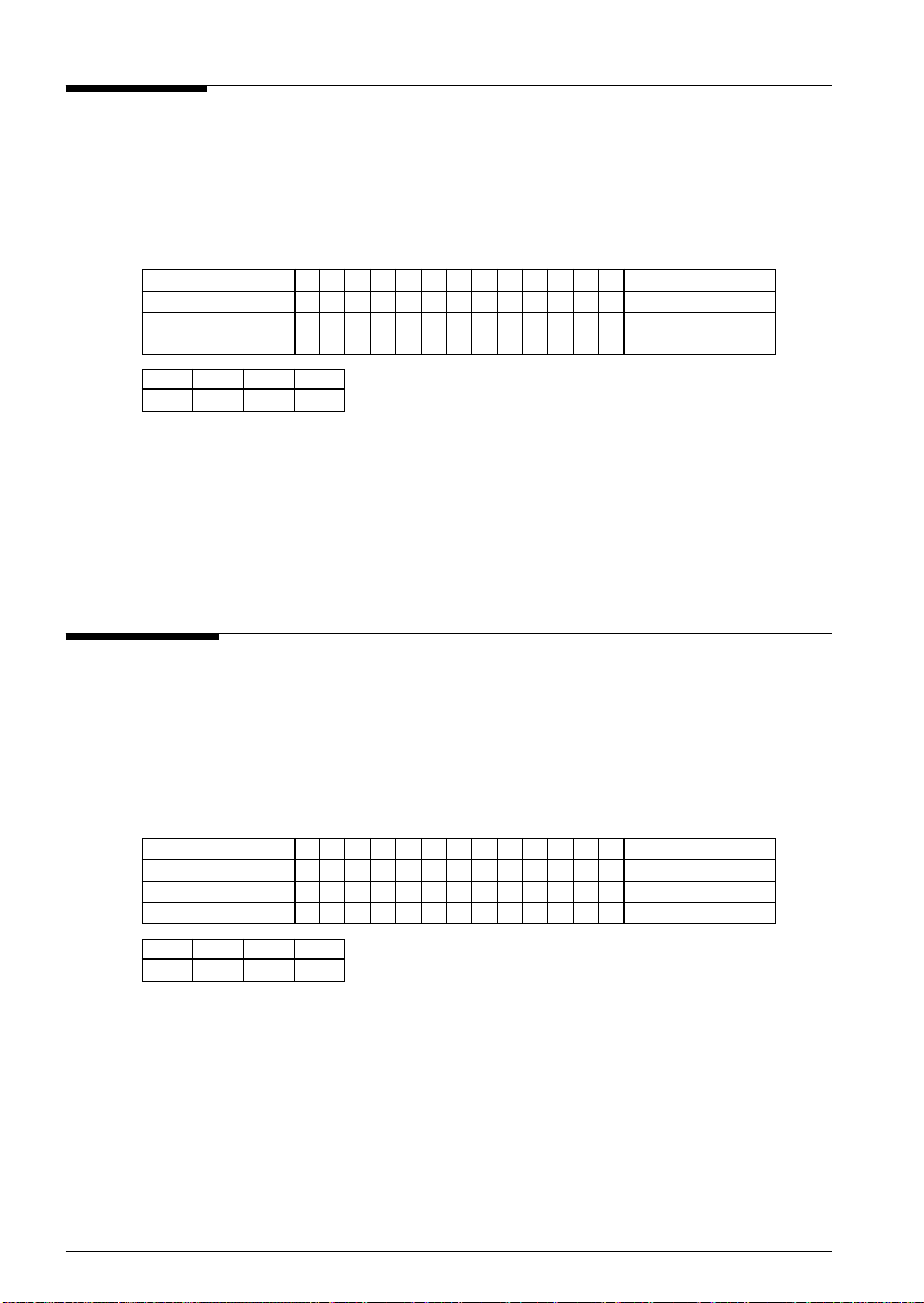

Comparison table between new and previous number of development tools

Development tools for the S1C63 Family Development tools for the S1C63/88 Family

Previous No.

ADP63366

ADP63466

ASM63

GAM63001

ICE63

PRC63001

PRC63002

PRC63004

PRC63005

PRC63006

PRC63007

URS63366

New No.

S5U1C63366X

S5U1C63466X

S5U1C63000A

S5U1C63000G

S5U1C63000H1

S5U1C63001P

S5U1C63002P

S5U1C63004P

S5U1C63005P

S5U1C63006P

S5U1C63007P

S5U1C63366Y

Previous No.

ADS00002

GWH00002

URM00002

New No.

S5U1C88000X1

S5U1C88000W2

S5U1C88000W1

Page 4

Page 5

CONTENTS

S1C63000 CORE CPU MANU AL

PREFACE

This manual explains the architecture, operation and instruction of the core CPU S1C63 of the CMOS 4-bit

single chip microcomputer S1C63 Family.

Also, since the memory configuration and the peripheral circuit configuration is different for each device

of the S1C63 Family, you should refer to the respective manuals for specific details other than the basic

functions.

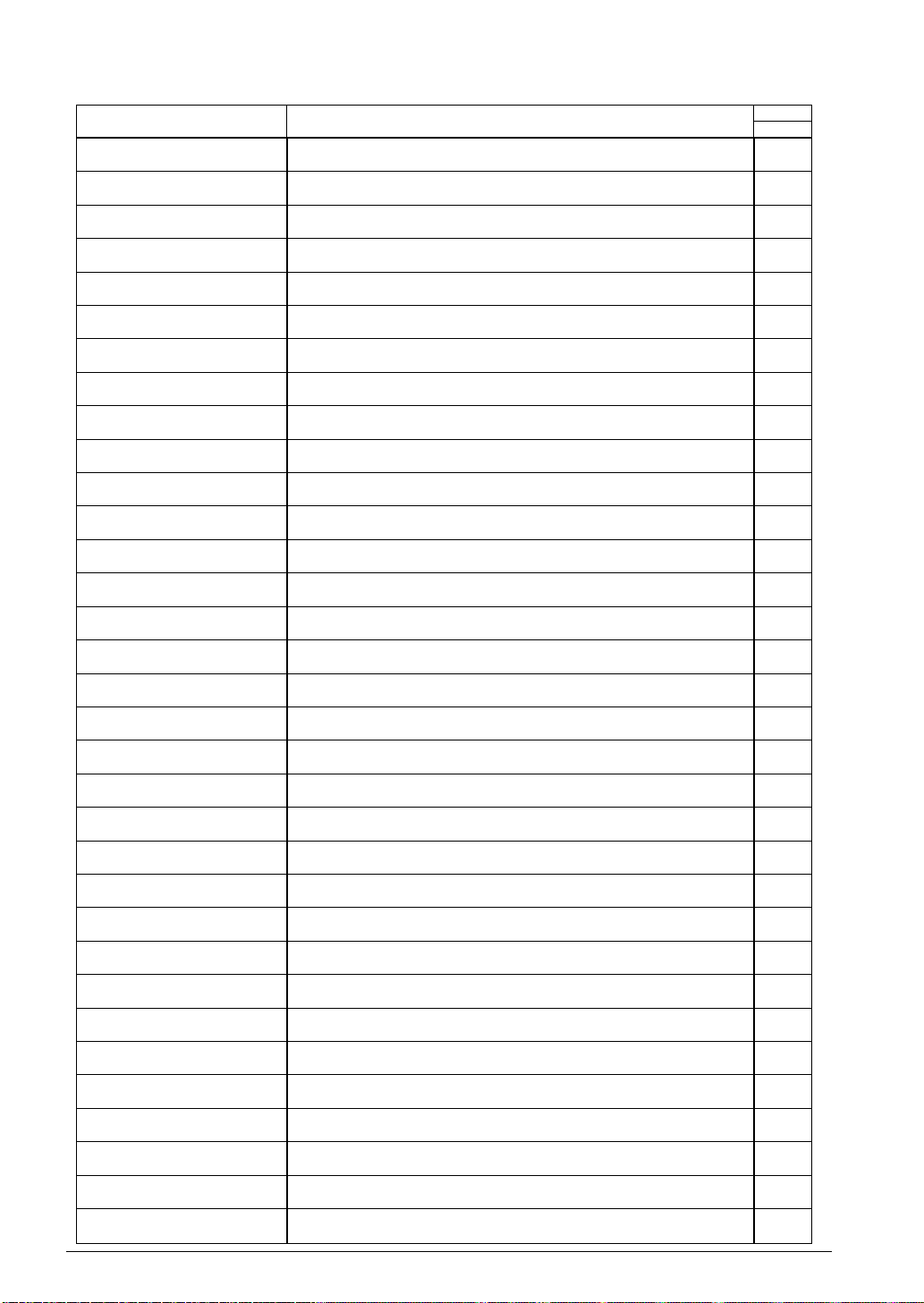

CONTENTS

CHAPTER 1OUTLINE ................................................................................................. 1

1.1 Features......................................................................................................... 1

1.2 Instruction Set Features ................................................................................1

1.3 Block Diagram ..............................................................................................2

1.4 Input-Output Signals .....................................................................................2

CHAPTER 2ARCHITECTURE ........................................................................................ 4

2.1 ALU and Registers ........................................................................................ 4

2.1.1 ALU ............................................................................................................. 4

2.1.2 Register configuration ................................................................................ 4

2.1.3 Flags ........................................................................................................... 5

2.1.4 Arithmetic operations with numbering system............................................ 7

2.1.5 EXT register and data extension ................................................................. 8

2.2 Program Memory ......................................................................................... 11

2.2.1 Configuration of program memory ............................................................ 11

2.2.2 PC (program counter)................................................................................ 11

2.2.3 Branch instructions .................................................................................... 12

2.2.4 Table look-up instruction ........................................................................... 16

2.3 Data Memory ............................................................................................... 17

2.3.1 Configuration of data memory................................................................... 17

2.3.2 Addressing for data memory ...................................................................... 18

2.3.3 Stack and stack pointer .............................................................................. 19

2.3.4 Memory mapped I/O .................................................................................. 21

CHAPTER 3 CPU OPERATION.................................................................................... 22

3.1 Timing Generator and Bus Cycle................................................................. 22

3.2 Instruction Fetch and Execution ..................................................................22

3.3 Data Bus (Data Memory) Control ............................................................... 23

3.3.1 Data bus status........................................................................................... 23

3.3.2 High-impedance control ............................................................................ 23

3.3.3 Interrupt vector read.................................................................................. 24

3.3.4 Memory write ............................................................................................. 24

3.3.5 Memory read .............................................................................................. 25

3.4 Initial Reset .................................................................................................. 25

3.4.1 Initial reset sequence ................................................................................. 25

3.4.2 Initial setting of internal registers ............................................................. 26

S1C63000 CORE CPU MANUAL EPSON i

Page 6

CONTENTS

3.5 Interrupts...................................................................................................... 26

3.5.1 Interrupt vectors ........................................................................................ 26

3.5.2 Interrupt sequence ..................................................................................... 27

3.5.3 Notes for interrupt processing ................................................................... 30

3.6 Standby Status ..............................................................................................31

3.6.1 HALT status................................................................................................ 31

3.6.2 SLEEP status.............................................................................................. 31

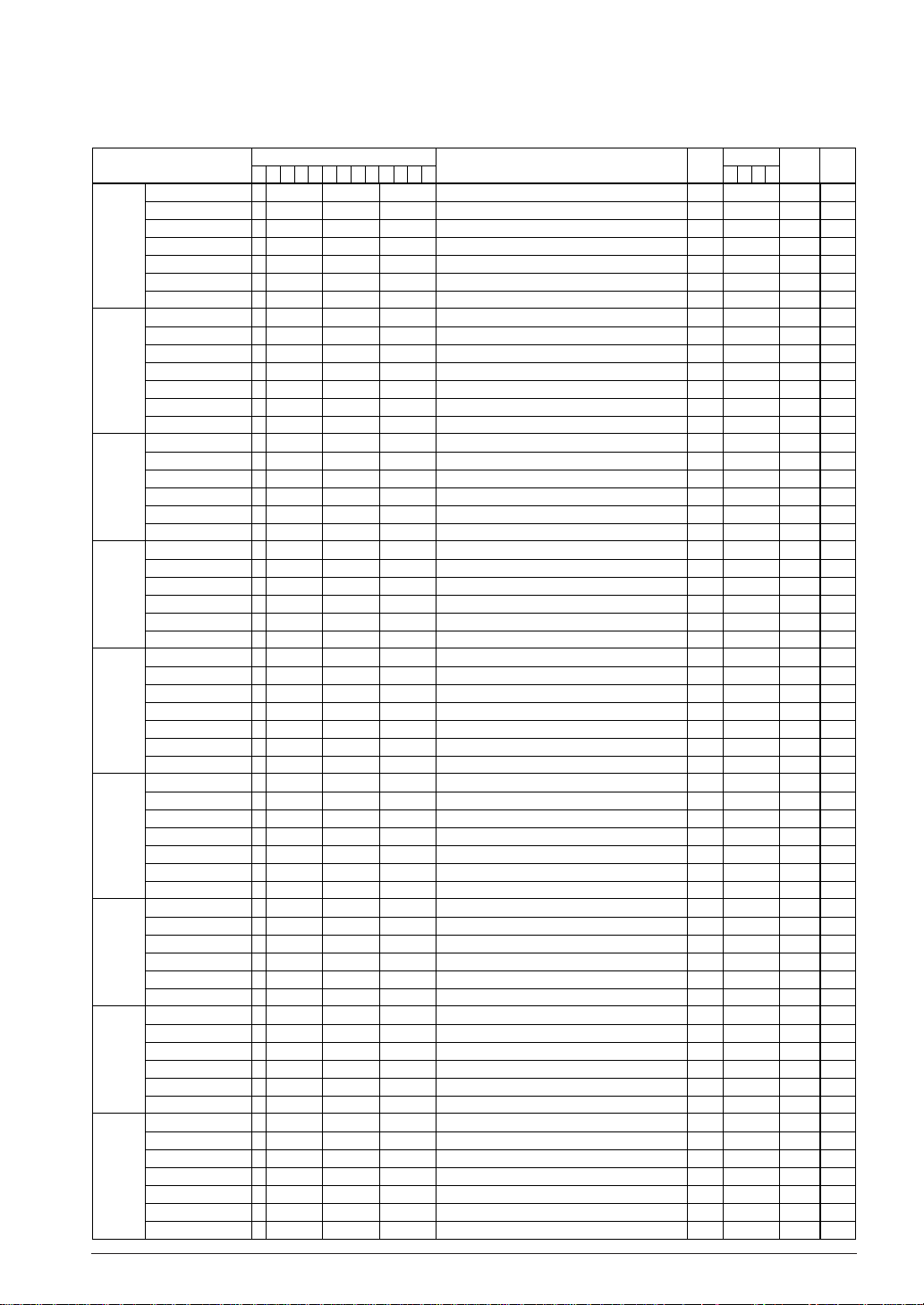

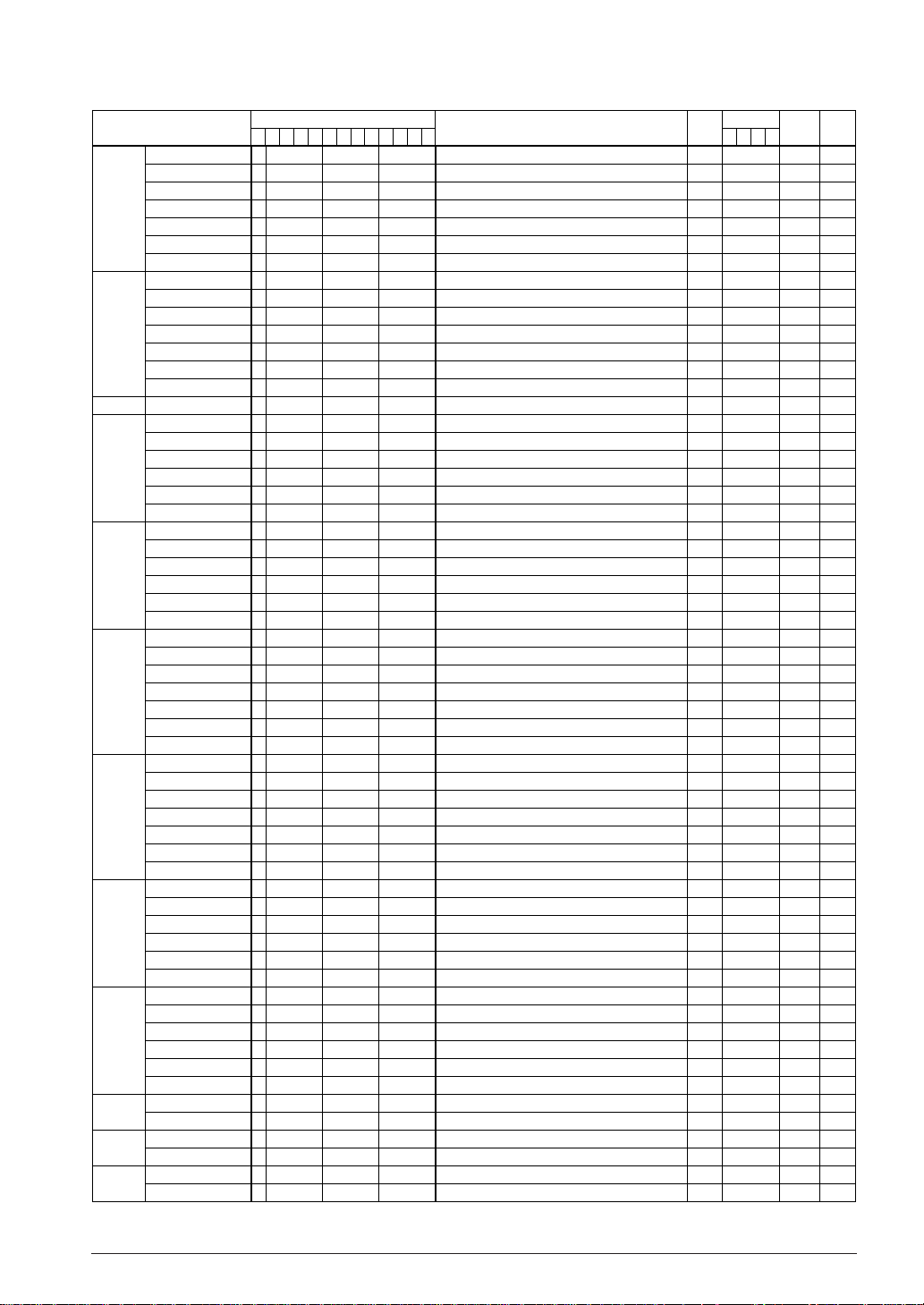

CHAPTER 4INSTRUCTION SET ................................................................................... 33

4.1 Addressing Mode.......................................................................................... 33

4.1.1 Basic addressing modes ............................................................................. 33

4.1.2 Extended addressing mode......................................................................... 35

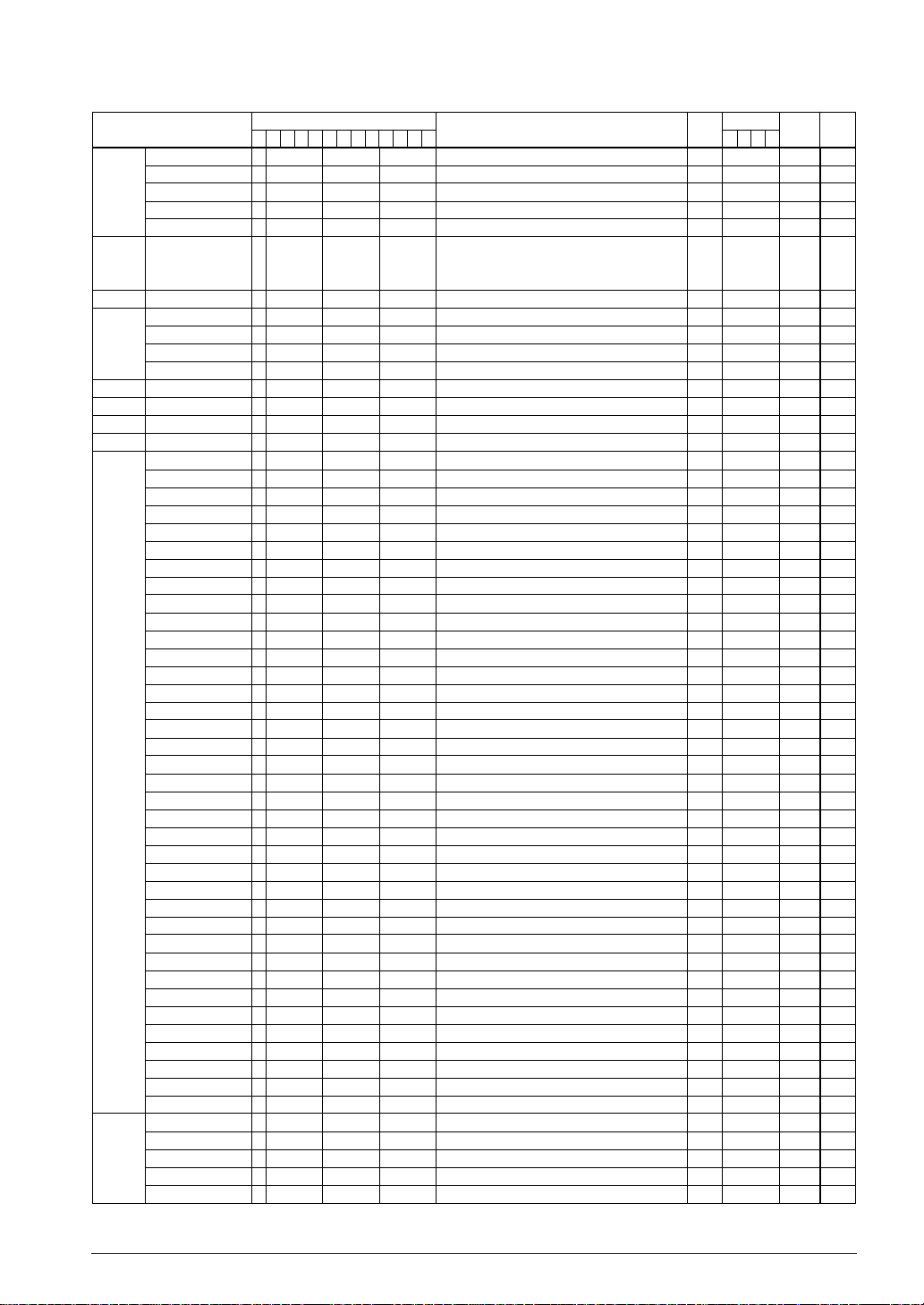

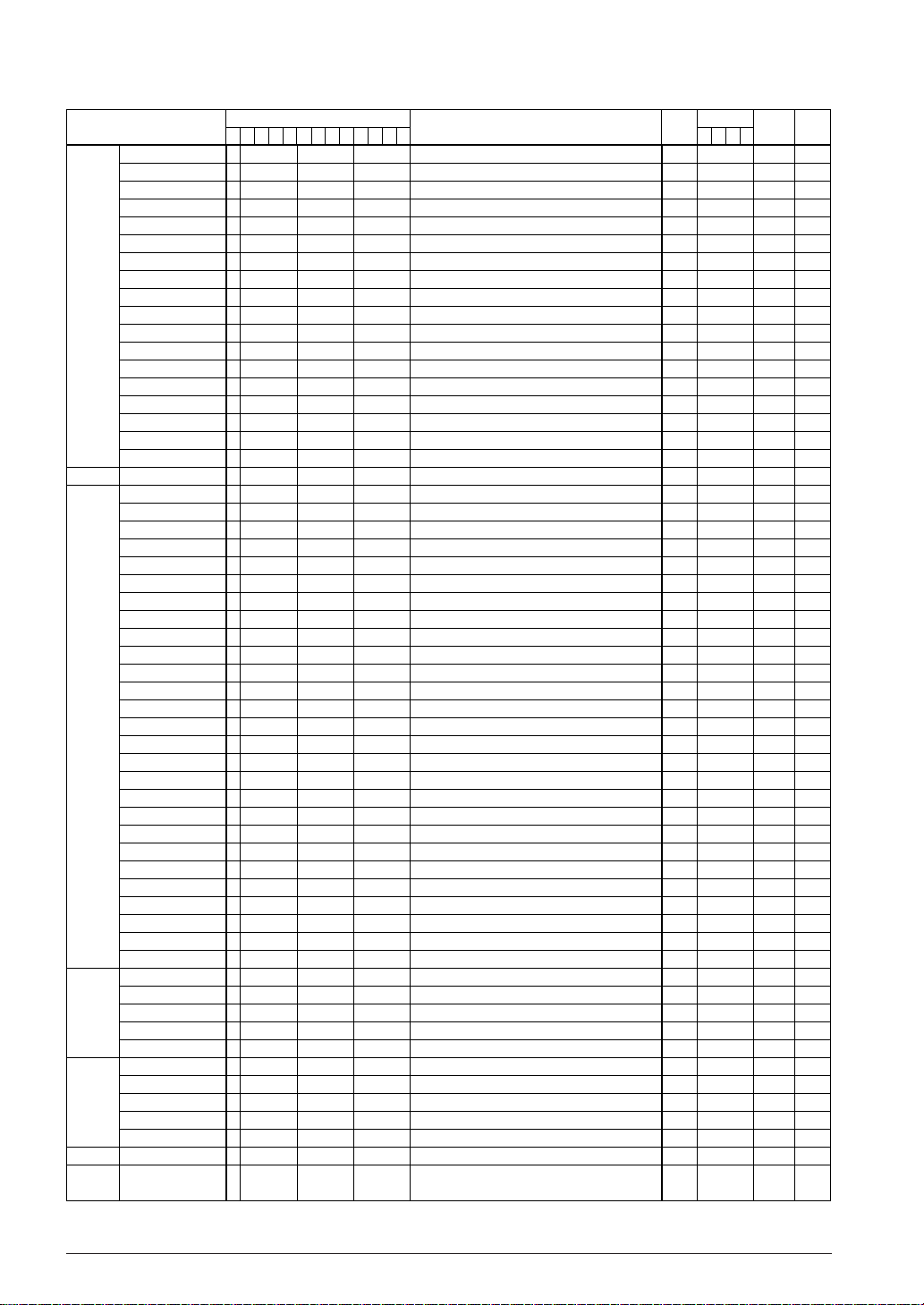

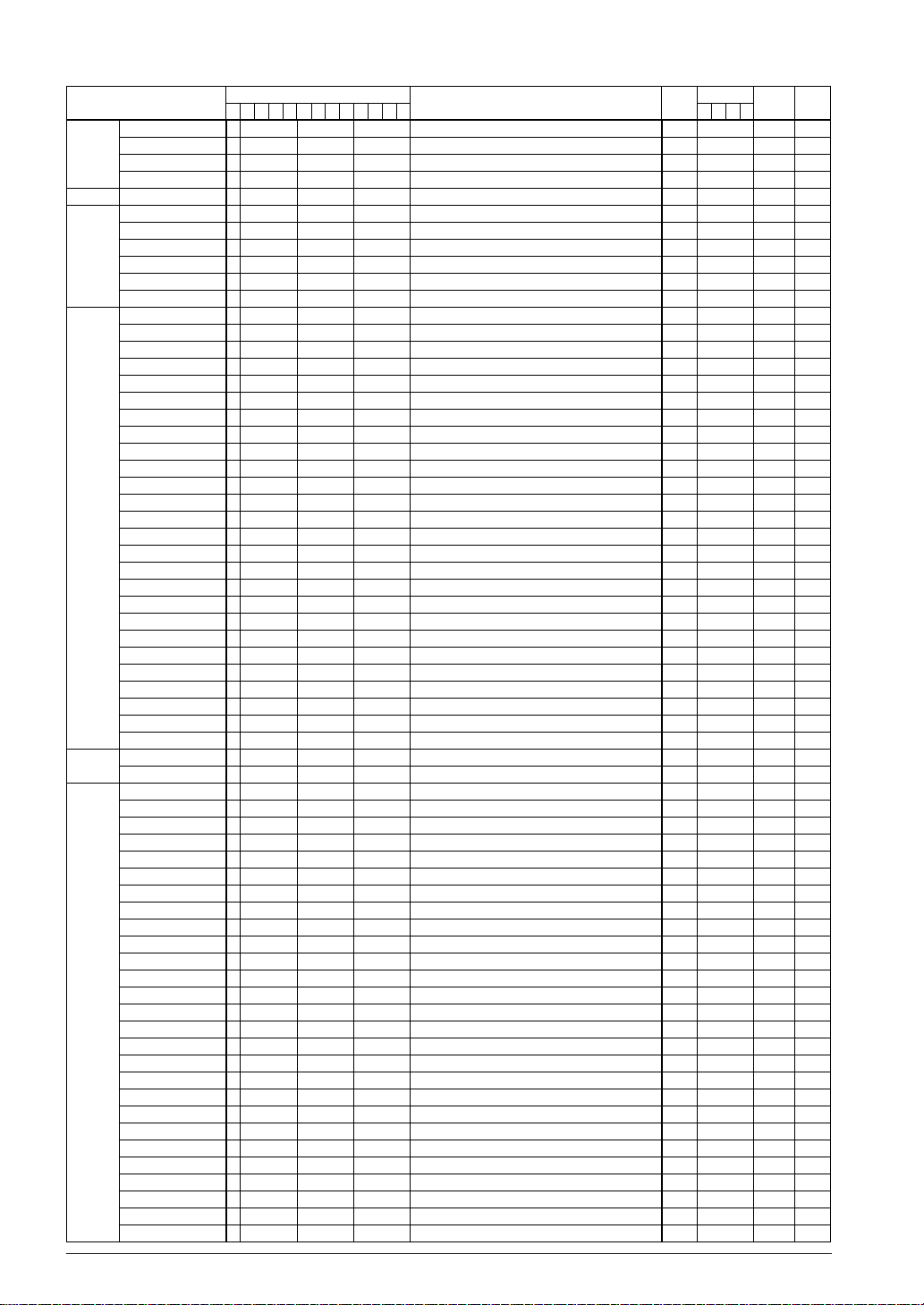

4.2 Instruction List ............................................................................................. 37

4.2.1 Function classification............................................................................... 37

4.2.2 Symbol meanings ....................................................................................... 38

4.2.3 Instruction list by function ......................................................................... 40

4.2.4 List in alphabetical order........................................................................... 48

4.2.5 List of extended addressing instructions.................................................... 55

4.3 Instruction Formats...................................................................................... 59

4.4 Detailed Explanation of Instructions ........................................................... 60

ii EPSON S1C63000 CORE CPU MANUAL

Page 7

CHAPTER 1: OUTLINE

CHAPTER 1OUTLINE

The S1C63000 is the core CPU of the 4-bit single chip microcomputer S1C63 Family that utilizes

original EPSON architecture. It has a large and linear addressable space, maximum 64K words (13 bits/

word) program memory (code ROM area) and maximum 64K words (4 bits/word) data memory (RAM,

data ROM and I/O area), and high speed, abundant instruction sets. It operates in a wide range of supply

voltage and features low power consumption. Furthermore, modularization of programs can be done

easily because the program memory does not need bank and page management and relocatable programming is possible.

In addition, it has adopted a unified architecture and a peripheral circuit interface in memory mapped I/O

method to flexibly meet future expansion of the S1C63 Family.

1.1 Features

The S1C63000 boasts the below features.

Program memory Maximum 64K × 13 bits (linear address, non-page method)

Data memory Maximum 64K × 4 bits

Basic instruction set 47 types with 5 types of basic addressing modes and 3 types of extended

addressing modes

Instruction cycle 1 cycle (2 clocks), 2 cycles (4 clocks) and 3 cycles (6 clocks)

Register configuration Data register 2 × 4 bits

Index register 2 × 16 bits

Address extension register 8 bits

Program counter 16 bits

Stack pointer 2 × 8 bits

Condition flag 4 bits

Queue register 16 bits

Interrupt function NMI (Non Maskable Interrupt) vector 1

Hardware interrupt vector Maximum 15 vectors

Software interrupt vector Maximum 63 vectors

Standby function HALT/SLEEP

Peripheral circuit interface Memory mapped I/O method

Pipeline processing 2 stages (fetch and execution) pipeline processing

1.2 Instruction Set Features

(1) It adopts high efficiency machine cycles, high speed and abundant instruction set.

Almost all standard instructions operate in 1 cycle (2 clock).

(2) Both the program space and the data space are designed as a 64K-word linear space without page

concept and can be addressed with 1 instruction.

(3) The instruction system includes relocatable jump instructions and allows a relocatable programming.

Thus modular programming and software library development can be realized easily, and it increases

an efficiency for developing applications.

(4) Memory management can be done easily by 5 types of basic addressing modes, 3 types of extended

addressing modes with the address extension register and 16-bit operation function that is useful in

address calculations.

(5) 8-bit data processing is possible using the table look-up instruction and other instructions.

(6) Some instructions support a numbering system, thus binary to hexadecimal software counters can be

made easily.

S1C63000 CORE CPU MANUAL EPSON 1

Page 8

CHAPTER 1: OUTLINE

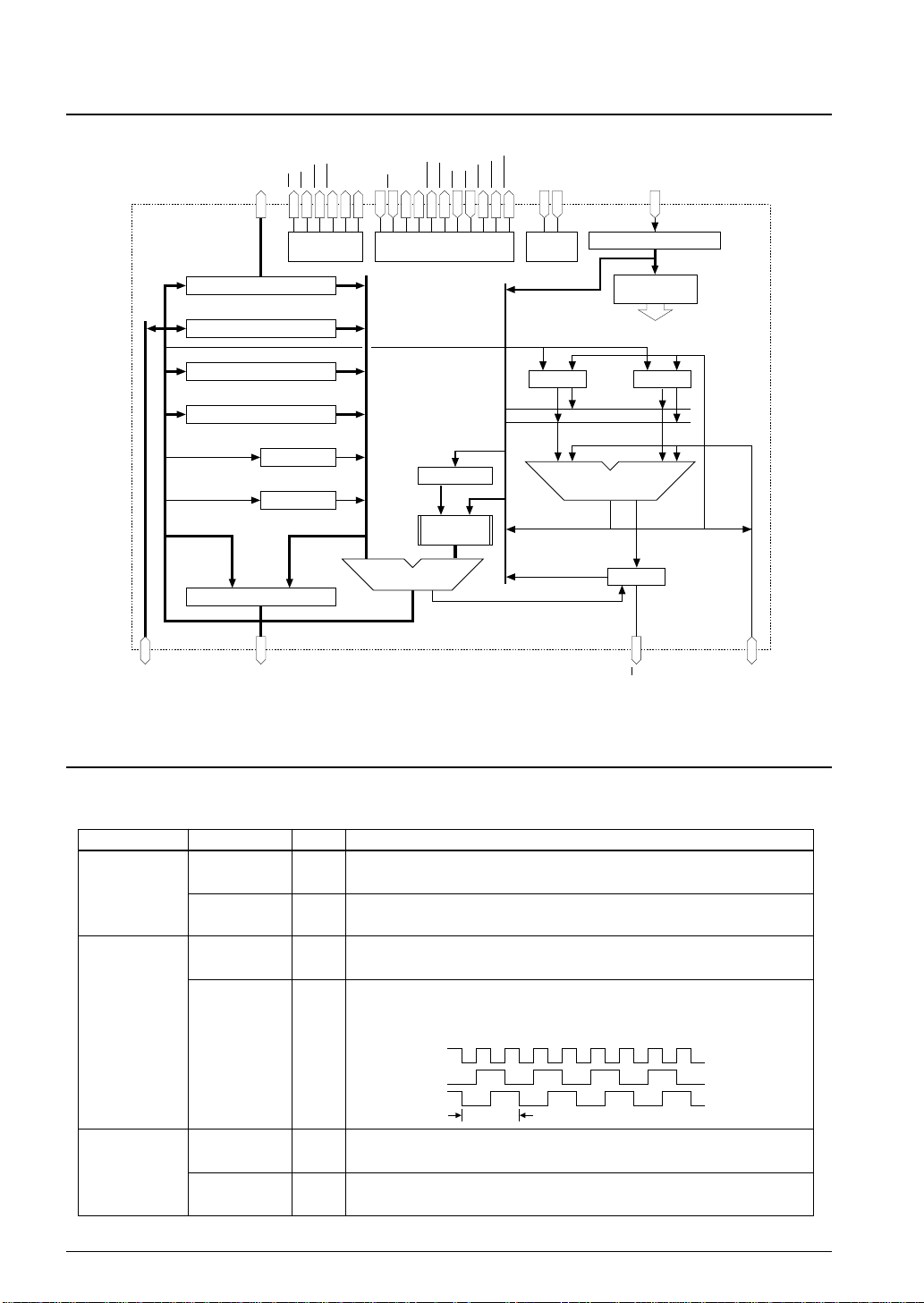

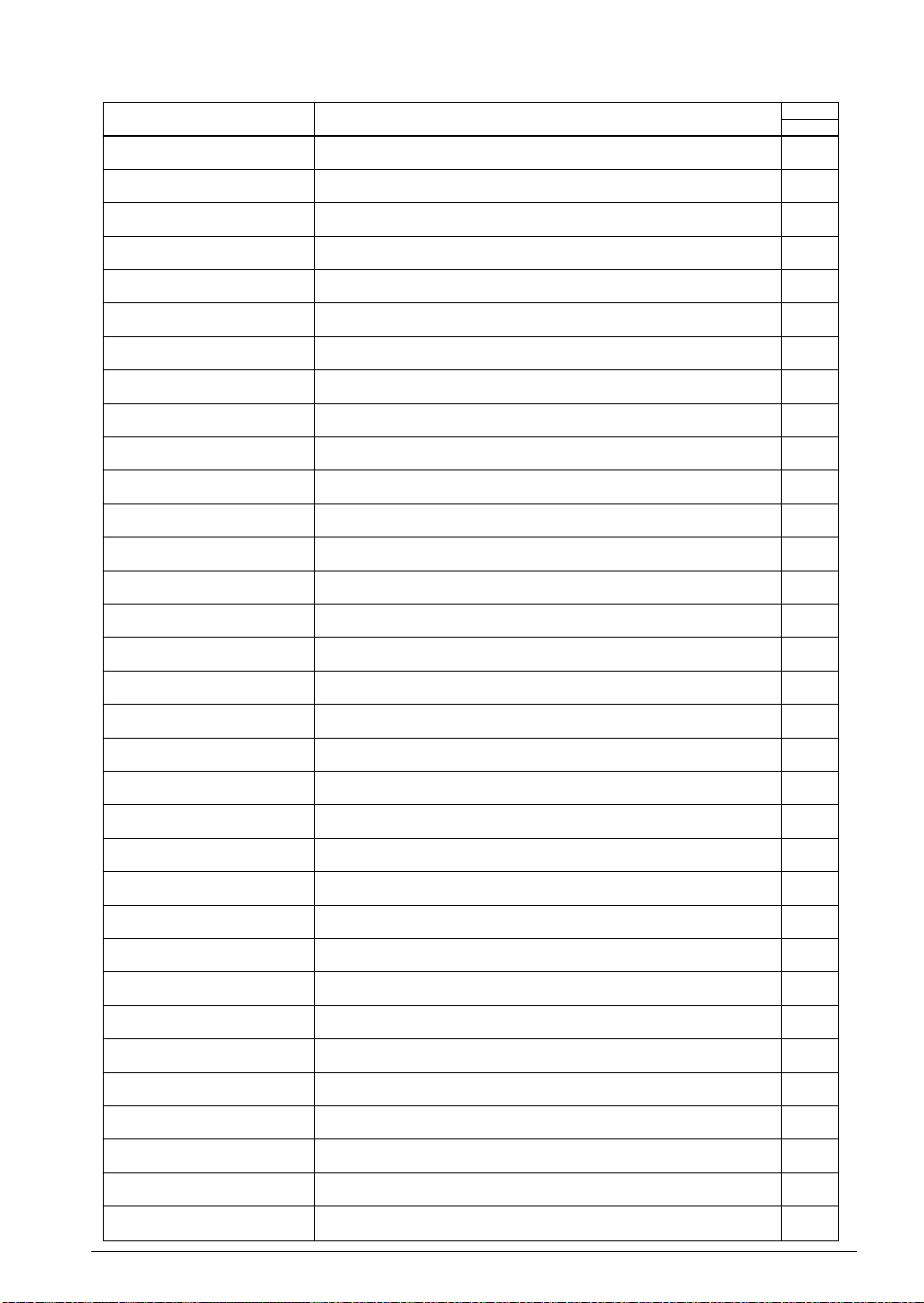

1.3 Block Diagram

Figure 1.3.1 shows the S1C63000 block diagram.

M00

DATA ADDRESS LATCH

–M15

IA00

–IA15

PC (16)

QUEUE (16)

X (16)

Y (16)

SP2 (8)

SP1 (8)

DA00

–DA15

RDWRRDIV

BS16

DBS0

DBS1

BUS

CONTROL

CLKSRPKPLSTOP

TIMING & INTERRUPT

Port A Port B

16-bit ADDER

USLP

CONTROL

EXT (8)

ADDRESS

OPERATOR

IRQ

NMI

IACK

Fig. 1.3.1 S1C63000 block diagram

NACK

SS

FETCH

VDDV

POWER

SUPPLY

A (4)

Port A Port B

S1C63000

INSTRUCTION

4-bit ALU

I00

–I12

IR (13)

DECODER

µ Instruction

B (4)

F (4)

IF

D0

–D3

1.4 Input-Output Signals

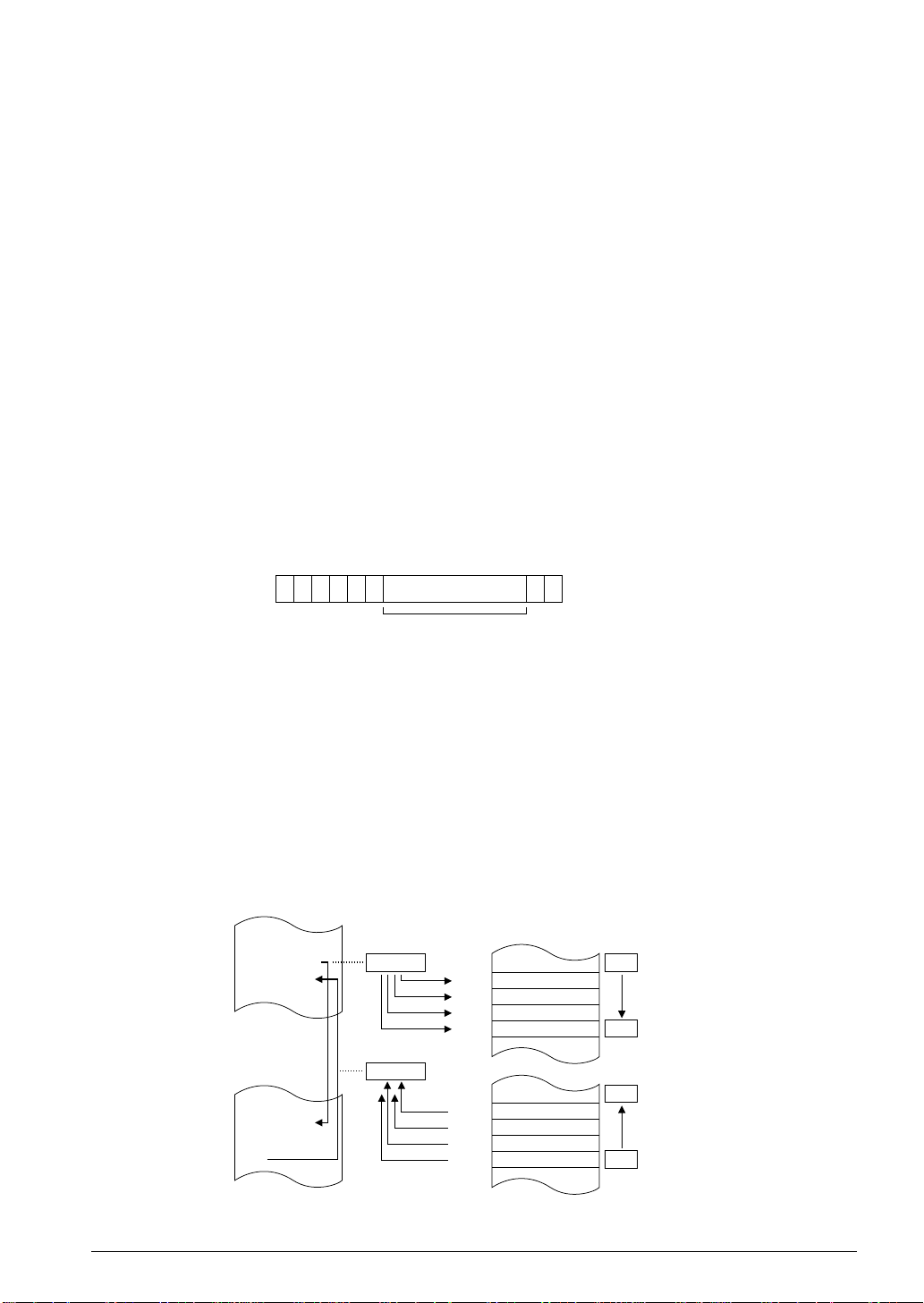

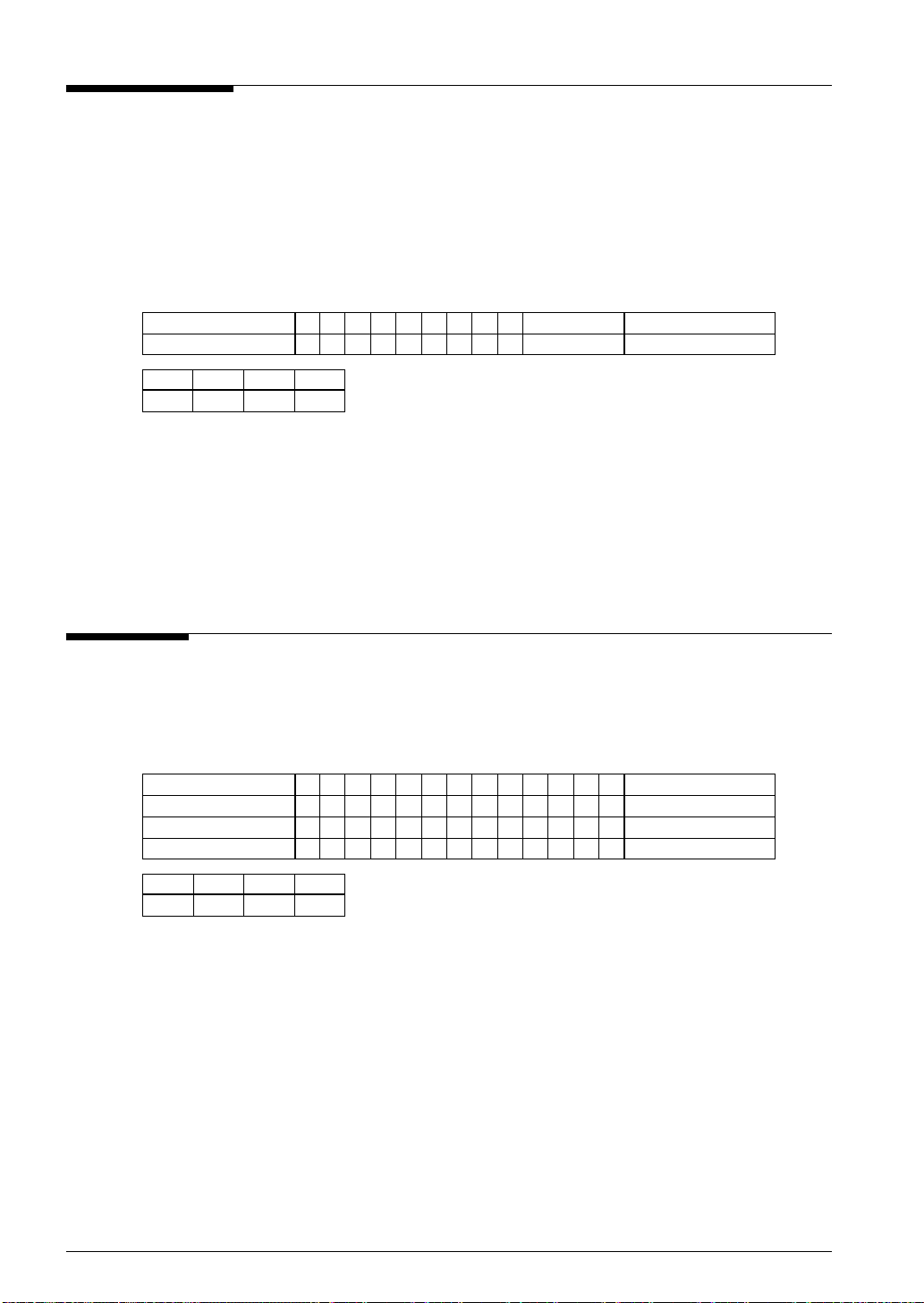

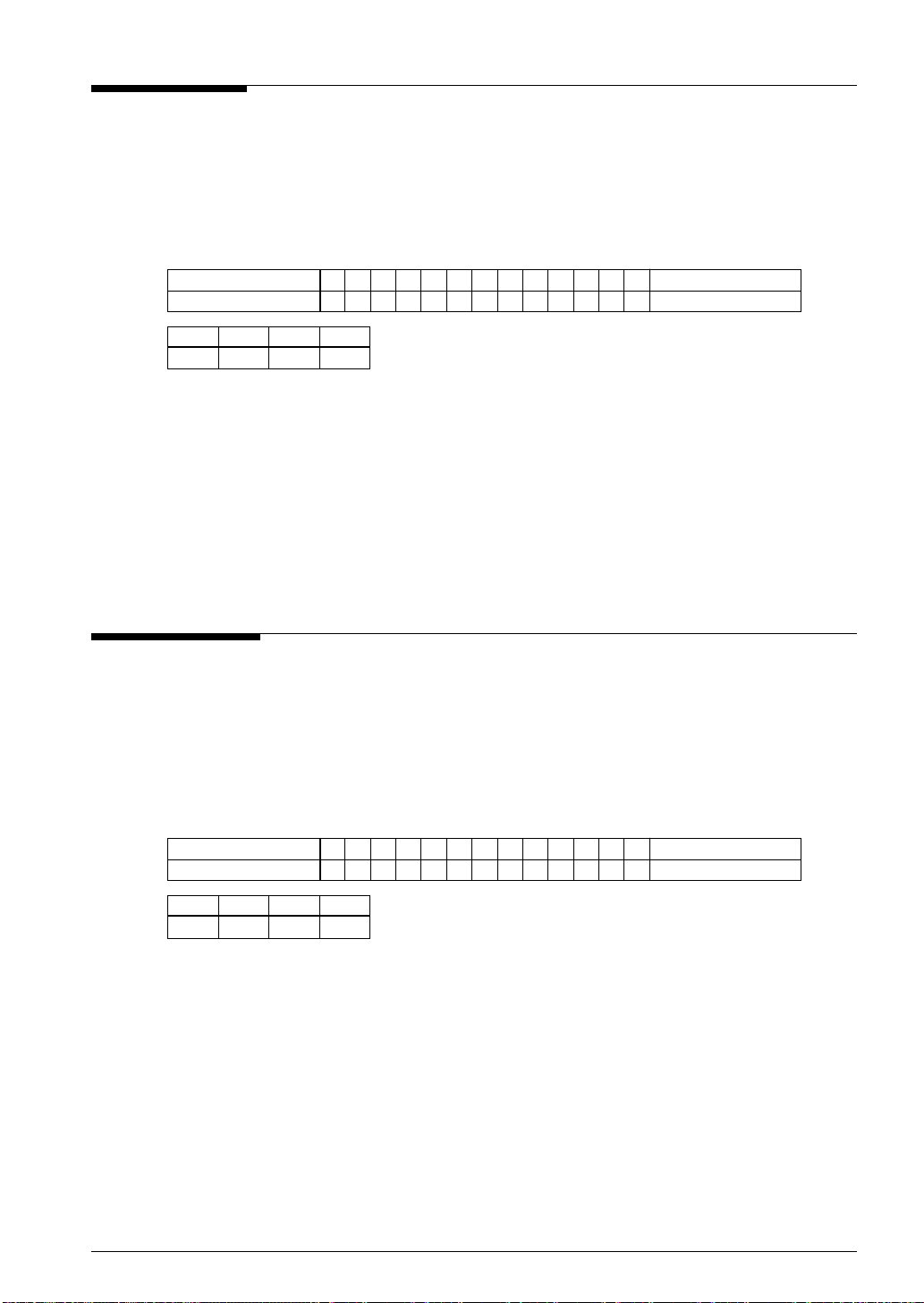

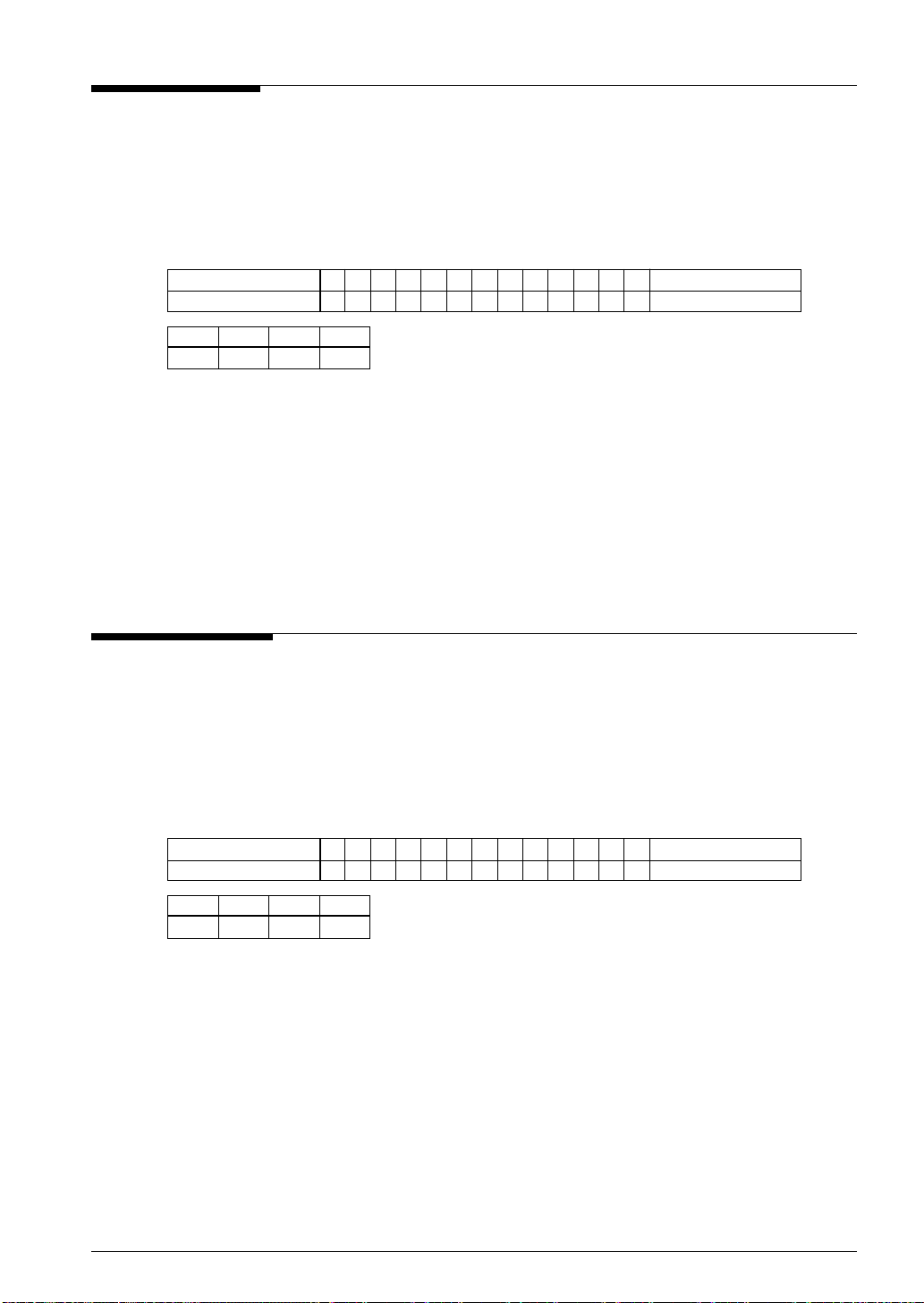

Tables 1.4.1 (a) and 1.4.1 (b) show the input/output signals between the S1C63000 and peripheral circuits.

Table 1.4.1(a) Input/output signal list (1)

Type I/O

Power supply

VDD (VD1)

Power supply (+)

I

Inputs a plus supply voltage.

VSS (VS1)

Power supply (-)

I

Inputs a minus supply voltage.

Clock

CLK

I

Clock input

Inputs the system clock from the peripheral circuit.

PK

PL

2-phase divided clock output

O

Outputs the 2-phase divided signals to be generated from the system clock

input to the CLK terminal as following phase.

CLK

PK

PL

1 cycle

Address bus

IA00–IA15

Instruction address output

O

Outputs an instruction (code ROM) address.

DA00–DA15

Data address output

O

Outputs a data (RAM, I/O) address.

2 EPSON S1C63000 CORE CPU MANUAL

FunctionTerminal name

Page 9

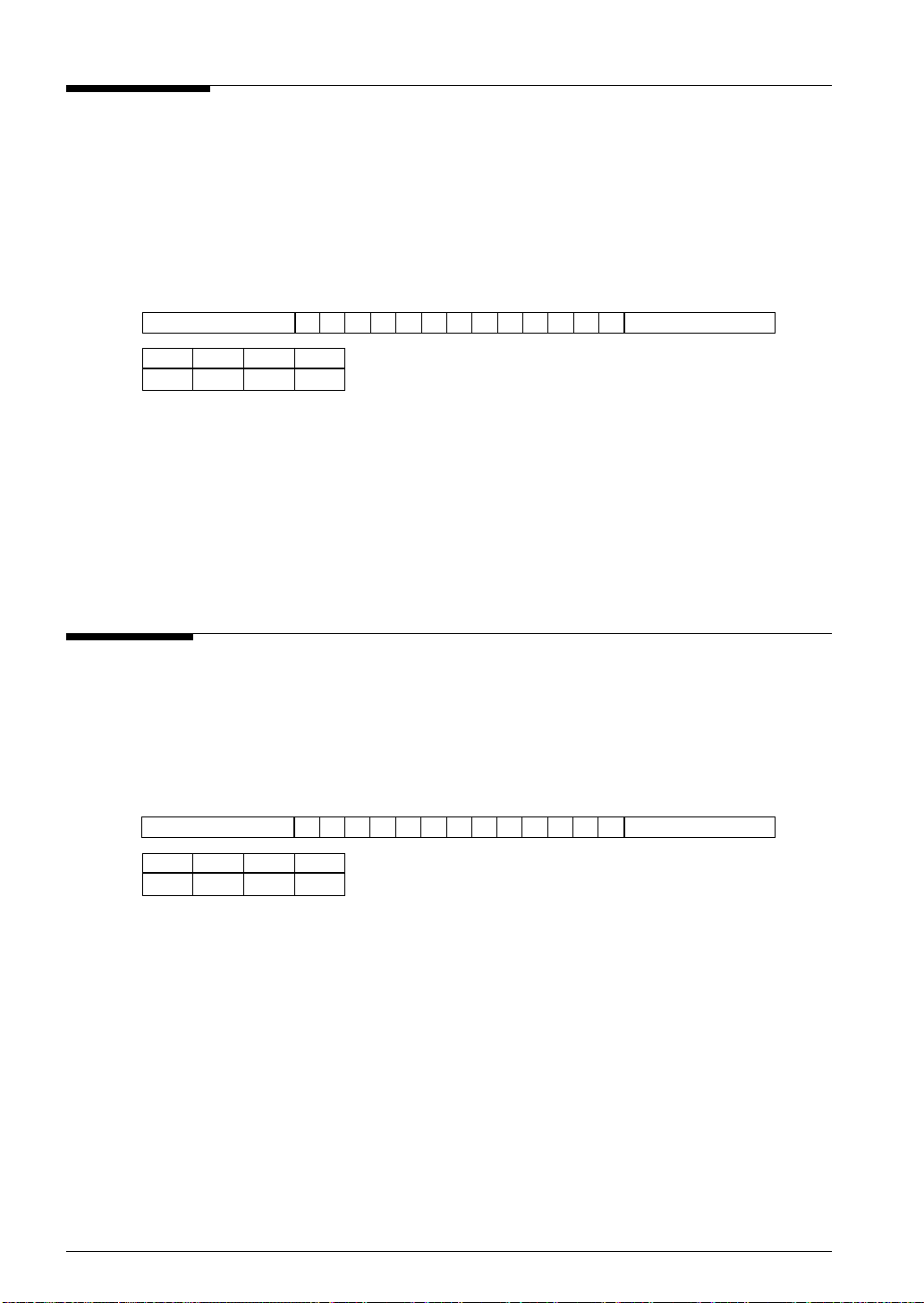

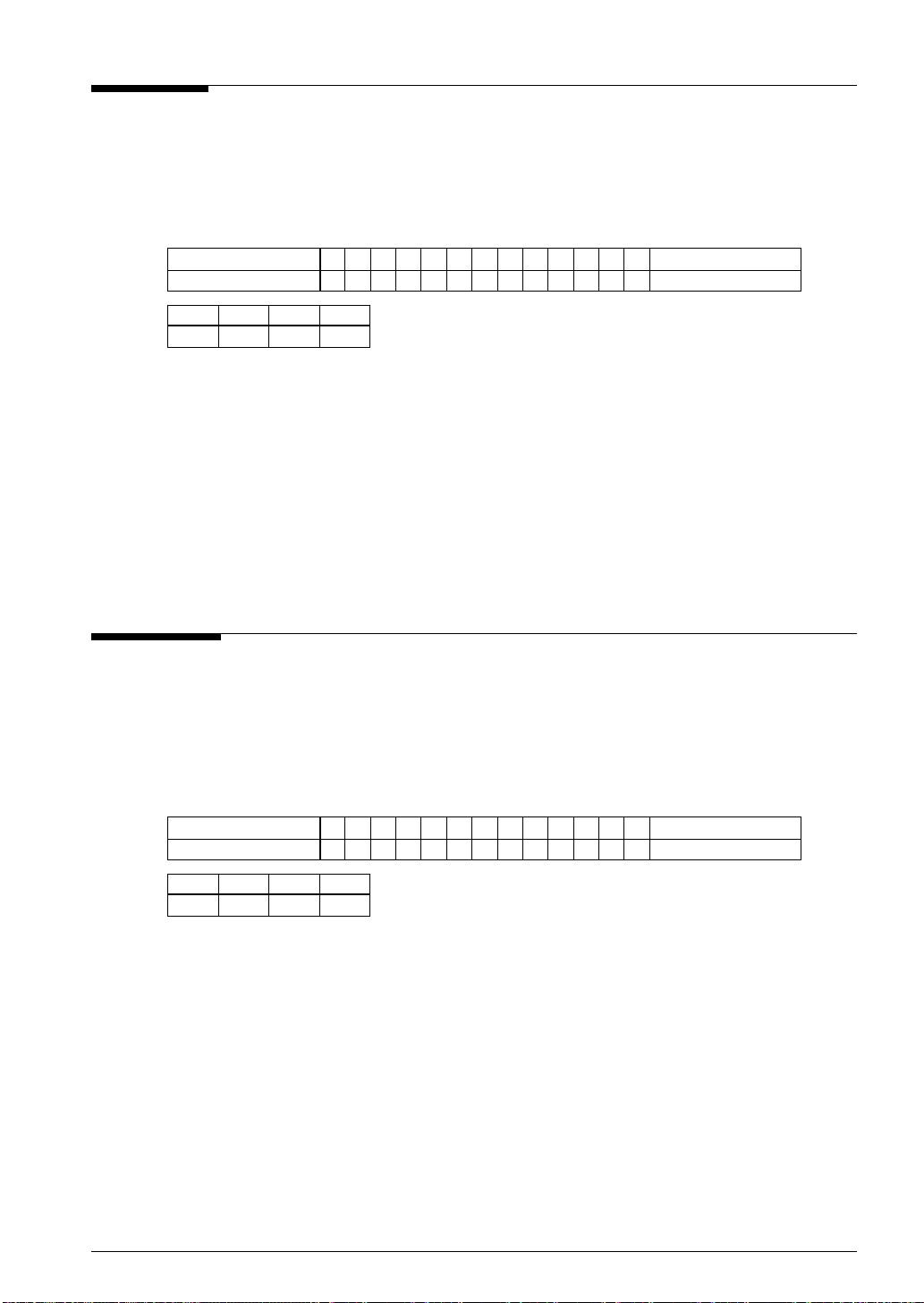

Type I/O

Data bus

Bus control

signal

System control

signal

Interrupt signal

Status signal

I00–I12

M00–M15

D0–D3

RD

WR

RDIV

SR

USLP

NMI

IRQ

IACK

NACK

FETCH

STOP

IF

BS16

DBS0

DBS1

CHAPTER 1: OUTLINE

Table 1.4.1(b) Input/output signal list (2)

FunctionTerminal name

I

Instruction bus

Inputs an instruction code.

I/O

16-bit data bus

A bidirectional data bus to connect to the RAM (stack RAM) for 16-bit accessing.

I/O

4-bit data bus

A bidirectional data bus to connect to the RAM and I/O.

O

Data read

Goes to a low level when the CPU reads data (from RAM, I/O).

O

Data write

Goes to a low level when the CPU writes data (to RAM, I/O).

O

Read interrupt vector

Goes to a low level when the CPU reads an interrupt vector.

I

Reset input

A low level input resets the CPU.

O

Micro sleep

Goes to a low level when the CPU executes the SLP instruction.

The peripheral circuit stops oscillation on the basis of this signal.

I

Non-maskable interrupt request

An interrupt request terminal for an interrupt that cannot be masked by software.

It is accepted at the falling edge of an input signal to this terminal.

I

Interrupt request

An interrupt request terminal for interrupts that can be masked by software.

It is accepted by a low level signal input to this terminal.

O

Interrupt acknowledge

Goes to a low level while executing an NMI or IRQ interrupt response cycle.

O

Non-maskable interrupt acknowledge

Goes to a low level while executing a non-maskable interrupt response cycle.

O

Fetch cycle

Goes to a low level when the CPU fetches an instruction.

O

Stop signal

Goes to a low level when the CPU is in stop status after executing the HALT

or SLP instruction, or in reset status (SR is low).

O

Interrupt flag

Outputs a status (inverted value) of the interrupt flag in the flag (F) register.

O

16-bit access

Goes to a low level when the CPU accesses to a 16-bit RAM.

O

Data bus status

Outputs data bus status (for both the 4-bit and 16-bit data bus).

DBS1

DBS0

State

0

0

High impedance

0

1

Interrupt vector read

1

0

Memory write

1

1

Memory read

See Chapter 3, "CPU OPERATION", for the timing of the signals.

S1C63000 CORE CPU MANUAL EPSON 3

Page 10

CHAPTER 2: ARCHITECTURE

CHAPTER 2ARCHITECTURE

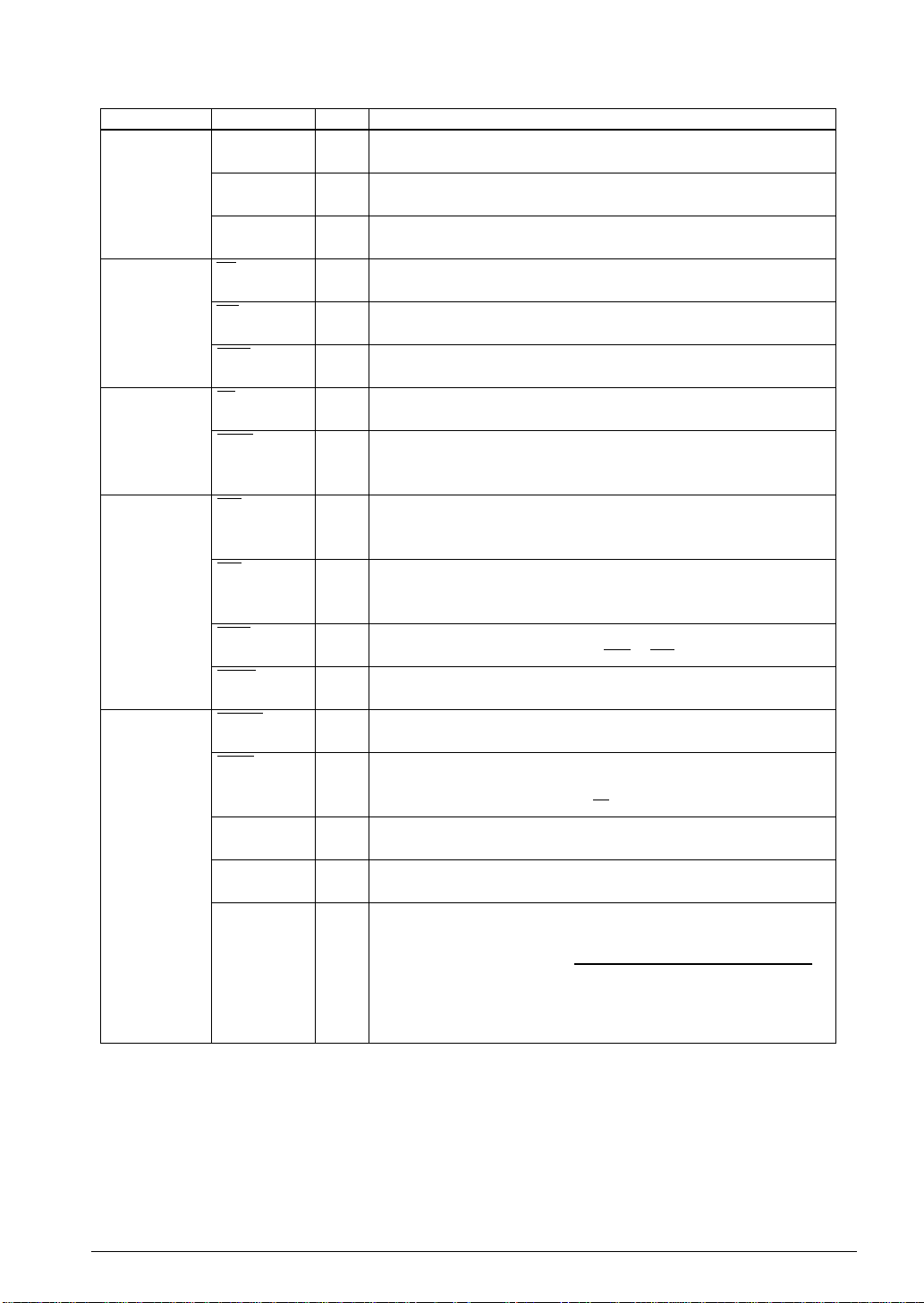

This chapter explains the S1C63000 ALU, registers, configuration of the program memory area and

data memory area, and addressing.

2.1 ALU and Registers

2.1.1 ALU

The ALU (Arithmetic and Logic Unit) loads 4-bit data from a memory or a register and operates the data

according to the instruction. Table 2.1.1.1 shows the ALU operation functions.

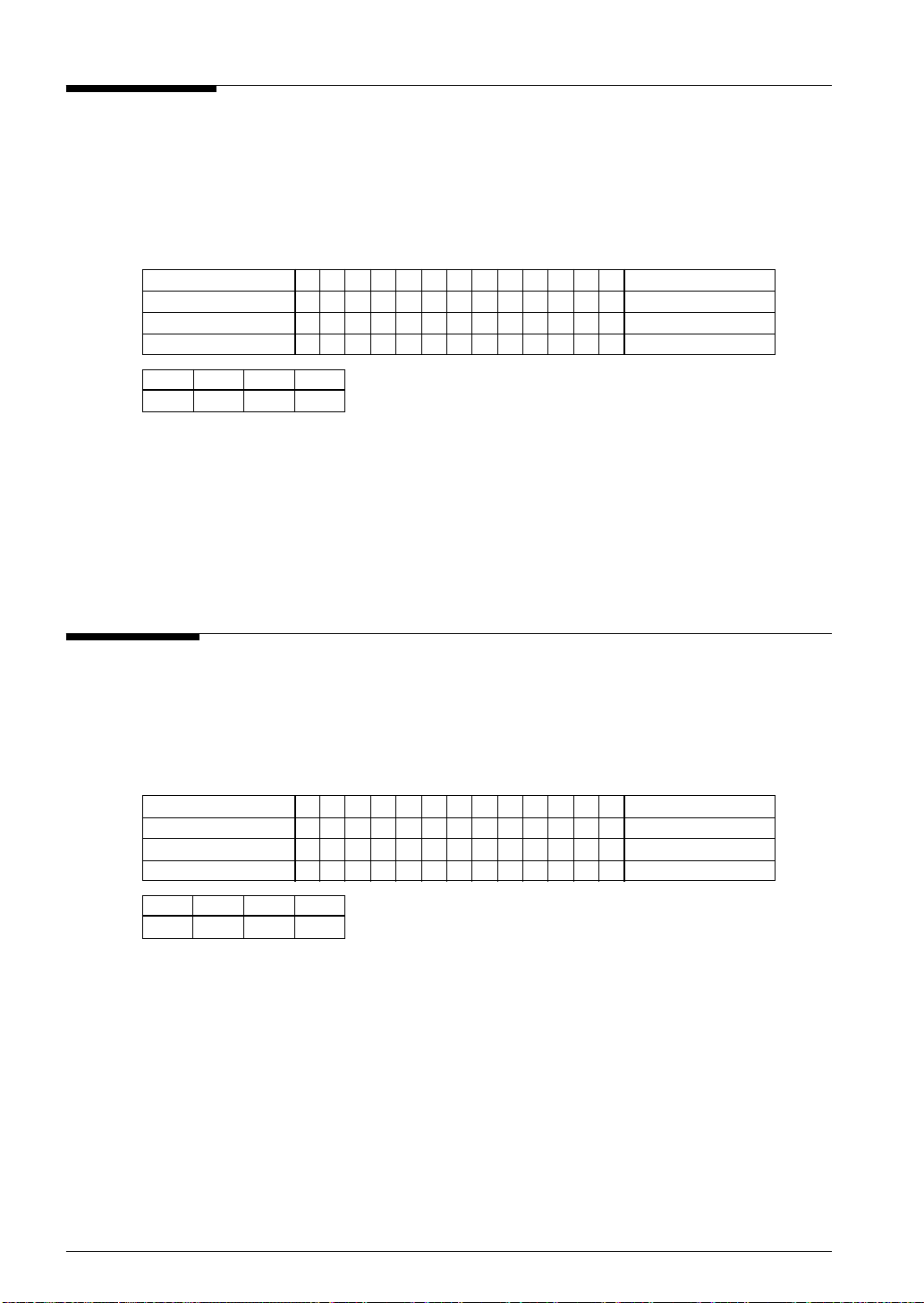

Table 2.1.1.1 ALU operation functions

Function classification

Arithmetic

Logic

Rotate / shift

Mnemonic Operation

ADD

ADC

SUB

SBC

CMP

INC

DEC

AND

OR

XOR

BIT

CLR

SET

TST

RL

RR

SLL

SRL

Addition

Addition with carry

Subtraction

Subtraction with carry

Comparison

Increment (adds 1)

Decrement (subtracts 1)

Logical product

Logical sum

Exclusive OR

Bit test

Bit clear

Bit set

Bit test

Rotate to left with carry

Rotate to right with carry

Logical shift to left

Logical shift to right

The operation result is stored to a register or memory according to the instruction.

In addition, the Z (zero) flag and C (carry) flag are set/reset according to the operation result.

2.1.2 Register configuration

Figure 2.1.2.1 shows the register configuration of the S1C63000.

15 0

15 0

XH

70

15 0

YH

70

15 0

00H

Fig. 2.1.2.1 Register configuration

4 EPSON S1C63000 CORE CPU MANUAL

PC

X

07

XL

Y

07

YL

QUEUE

SP1

7

7

7

70

B

30

0

SP2

EXT

BA

03

30

Program counter

Index register X

Index register Y

Queue register

Stack pointer 1

00000000

Stack pointer 2

0

Extension register

0

Data register B & A

A

F

Flag register

ZCIE

Page 11

CHAPTER 2: ARCHITECTURE

• A and B registers

The A and B registers are respective 4-bit data registers that are used for data transfer and operation

with other registers, data memories or immediate data. They are used independently for 4-bit trans-

fer/operations and used in a BA pair that makes the B register the high-order 4 bits for 8-bit transfer/

operations.

• X and Y registers

The X and Y registers are respective 16-bit index registers that are used for indirect addressing of the

data memory. These registers are configured as an 8-bit register pair (high-order 8 bits: XH/YH, low-

order 8 bits: XL/YL) and data transfer/operations can be done in an 8-bit unit or a 16-bit unit.

• PC (program counter)

The PC is a 16-bit counter to address a program memory and indicates the following address to be

executed.

• SP1 and SP2 (stack pointers)

The SP1 and SP2 are respective 8-bit registers that indicate a stack address in the data memory. 8 bits

of the SP1 correspond to the DA02 to DA09 bits of the address bus for 16-bit data accessing (address

stacking) and it is used to operate the stack in a 4-word (16-bit) unit. 8 bits of the SP2 correspond to

the low-order 8 bits (DA01 to DA07) of the address bus for 4-bit data accessing and it is used to

operate stack in 1-word (4-bit) unit.

See Section 2.3.3, "Stack and stack pointer" for details of the stack operation.

• EXT register

The EXT register is an 8-bit data register that is used when an address or data is extended into 16 bits.

See Section 2.1.5, "EXT register and data extension", for details.

• F register

The F register includes 4 bits of flags; Z and C flags that are changed by operation results, I flag that is

used to enable/disable interrupts, and E flag that indicates extended addressing mode.

• Queue register

The queue register is used as a queue buffer for data when the SP1 processes 16-bit stack operations.

This register is provided in order to process 16-bit data pop operations from the SP1 stack at high-

speed. The queue register is accessed by the hardware, so it is not necessary to be aware of the register

operation when programming.

2.1.3 Flags

The S1C63000 contains a 4-bit flag register (F register) that indicates such things as the operation result

status within the CPU.

30

F

Flag register

ZCIE

Z (zero) flag

C (carry) flag

I (interrupt) flag

E (extension mode) flag

Fig. 2.1.3.1 F (flag) register

• Z (zero) flag

The Z flag is set to "1" when the execution result of an arithmetic instruction or a shift/rotate instruc-

tion has become "0" and is reset to "0'" when the result is other than "0".

Arithmetic instructions that change the Z flag:

ADD, ADC, SUB, SBC, CMP, INC, DEC, AND, OR, XOR, BIT, CLR, SET, TST

S1C63000 CORE CPU MANUAL EPSON 5

Page 12

CHAPTER 2: ARCHITECTURE

Shift/Rotate instructions that change the Z flag:

SLL, SRL, RL, RR

The Z flag is used for condition judgments when executing the conditional jump ("JRZ sign8" and

"JRNZ sign8") instructions, thus it is possible to branch processing to a routine according to the

operation result.

• C (carry) flag

The C flag is set to "1" when a carry (carry from the most significant bit) or a borrow (the most significant bit borrows) has been generated by the execution of an arithmetic instruction and a shift/rotate

instruction, otherwise the flag is set to "0".

Arithmetic instructions that change the C flag:

ADD, ADC, SUB, SBC, CMP, INC, DEC

(It is different from the Z flag, the logic operation instructions except for the instruction that operates

the F register does not change the C flag. In addition, the ADD instructions for the X and Y register

operations and the INC and DEC instructions for the stack pointer operation does not change the C

flag.)

Shift/Rotate instructions that change the C flag:

SLL, SRL, RL, RR

The C flag is used for condition judgments when executing the conditional jump ("JRC sign8" and

"JRNC sign8") instructions, thus it is possible to branch processing to a routine according to the

operation result.

• I flag

The I flag permits and forbids the hardware interrupts except for the NMI. By setting the I flag to "1",

the CPU enters in the EI (enable interrupts) status and the hardware interrupts are enabled. When the

I flag is set to "0", the CPU is in the DI (disable interrupts) and the interrupts except for NMI are

disabled. Furthermore, when a hardware interrupt (including the NMI) is generated, the I flag is reset

to "0" and interrupts after that point are disabled. The multiple interrupts can be accepted by setting

the I flag to "1" in the interrupt processing routine.

The NMI (non-maskable interrupt) is accepted regardless of the I flag setting.

The software interrupts are accepted regardless of the I flag and do not reset the I flag.

The I flag is set to "0" (DI status) at an initial reset, therefore it is necessary to set "1" before using

interrupts by software.

See Section 3.5, "Interrupts" for details.

• E (extension mode) flag

The E flag indicates whether an extended addressing that uses the EXT (extension) register is valid or

invalid. When data is loaded into the EXT register, this flag is set to "1" and the data of the instruction

immediately after that (extended addressable instructions only) is extended with the EXT register.

Then the instruction is executed and the E flag is reset to "0".

See Section 2.1.5, "EXT register and data extension" for details.

• Flag operations

As described above, the flags are automatically set/reset by the hardware. However, it is necessary to

set by software, especially the I flag. The following instructions are provided in order to operate the F

flag.

LD %A,%F Reads all the flag data

LD %F,%A Writes all the flag data

LD %F,imm4 Writes all the flag data

AND %F,imm4 Resets flag(s)

OR %F,imm4 Sets flag(s)

∗ The RETI instruction is used to return from interrupt processing routines (including software

interrupts), and returns the F register data that was evacuated when the interrupt was generated.

XOR %F,imm4 Inverts flag(s)

PUSH %F Evacuates the F register

POP %F Returns the F register

RETI Returns the F register∗

6 EPSON S1C63000 CORE CPU MANUAL

Page 13

CHAPTER 2: ARCHITECTURE

2.1.4 Arithmetic operations with numbering system

In the S1C63000, some instructions support a numbering system. These instructions are indicated with

the following notations in the instruction list.

ADC operand,n4

SBC operand,n4

INC operand,n4

DEC operand,n4

(See "Instruction List" or "Detailed Explanation of Instructions" for the contents of the operand.)

"n4" is a radix, and can be specified from 1 to 16. The additions/subtractions are done in the numbering

system with n4 as the radix. Various counters (such as binary, octal, decimal and hexadecimal) can be

realized easily by software.

The Z flag indicates that an operation result is "0" or not in arithmetics with any numbering system. The

C flag indicates a carry/borrow according to the radix.

The following shows examples of these operation.

Example 1) Octal addition ADC %B,%A,8 (C flag is "0" before operation)

Setting value Result F register

B register A register B register E I C Z

0010B(2) 0111B(7) 0001B(1) 0 – 1 0

0101B(5) 0011B(3) 0000B(0) 0 – 1 1

Example 2) Decimal subtractio SBC %B,%A,10 (C flag is "0" before operation)

Setting value Result F register

B register A register B register E I C Z

1001B(9) 0111B(7) 0010B(2) 0 – 0 0

0001B(1) 0010B(2) 1001B(9) 0 – 1 0

Example 3) 3-digit BCD down counter

LDB %EXT,0 ; Counter base address [0010H]

LD %XL,0x10

LDB [%X]+,0 ; Initial value setting [100]

LDB [%X]+,0

LDB [%X]+,1

:

:

CTDOWN: ; Count down subroutine----------

LDB %EXT,0 ; Counter base address [0010H]

LD %XL,0x10

DEC [%X]+,10 ; Decrements digit 1

SBC [%X]+,0,10 ; Decrements carry from digit 2

SBC [%X],0,10 ; Decrements carry from digit 3

CALR CTDISP ; Count number display routine

LD %A,0 ; Zero check

ADD %A,[%X]

ADD %X,-1

ADD %A,[%X]

ADD %X,-1

JRNZ CTEXIT ; Return if counter is not zero

CALR CTOVER ; Count over processing routine

CTEXIT:

RET

This routine constructs a 3-digit BCD counter using the decimal operation instructions underlined.

Calling the CTDOWN subroutine decrements the counter, and then returns to the main routine. If the

counter has to be zero, the CTOVER subroutine is called before returning to the main routine to

process the end of counting.

S1C63000 CORE CPU MANUAL EPSON 7

Page 14

CHAPTER 2: ARCHITECTURE

• Notes in numbering operations

When performing a numbering operation, set operands in correct notation according to the radix

before operation.

For example, if a decimal operation is done for hexadecimal values (AH to FH), the correct operation

result is not obtained as shown in the following example.

Example: ADC %B,%A,10

Setting value Result F register

B register A register B register E I C Z

1 1001B(9) 1001B(9) 1000B(8) 0 – 1 0 ●●

2 0101B(AH) 1001B(9) 1001B(9) 0 – 1 0 ▲▲

3 1010B(AH) 1010B(AH) 1010B(AH) 0 – 1 0 ×

4 1010B(AH) 1111B(FH) 1111B(FH) 0 – 1 0 ×

Example 1 operates correctly because a decimal value is loaded in the B and A registers.

Examples 3 and 4 do not operate correctly.

Example 2 operates correctly even though it is a wrong setting.

2.1.5 EXT register and data extension

The S1C63000 has a linear 64K-word addressable space, therefore it is required to handle 16-bit address

data. The EXT register and the F flag that extend 8-bit data into 16-bit data permit 16-bit data processing.

The EXT register is an 8-bit register for storing extension data. The E flag indicates that the EXT register

data is valid (extended addressing mode), and is set to "1" by writing data to the EXT register. The E flag

is reset at 1 cycle after setting (during executing the next instruction), therefore an EXT register data is

valid only for the executable instruction immediately after writing. However, that executable instruction

must be a specific instruction which permits the extended addressing to extend the data using the EXT

register. These instructions are specified in "Instruction List" and "Detailed Explanation of Instructions".

Make sure of the instructions when programming.

Note: Do not use instructions (see Instruction List) which are invalid for the extended addressing when

the E flag is set to "1". (Do not use them following instructions that write data to the EXT register or

that set the E flag.) Normal operations cannot be guaranteed if such instructions are used.

(1)Operation for EXT register and E flag (flag register)

The following explains the operation for the EXT register and the E flag (flag register).

• Data setting to the EXT register

The following two instructions are provided to set data in the EXT register.

LDB %EXT,imm8 Loads an 8-bit immediate data to the EXT register

LDB %EXT,%BA Loads the content of the BA register to the EXT register

By executing the instruction, the EXT flag is set to "1" and it indicates that the content of the EXT

register is valid (the content of the EXT register will be used for data extension in the following

instructions).

Furthermore, the content of the EXT register can be read using the instruction below.

LDB %BA,%EXT Loads the content of the EXT register to the BA register

• Setting/resetting the E flag

As mentioned above, the E flag is set to "1" by data setting to the EXT register and reset to "0" while

executing the next instruction.

In addition, the E flag can be set/reset using the following instructions that operate the flags.

LD %F,%A Writes all the flag data

LD %F,imm4 Writes all the flag data

AND %F,imm4 Resets flag(s)

OR %F,imm4 Sets flag(s)

XOR %F,imm4 Inverts flag(s)

8 EPSON S1C63000 CORE CPU MANUAL

Page 15

CHAPTER 2: ARCHITECTURE

The EXT register maintains the data set previously until new data is written or an initial reset. In other

words, the content of the EXT register becomes valid by only setting the E flag using an above instruc-

tion without the register writing and is used for an extended addressing. However, the EXT register is

undefined at an initial reset, therefore, do not directly set the E flag except when the content of the

EXT register has been set for certain.

The following shows the other instructions related to flag data transfer.

LD %A,%F Reads all the flag data

PUSH %F Evacuates the F register

POP %F Returns the F register

RETI Returns the F register ∗

∗ The RETI instruction is used to return from interrupt processing routines (including software inter-

rupts), and returns the F register data that was evacuated when the interrupt was generated.

If an interrupt (including NMI) is generated while fetching an instruction, such as a "LDB %EXT, ••"

instruction or an instruction which writes data to the flag register (the E flag may be set), the interrupt

is accepted after fetching (and executing) the next instruction. In normal processing, data extension

processing is not performed after returning from the interrupt service routine because the interrupt

processing including the F register evacuation is performed after the data extension has finished (E

flag is reset). However, if the stack data in the memory is directly changed in the interrupt service

routine, the F register in which the E flag is set may return. In this case, the instruction immediately

after returning by the RETI instruction is executed in the extended addressing mode by the E flag set

to "1". Pay attention to the F register setting except when consciously describing such a processing. It

is necessary to pay the same attention when returning the F register using the "POP %F" instruction.

(2)Extension with E flag

The following explains the instructions that can be executed when the E flag is set to "1" and its

operation.

• Modifying the indirect addressing with the X and Y registers (for 4-bit data access)

The indirect addressing instructions, which contain [%X] or [%Y] as an operand and accesses 4-bit

data using the X or Y register, functions as an absolute addressing that uses the EXT register data

together with the E flag (= "1").

When an 8-bit immediate data (imm8) is written to the EXT register and the E flag is set immediately

before these instructions, the instruction is modified executing as [%X] = [0000H + imm8] or [%Y] =

[FF00H + imm8]. Therefore, the addressable space with this function is data memory address from

0000H to 00FFH when [%X] is used, and from FF00H to FFFFH when [%Y] is used. Generally, data

that are often used are allocated to the data memory from 0000H to 00FFH and the area from FF00H to

FFFFH is assigned to the I/O memory area (for peripheral circuit control), so these areas are fre-

quently accessed. To access these areas by a normal indirect addressing (if the E flag has not been set)

using the X or Y register, two or three steps of instructions are necessary for setting an address data. In

other words, using this function promotes efficiency of the entire program. See Section 2.3, "Data

Memory" for details of the data memory.

Examples:

LDB %EXT,0x37

LD %A,[%X] ...Works as "LD %A, [0x0037]"

LDB %EXT,0x9C

ADD [%Y],5 ...Works as "ADD [0xFF9C], 5"

Note: This function can be used by only the specific instructions which permits the extended addressing

(see "Instruction List"). Be aware that the operation cannot be guaranteed if the instructions

indicated below are used.

1.Instructions which have a source and /or a destination operand with the post-increment function,

[%X]+ and [%Y]+.

2.Instructions which have [%X] and/or [%Y] in both the source and destination operands.

3.The RETD instruction and the LDB instructions which transfers 8-bit data.

S1C63000 CORE CPU MANUAL EPSON 9

Page 16

CHAPTER 2: ARCHITECTURE

• 16-bit data transfer/arithmetic for the index registers X and Y

The following six instructions, which handle the X or Y register and have an 8-bit immediate data as

the operand, permit the extended addressing.

LDB %XL,imm8 LDB %YL,imm8

ADD %X,sign8 ADD %Y,sign8

CMP %X,imm8 CMP %Y,imm8

When data is written to the EXT register and the E flag is set immediately before these instructions,

the data is processed after extending into 16-bit; imm8 (sign8) is used as the low-order 8 bits and the

content of the EXT register is used as the high-order 8 bits.

Examples:

LDB %EXT,0x15

LDB %XL,0x7D ...Works as "LD %X,0x157D"

LDB %EXT,0xB8

ADD %X,0x4F ...Works as "ADD %X, 0xB84F"

LDB %EXT,0xE6

CMP %X,0xA2 ...Works as "CMP %X, 0x19A2"

∗ 19H = FFH - [EXT] (E6H)

Above examples use the X register, but work the same even when the Y register is used.

Note: The CMP instruction performs a subtraction with a complement, therefore it is necessary to set the

complement (1's complement) of the high-order 8-bit data in the EXT register.

EXT register

←

[FFH - High-order 8-bit data]

• Extending branch addresses

The following PC relative branch instructions, which have a signed 8-bit relative address as the

operand, permit extended addressing.

JR sign8 JRC sign8 JRNC sign8 JRZ sign8 JRNZ sign8

CALR sign8

When data is written to the EXT register and the E flag is set immediately before these instructions,

the relative address is processed after extending into signed 16-bit; sign8 is used as the low-order 8

bits and the content of the EXT register is as the high-order 8 bits.

Examples:

LDB %EXT,0x64

JR 0x29 ...Works as "JR 0x6429"

LDB %EXT,0x00

JR 127 ...Works as "JR 127"

LDB %EXT,0xFF

JR -128 ...Works as "JR -128"

LDB %EXT,0x3A

JR∗ 0x88 ...Works as "JR∗ 0x3A88" (∗ = C, NC, Z, or NZ)

LDB %EXT,0xF8

CALR 0x62 ...Works as "CALR 0xF862"

See Section 2.2.3, "Branch instructions" for the branch instructions.

10 EPSON S1C63000 CORE CPU MANUAL

Page 17

CHAPTER 2: ARCHITECTURE

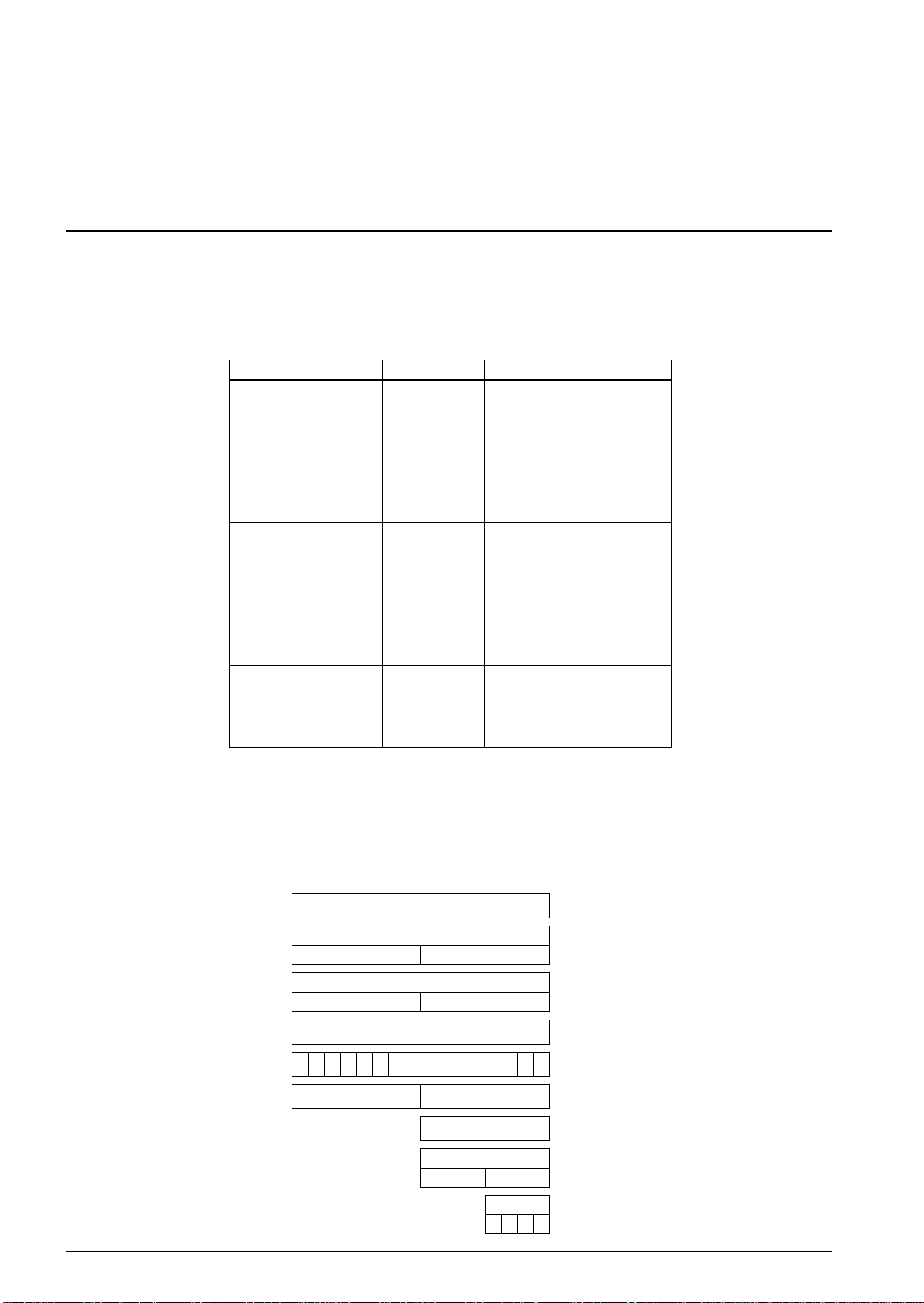

2.2 Program Memory

2.2.1 Configuration of program memory

The S1C63000 can access a maximum 64K-word (× 13 bits) program memory space. In the individual

model of the S1C63 Family, the ROM of which size is decided depending on the model is connected to

this space to write a program and static data.

Figure 2.2.1.1 shows the program memory map of the S1C63000.

Address

0000H

00FFH

0100H

0101H

010FH

0110H

0111H

013FH

0140H

Program area

Common subroutine, etc.

NMI interrupt vector

Hardware interrupt vectors

Program start address

Software interrupt vectors

Program area

13-bit

FFFFH

Fig. 2.2.1.1 S1C63000 program memory map

The S1C63000 can access 64K-word space linearly without any page management used in current 4-bit

microcomputers.

As shown in Figure 2.2.1.1, the program start address after an initial reset is fixed at 0110H independent

of the S1C63 Family models. Programming should be done so that the execution program starts from that

address.

The address 0100H to 010FH is the hardware interrupt vector's area in which up to 16 interrupt vectors

can be assigned. Address 0100H is for the exclusive use of NMI (non-maskable interrupt). The number of

interrupt vectors is dependent on the interrupt function of the S1C63 Family models. Branch instructions

to the interrupt service routines should be written in this area. See Section 3.5, "Interrupts" for details of

the interrupts.

The address 0111H to 013FH is the software interrupt vector's area. Up to 63 software interrupts can be

set up together with the hardware interrupt vector area. Set branch instructions to the interrupt service

routines in this area similarly to the hardware interrupts.

Addresses from 0000H to 00FFH and from 0140H to FFFFH are program area. A call instruction (CALZ)

that is for the exclusive use of the area from 0000H to 00FFH is provided so that the area is useful to store

common subroutines that are called from relocatable modules.

2.2.2 PC (program counter)

The PC (program counter) is a 16-bit counter that keeps the program address to be executed next. The PC

is incremented by executing every instruction step to execute a program sequentially. When a branch

instruction is executed or an interrupt is generated, the content of the PC is modified to branch the

process flow.

The PC covers the entire program memory space alone, therefore processing such as page management

are unnecessary.

At initial reset, the PC is initialized to 0110H and the program starts executing from that address.

S1C63000 CORE CPU MANUAL EPSON 11

Page 18

CHAPTER 2: ARCHITECTURE

2.2.3 Branch instructions

Various branch instructions are provided for program repeat and subroutine calls that change a sequential program flow controlled with the PC. The branch instruction modifies the PC to branch the program

to an optional address. The types of the branch instructions are classified as follows, according to their

operation differences.

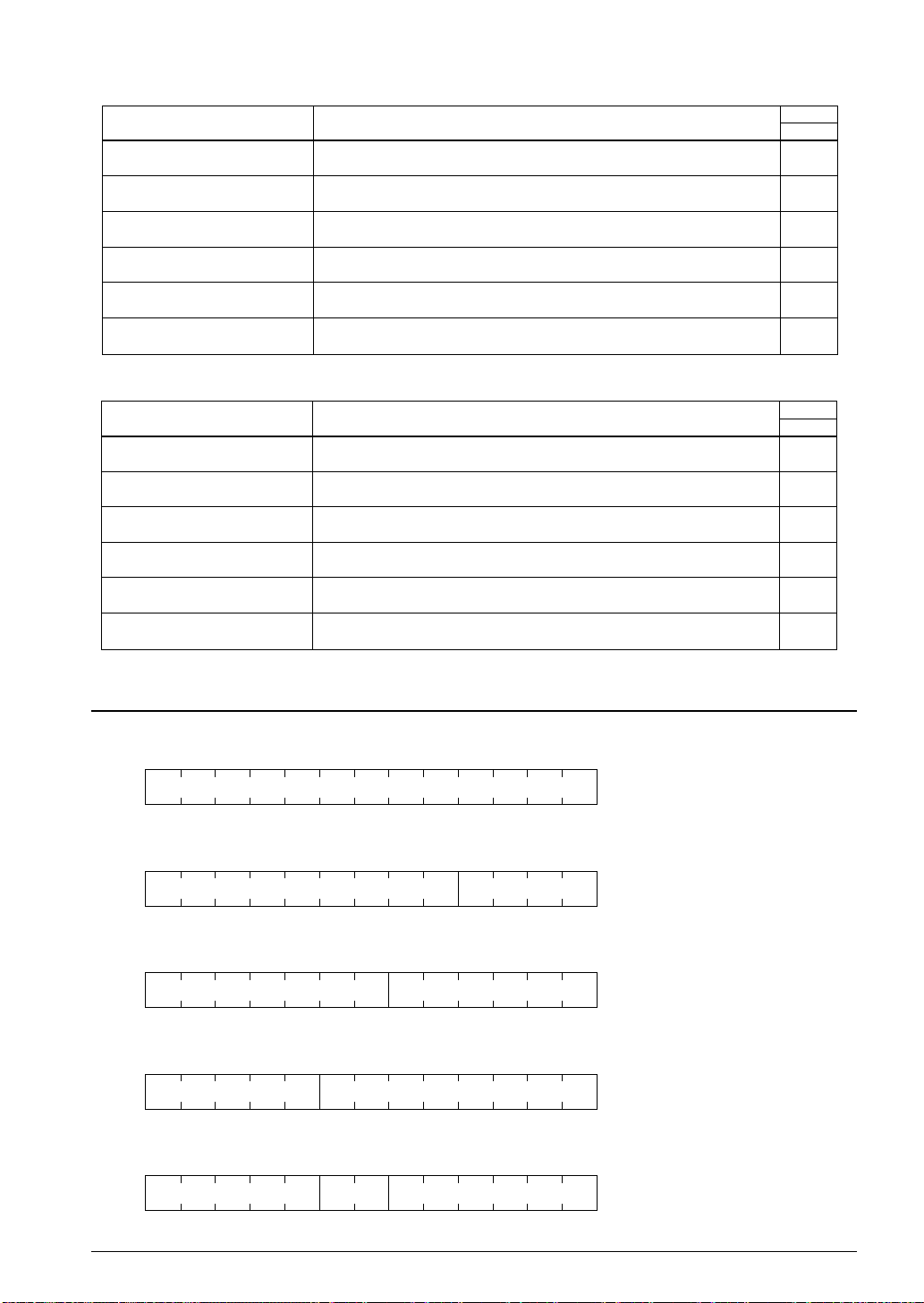

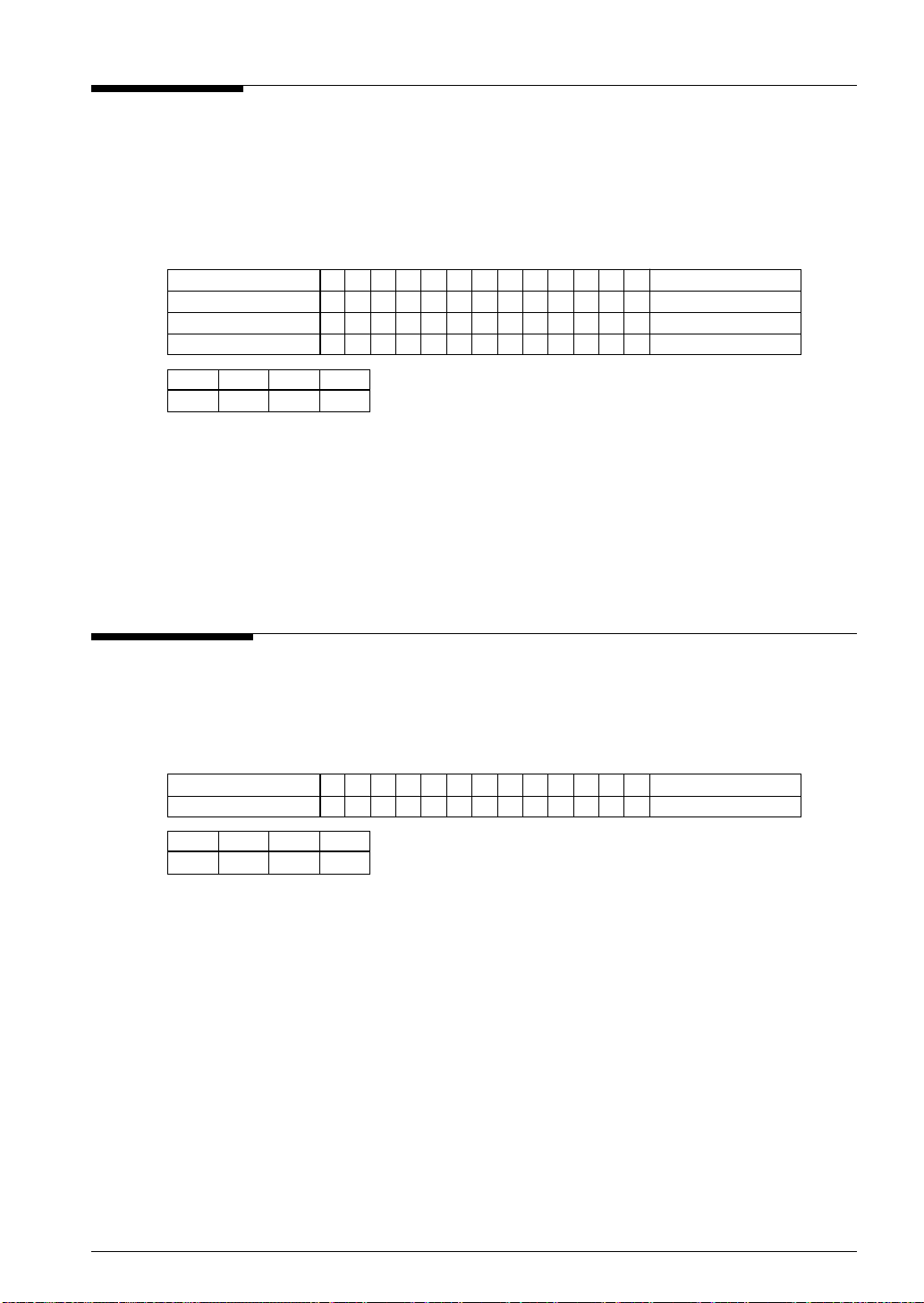

Table 2.2.3.1 Types of branch instructions

Type

PC relative jump

PC relative jump

Indirect jump

Absolute call

PC relative call

Return

Software interrupt

• PC relative jump instructions (JR)

The PC relative jump instruction adds the relative address specified in the operand to the PC that has

indicated the next address, and branches to that address. It permits relocatable programming.

The relative address to be specified in the operand is a displacement from the PC value (address of the

next instruction) when the branch instruction is executed to the branch destination address. When

programming using the S1C63 Family assembler, it is not necessary to calculate displacements

because a branch destination address can be defined as a label and it can be used as an operand.

However, the range of branch destination addresses is different depending on the number of data bits

that are handled as relative addresses.

The following explains the PC relative jump instructions and the relative addresses.

Condition Instruction

Unconditional

Conditional

Unconditional

Unconditional

Unconditional

Unconditional

Unconditional

JR

JRC, JRNC, JRZ, JRNZ

JP

CALZ

CALR

RET, RETS, RETD, RETI

INT

(1) Instructions with a signed 8-bit immediate data sign8 that specifies a relative address

Unconditional jump JR sign8

Conditional jump JRC sign8 JRNC sign8 JRZ sign8 JRNZ sign8

These instructions branch the program sequence with the sign8 specified in the operand as a

signed 8-bit relative address. The range that can be branched is from the next instruction address 128 to +127. A value within the range from -128 to +127 should be used if specifying a value for

jumping in the assembler. Generally branch destination labels such as "JR LABEL" are used, and

they are expanded into the actual address by the assembler.

These instructions permit the extended addressing with the E flag, and the 8-bit relative address

can be extended into 16 bits (the contents of the EXT register become the high-order 8 bits). In this

case, the range that can be branched is from the next instruction address -32768 to +32767. Consequently, in the extended addressing mode these instructions can branch the entire 64K program

memory.

Examples:

JR -100 ...Jumps to the instruction 99 steps before

LDB %EXT,100 ...(100 × 256) = 25600

JR 100 ...Jumps to the instruction 25701 steps after

The unconditional jump instruction "JR sign8" jumps to the branch destination unconditionally

when it is executed.

The conditional jump instructions jump according to the status of C flag or the Z flag.

JRC sign8 ...Jumps if the C flag is "1", or executes the next instruction if the C flag is "0"

JRNC sign8 ...Jumps if the C flag is "0", or executes the next instruction if the C flag is "1"

JRZ sign8 ...Jumps if the Z flag is "1", or executes the next instruction if the Z flag is "0"

JRNZ sign8 ...Jumps if the Z flag is "0", or executes the next instruction if the Z flag is "1"

12 EPSON S1C63000 CORE CPU MANUAL

Page 19

CHAPTER 2: ARCHITECTURE

(2) Instruction with a 4-bit A register data that specifies a relative address

JR %A

This instruction branches the program sequence with the content of the A register as an unsigned

4-bit relative address. The range that can be branched is from the next instruction address +0 to

+15 (absolute value in the A register). This instruction is useful when operation results are used as

the 4-bit relative addresses.

Example:

LD %A,4

JR %A ...Jumps to the instruction 5 steps after

(3) Instruction with an 8-bit BA register data that specifies a relative address

JR %BA

This instruction branches the program sequence with the content of the BA register as an unsigned

8-bit relative address ( the B register data becomes the high-order 4 bits). The range that can be

branched is from the next instruction address +0 to +255 (absolute value in the BA register). This

instruction is useful when operation results are used as the 8-bit relative addresses.

Example:

LDB %BA,29

JR %BA ...Jumps to the instruction 30 steps after

(4) Instruction with a data memory address within 0000H to 003FH in which the content specifies a 4-bit

relative address

JR [addr6]

This instruction branches the program sequence with the content of the data memory specified by

the [addr6] as an unsigned 4-bit relative address. The operand [addr6] can specify a data memory

address within 0000H to 003FH. The range that can be branched is from the next instruction

address +0 to +15 (absolute value in the specified data memory). For the data memory area that is

specified with [addr6], bit operation instructions (CLR, SET, TST) are provided so that various

flags can be set simply. This jump instruction can be used as a conditional jump according to these

flags.

Example: When the content of the address 0010H is 4 (0100B).

SET [0x0010],0 ...Sets the bit 0 in the address 0010H to "1" ([0010H] = 5)

JR [0x0010] ...Jumps to the instruction 6 steps after

• Indirect jump instruction (JP)

The indirect jump instruction "JP %Y" loads the content of the Y register into the PC to branch to that

address unconditionally. This instruction can branch entire 64K program memory because the 16-bit

data in the Y register becomes a branch destination address as it is.

Example:

LDB %EXT,0x24

LDB %YL,0x00 ...Y = 2400H

JP %Y ...Jumps to the address 2400H

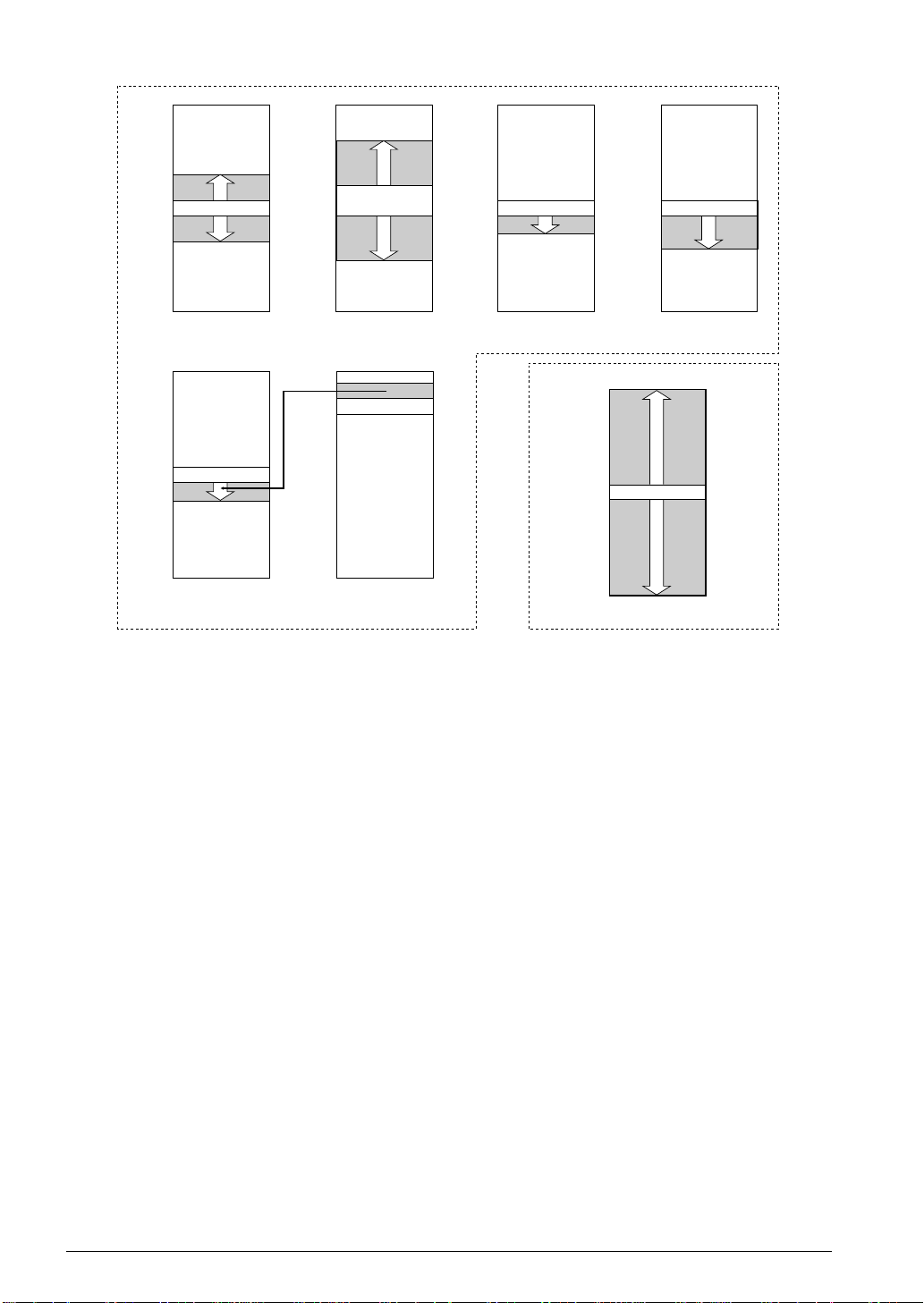

Figure 2.2.3.1 shows the operation of the jump instructions and the branch range.

S1C63000 CORE CPU MANUAL EPSON 13

Page 20

CHAPTER 2: ARCHITECTURE

0000H

xxxxH-127

xxxxH

xxxxH+128

FFFFH

0000H

xxxxH

xxxxH+16

FFFFH

Program memory

Program memory Program memory Program memory

0000H

∗

xxxxH-32767

xxxxH-1

JR sign8

xxxxH+32768

LDB %EXT,imm8

xxxxH

JR sign8

∗

FFFFH

∗ In the extended addressing mode,

this instruction can branch the

entire 64K program memory.

Program memory Data memory

JR [addr6]

[addr6]=0 → xxxxH+1

:

[addr6]=15 → xxxxH+16

PC relative jump instructions

Fig. 2.2.3.1 Operation of jump instructions

xxxxH+16

0000H

addr6

003FH

FFFFH

0000H

xxxxH

FFFFH

JR %A

A=0 → xxxxH+1

:

A=15 → xxxxH+16

0000H

xxxxH

xxxxH+256

FFFFH

Program memory

0000H

JP %Y

FFFFH

Y → Branch destination

absolute address

Indirect jump instruction

JR %BA

BA=0 → xxxxH+1

:

BA=255 → xxxxH+256

• Absolute call instruction (CALZ)

The absolute call instruction "CALZ imm8" calls a subroutine within addresses 0000H to 00FFH. A

subroutine start address (absolute address) should be specified to imm8. When the call instruction is

executed, the PC value (address of the next instruction) is saved into the stack for return, then it

branches to the specified address.

Generally common subroutines that are called from two or more modules are placed in this area when

the program is developed as multiple modules.

Example:

CALZ 0x50 ...Calls the subroutine located at the address 0050H

See Section 2.3.3, "Stack and stack pointer" for stack.

• PC relative call instructions (CALR)

The PC relative call instruction adds the relative address specified in the operand to the PC that has

indicated the next address, and calls a subroutine started from that address. It permits relocatable

programming.

The relative address to be specified in the operand is same as the PC related jump instruction.

The PC value (address of the next instruction) is saved into the stack before branching.

(1) Instructions with a signed 8-bit immediate data sign8 that specifies a relative address

CALR sign8

This instruction branches the program sequence with the sign8 specified in the operand as a

signed 8-bit relative address. The range that can be branched is from the next instruction address 128 to +127. A value within the range from -128 to +127 should be used if specifying a value for

calling in the assembler. Generally branch destination labels such as "CALR LABEL" are used, and

they are expanded into the actual address by the assembler.

14 EPSON S1C63000 CORE CPU MANUAL

Page 21

CHAPTER 2: ARCHITECTURE

This instruction permits the extended addressing with the E flag, and the 8-bit relative address can

be extended into 16 bits (the contents of the EXT register becomes the high-order 8 bits). In this

case, the range that can be branched is from the next instruction address -32768 to +32767. Consequently, in the extended addressing mode this instruction can call subroutines over a 64K program

memory.

Examples:

CALR -50 ...Calls the subroutine 49 steps before

LDB %EXT,50 ...(50 × 256) = 17800

CALR 50 ...Calls the subroutine 17851 steps after

(2) Instruction with a data memory address within 0000H to 003FH in which the content specifies a 4-bit

relative address

CALR [addr6]

This instruction branches the program sequence with the content of the data memory specified by

the [addr6] as an unsigned 4-bit relative address. The operand [addr6] can specify a data memory

address within 0000H to 003FH. The range that can be branched is from the next instruction

address +0 to +15. Same with the "JR [addr6]", this call instruction can be used as a conditional

call according to the flags that are set in the memory specified with [addr6].

Example: When the content of the address 0010H is 4 (0100B).

SET [0x0010],0 ...Sets the bit 0 in the address 0010H to "1" ([0010H] = 5)

CALR [0x0010] ...Calls the subroutine 6 steps after

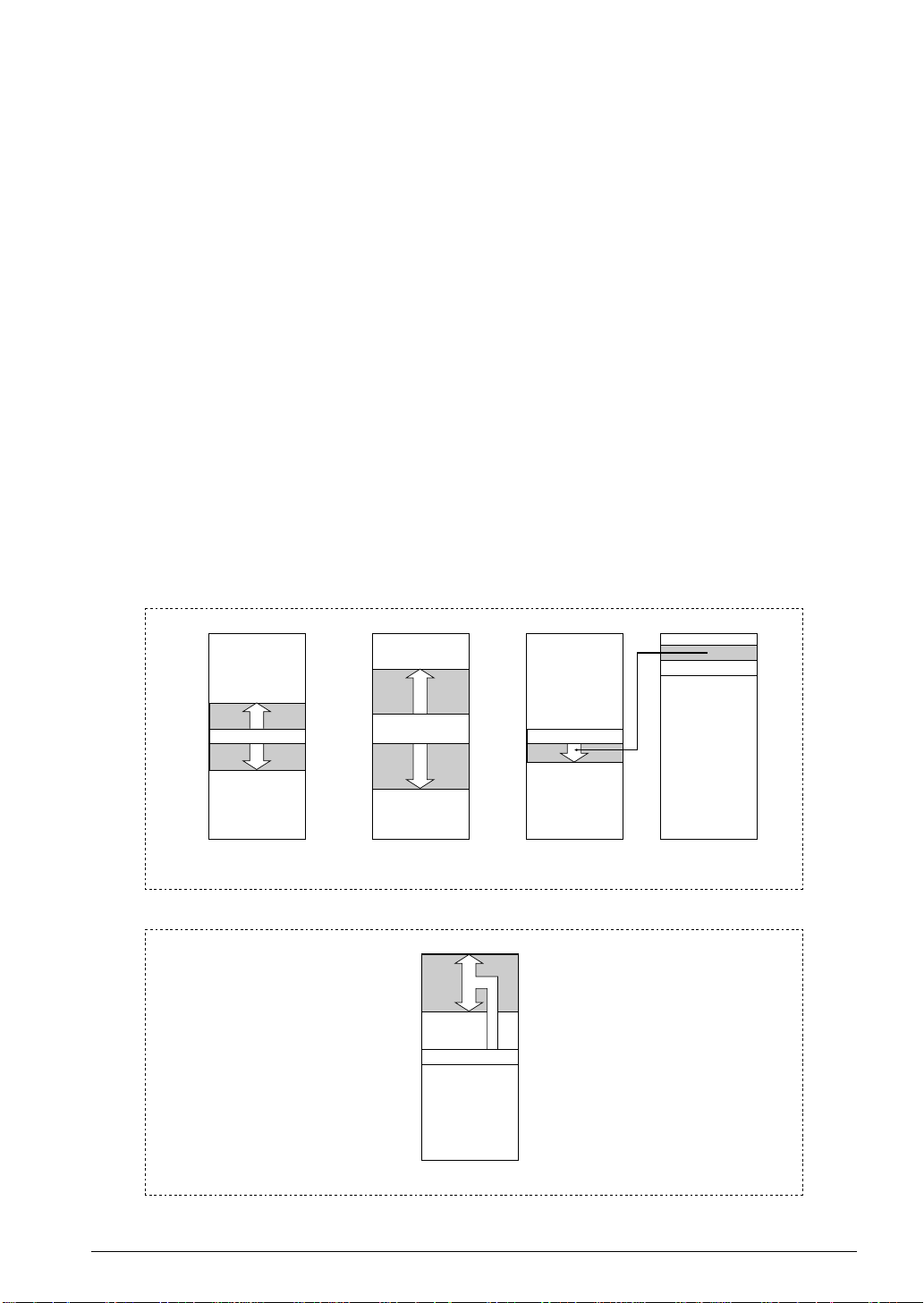

Figure 2.2.3.2 shows the operation of the call instructions and the branch range.

0000H

xxxxH-127

xxxxH

xxxxH+128

FFFFH

Program memory

xxxxH-32767

CALR sign8

xxxxH+32768

Program memory Program memory Data memory

0000H

∗

xxxxH-1

LDB %EXT,imm8

xxxxH

CALR sign8

xxxxH

xxxxH+16

CALR [addr6]

∗

FFFFH

∗ In the extended addressing mode,

this instruction can call subroutines

over a 64K program memory.

FFFFH

[addr6]=0 → xxxxH+1

:

[addr6]=15 → xxxxH+16

PC relative call instructions

Program memory

0000H

00FFH

CALZ imm8

0000H

addr6

003FH

FFFFH

FFFFH

imm → Branch destination

absolute address

Absolute call instruction

Fig. 2.2.3.2 Operation of call instructions

S1C63000 CORE CPU MANUAL EPSON 15

Page 22

CHAPTER 2: ARCHITECTURE

• Return instructions (RET, RETS, RETD, RETI)

A return instruction is used to return from a subroutine called by the call instruction to the routine

that called the subroutine. Return operation is done by loading the PC value (address next to the call

instruction) that was stored in the stack when the subroutine was called into the PC.

The RET instruction operates only to return the PC value in the stack, and the processing is continued

from the address next to the call instruction.

The RETS instruction returns the PC value then adds "1" to the PC. It skips executing an instruction

next to the call instruction.

Figure 2.2.3.3 shows return operations from a subroutine.

Mainroutine Subroutine

:

:

Address

xxxxH

xxxxH+1

xxxxH+2 Return to

:

CALR sign8

JR

sign8

LD

%A,[%X]

:

ADD

A,B

:

JR

NC,1

RET (RETD)

RETS

xxxxH+1

Return to

xxxxH+2

Fig. 2.2.3.3 Return from subroutine

The RETD instruction performs the same operation as the RET instruction, then stores the 8-bit data

specified in the operand into the memory specified with the X register. This function is useful to create

data tables that will be explained in the next section.

The RETI instruction is for the exclusive use of hardware and software interrupt service routines.

When an interrupt is generated, the content of the F register is saved into the stack with the current

PC value. The RETI instruction returns them.

• Software interrupt instruction (INT)

The software interrupt instruction "INT imm6" specifies a vector address within the addresses from

0111H to 013FH to execute its interrupt service routine. It can also call a hardware interrupt service

routine because it can specify an address from 0100H. It performs the same operation with the call

instruction, but the F register is also saved into the stack before branching. Consequently, the RETI

instruction must be used for returning from interrupt service routines. See Section 3.5, "Interrupts" for

details of the interrupt.

2.2.4 Table look-up instruction

The RETD instruction, one of the return instructions, has an 8-bit data in the operand, and stores the data

in the memory specified with the X register (the low-order 8 bits are stored in [X] and the high-order 8

bits are stored in [X+1]) immediately after returning.

By using the RETD instruction combined with the "JR %BA" or "JR %A" instructions, an 8-bit data table

for an LCD segment data conversion or similar can simply be constructed in the code ROM.

Example: The following is an example of a table for converting a BCD data (0 to 9) in the A register

into an ASCII code (30H to 39H). The conversion result is stored in the addresses 0040H

(low-order 4 bits) and 0041H (high-order 4 bits).

LD %A,3 ;Sets data to be converted

CALR TOASCII ;Calls converting routine

LDB %BA,[%X]+ ;Loads result from memory to BA register

:

:

16 EPSON S1C63000 CORE CPU MANUAL

Page 23

CHAPTER 2: ARCHITECTURE

TOASCII: ;BCD to ASCII conversion

LDB %EXT,0x00 ;Sets address 0040H

LDB %XL,0x40

JR %A

RETD 0x30 ;"0"

RETD 0x31 ;"1"

RETD 0x32 ;"2"

RETD 0x33 ;"3"

RETD 0x34 ;"4"

RETD 0x35 ;"5"

RETD 0x36 ;"6"

RETD 0x37 ;"7"

RETD 0x38 ;"8"

RETD 0x39 ;"9"

As shown in the example, operation results in the A or BA register can simply be converted into other

formats.

2.3 Data Memory

2.3.1 Configuration of data memory

In addition to the program memory space, the S1C63000 can also access 64K-word (× 4 bits) data memory.

In the individual model of the S1C63 Family, RAM of which size is decided depending on the model and

I/O memory are connected to this space.

Figure 2.3.1.1 shows the data memory map of the S1C63000.

4-bit

Address

0000H

00FFH

0100H

03FFH

0400H

FEFFH

FF00H

FFFFH

Fig. 2.3.1.1 S1C63000 data memory map

The S1C63000 can access 64K-word space linearly without any of the page management commonly used

in current 4-bit microcomputers.

The S1C63000 has a built-in 16-bit data bus for the address stack (SP1), and a RAM that permits 16-bit

data accessing can be connected to the addresses 0000H to 03FFH. The 16-bit accessible area is different

depending on the individual models. That area permits normal 4-bit accessing. Switching between 4-bit

accessing and 16-bit accessing is done according to the instruction by the hardware. A normal 4-bit data

stack (SP2) is assigned within the addresses 0000H to 00FFH.

SP1, SP2 stack area

Data

and

Data

and

SP1 stack area

Data area

I/O memory area

The addresses FF00H to FFFFH are used for an I/O memory area to control the peripheral circuits.

S1C63000 CORE CPU MANUAL EPSON 17

Page 24

CHAPTER 2: ARCHITECTURE

2.3.2 Addressing for data memory

For addressing to access the data memory, the index registers X and Y, and stack pointers SP1 and SP2 are

used. (The next section will explain the stack pointers.)

Index registers X and Y are both 16-bit registers and cover the entire 64K data memory space. The data

memory is accessed by setting an address in the register.

Example:

LDB %EXT,0x00

LDB %XL,0x10 ...Sets 0010H in the X register

LD A,[%X] ...Loads the content of the memory address 0010H into the A register

The indirect addressing with the X or Y register permits use of the post-increment function and processing for continuous addresses can be done efficiently. This function can be used in the instruction with

[%X]+ or [%Y]+ as an operand. [%X]+ indicates that the content of the X register is incremented after end

of transfer or operation, therefore the next address can be accessed without the X register re-setting. It is

the same in case of the Y register.

Example: To copy the 3-word data from the address specified with the X register to the area specified

with the Y register

LD [%Y]+,[%X]+

LD [%Y]+,[%X]+

LD [%Y],[%X]

In addition, the S1C63000 has also provided instructions in order to efficiently access only the area which

is accessed frequently such as the I/O memory and lower addresses.

One of that is the addressing using the EXT register explained in Section 2.1.5.

• Accessing for addresses 0000H to 00FFH

For absolute addressing in this area, the EXT register and an indirect instruction with the X register

([%X]) are used. To access this area, first write an 8-bit low-order address (00H to FFH) in the EXT

register, then execute an indirect addressing instruction with an operand [%X] (only the instruction

that permits the extended addressing). In this case, the content of the X register does not affect the

address to be accessed. Also the content of the X register is not changed.

Example:

LDB %EXT,0x37

LD %A,[%X] ...Works as "LD %A, [0x0037]"

• Accessing for addresses FF00H to FFFFH (I/O memory area)

For absolute addressing in this area, the EXT register and an indirect instruction with the Y register

([%Y]) are used. To access this area, first write an 8-bit low-order address (00H to FFH) in the EXT

register, then execute an indirect addressing instruction with an operand [%Y] (only the instruction

that permits the extended addressing). In this case, the content of the Y register does not affect the

address to be accessed. Also the content of the Y register is not changed.

Example:

LDB %EXT,0x9C

ADD [%Y],5 ...Works as "ADD [0xFF9C], 5"

Note: The extended addressing function using the EXT register is effective only for the instruction

following immediately after writing data to the EXT register or setting the E flag to "1". For that

instruction, do not use instructions other than the instructions that permit the extended addressing.

Operation cannot be guaranteed if used.

In addition to the above functions, some 6-bit addressing instructions are provided to directly access

that area. These instructions have a [addr6] as the operand and can alone directly access the area

0000H to 003FH or FFC0H to FFFFH.

18 EPSON S1C63000 CORE CPU MANUAL

Page 25

CHAPTER 2: ARCHITECTURE

• Accessing for addresses 0000H to 003FH

Data in this area is used for a relative address by the "JR [addr6]" and "CALR [addr6]" explained in

Section 2.2.3. This area is suitable for setting up various flags and counters since the bit operation

instructions (CLR, SET, TST) and increment/decrement instructions (INC, DEC) are provided for

accessing this area.

• Accessing for addresses FFC0H to FFFFH (I/O memory area)

The bit operation instructions (CLR, SET, TST) are provided for accessing this area. Therefore, control

bits in the I/O memory can be operated simply.

Examples:

CLR [0xFFC0],0 ...Clears the D0 bit in the I/O memory address FFC0H to "0"

SET [0xFFD2],3 ...Sets the D3 bit in the I/O memory address FFD2H to "1"

2.3.3 Stack and stack pointer

The stack is a memory that is accessed in the LIFO (Last In, First Out) format and is allocated to the RAM

area of the address 0000H to 03FFH. The stack area can be set from an optional address (toward the lower

address) using the stack pointer.

The S1C63000 contains two stack pointers SP1 and SP2.

(1)Stack pointer SP1

The SP1 is used for the address data stack, and permits 16-bit data accessing.

D0D1D2D9D10D15

0SP17 00000000

Stack pointer 1

8 bits to be modified

Fig. 2.3.3.1 SP1 configuration

As shown in the figure, the D0, D1 and D10–D15 within the 16 bits are fixed at "0". 8 bits of the D2–D9

can be set by software. Furthermore, the hardware also operates for this 8-bit field. Therefore, addressing by the SP1 is done in 4-word units, and a 16-bit address data can be transferred in one

accessing. Since the SP1 performs 16-bit data accessing, this stack area is limited to the 16-bit accessible RAM area even though it is within the addresses 0000H to 03FFH.

This stack is used to evacuate return addresses when the call instructions are executed or the interrupts are generated. It is also used when the 16-bit data in the X or Y register is evacuated using the

PUSH instruction. The return address data is written into the stack as shown in Figure 2.3.3.2.

The SP1 is decremented after the data is evacuated and is incremented when a return instruction is

executed or after returning data by executing the POP instruction.

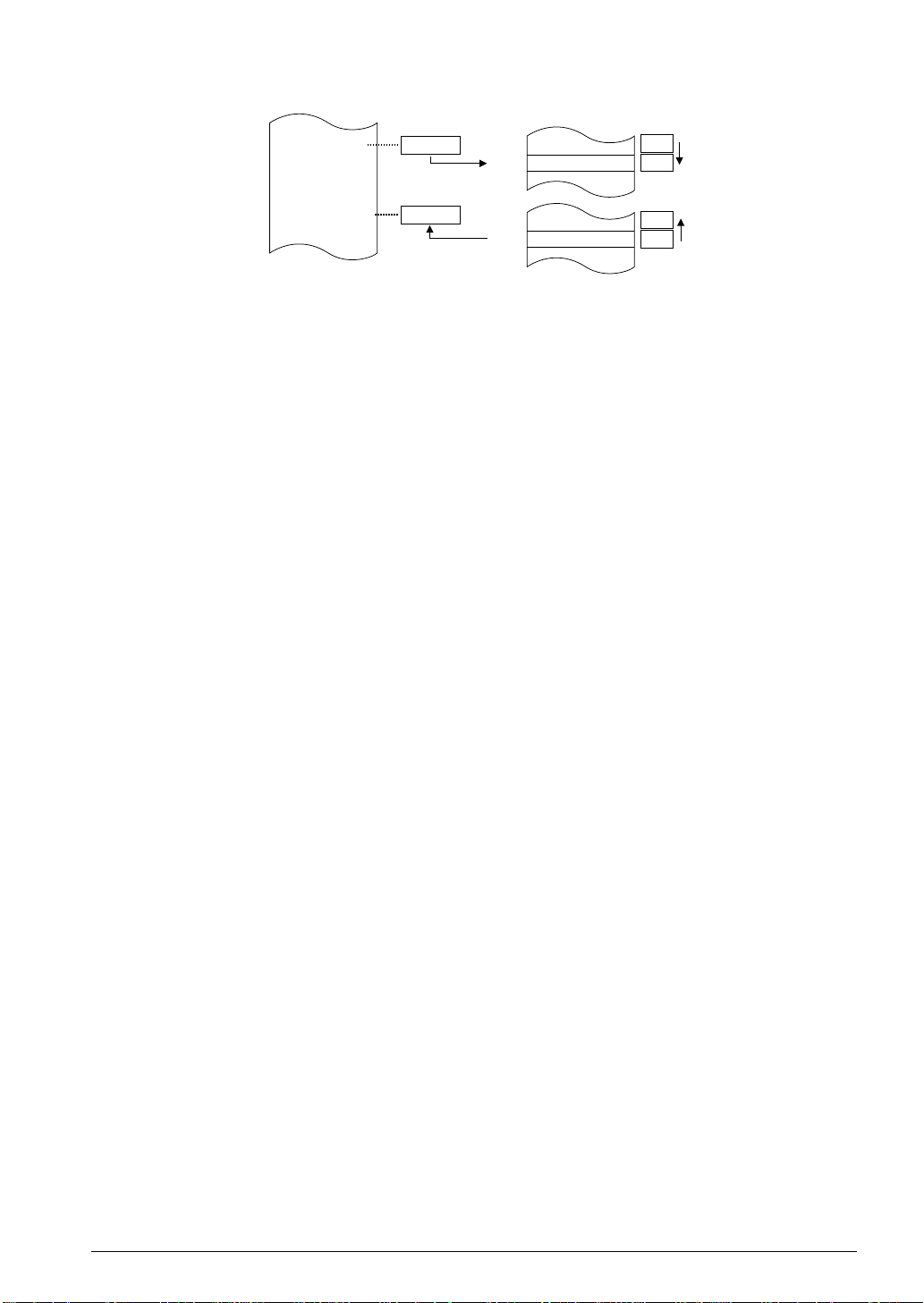

Program memory

ROM

Address

1234H

1235H

:

CALR sign8

:

Subroutine

:

RET

PC

1235H

PC

1235H

Address

00FFH

00FEH

00FDH

00FCH

00FFH

00FEH

00FDH

00FCH

ROM

Stack (SP1)

5H

3H

2H

1H

5H

3H

2H

1H

SP1

40H

(= Address 100H)

(= Address FCH)

3FH

SP1

40H

(= Address 100H)

(= Address FCH)

3FH

Fig. 2.3.3.2 Address stack operation

S1C63000 CORE CPU MANUAL EPSON 19

Page 26

CHAPTER 2: ARCHITECTURE

The SP1 increment/decrement affects only the 8-bit field shown in Figure 2.3.3.1, and its operation is

performed cyclically. In other words, if the SP1 is decremented by the PUSH instruction or other

conditions when the SP1 is 00H (indicating the memory address 0000H), the SP1 becomes FFH

(indicating the memory address 03FCH). Similarly, if the SP1 is incremented by the POP instruction or

other conditions when the SP1 is FFH (indicating the memory address 03FCH), the SP1 becomes 00H

(indicating the memory address 0000H).

• Queue register

The queue register is provided in order to reduce the process time of the 16-bit data transfer by

the SP1. The queue register retains 16-bit data in the RAM indicated with the SP1. It is accessed

when the following instructions are executed, not by programs directly.

1. When the call instruction or the PUSH instruction is executed, and when an interrupt is generated

When the CALR or CALZ instruction is executed, a software interrupt by the INT instruction is

generated, and a hardware interrupt is generated, the PC value for returning is written in the

memory [SP1-1]. When the "PUSH %X" or "PUSH %Y" instruction is executed, the content of

the X register or Y register is written in the memory [SP1-1]. At this time, the same data which

is written in the memory [SP1-1] is also written to the queue register.

2. When the return instruction or the POP instruction is executed

When the RET, RETS, RETD, RETI, "POP %X" or "POP %Y" instructions are executed, the data

retained in the queue register is returned to the PC, X register or Y register. Since the SP1 is

incremented, the content of the queue register is renewed (it generates a bus cycle to load the

content of the memory [SP1+1] to the queue register).

3. When the "LDB %SP1, %BA", "INC SP1" or "DEC SP1" instructions are executed

When these instructions are executed, the content of the queue register is also renewed (it

generates a bus cycle to load the content of the memory [SP1] to the queue register).

Note: As shown above, the memory content that is indicated by the SP1 is written to the queue register

according to the SP1 changes. Therefore, the queue register is not renewed even if the memory

[SP1] is directly modified when the SP1 is not changed. Be aware that intended return and POP

operations cannot be performed if such an operation is done.

(2)Stack pointer SP2

The SP2 is used for the normal 4-bit data stack.

D0D7D8D15

Stack pointer 2

SP2

00H

7

8 bits to be modified

Fig. 2.3.3.3 SP2 configuration

In the case of the SP1, the D8–D15 within the 16 bits are fixed at "0". 8 bits of the D0–D7 can be set by

software. Furthermore, the hardware also operates for this 8-bit field. The address range that can be

used for the data stack is limited to within 0000H to 00FFH. Data evacuation/return is done in 1-word

units.

This stack is used to evacuate the F register data when an interrupt is generated. It is also used when

the 4-bit register data (A, B, F) is evacuated using the PUSH instruction. The register data is written

into the stack as shown in Figure 2.3.3.4.

The SP2 is decremented after the data is evacuated and is incremented when the data is returned.

0

20 EPSON S1C63000 CORE CPU MANUAL

Page 27

CHAPTER 2: ARCHITECTURE

Program memory

:

PUSH A

:

POP A

A register

6H

A register

6H

Address

004FH

004EH

004FH

004EH

ROM

Stack (SP2)

6H

6H

SP2

50H

4FH

SP2

50H

4FH

Fig. 2.3.3.4 4-bit stack operation

The SP2 increment/decrement affects only the 8-bit field shown in Figure 2.3.3.3, and its operation is

performed cyclically. In other words, if the SP2 is decremented by the PUSH instruction or other

conditions when the SP2 is 00H (indicating the memory address 0000H), the SP2 becomes FFH

(indicating the memory address 00FFH). Similarly, if the SP2 is incremented by the POP instruction or

other conditions when the SP2 is FFH (indicating the memory address 00FFH), the SP2 becomes 00H

(indicating the memory address 0000H).

(3)Notes for using the stack pointer

• The SP1 and SP2 are undefined at an initial reset. Therefore, both the stack pointers must be initialized

by software.

For safety, all the interrupts including NMI are masked until both the SP1 and SP2 are set by software.

Furthermore, if either the SP1 or SP2 is re-set, all the interrupts are masked again until the other is reset. Therefore be sure to set the SP1 and SP2 as a pair.

• The increment/decrement for the SP1 and SP2 is operated cyclically from 0000H to 03FFH (SP1) and

from 0000H to 00FFH (SP2) regardless of the memory capacity/allocation set up in each model.

Control with the program so that the stacks do not cross over the upper/lower limits of the mounted

memory.

• The SP1 must be set in the RAM area that permits 16-bit accessing depending on the model. The SP1

address stack cannot be allocated to other than the 16-bit accessible area even if the address is less

than 03FFH.

• The area management for the SP1 stack, SP2 stack and data RAM should be done by the user. Pay

attention to these areas so that they do not overlap in the same addresses.

2.3.4 Memory mapped I/O

The S1C63 Family contains the S1C63000 as the core CPU and various types of peripheral circuits, such as

input/output ports. The S1C63000 has adopted a memory mapped I/O system for controlling the

peripheral circuits, and the control bits and the registers for exchanging data are arranged in the data

memory area.

The I/O memory for controlling the peripheral circuits is assigned to the area from FF00H to FFFFH, and

is distinguished from RAM and others. However, the accessing method is the same as RAM, so indirect

addressing can be done using the X or Y register. In addition, since the I/O memory is accessed frequently, the exclusive instructions for this area are also provided. (See Section 2.3.2.)

Refer to the manual for the individual model of the S1C63 Family for the I/O memory and the peripheral

circuits.

S1C63000 CORE CPU MANUAL EPSON 21

Page 28

CHAPTER 3: CPU OPERATION

CHAPTER 3 CPU OPERATION

This section explains the CPU operations and the operation timings.

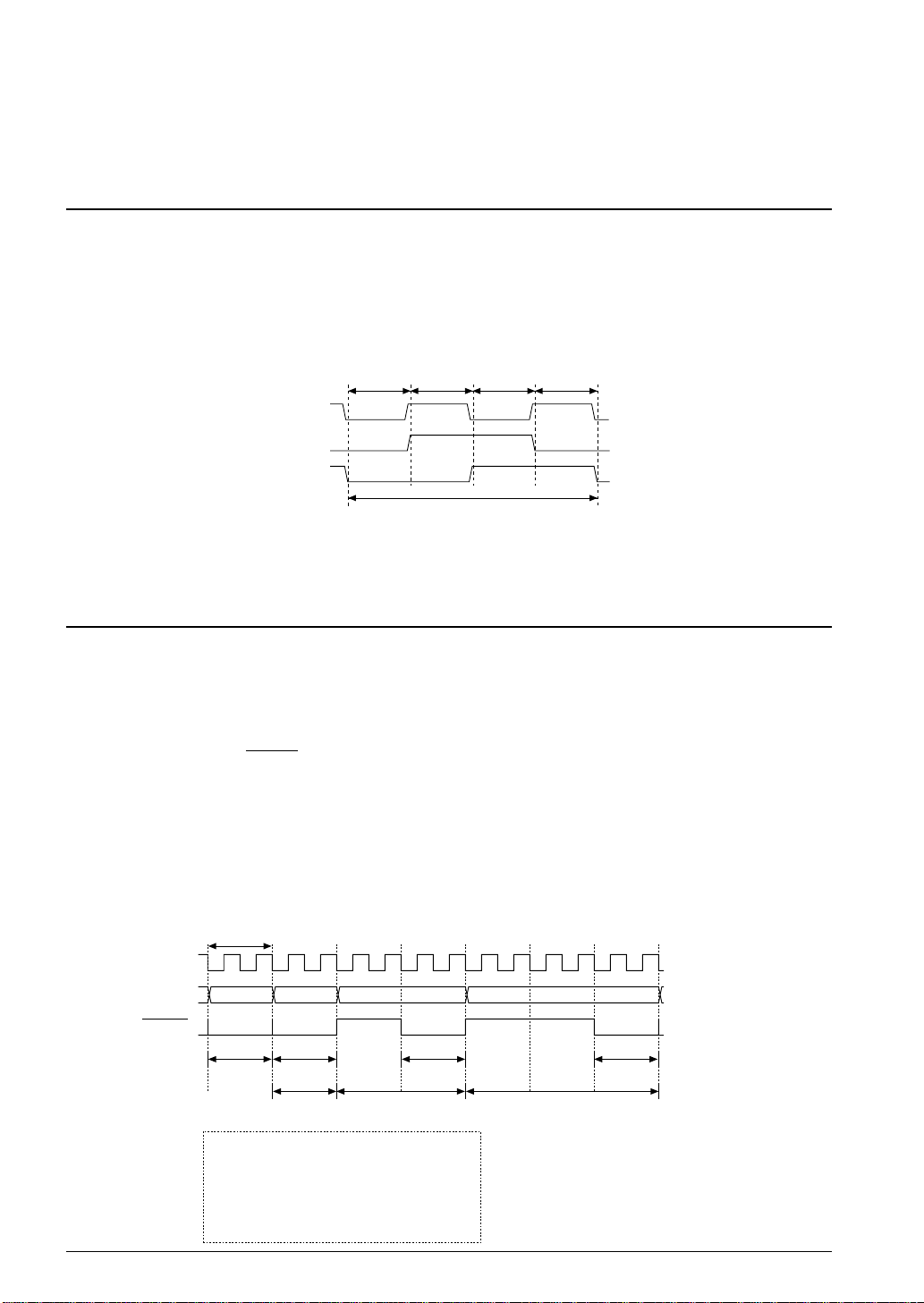

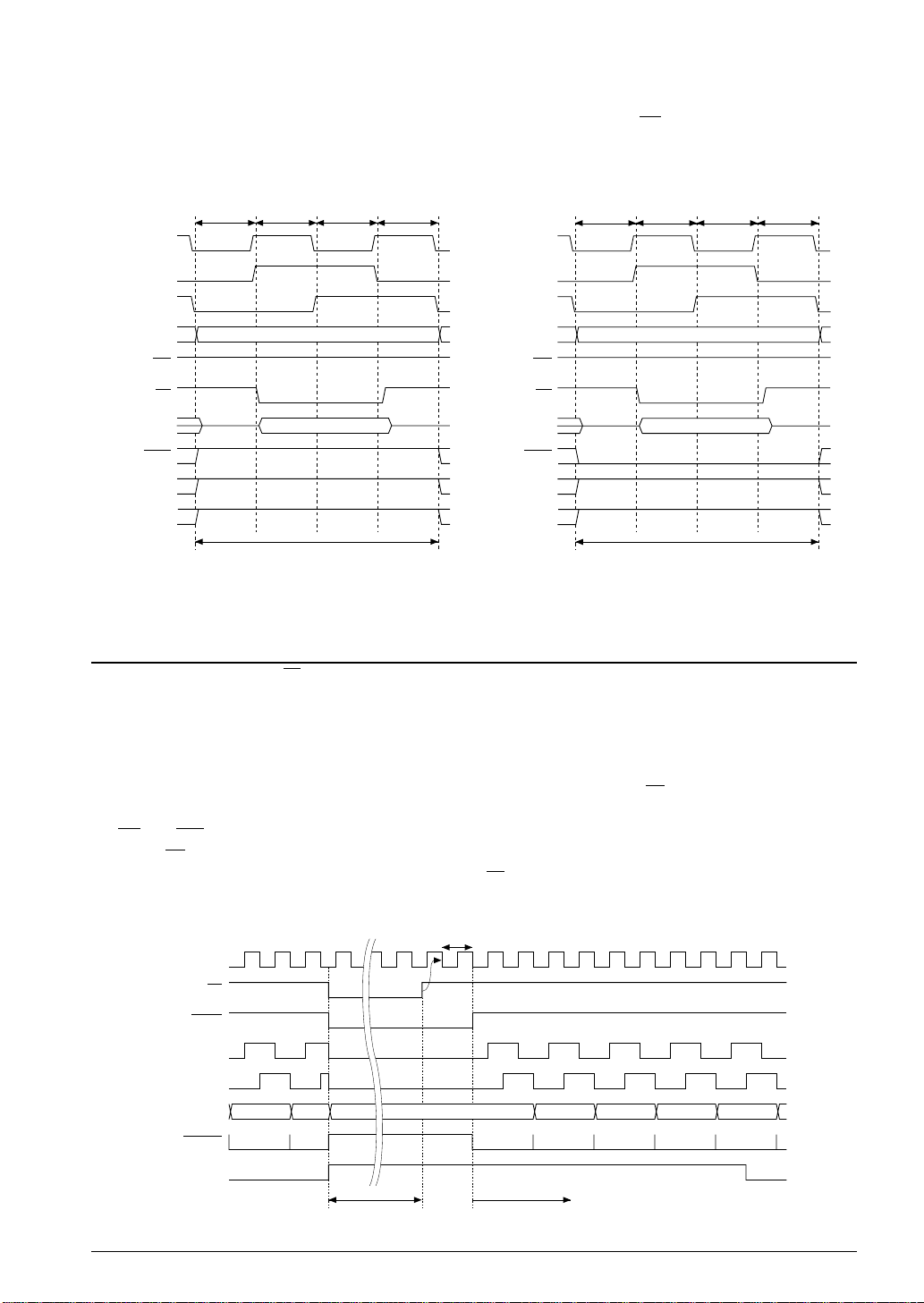

3.1 Timing Generator and Bus Cycle

The S1C63000 has a built-in timing generator. The timing generator of the S1C63000 generates the twophase divided signals PK and PL based on the clock (CLK) input externally (∗) to make states. One state

is a 1/2 cycle of the CLK and the one bus cycle that becomes the instruction execution unit is composed

of four states.

∗ The clock that is input to the S1C63000 is generated by an oscillation circuit provided outside of the

CPU. The S1C63 Family models have a built-in oscillation circuit.

State State State State

T1 T2 T3 T4

CLK

PK

PL

Bus cycle

Fig. 3.1.1 State and bus cycle

The number of cycles which is stated in the instruction list indicates the number of bus cycles.

3.2 Instruction Fetch and Execution

The S1C63000 executes the instructions indicated with the PC (program counter) one by one. That

operation for an instruction is divided into two stages; one is a fetch cycle to read an instruction, and

another is an execution cycle to execute the instruction that has been read.

All the S1C63000 instructions are composed of one step (word), and are fetched in one bus cycle. An

instruction code that is written in the ROM is read out during the fetch cycle and is analyzed by the

instruction decoder. The FETCH signal goes to a low level during that time. In addition, the PC is

incremented at the end of each fetch.

The analyzed instruction is executed from the next bus cycle. The number of execution cycles is shown in

the instruction list and it is one, two or three bus cycles depending on the instruction.

The S1C63000 contains two different buses for the program memory and the data memory. Consequently,

a fetch cycle for the next instruction can be executed to overlap with the last execution cycle, and it

increases the processing speed. In the one-cycle instructions, the next instruction is fetched at the same

time an instruction is executed.

One bus cycle

T1 T2 T3 T4

CLK

ROM address (PC)

FETCH

Fetch cycle

Execution cycle

PC PC+1 PC+2 PC+3

(PC) (PC+1) (PC+2)

inst. 1 inst. 2 inst. 3

inst. 1 inst. 2 inst. 3

ROM address

:

PC

PC+1

PC+2

PC+3

:

one-cycle

instruction

inst. 1 (one-cycle instruction)

inst. 2 (two-cycle instruction)

inst. 3 (three-cycle instruction)

inst. 4 (one-cycle instruction)

two-cycle

instruction

Instruction

:

:

(PC+3)

inst. 4

three-cycle

instruction

Fig. 3.2.1 Fetch cycle and execution cycle

22 EPSON S1C63000 CORE CPU MANUAL

Page 29

CHAPTER 3: CPU OPERATION

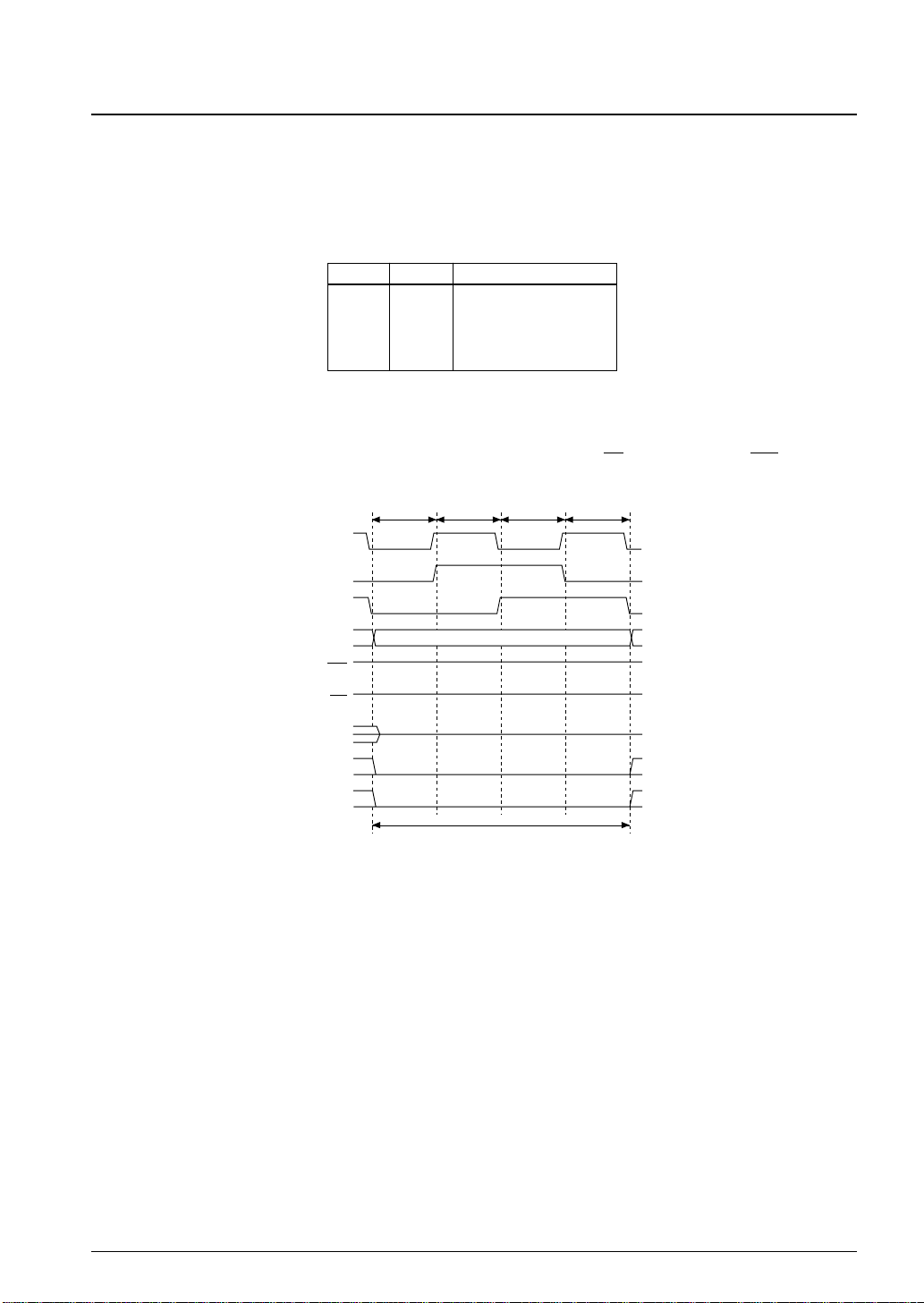

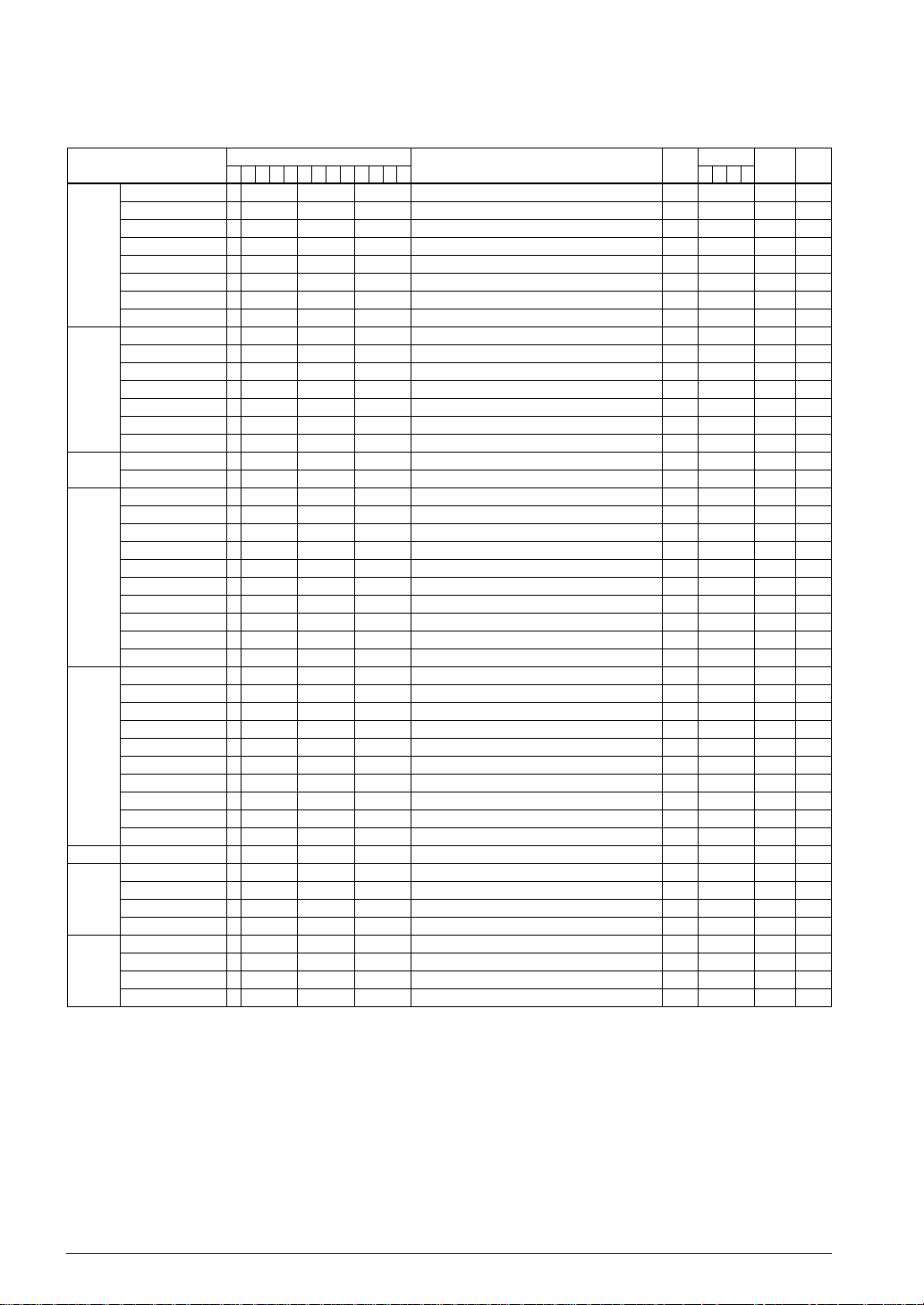

3.3 Data Bus (Data Memory) Control

3.3.1 Data bus status

The S1C63000 output the data bus status in each bus cycle externally on the DBS0 and DBS1 signals as a

2-bit status. The peripheral circuits perform the direction control of the bus driver and other controls with

these signals. The data bus statuses indicated by the DBS0 and DBS1 are as shown in Table 3.3.1.1.

Table 3.3.1.1 Data bus status

DBS1

3.3.2 High-impedance control

The data bus goes to a high-impedance during an execution cycle (∗) that accesses only the internal

registers in the CPU. During the bus cycle period, both the read signal RD and write signal WR are fixed

at a high level and a dummy address is output on the address bus.

CLK

DBS0

0

0

1

1

0

High impedance

1

Interrupt vector read

0

Memory write

1

Memory read

T1 T2 T3 T4

State

PK

PL

DA00–DA15

WR

RD

D0–D3

DBS1

DBS0

Dummy address

Bus cycle

Fig. 3.3.2.1 Bus cycle during accessing internal register

∗ Data is output on the data bus only when the stack pointer SP1 is accessed because a data transfer is

performed between the queue register and the data memory. In this case, the data bus status becomes a

memory write or a memory read depending on the instruction that accesses the SP1.

S1C63000 CORE CPU MANUAL EPSON 23

Page 30

CHAPTER 3: CPU OPERATION

3.3.3 Interrupt vector read

When an interrupt is generated, the CPU reads the interrupt vector output to the data bus by the peripheral circuit that has generated the interrupt. The interrupt vector read status indicates this bus cycle. The

peripheral circuit outputs the interrupt vector to the data bus during this status, and the CPU reads the

data between the T2 and T3 states. At this time, the CPU outputs the RDIV signal (for exclusive use of the

interrupt vector read) as a read signal, not the RD signal that is used for normal data memory read. The

address bus outputs a dummy address during this bus cycle. See Section 3.5 for the operation when an

interrupt is generated.

CLK

PK

PL

DA00–DA15

RDIV

WR

RD

D0–D3

DBS1

T1 T2 T3 T4

Dummy address

Interrupt vector

DBS0

Bus cycle

Fig. 3.3.3.1 Bus cycle during reading interrupt vector

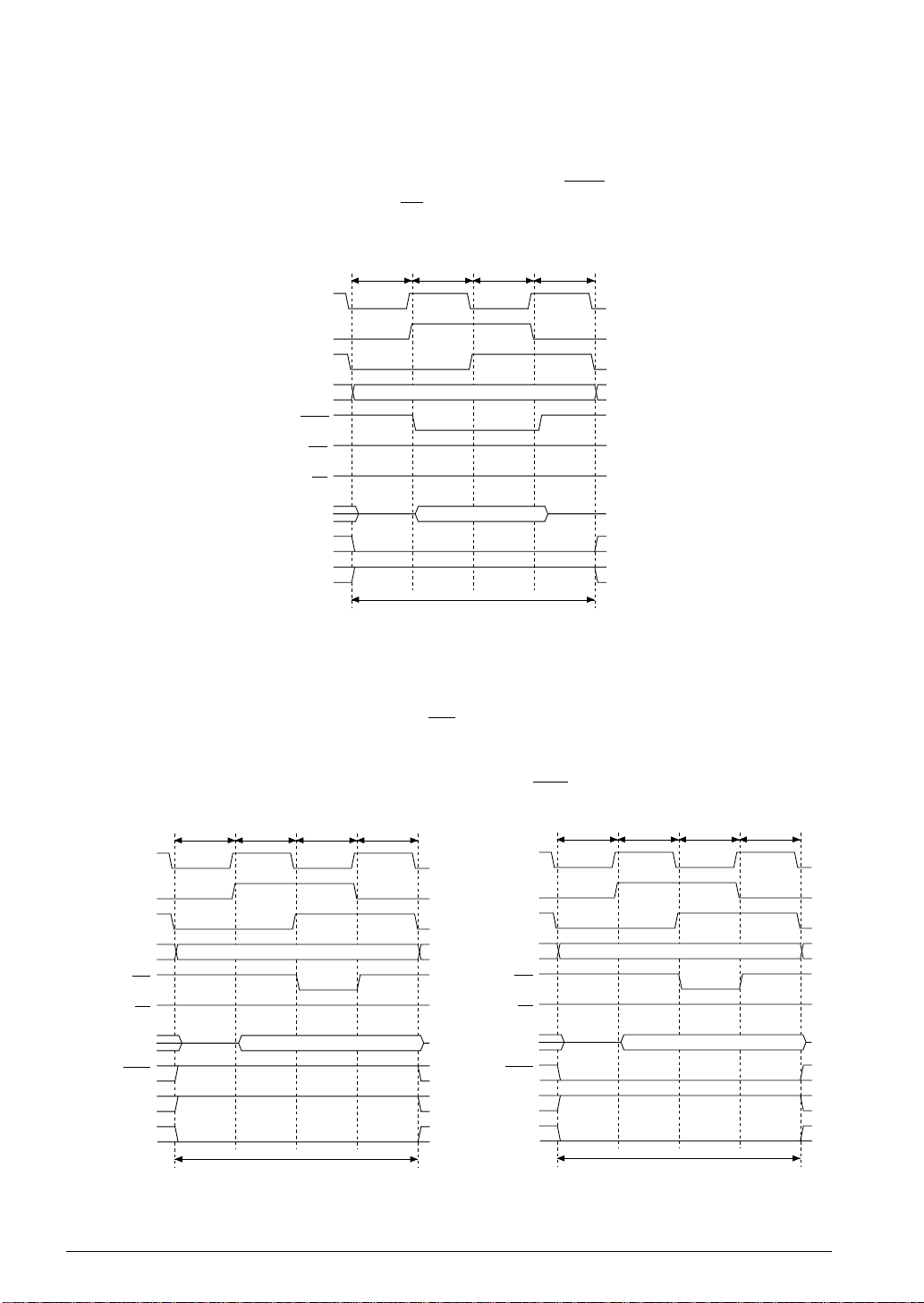

3.3.4 Memory write

In an execution cycle that writes data to the data memory, the writing data is output to the data bus

between the T2 and T4 states and the write signal WR is output in the T3 state. The address bus outputs

the target address during this bus cycle.

The S1C63000 contains a 4-bit data bus (D0–D3) and a 16-bit data bus (M00–M15) for an address stacking.

The CPU switches the data bus according to the instruction. The BS16 signal is provided for this switching.

DA00–DA15

CLaK

PK

PL

WR

RD

D0–D3