Epic EI16C552 Datasheet

Ei16C552

Part Numbers May Be Marked With "IMP" or "Ei."

For additional information, contact IMP, Inc. at 408.432.9100 or visit www.impweb.com

IMP, Inc. acquired Epic products on January 26, 2001. (see press release at http://www.impweb.com/PRESS/PR012601.htm)

Dual FIFO UART and

Parallel Port

FEATURES

• IBM PC AT™ and PS/2™ compatible

• Dual channel version of Ei16C550 with

Centronics printer interface

• Independent control of transmit, receive, line

status and data set interrupts on each channel

• Programmable serial interface characteristics for

each channel:

-5, 6, 7 or 8 bit characters

-Even, odd or no parity bit generation and

dectection

-1, 1.5 or 2 stop bit generation

• Programmable baud rate generator divides

CLK input by a divisor between 1 and (216 -1)

• Tri-State® TTL drive capability for bidirectional

data bus and control bus on each channel

• 16 byte FIFO for receiver as well as for trans

mitter.

• Advanced CMOS low power technology with

single 5 volt supply

DESCRIPTION

The Ei16C552 is an enhanced dual channel version

of the Ei16C550 Universal Asynchronous Receiver

Transmitter (UART). The device serves two serial

input/output interfaces simultaneously in microcomputer or microprocessor based systems.Each channel performs a serial-to-parallel conversion on data

characters received from peripheral devices or

modems, and a parallel-to-serial conversion on data

characters transmitted by the CPU. The complete

status of each channel of the dual UART can be

read at any time during functional operation by the

CPU.The information obtained includes the type and

condition of the transfer operations being performed,

and error conditions. In addition to its dual communications interface capabilities, the Ei16C552 provides the user with a fully bidirectional parallel data

port that fully suppor ts the parallel Centronics type

printer.The parallel port, together with the two serial

ports, provide IBM PC AT™ and PS2 compatible

computers with a single device to serve the three

system ports.

PIN CONFIGURATION

SOUT1

DTR1•

RTS1•

CTS1•

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

TXRDY0•

VCC

RTS0•

DTR0•

SOUT0

RXRDY0•

RSLD1•

GND

RI1•

DSR1•

CLK

CS1•

GND

LPTOE•

CS0

DSR0•

ACK•PEBUSY

68676665646362

A2A1A0

IOW•

987654321

10

11

12

13

14

15

16

17

Ei16C552-CJ68

18

19

20

21

22

23

24

25

26

2728293031323334353637383940414243

RI0•

GND

CTS0•

RSLD0•

IOR•

SLCT

CS2•

VCC

ERR•

VCC

RESET•

SIN0

SIN1

TXRDY1•

RXRDY1•

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

INTSLC

INT1

INT2

SLIN•

INIT•

AFD•

STB•

GND

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

INT0

BD0

5

Ei16C552

For additional information, contact IMP, Inc. at 408.432.9100 or visit www.impweb.com

IMP, Inc. acquired Epic products on January 26, 2001. (see press release at http://www.impweb.com/PRESS/PR012601.htm)

NOTES ON PIN DESCRIPTION:

1) Pin 4 and Pin 2 can be used by external crystal oscillator in future versions

2) Pin 23 and Pin 43 can be used as OUT20• and OUT21• respectively in future versions

ORDERING INFORMATION

Ei16C552-CJ68 68 Pin PLCC package

LIFE SUPPORT POLICY: Epic products are not to be used in life support devices without prior wr itten

authorization.

Epic Semiconductor Inc. retains the right to make changes these specifications at any time, without notice.

Tri-state® is a Registered Trademark of National Semiconductor,Inc.

IBM PC AT™ and PS2 are Trademark s of International Business Machines.

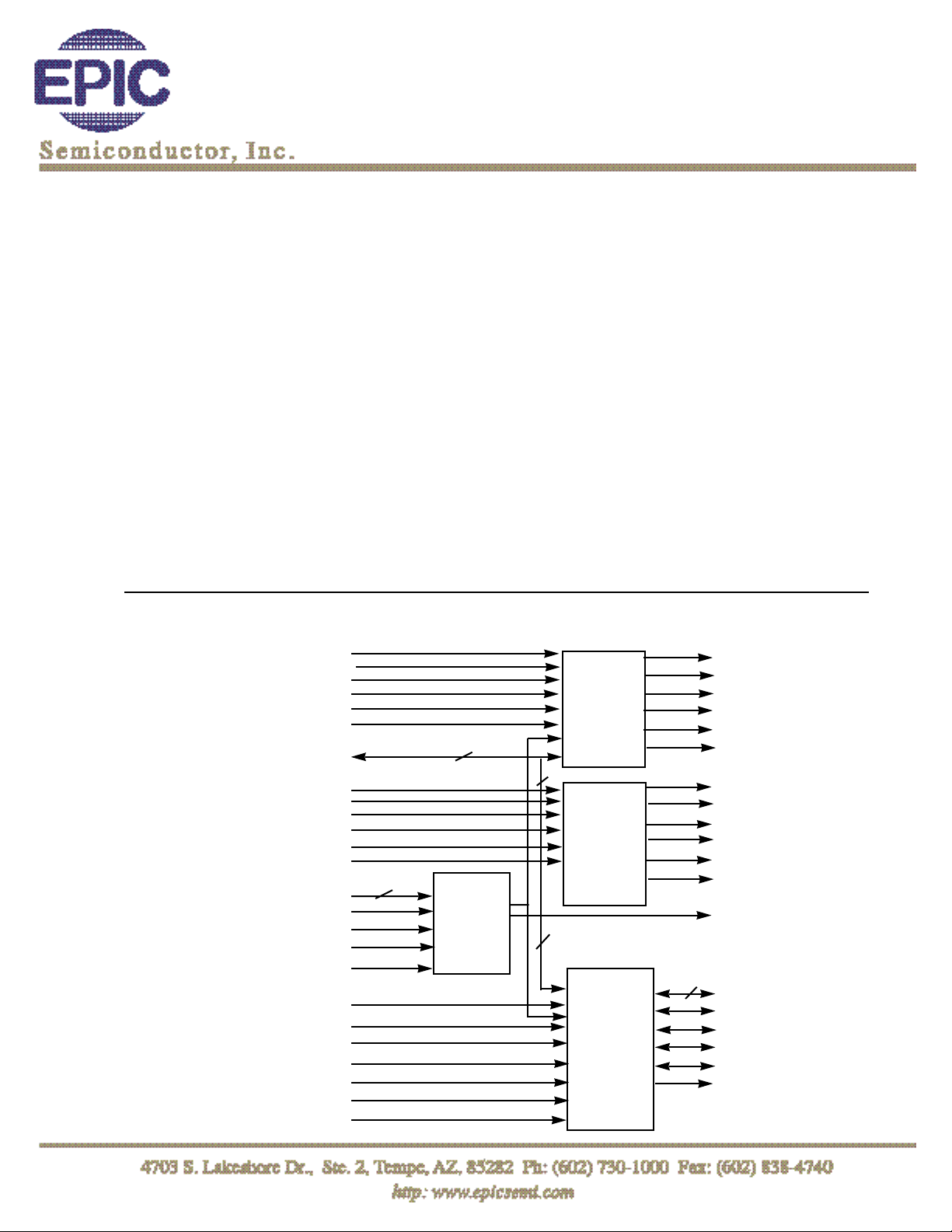

BLOCK DIAGRAM

CTS0•

DSDR0•

RLSD0•

R10•

SIN0

CS0•

DB0-DB7

CTS1•

DSR1•

RLSD1•

RI1•

SIN1

CS1•

A0-A2

IOW•

IOR•

RESET•

CLK

ERR•

SLCT

BUSY

PE

ACK•

LPTOE•

6

CS2•

3

8

SELECT

AND

CONTROL

LOGIC

•

UART

#1

8

UART

#2

8

PARALLEL

PORT

8

RTS0•

•

DTR0

SOUT0

INT0

TXRDY0•

RXRDY0*

RTS1•

DTR1•

SOUT1

INT1

TXRDY1•

RXRDY1•

BDO

PD0-PD7

INIT•

AFD•

STB•

SLIN•

INT2

Loading...

Loading...