EON EN29LV160JT-90TI, EN29LV160JT-90T, EN29LV160JT-70TI, EN29LV160JT-70T, EN29LV160JB-90TI Datasheet

...

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

1

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

0.

FEATURES

•

3.0V, single power supply operation

- Minimizes system level power requirements

•

Manufactured on 0.28 µm process technology

•

High performance

- Access times as fast as 70 ns

•

Low power consumption (typical values at 5

MHz)

- 7 mA typical active read current

- 15 mA typical program/erase current

- 1 µA typical standby current (standard access

time to active mode)

•

Flexible Sector Architecture:

- One 16 Kbyte, two 8 Kbyte, one 32 Kbyte, and

thirty-one 64 Kbyte sectors (byte mode)

- One 8 Kword, two 4 Kword, one 16 Kword

and thirty-one 32 Kword sectors (word mode)

- Supports full chip erase

- Individual sector erase supported

- Sector protection:

Hardware locking of sectors to prevent

program or erase operations within individual

sectors

Additionally, temporary Sector Group

Unprotect allows code changes in previously

locked sectors.

•

High performance program/erase speed

- Byte program time: 8µs typical

- Sector erase time: 200ms typical

- Chip erase time: 3.5s typical

•

JEDEC Standard program and erase

commands

•

JEDEC standard

DATA

polling and toggle

bits feature

•

Single Sector and Chip Erase

•

Sector Unprotect Mode

•

Embedded Erase and Program Algorithms

•

Erase Suspend / Resume modes:

Read and program another Sector during

Erase Suspend Mode

•

0.28 µm double-metal double-poly

triple-well CMOS Flash Technology

•

Low Vcc write inhibit < 2.5V

• >100K program/erase endurance cycle

•

48-pin TSOP (Type 1)

•

Commercial Temperature Range

GENERAL DESCRIPTION

The EN29LV160J is a 16-Megabit, electrically erasable, read/write non-volatile flash memory,

organized as 2,097,152 bytes or 1,048,576 words. Any byte can be programmed typically in 10µs.

The EN29LV160J features 3.0V voltage read and write operation, with acces s times as fas t as 55ns

to eliminate the need for WAIT states in high-performance microprocessor systems.

The EN29LV160J has separate Output Enable (

OE

), Chip Enable (CE), and Write Enable (WE)

controls, which eliminate bus contention issues. This device is designed to allow either single Sector

or full chip erase operation, where each Sector can be individually protected against program/erase

operations or temporarily unprotected to erase or program. The device can sustain a minimum of

100K program/erase cycles on each Sector.

EN29LV160J ******PRELIMINARY DRAFT******

16 Megabit (2048K x 8-bit / 1024K x 16-bit) Flash Memory

Boot Sector Flash Memory, CMOS 3.0 Volt-only

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

2

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

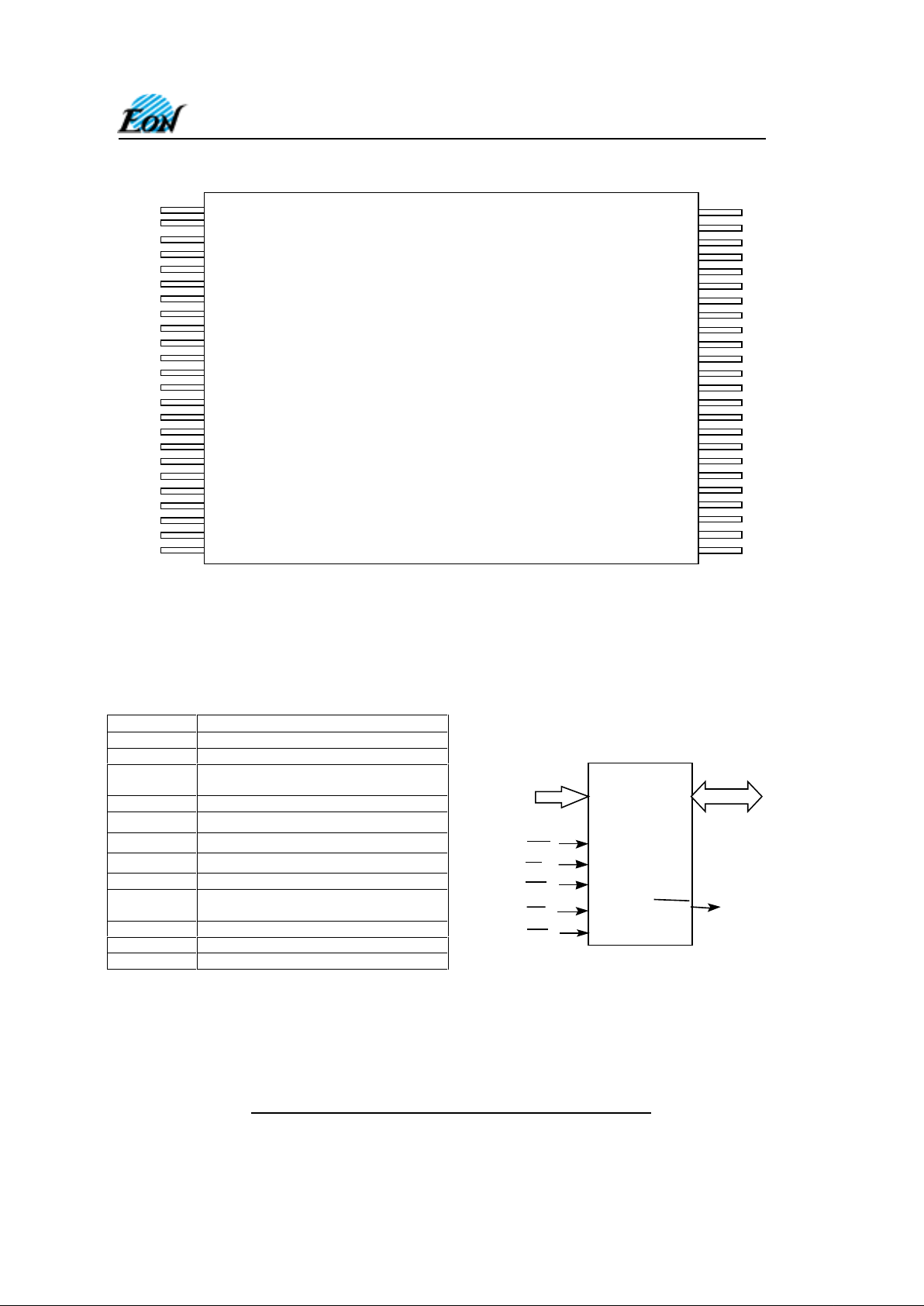

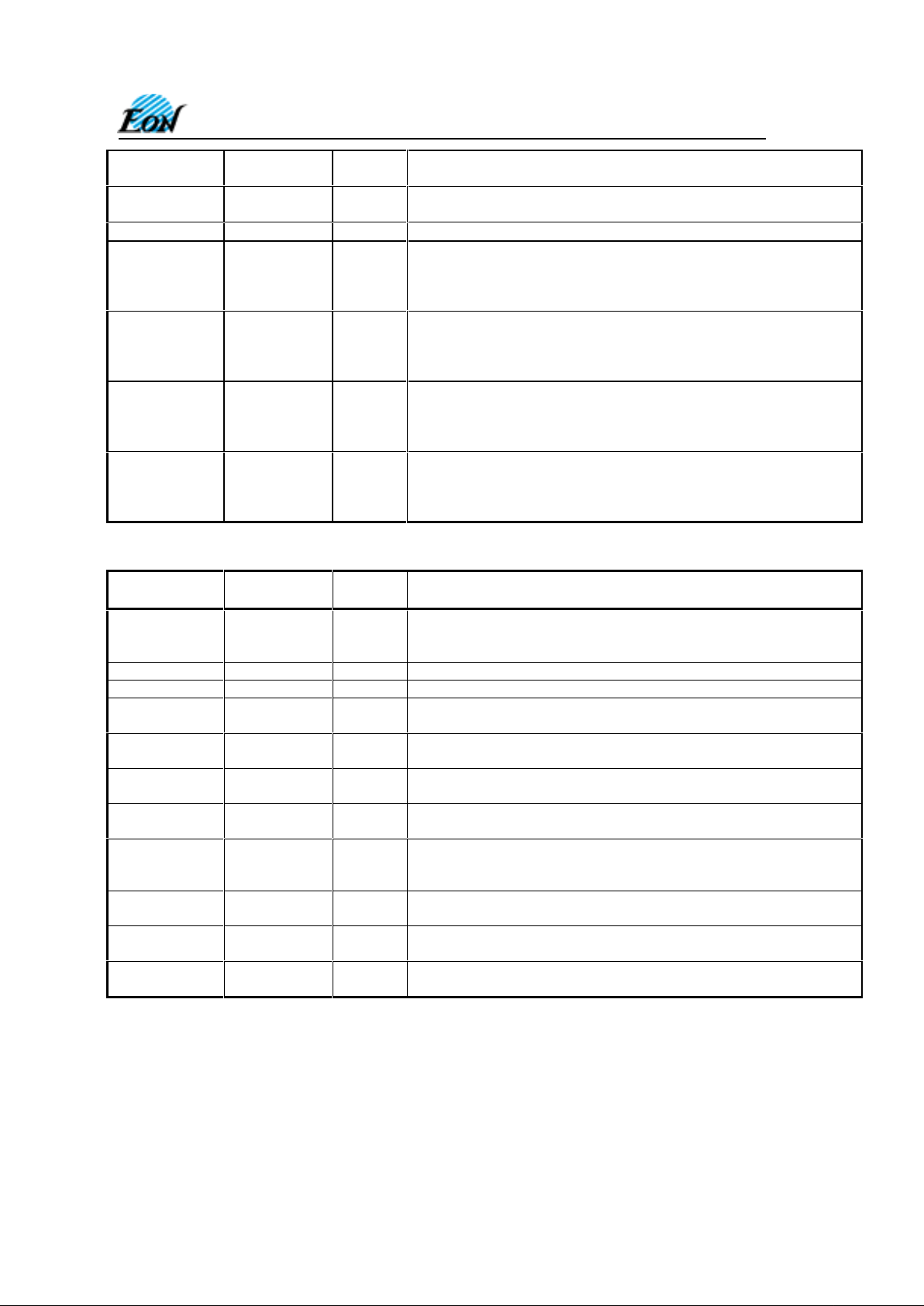

CONNECTION DIAGRAMS

TABLE 1. PIN DESCRIPTION FIGURE 1. LOGIC DIAGRAM

Pin Name Function

A0-A19 20 Addresses

DQ0-DQ14 15 Data Inputs/Outputs

DQ15 / A-1

DQ15 (data input/output, word mode),

A-1 (LSB address input, byte mode)

CE# Chip Enable

OE# Output Enable

RESET#

Hardware Reset Pin

RY/BY# Ready/Busy Output

WE# Write Enable

Vcc

Supply Voltage

(2.7-3.6V)

Vss Ground

NC Not Connected to anything

BYTE# Byte/Word Mode

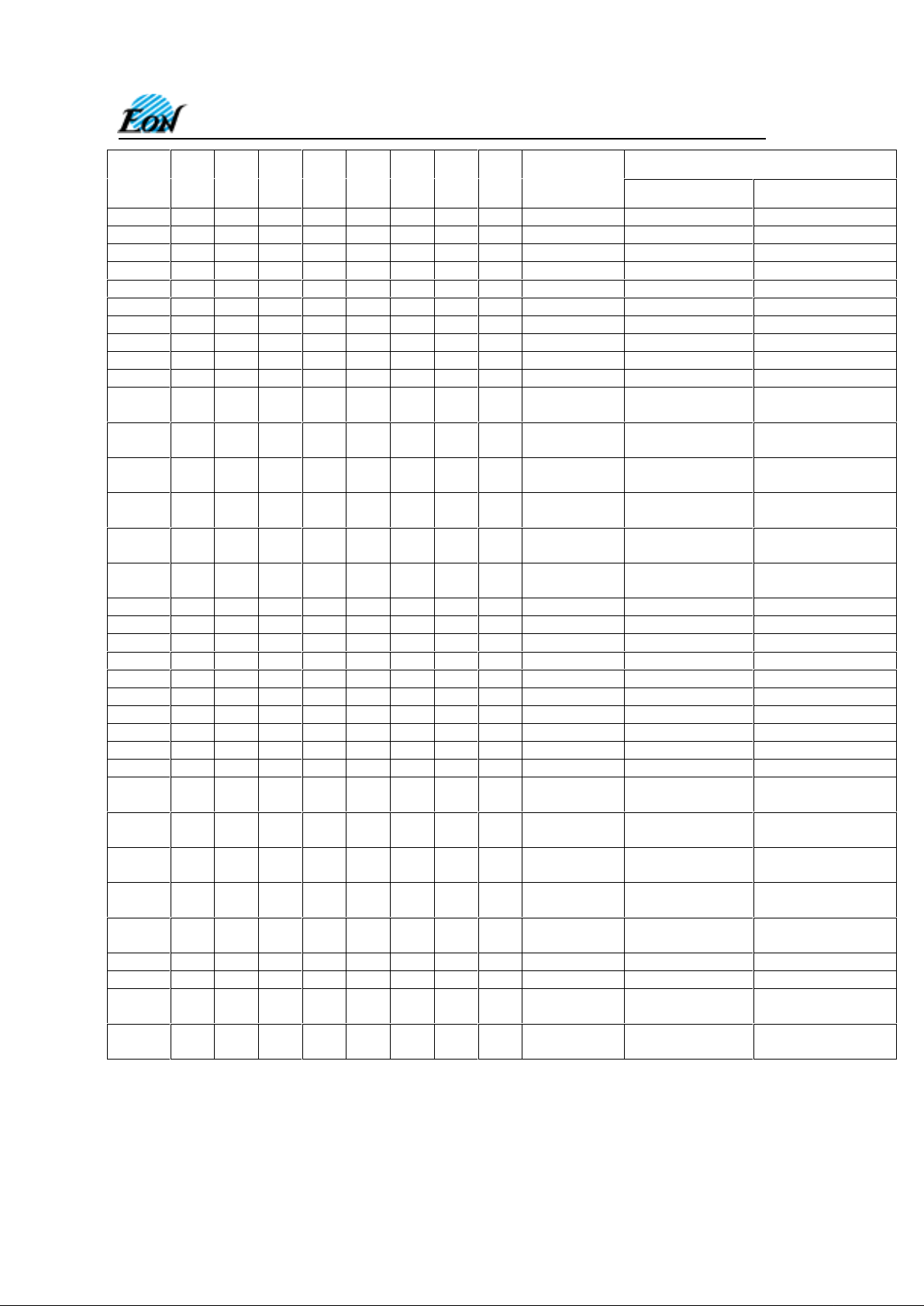

Table 2. Sector Address Tables (EN29LV160J)

EN29LV160

DQ0 – D

Q15

(A-1)

A0 – A19

WE

CE

OE

RY/BY

Reset

Byte

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

Standard

TSOP

A15

A14

A13

A12

A11

A10

A9

A8

A19

NC

WE#

RESET#

NC

NC

RY/BY#

A18

A17

A7

A6

A5

A4

A3

A2

A1

A16

BYTE#

Vss

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

Vcc

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

Vss

CE#

A0

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

3

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

Address Range (in hexadecimal)

Sector A19 A18 A17 A16 A15 A14 A13 A12

Sector Size

(Kbytes/

Kwords)

Byte mode (x8) Word Mode (x16)

SA0 0 0 0 0 0 X X X 62/32 000000–00FFFF 00000–07FFF

SA1 0 0 0 0 1 X X X 64/32 010000–01FFFF 08000–0FFFF

SA2 0 0 0 1 0 X X X 64/32 020000–02FFFF 10000–17FFF

SA3 0 0 0 1 1 X X X 64/32 030000–03FFFF 18000–1FFFF

SA4 0 0 1 0 0 X X X 64/32 040000–04FFFF 20000–27FFF

SA5 0 0 1 0 1 X X X 64/32 050000–05FFFF 28000–2FFFF

SA6 0 0 1 1 0 X X X 64/32 060000–06FFFF 30000–37FFF

SA7 0 0 1 1 1 X X X 64/32 070000–07FFFF 38000–3FFFF

SA8 0 1 0 0 0 X X X 64/32 080000–08FFFF 40000–47FFF

SA9 0 1 0 0 1 X X X 64/32 090000–09FFFF 48000–4FFFF

SA10 0 1 0 1 0 X X X 64/32

0A0000–

0AFFFF

50000–57FFF

SA11 0 1 0 1 1 X X X 64/32

0B0000–

0BFFFF

58000–5FFFF

SA12 0 1 1 0 0 X X X 64/32

0C0000–

0CFFFF

60000–67FFF

SA13 0 1 1 0 1 X X X 64/32

0D0000–

0DFFFF

68000–6FFFF

SA14 0 1 1 1 0 X X X 64/32

0E0000–

0EFFFF

70000–77FFF

SA15 0 1 1 1 1 X X X 64/32

0F0000–

0FFFFF

78000–7FFFF

SA16 1 0 0 0 0 X X X 64/32 100000–10FFFF 80000–87FFF

SA17 1 0 0 0 1 X X X 64/32 110000–11FFFF 88000–8FFFF

SA18 1 0 0 1 0 X X X 64/32 120000–12FFFF 90000–97FFF

SA19 1 0 0 1 1 X X X 64/32 130000–13FFFF 98000–9FFFF

SA20 1 0 1 0 0 X X X 64/32 140000–14FFFF A0000–A7FFF

SA21 1 0 1 0 1 X X X 64/32 150000–15FFFF A8000–AFFFF

SA22 1 0 1 1 0 X X X 64/32 160000–16FFFF B0000–B7FFF

SA23 1 0 1 1 1 X X X 64/32 170000–17FFFF B8000–BFFFF

SA24 1 1 0 0 0 X X X 64/32 180000–18FFFF C0000–C7FFF

SA25 1 1 0 0 1 X X X 64/32 190000–19FFFF C8000–CFFFF

SA26 1 1 0 1 0 X X X 64/32

1A0000–

1AFFFF

D0000–D7FFF

SA27 1 1 0 1 1 X X X 64/32

1B0000–

1BFFFF

D8000–DFFFF

SA28 1 1 1 0 0 X X X 64/32

1C0000–

1CFFFF

E0000–E7FFF

SA29 1 1 1 0 1 X X X 64/32

1D0000–

1DFFFF

E8000–EFFFF

SA30 1 1 1 1 0 X X X 64/32

1E0000–

1EFFFF

F0000–F7FFF

SA31 1 1 1 1 1 0 X X 32/16 1F0000–1F7FFF F8000–FBFFF

SA32 1 1 1 1 1 1 0 0 8/4 1F8000–1F9FFF FC000–FCFFF

SA33 1 1 1 1 1 1 0 1 8/4

1FA000–

1FBFFF

FD000–FDFFF

SA34 1 1 1 1 1 1 1 X 16/8

1FC000–

1FFFFF

FE000–FFFFF

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

4

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

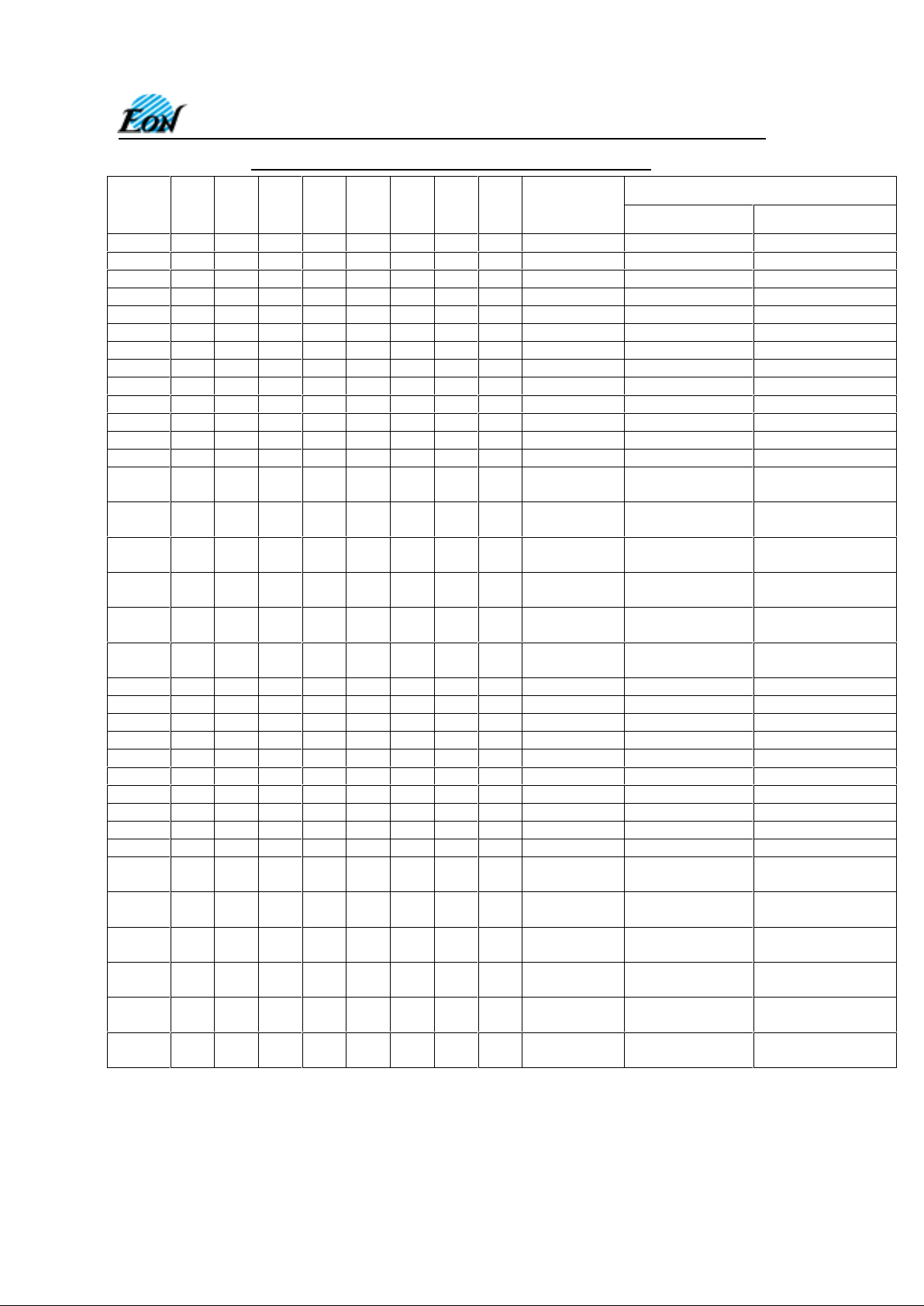

Table 3. Sector Address Tables (EN29LV160J)

Address Range (in hexadecimal)

Sector A19 A18 A17 A16 A15 A14 A13 A12

Sector Size

(Kbytes/

Kwords)

Byte mode (x8) Word Mode (x16)

SA0 0 0 0 0 0 0 0 X 16/8 000000–003FFF 00000–01FFF

SA1 0 0 0 0 0 0 1 0 8/4 004000–005FFF 02000–02FFF

SA2 0 0 0 0 0 0 1 1 8/4 006000–007FFF 03000–03FFF

SA3 0 0 0 0 0 1 X X 32/16 008000–00FFFF 04000–07FFF

SA4 0 0 0 0 1 X X X 64/32 010000–01FFFF 08000–0FFFF

SA5 0 0 0 1 0 X X X 64/32 020000–02FFFF 10000–17FFF

SA6 0 0 0 1 1 X X X 64/32 030000–03FFFF 18000–1FFFF

SA7 0 0 1 0 0 X X X 64/32 040000–04FFFF 20000–27FFF

SA8 0 0 1 0 1 X X X 64/32 050000–05FFFF 28000–2FFFF

SA9 0 0 1 1 0 X X X 64/32 060000–06FFFF 30000–37FFF

SA10 0 0 1 1 1 X X X 64/32 070000–07FFFF 38000–3FFFF

SA11 0 1 0 0 0 X X X 64/32 080000–08FFFF 40000–47FFF

SA12 0 1 0 0 1 X X X 64/32 090000–09FFFF 48000–4FFFF

SA13 0 1 0 1 0 X X X

64/32

0A0000–

0AFFFF

50000–57FFF

SA14 0 1 0 1 1 X X X

64/32

0B0000–

0BFFFF 58000–5FFFF

SA15 0 1 1 0 0 X X X

64/32

0C0000–

0CFFFF

60000–67FFF

SA16 0 1 1 0 1 X X X

64/32

0D0000–

0DFFFF

68000–6FFFF

SA17 0 1 1 1 0 X X X

64/32

0E0000–

0EFFFF

70000–77FFF

SA18 0 1 1 1 1 X X X

64/32

0F0000–

0FFFFF

78000–7FFFF

SA19 1 0 0 0 0 X X X 64/32 100000–10FFFF 80000–87FFF

SA20 1 0 0 0 1 X X X 64/32 110000–11FFFF 88000–8FFFF

SA21 1 0 0 1 0 X X X 64/32 120000–12FFFF 90000–97FFF

SA22 1 0 0 1 1 X X X 64/32 130000–13FFFF 98000–9FFFF

SA23 1 0 1 0 0 X X X 64/32 140000–14FFFF A0000–A7FFF

SA24 1 0 1 0 1 X X X 64/32 150000–15FFFF A8000–AFFFF

SA25 1 0 1 1 0 X X X 64/32 160000–16FFFF B0000–B7FFF

SA26 1 0 1 1 1 X X X 64/32 170000–17FFFF B8000–BFFFF

SA27 1 1 0 0 0 X X X 64/32 180000–18FFFF C0000–C7FFF

SA28 1 1 0 0 1 X X X 64/32 190000–19FFFF C8000–CFFFF

SA29 1 1 0 1 0 X X X

64/32

1A0000–

1AFFFF

D0000–D7FFF

SA30 1 1 0 1 1 X X X

64/32

1B0000–

1BFFFF

D8000–DFFFF

SA31 1 1 1 0 0 X X X

64/32

1C0000–

1CFFFF

E0000–E7FFF

SA32 1 1 1 0 1 X X X

64/32

1D0000–

1DFFFF

E8000–EFFFF

SA33 1 1 1 1 0 X X X

64/32

1E0000–

1EFFFF

F0000–F7FFF

SA34 1 1 1 1 1 X X X

64/32

1F0000–

1FFFFF

F8000–FFFFF

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

5

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

6

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

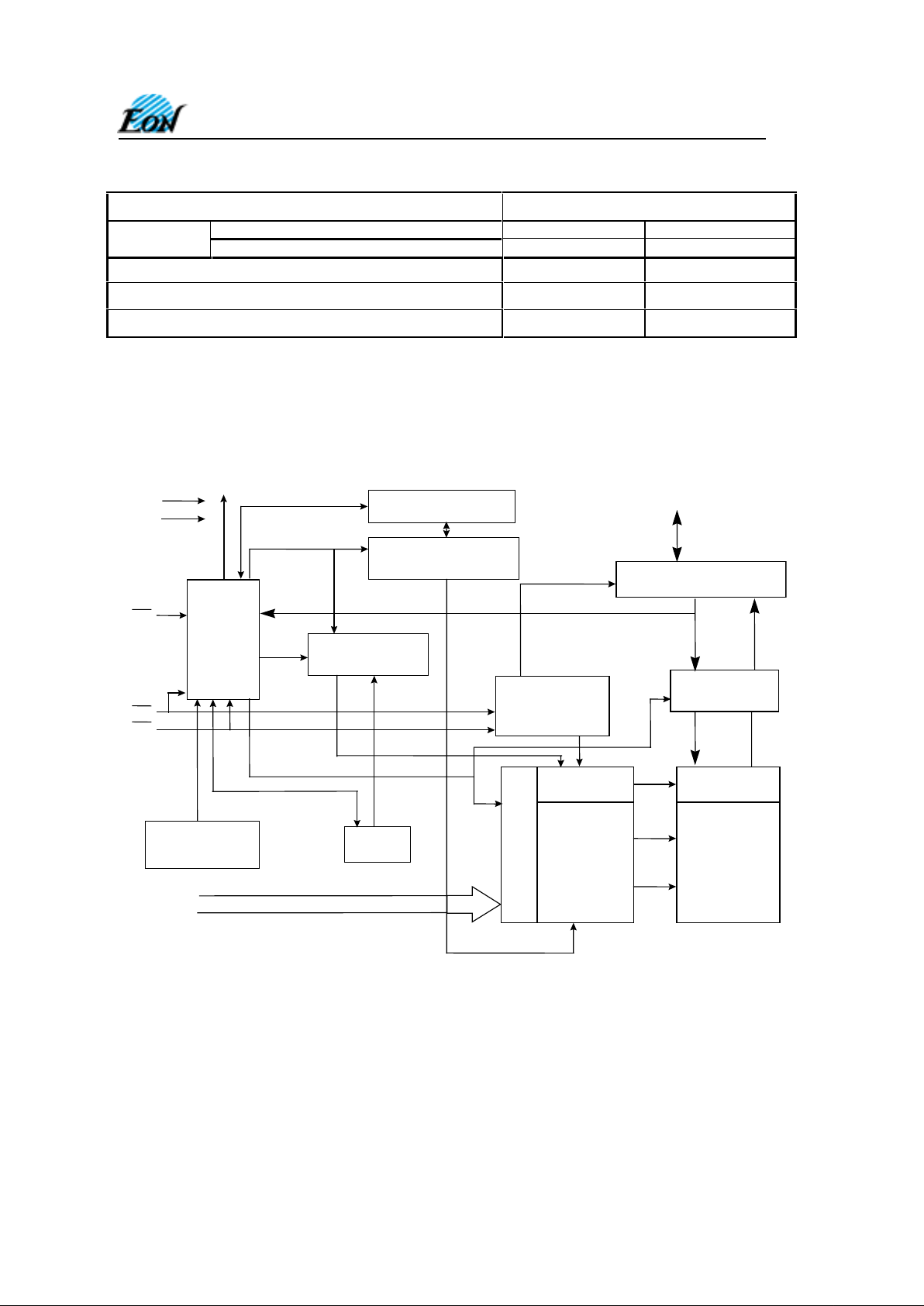

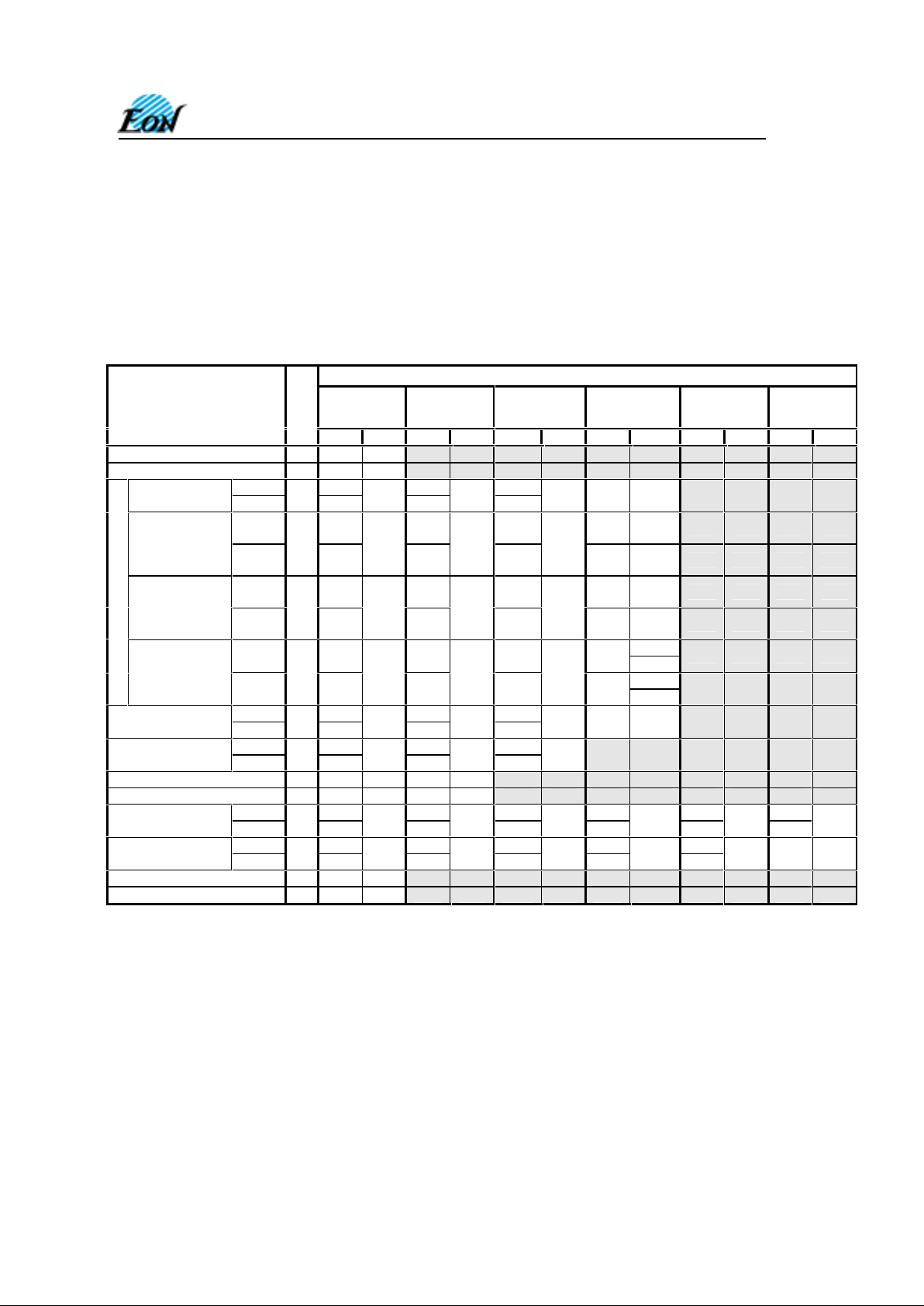

PRODUCT SELECTOR GUIDE

Product Number EN29LV160J

Regulated Voltage Range: Vcc=3.0 – 3.6 V

-70 -

Speed Option

Full Voltage Range: Vcc=2.7 – 3.6 V

- -90

Max Access Time, ns (t

acc

) 70 90

Max CE# Access, ns (tce) 70 90

Max OE# Access, ns (toe) 30 35

BLOCK DIAGRAM

WE

CE

OE

State

Control

Command

Register

Erase Voltage Generator

Input/Output Buffers

Program Voltage

Generator

Chip Enable

Output Enable

Logic

Data Latch

Y-Decoder

X-Decoder

Y-Gating

Cell Matrix

Timer Vcc Detector

A0-A18

Vcc

Vss

DQ0-DQ15 (A-1)

Address Latch

Block Protect Switches

STB

STB

RY/BY

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

7

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

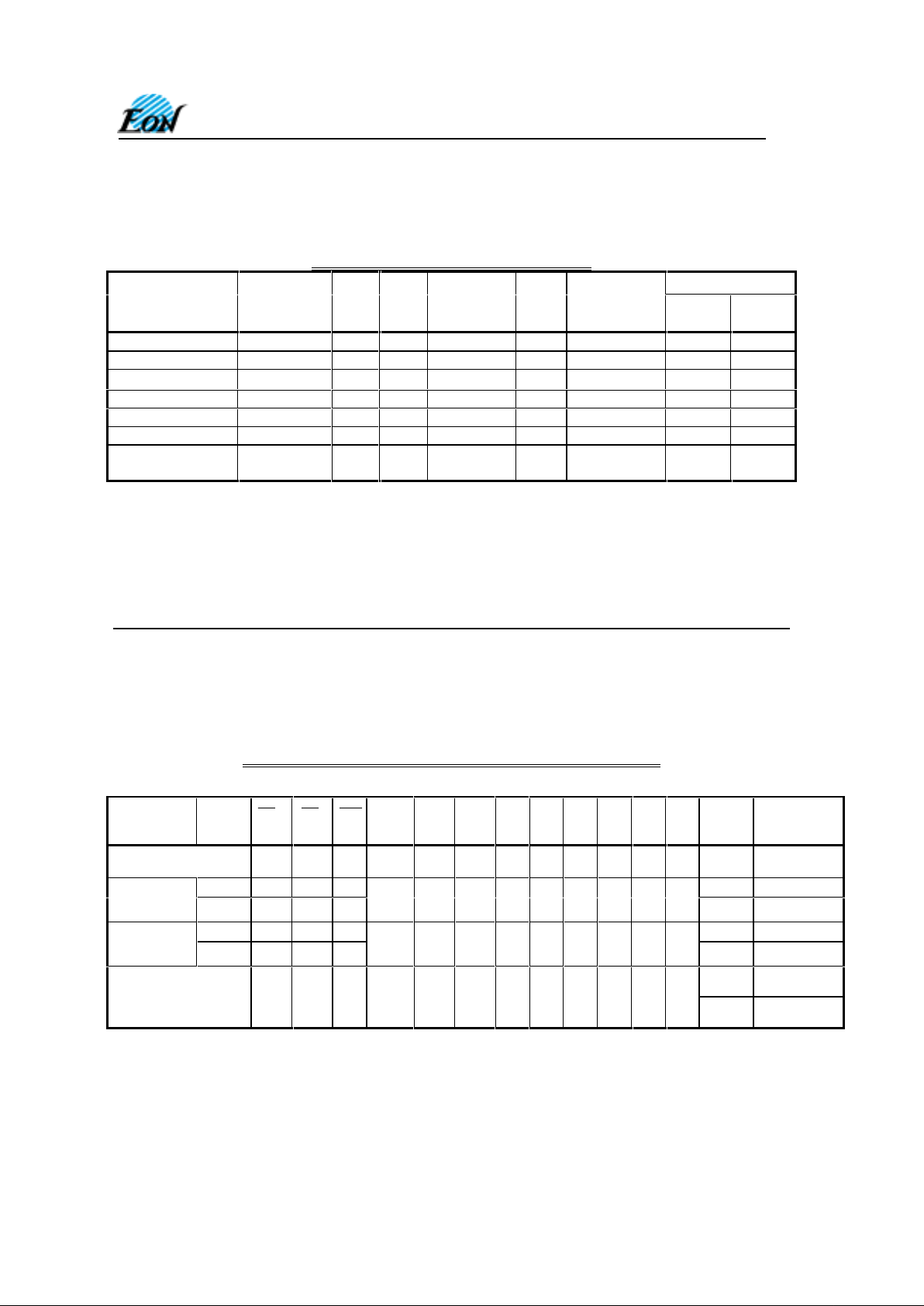

TABLE 3. OPERATING MODES

16M FLASH USER MODE TABLE

DQ8-DQ15

Operation CE# OE#

WE

# Reset#

A0A18 DQ0-DQ7

Byte#

= V

IH

Byte#

= VIL

Read L L H H AIN D

OUT

D

OUT

High-Z

Write L H L H AIN DIN D

IN

High-Z

CMOS Standby

V

cc

± 0.3V

X X

Vcc ± 0.3V

X High-Z High-Z High-Z

TTL Standby H X X H X High-Z High-Z High-Z

Output Disable L H H H X High-Z High-Z High-Z

Hardware Reset X X X L X High-Z High-Z High-Z

Temporary

Sector Unprotect X X X V

ID

A

IN

DIN D

IN

X

Notes:

L=logic low= V

IL

, H=Logic High= VIH, VID =11 ± 0.5V, X=Don’t Care (either L or H, but not f l oat i ng!),

D

IN

=Data In, D

OUT

=Data Out, AIN=Address In

TABLE 4. DEVICE IDENTIFICTION (Autoselect Codes)

16M FLASH MANUFACTURER/DEVICE ID TABLE

Note:

1. If a manufacturing ID is read with A 8=L, the chip will output a configuration code 7Fh. A further Manufacturing ID must be

read with A8=H.

2. A9 = VID is for HV A9 Autoselect mode onl y. A9 must be ≤ Vcc (CMOS l ogic level) for Command A utoselect Mode.

Description Mode A19

to

A12

A11

to

A10

A9

2

A8 A7 A6 A5

to

A2

A1 A0 DQ8

to

DQ15

DQ7 to

DQ0

Manufacturer ID:

Eon

L L H X X VID H1 X L X L L X 04H

Word L L H 22h C4H

Device ID

(top boot

block)

Byte L L H

X X VID X X L X L H

X 22C4H

Word L L H 22h 49H

Device ID

(bottom boot

block)

Byte L L H

X X VID X X L X L H

X 2249H

X

01h

(Protected)

Sector Protection

Verification

L L H SA X VID X X L X H L

X

00h

(Unprotected)

OE

CE

WE

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

8

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

USER MODE DEFINITIONS

Word / Byte Configuration

The signal set on the BYTE# Pin controls whether the device data I/O pins DQ15-DQ0 operate in the

byte or word configuration. When the Byte# Pin is set at logic ‘1’, then the device is in word

configuration, DQ15-DQ0 are active and are controlled by CE# and OE#.

On the other hand, if the Byte# Pin is set at logic ‘0’, then the device is in byte configuration, and only

data I/O pins DQ0-DQ7 are active and controlled by CE# and OE#. The data I/O pins DQ8-DQ14

are tri-stated, and the DQ15 pin is used as an input for the LSB (A-1) address function.

Standby Mode

The EN29LV160J has a CMOS-compatible standby mode, which reduces the

current to < 1µA

(typical). It is placed in CMOS-com patible standby when the

CE

pin is at VCC ± 0.5. RESET# and

BYTE# pin must also be at CMOS input levels. The device also has a TTL-compatible standby mode,

which reduces the maxim um V

CC

current to < 1mA. It is placed in TTL-c ompatible standby when the

CE

pin is at VIH. W hen in st andby modes, the outputs are in a high- im pedance state independent of

the

OE

input.

Read Mode

The device is automatically set to reading array data after device power-up. No commands are required to

retrieve data. The device is also ready to read array data after completing an Embedded Program or

Embedded Erase algorithm.

After the device accepts an Erase Suspend command, the device enters the Erase Suspend mode. The

system can read array data using the standard read timings, except that if it reads at an address within

erase-suspended sectors, the device outputs status data. After completing a programming operation in

the Erase Suspend mode, the system may once again read array data with the same exception. See

“Erase Suspend/Erase Resume Commands” for more additional information.

The system

must issue the reset command to re-enable the device for reading array data if DQ5 goes

high, or while in the autoselect mode. See the “Reset Command” additional details.

Output Disable Mode

When the

CE

or OE pin is at a logic high level (VIH), the output from the EN29LV160J is dis abled.

The output pins are placed in a high impedance state.

Auto Select Identification Mode

The autoselect mode provides manufacturer and device identification, and sector protection

verification, through identifier codes output on DQ15–DQ0. This mode is primarily intended for

programming equipment to automatically match a device to be programmed with its corresponding

programming algorithm. However, the autoselect codes can also be accessed in-system through the

command register.

When using programming equipment, the autoselect mode requires V

ID

(10.5 V to 11.5 V) on

address pin A9. Address pins A6, A1, and A0 must be as shown in Autoselect Codes table. In

addition, when verifying sector protection, the sector address must appear on the appropriate highest

order address bits. Refer to the corresponding Sector Address Tables. The Command Definitions

table shows the remaining address bits that are don’t-care. When all necessary bits have been set as

required, the programming equipment may then read the corresponding identifier code on DQ15–

DQ0.

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

9

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

To access the autoselect codes in-system; the host system can issue the autoselect command via

the command register, as shown in the Command Definitions table. This method does not require

V

ID

. See “Command Definitions” for details on using the autoselect mode.

Write Mode

Programming is a four-bus-cycle operation. The program command sequence is initiated by writing two

unlock write cycles, followed by the program set-up command. The program address and data are written

next, which in turn initiate the Embedded Program algorithm. The system is

not required to provide further

controls or timings. The device automatically provides internally generated program pulses and verifies

the programmed cell margin. The Command Definitions in Table 5 show the address and data

requirements for the byte program command sequence.

When the Embedded Program algorithm is complete, the device then returns to reading array data and

addresses are no longer latched. The system can determine the status of the program operation by using

DQ7 or DQ6. See “Write Operation Status” for information on these status bits.

Any commands written to the device during the Embedded Program Algorithm are ignored.

Programming is allowed in any sequence and across sector boundaries. A bit cannot be programmed

from a “0” back to a “1”. Attempting to do so may halt the operation and set DQ5 to “1”, or cause the

Data# Polling algorithm to indicate the operation was successful. However, a succeeding read will show

that the data is still “0”. Only erase operations can convert a “0” to a “1”.

Sector Protection/Unprotection

The hardware sector protection feature disables both program and erase operations in any sector. The

hardware sector unprotection feature re-enables both program and erase operations in previously

protected sectors.

There are two m ethods to enabling this hardware protection circ uitry. The first one requires

only that the RESET# pin be at V

ID

and then standard microproces s or timings can be used to enable

or disable this feature. See Flowchart 7a and 7b for the algorithm and Figure 12 for the timings.

When doing Sector Unprotect, all the other sectors should be protected first.

The second method is meant for programming equipment. This method requires V

ID

be

applied to both OE# and A9 pin and non- standard m icroproces sor tim ings are used. T his m ethod is

described in a separate document called EN29LV160J Supplement,

which can be obtained by

contacting a representative of Eon Silicon Devices, Inc.

Temporary Sector Unprotect

This feature allows temporary unprotection of previously protected

sector groups to change data while in-system. The Sector Unprotect

mode is activated by setting the RESET# pin to V

ID

. During this mode,

formerly protected sectors can be programmed or erased by simply

selecting the sector addresses. Once is removed from the RESET#

pin, all the previously protected sectors are protected again. See

accompanying figure and timing diagrams for more details.

COMMON FLASH MEMORY

INTERFACE

(CFI)

The common flash interface (CFI)

specification outlines device and host s ystems

software interrogation handshake, which

allows specific vendor-specified software

algorithms to be used for entire families of

devices. Software support can then be

Start

Reset#=VID (note 1)

Perform Erase or Program

Operations

Reset#=VIH

Temporary Sector

Unprotect Completed

(note 2)

Notes:

1. All protected sectors unprotected.

2. Previously protected sectors protected

again.

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

10

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

device-independent, JEDEC ID-independent,

and forward- and backward-c om patible for the

specified flash devic e families. Flash vendirs

can standardize their existing interfaces for

long-term compatibility.

This device enters the CFI Query mode when

the system writes the CFI Query command,

98h, to address 55h in word mode (or addres s

AAh in byte mode), any time the device is

ready to read array data.

The system can read CFI information at the

addresses given in Tables 5-8. In word mode,

the upper address bits (A7–MSB) m ust be all

zeros. To terminate reading CFI data, the

system must write the reset command.

The system can also write the CFI query

command when the device is in the autos elec t

mode. The device enters the CFI query mode

and the system can read CFI data at the

addresses given in Tables 5–8. The system

must write the reset command to return the

device to the autoselect mode.

Table 5. CFI Query Identification String

Adresses

(Word Mode)

Adresses

(Byte Mode) Data Description

10h

11h

12h

20h

22h

24h

0051h

0052h

0059h

Query Unique ASCII string “QRY”

13h

14h

26h

28h

0002h

0000h

Primary OEM Command Set

15h

16h

2Ah

2Ch

0040h

0000h

Address for Primary Extended Table

17h

18h

2Eh

30h

0000h

0000h

Alternate OEM Command set (00h = none exists)

19h

1Ah

32h

34h

0000h

0000h

Address for Alternate OEM Extended Table (00h = none exists

Table 6. System Interface String

Addresses

(Word Mode)

Addresses

(Byte Mode) Data Description

1Bh 36h 0027h Vcc Min (write/erase)

D7-D4: volt, D3 –D0: 100 millivolt

1Ch 38h 0036h Vcc Max (write/erase)

D7-D4: volt, D3 –D0: 100 millivolt

1Dh 3Ah 0000h Vpp Min. voltage (00h = no Vpp pin present)

1Eh 3Ch 0000h Vpp Max. voltage (00h = no Vpp pin present)

1Fh 3Eh 0004h

Typical timeout per single byte/word write 2^N µs

20h 40h 0000h

Typical timeout for Min, size buffer write 2^N µs (00h = not

supported)

21h 42h 000Ah Typical timeout per individual block erase 2^N ms

22h 44h 0000h Typical timeout for full chip erase 2^N ms (00h = not supported)

23h 46h 0005h Max. timeout for byte/word write 2^N times typical

24h 48h 0000h Max. timeout for buffer write 2^N times typical

25h 4Ah 0004h Max. timeout per individual block erase 2^N times typical

26h 4Ch 0000h Max timeout for full chip erase 2^N times typical (00h = not

supported)

Table 7. Device Geometry Definition

Addresses

(Word mode)

Addresses

(Byte Mode) Data Description

27h 4Eh 0015h Device Size = 2^N byte

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

11

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

28h

29h

50h

52h

0002h

0000h

Flash Device Interface description (refer to CFI publication 100)

2Ah

2Bh

54h

56h

0000h

0000h

Max. number of byte in multi-byte write = 2^N

(00h = not supported)

2Ch 58h 0004h Number of Erase Block Regions within device

2Dh

2Eh

2Fh

30h

5Ah

5Ch

5Eh

60h

0000h

0000h

0040h

0000h

Erase Block Region 1 Information

(refer to the CFI specification of CFI publication 100)

31h

32h

33h

34h

62h

64h

66h

68h

0001h

0000h

0020h

0000h

Erase Block Region 2 Information

35h

36h

37h

38h

6Ah

6Ch

6Eh

70h

0000h

0000h

0080h

0000h

Erase Block Region 3 Information

39h

3Ah

3Bh

3Ch

72h

74h

76h

78h

001Eh

0000h

0000h

0001h

Erase Block Region 4 Information

Table 8. Primary Vendor-specific Extended Query

Adresses

(Word Mode)

Addresses

(Byte Mode) Data Description

40h

41h

42h

80h

82h

84h

0050h

0052h

0049h

Query-unique ASCII string “PRI”

43h 86h 0031h Major version number, ASCII

44h 88h 0030h Minor version number, ASCII

45h 8Ah 0000h

Address Sensitive Unlock

0 = Required, 1 = Not Required

46h 8Ch 0002h

Erase Suspend

0 = Not Supported, 1 = To Read Only, 2 = To Read & Write

47h 8Eh 0001h

Sector Protect

0 = Not Supported, X = Number of sectors in per group

48h 90h 0001h

Sector Temporary Unprotect

00 = Not Supported, 01 = Supported

49h 92h 0004h

Sector Protect/Unprotect scheme

01 = 29F040 mode, 02 = 29F016 mode,

03 = 29F400 mode, 04 = 29LV800A mode

4Ah 94h 0000h

Simultaneous Operation

00 = Not Supported, 01 = Supported

4Bh 96h 0000h

Burst Mode Type

00 = Not Supported, 01 = Supported

4Ch 98h 0000h

Page Mode Type

00 = Not Supported, 01 = 4 Word Page, 02 = 8 Word Page

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

12

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

Hardware Data protection

The command sequence requirement of unlock cycles for programming or erasing provides data

protection against inadvertent writes as seen in the Command Definitions table. Additionally, the

following hardware data protection measures prevent accidental erasure or programming, which might

otherwise be caused by false system level signals during Vcc power up and power down transitions, or

from system noise.

Low VCC Write Inhibit

When Vcc is less than V

LKO

, the device does not accept any write cycles. This protects data during Vcc

power up and power down. The command register and all internal program/erase circuits are disabled,

and the device resets. Subsequent writes are ignored until Vcc is greater than V

LKO

. The system must

provide the proper signals to the control pins to prevent unintentional writes when Vcc is greater than

V

LKO

.

Write Pulse “Glitch” protection

Noise pulses of less than 5 ns (typical) on

OE

, CE or

WE

do not initiate a write cycle.

Logical Inhibit

Write cycles are inhibited by holding any one of

OE

= VIL, CE = VIH, or

WE

= VIH

. To initiate a write

cycle,

CE

and WE

must be a logical zero while

OE

is a logical one. If CE,

WE

, and OE are all

logical zero (not recommended usage), it will be considered a read.

Power-up Write Inhibit

During power-up, the device automatically resets to READ mode and loc ks out write cycles. Even

with

CE

= VIL, WE = VIL and OE = VIH, the device will not accept com mands on the r ising edge of

WE

.

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

13

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

COMMAND DEFINITIONS

The operations of the EN29LV160J are selected by one or more commands written into the

command register to perform Read/Reset Memory, Read ID, Read Sector Protection, Program,

Sector Erase, Chip Erase, Erase Suspend and Er ase Resume. Comm ands are made up of data

sequences written at specific addresses via the command register. The sequences for the

specified operation are defined in the Command Definitions table (Table 5). Incorrect address es,

incorrect data values or improper sequences will reset the device to Read Mode.

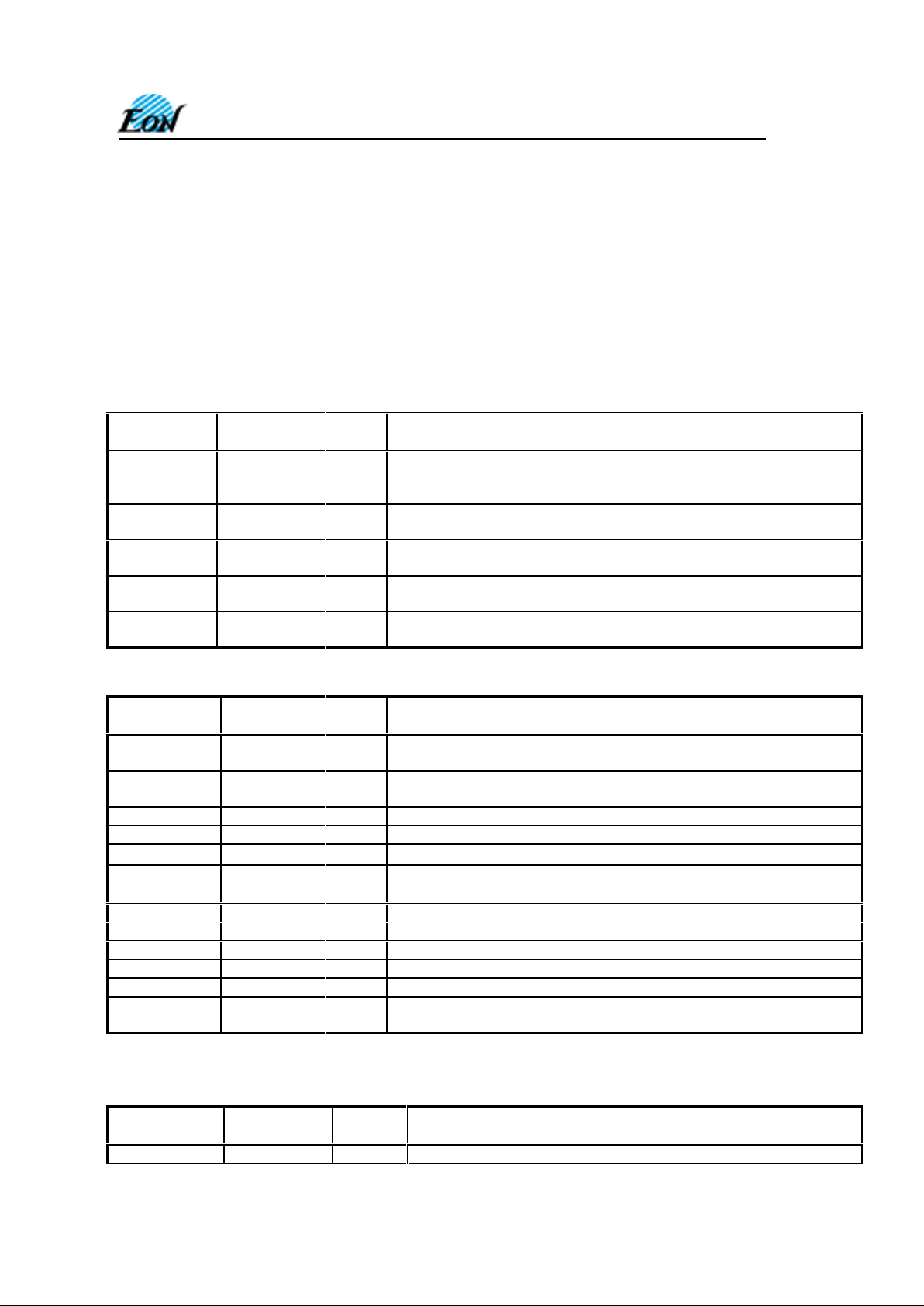

Table 5. EN29LV160J Command Definitions

Bus Cycles

1

st

Write Cycle

2

nd

Write Cycle

3

rd

Write Cycle

4

th

Write Cycle

5

th

Write Cycle

6

th

Write Cycle

Command

Sequence

Cycles

Add Data Add Data Add Data Add Data Add Data Add Data

Read 1 RA RD

Reset 1 xxx F0

Word 555 2AA 555 Manufacturer

ID

Byte

4

AAA

AA

555

55

AAA

90

000/

100

7F/

1C

Word 555 2AA 555

001/

101

7F/

22DA

Device ID

Top Boot

Byte

4

AAA

AA

555

55

AAA

90

002/

102

7F/

DA

Word 555 2AA 555

001/

101

7F/

225B

Device ID

Bottom Boot

Byte

4

AAA

AA

555

55

AAA

90

002/

102

7F/

5B

XX00

Word 555

2AA

555

(SA)

X02

XX01

00

Autoselect

Sector Protect

Verify

Byte

4

AAA

AA

555

55

AAA

90

(SA)

X04

01

Word 555 2AA 555

Program

Byte

4

AAA

AA

555

55

AAA

A0 PA PD

Word 555 2AA 555

Unlock Bypass

Byte

3

AAA

AA

555

55

AAA

20

Unlock Bypass Program 2 XXX A0 PA PD

Unlock Bypass Res et 2 XXX 90 XXX 00

Word 555 2AA 555 555 2AA 555

Chip Erase

Byte

6

AAA

AA

555

55

AAA

80

AAA

AA

555

55

AAA

10

Word 555 2AA 555 555 2AA

Sector Erase

Byte

6

AAA

AA

555

55

AAA

80

AAA

AA

555

55 SA 30

Erase Suspend 1 xxx B0

Erase Resume 1 xxx 30

Address and Data values indicat ed i n hex

RA = Read Address: address of the memory location to be read. Thi s is a read cycle.

RD = Read Data: data read from locat i on RA duri ng Read operation. This is a read cycle.

PA = Program Address: address of the memory location to be programmed. X = Don’t-Care

PD = Program Data: data to be programmed at location PA

SA = Sector Address: address of the Sector to be erased or verif i ed. Address bits A18-A12 uniquely select any Sector.

Reading Array Data

The device is automatically set to reading array data after power up. No commands are required to

retrieve data. The device is also ready to read array data after completing an Embedded Program or

Embedded Erase algorithm.

Following an Erase Suspend command, Erase Suspend mode is entered. The system can read array data

using the standard read timings, with the only difference in that if it reads at an address within erase

4800 Great America Parkway, Suite 202 Tel: 408-235-8680

Santa Clara, CA 95054 Fax: 408-235-8685

14

EN29LV160J

Rev 0.3 Release Date: 2002/01/30

suspended sectors, the device outputs status data. After completing a programming operation in the Erase

Suspend mode, the system may once again read array data with the same exception.

The Reset command must be issued to re-enable the device for reading array data if DQ5 goes high, or while

in the autoselect mode. See next section for details on Reset.

Reset Command

Writing the reset command to the device resets the device to reading array data. Address bits are don’tcare for this command.

The reset command may be written between the sequence cycles in an erase command sequence before

erasing begins. This resets the device to reading array data. Once erasure begins, however, the device

ignores reset commands until the operation is complete. The reset command may be written between the

sequence cycles in a program command sequence before programming begins. This resets the device to

reading array data (also applies to programming in Erase Suspend mode). Once programming begins,

however, the device ignores reset commands until the operation is complete.

The reset command may be written between the sequence cycles in an autoselect command sequence.

Once in the autoselect mode, the reset command

must be written to return to reading array data (also

applies to autoselect during Erase Suspend).

If DQ5 goes high during a program or erase operation, writing the reset command returns the device to

reading array data (also applies during Erase Suspend).

Autoselect Command Sequence

The autoselect command sequence allows the host system to access the manufacturer and devices

codes, and determine whether or not a sector is protected. The Command Definitions table shows the

address and data requirements. This is an alternative to the method that requires V

ID

on address bit A9

and is intended for PROM programmers.

Two unlock cycles followed by the autoselect command initiate the autoselect command sequence.

Autoselect mode is then entered and the system may read at addresses shown in Table 4 any number of

times, without needing another command sequence.

The system must write the reset command to exit the autoselect mode and return to reading array data.

Word / Byte Programming Command

The device may be programmed by byte or by word, depending on the state of the Byte# Pin.

Programming the EN29LV160J is performed by using a four bus-cycle operation (two unlock write

cycles followed by the Program Setup command and Program Data Write cycle). When the program

command is executed, no additional CPU controls or timings are necessary. An internal timer

terminates the program operation automatically. Address is latched on the falling edge of

CE

or

WE

, whichever is last; data is latched on the rising edge of CE or

WE

, whichever is first.

Programming status may be checked by sampling data on DQ7 (

DATA

polling) or on DQ6 (toggle

bit). ). When the program operation is successfully completed, the device returns to read mode and

the user can read the data programmed to the device at that address. Note that data can not be

programmed from a 0 to a 1. Only an erase operation can change a data from 0 to 1. When

programming time limit is exceeded, DQ5 will produce a logical “1” and a Reset command can return

the device to Read mode.

Unlock Bypass

To speed up programming operation, the Unlock Bypass Command may be used. Once this feature

is activated, the shorter two cycle Unlock Bypass Program command can be used instead of the

Loading...

Loading...