Page 1

Inside SQ80 – a technical description

Rainer Buchty

eMail: rainer@buchty.net

http://www.buchty.net

September 29, 1999

Page 2

Page 3

Abstract

Since Ensoniq refuses to give any technical information about the SQ80

Cross Wave Synthesizer someone had to do the job... I hope this documentation will help the electronically skilled to repair and/or improve their

beloved machine. At least it will give some deeper understanding of what’s

going on inside.

Page 4

Contents

1 Introduction 5

1.1 What is the (E)SQ family of synthesizers all about? . . . . . 6

1.2 Synthesis Parameters . . . . . . . . . . . . . . . . . . . . . . . 6

1.3 The sequencer . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.4 Multitimbrality - I need more voices! . . . . . . . . . . . . . . 8

2 Technical Documentation 11

2.1 System Overview . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.2 The one which drives it all: MC6809E . . . . . . . . . . . . . 13

2.3 Let there be sound: DOC5503 and CEM3379 . . . . . . . . . 14

2.4 The art of disk storage . . . . . . . . . . . . . . . . . . . . . . 15

2.4.1 Track Layout . . . . . . . . . . . . . . . . . . . . . . . 15

2.4.2 Disk Directory Structure . . . . . . . . . . . . . . . . . 16

2.4.3 Sequencer Memory Dumps . . . . . . . . . . . . . . . 16

2.4.4 Bank Files . . . . . . . . . . . . . . . . . . . . . . . . 17

2.4.5 Program Files . . . . . . . . . . . . . . . . . . . . . . . 17

2.5 What comes in, must come out - the I/O subsystem . . . . . 19

2.6 The system software . . . . . . . . . . . . . . . . . . . . . . . 20

2.6.1 OSRAM . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.6.2 Cartridge . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.6.3 Hidden Functions . . . . . . . . . . . . . . . . . . . . . 20

3 Troubleshooting 23

3.1 General problems . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2 MIDI mysteries . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.3 Keyboard Trouble . . . . . . . . . . . . . . . . . . . . . . . . 25

3.4 Storage Hassles . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.5 Panel Problems . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.6 Flaky Tape . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

A Parts List 27

B Schematics 29

2

Page 5

CONTENTS 3

C Datasheets 39

C.1 WD1770/1772 Floppy Disk Controller / Formatter . . . . . . 41

C.1.1 Description . . . . . . . . . . . . . . . . . . . . . . . . 41

C.1.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . 41

C.1.3 Processor Interface . . . . . . . . . . . . . . . . . . . . 43

C.1.4 General Disk Read Operation . . . . . . . . . . . . . . 45

C.1.5 General Disk Write Operation . . . . . . . . . . . . . 45

C.1.6 Command Description . . . . . . . . . . . . . . . . . . 46

C.1.7 Type 1 Commands . . . . . . . . . . . . . . . . . . . . 48

C.1.8 Type 2 Commands . . . . . . . . . . . . . . . . . . . . 50

C.1.9 Type 3 Commands . . . . . . . . . . . . . . . . . . . . 52

C.1.10 Type 4 Commands . . . . . . . . . . . . . . . . . . . . 54

C.1.11 Status Register . . . . . . . . . . . . . . . . . . . . . . 55

C.1.12 Recommended Layout for 128-Byte Sectors . . . . . . 56

C.1.13 Recommended Layout for 256-Byte Sectors . . . . . . 57

C.1.14 Generic (non-standard) formats . . . . . . . . . . . . . 58

C.2 SSM2300 Octal Sample&Hold . . . . . . . . . . . . . . . . . . 61

C.3 MC/SN 2681 DUART . . . . . . . . . . . . . . . . . . . . . . 63

C.4 CEM3360 Dual VCA . . . . . . . . . . . . . . . . . . . . . . . 89

C.5 CEM3379 Analog Signal Processor . . . . . . . . . . . . . . . 93

C.6 Ensoniq DOC5503 . . . . . . . . . . . . . . . . . . . . . . . . 103

C.6.1 Common Registers . . . . . . . . . . . . . . . . . . . . 103

C.6.2 DOC registers for individual Oscillators . . . . . . . . 103

C.6.3 Wavetable Address Generation . . . . . . . . . . . . . 106

C.6.4 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

C.7 MC/HD 68B09E CPU . . . . . . . . . . . . . . . . . . . . . . 109

C.8 AD7524 Analog/Digital Converter . . . . . . . . . . . . . . . 145

Page 6

4 CONTENTS

Page 7

Chapter 1

Introduction

The SQ80 was released at the beginning of 1988 (at least here Europe) and

was one of the first so-called workstations. It not only was a synthesizer

but also came along with a 8-track sequencer. Obviously, it also featured

multi-timbrality and dynamic voice allocation which was quite a novum.

And as one of the first synthesizers it was equipped with a 3.5” disk drive

- no need for expensive sound cartridges or excessive bulk dump sessions

anymore.

What also made the (E)SQ family of synthesizers a success was the

easy-to-use user interface. Unlike most synthesizers of that time where

one had to select a parameter by number (!) and editing that one again

by number (sometimes even in hexadecimal) the SQ80 came (as its little

brother the ESQ-1) with a big alpha-numeric display and a load of buttons

each being responsible for a group of functions.

Unfortunately, the early Ensoniq synths and accessories for these such

as the single output expansion unit disappeared completely after the first

TransWave

T M

synthesizer – the VFX – hit the market.

5

Page 8

6 CHAPTER 1. INTRODUCTION

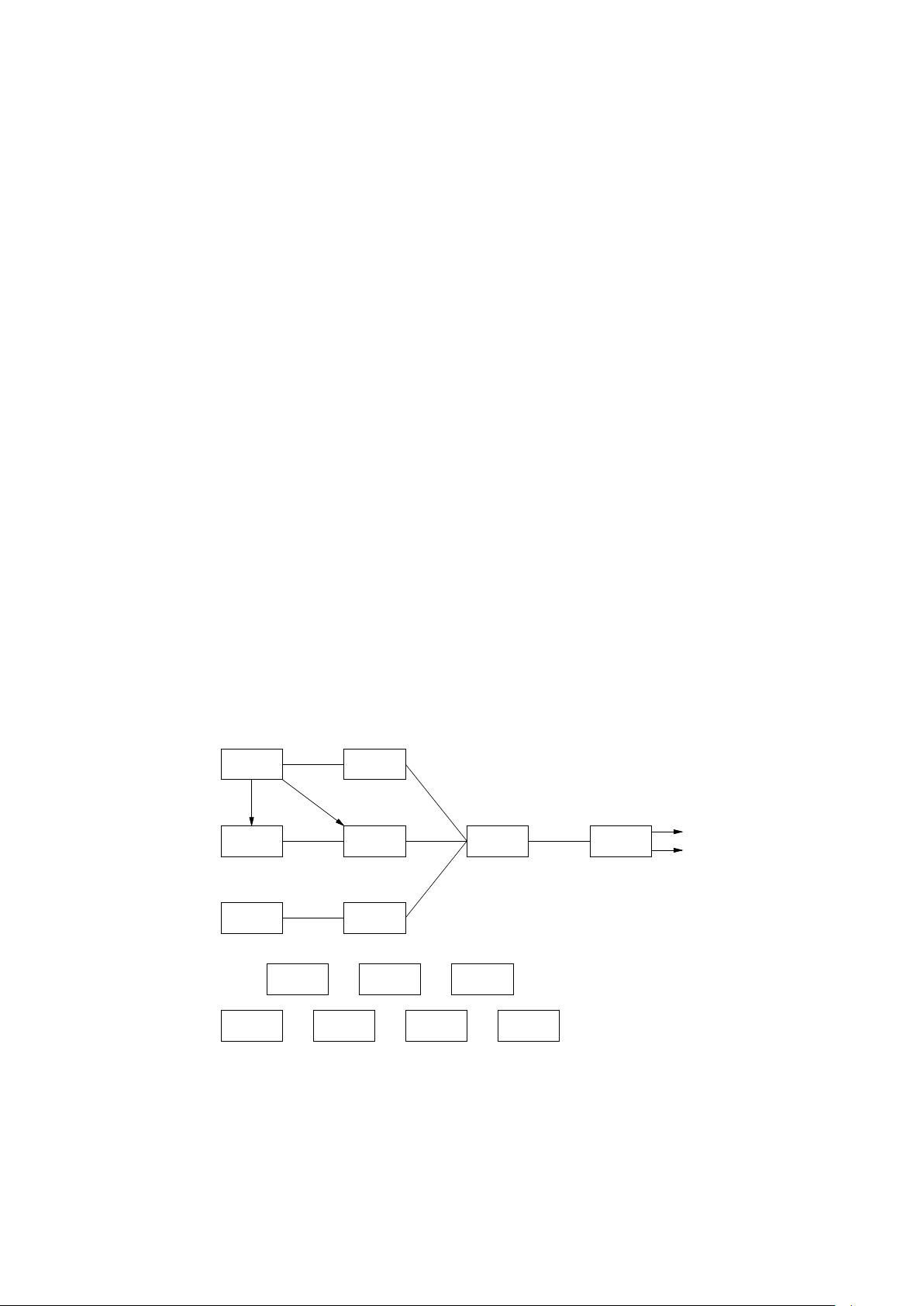

OSC #1

OSC #2

OSC #3

DCA #1

DCA #2

DCA #3

VCF VCA/PAN

LFO #2LFO #1 LFO #3

EG #1 EG #2 EG #3 EG #4

Sync

AM

1.1 What is the (E)SQ family of synthesizers all

about?

The (E)SQ synthesizers aswell as Ensoniq’s first sampler (which was a great

success) are based on the so called DOC chip. This abbreviation stands for

Digital Oscillator Circuit and is the musical heart of all of these machines.

Speaking of the synthesizers we could say that the SQ80 is a superset of the

ESQ-1 offering the following enhancements:

• bigger waveform memory (75 waves including the 32 ESQ-1 waves)

• bigger sequencer memory (64kB by default)

• built-in 3.5” disk drive

• keyboard with polyphonic aftertouch

What makes the (E)SQ synthesizers (even today!) quite interesting is

their great flexibility. They can either sound warm and analog but also cold

and digital. The reason lies in their hybrid nature – digital oscillators but

analog sound processing. The factory presets give a rough overview over the

SQ80’s capabilies but to get a real impression of what this machine can do

should get e.g. the Transoniq Hacker patches.

1.2 Synthesis Parameters

Figure 1.1 shows the basic architecture of each voice:

Figure 1.1: Architecture of an SQ80 voice

Page 9

1.2. SYNTHESIS PARAMETERS 7

Unlike modern synthesizers where a single voice mostly consists of an

oscillator plus filters the SQ80 offers 3 oscillators per voice (using 4 oscillators

might have overextended the CPU’s capabilities, I just don’t know) which

gives it a rich base sound. Also pretty nice is that per voice four envelope

generators and three LFOs exist – soundprogrammer’s heaven. Besides, the

SQ80 offers some more features which I will explain as follows:

Gated Mode: Besides some one-shot (not loopable) waveforms the SQ80

offers a special playback mode where an Envelope is only processed

once treating the sustain level as just an ordinary envelope step. This

is nice for producing percussive sounds which don’t need a sustain

phase.

Synchronization: You know that fancy “EEEOOOOW” sounds? It’s the

audible effect of one oscillator synchronizing another. The SQ80 can

produce these, too, since the DOC chip supports oscillator synchronization - unfortunately only between an even/odd pair of oscillators,

that’s why only synchronizing OSC2 by OSC1 is possible.

Amplitude Modulation: Good for making gong sounds or any other

which need disharmonic spectrals. Not quite the same as ring modulation but pretty close.

Oscillator Restart In usual DCO-based synthesizers the oscillator starts

playing back a wave from its very beginning when a key is played.

This is ok for complex waves but results in a static sound when using

short, looped waves such as e.g. SAW. Thinking of analog oscillators

such a reset of the waveform is unnatural (saw oscillators are based

on integrators) - the SQ80 offers both: oscillator reset or free-running

waves. However, this can be only programmed per sound program,

not individual for each oscillator.

LFO Specialties: Instead of a fixed output amplitude the modula-

tion depth of each LFO can be programmed to fade in (or out).

If that’s not enough an assignable modulation depth modulator exists.

Digitally controlled synthesizers tend to offer very static LFOs: As

soon as you hit a key the LFO starts at position 0 of the selected wave

- this is very annoying when using the LFO for e.g. filter sweeps, so

the SQ80’s LFOs can be programmed to be running freely or being

reset by each keystroke. And if you think that digital LFOs sound too

static – switch on the HUMANIZE function!

Envelope Specialties: Not much uncommon here, but for completeness’

sake I’d mention that an envelope generator can be programmed

Page 10

8 CHAPTER 1. INTRODUCTION

to react on key velocity (linear and exponential response) and key

position. What’s really fancy about the envelopes is that the so called

second release which does not really replace a reverb but produces a

similar effect.

Of course the envelopes are not of ADSR-type but a 4 level/rate model.

1.3 The sequencer

Normally, on-board sequencers are a nice add-on but nothing more. Not

the SQ80 built-in sequencer which is really useful. It’s a pattern-oriented

sequencer capable of holding up to 20 songs consisting of up to 60 sequences. What makes it so useful is the fact that you not only have a basic

record/quantize/playback functionality but also the capabilites of track

transpose, sequence editing (add/delete bars) and even single step editing

of track contents. Also it contains a very flexible song editor and locator.

Needless to say that the sequencer not only can be controlled by MIDI but

also synchronized to MIDI clock or Tape Sync.

On the “minus” side there’s only few. Have you ever tried to attach a

new volume level to an existing track after having recorded it? On earlier

software versions this is impossible.

1.4 Multitimbrality - I need more voices!

The SQ80 was one of the first synthesizers offering multitimbrality which

means that one machine was able to play independent sounds on each voice

(to that time we used the term MIDI multi mode capable which is pretty

the same).

Unfortunately, the SQ80 offers only 8 voices which is not much if you

think of complex arrangements. Fortunately, it has a really neat voice

allocation algorithm (much better as the very static one used e.g. in the

Yamaha SY-77) which can be influenced per sound program individually.

Think of natural instruments - if you play the same note twice the

previously played note will be replaced by the following one. The SQ80

can mimic this behaviour – or disregard nature, just as you like. But keep

in mind that the latter one forces a more aggressive voice allocation since

there’s no oscillator to “recycle”.

Lucky people (such as me :-) own more than one SQ80 – and can easily

daisy-chain these by enabling the overflow mode. This means that any note

Page 11

1.4. MULTITIMBRALITY - I NEED MORE VOICES! 9

which an SQ80 can’t play since all oscillators are used will be handed down

the chain to another SQ80 which might have free resources.

Page 12

10 CHAPTER 1. INTRODUCTION

Page 13

Chapter 2

Technical Documentation

I’ve asked Ensoniq three times for the original technical documentation of

the SQ80, here’s what they responded:

1. “The schematics are proprietary and not meant to be given away.”

(This was after my naive(?) first-time asking, but hey, I got the

schematics of my Yamaha equipment aswell - and these are far more

high-tech!)

2. “Your work sounds incredible – but we wish you all the best.” (after

telling them that I started to reverse-engineer the SQ80)

3. “Congratulations on your work!” (when finally telling them that I

succeeded in drawing schematics, documenting the OS and creating

an assembly language source code for further OS development)

With no word they told me that they dislike these efforts, neither they

told me to keep that knowledge for myself. So here it comes...

11

Page 14

12 CHAPTER 2. TECHNICAL DOCUMENTATION

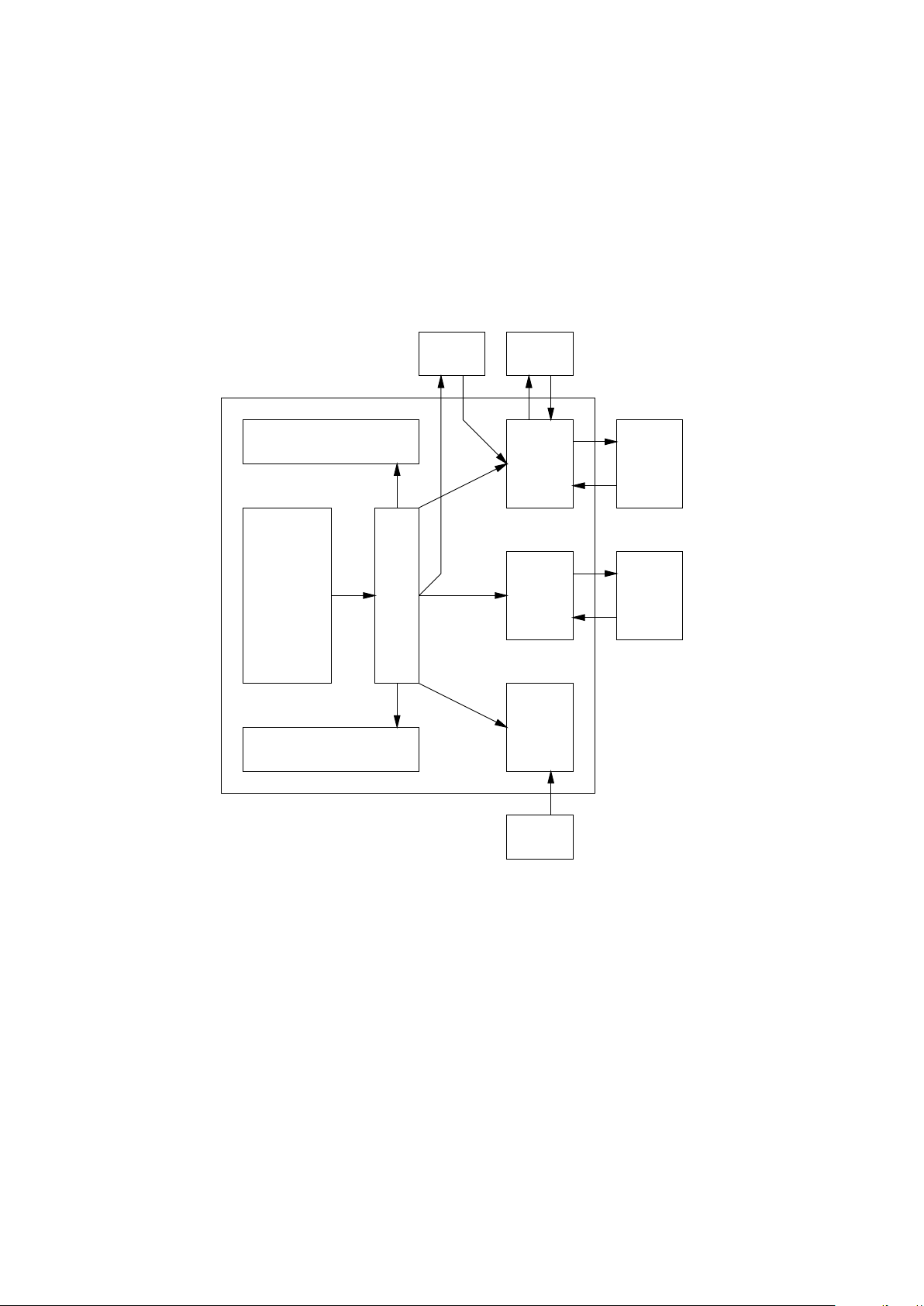

Sequencer Memory

DOS Memory

Operating System

System Memory

CPU

DUART

Cart. MIDI

Keybrd.

&

Displ.

Control

Address Decodier

Floppy

Drive

DOC

FDC

2.1 System Overview

Basically, the SQ80 is nothing more than a microcomputer with some specialized peripherals. Figure 2.1 gives an overview over the system architecture:

Figure 2.1: Anatomy of an SQ80

Mostly computer stuff, the only dedicated “musical” parts are the DOC

and the analog sound processors. This is a big advantage over other, especially modern synthesizers, since you can get replacement parts from the

next distributor of electronic parts.

Page 15

2.2. THE ONE WHICH DRIVES IT ALL: MC6809E 13

2.2 The one which drives it all: MC6809E

The Motorola 6809 was widely used for synthesizers back in the 80’s.

Not only Ensoniq did use it in their (E)SQ synthesizers and the Mirage

samplers, it’s also the heart of e.g. the Oberheim XPander. And even the

DX-7 used some special kind of 6809, the Hitachi 6309 (an improved 6809).

What made the 6809 that attractive was its computing power combined

with a very flexible instruction set. The SQ80 makes heavy use of the 6809’s

specialties:

• loadable system stack pointer S (used for context switching)

• loadable user stack pointer U (used as another 16-bit index register)

• 16-bit index registers X and Y

• 16-bit accumulator D

• fast (integer) multiplication / division

• software interrupts (used for error signalling)

• SYNC and CWAI commands forcing the CPU to wait for an external

interrupt

In the SQ80 the 6809E was used. Unlike the 6809 it’s E–mate could be

completely externally controlled which is needed inside the SQ80 where the

generation of clock signals is influenced by the DOC chip. See p.111 for

details on this processor.

Page 16

14 CHAPTER 2. TECHNICAL DOCUMENTATION

2.3 Let there be sound: DOC5503 and CEM3379

Some of you might know that the creator of the DOC, Bob Yannes, was

also the designer of the all famous SID chip which was the sound engine of

the Commodore 64 home computer. Both are based on the same principle:

phase accumulation. This means that the frequency of a digital voice is

not determined by the playback frequency (clock) as it was used in former

drum computers (and which will drive every today’s studio technician mad

since a variable playback frequency won’t fit very well into digital mastering

using fixed frequencies of 44.1kHz or 96kHz), instead the frequency will

be derived from a counter: This counter – roughly said – counts up the

waveform address. If you need to get higher frequencies you increment the

counter steps, for lower frequencies you decrement them. Thus the name

“phase accumulator” – it’s an accumulator where the resulting address is a

phase pointer.

The DOC uses a 24bit counter for this purpose. The frequencydetermining value will be added to the lower 16 bit whereas the higher

bits are used as the phase pointer (which of them will be used can be

programmed, see 107 for details).

The DOC contains 32 digital oscillators and 32 amplifiers aswell as an

output multiplexer to make it possible to route these 32 oscillators to one

out of 16 channels. The SQ80 makes only use of 24 oscillators/amplifiers

and 8 channels. The uppermost channel mux bit is used for selecting either

Wave ROM 0 or 1.

Now the CEM3379: It was designed by Curtis Electromusic and contains an analog 4pole low-pass filter with adjustable center frequency and

resonance. Furthermore it also contains a dual VCA with adjustable gain

and pan position. Each SQ80 voice contains mainly of one CEM3379, the

DOC’s output is routed to the desired CEM3379 using an ordinary 4051

multiplexer.

Page 17

2.4. THE ART OF DISK STORAGE 15

2.4 The art of disk storage

The SQ80 uses standard 3.5” DD disks for storage of programs, program

banks and sequencer data. As disk controller it uses the Western Digital

WD1772 which was quite common in the 80s, the same chip is used e.g.

inside the Atari ST machines and the Commodore 1581 disk drive.

The disks have a fixed geometry: Although one disk may hold up to

880kB of data it’s not possible to make dynamic use of a disk in a way

of storing e.g. up to 220 program banks or up to 8834 single programs.

Neither it is possible to store more than 10 sequencer files even if they don’t

make use of the entire disk. Instead the fixed disk geometry causes the well

known layout of 10 sequencer/sysex files, 40 program banks and 128 single

programs – which unfortunately most of the time is just wasting disk space.

2.4.1 Track Layout

Some of you might have tested it: It’s almost impossible to copy a SQ80

disk using standard PC drives. This is due to the fact that Ensoniq –

in their eternal wisdom – decided to use a very special disk format. Not

only that they use a fixed disk layout (which is understandable in terms of

complexity: A fixed disk layout is just way easier to program and needs less

administration – on the other hand it wouldn’t have been a big problem to

modify the SQ80 hardware to have additional ROM space which would be

needed for the implementation of a “real” DOS making dynamic use of the

disk space), they also use a special track/sector layout:

• sectors 0 to 4 hold 1024 data bytes each

• sector 5 holds 512 data bytes

The reason why a lot of PC disk controllers fail to read and even

write these disks is the change in sector size inside a track. Whereas the

WD177x family can perform single sector reads and writes older PC floppy

controllers such as the NEC 765 or Intel 8278 based ones can only read and

write a single track. More modern ones like Intel 82077 and newer are at

least able to read and write single sectors – but not format these individually.

Have you ever wondered why the SQ80 won’t format a disk where

your PC formats it without bad sectors? That’s because Ensoniq formats

DD disks to their limit (880kB / 901120 bytes) – which also made the

Commodore Amiga be very sensitive to cheapo disks. (Mean trick: Let the

SQ80 format and complain, then put the disk into your PC and copy disk

images using the SQ80 Toolkit onto it.

Page 18

16 CHAPTER 2. TECHNICAL DOCUMENTATION

2.4.2 Disk Directory Structure

The disk directory consists of two parts: The first part is responsible for

“big files”, namely sequencer memory dumps and sound banks. Thus, it

holds 50 entries of the following structure:

typedef struct directory_entry {

char type;

char name[10];

int size;

} de_t;

Size and type are only vital for sequencer files since they tell, guess

what... File size is measured in bytes, but the file type needs some more

explanation:

/* standard file types */

#define FREE 0 /* unused */

#define OS 1 /* operating system */

#define BNK 2 /* program bank */

#define SNG 3 /* all sequence (song) */

#define SEQ 4 /* one sequence */

#define SYX 5 /* system exclusive */

#define PRG 6 /* single program */

I guess you get it from the above table. The very first entry is used for

unused or deleted file, the second one is not used on the SQ80 and is a

remnant of the good old Mirage times - it’s reserved for bootable system files.

But what about the single program files? It’s definitely not true that

you need to extract the program names from a program files PCB structure

- if that would be the case you’d hear annoying floppy noises each time

you access the DISK/LOAD/PROGRAM menu. Instead, the file names are

listed just behind that 50 “big” entries.

2.4.3 Sequencer Memory Dumps

This kind of files occupies the first and biggest disk partition, you will find

these at the following locations (format: start c/h/s, end c/h/s):

{ 0,0,0, 6,0,3}, /* seqram #1 */

{ 6,0,4,12,1,2}, /* seqram #2 */

{12,0x11,3,19,1,1}, /* seqram #3 */

{19,1,2,25,0,0}, /* seqram #4 */

{25,0x10,1,31,0,4}, /* seqram #5 */

Page 19

2.4. THE ART OF DISK STORAGE 17

{32,0,0,38,0,3}, /* seqram #6 */

{38,0,4,44,1,2}, /* seqram #7 */

{44,0x11,3,51,1,1}, /* seqram #8 */

{57,1,2,57,0,0}, /* seqram #9 */

{57,0x10,1,63,0,4}, /* seqram #10 */

Looks easy? It indeed is - but not as simple as it looks like. Your SQ80

is a lazy guy which changes disk sides only when it’s necessary. This means

a multi-track read goes like this: c/0 – c/1 – c+1/1 – c+1/0 – c+2/0 and

so on. To mark whether the head has changed before or not bit 4 of the

head byte is used - if it is set to 1 it forces a head change together with the

next track change.

But there’s even more: On sector 5 of the end track/side there’s additional information stored such as song names. You’ll see the side effects of

this when discussing the storage of single program files.

2.4.4 Bank Files

Program bank file storage is easy: Each bank occupies 4 long sectors on

disk starting with track 64 and ending with track 79. Banks 1 to 20 will be

stored on side 0, banks 21 to 40 on side 1 of a disk. Each bank consist of

40 single program dumps organized as PCBs.

In the directory structure these files are marked with file type 2 (BNK)

and size 0.

2.4.5 Program Files

Getting a program file’s position on disk is a tricky task. In theory the single

programs reside on the remaining (read: not occupied by the directory)

sectors 5 of a disk – but remember what I said about the sequencer files:

These need another 10 short sectors which leads to the following routine:

geo_t *get_prog_pos(geo_t *prgpos, int pnum) {

switch( ((pnum-1)&64)|(((pnum-1)&63)+2) ) {

case 0x06: prgpos->st=0x42;

prgpos->sh=0; break;

case 0x19: prgpos->st=0x42;

prgpos->sh=1; break;

case 0x1f: prgpos->st=0x43;

prgpos->sh=1; break;

case 0x39: prgpos->st=0x44;

prgpos->sh=0; break;

case 0x3f: prgpos->st=0x44;

Page 20

18 CHAPTER 2. TECHNICAL DOCUMENTATION

prgpos->sh=1; break;

case 0x53: prgpos->st=0x45;

prgpos->sh=1; break;

case 0x6c: prgpos->st=0x46;

prgpos->sh=0; break;

case 0x73: prgpos->st=0x46;

prgpos->sh=1; break;

default: prgpos->st=((pnum-1)&63)+2;

prgpos->sh=((pnum-1)&64)>>6;

break;

}

prgpos->ss=5;

prgpos->et=prgpos->st; prgpos->eh=prgpos->sh; prgpos->es=prgpos->ss;

return prgpos;

}

Needless to say that the storage format – again – is PCB.

Page 21

2.5. WHAT COMES IN, MUST COME OUT - THE I/O SUBSYSTEM19

2.5 What comes in, must come out - the I/O subsystem

Big words for a small chip - but indeed the MC2681 DUART is a vital part

of any SQ80 since it’s responsible for the following functions:

• MIDI communication (Serial Port A)

• communication with keyboard processor (Serial Port B)

• communication with panel processor (Serial Port B)

• tape I/O

• cartridge presence checking

• disk head access

• disk change detection

• selection of voltages to be sampled

• OSROM low bank switching

• SEQRAM selection and bank switching

• metronome click generation

• timing

To be more precise, the input and output lines are used for the following

tasks:

Inport Task Outport Task

0 Tape In 0 Disk Head

1 Disk Change Detection 1 Multiplexer Bit 0

2 Cartridge Detection 2 Multiplexer Bit 1

3 500Hz Interrupt 3 Multiplexer Bit 2

4 500Hz Interrupt 4 Metronome Click Generation

5 1kHz Interrupt 5 Metronome Click Generation

6 1kHz Interrupt 6 Tape Out

- 7 Tape Out

Table 2.1: Additional DUART tasks

Page 22

20 CHAPTER 2. TECHNICAL DOCUMENTATION

2.6 The system software

Now this is something which really impressed me: The SQ80 has a really

nice multitasking real-time operating system (RTOS). Normally, you don’t

get in contact with the mysteries of this OS, but just for completeness’ sake

I’ll give a rough overview:

2.6.1 OSRAM

The OSRAM needs to be ”formatted” since some vital data structures are

stored here, the most relevant one is the context table which is responsible for

proper task switching. Since the OSRAM is battery buffered (it also holds

the sound programs) you normally don’t run into problems, even when you

need to replace the battery after some years (mine is doing fine for over

11 years now), since the OS checks for an empty OSRAM during reset and

reformats it if necessary. When upgrading the OS ROMs this check might

fail and you need to reformat it manually (see 2.6.3 for details).

2.6.2 Cartridge

You know the cartridge as something to hold program banks. Like the

OSRAM it also holds some status data which is explained below:

0x3FFD: set to 0 if cartridge bank B contains data, 0xff else

0x3FFE: set to 0 if cartridge bank A contains data, 0xff else

0x3FFF: set to 0x01 if cartridge contains program banks, it’s also possible

to take over the system if 0x55 is stored here.

If a cartridge is present or not is detected by the DUART’s input port

2.

2.6.3 Hidden Functions

Yes, the SQ80 offers hidden functions which are not mentioned in the Musician’s Manual. You can reach these by pressing RECORD with one of the

following keys:

COMPARE

Analog Voltage Check

FILTER

With this function the SQ80 recalibrates its filters. This is to ensure

that all 8 voices have (nearly) the same filter response parameters unfortunately, this tuning is responsible for the SQ80’s filter not being

able to self oscillate: The filter tuning parameters are calculated in a

way that self-oscillation is just impossible.

Page 23

2.6. THE SYSTEM SOFTWARE 21

MASTER

Prints the OS version. The latest version released by Ensoniq was 1.8,

unfortunately there’s no official support anymore but if you are able

to program EPROMs yourself you’ll find the images on my web page.

MODES

If you ever wondered who built the SQ80 call this menu.

Soft Button 1

Reinitialization (“OSRAM Formatting”) - as mentioned above this

function is needed after an OSROM upgrade.

Soft Button 6

Warm Reset. Nice idea, but jams the machine - at least on OS versions

1.7 and 1.8.

SPLIT/LAYER

Keyboard recalibration.

Page 24

22 CHAPTER 2. TECHNICAL DOCUMENTATION

Page 25

Chapter 3

Troubleshooting

Almost all eMails I get concerning the SQ80 are about the synthesizer behaving strange or not working at all. On the following pages you’ll find hints

about what might cause misbehaviour and how to fix it.

23

Page 26

24 CHAPTER 3. TROUBLESHOOTING

3.1 General problems

The system won’t come up...

If your SQ80 does not come up at all, showing a blank display and

no reaction to any MIDI message or key pressure its most likely the

power supply. Check for blown fuses or dried-out capacitors. If that’s

not the problem replace U6 and/or U10.

I’ve upgraded the OS and now the system doesn‘t come up!

Just press RECORD together with soft button 1 (the upper left above

the display). This will perform a complete reset including reformatting

the OSRAM. Afterwards, everything should be ok again. If not check

the OSROMs for correct placement.

Display says that the battery voltage is low.

Just replace it. Any 3V to 5V lithium battery will be fine. If you don’t

find the battery on the motherboard you should probably leave that

step to somebody who knows on which side the soldering iron heats...

The pedal won’t work.

Check cabling. Otherwise replace U33 – if that doesn’t help either

your DOC is f*cked up, try to get one from a used/dead Apple IIGS,

ESQ-1 or SQ80. Or send it to me so that I can make an expander

version out of it.

The wheels won’t work.

Check pedal cabling. Rest see above.

My cartridge isn’t recognized.

Check if cartridge is formatted. Check cabling. Check presence of 5V

at pin x of U6 while cartridge is inserted. Voltage found? Build a new

cable using new connectors. If that won’t help replace U6. If you did

not find the voltage replace U2 to U4.

There are no metronome clicks anymore.

Replace U39. If that doesn’t help replace U44. If that didn’t help

either replace U6.

I can’t hear anything.

Check pins 6 and 9 of U44 if it gets any signals. If this is not the case

replace U39, otherwise replace U44.

Some voices are missing.

Check pin 8 of U40-43, U45-48 playing an 8-note chord. If one or more

doesn’t get an input signal replace U36. If that doesn’t help search for

a new DOC and replace U27.

Page 27

3.2. MIDI MYSTERIES 25

The voices are stuck!

Check sustain switch. Replace U33.

The sustain switch doesn’t work.

See above.

The pedal doesn’t work.

Check pedal. Replace U33.

The Sequencer switch doesn’t work.

Check switch. Replace U33.

If they all get input signals identify the one which does not output a

signal on pin 15 and 17 (be sure to have pan set to 8 with no modulation while testing this) and replace it.

3.2 MIDI mysteries

I can’t send MIDI messages, but receiving them is fine.

Replace Q1 to Q4. If that doesn’t help, replace U6.

I can’t receive MIDI messages,but sending them is fine.

Replace U12. If that doesn‘t help, replace U6.

I can only receive/send some MIDI messages.

Duh! Go to MIDI menu and enable the desired messages.

3.3 Keyboard Trouble

During reset display says keyboard is disabled!?

Check cabling. Power the system on and check U6 pin 10 and 11 for

serial communication. If you don’t see anything at pin 10 replace U1

(68HC11) on the keyboard PCB – otherwise replace U6.

I get keyboard processor errors.

Check cabling. Replace U1 (68HC11) on the keyboard PCB. If that

doesn’t help replace U6.

Keyboard calibration fails all the time.

Check cabling. If that doesn‘t help try to get a new keyboard ASIC

or send the SQ80 to me to make a nice expander version out of it.

The SQ80 won’t leave keyboard calibration.

Check cabling. Check keyboard PCB for cold soldering spots. Check

serial communication (see above).

My keyboard doesn’t work – but I get no error message!

Duh! Go to MASTER menu and enable it.

Page 28

26 CHAPTER 3. TROUBLESHOOTING

3.4 Storage Hassles

I get more and more read/write errors.

Clean the drive using an ordinary cleaning diskette – or be tough and

clean the drive heads using Q-tips and isopropanole.

If that won’t help replace the drive. Any 720kB drive with shugart

bus will do the job.

The drive doesn’t show any reaction.

Check cabling. Replace U24 and U29. If that won’t help, replace U9.

3.5 Panel Problems

I can’t see anything...

Check cabling. Check for correct display voltage. If that’s not the

problem check/replace the display drivers. If that won‘t help, send

the SQ80 to me to make a nice expander version from it since either

the display itself or the panel CPU is broken. No replacement possible.

Some keys won’t work.

Remove the panel PCB and clean the contacts.

Some keys are stuck.

Remove the panel and clean the keys / holes.

3.6 Flaky Tape

I can’t load from tape.

Replace U25. If that doesn’t help replace U6.

I can’t sync in.

see above

I can’t write to tape.

Replace U6.

I can’t sync out.

see above

Page 29

Appendix A

Parts List

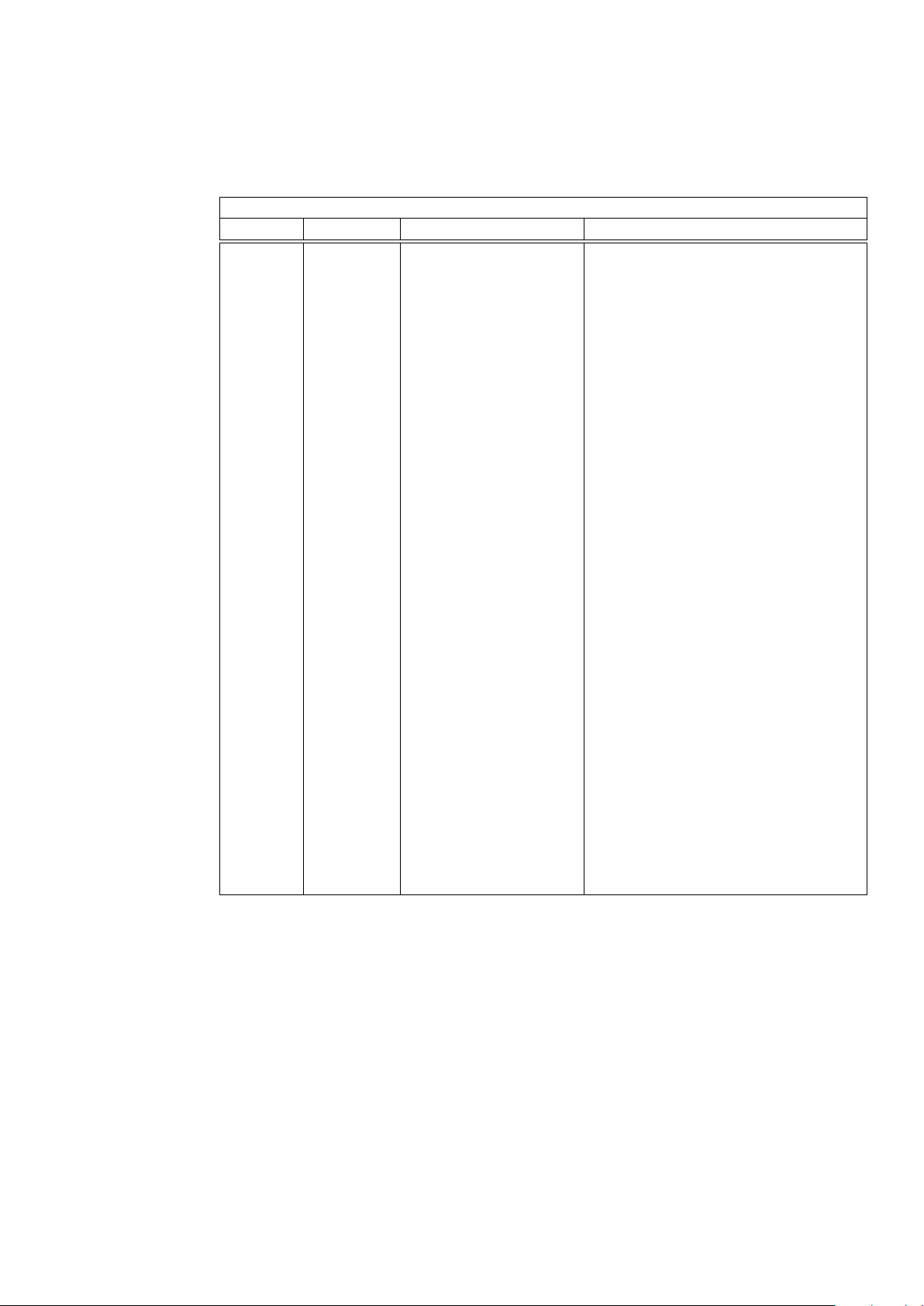

# Type Description Task

Q1 2N3906 MIDI out

Q2 2N3904 MIDI thru

Q3 2N3906 MIDI thru

Q4 2N3906 MIDI out

Q6 JE182 Amplification

Q7 Amplification

U1 74LS04 hex inverter

U2 74ALS245 8x bidir. buffer/driver Cartridge Data

U3 74ALS244 8x buffer/driver Cartridge Address/Control

U4 74ALS244 8x buffer/driver Cartridge Address/Control

U5 74LS161 4bit counter Timer

U6 MC2681, SCN2681 DUART Communication & Control

U7 74LS10 3x 3-input NAND misc. Cartridge

U8 74LS00 4x 2-input NAND Clock Generation

U9 WD1772 FDC Disk Drive Control

U10 MC6809E CPU Central Processing Unit

U11 74LS74 2x D-type FF Q-Clock Generation

U12 6N138 opto coupler MIDI in

U13 74F139 2x 2-to-4 mux Address Decoding

U14 4364-15 SRAM 8kx8 OSRAM

U15 74F139 2x 2-to-4 mux Address Decoding

U16 27C256-20 EPROM 32kx8 OSROM high

U17 74LS244 8x buffer/driver DOC Addressing

U18 4364-15 SRAM 8kx8 DOSRAM

U19 74F139 2x 2-to-4 mux Address Decoding

continued on next page

27

Page 30

28 APPENDIX A. PARTS LIST

continued from previous page

# Type Description Task

U20 27C256-20 EPROM 32kx8 OSROM low

U21 74LS245 8x bidir. buffer/driver DOC Data

U22 27C512 EPROM 64kx8 WAVE 0

U23 27C512 EPROM 64kx8 WAVE 1

U24 7406 hex inverter Signal Driver (to Floppy)

U25 LM311 voltage comparator Tape Input

U26 74LS373 octal latch Wave Address Demultiplexing

U27 DOC5503 ASIC Sound Generation, A/D Conversion

U28 74LS377 octal latch Analog Parts Addressing

U29 AD7524 DAC CV Generator

U30 TL081 OPAMP CV amplification

U31 MC34085 OPAMP Sound Amplifier

U32 TL081 OPAMP Volume Adjustment

U33 4051 1-to-8 analog mux Voltage Multiplexer (for ADC)

U34 SSM2300 8x sample & hold ENV4 CV mux

U35 SSM2300 8x sample & hold Q CV mux

U36 4051 1-to-8 analog mux Audio Router

U37 SSM2300 8x sample & hold PAN CV mux

U38 SSM2300 8x sample & hold FF VC mux

U39 TL084 4x OPAMP Audio L/R

U40-U43 CEM3379 analog voice processor Filter / DCA4 / PAN

U44 CEM3360 dual VCA final amplifier

U45-U48 CEM3379 analog voice processor Filter / DCA4 / PAN

U49 74LS05 hex inverters Floppy Driver

U50 43256C-12 SRAM 32kx8 SEQRAM low

U51 43256C-12 SRAM 32kx8 SEQRAM high

U52 74LS138 3-to-8 mux SEQRAM select

U53 74LS74 2x D-type FF Mapper

U54 27C512 EPROM 64kx8 WAVE 2 (not installed)

U55 27C512 EPROM 64kx8 WAVE 3 (not installed)

Y1 OSC8MHz Quartz Oscillator System Clock Generator

Table A.1: Parts list

Page 31

Appendix B

Schematics

Caution: These schematics do only cover the (vital) digital part of the

SQ80. I’ve spent some time tracing the signals using an ordinary multi-meter

and tons of paper... I do not guarantee the correctness of these self-made

schematics so use them entirely at your own risk.

However, if you encounter any errors feel free to contact me so that I can

bugfix the schematics and publish a error-corrected version of this document.

29

Page 32

30 APPENDIX B. SCHEMATICS

Page 33

31

Figure B.1: Memory Decoding & Timing Generator

Page 34

32 APPENDIX B. SCHEMATICS

Page 35

33

Figure B.2: System Memory

Page 36

34 APPENDIX B. SCHEMATICS

Page 37

35

Figure B.3: WaveROM & DOC access

Page 38

36 APPENDIX B. SCHEMATICS

Page 39

37

Figure B.4: Peripheral Interfacing

Page 40

38 APPENDIX B. SCHEMATICS

Page 41

Appendix C

Datasheets

For your convenience here are the (some times hard to find) schematics of

all vital parts of the SQ80. What I have not included are the common parts

such as TTL ICs or OPAMPs which you will find in any usual data book.

39

Page 42

40 APPENDIX C. DATASHEETS

Page 43

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 41

C.1 WD1770/1772 Floppy Disk Controller / For-

matter

C.1.1 Description

The WD177x is a MOS LSI device which performs the functions of a Floppy

Disk Controller/Formatter. It is similar to its predecessor, the WD179x

but also contains a digital data separator and write precompensation circuitry. The drive side of the interface needs no additional logic except for

buffers/receivers. Designed for single or double density operation. The device contains a programmable Motor On signal.

The WD177x is a low cost version of the FD179x Floppy Disk Controller/Formatter. It is compatible with the 179x, but has a built-in digital

data separator and write precompensation circuits. A single read line (RD#,

pin 19) is the only input required to recover serial FM or MFM data from

the disk drive. The device has been specifically designed for control of

floppy disk drives with data rates of 125 Kbits/sec (single density) and 250

Kbits/sec (double density). In addition write precompensation of 125 Nsec

from nominal can be enabled at any point through simple software commands. Another programmable feature, Motor On, has been incorporated

to enable the spindle motor prior to operating a selected drive.

Two versions of the WD1770 are available. The standard version is

compatible with the 179x stepping rates, while the WD1772 offers stepping

rates of 2, 3, 5 and 6 msec.

The processor interface consists of an 8-bit bidirectional bus for transfer

of status, data and commands. All host communication with the drive

occurs through these data lines. They are capable of driving one standard

TTL load or three ”LS” loads.

C.1.2 Architecture

The Floppy Disk Formatter block diagram is illustrated on page 4. The

primary sections include the parallel processor interface the the Floppy Disk

Interface.

Data Shift Register

This 8-bit register assembles serial data from the Read Data input

(RD#) during Read operations and transfers serial data to the Write

Data output during write operations.

Page 44

42 APPENDIX C. DATASHEETS

3

4

5

6

7

8

9

10

11

12

13

14

2

1 28

27

26

25

24

23

22

21

20

19

18

17

16

15

INTRQ

DRQ

DDEN#

WPRT#

IP#

TR00#

WD

WG

MO

RD#

CLK

DIR

STEP

Vcc

CS#

R/W

A0

A1

D0

D1

D2

D3

D4

D5

D6

D7

MR#

GND

Figure C.1: WD177x Pinout

Data Register

This 8-bit register is used as a holding register during Disk read and

Write operations. In Disk Read operations the assembled data byte is

transferred in parallel to the Data register from the Data Shift Register. In Disk Write operations information is transferred in parallel

from the the Data Register to the Data Shift Register.

When executing the Seek command the Data Register holds the address of the desired Track position. This register is loaded from the

DAL and gated into the DAL under processor control.

Track Register

This 8-bit register holds the track number of the current Read/Write

hed position. It is incremented by one every time the head is stepped in

and decremented by one when the head is stepped out (towards track

00). The contents of the register are compared with the recorded track

number in the ID field during disk Read, Write and Verify operations.

The track register can be loaded from or transferred to the DAL. This

register should not be loaded when the device is busy.

Sector Register (SR)

This 8-bit register holds address of the desired sector postition. The

contents of the register are compared with the recorded sector number

in the ID field during disk Read or Write operations. The Sector

Register contents can be loaded from or transferred to the DAL. This

register should not be loaded when the device is busy.

Command Register (CR)

Page 45

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 43

This 8-bit register holds the command presently being executed. This

register should not be loaded when the device is busy unless the new

command is a force interrupt. The command register can be loaded

from the DAL, but not read into the DAL.

Status Register (STR)

This 8-bit register holds device Status information. The meaning of the

status bits is a function of the type of command previously executed.

This register can be read into the DAL, but not loaded from the DAL.

CRC Logic

This logic is used to check or to generate the 16-bit Cyclic Redundancy

Check (CRC). The polynominal is: g(x) = x16+x12+x5+1 The CRC

includes all information starting with the address mark and up to the

CRC characters. The CRC register is preset to ones prior to data

being shifted through the circuit.

Arithmetic/Logic Unit (ALU)

The ALU is a serial comperator, incrementer and decrementer and is

used for register modification and comparisons with the disk recorded

ID field.

Timing and Control

All computer and floppy disk interface controls are generated through

this logic. The internal device timing is generated from an external

crystal clock. The WD177x has two different modes of operation according to the state of DDEN#. When DDEN# = 0, double density is

enabled. When DDEN# = 1, single density is enabled.

AM Detector

The address mark detector detects ID, data and index address marks

during read and write operations.

Data Separator

A digital data separator consisting of a nng shift register and data

window detection logic provides read data and a recovery clock to the

AM detector.

C.1.3 Processor Interface

The interface to the processor is accomplished through the eight Data Access

Lines (DAL) and associated control signals. The DAL are used to transfer

data, Status and Control words out of, or into the WD177x. The DAL are

three state buffers that are enabled as output drivers when Chip Select (CS#)

and R/W = 1 are active or act as input receivers when CS and R/W = 0 are

active.

Page 46

44 APPENDIX C. DATASHEETS

When transfer of data with the Floppy Disk Controller is required by the

host processor, the device address is decoded and CS# is made low. The address bits A1 and A0, combined with the signal R/W during a Read operation

or Write operation are interpreted as selecing the following registers:

A1 A0 Read Write

0 0 Status Register Command Register

0 1

1 0

1 1

Table C.1: WD1770/1772 Registers

During Direct Memory Access (DMA) types of data transfers between

the Data Register of the WD177x and the processor, the Data ReQuest

(DRQ) output is used in Data Transfer control. This signal also appears as

status bit 1 during Read and Write operations.

Track Register

Sector Register

Data Register

On Disk Read operations the Data Request is activated (set high) when

an assembled serial input byte is transferred in parallel to the Data Register.

This bit is cleared when the Data Register is read by the processor. If the

Data Register is read after one or more characters are lost, by having new

data transferred to the register prior to processor readout, the Lost Data

bit is set in the Status Register. The read operation continues until the end

of sector is reached.

On Disk Write operations the Data ReQuest is activated when the Data

Registers its contents to the Data Shift Register and requires a new data

byte. It is reset when the Data Register is loaded with new data by the

processor. If new data is not loaded at the time serial byte is required by

the Floppy Disk, a byte of zeroes is written on the diskette and the Lost

Data bit is set in the Status Register.

At the completion of every command an INTRQ is generated. INTRQ is

reset by either reading the status register or by loading the command register

with a new command. In addition INTRQ is generated if a Force Interrupt

command condition is met.

The WD177x has two modes of operation according to the state of DDEN#

(pin 26). When DDEN# = 1, single density is selected. In either case, the

CLK input (pin 18) is at 8 MHz.

Page 47

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 45

C.1.4 General Disk Read Operation

Sector lengths of 128, 256, 512 or 1024 bytes are obtainable in either FM

or MFM formats. For FM formats, DDEN# should be placed to logical ”1”.

For MFM formats, DDEN# should be placed to logic ”0”. Sector lengths are

determined at format time by the fourth byte in the ID field.

Sector Length # of Bytes/Sector

00 128

01 256

02 512

03 1024

Table C.2: Sector Length Settings

The number of sectors per track as far as the WD177x is concerned can

be from 1 to 255 sectors. The number of tracks as far as the WD177x is

concerned is from 0 to 255 tracks.

C.1.5 General Disk Write Operation

When writing is to take place on the diskette, the Write Gate (WG) output

is activated, allowing current to flow into the Read/Write head. As a precaution to erroneous writing the first data must be loaded into the Data

Register in response to a Data ReQuest from the device before the Write

Gate signal can be activated.

Writing is inhibited when the WP# (Write Protect) input is a logic low,

in which case any Write command is immediately terminated, an interrupt

generated and the Write Protection status bit is set.

For Write operations, the WD177x provides Write Gate (WG, pin 21)

to enable a write condition and Write Data (WD, pin 22) which consists of

a series of active high pulses. These pulses contain both Clock and Data

information in FM or MFM. Write Data provides the unique missing clock

patterns for recording Address Marks.

The Precomp Enable bit in Write commands allow automatic Write Precompensation to take place. The outgoing Write Data Stream is delayed or

advanced according to the following table:

Pattern MFM FM

x 1 1 0 Early N/A

continued on next page

Page 48

46 APPENDIX C. DATASHEETS

continued from previous page

Pattern MFM FM

x 0 1 1 Late N/A

0 0 0 1 Early N/A

1 0 0 0 Late N/A

Table C.3: Precompensation Scheme

Hereby represent the four pattern bits (from left to right) the previous

sent bits, the bit currently being sent and the next bit to send.

Precompensation is typically enabled on the innermost tracks where bit

shifts usually occur and bit density is at its maximum.

C.1.6 Command Description

De WD177x will accept eleven commands. Command words should only be

loaded in the Command Register when the Busy status bit is off (Status

bit 0). The one exception is the force interrupt command. Whenever a

command is being executed, the Busy status bit is set. When a command is

completed, an interrupt is generated and the Busy status bit is reset. The

status register indicates whether the completed command encountered an

error or was fault free. For ease of discussion, commands are divided into

four types. Commands and types are summarized in table C.4.

Type Command

Bits 7-0

1 Restore 0 0 0 0 h v r1 r0

1 Seek 0 0 0 1 h v r1 r0

1 Step 0 0 1 u h v r1 r0

1 Step-in 0 1 0 u h v r1 r0

1 Step-out 0 1 1 u h v r1 r0

2 Rd sectr 1 0 0 m h E 0 0

2 Wt sectr 1 0 1 m h E P a0

3 Rd addr 1 1 0 0 h E 0 0

3 Rd track 1 1 1 0 h E 0 0

3 Wt track 1 1 1 1 h E P 0

4 Forc int 1 1 0 1 i3 i2 i1 i0

Table C.4: Command Summary

Type 1 Commands

h = Motor on Flag (bit 3)

h = 0 Enable spin-up Sequence

continued on next page

Page 49

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 47

continued from previous page

Type 1 Commands

h = 1 Disable spin-up Sequemce

v = Verify Flag (bit 2)

v = 0 No verify

v = 1 Verify on destn track

r1, r0 = Stepping rate (bits 1, 0)

r1 r0 WD1770 WD1772

0 0 6 ms 2 ms

0 1 12 ms 3 ms

1 0 20 ms 5 ms

1 1 30 ms 6 ms

u = Update Flag (bit 4)

u = 0 No update

u = 1 Update Track Register

Table C.5: Type 1 Commands Flag Summary

Type 2 Commands

m = Multiple Sector Flag (bit 4)

m = 0 Single sector

m = 1 Multiple sector

a0= Data Address Mark (bit 0)

a0= 0 Write normal Data Mark

a0= 1 Write Deleted Data Mark

E = 30ms Settling Delay (bit 2)

E = 0 No delay

E = 1 Add 30ms Delay

P = Write Precompensation (bit 1)

P = 0 Enable Write Precomp

P = 1 Disable Write Precomp

Table C.6: Type 2 Commands Flag Summary

Type 4 Commands

i3-i0 Interrupt condition (bit 3-0)

continued on next page

Page 50

48 APPENDIX C. DATASHEETS

continued from previous page

Type 4 Commands

i0= 1 Don’t care

i1= 1 Don’t care

i2= 1 Interrupt on index pulse

i3= 1 Immediate interrupt

13-i0 = 0 Terminate without interrupt

Table C.7: Type 4 Commands Flag Summary

C.1.7 Type 1 Commands

The type 1 commands include the Restore, Seek, Step, Step-in and Step-out

commands. Each of the Type 1 commands contains a rate field (r0, r1),

which determines the stepping motor rate.

A 4µs (MFM) of 8µs (FM) pulse is provided as an output to the drive.

For every step pulse issued, the drive moves one track location in a direction

determined by the direction output. The chip will step the drive in the same

direction it last stepped, unless the command changes the direction.

The direction signal is active high when stepping in and low when stepping out. The Direction signal is valid 24uS before the first stepping pulse

is generated.

After the last directional step an additional 30 milliseconds of head settling time takes if the verify flag is set in type 1 commands. There is also a

30ms head settling time if the E flag is set in any Type 2 or 3 command.

When a Seek, Step or Restore command is executed, an optional verification of Read/Write head position can be performed by setting bit 2 (V=1)

in the command word to a logic ”1”. The verification operation begins at

the end of the 30ms settling time after the head is loaded against the media.

The track number from the first encountered ID field is compared against

the contents of the Track Register. If the track numbers compare and the

ID field CRC is correct, the verify operations is complete and an INTRQ is

generated with no errors. If there is a match but not a valid CRC, the CRC

error status bit is set (Status bit 3) and the next encountered ID field is

read from the disk for the verification operation.

The WD177x must find an ID field with correct track number and correct

CRC within 5 revolutions of the media, otherwise the seek error is set and

an INTRQ is generated. If V=0 no verification is performed.

Page 51

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 49

All commands except the Force Interrupt command may be programmed

via the h Flag to delay for spindle motor startup time. If the h Flag is set

and the Motor On line (MO, pin 20) is low when a command is received, the

WD177x will force Motor On to a logic ”1” and wait 6 revolutions before

executing the command. At 300rpm this guarantees a one second spindle

startup time. If after finishing the command, the device remains idle for 10

revolutions, the Motor On line will go back to a logic ”0”. If a command

is issued while Motor On is high, the command will execute immediately,

defeating the 6 revolutions start up. This feature allows consecutive Read or

Write commands without waiting for motor start up each time; the WD177x

assumes the spindle motor is up to speed.

Restore (Seek Track 0)

Upon receipt of this command, the Track 00 (TR00#) input is sampled.

If TR00# is active low indicating the Read/Write head is positioned

over track 0, the Track register is loaded with zeroes and an interrupt

is generated. If TR00# is not active low, stepping pulses (pin 16) at

a rate specified by the r1, r0 field are issued until the TR00# input is

activated. At this time, the Track Register is loaded with zeroes and an

interrupt is generated. If the TR00# input does not go active low after

255 stepping pulses, the WD177x terminates operation, interrupts and

sets the Seek error status bit, providing the V flag is set. A verification

als takes place if the V flag is set. The h bit allows the Motor On option

at the start of command.

Seek

This command assumes that the track register contains the track number of the current position of the Read/Write head and the Data Register contains the desired track number. The WD177x will update the

Track Register and issue stepping pulses in the appropiate direction

until the contents of the Track Register are equal to the contents of

the Data Register (the desired Track location). A verification operation takes place if the V flag is on. The h bit allows the Motor On

option at the start of the command. An interrupt is generated at the

completion of the command. Note: When using mutiple drives, the

track register must be updated for the drive selected before seeks are

issued.

Step

Upon receipt of this command, the WD177x issues one stepping pulse

to the disk drive. The stepping motor direction is the same as in the

previous step command. After a delay determined by the r1, r0 field,

a verification takes place if the V flag is on. If the U flag is on, the

Track Register is updated. The h bit allows the Motor On option at

Page 52

50 APPENDIX C. DATASHEETS

the start of the command. An interrupt is generated at the completion

of the command.

Step-In

Upon receipt of this command, the WD177x issues one stepping pulse

in the direction towards track 76. If the U flag is on, the Track Register

is incremented by one. After a delay determined by the r1, r0 field, a

verification takes place if the V flag is on. The h bit alows the Motor

On option at the startof the command. An interrupt is generated at

the completion of the command

Step-Out

Upon receipt of this command, the WD177x issues one stepping pulse

in the direction towards track 0. If the U flag is on, the Track Register

is decremented by one. After delay determined by the r1, r0 field, a

verification takes place if the V flag is on. The h bit allows the Motor

On option at the start of the command.

C.1.8 Type 2 Commands

The type 2 commands are the read sector and write sector commands. Prior

to loading the type 2 command into the command register, the computer

must load the sector register with the desired sector number. Upon receipt

of the type 2 command, the busy status bit is set. If the E flag is 1, the

command will execute after 30ms delay.

When an ID field is located on the disk, the WD177x compares the track

number on the ID field with the Track register. If there is not a match, the

next encountered ID field is read and a comparison is again made. If there

was a match, the Sector Number of the ID field is compared with the Sector

Register. If there is not a Sector match, the next encountered ID field is

read off the disk and comparisons again made. If the ID field CRC is correct,

the data field is then located and will be either written into, or read from

depending upon the command. The WD177x must find an ID field with a

track number, sector number and CRC within four revolutions of the disk,

otherwise, the Record not found status bit is set (status bit 4) and the

command is terminated with an interrupt (INTRQ).

Each of the type 2 commands contains an (m) flag which determines

if multiple records (sectors) are to be read or written, depending upon the

command. If m=0, a single record is read or written and an interrupt is

generated at the completion of the command. If m=1, multiple records

are read or written with the sector register internally updated so that an

address verification can occur on the next record. The WD177x will continue

to read or write multiple records and update the sector register in numerical

Page 53

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 51

ascending sequence until the sector number exceeds the number of sectors

on the track or until the Force Interrupt command is loaded in the command

register, which terminates the command and generates an interrupt.

Example: If the WD177x is instructed to read sector 17 and there are

only 16 sectors on the track, the sector register exceeds the number available.

The WD177x will search for 5 disk revolutions, interrupt out, reset busy and

set the record not found status bit.

Read Sector

Upon receipt of the Read Sector command, the busy status bit is set,

and when an ID field is encountered that has the correct track number,

corect sector number and correct CRC, the data field is presented to

the computer. The data address mark of the data field must be found

within 30 bytes in single density and 43 bytes in double density of

the last ID field CRC byte; if not, the ID field is searched for and

verified again followed by the Data Address Mark search. If after 5

revolutions the DAM cannot be found, the record not found bit is set

and the operation terminated. When the first character or byte of the

data field has been shifted through the DSR, it is transferred to the

DR, and DRQ is generated. When the next byte is accumulated in

the DSR, it is transferred to the DR and another DRQ is generated.

If the computer has not read the previous contents of the DR before

a new character is transferred that character will be lost and the lost

data status bit is set. This sequence continues until the complete data

field has been inputted to the computer. If there is a CRC error at the

end of the data field, the CRC error status bit is set and the command

is terminated (even if it is a multiple record command).

At the end of the Read operation, the type of Data Address Mark

encountered in the data field is recorded in the status register (bit 5)

as shown:

1 represents a deleted data mark whereas

0 represents a data mark

Write Sector

Upon receipt of the Write Sector command, the Busy status bit is set.

When an ID field is encountered that has the correct track number,

correct sector number and correct CRC, a DRQ is generated. The

WD177x counts off 11 bytes in single density and 22 bytes in double

density from the CRC field and the Write Gate (WG) output is made

active if the DRQ is serviced (i.e. the DR has been loaded by the

computer). If DRQ has not been serviced, the command is terminated

and the lost data status bit is set. If the DRQ has been serviced, the

Page 54

52 APPENDIX C. DATASHEETS

WG is made active and six bytes of zeroes in single density and 12

bytes in double density are then written to the disk. At this time, the

Data Address Mark is then written on the disk as determined by the

a0 field of the command as shown below:

1 represents a deleted data mark whereas

0 represents a data mark

The WD177x then writes the data field and generates DRQ’s to the

computer. If the DRQ is not serviced in time for conitinious writing

the lost data status bit is set and a byte of zeroes is written on the

disk. The command is not terminated. After the last data byte has

been written on the disk, the two byte CRC is computed internally and

written on the disk followed by one byte of logic ones in FM or MFM.

The WG output is then activated. INTRQ will set 24uSec (MFM) after

the last CRC byte is written. For partial sector writing, the proper

method is to write data and fill the balance with zeroes.

C.1.9 Type 3 Commands

Read Address

Upon receipt of the Read Address command, the Busy status bit is

set. The next encountered ID field is then read in from the disk, and

six data bytes of the ID field are assembled and transferred to the DR,

and a DRQ is generated for each byte. The six bytes of the ID field

are shown below.

Track Side Sector Sector CRC CRC

Address Number Address Length 1 2

1 2 3 4 5 6

Table C.8: ID Field

Although the CRC characters are transferred to the computer, the

WD177x checks for validity and the CRC error status bit if there is

a CRC error. The Track Address of the ID field is written into the

sector register so that a comparison can be made by the user. At the

end of the operation an interrupt is generated and the Busy status bit

is reset.

Read Track

Upon receipt of the Read Track command, the head is loaded and the

Busy status bit is set. Reading starts with the leading edge of the first

encountered index pulse and continues until the next index pulse. All

gap, Header and data bytes are assembled and transferred to the data

Page 55

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 53

register and DRQ’s are generated for each byte. The accumulation of

bytes is synchronized to each address mark encountered. An interrupt

is generated at the completion of the command. This command has

several characteristics which makes it suitable for diagnostic purposes.

They are: no CRC checking is performed; gap information is included

in the datastream; and the address mark detector is on for the duration

of the command. Because the AM detector is always on, write splices

or noise may cause the chip to look for an DM.

The ID am, ID field, ID CRC bytes, DAM, data, and data CRC bytes

for each sector will be correct. The Gap Bytes may be read incorrectly

during write-splice time because of synchronization.

Write Track / Formatting the Disk

Formatting the disk is a relatively simple task when operating programmed I/O or when operating under DMA with a large amount of

memory. Data and gap information must be provided at the computer

interface. Formatting the disk is accomplished by positioning the R/W

head over the desired track and issuing the Write Track command.

Upon receipt of the Write Track command, the Busy status bit is set.

Writing starts with the leading edge of the first encountered index

pulse and continues until the next index pulse, at which time the

interrupt is activated. The Data ReQuest is activated immediately

upon receiving the command, but writing will not start until after the

first byte has been loaded into the Data Register. If the DR has not

been loaded within 3 byte times, the operation is terminated making

the device not busy, the Lost Data Status bit is set, and the interrupt

is activated. If a byte is not present in the DR when needed, a byte of

zeroes is substituted.

This sequence continues from one index mark to the next index mark.

Normally, whatever data pattern appears in the data register is written on the disk with a normal clock pattern. However, if the WD177x

detects a data pattern of F5 through FE in the data register, this is

interpreted as data address marks with missing clocks or CRC generation.

Data Pattern

in DR (hex) in FM (DDEN#=1) in MFM (DDEN#=0)

00 thru F4 Wt 00 thru F4 with CLK = FF Wt 00 thru F4 in MFM

F5 Not Allowed Wt A1 in MFM, Preset CRC

continued on next page

Page 56

54 APPENDIX C. DATASHEETS

continued from previous page

Data Pattern

in DR (hex) in FM (DDEN#=1) in MFM (DDEN#=0)

F6 Not Allowed Wt C2 in MFM

F7 Generate 2 CRC bytes Generate 2 CRC bytes

F8 thru FB Wt F8-FB, Clk=C7,Preset CRC Wt F8 thru Fb, in MFM

FC Wt FC with Clk=D7 Wt FC in MFM

FD Wt FD with Clk=FF Wt FD in MFM

FE Wt FE, Clk=C7, Preset CRC Wt FE in MFM

FF Wt FF with Clk=FF Wt FF in MFM

Table C.9: ID Field

The CRC generator is initialized when any data byte from F8 to FE is

about to be transferred from the DR to the DSR in FM or by receipt

of F5 in MFM. An F7 pattern will generate two CRC characters in

FM or MFM. As a consequence, the patterns F5 through FE must

not appear in the gaps, data fields or ID fields. Also, CRC’s must be

generated by an F7 pattern.

Disks may be formatted in IBM 3740 or system 34 formats with sector

lengths of 128, 256, 512 or 1024 bytes.

C.1.10 Type 4 Commands

The forced interrupt command is generally used to terminate a multiple

sector read or write command or to insure Type 1 status in the status

register. This command can be loaded into the command register at any

time. If there is a current command under execution (Busy status bit set)

the command will be terminated and the busy status bit reset.

The lower four bits of the command determine the conditional interrupt

as follows:

i0 Don’t care

i1 Don’t care

i2 Every index puls

i3 Immediate interrupt

The conditional interrupt is enabled when bit positions of the command

(i3-i0) are set to a ”1”. Then, when the condition for interrupt is met, the

INTRQ line will go high signifying that the condition specified has occurred.

If i3-i0 are all set to zero ($d0), no interrupt will occur, but any command

Page 57

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 55

presently under execution will be immediately terminated. When using the

immediate interrupt condition (i3=1) an interrupt will be immediately generated and the current command terminated. Reading the status or writing

to the command register will not automatically clear the interrupt. $d0 is

the only command that will enable the immediate interrupt ($d6) to clear

on a subsequent load command register or read status register operation.

Follow a $d6 with $d0 command.

Wait 16µs (double density) or 32µs (single density) before issuing a new

command after issuing the forced interrupt. Loading a new command sooner

than this will nullify the forced interrupt.

Forced interrupt stops any command at the end of an internal microinstruction and generates INTRQ when the specified condition is met. Forced

interrupt will wait until ALU operations in progress are complete (CRC

calculations, compares, etc.).

C.1.11 Status Register

Upon receipt of any command, except the Force interrupt command the

Busy status bit is set and the rest of the status bits are updated or cleared

for the new command. If the Force Interrupt Command is received when

there is a current command under execution, the Busy status bit is reset and

the rest of the status bits are unchanged. If the Forced interrupt command

is received when there is not a current command under execution, the Busy

status bit is reset and the rest of the status bits are updated or cleared. In

this case, Status reflects the type 1 commands.

The user has the option of reading the status register through program

control or using the DRQ with DMA or interrupt methods. When the Data

register is read the DRQ bit in the status register and the DRQ line are

automatically reset. A write to the Data Register also causes both DRQ’s

to reset.

The busy bit is the status may be monitored with a user program to

determine when a command is complete, in lieu of using the INTRQ line.

When using the INTRQ, a busy status check is not recommended because a

read of the status register to determine the condition of busy will reset the

INTRQ line.

The format of the Status register is shown in the following table:

Page 58

56 APPENDIX C. DATASHEETS

Bit Name Meaning

7 MOTOR ON This bit reflects the status of the Motor On out-

put.

6 WRITE PROTECT On read record: not used.

On read track: not used.

On any write: it indicates a Write Protect. This

bit is reset when updated.

5 SPIN-UP When set, this bit indicates that the Motor Spin-

Up sequence has completed (6 revolutions) on

type 1 commands.

RECORD-TYPE On Type 2 & 3 commands, this bit indicates

record Type.

0 = Data Mark, 1 = Deleted Data Mark.

4 RECORD NOT FOUND When set, it indicates that the desired track,

sector, or side were not found. This bit is reset

when updated.

3 CRC ERROR If bit 4 is set, an error is found in one or more ID

fields; otherwise it indicates error in data field.

This bit is reset when updated.

2 LOST DATA When set, it indicates the computer did not re-

spond to DRQ in one byte time. This bit is reset

to zero when update.

TRACK00 On type 1 commands, this bit reflects the status

of the TR00# pin.

1 DATA REQUEST This bit is a copy of the DRQ output. When set,

it indicates the DR is full on a Read Operation

or the DR is empty on a write operation. This

bit is reset to zero when updated.

INDEX On type 1 commands, this bit indicates the sta-

tus of the index pin.

0 BUSY When set, command is under execution. When

reset, no command is under execution.

Table C.10: Status Register

C.1.12 Recommended Layout for 128-Byte Sectors

Shown below is the recommended single-density format with 128

bytes/sector. In order to format a diskette, the user must issue the Write

Track command and load the data register with the following values. For

every byte to be written there is one Data Request.

Page 59

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 57

# of bytes Value of Byte(s) Meaning

40 $ff (or $00) GAP1

6 $00 GAP3

1 $fe ID field Address Mark

1 tn Track number

1 hn Side number (0 or 1)

1 sn Sector number (0 thru 25)

1 $00 Sector length

1 $f7 CRC

11 $ff (or $00) GAP2

6 $00 GAP2

1 $fb Data Address Mark

128 data (IBM uses $e5)

1 $f7 CRC

10 $ff (or $00) GAP4a

369 $ff (or $00) GAP4b

Table C.11: ID Field for 128-Byte Sectors

The enclosed area is written 16 times. GAP4 has to be written until

WD1772 interrupts out, 369 bytes as an approximate value.

C.1.13 Recommended Layout for 256-Byte Sectors

Shown below is the recommended dual-density format with 256 bytes/sector.

In order to format a diskette the user must issue the Write Track command

and load the data register with the following values. For every byte to be

written there is one data request.

# of bytes Value of Byte(s) Meaning

40 $4e GAP1

12 $00 GAP3

3 $f5 writes A1, GAP3

1 $fe ID field Address Mark

1 tn Track number

1 hn Side number (0 or 1)

1 sn Sector number (0 thru 25)

1 $01 Sector length

1 $f7 CRC

22 $4e GAP2

12 $ff (or $00) GAP2

3 $f5 writes $A1, GAP2

continued on next page

Page 60

58 APPENDIX C. DATASHEETS

continued from previous page

# of bytes Value of Byte(s) Meaning

1 $fb Data Address Mark

256 data (IBM uses $e5)

1 $f7 CRC

24 $4e GAP4a

668 $4e GAP4b

Table C.12: ID Field for 256-Byte Sectors

The enclosed area is written 16 times. GAP4 has to be written until

WD1772 interrupts out, 668 bytes as an approximate value.

C.1.14 Generic (non-standard) formats

Variations in the recommended formats are possible to a limited extent if

the following requirements are met.

1. Sector length must be 128, 256, 512 or 1024 bytes.

2. Gap 2 cannot be varied from the recommended format.

3. 3 bytes of $a1 must be used in MFM.

In addition, the index Address Mark is not required for operation by the

WD177x. Gap 1, 3 and 4 lengths can be as short as 2 bytes for WD177x

operation, however PLL lock up time, motor speed variation, write splice

area, etc. will add more bytes to each gap to achieve proper operation. It

is recommended that the recommended format be used for highest system

reliability.

# of bytes Value of Byte Comments

60 $4e Gap 1 and Gap 3

Start and end of index pulse.

12 $00 Gap 3

Start of bytes repeated for each sector

3 $a1 Gap 3

Start of ID field (see C.1.9)

1 $fe ID address mark (IDAM)

1 track # Track number

1 side # Head number (0 or 1)

1 sector # Sector number (0 to 25)

1 length code Sector length (see C.2)

continued on next page

Page 61

C.1. WD1770/1772 FLOPPY DISK CONTROLLER / FORMATTER 59

continued from previous page

# of bytes Value of Byte Comments

2 CRC END of ID field (see C.1.9)

22 $4e Gap 2

12 $00 Gap 2

During Write Sector commands the drive

starts writing at the beginning of this.

3 $a1 Gap 2

Start of data field (see C.1.9)

1 $fb Data Address Mark (DAM)

sector size data Values $f5 to $f7 are invalid.

(see C.1.9)

2 CRC End of data field.

(see C.1.9)

24 $4e Gap 4

During Write Sector Commands the drive

stops writing shortly after the beginning

of this.

sector size*2.5 $4e Continue writing until the 177x generates

an interrupt. The listed byte count is approximate.

Table C.13: Gap settings for non-standard formats

[Command Flow Diagrams left out]

Page 62

60 APPENDIX C. DATASHEETS

Page 63

C.2. SSM2300 OCTAL SAMPLE&HOLD 61

C.2 SSM2300 Octal Sample&Hold

Figure C.2: SSM2300 Octal Sample&Hold

Page 64

62 APPENDIX C. DATASHEETS

Page 65

C.3. MC/SN 2681 DUART 63

C.3 MC/SN 2681 DUART

Page 66

64 APPENDIX C. DATASHEETS

Page 67

C.3. MC/SN 2681 DUART 65

Philips Semiconductors Product specification

SCN2681

Dual asynchronous receiver/transmitter (DUART)

1

1995 May 1 853-1077 15179

DESCRIPTION

The Philips Semiconductors SCN2681 Dual Universal

Asynchronous Receiver/Transmitter (DUART) is a single-chip

MOS-LSI communications device that provides two independent

full-duplex asynchronous receiver/transmitter channels in a single

package. It interfaces directly with microprocessors and may be

used in a polled or interrupt driven system.

The operating mode and data format of each channel can be

programmed independently. Additionally, each receiver and

transmitter can select its operating speed as one of eighteen fixed

baud rates, a 16X clock derived from a programmable counter/timer,

or an external 1X or 16X clock. The baud rate generator and

counter/timer can operate directly from a crystal or from external

clock inputs. The ability to independently program the operating

speed of the receiver and transmitter make the DUART particularly

attractive for dual-speed channel applications such as clustered

terminal systems.

Each receiver is quadruply buffered to minimize the potential of

receiver over-run or to reduce interrupt overhead in interrupt driven

systems. In addition, a flow control capability is provided to disable

a remote DUART transmitter when the buffer of the receiving device

is full.