Page 1

User’s Manual

from Emerson Network Power

Embedded Computing

™

PmPPC7448: PowerPC™-Based Processor PMC Module

September 2007

Page 2

The information in this manual has been checked and is believed to be accurate and reliable. HOWEVER, NO RESPONSIBILITY IS ASSUMED BY EMERSON NETWORK POWER,

EMBEDDED COMPUTING FOR ITS USE OR FOR ANY INACCURACIES. Specifications are subject to change without notice. EMERSON DOES NOT ASSUME ANY LIABILITY ARISING OUT

OF USE OR OTHER APPLICATION OF ANY PRODUCT, CIRCUIT, OR PROGRAM DESCRIBED

HEREIN. This document does not convey any license under Emerson patents or the rights of

others.

Emerson. Consider It Solved is a trademark, and Business-Critical Continuity, Emerson Network Power, and the Emerson Network Power logo are trademarks and service marks of

Emerson Electric Co. © 2007 Emerson Electric Co.

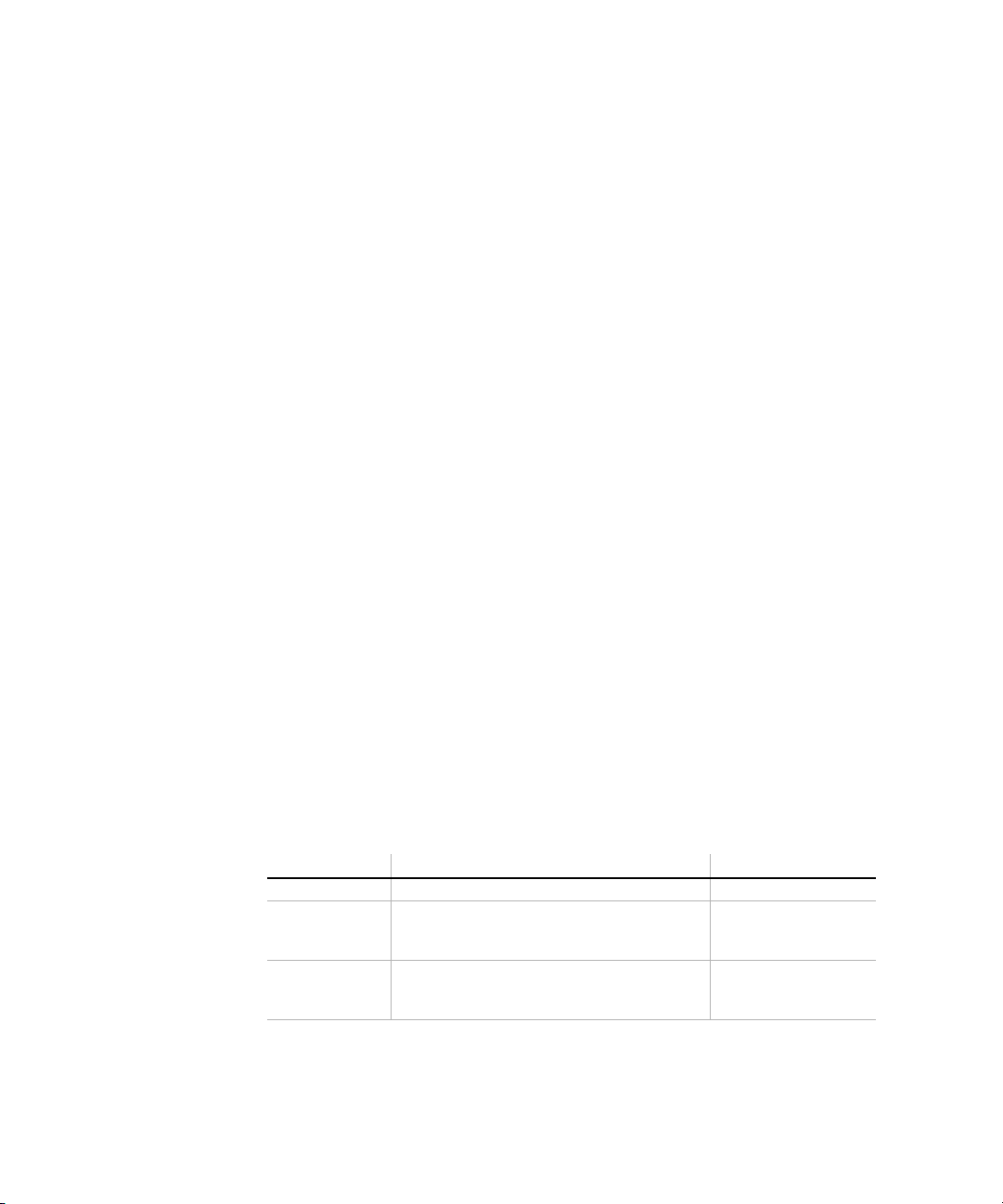

Revision Level: Principal Changes: Date:

10006757-00 Original release October 2005

10006757-01 Artwork stitch, added “RoHS Compliance”,

updated memory map and monitor (version

1.4), added “Internal SRAM”

10006757-02 Added caution for front panel reset switch;

updated “Monitor” chapter and environment

variables

Copyright © 2005-2007 Emerson Electric Co. All rights reserved.

June 2006

September 2007

Page 3

Regulatory Agency Warnings & Notices

!

!

The Emerson PmPPC7448 meets the requirements set forth by the Federal Communications Commission (FCC) in Title 47 of the Code of Federal Regulations. The following information is provided as required by this agency.

Thi s devi ce compli es wit h part 15 of the FCC Rules. Operation is subject to the following two

conditions: (1) This device may not cause harmful interference, and (2) this device must

accept any interference received, including interference that may cause undesired operation.

FCC RULES AND REGULATIONS — PART 15

This equipment has been tested and found to comply with the limits for a Class B digital

device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment

generates, uses and can radiate radio frequency energy and, if not installed and used in

accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception,

which can be determined by turning the equipment off and on, the user is encouraged to

try to correct the interference by one or more of the following measures:

• Reorient or relocate the receiving antenna

• Increase the separation between the equipment and receiver

• Connect the equipment into an outlet on a circuit different from that to which the

receiver is connected

• Consult the dealer or an experienced radio/TV technician for help

Caution: Making changes or modifications to the PmPPC7448 hardware without the explicit consent

of Emerson Network Power could invalidate the user’s authority to operate this equipment.

EMC COMPLIANCE

The electromagnetic compatibility (EMC) tests used a PmPPC7448 model that includes a

front panel assembly from Emerson Network Power.

Caution: For applications where the PmPPC7448 is provided without a front panel, or where the

front panel has been removed, your system chassis/enclosure must provide the required

electromagnetic interference (EMI) shielding to maintain EMC compliance.

10006757-02 PmPPC7448 User’s Manual

i

Page 4

Regulatory Agency Warnings & Notices (continued)

EC Declaration of Conformity

According to EN 45014:1998

Manufacturer’s Name: Emerson Network Power

Embedded Computing

Manufacturer’s Address: 8310 Excelsior Drive

Madison, Wisconsin 53717

Declares that the following product, in accordance with the requirements of 2004/108/EEC, EMC

Directive and 1999/5/EC, RTTE Directive and their amending directives,

Product: PowerPC™-Based Processor PMC Module

Model Name/Number: PmPPC7448/10005277-xx

has been designed and manufactured to the following specifications:

EN55022:1998 Information Technology Equipment, Radio disturbance characteristics, Limits and

methods of measurement

EN55024:1998 Information Technology Equipment, Immunity characteristics, Limits and methods

of measurement

EN300386 V.1.3.1 Electromagnetic compatibility and radio spectrum matters (ERM);

Telecommunication network equipment; EMC requirements

As manufacturer we hereby declare that the product named above has been designed to comply

with the relevant sections of the above referenced specifications. This product complies with the

essential health and safety requirements of the EMC Directive and RTTE Directive. We have an internal production control system that ensures compliance between the manufactured products and

the technical documentation.

Issue date: September 26, 2007

Bill Fleury

Compliance Engineer

ii

PmPPC7448 User’s Manual 10006757-02

Page 5

Contents

1Overview

Components and Features . . . . . . . . . . . 1-1

Functional Overview . . . . . . . . . . . . . . . . 1-3

Physical Memory Map . . . . . . . . . . . . . . . 1-4

Additional Information . . . . . . . . . . . . . . 1-6

Product Certification . . . . . . . . . . . . .1-6

UL Certification. . . . . . . . . . . . . . . . . .1-7

RoHS Compliance. . . . . . . . . . . . . . . .1-8

Terminology and Notation. . . . . . . .1-8

Technical References. . . . . . . . . . . . .1-8

2Setup

Electrostatic Discharge . . . . . . . . . . . . . . 2-1

PmPPC7448 Circuit Board. . . . . . . . . . . . 2-1

Connectors . . . . . . . . . . . . . . . . . . . . .2-4

LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

Front Panel . . . . . . . . . . . . . . . . . . . . . 2-6

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

PmPPC7448 Setup . . . . . . . . . . . . . . . . . . 2-8

Power Requirements. . . . . . . . . . . . .2-9

Environmental Considerations . . . . 2-9

Installing the Module. . . . . . . . . . . .2-10

Troubleshooting. . . . . . . . . . . . . . . . . . . 2-11

Technical Support . . . . . . . . . . . . . .2-12

Product Repair . . . . . . . . . . . . . . . . .2-13

3 Central Processing Unit

Processor Reset. . . . . . . . . . . . . . . . . . . . . 3-2

Processor Initialization. . . . . . . . . . . . . . . 3-2

Hardware Implementation Dependent

0 Register. . . . . . . . . . . . . . . . . . . . . . . 3-3

Hardware Implementation Dependent

1 Register. . . . . . . . . . . . . . . . . . . . . . . 3-5

Exception Handling . . . . . . . . . . . . . . . . . 3-6

Exception Processing. . . . . . . . . . . . . . . . 3-8

Machine State Register . . . . . . . . . . . 3-8

Cache Memory . . . . . . . . . . . . . . . . . . . . 3-10

L1 Cache. . . . . . . . . . . . . . . . . . . . . . .3-10

L2 Cache. . . . . . . . . . . . . . . . . . . . . . .3-11

4 On-Card Memory

Configuration

Boot Memory Configuration. . . . . . . . . . 4-1

User Flash. . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

On-Card SDRAM . . . . . . . . . . . . . . . . . . . . .4-2

NVRAM Allocation . . . . . . . . . . . . . . . . . . .4-2

5System Controller

CPU Interface . . . . . . . . . . . . . . . . . . . . . . .5-2

CPU Interface Registers . . . . . . . . . . 5-2

Memory Interface. . . . . . . . . . . . . . . . . . . .5-2

DDR SDRAM Controller . . . . . . . . . . 5-2

Internal SRAM. . . . . . . . . . . . . . . . . . . 5-3

Device Controller Interface. . . . . . . . . . . .5-3

Device Control Registers . . . . . . . . . 5-4

Internal (IDMA) Controller . . . . . . . . . . . .5-4

Timer/Counter . . . . . . . . . . . . . . . . . . 5-4

PCI Interface . . . . . . . . . . . . . . . . . . . . . . . .5-4

PCI Configuration Space. . . . . . . . . . 5-5

PCI Subsystem Device and Vendor ID

Assignment. . . . . . . . . . . . . . . . . . . . . 5-5

PCI Read/Write. . . . . . . . . . . . . . . . . . 5-5

PCI Interface Registers . . . . . . . . . . . 5-7

PCI Bus Control Signals . . . . . . . . . . . . . . .5-7

PMC Connector Pinouts . . . . . . . . . . . . 5-10

P11 and P12 Pin Assignments . . . . 5-10

P13 and P14 Pin Assignments . . . . 5-11

PMC Connector . . . . . . . . . . . . . . . . 5-12

Doorbell Registers . . . . . . . . . . . . . . . . . 5-13

Outbound Doorbells . . . . . . . . . . . . 5-13

Inbound Doorbells. . . . . . . . . . . . . . 5-13

Monarch Functionality . . . . . . . . . . . . . 5-13

66 MHz Bus Operation. . . . . . . . . . . . . . 5-14

Watchdog Timer . . . . . . . . . . . . . . . . . . 5-14

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

6 Ethernet Interface

MV64460 Ethernet Registers. . . . . . . . . .6-1

Ethernet Address . . . . . . . . . . . . . . . . . . . .6-2

Ethernet Connection (P1). . . . . . . . . . . . .6-2

7CPLD

Reset Registers . . . . . . . . . . . . . . . . . . . . . .7-1

Reset Event Register (RER). . . . . . . . 7-1

Reset Command Register (RCR) . . . 7-1

PCI Reset Out Enable Register (ROER).

7-2

Interrupt Registers. . . . . . . . . . . . . . . . . . .7-3

Interrupt Enable Register (IER) . . . . 7-4

10006757-02 PmPPC7448 User’s Manual

iii

Page 6

Contents (continued)

Interrupt Pending Register (IPR) . . . 7-4

Product ID Register (PIR). . . . . . . . . . . . . .7-5

EReady Register (ERdy) . . . . . . . . . . . . . . .7-5

Revision Registers . . . . . . . . . . . . . . . . . . .7-5

Hardware Version Register (HVR) . . 7-6

PLD Version Register (PVR) . . . . . . . 7-6

Board Configuration Registers. . . . . . . . .7-6

8 Serial Input/Output

Multi-Protocol Serial Controllers (MPSC)8-1

Serial DMA (SDMA) Channels. . . . . . . . . .8-1

Programmable Baud Rate. . . . . . . . . . . . .8-1

BRGx Configuration Register . . . . . .8-1

BRGx Tuning Register . . . . . . . . . . . .8-2

I2C Interface . . . . . . . . . . . . . . . . . . . . . . . .8-2

I/O Connection . . . . . . . . . . . . . . . . . . . . . .8-2

9 Real-Time Clock

Block Diagram. . . . . . . . . . . . . . . . . . . . . . .9-1

Operation. . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

Clock Operation . . . . . . . . . . . . . . . . . . . . .9-2

10Development Mezzanine

Card

DMC Circuit Board . . . . . . . . . . . . . . . . . 10-1

Serial Numbers . . . . . . . . . . . . . . . . .10-2

Connectors . . . . . . . . . . . . . . . . . . . . . . . 10-3

P1 Connector Pin Assignments . . . 10-3

P2 EIA-232 Interface . . . . . . . . . . . .10-6

PmPPC7448 to DMC JTAG . . . . . . . . . . 10-7

P3 JTAG/COP. . . . . . . . . . . . . . . . . . .10-7

P4 JTAG Chain Header . . . . . . . . . . .10-8

DMC Jumpers (JP1). . . . . . . . . . . . . . . . . 10-9

Jumper Setting Register . . . . . . . .10-10

Debug/Status LEDs . . . . . . . . . . . . . . . 10-10

DMC Setup. . . . . . . . . . . . . . . . . . . . . . . 10-11

Installing the DMC Card . . . . . . . .10-11

Troubleshooting. . . . . . . . . . . . . . . . . . 10-13

Technical Support . . . . . . . . . . . . .10-13

Product Repair . . . . . . . . . . . . . . . .10-13

11Monitor

Command-Line Features. . . . . . . . . . . . 11-1

Basic Operation. . . . . . . . . . . . . . . . . . . . 11-2

Power-up/Reset Sequence . . . . . . 11-2

POST Diagnostic Results . . . . . . . . 11-4

Monitor SDRAM Usage. . . . . . . . . . 11-4

Monitor Recovery and Updates . . . . . . 11-4

Recovering the Monitor . . . . . . . . . 11-4

Updating the Monitor via TFTP . . . 11-5

Restoring the PmPPC7448 Monitor

Using the KatanaQP . . . . . . . . . . . . 11-6

Resetting Environment Variables . 11-7

Accessing the Console Over Ethernet. 11-8

Monitor Command Reference . . . . . . . 11-8

Command Syntax . . . . . . . . . . . . . . 11-9

Command Help . . . . . . . . . . . . . . . . 11-9

Typographic Conventions . . . . . . . 11-9

Boot Commands . . . . . . . . . . . . . . . . . . 11-9

bootd . . . . . . . . . . . . . . . . . . . . . . . . . 11-9

bootelf. . . . . . . . . . . . . . . . . . . . . . .11-10

bootm . . . . . . . . . . . . . . . . . . . . . . .11-10

bootp . . . . . . . . . . . . . . . . . . . . . . . .11-10

bootv . . . . . . . . . . . . . . . . . . . . . . . .11-10

bootvx . . . . . . . . . . . . . . . . . . . . . . . 11-10

dhcp. . . . . . . . . . . . . . . . . . . . . . . . . 11-11

rarpboot . . . . . . . . . . . . . . . . . . . . . 11-11

tftpboot. . . . . . . . . . . . . . . . . . . . . . 11-11

Memory Commands . . . . . . . . . . . . . . 11-11

cmp . . . . . . . . . . . . . . . . . . . . . . . . . 11-11

cp . . . . . . . . . . . . . . . . . . . . . . . . . . .11-12

find . . . . . . . . . . . . . . . . . . . . . . . . . .11-12

md . . . . . . . . . . . . . . . . . . . . . . . . . . 11-12

mm. . . . . . . . . . . . . . . . . . . . . . . . . . 11-13

nm . . . . . . . . . . . . . . . . . . . . . . . . . . 11-13

mw . . . . . . . . . . . . . . . . . . . . . . . . . .11-13

Flash Commands . . . . . . . . . . . . . . . . . 11-14

cp . . . . . . . . . . . . . . . . . . . . . . . . . . .11-14

erase . . . . . . . . . . . . . . . . . . . . . . . . 11-14

flinfo. . . . . . . . . . . . . . . . . . . . . . . . . 11-14

protect. . . . . . . . . . . . . . . . . . . . . . . 11-15

EEPROM/I2C Commands . . . . . . . . . . 11-15

eeprom . . . . . . . . . . . . . . . . . . . . . . 11-15

icrc32. . . . . . . . . . . . . . . . . . . . . . . .11-16

iloop. . . . . . . . . . . . . . . . . . . . . . . . .11-16

imd . . . . . . . . . . . . . . . . . . . . . . . . . .11-16

imm . . . . . . . . . . . . . . . . . . . . . . . . .11-16

imw . . . . . . . . . . . . . . . . . . . . . . . . .11-16

inm . . . . . . . . . . . . . . . . . . . . . . . . . .11-16

iprobe . . . . . . . . . . . . . . . . . . . . . . .11-16

Environment Parameter Commands 11-17

printenv. . . . . . . . . . . . . . . . . . . . . .11-17

iv

PmPPC7448 User’s Manual 10006757-02

Page 7

Contents (continued)

saveenv . . . . . . . . . . . . . . . . . . . . . .11-17

setenv. . . . . . . . . . . . . . . . . . . . . . . .11-17

Test Commands . . . . . . . . . . . . . . . . . . 11-17

diags . . . . . . . . . . . . . . . . . . . . . . . . .11-18

mtest . . . . . . . . . . . . . . . . . . . . . . . .11-18

um. . . . . . . . . . . . . . . . . . . . . . . . . . .11-18

Other Commands. . . . . . . . . . . . . . . . . 11-18

autoscr . . . . . . . . . . . . . . . . . . . . . . .11-18

base . . . . . . . . . . . . . . . . . . . . . . . . .11-18

bdinfo. . . . . . . . . . . . . . . . . . . . . . . .11-18

coninfo. . . . . . . . . . . . . . . . . . . . . . .11-18

crc32. . . . . . . . . . . . . . . . . . . . . . . . .11-19

date. . . . . . . . . . . . . . . . . . . . . . . . . .11-19

echo . . . . . . . . . . . . . . . . . . . . . . . . .11-19

enumpci. . . . . . . . . . . . . . . . . . . . . .11-19

getmonver. . . . . . . . . . . . . . . . . . . .11-19

go . . . . . . . . . . . . . . . . . . . . . . . . . . .11-19

help. . . . . . . . . . . . . . . . . . . . . . . . . .11-20

iminfo. . . . . . . . . . . . . . . . . . . . . . . .11-20

isdram . . . . . . . . . . . . . . . . . . . . . . .11-20

loop . . . . . . . . . . . . . . . . . . . . . . . . . 11-20

memmap . . . . . . . . . . . . . . . . . . . . 11-20

moninit . . . . . . . . . . . . . . . . . . . . . . 11-20

pci. . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

ping . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

reset. . . . . . . . . . . . . . . . . . . . . . . . . 11-21

run . . . . . . . . . . . . . . . . . . . . . . . . . .11-21

script . . . . . . . . . . . . . . . . . . . . . . . . 11-22

showmac. . . . . . . . . . . . . . . . . . . . .11-22

showpci . . . . . . . . . . . . . . . . . . . . . . 11-22

sleep. . . . . . . . . . . . . . . . . . . . . . . . . 11-22

version. . . . . . . . . . . . . . . . . . . . . . . 11-22

Environment Variables . . . . . . . . . . . . 11-22

Troubleshooting. . . . . . . . . . . . . . . . . . 11-25

Download Formats. . . . . . . . . . . . . . . . 11-25

Binary. . . . . . . . . . . . . . . . . . . . . . . .11-25

Motorola S-Record . . . . . . . . . . . . 11-25

12Acronyms

10006757-02 PmPPC7448 User’s Manual

v

Page 8

(blank page)

vi

PmPPC7448 User’s Manual 10006757-02

Page 9

Figures

Figure 1-1: General System Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Figure 1-2: PmPPC7448 Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Figure 2-1: Component Map, Top (Rev. 06) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2: Component Map, Bottom (Rev. 06). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Figure 2-3: LED Locations, Bottom . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Figure 2-4: Front Panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Figure 2-5: Reset Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 2-6: Module Location on Emerson CC1000-DM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Figure 2-7: Installing the Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Figure 2-8: Serial Number and Product ID on Bottom Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Figure 3-1: MPC7448 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Figure 5-1: MV64460 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Figure 5-2: PCI Device and Vendor ID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Figure 5-3: Example PCI0 Address Map, Monarch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Figure 5-4: Example PCI0 Address Map, Non-Monarch (Default) . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Figure 5-5: PCI JTAG Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Figure 5-6: PMC Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Figure 6-1: Front Panel Ethernet Connector (P1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Figure 6-2: Ethernet Cable Assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Figure 8-1: Front Panel Serial Port Connector (P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

Figure 8-2: Serial Cable Assembly (Emerson Part Number C0007662-00) . . . . . . . . . . . . . . . . . . . 8-3

Figure 9-1: M41T00 Real-Time Clock Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

Figure 10-1: DMC Component Maps, Top and Bottom (Revision 01) . . . . . . . . . . . . . . . . . . . . . . . 10-2

Figure 10-2: DMC P1 PCB-to-PCB Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

Figure 10-3: DMC P2 Mini-USB Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-6

Figure 10-4: PmPPC7448 to DMC JTAG Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-7

Figure 10-5: DMC P3 JTAG/COP Header. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-7

Figure 10-6: DMC P4 JTAG Chain Header. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

Figure 10-7: DMC JP1 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

Figure 10-8: DMC Location on PmPPC7448 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

Figure 11-1: Example Monitor Start-up Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

Figure 11-2: Power-up/Reset Sequence Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

10006757-02 PmPPC7448 User’s Manual

vii

Page 10

(blank page)

viii

PmPPC7448 User’s Manual 10006757-02

Page 11

Tables

Table 1-1: Address Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Table 1-2: Regulatory Agency Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Table 1-3: Technical References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Table 2-1: Circuit Board Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Table 2-2: Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Table 2-3: Environmental Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Table 3-1: PmPPC7448 CPU Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Table 3-2: CPU Internal Register Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table 3-3: MPC7448 Exception Priorities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Table 4-1: Memory Configuration Jumper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-2: Flash Memory Configurations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-3: NVRAM Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Table 5-1: P11/P12 Pin Assignments—32-Bit PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Table 5-2: P13/P14 Pin Assignments—64-Bit PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Table 6-1: Ethernet Port Address Numbering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Table 6-2: Front Panel Ethernet Pin Assignments (P1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Table 6-3: Ethernet Cable Wiring Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Table 8-1: I2C Device Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

Table 8-2: Front Panel Serial Port Pin Assignments (P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

Table 8-3: Serial Cable Wiring Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

Table 9-1: RTC Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

Table 10-1: DMC Mechanical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

Table 10-2: DMC P1 Connector Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

Table 10-3: DMC P2 Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-6

Table 10-4: DMC P3 Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

Table 10-5: DMC P4 Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

Table 11-1: POST Diagnostic Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4

Table 11-2: Standard Environment Variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-22

Table 11-3: Optional Environment Variables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-24

10006757-02 PmPPC7448 User’s Manual

ix

Page 12

(blank page)

x

PmPPC7448 User’s Manual 10006757-02

Page 13

Registers

Register 3-1: MPC7448 Hardware Implementation Dependent, HID0. . . . . . . . . . . . . . . . . . . . . . . . 3-3

Register 3-2: MPC7448 Hardware Implementation Dependent, HID1. . . . . . . . . . . . . . . . . . . . . . . . 3-5

Register 3-3: CPU Machine State Register (MSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Register 3-4: L2 Cache Control Register (L2CR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Register 7-1: Reset Event Register (RER) at 0xf820,0000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Register 7-2: Reset Command Register (RCR) at 0xf820,1000. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Register 7-3: Reset Out Enable Register (ROER) at 0xf820,e000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Register 7-4: PmPPC7448 Interrupt Enable Register (IER) at 0xf820,2000 . . . . . . . . . . . . . . . . . . . . 7-4

Register 7-5: PmPPC7448 Interrupt Pending Register (IPR) at 0xf820,3000 . . . . . . . . . . . . . . . . . . . 7-4

Register 7-6: PmPPC7448 Product ID Register (PIR) at 0xf820,4000 . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Register 7-7: PmPPC7448 ERdy Register (ERdy) at 0xf820,5000. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Register 7-8: Hardware Version Register (HVR) at 0xf820,7000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Register 7-9: PLD Version Register (PVR) at 0xf820,8000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Register 7-10: PmPPC7448 Board Configuration 3 (BCR3) at 0xf820,c000 . . . . . . . . . . . . . . . . . . . . . 7-6

Register 7-11: PmPPC7448 Board Configuration 1 (BCR1) at 0xf820,a000 . . . . . . . . . . . . . . . . . . . . . 7-7

Register 7-12: PmPPC7448 Board Configuration 0 (BCR0) at 0xf820,9000 . . . . . . . . . . . . . . . . . . . . . 7-7

Register 10-1: DMC Jumper Setting Register at 0xf820,6000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10

Register 10-2: DMC LED Register at 0xf820,d000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10

10006757-02 PmPPC7448 User’s Manual

xi

Page 14

(blank page)

xii

PmPPC7448 User’s Manual 10006757-02

Page 15

Overview

The Emerson PmPPC7448 module is a Processor PCI Mezzanine Card (PPMC). It is based on

the Freescale® Semiconductor PowerPC™ MPC7448 central processor unit and provides

additional processing power for the baseboard, which must be compatible with PPMC

architecture. The PmPPC7448 module supports various memory configurations, programmable user Flash memory, a PCI bridge/controller, three Ethernet interfaces, two serial

ports, as well as a real-time clock, and EEPROM.

COMPONENTS AND FEATURES

The following is a brief summary of the PmPPC7448 hardware components and features:

CPU: The Freescale MPC7448 RISC PowerPC microprocessor has an internal speed of up to 1.4

GHz and 166 MHz local bus speed. The MPC7448 includes 32 kilobytes separate level-one

(L1) data and instruction caches and 1 megabyte L2 cache. Standard power supply is 3.3

volts, with a configuration option for both 3.3 and 5 volts.

System Controller/PCI Bridge:

Section 1

The Marvell® MV64460 (Discovery™III) is a single-chip solution that provides one PCI-X

bus, three integrated gigabit Ethernet Medium Access Control (MAC) controllers, twomegabit integrated Synchronous Random Access Memory (SRAM), four Independent

Direct Memory Access (IDMA) engines and two XOR Direct Memory Access (DMA) engines.

The 64-bit PCI interface can operate up to 66 MHz (60X) or 133 MHz (PCI-X).

SDRAM: The PmPPC7448 includes a 32M x 72-bit Double Data Rate (DDR) Synchronous Dynamic

Random Access Memory (SDRAM) Small-Outline Dual In-line Memory Module (SO-DIMM).

Options include 256 megabytes, 512 megabytes, 1 gigabyte, and 2 gigabytes. The interface implements eight additional bits to permit the use of error-correcting code (ECC). The

MV64460 bridge acts as the memory controller.

Flash: The PmPPC7448 includes Flash configuration options of 32 or 64 megabytes. The

PmPPC7448 is capable of booting from either an 8-bit, 32-pin PLCC ROM socket on the

Development Mezzanine Card (DMC) or from 32-bit soldered Flash (default).

Serial I/O: The PmPPC7448 includes up to two EIA-232 ports operating between 9600 and 115,200

baud. Serial port one is always routed to the Development Mezzanine Card (DMC) serial

connector; build options include connections to the front panel serial connector, or the P14

connector. When routed to P14, the port has the option of either EIA-232 or TTL signaling

levels. Serial port two is routed to P14 with the same signaling options.

Ethernet: The PmPPC7448 includes three Ethernet ports. Two Broadcom BCM5461S gigabit PHY

devices route Ethernet (ports 0 and 1) through connector P14. The Micrel KSZ8721CL

10/100 PHY device routes Ethernet (port 2) through a mini-USB connector on the front

panel. The Broadcom and Micrel devices are IEEE 802.3-compliant.

10006757-02 PmPPC7448 User’s Manual

1-1

Page 16

Overview: Components and Features

Note: GbE ports (0 and 1) are routed through the PHYs directly to connector P14. Therefore, magnetics are

required on the Rear Transition Module (RTM) or baseboard.

CPLD: The PmPPC7448 uses a Complex Programmable Logic Device (CPLD) to implement various

memory-mapped registers and to control access to the Flash, ROM socket, and enumeration of Monarch/non-Monarch systems.

RTC: The real-time clock is an ST®Microelectronics M41T00 Serial Access Timekeeper®.

Development Mezzanine Card (DMC):

The DMC is a custom, optional plug-on card mounted on the back of the PmPPC7448. This

card facilitates hardware and software development. See Chapter 10.

1-2

PmPPC7448 User’s Manual 10006757-02

Page 17

Overview: Functional Overview

Motorola

MPC7448

Microprocessor

Flash

32/64 MB

10/100

Magnetics

10/100

PHY

GbE

PHY

GbE

PHY

Device

CPLD

EIA-232

Tranceivers

Marvell

Config.

SEEPROM

NVRAM

SEEPROM

8 KB

ST Micro

M41T00

RTC

DDR SDRAM

256 MB, 512 MB,

1 GB, 2 GB

SROM

P11

P12

P13

P14

512 K

Socketed

Flash

COP Debug

Jumpers

PLD JTAG

LEDs (4)

Development

Mezzanine Card

(DMC)

MPX Bus

up to 166 MHz

DMC Connector

MII

Device Bus

MPP Bits

DRAM Bus

133 MHz

Mini USB

Connector

Marvell

MV64460

System

Controller

Port 2

(portdbg)

Port 1

(portb)

Port 0

(porta)

GMII

GMII

Serial1

Serial2

I2C

PCI 0

1.1 V

Supply

1.25 V

Supply

1.8 V

Supply

1.5 V

Supply

2.5 V

Supply

3.3 V

Supply

Mini-USB

P2

Mini-USB

P1

Front Panel

PCI/PCI-X 64-bit PMC

(3.3 V only)

GPIO

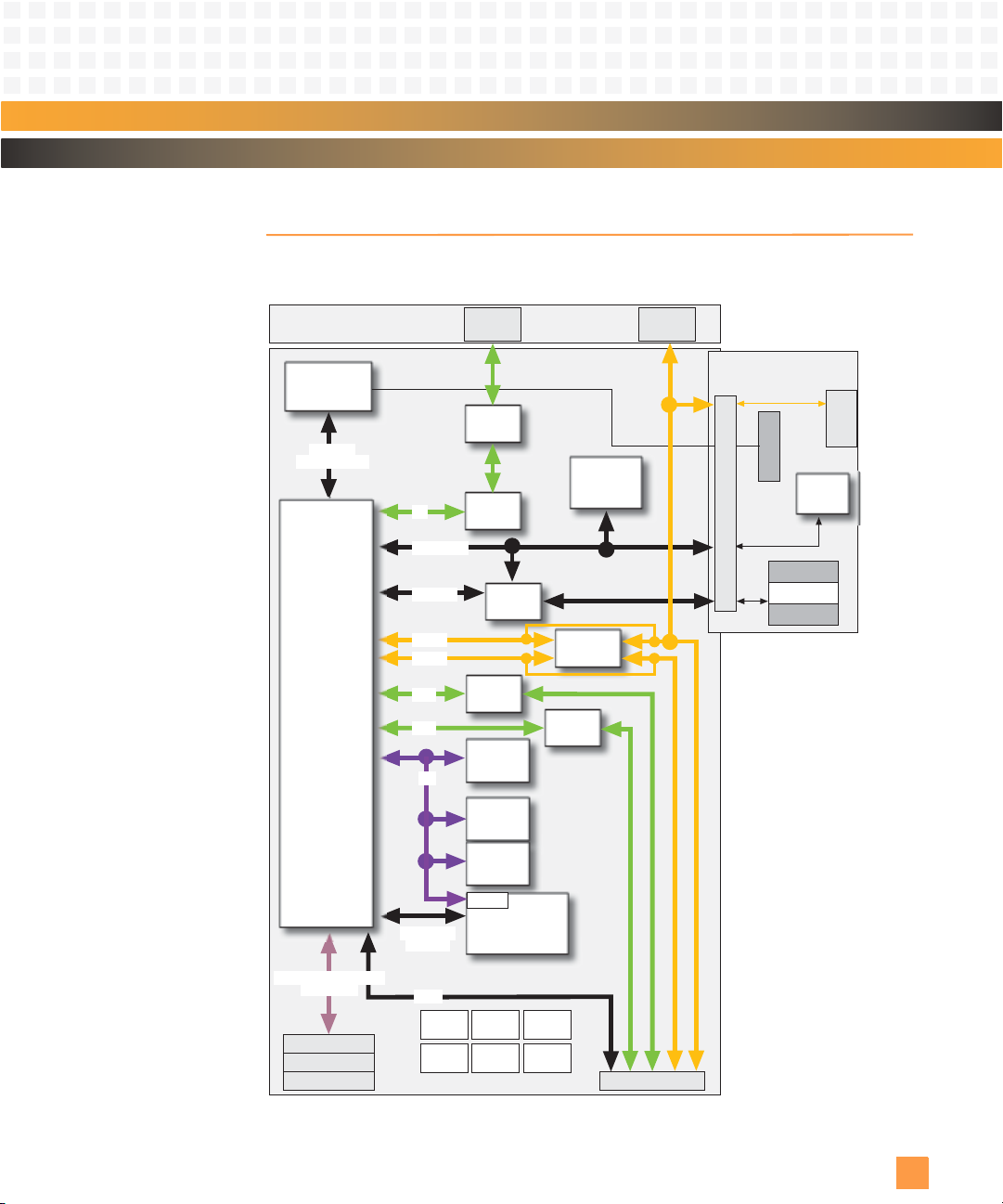

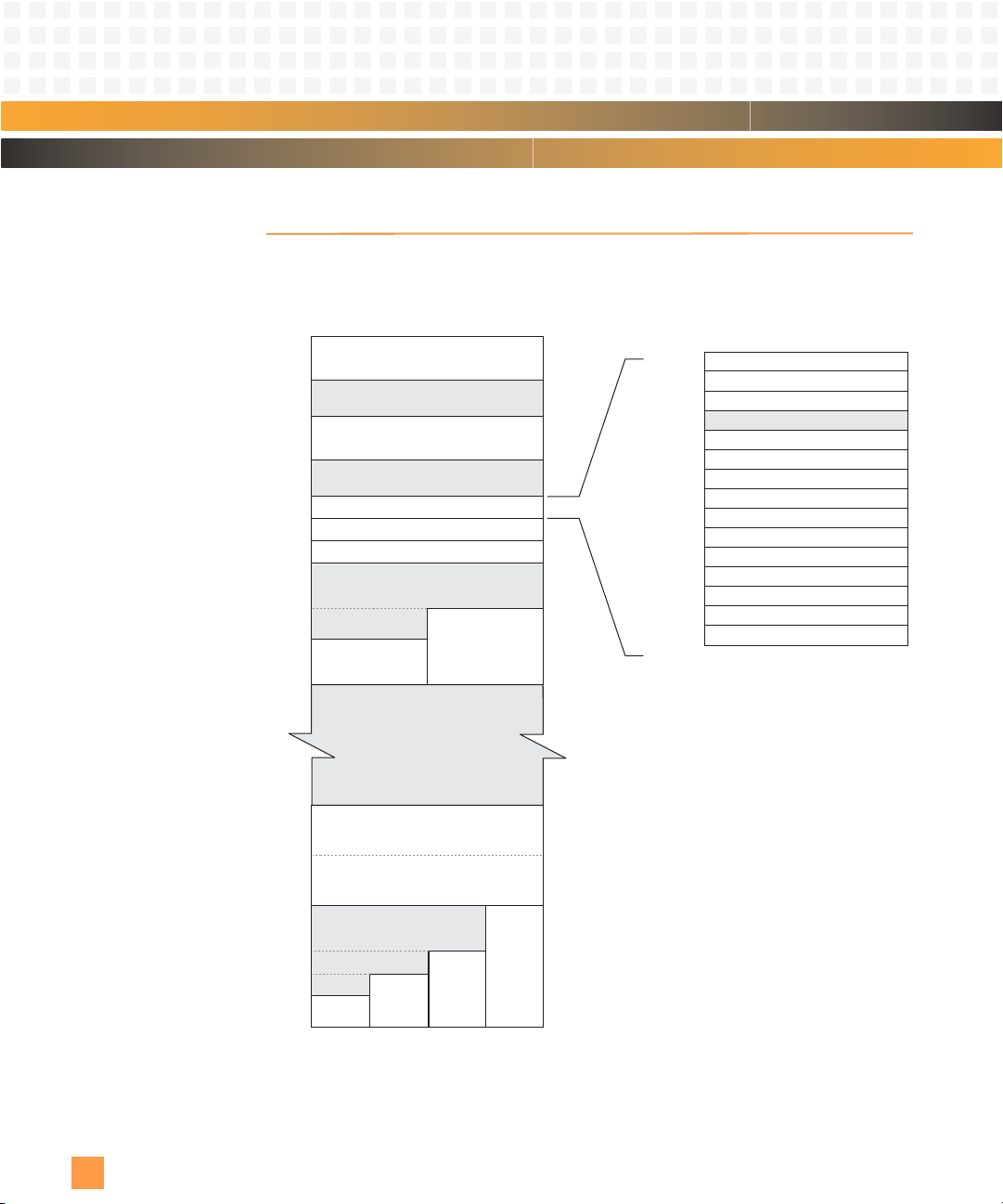

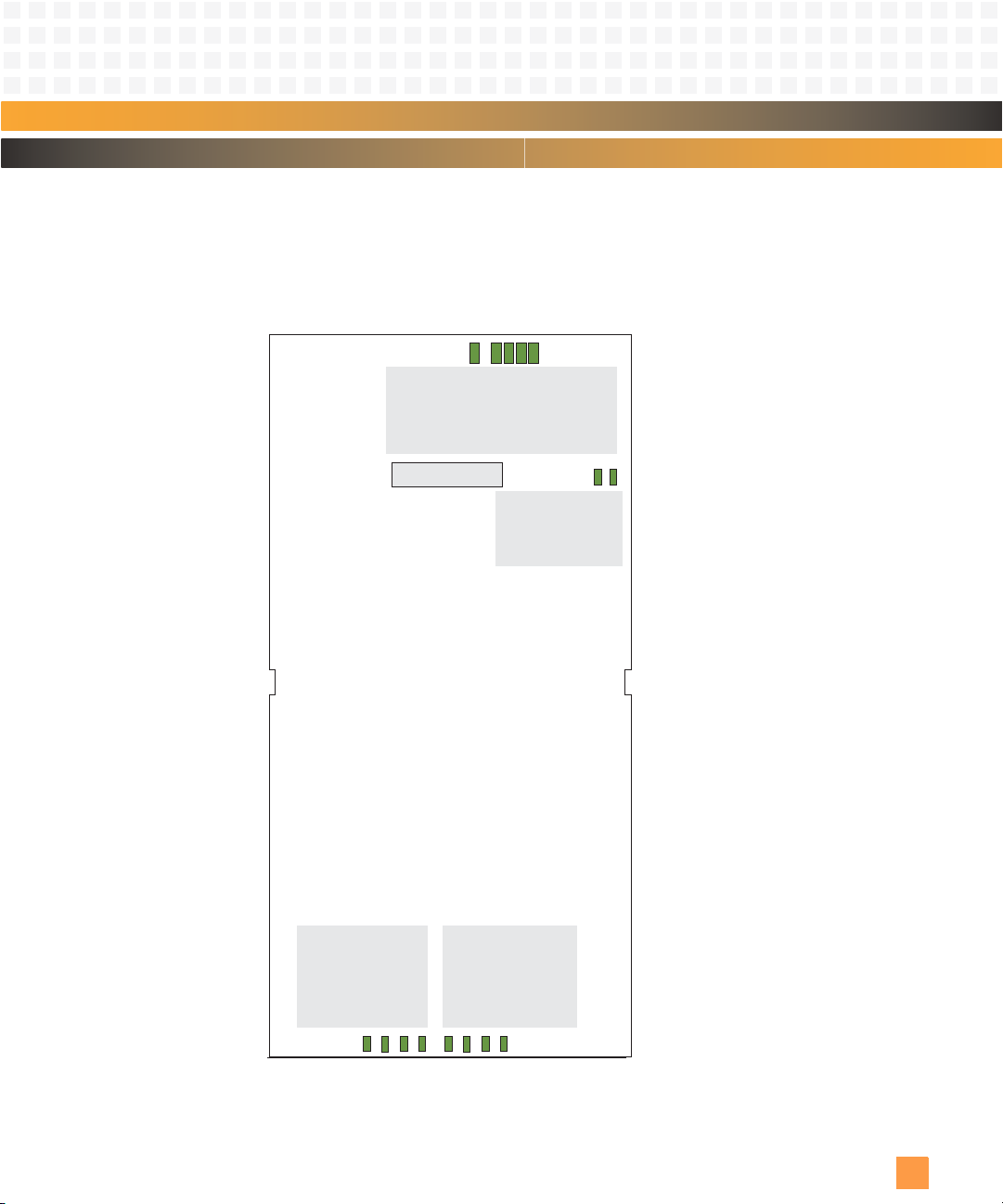

FUNCTIONAL OVERVIEW

The following block diagram provides a functional overview for the PmPPC7448:

Figure 1-1: General System Block Diagram

10006757-02 PmPPC7448 User’s Manual

1-3

Page 18

8000,0000

C000,0000

F810,0000

E800,0000

F800,0000

E9FF,FFFF

EBFF,FFFF

F820,0000

F830,0000

FFFF,FFFF

Hex Address

0000,0000

PCI 0

Memory

I/O

MV64460

CPLD

ROM Socket

Boot Mirror

Reserved

Reserved

Flash

32 MB

Flash

64 MB

FF80,0000

Hex Address

F820,0000

Board Configuration Register 3

Reset Event Register

Reset Command Register

Interrupt Enable Register

Board Configuration Register 0

Board Configuration Register 1

DMC LED Register

PLD Version Register

Hardware Version Register

Jumper Settings Register

EREADY Register

Product ID Register

F820,1000

F820,2000

F820,4000

F820,5000

F820,6000

F820,7000

F820,8000

F820,9000

F820,A000

F820,B000

F820,C000

F820,D000

F820,E000

PCI Reset Out Enable Register

Reserved

Reserved

MV64460 SRAM

F850,0000

F854,0000

Interrupt Pending Register

F820,3000

SDRAM

256 MB

SDRAM

512 MB

SDRAM

1 GB

0FFF,FFFF

1FFF,FFFF

3FFF,FFFF

Reserved

B000,0000

Reserved

SDRAM

2 GB

Overview: Physical Memory Map

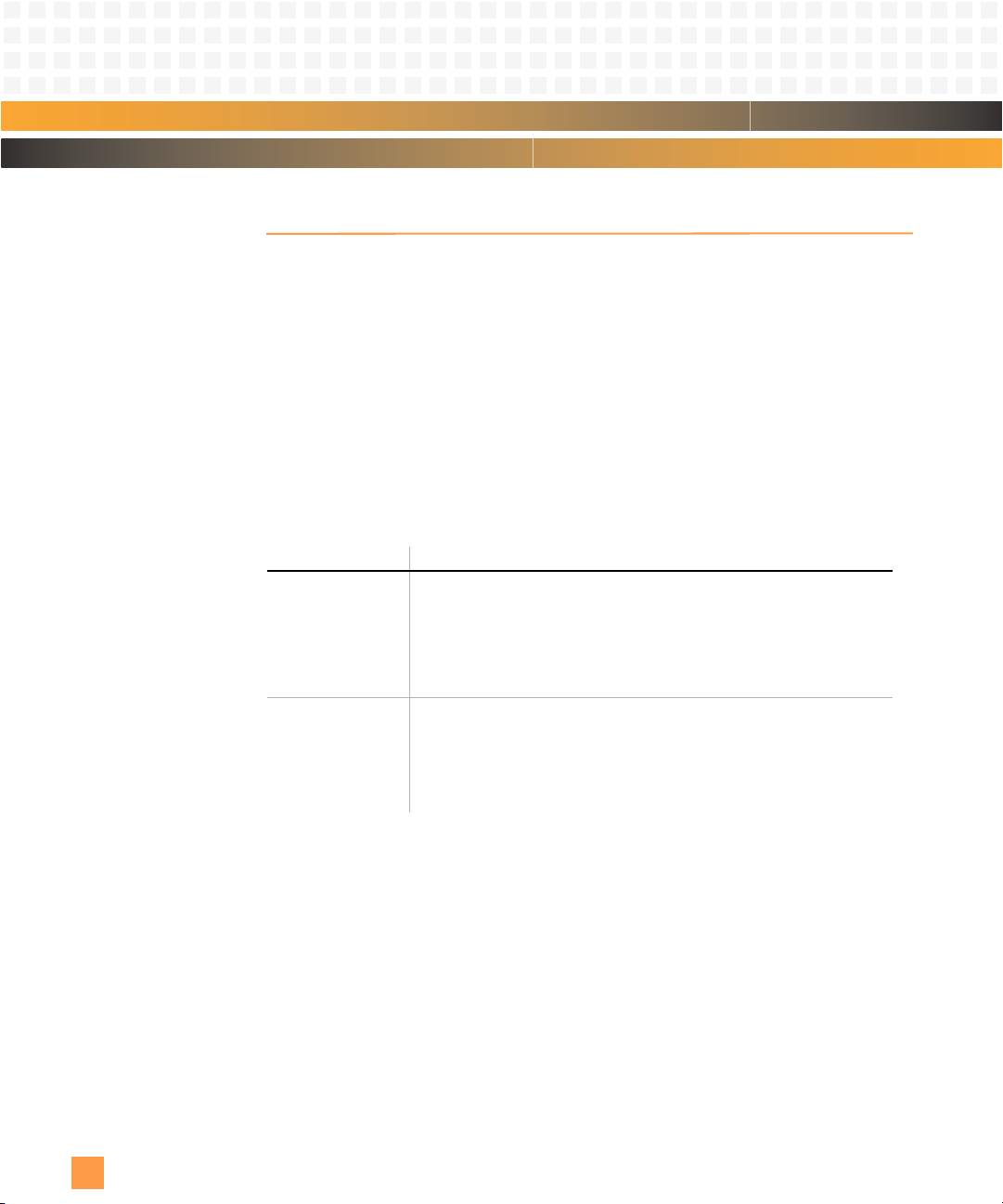

PHYSICAL MEMORY MAP

Fig. 1-1 illustrates the PmPPC7448 memory map:

Figure 1-2: PmPPC7448 Memory Map

1-4

PmPPC7448 User’s Manual 10006757-02

Page 19

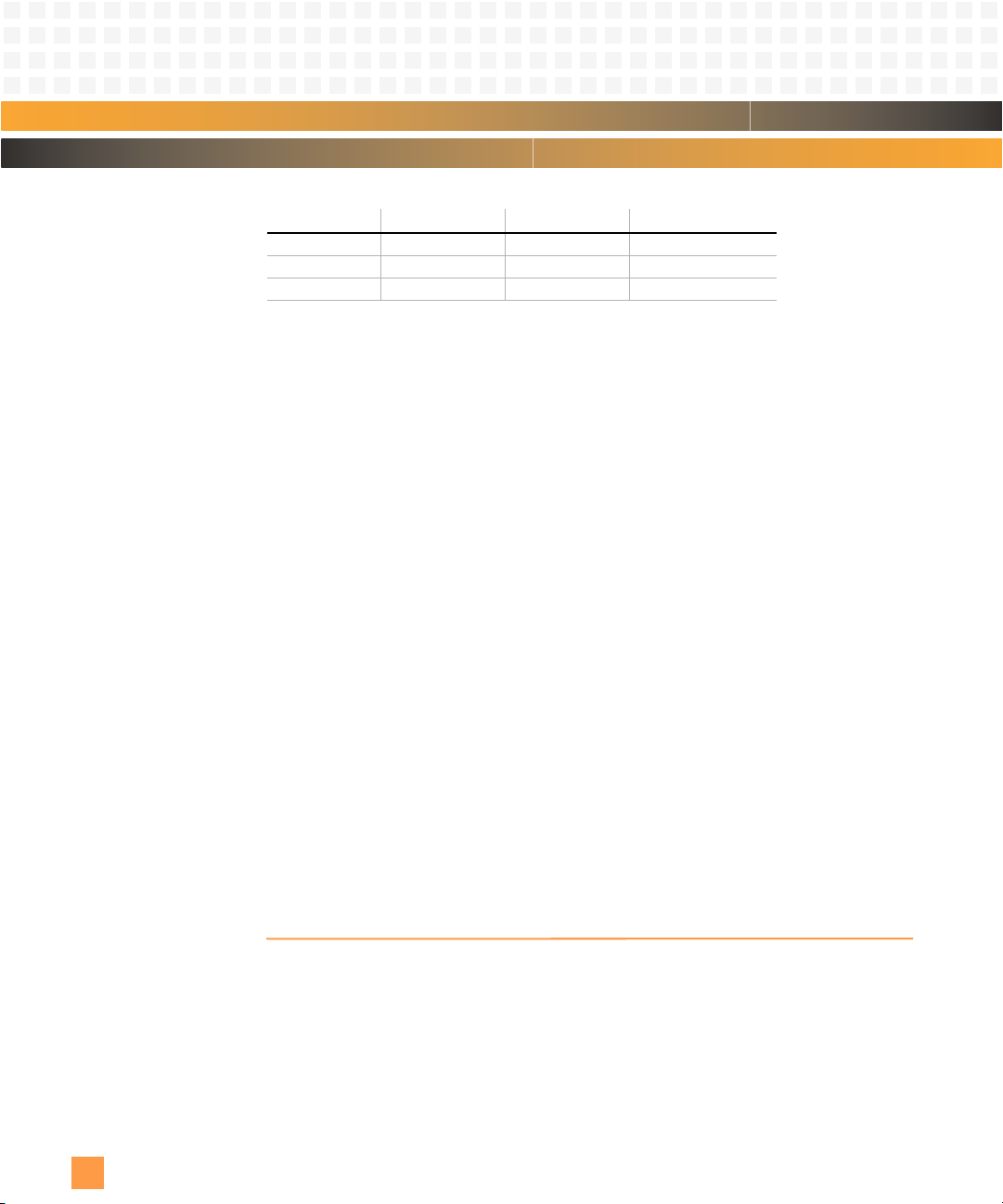

Overview: Physical Memory Map

Table 1-1 summarizes the physical addresses for the PmPPC7448 and provides a reference

to more detailed information:

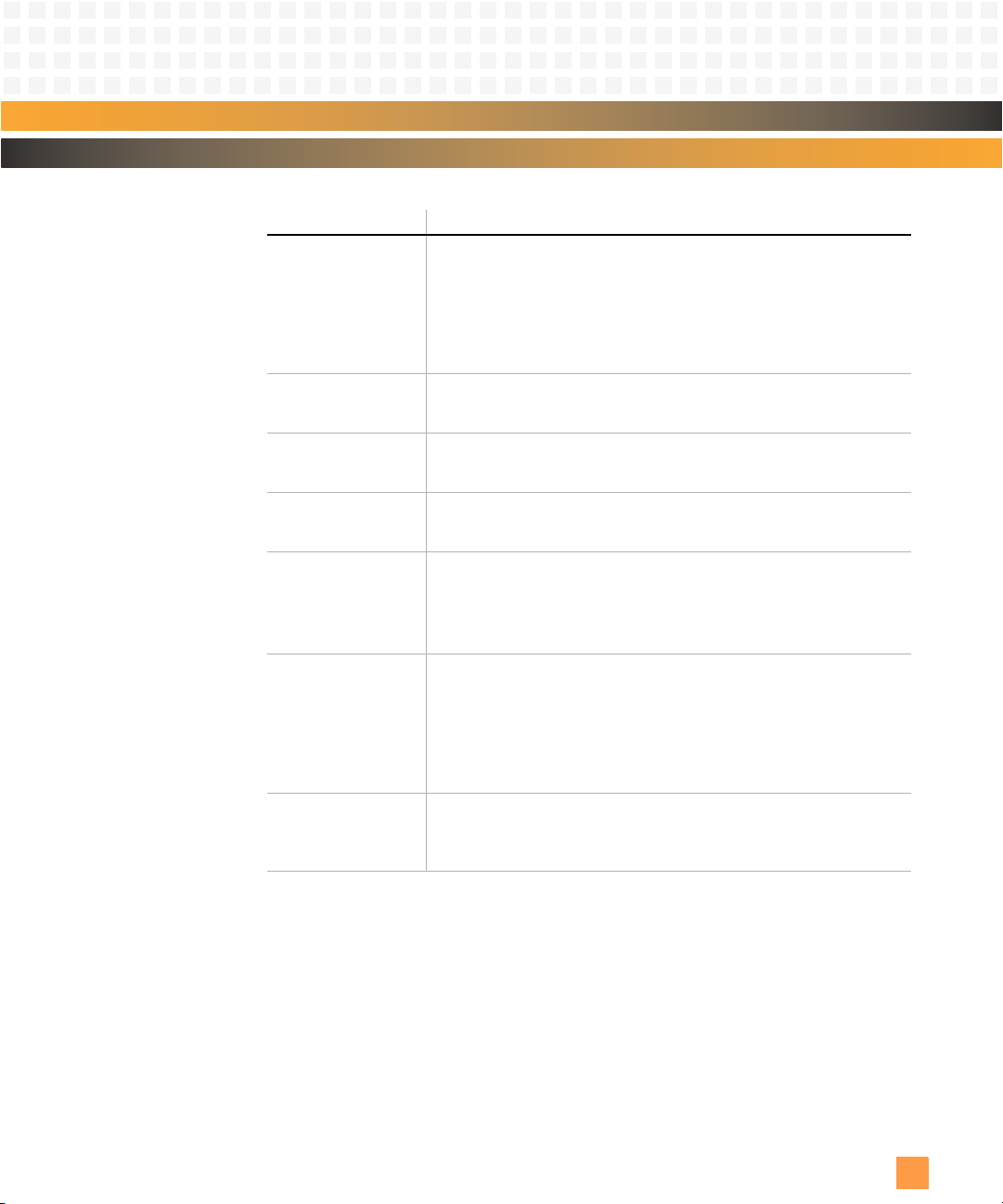

Table 1-1: Address Summary

Hex Physical

Address:

FF80,0000 R/W Boot Mirror –

FF80,0000 R/W Boot Mirror –

F854,0000 – Reserved –

F850,0000 MV64460 SRAM 5-3

F830,0000 – Reserved –

F820,E000 R/W PCI Reset Out Enable register 7-2

F820,D000 W DMC LED register 10-10

F820,C000 R Board Configuration register 3 (BCR3) 7-6

F820,B000 – Reserved (BCR2) –

F820,A000 R/W Board Configuration register 1 (BCR1) 7-6

F820,9000 R Board Configuration register 0 (BCR0) 7-6

F820,8000 R PLD Version register (PVR) 7-6

F820,7000 R Hardware Version register (HVR) 7-6

F820,6000 R Jumper Settings register (JSR) 10-10

F820,5000 R/W

F820,4000 R Product ID register (PIR) 7-5

F820,3000 R/W Interrupt Pending register (IPR) 7-4

F820,2000 R/W Interrupt Enable register (IER) 7-4

F820,1000 W Reset Command register (RCR) 7-2

F820,0000 R Reset Event register (RER) 7-1

F820,0000 R/W CPLD 7-1

F810,0000 R/W MV64460 5-5

F800,0000 R/W ROM Flash Socket 4-1

EBFF,FFFF – Reserved

E800,0000 R/W Flash (32 MB, 64 MB) 4-1, 11-14

C000,0000 – Reserved –

8000,0000 R/W PCI 0 — Memory and I/O Space 5-4

0000,0000 R/W SDRAM (256 MB, 512 MB, 1 GB, 2 GB) 4-2

Access

Mode: Description: See Page:

11

EReady (ERdy) register 7-5

2

–

1.If Monarch, read only; if non-Monarch, write only.

2.Depends on Flash size.

10006757-02 PmPPC7448 User’s Manual

1-5

Page 20

Overview: Additional Information

ADDITIONAL INFORMATION

This section lists the PmPPC7448 hardware regulatory certifications and briefly discusses

the terminology and notation conventions used in this manual. It also lists general technical

references.

Mean time between failures (MTBF) has been calculated at 309,632 hours using Telcordia

Issue 1 Method I Case 3.

Product Certification

The PmPPC7448 hardware has been tested to comply with various safety, immunity, and

emissions requirements as specified by the Federal Communications Commission (FCC),

Industry Canada (IC), Underwriters Laboratories (UL), and the European Union Directives

(CE mark). The following table summarizes this compliance:

Table 1-2: Regulatory Agency Compliance

Type: Specification:

Safety UL60950-1, CSA C22.2 No. 60950-1-03, 1st Edition – Safety of

Information Technology Equipment, including Electrical Business

Equipment (Bi-National)

IEC60950/EN60950 – Safety of Information Technology Equipment

(Western Europe)

AS/NZS 60950– Safety Standard for Australia and New Zealand

Environmental NEBS: Telcordia GR-63 –

Section 4.1 Transportation and Storage

Section 4.3 Equipment Handling

Section 4.4.3 Office Vibration

Section 4.4.4 Transportation Vibration

Section 4.5 Airborne Contaminants

1-6

PmPPC7448 User’s Manual 10006757-02

Page 21

Overview: Additional Information

Type: Specification:

EMC FCC Part 15, Class B – Title 47, Code of Federal Regulations, Radio

Note: EMC testing was performed without the front panel serial or Ethernet cables installed. These ports are for

debug purposes only. Also, EMC testing was not performed for the configuration with the taller heatsink (for

15 mm connector stackup). This configuration is designed for use on a customer’s proprietary carrier that

can support 15 mm PCI mezzanine cards. It is the customer’s responsibility to test this PmPPC7448 configuration in their system.

Emerson maintains test reports that provide specific information regarding the methods

and equipment used in compliance testing. Unshielded external I/O cables, loose screws, or

a poorly grounded chassis may adversely affect the PmPPC7448 hardware’s ability to comply with any of the stated specifications.

Frequency Devices

ICES 003, Class B – Industry Canada Interference-causing Equipment

Standard for Digital Apparatus, Radiated and Conducted Emissions

NEBS: Telcordia GR-1089 level 3 – Emissions and Immunity (circuit pack

level testing only)

AS/NZS 3548 003, Class A – Standard for radiated and conducted

emissions for Australia and New Zealand

EN55022, Class B – Information Technology Equipment, Radio

Disturbance Characteristics, Limits and Methods of Measurement

EN55024 – Information Technology Equipment, Immunity

Characteristics, Limits and Methods of Measurement

EN300386-2 – Electromagnetic Compatibility and Radio Spectrum

Matters (ERM); Telecommunication Network Equipment;

Electromagnetic Compatibility (EMC) Requirements

VCCI, Class 2 – Radiated and Conducted Emissions (Japan)

UL Certification

The UL web site at ul.com has a list of Emerson’s UL certifications.

1 To find the list, search in the online certifications directory using Emerson’s UL file number,

E190079.

2 There is a list for products distributed in the United States, as well as a list for products

shipped to Canada. To find the PmPPC7448, search in the list for the model name and/or

number. The PmPPC7448 is a Processor PCI Mezzanine Card (PPMC). The model number is

PmPPC7448’s Printed Circuit Board (PCB) artwork number, which is 10005277-xx (xx

changes with each artwork revision).

10006757-02 PmPPC7448 User’s Manual

1-7

Page 22

Overview: Additional Information

RoHS Compliance

The PmPPC7448 is compliant with the European Union’s RoHS (Restriction of Use of Hazardous Substances) directive created to limit harm to the environment and human health

by restricting the use of harmful substances in electrical and electronic equipment. Effective July 1, 2006, RoHS restricts the use of six substances: cadmium (Cd), mercury (Hg),

hexavalent chromium (Cr (VI)), polybrominated biphenyls (PBBs), polybrominated diphenyl ethers (PBDEs) and lead (Pb). Configurations that are RoHS compliant are built with

lead-free solder. Configurations that are 5-of-6 are built with tin-lead solder per the lead-insolder RoHS exemption.

To obtain a certificate of conformity (CoC) for the PmPPC7448, send an e-mail to

sales@artesyncp.com or call 1-800-356-9602. Have the part number(s) (e.g., C000######) for your configuration(s) available when contacting Emerson.

Terminology and Notation

Active low signals: An active low signal is indicated with an asterisk * after the signal name.

Byte, word: Throughout this manual byte refers to 8 bits, word refers to 16 bits, long word refers to 32

bits, and double long word refers to 64 bits.

MAC: This manual uses the acronym MAC to refer to both a medium access control address and

the media-specific access control protocol within IEEE 802 specifications.

PLD: This manual uses the acronym PLD as a generic term for programmable logic device (also

known as FPGA, CPLD, EPLD, etc.).

Radix 2 and 16: Hexadecimal numbers either end with a subscript 16 or begin with 0x. Binary numbers are

shown with a subscript 2.

Technical References

Further information on basic operation and programming of the PmPPC7448 components

can be found in the following documents:

Table 1-3: Technical References

Device / Interface: Document:

CPU MPC7450 RISC Microprocessor Family User’s Manual

System controller/

PCI bridge

1-8

PmPPC7448 User’s Manual 10006757-02

3

(Freescale Semiconductor MPC7450UM Rev. 4.2 10/2004)

http://www.freescale.com

Discovery™ III PowerPC

(Marvell, MV64460-001 9/03)

http://www.marvell.com

VESA Unified Memory Architecture

http://www.vesa.org

®

System Controller MV64460 Product Brief

Page 23

Overview: Additional Information

Device / Interface: Document:

Ethernet KSZ8721CL 3.3V Single Power Supply 10/100BASE-TX/FX MII Physical Layer

Flash Intel

Real-Time Clock Serial Access Timekeeper

SDRAM (SO-DIMM)

Module

PCI PCI Local Bus Specification

PMC IEEE Standard for a Common Mezzanine Card (CMC) Family: IEEE Std 1386-

PPMC Processor PMC Standard for Processor PCI Mezzanine Cards: VITA 32-2003

Transceiver Data Sheet

(Micrel® Inc., Rev. 1.2, M9999-041405 April 2005)

http://www.micrel.com

BCM5461S 10/100/1000BASE-T Gigabit Ethernet Transceiver Data Sheet

(Broadcom® Corporation, 5461S-DS05-R 09/02/04)

http://www.broadcom.com

®

(Intel, Order Number: 306666 Revision: 002 August 2005)

http://www.intel.com

®

(ST

Microelectronics, July 2001)

http://www.st.com

32M X 72 Bits (256MB) 200-Pin DDR SDRAM SO-DIMM with ECC

(SimpleTech, Inc. Doc. Part Number 61000-01906-101 June 2001)

http://www.simpletech.com

(PCI Special Interest Group, Revision 2.2, December 18, 1998)

PCI-X Addendum to the PCI Local Bus Specification

(PCI Special Interest Group, Revision 1.0a, July 24, 2000)

http://www.pcisig.com

2001

(IEEE: New York, NY)

IEEE Standard for Physical and Environmental Layers for PCI Mezzanine Cards:

IEEE Std 1386.1-2001

(IEEE: New York, NY)

http://www.ieee.org

Revision 1.0a / 29 April 2003

(VITA: Scottsdale, AZ)

http://www.vita.com

3

StrataFlash® Embedded Memory (P30) Datasheet

®

M41T00

(continued)

3.Frequently, the most current information regarding addenda/errata for specific documents may be found on

the corresponding web site.

10006757-02 PmPPC7448 User’s Manual

1-9

Page 24

(blank page)

1-10

PmPPC7448 User’s Manual 10006757-02

Page 25

Setup

!

Section 2

This chapter describes the physical layout of the boards, the setup process, and how to

check for proper operation once the boards have been installed. This chapter also includes

troubleshooting, service, and warranty information.

ELECTROSTATIC DISCHARGE

Before you begin the setup process, please remember that electrostatic discharge (ESD)

can easily damage the components on the PmPPC7448 hardware. Electronic devices, especially those with programmable parts, are susceptible to ESD, which can result in operational failure. Unless you ground yourself properly, static charges can accumulate in your

body and cause ESD damage when you touch the board.

Caution: Use proper static protection and handle PmPPC7448 boards only when absolutely

necessary. Always wear a wriststrap to ground your body before touching a board. Keep

your body grounded while handling the board. Hold the board by its edges–do not touch

any components or circuits. When the board is not in an enclosure, store it in a staticshielding bag.

To ground yourself, wear a grounding wriststrap. Simply placing the board on top of a

static-shielding bag does not provide any protection–place it on a grounded dissipative

mat. Do not place the board on metal or other conductive surfaces.

PMPPC7448 CIRCUIT BOARD

The PmPPC7448 is a fourteen-layer circuit board that conforms to the IEEE 1386 Common

Mezzanine Card (CMC) standard. It has the following physical dimensions:

Table 2-1: Circuit Board Dimensions

Width: Depth: Height (top side): Height (bottom side):

2.913 in.

(74 mm)

5.866 in.

(149 mm)

0.323 in. (I/O area, 0.524 in.)

(8.2 mm, I/O area is 13.5 mm)

0.007 in.

(1.9 mm)

10006757-02 PmPPC7448 User’s Manual

2-1

Page 26

SW1

U3

SODIMM

C15

C19

C9

C43

C28

C29

C16

C17

C31

C18

C32

C110

C199

C5

C323

C253

C46

C40

C22

C27

C36

C38

C25

C37

C51

C23

C50

C49

C47

C62

C63

C53

C52

C54 C56

C58

C60

C24

C26

C30

C33

C34

C35

C39

C41

C42

C44

C48

C294

C295

C280

C281

C286

C45

R25

R470

R471

R472

R473

R482 R483

R486

R485

R484

R487

R488

R491

R490

R489

R76

R88

R33

R34

R85

R86

R87

R89

R492

R75

R1

R19

R2

R291

R293

R30

R36

R4

R40

R5

R505

R507

R508

R510

R511

R6

R80

R81

R83

R84

R90

R91

R12

R13

R29

R7

L2

C1

R10

R11

R175

R18

R183

R24

R3

R303 R306

R307

R308

R32

R37

R38

R39

R41

R42

R43

R47

R48

R50

R504

R51

R52

R53

R54 R55

R56

R57

R58

R59

R60

R61

R62

R63

R64

R65

R66

R67

R68

R69

R70

R71

R72

R73

R78

R79

R8

R82

C55

C57

C59

C61

R20

R22

R23

R26

R27

R31

L3

L4

L5

R493

R562

C320

C321

R585

U2

U10

U11

U12

U13

U14

U15

U5 U6

U9

U7

U8

C300

R563

R564

C325

C326

RN1

RN10

RN12

RN14

RN16

RN17

RN18

RN5

RN6

RN7

RN8

RN9

RN3

RN4

RN11

RN13

RN15

RN19

RN2

U4

MV64460

System Controller

U1

MPC7447

CPU

M5 M6

P1

P11

1

2

63

64

P12

1

2

63

64

P13

1

2

63

64

P14

1

2

63

64

P2

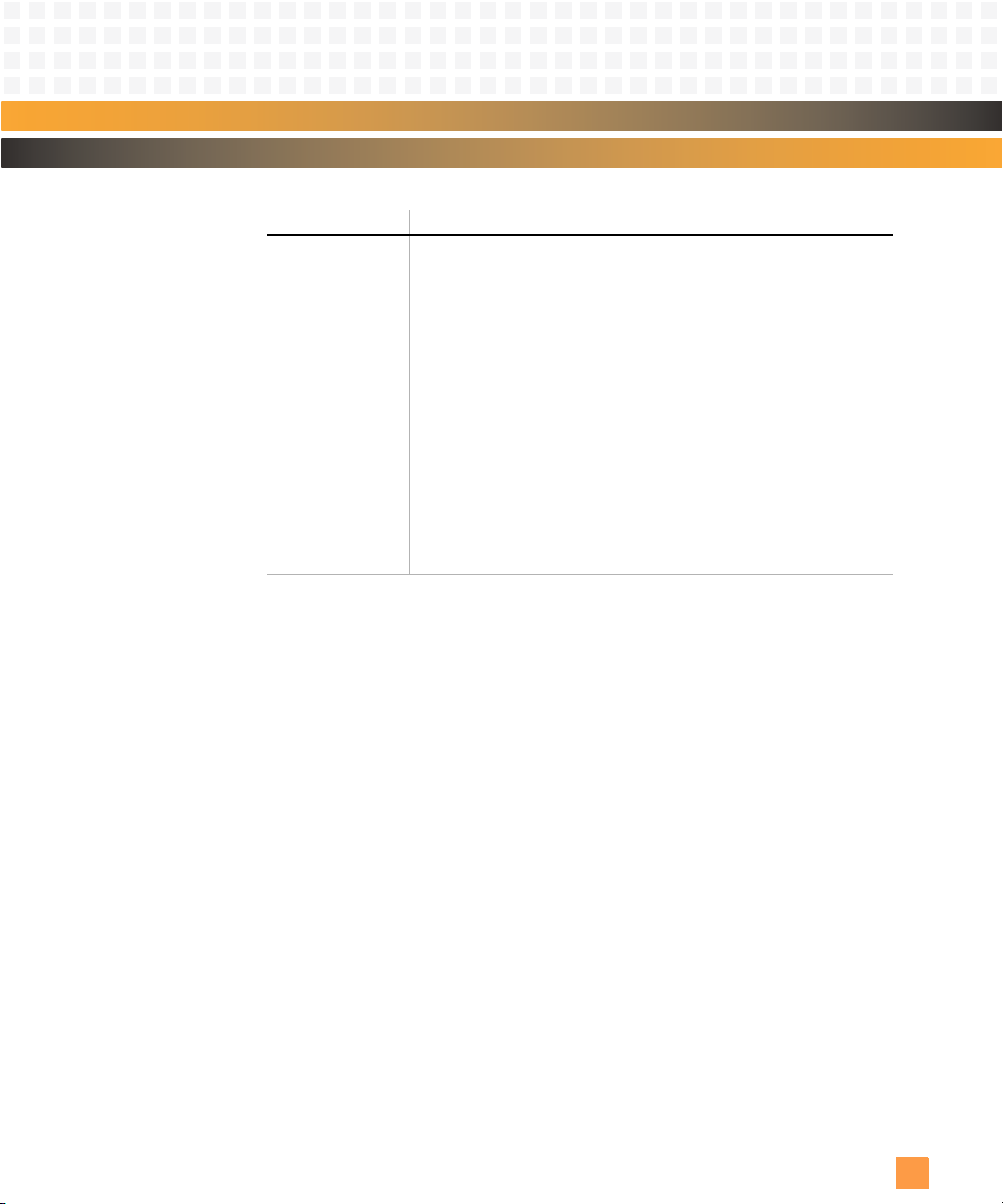

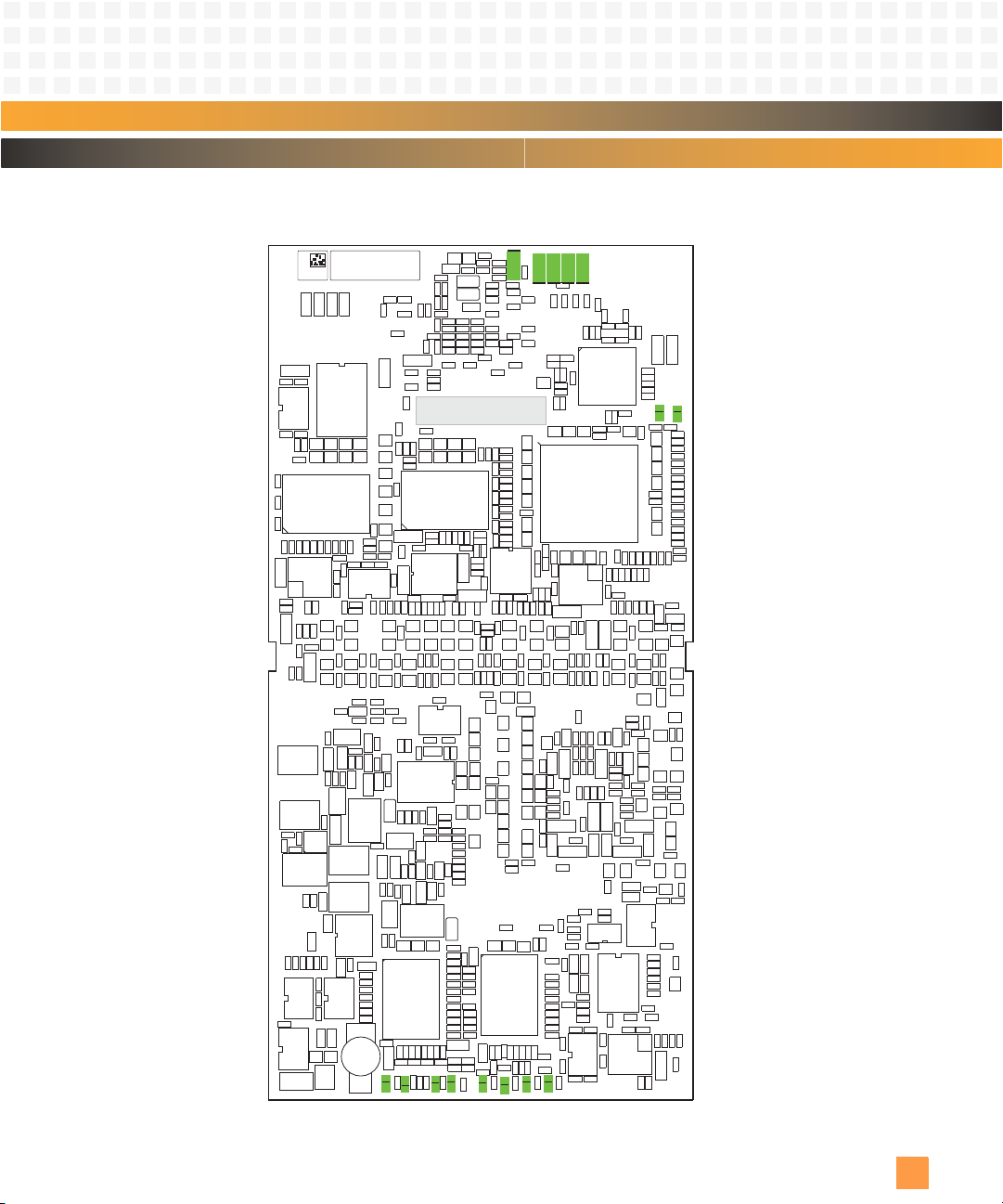

Setup: PmPPC7448 Circuit Board

The following figures show the component maps for the PmPPC7448 circuit board.

Figure 2-1: Component Map, Top (Rev. 06)

2-2

PmPPC7448 User’s Manual 10006757-02

Page 27

Setup: PmPPC7448 Circuit Board

C189

C245

C91

C249

C248

C274

C261

C263

C250

C265

C73

C251

C231

C215

C180

C247

C242

C246

C241

C232

C188

Y3

C190

L13

C20

C174

C107

C21

C185

C142 C144

C104

C76

C89

C90

C103

C84

C79

C97

C68

C85

C80

C66

C77

C101

C95

C75

C98

C81

C71

C225

C102

C86

C78

C94

C92

C96

C74

C87

C72

C93

C99

C100

C82

C88

C70

C235

C112

C83

C64

C268

C120

C278

C129

C119

C171

C111

C139

C115

C173

C184

C153

C113

C237

C269

C156

C106

C109

C167

C147

C267

C131

C130

C158

C135

C125

C116

C164

C140

C168

C141

C137

C136

C134

C133

C160

C138

C148

C151

C161

C162

C159

C117

C108

C114

C126

C163

C256

C255

C240

C266

C264

C128

C254

C221

C127

C276

C262

C238

C271

C260

C244

C270

C272

C218

C105

C275

C183

C182

C181

C194

C187

C192

C179

C176

C175

C178

C196

C177

C201

C213

C214

C209

C186

C208

C197

C210

C203

C202

C198

C216

C155

C211

C229

C154

C152

C165

C217

C205

C220

C207

C206

C204

C149

C212

C150

C169

C145

C239

C118

C121

C123

C122

C277

C124

C219

C172

C252

C279

C65

C200

C230

C227

C224

C259

C258

C273

C257

L18

C236

C243

C226

C228

C234

C233

C143

C146

C157

C166

C191

C195

C222C223

C14

C284

C29

C170

L22

C282

C299

CR22

R520

R349

R350

R351

R352

R122

R123

R337

R382

R275

R290

R295

R312

R313

R322

R323

R324

R335

R395

R407

R414

R415

R419

R420

R422

R423

R427

R428

R465

R480

R481

R500

R501

R523

R227

R229

R231

R233

R235

R244

R246

R249

R251

R255

R259

R273

R276

R277

R278

R279

R284

R285

R286

R287

R296

R301

R316

R317

R318

R320

R321

R334

R339

R342

R343

R347

R348

R360

R366

R377

R468

R469

R300

R292

R425

R426

R444

R447

R393

R440

R107

R108

R109

R110

R454

R455

R456

R457

R458

R459

R460

R461

R95

R325

R371

R298

R98

R413

R336

R330

R477

R202

R204R221

R305

R315

R326

R327

R328

R331

R370

R372

R373

R374

R384

R387

R436

R74

R105

R106

R112

R113

R114R115

R124

R125

R138

R187

R189

R192

R361

R375

R390

R400

R421

R424

R429

R448

R449

R450

R495

R506

R509 R512

R513

R516

R517

R521

R92

R93

R94

R96

R97

R99

R219

R223

R205

R238

R274

R280

R281

R282

R283

R329

R365

R443

R462

L11

L12

L14

L15

L16

L17

L19

L21

L6

L7

L8

L9

R381

R376

R379

R253

R254

R311

R314

R319

R341

R396

R399

R438

R439

R206

R222

CR14

CR15

CR16

CR21

R338

R383

R389

R111

R332

R385

R100

R102

R103

R104

R117

R118

R119

R120

R121

R127

R128

R129

R131

R132

R133

R134

R139

R140

R141

R142

R143

R144

R145

R146

R147

R148

R149

R150

R151

R152

R153

R154

R155

R156

R157

R158

R159

R162

R163

R164

R165

R167

R168

R169

R170

R171

R172

R173

R174

R176

R177

R179

R180

R182

R185

R186

R188

R190

R191

R193

R194

R195

R196

R197

R198

R199

R200

R208

R209

R210

R211

R212

R213

R256

R257

R258

R288

R289

R304

R309

R310

R333

R340

R344

R345

R346

R555

R353

R354

R355

R356

R357

R358R359

R362

R363

R364

R367

R368

R369

R378

R391

R392

R394

R397

R401

R402

R403

R404

R405

R406

R408

R433

R434

R435

R44

R441

R442

R445

R446

R45

R451

R46

R49

R494

R515

R476

R226

R294

R299

R466R467

R474

C67

C69

R475

R409

R418

C285

R502

R503

R101

R116

R136

R137

R160

R166

R203

R217

R218

R225

R228

R230

R232

R234

R236

R245

R247

R250

R252

R260

R261

R262

R263

R264

R265

R267

R268

R269

R270

R271

R297

R398

R410

R411

R412

R416

R417

R431

R432

R452

R453

R463

R464

R514

R478

R380

R388

R430

R479

R522

R518

R519

R559

R561

R524

R551

R541

R549

R552

C322

R536

R542

R545

R546

R547

C304

C305

C307

C312

C314

C315

C317

C318

C319

C324

C331

C332

C333

C334

C335

C336

C337

C338

R565

R566

R567

R568

R569

R570

R571

R572

R573

R574

R575

R576

R577

R578

R579

R580

R581

R582

R583

R584

R543

U40

U41

R526

R527

R528

R529

R530

R531

R532

R533

R538

R539

R550

R535

R537

R548

C301

C302

C308

C309

C310

C327

C328

R557

U42

R534

U36

U33

U34

U39

U29

U28

U27

U16

U26

U30

U37

U38

C297

C298

C303

C306

C311

C313

C343

U35

U24

R525

C344

C345

Y1

Y2

Y4

RN46

RN107

RN108

RN117

RN118

RN189

RN26RN27

RN30

RN41

RN51

RN52

RN53

RN55

RN57

RN58

RN61

RN63

RN64

RN84RN85

RN86

RN102

RN103

RN104

RN105

RN106

RN109

RN110

RN111

RN112

RN120

RN121

RN128

RN129

RN130

RN131

RN132

RN136

RN139RN140

RN141

RN150

RN151

RN152

RN167

RN42RN43RN44RN45

RN47RN48RN49RN50

RN79

RN80RN81

RN82RN83

RN87

RN88

RN89

RN90

RN113RN114

RN115

RN116

RN119

RN122

RN125

RN126

RN133

RN137

RN143

RN145

RN146

RN148

RN154

RN155

RN157

RN160

RN161

RN163

RN164

RN165

RN166

RN100

RN101

RN172

RN173

RN175

RN176

RN177

RN24RN25

RN29

RN40

RN54

RN56

RN59

RN60

RN62

RN65

RN66

RN67

RN68

RN69

RN70

RN71

RN72

RN73

RN74

RN75

RN76

RN77

RN78

RN91

RN92

RN93

RN94RN95

RN96RN97RN98

RN99

RN123

RN124

RN127

RN134

RN135

RN138

RN142

RN144

RN147

RN149

RN153

RN156

RN158

RN159

RN162

RN168RN169

RN170

RN171

RN178

RN187

RN188

RN20

RN21

RN28

RN31RN32RN33RN34

RN35

RN36RN37RN38RN39

U20

Flash

U31

GbE

U32

GbE

U18

PLD

M1

M2

M3

M4

R161

684-

XXXXXX

1000XXXX-XX D

R272

U19

Flash

P3

PMC-to-PMC

CR5

CR4

CR3

CR2

CR1

CR11

CR10

R544

C193

RN174

CR23

CR24

CR25

CR26

CR27

CR28

CR29

CR30

Figure 2-2: Component Map, Bottom (Rev. 06)

10006757-02 PmPPC7448 User’s Manual

2-3

Page 28

Setup: PmPPC7448 Circuit Board

Connectors

The PmPPC7448 has the following connectors:

P1: This mini-USB (universal serial bus) is the connection to the front panel 10/100 PHY Ether-

net (port 2). Refer to

Table 6-2 for the pin assignments.

P2: P2 is a mini-USB connector for the front panel serial port. Refer to

Table 8-2 for the pin

assignments.

P3: This is an 80-pin PCB-to-PCB male connector on the bottom side of the PmPPC7448. P3

routes memory, CPLD, and CPU signals from the PmPPC7448 to the DMC for development

use. See

Table 10-2 for the pin assignments.

P11, P12, P13: These 64-pin connectors provide the standard 64-bit PCI interface between the

PmPPC7448 and the PMC host. See

Table 5-1 for pinouts.

P14: This 64-pin connector conforms to the PCI specification as user-defined. Ethernet signals

are also available at P14. See

Table 5-2 for pinouts.

U3: This is the socket for the small-outline, dual inline memory module (SO-DIMM). The SO-

DIMM board layout depends on the memory configuration and manufacturer.

2-4

PmPPC7448 User’s Manual 10006757-02

Page 29

Setup: PmPPC7448 Circuit Board

P3-DMC

CR5

CR4

CR3

CR2

CR1

CR11

CR10

CR26

CR25

CR24

CR23

CR30

CR29

CR28

CR27

CR1-Debug LED4

CR2-Debug LED3

CR3-Debug LED2

CR4-Debug LED1

CR5-MPC7448 Check stop out

Port 2 Ethernet

(10/100BASE-TX/FX)

CR10-Link

CR11-Activity

Port 0 Ethernet

(10/100/1000BASE-T)

CR23-Activity

CR24-Link

CR25-Link1

CR26-Link2

Port 1 Ethernet

(10/100/1000BASE-T)

CR27-Activity

CR28-Link

CR29-Link1

CR30-Link2

LEDs

The PmPPC7448 has fifteen green light-emitting diodes (LEDs) on the back side of the

board (see

Figure 2-3: LED Locations, Bottom

Fig. 2-3).

10006757-02 PmPPC7448 User’s Manual

2-5

Page 30

Setup: PmPPC7448 Circuit Board

!

Ethernet

Reset

Serial

P1 Ethernet connector

P2 serial connector

SW1

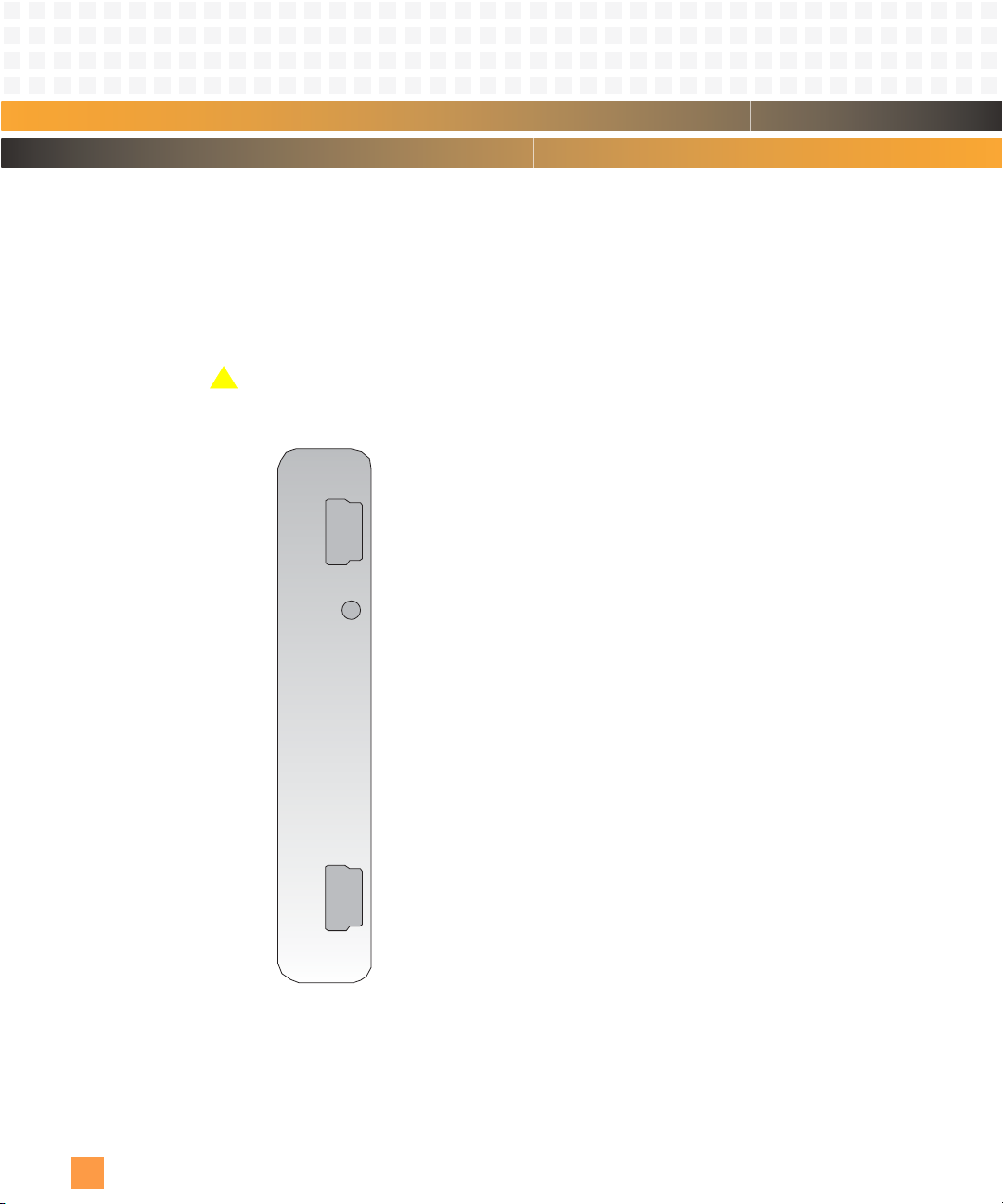

Front Panel

The PmPPC7448 has a single-wide PPMC front panel with an Electromagnetic Interference

(EMI) gasket.

Note: The electromagnetic compatibility (EMC) tests used a PmPPC7448 model that includes a

front panel assembly from Emerson.

Caution: For applications where the PmPPC7448 is provided without a front panel, or where the

front panel has been removed, your system chassis/enclosure must provide the required

electromagnetic interference (EMI) shielding to maintain EMC compliance.

Figure 2-4: Front Panel

2-6

PmPPC7448 User’s Manual 10006757-02

Page 31

Setup: PmPPC7448 Circuit Board

!

Reset

The reset signals are routed to the CPLD, unless stated otherwise. See Chapter 7 for the

reset registers. The following sources can reset the PmPPC7448:

Power-on: This causes a hard reset to the entire board, including the PCI interfaces.

Front panel: This reset switch is accessible through a small hole in the front panel and causes a hard reset

to the entire board, including the PCI interfaces.

Caution: Use minimal force when pressing the front panel reset switch. Excessive force may damage

the switch.

PCI RESET: This causes a hard reset to the entire board, including the PCI interfaces.

COP HRESET: This reset is activated by the common on-chip processor (COP) debugger interface via a

header located on the Development Mezzanine Card (DMC). It causes a hard reset to the

entire board, including the PCI interfaces.

COP SRESET: This reset is activated by the COP debugger interface and causes a soft reset to the Frees-

cale MPC7448 and a reset to Flash.

COP TRST: This is routed directly to the MPC7448 TRST.

PMC TRST: This is routed directly to the MV64460 TRST.

Software controlled: The software controlled resets are described in the Reset Command register, Register

Map 7-2.

10006757-02 PmPPC7448 User’s Manual

2-7

Page 32

Setup: PmPPC7448 Setup

CPLD

P11/P12

Ethernet

MII

(portdbg)

MV64460

PCI Bridge

CPLD_MV_64EN*

PER_AD(31:0)*

MV_SYSRST*

PCI_RST*

OSC_EN

Voltage

Monitor

ENET_RST*

DEBUG_HRESET

FLASH_RP*

MPC7448_HRESET*

Development

Mezzanine

Card

PMC_CPLD_PCI_REQ64*

MPC7448

MV_INIT_ACT

MV_WDE

Flash

PMC_CPLD_PCI_DEVSEL*

PMC_CPLD_PCI_STOP*

PMC_CPLD_PCI_TRDY*

PMC_CPLD_PCI_RST*

PMC_RESET_OUT*

POR_RST*

Voltage

Monitor

Ethernet

RGMII

(port0)

Ethernet

RGMII

(port1)

MPC7448_SRESET*

MPC7448_TRST*

DEBUG_SRESET

DEBUG_TRST

DMC_PD

DMC_BOOT_SRC

Init ROM

I2C

MV_SCL

MV_SDA

PMC_CPLD_PCI_RST_R*

Figure 2-5: Reset Diagram

2-8

PmPPC7448 User’s Manual 10006757-02

PMPPC7448 SETUP

You need the following items to set up and check the operation of the Emerson

PmPPC7448:

❐ An Emerson PmPPC7448 board

❐ A compatible host board, such as the Emerson CC1000-DM or Katana750i

❐ Card cage and power supply

❐ CRT terminal

When you unpack the board, save the antistatic bag and box for future shipping or storage.

Page 33

Setup: PmPPC7448 Setup

!

Caution: Do not install the board in a rack or remove the board from a rack while power is applied, at

risk of damage to the board.

Power Requirements

Be sure your power supply is sufficient for the PmPPC7448 circuit board. Standard power is

3.3 volts, however a dual power supply option is available.

power requirements.

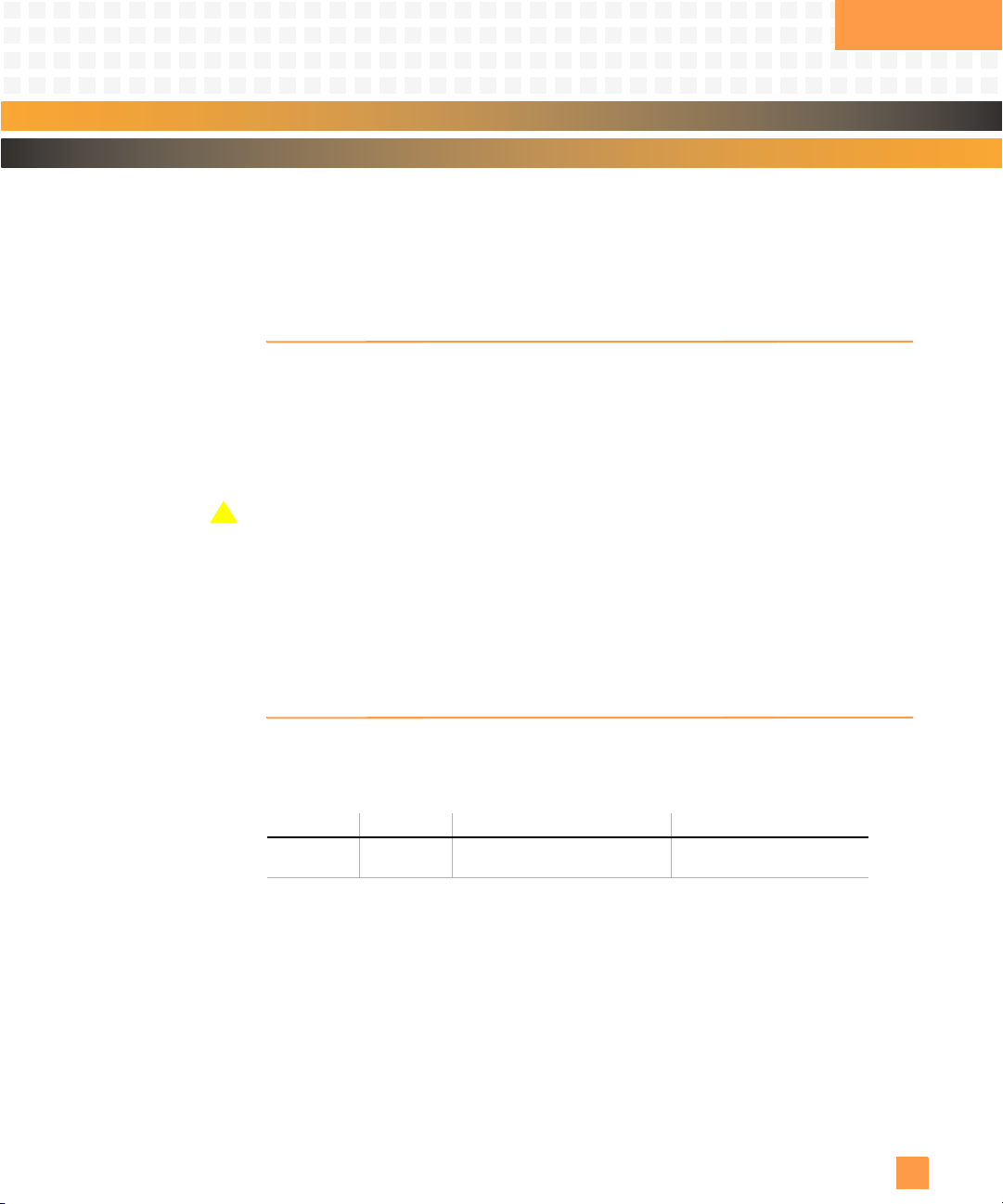

Table 2-2: Power Requirements

Voltage: Range:

+3.3 V +/- 5% 5.1 amps 1 GHz MPC7448 and 1 GB DDR SDRAM

Specific PmPPC7448 configurations may draw over 20 watts of power. The configurations

with a faster core CPU frequency and increased DDR memory draw more power and generate more heat. When monitoring the ambient air temperature increase across the module

(from the inlet side of the PmPPC7448 to the outlet), the temperature can rise approximately 4-7° C at high airflow (300 lfm) to 5-12° C at low airflow (100 lfm). The system

designer should consider the cumulative effects of installing multiple PMC modules on a

single carrier and ensure adequate airflow.

Table 2-2 lists the board’s specific

Current

(typical): Watt Requirements/Configuration:

configuration typically requires 17 watts

Environmental Considerations

As with any printed circuit board, be sure that air flow to the board is adequate. Chassis

constraints and other factors greatly affect the air flow rate. The environmental requirements are as follows:

Table 2-3: Environmental Requirements

Environment: Range: Relative Humidity:

Operating Temperature 0° to +55° Centigrade, ambient

Storage Temperature —40° to 85° Centigrade Not to exceed 95%

Altitude 0 to 4,000 meters above sea level n/a

1

Air Flow

1. Airflow is required at the processor to maintain junction temperature less than 95° C at specified

ambient temperature.

(at board)

100 linear feet/minute @ 45° C ambient

200 linear feet/minute @ 55° C ambient

10006757-02 PmPPC7448 User’s Manual

Not to exceed 85%

(non-condensing)

(non-condensing)

n/a

2-9

Page 34

Setup: PmPPC7448 Setup

PmPPC7448

(Bottomside)

PmPPC7448

(Bottomside)

J21

J22

J23

J24

J11

J12

J13

J14

J5J3J2J1

PMC 1 PMC 2

Installing the Module

Most PPMC-compatible baseboards have two sets of four connectors (J11, J12, J13, J14 and

J21, J22, J23, J24), as defined by the PMC standard P1386.1. This allows the PmPPC7448 to

be installed in either PPMC slot.

location of the PmPPC7448 modules on the baseboard.

Figure 2-6: Module Location on Emerson CC1000-DM

Fig. 2-6 shows the location of these connectors and the

2-10

Use the following procedure to attach the PmPPC7448 module to your baseboard in slot

PMC1 (see

1 Remove the screws from the standoffs on the PPMC module.

2 Hold the module at an angle and gently slide the faceplate into the opening on the

Fig. 2-7):

baseboard.

PmPPC7448 User’s Manual 10006757-02

Page 35

Setup: Troubleshooting

!

PmPPC7448

P14

P13

P11

P12

Tighten these two screws first.

PMC1

PMC2

J11

J12

Reset

Serial

J14

J13

J21

J22

J23

J24

3 Align the P11 and P12 connectors and gently press the module into place until firmly

mated.

Caution: To avoid damaging the module and/or baseboard, do not force the module onto the

baseboard.

Figure 2-7: Installing the Module

4 Using four M2.5x5 mm panhead screws (Emerson part #10006275-00), secure the

PmPPC7448 module from the bottom of the baseboard. First, insert and tighten the screws

closest to the P11 through P14 connectors. Next, insert and tighten the screws nearest to

the front panel.

TROUBLESHOOTING

In case of difficulty, use this checklist:

10006757-02 PmPPC7448 User’s Manual

2-11

Page 36

Setup: Troubleshooting

❐ Be sure the PmPPC7448 module is seated firmly on the PPMC host and that the PPMC

host is seated firmly in the card cage.

❐ Verify the boot jumper setting if the DMC is installed (see page 10-9).

❐ Be sure the system is not overheating.

❐ Check the cables and connectors to be certain they are secure.

❐ Check your power supply for proper DC voltages. If possible, use an oscilloscope to look

for excessive power supply ripple or noise (over 50 mV

Technical Support

If you need help resolving a problem with your PmPPC7448, visit

http://www.emersonembeddedcomputing.com/contact/postsalessupport.html on the

Internet or send e-mail to support@artesyncp.com. If you do not have internet access, call

Emerson for further assistance:

(800) 327-1251 or (608) 826-8006 (US)

44-131-475-7070 (UK)

below 10 MHz).

pp

Have the following information available when contacting support:

• PmPPC7448 serial number and product identification (see

• monitor version (see

• version and part number of the operating system (if applicable). This information is

labeled on the master media supplied by Emerson or another vendor

• whether your board has been customized for options such as a higher processor speed

or additional memory

Fig. 11-1 startup display)

Fig. 2-8)

2-12

PmPPC7448 User’s Manual 10006757-02

Page 37

684-

XXXXXX

00000000-00 D MMYY

PRODUCT OF XXXXX X

Serial Number

Product ID

Setup: Troubleshooting

Figure 2-8: Serial Number and Product ID on Bottom Side

Product Repair

If you plan to return the board to Emerson Network Power for service, visit

http://www.emersonembeddedcomputing.com/contact/productrepair.html on the internet or send e-mail to serviceinfo@artesyncp.com to obtain a Return Merchandise Authorization (RMA) number. We will ask you to list which items you are returning and the board

serial number, plus your purchase order number and billing information if your PmPPC7448

hardware is out of warranty. Contact our Test and Repair Services Department for any warranty questions. If you return the board, be sure to enclose it in an antistatic bag, such as

the one in which it was originally shipped. Send it prepaid to:

10006757-02 PmPPC7448 User’s Manual

2-13

Page 38

Setup: Troubleshooting

Please put the RMA number on the outside of the package so we can handle your problem

efficiently. Our service department cannot accept material received without an RMA number.

Emerson Network Power, Embedded Computing

Test and Repair Services Department

8310 Excelsior Drive

Madison, WI 53717

RMA #____________

2-14

PmPPC7448 User’s Manual 10006757-02

Page 39

Central Processing Unit

This chapter is an overview of the processor logic on the PmPPC7448. It includes information on the CPU, exception handling, and cache memory. The PmPPC7448 utilizes the Freescale MPC7448 RISC microprocessor, for more detailed information reference the Freescale

Semiconductor MPC7450 RISC Microprocessor Family User’s Manual.

The following table outlines some of the key features for the MPC7448 CPU.

Table 3-1: PmPPC7448 CPU Features

Category: MPC7448 Key Features:

Instruction Set Up to three instructions can be dispatched, four

CPU Speed (Internal) Up to 1.4 GHz

Data Bus 64-bit with 8 bits of data parity

Address Bus 36-bit with 5 bits of address parity

Seven Stage Pipeline

Control

L1 Cache 32 kilobytes instruction, 32 kilobytes data

L2 Cache 1 megabyte, eight-way set-associative unified

Execution Units Branch processing (BPU), four integer (IU), 64-bit

Memory

Management Units

Voltages Processor core, 1.0 V at 1.0 GHz or lower,

Power Management Dynamic Frequency Switching capability (divide-by-

Section 3

instructions can be fetched, 12 instructions can be in

the queue, and 16 instructions can be at some stage of

execution

Fetch, dispatch/decode, execute, complete/write

back

instruction and data cache, ECC capability

floating-point (FPU), four vector (VPU, VIU1, VIU2,

VFPU), three-stage load/store (LSU), three issue

queues (FIQ, VIQ, GIQ), rename buffers, dispatch, and

completion

52-bit virtual address, 32- or 36-bit physical address

1.15 V at 1.4 GHz

two and divide-by-four modes)

10006757-02 PmPPC7448 User’s Manual

3-1

Page 40

Central Processing Unit: Processor Reset

Memory Subsystem

System Bus

Interface

1 MB L2

Cache

Controller

L1 Service

Queues

Floating

Point

Unit

Instruction MMU

Data MMU

Tags

32-KB

D Cache

Tags

32-KB

I Cache

Integer

Unit 2

Integer

Unit 1

(3)

Completion

Unit

Branch

Processing

Unit

Instruction

Queue

VR Issue GPR Issue FPR Issue

Instruction Unit

Load/Store Unit

Vector

Permute Unit

Vector Integer

Unit 2

Vector Integer

Unit 1

Vector FPU

Figure 3-1: MPC7448 Block Diagram

PROCESSOR RESET

Circuitry on the PmPPC7448 module resets the processor and the board. It activates the

RESET_OUT* signal on pin 60 of the P12 connector if the module voltages fall out of tolerance or if the optional on-board reset switch is activated. A COP SRESET causes a soft reset

Table 3-2: CPU Internal Register Initialization

3-2

PmPPC7448 User’s Manual 10006757-02

to the processor, see the Reset Command register in Register Map 7-2.

PROCESSOR INITIALIZATION

Initially, the PmPPC7448 powers up with specific values stored in the CPU registers. The initial power-up state of the Hardware Implementation Dependent register (HID0) and the

Machine State register (MSR) are given in

Register: Default After Initialization (Hex): Notes:

HID0 8000,0000 (icache and dcache off) Hardware Implementation

8000,C000 (icache and dcache on)

MSR 0000,B032 Machine State register

Table 3-2.

Dependent register

(See Register Map 3-1)

(See Register Map 3-3)

Page 41

Central Processing Unit: Processor Initialization

Hardware Implementation Dependent 0 Register

The Hardware Implementation Dependent 0 (HID0) register contains bits for CPU-specific

features. Most of these bits are cleared on initial power-up of the PmPPC7448. Please refer

to the MPC7450 RISC Microprocessor Family User’s Manual for more detailed descriptions of

the HIDx registers. The following register map summarizes HID0 for the MPC7448 CPU:

Register 3-1: MPC7448 Hardware Implementation Dependent, HID0

0 4 5 6 7 8 9 10 11 12 13 14 15

BHT

reserved TBE RSTEHBENAPSLPDPMR

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

CLR

XAE NHR

ICE DCE

ILOCKDLO

CK

ICFI DCFI SPD

XBS

EN

SGE

RBTIC

LRSTKFOL

D

BHT

TBE: Time Base Enable—this bit must be set and the TBEN signal must be asserted to enable the

time base and decrementer.

STE: Software Table Search Enable—after a TLB miss, one of the three TLB miss exceptions is

taken so that software can search the page tables for the appropriate PTE.

0 Hardware table search enabled

1 Software table search enabled

HBE: High BATs Enable

0 Additional 4 IBATs (4-7) and 4 DBATs (4-7) disabled

1 Additional 4 IBATs (4-7) and 4 DBATs (4-7) enabled

NAP: Nap Mode Enable

0 Nap mode disabled