Page 1

User’s Manual

from Emerson Network Power

Embedded Computing

™

PmT1 and PmE1: High Speed T1 and E1 Interface Module

December 2007

Page 2

The information in this manual has been checked and is believed to be accurate and reliable.

HOWEVER, NO RESPONSIBILITY IS ASSUMED BY EMERSON NETWORK POWER, EMBEDDED

COMPUTING FOR ITS USE OR FOR ANY INACCURACIES. Specifications are subject to change

without notice. EMERSON DOES NOT ASSUME ANY LIABILITY ARISING OUT OF USE OR

OTHER APPLICATION OF ANY PRODUCT, CIRCUIT, OR PROGRAM DESCRIBED HEREIN. This

document does not convey any license under Emerson patents or the rights of others.

Emerson. Consider It Solved is a trademark, and Business-Critical Continuity, Emerson Network Power, and the Emerson Net work Power logo are trademarks and service marks of

Emerson Network Power, Embedded Computing, Inc.

© 2007 Emerson Network Power, Embedded Computing, Inc.

Revision Level: Principal Changes: Date:

10002367-00 Original release March 2001

10002367-01 RoHS 5-of6 compliance, ECR000272 March 2006

10002367-02 Artwork rev.-33 December 2007

Copyright © 2007 Emerson Network Power, Embedded Computing, Inc. All rights reserved.

Page 3

Regulatory Agency Warnings & Notices

!

!

The Emerson PmT1 and PmE1 meets the requirements set forth by the Federal Communications Commission (FCC) in Title 47 of the Code of Federal Regulations. The following

information is provided as required by this agency.

This device complies with part 15 of the FCC Rules. Operation is subject to the following

two conditions: (1) This device may not cause harmful interference, and (2) this device

must accept any interference received, including interference that may cause undesired

operation.

FCC RULES AND REGULATIONS — PART 15

This equipment has been tested and found to comply with the limits for a Class A digital

device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses and can radiate radio frequency energy

and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely

to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

Caution: Making changes or modifications to the PmT1 and PmE1 hardware without the explicit

consent of Emerson Network Power could invalidate the user’s authorit y to operate this

equipment.

EMC COMPLIANCE

The electromagnetic compatibility (EMC) tests used a PmT1 and PmE1 model that includes

a front panel assembly from Emerson Network Power.

Caution: For applications where the PmT1 and PmE1 is provided without a front panel, or where the

front panel has been removed, your system chassis/enclosure must provide the required

electromagnetic interference (EMI) shielding to maintain EMC compliance.

FCC RULES AND REGULATIONS — PART 68

This equipment complies with Part 68 of the FCC rules. There is a label on the PmT1 and

PmE1 board that contains the FCC registration number. If requested, this information must

be provided to the telephone company.

1000236 7-02 PmT1 and PmE 1 User’s Manua l

i

Page 4

Regulatory Agency Warnings & Notices (continued)

This board is designed to be connected to the telephone network or premises wiring using

a compatible modular jack which is Part 68 compliant. This board cannot be used on telephone company-provided coin service. Connection to Part y Line Ser vice is subject to state

tariffs.

If this board causes harm to the telephone network, the telephone company will notify you

in advance that temporary discontinuance of service may be required. If advance notice is

not practical, the telephone company will notify the customer as soon as possible. Also, you

will be advised of your right to file a complaint with the FCC if you believe it is necessary.

The telephone company may make changes in its facilities, equipment, operations, or procedures that could affect the operation of the equipment. If this happens, the telephone

company will provide advance notice in order for you to make the necessary modifications

in order to maintain uninterrupted service.

It is recommended that the customer install an AC surge arrestor in the AC outlet to which

this device is connected. This is to avoid damaging the equipment caused by local lightening strikes and other electrical surges.

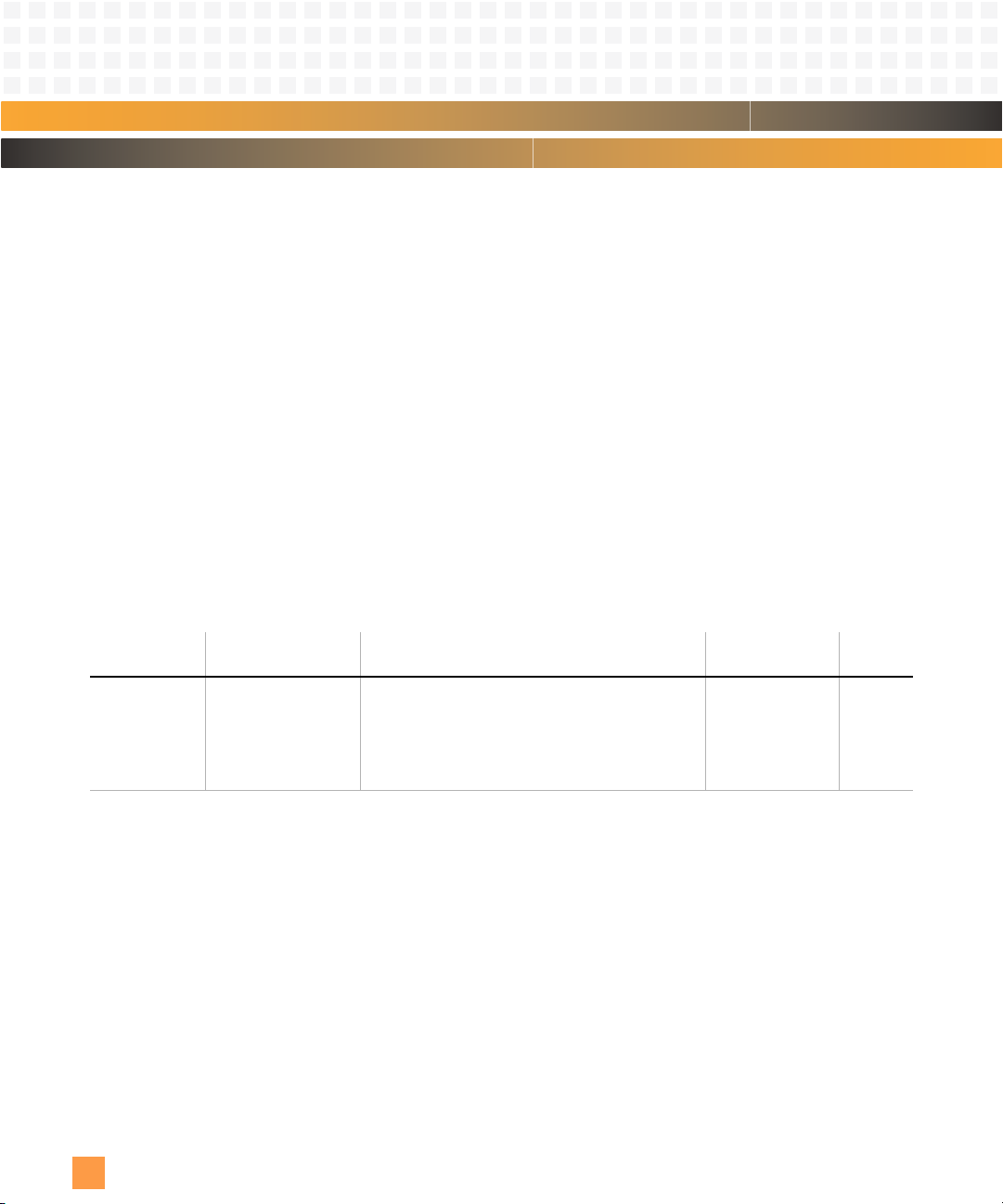

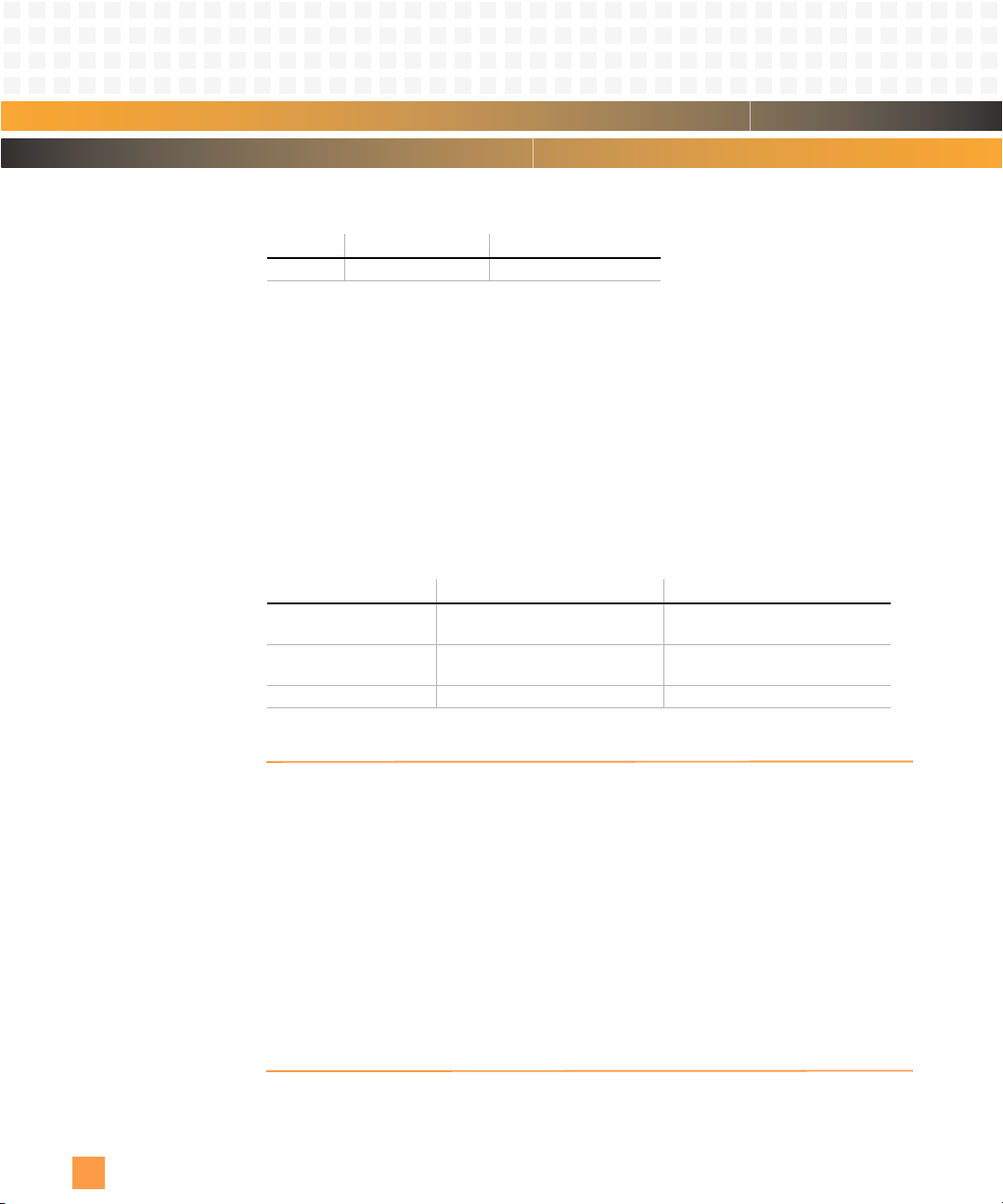

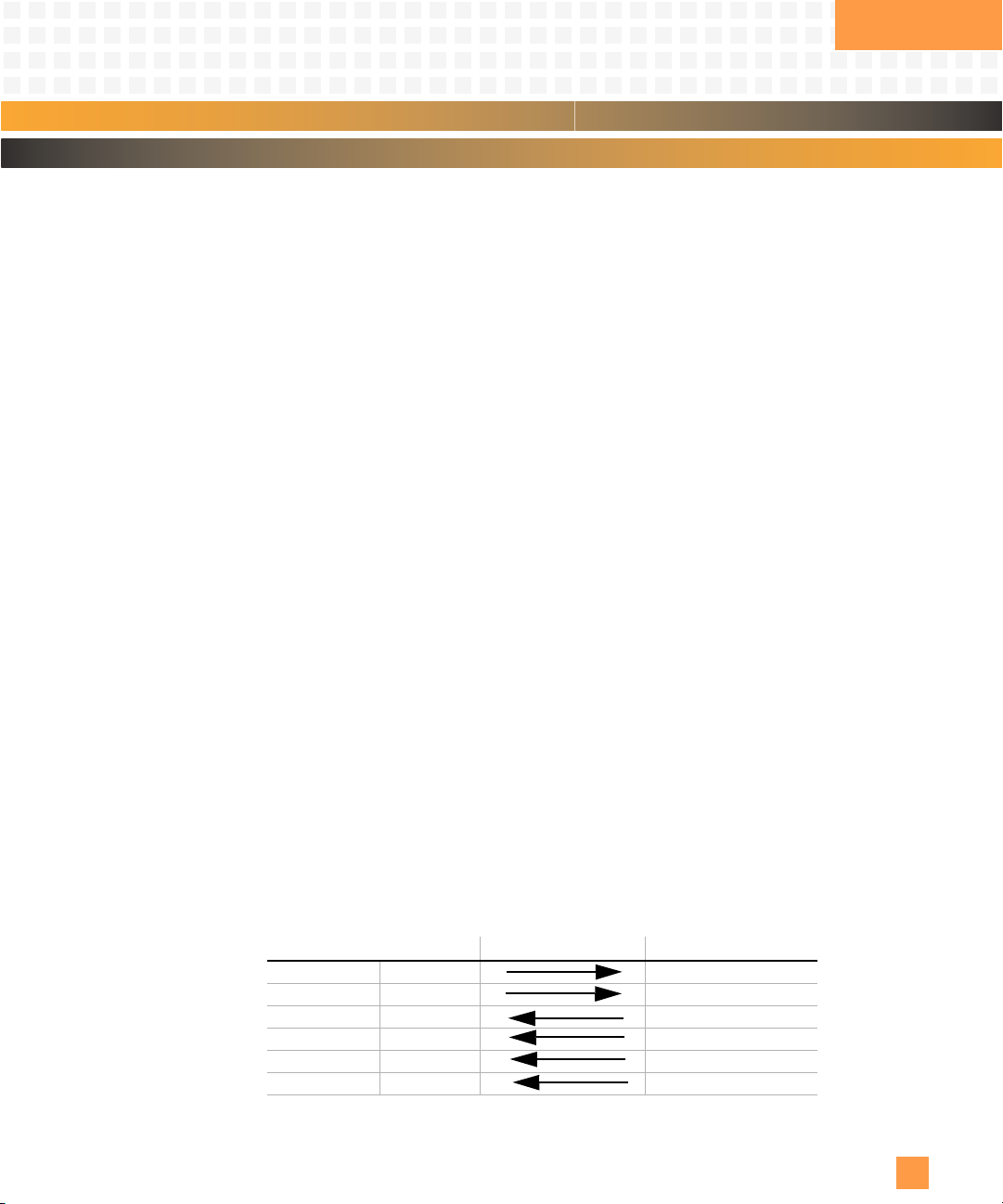

The following table lists each applicable Facility Interface Code (FIC) along with the Service

Order Code (SOC) and connector jack type for the PmT1 and PmE1.

Facility Interface

Board Name:

PmT1 and PmE1 04DU9.BN

a. Combinations of equipment provide full protection to digital service. Billing protection and encoded analog protection are provided

either by including auxiliary equipment within the registration envelope or by use of a separately registered device.

Code (FIC):

04DU9.DN

04DU9.1KN

04DU9.1SN

Note: The following information and instructions must be given to the final assembler/end user.

FIC

Description:

1.54 Mbps AMI Superframe Format (SF) without

line power

1.544 Mbps SF and B8ZF without line power

1.544 Mbps AMI ESF without line power

1.544 Mbps AMI ESF and B8ZS without line power

Service Order

Code (SOC):

a

6.0N

The mounting of the PmT1 and PmE1 in the final assembly must be made so that the PmT1

and PmE1 is isolated from exposure to hazardous voltages within the assembly. Adequate

separation and restraint of cables and cords must be provided.

The circuitr y from the PmT1 and PmE1 to the telephone line must be provided in wiring

that carries no other circuitry that is specifically allowed in the rules, such as PR and PC

leads.

PC board traces carrying tip and ring leads shall have sufficient spacing to avoid surge

breakdown.

ii

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Jack

Typ e:

RJ48C

Page 5

Regulatory Agency Warnings & Notices (continued)

!

Information shall be provided as to the power source requirements. See the PmT1 and

PmE1 power requirements in the hardware manual.

If the device is enclosed in an assembly, and not readily accessible, a label shall be placed on

the exterior of the cabinet listing the registration number of each PmT1 and PmE1 contained therein.

The final assembler shall provide, in the consumer instructions, all applicable Network Connection Information.

INDUSTRY CANADA RULES AND REGULATIONS — CS03

NOTICE: The Industry Canada label identifies certified equipment. This certification means

that the equipment meets certain telecommunications network protective, operational,

and safety requirements as prescribed in the appropriate Terminal Equipment Technical

Requirements document(s). The Department does not guarantee the equipment will operate to the user’s satisfaction.

Before installing this equipment, users should ensure that it is permissible to be connected

to the facilities of the local telecommunications company. The equipment must also be

installed using an acceptable method of connection. The customer should be aware that

compliance with the above conditions may not prevent degradation of service in some situations.

Repairs to certified equipment should be coordinated by a representative designated by

the supplier. Any repairs or alterations made by the user to this equipment, or equipment

malfunctions, may give the telecommunications company cause to request the user to disconnect the equipment.

Users should ensure for their own protection that the electrical ground connections of the

power utility, telephone lines, and internal metallic water pipe system, if present, are connected together. This precaution may be particularly important in rural areas.

Caution: Users should not attempt to make such connections themselves, but should contact the

appropriate electric inspection authority, or electrician as appropriate.

The standard connecting arrangement code (telephone jack type) for this equipment is

CA48C.

1000236 7-02 PmT1 and PmE 1 User’s Manua l

iii

Page 6

Regulatory Agency Warnings & Notices (continued)

EC Declaration of Conformity

According to EN 45014:1998

Manufacturer’s Name: Emerson Network Power

Embedded Computing

Manufacturer’s Address: 8310 Excelsior Drive

Madison, Wisconsin 53717

Declares that the following product, in accordance with the requirements of 2004/108/EEC, EMC

Directive and 1999/5/EC, RTTE Directive and their amending directives,

Product: PMC Module

Model Name/Number: PmT1 and PmE1/01439143-xx

has been designed and manufactured to the following specifications:

EN55022:1998 Information Technology Equipment, Radio disturbance characteristics, Limits and

methods of measurement

EN55024:1998 Information Technology Equipment, Immunity characteristics, Limits and methods

of measurement

EN300386 V.1.3.1 Electromagnetic compatibility and radio spectrum matters (ERM);

Telecommunication network equipment; EMC requirements

As manufacturer we hereby declare that the product named above has been designed to comply

with the relevant sections of the above referenced specifications. This product complies with the

essential health and safety requirements of the EMC Directive and RTTE Directive. We have an internal production control system that ensures compliance between the manufactured products and

the technical documentation.

Issue date: December 14, 2007

Bill Fleury

Compliance Engineer

iv

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 7

Contents

1Overview

Components and Features . . . . . . . . . . . 1-1

Functional Overview . . . . . . . . . . . . . . . . 1-1

Physical Memory Map . . . . . . . . . . . . . . . 1-2

Additional Information . . . . . . . . . . . . . . 1-4

Product Certification . . . . . . . . . . . . . 1-4

RoHS Compliance. . . . . . . . . . . . . . . . 1-6

Terminology and Notation. . . . . . . . 1-6

Technical References. . . . . . . . . . . . . 1-6

2Setup

Electrostatic Discharge . . . . . . . . . . . . . . 2-1

PmT1 and PmE1 Circuit Board . . . . . . . . 2-1

Connectors . . . . . . . . . . . . . . . . . . . . .2-4

Installation . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

PmT1 and PmE1 Setup . . . . . . . . . . . . . . 2-5

Power Requirements. . . . . . . . . . . . .2-5

Environmental Considerations . . . .2-6

Reset Methods . . . . . . . . . . . . . . . . . . . . . 2-6

Troubleshooting . . . . . . . . . . . . . . . . . . . . 2-6

Technical Support . . . . . . . . . . . . . . .2-7

Product Repair . . . . . . . . . . . . . . . . . . 2-8

3 Central Processing Unit

MPC860P Initialization . . . . . . . . . . . . . . 3-1

MPC860P Exception Handling . . . . . . . . 3-3

CPU Interrupts . . . . . . . . . . . . . . . . . .3-4

System Interface Unit (SIU). . . . . . . . . . . 3-4

Timebase Counter . . . . . . . . . . . . . . .3-5

Decrementer Counter. . . . . . . . . . . .3-5

Software Reset . . . . . . . . . . . . . . . . . . . . . 3-5

MPC860 Parallel Port configuration . . . 3-5

Optional BDM Header . . . . . . . . . . . . . . . 3-6

4 On-Card Memory

Configuration

Socketed Flash . . . . . . . . . . . . . . . . . . . . . 4-1

I2C EEPROM . . . . . . . . . . . . . . . . . . . . . . . . 4-1

I2C EEPROM Operation . . . . . . . . . . . 4-2

Emerson Memory Map . . . . . . . . . . .4-2

On-card DRAM . . . . . . . . . . . . . . . . . . . . . 4-2

On-card Memory Sizing and Type. . 4-3

DRAM Timing . . . . . . . . . . . . . . . . . . .4-3

5 Serial I/O

The Communications Processor Module5-1

CPM Register Initialization Format. 5-2

RISC Controller . . . . . . . . . . . . . . . . . . 5-2

CPM Interrupt Handling . . . . . . . . . . 5-3

Dual-Port RAM . . . . . . . . . . . . . . . . . . 5-3

General Purpose Timers . . . . . . . . . . 5-4

Independent DMA (IDMA) Channels5-4

Serial DMA (SDMA) Channels . . . . . 5-4

MPC860P Serial Interface . . . . . . . . . . . . .5-4

Serial Communication Controllers

(SCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Serial Manag ement Contr ollers

(SMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Time Slot Assigner (TSA) . . . . . . . . . 5-5

UART Baud Rate Selection . . . . . . . . . . . .5-6

Serial Connector Pin Assignments . . . . .5-7

6TDM Interface

The T1 or E1 Line Interface . . . . . . . . . . . .6-4

Configuring the T1 or E1 Interface . . . . .6-5

The T1 FDL Interface . . . . . . . . . . . . . . . . .6-5

The Management Data Interface (MDI) . 6-7

Front Panel I/O . . . . . . . . . . . . . . . . . . . . . .6-8

7PMC/PCI Interface

PCI9060ES Register Map. . . . . . . . . . . . . .7-1

PCI Configuration Registers. . . . . . . 7-1

Local Configuration Registers . . . . . 7-2

Shared Runtime Registers . . . . . . . . 7-3

PCI9060ES Initialization . . . . . . . . . . . . . .7-3

Deadlocked Cycles . . . . . . . . . . . . . . 7-6

Retries on Local Direct Master

Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

Retries on Direct Slave Cycles. .7-6

Assigning Priorities. . . . . . . . . . .7-6

Controlling Access Latency . . . . . . . 7-7

Avoiding the PCI9060ES Phantom

Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Managing Bandwidth . . . . . . . . . . . . 7-8

Bridge to Bridge Considerations. . . 7-8

PCI Interrupts . . . . . . . . . . . . . . . . . . . . . . .7-8

PCI Bus Interface . . . . . . . . . . . . . . . . 7-8

PMC Connector Pin Assignments . . . . . .7-8

PCI Bus Control Signals . . . . . . . . . . 7-10

1000236 7-02 PmT1 and PmE 1 User’s Manua l

v

Page 8

8 Monitor

Power-up/Reset Sequence . . . . . . . . . . . .8-1

Start-up Display . . . . . . . . . . . . . . . . . . . . .8-4

Command-line History . . . . . . . . . . . . . . .8-5

Command-line Editor . . . . . . . . . . . . . . . .8-5

Initializing Memory . . . . . . . . . . . . . . . . . .8-6

Command Syntax. . . . . . . . . . . . . . . . . . . .8-6

Initializing Memory . . . . . . . . . . . . . . . . . .8-7

Command Syntax. . . . . . . . . . . . . . . . . . . .8-7

Typographic Conventions . . . . . . . . 8-7

Boot Commands. . . . . . . . . . . . . . . . . . . . .8-7

bootbus . . . . . . . . . . . . . . . . . . . . . . . .8-7

booteprom . . . . . . . . . . . . . . . . . . . . . 8-8

bootrom. . . . . . . . . . . . . . . . . . . . . . . . 8-9

bootserial. . . . . . . . . . . . . . . . . . . . . . .8-9

Help Commands. . . . . . . . . . . . . . . . . . . 8-10

help. . . . . . . . . . . . . . . . . . . . . . . . . . .8-10

Memory/Register Commands . . . . . . . 8-10

checksummem. . . . . . . . . . . . . . . . .8-10

clearmem . . . . . . . . . . . . . . . . . . . . .8-10

cmpmem . . . . . . . . . . . . . . . . . . . . . .8-10

copymem . . . . . . . . . . . . . . . . . . . . .8-10

displaymem . . . . . . . . . . . . . . . . . . .8-11

fillmem. . . . . . . . . . . . . . . . . . . . . . . .8-11

findmem . . . . . . . . . . . . . . . . . . . . . .8-11

findnotmem . . . . . . . . . . . . . . . . . . .8-11

findstr. . . . . . . . . . . . . . . . . . . . . . . . .8-11

readmem . . . . . . . . . . . . . . . . . . . . . .8-11

setmem . . . . . . . . . . . . . . . . . . . . . . .8-12

swapmem . . . . . . . . . . . . . . . . . . . . .8-12

testmem . . . . . . . . . . . . . . . . . . . . . .8-12

um. . . . . . . . . . . . . . . . . . . . . . . . . . . .8-12

writemem . . . . . . . . . . . . . . . . . . . . .8-12

writestr. . . . . . . . . . . . . . . . . . . . . . . .8-13

NVRAM Commands . . . . . . . . . . . . . . . . 8-13

nvdisplay . . . . . . . . . . . . . . . . . . . . . .8-13

nvinit . . . . . . . . . . . . . . . . . . . . . . . . .8-14

nvopen . . . . . . . . . . . . . . . . . . . . . . . .8-14

nvset. . . . . . . . . . . . . . . . . . . . . . . . . .8-14

nvupdate . . . . . . . . . . . . . . . . . . . . . .8-15

Configuring the Default Boot

Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-15

Power-up Diagnostic/Test Commands8-17

cachetest . . . . . . . . . . . . . . . . . . . . . .8-18

eepromtest . . . . . . . . . . . . . . . . . . . .8-18

memtest . . . . . . . . . . . . . . . . . . . . . .8-18

Remote Host Commands . . . . . . . . . . . 8-18

call. . . . . . . . . . . . . . . . . . . . . . . . . . . .8-19

download . . . . . . . . . . . . . . . . . . . . . 8-19

Binary Download Format . . . . . . . . 8-19

transmode . . . . . . . . . . . . . . . . . . . . 8-20

Configuring the Download Port . . 8-20

Hex-Intel Format . . . . . . . . . . . . . . . 8-21

Extended Address Record . . . . . . . 8-21

Data Record . . . . . . . . . . . . . . . . . . . 8-22

End-of-file Record . . . . . . . . . . . . . . 8-22

Motorola S-record Format . . . . . . . 8-24

S0-records (User Defined) . . . . . . . 8-24

S1-S2-and S3-records

(Data Records) . . . . . . . . . . . . . . . . . . . . . . . . . 8-25

S5-records (Data Count Records). 8-25

S7-S8-and S9-records (Termination and

Start Address Records) . . . . . . . . . . . . . . . . . . 8-26

Utilities. . . . . . . . . . . . . . . . . . . . . . . . . . . 8-27

configboard . . . . . . . . . . . . . . . . . . . 8-27

Arithmetic Commands . . . . . . . . . . . . . 8-27

add . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-27

div. . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-27

mul . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-28

rand . . . . . . . . . . . . . . . . . . . . . . . . . . 8-28

sub . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-28

Errors and Screen Messages . . . . . . . . . 8-28

Monitor Function Reference . . . . . . . . 8-29

PmT1 and PmE1-Specific Functions . . 8-30

ChangeBaud . . . . . . . . . . . . . . . . . . . 8-30

EEPROMAcc . . . . . . . . . . . . . . . . . . . 8-30

getchar . . . . . . . . . . . . . . . . . . . . . . . 8-30

InitBoard . . . . . . . . . . . . . . . . . . . . . . 8-31

Misc . . . . . . . . . . . . . . . . . . . . . . . . . . 8-31

NvHkOffset . . . . . . . . . . . . . . . . . . . . 8-32

NvRamAcc . . . . . . . . . . . . . . . . . . . . 8-32

SetUnExpIntFunct . . . . . . . . . . . . . . 8-33

MPC860P-Specific Functions . . . . . . . . 8-33

Cache . . . . . . . . . . . . . . . . . . . . . . . . . 8-33

Exceptions. . . . . . . . . . . . . . . . . . . . . 8-33

Interrupts . . . . . . . . . . . . . . . . . . . . . 8-35

Status. . . . . . . . . . . . . . . . . . . . . . . . . 8-36

Standard Monitor Functions. . . . . . . . . 8-36

atoh . . . . . . . . . . . . . . . . . . . . . . . . . . 8-36

BootUp . . . . . . . . . . . . . . . . . . . . . . . 8-37

InitFifo . . . . . . . . . . . . . . . . . . . . . . . . 8-38

IsLegal . . . . . . . . . . . . . . . . . . . . . . . . 8-38

MemMng. . . . . . . . . . . . . . . . . . . . . . 8-39

NVSupport . . . . . . . . . . . . . . . . . . . . 8-40

Seed . . . . . . . . . . . . . . . . . . . . . . . . . . 8-42

Serial . . . . . . . . . . . . . . . . . . . . . . . . . 8-42

vi

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 9

Contents (continued)

TestSuite . . . . . . . . . . . . . . . . . . . . . .8-44

xprintf. . . . . . . . . . . . . . . . . . . . . . . . .8-45

9Acronyms

1000236 7-02 PmT1 and PmE 1 User’s Manua l

vii

Page 10

Contents (continued)

viii

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 11

Figures

Figure 1-1: General System Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Figure 1-2: Physical Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Figure 2-1: PmT1 and PmE1 Front Panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

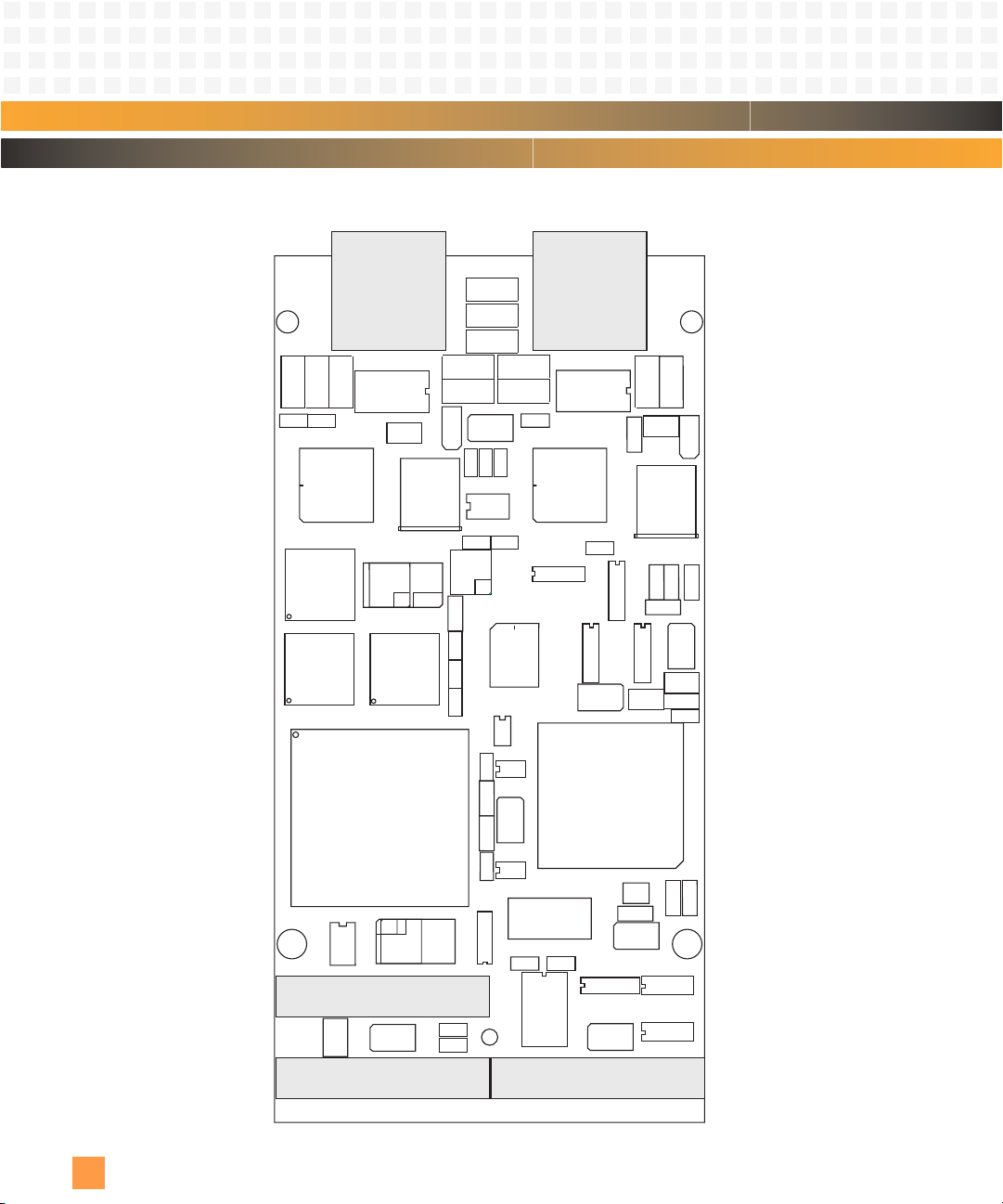

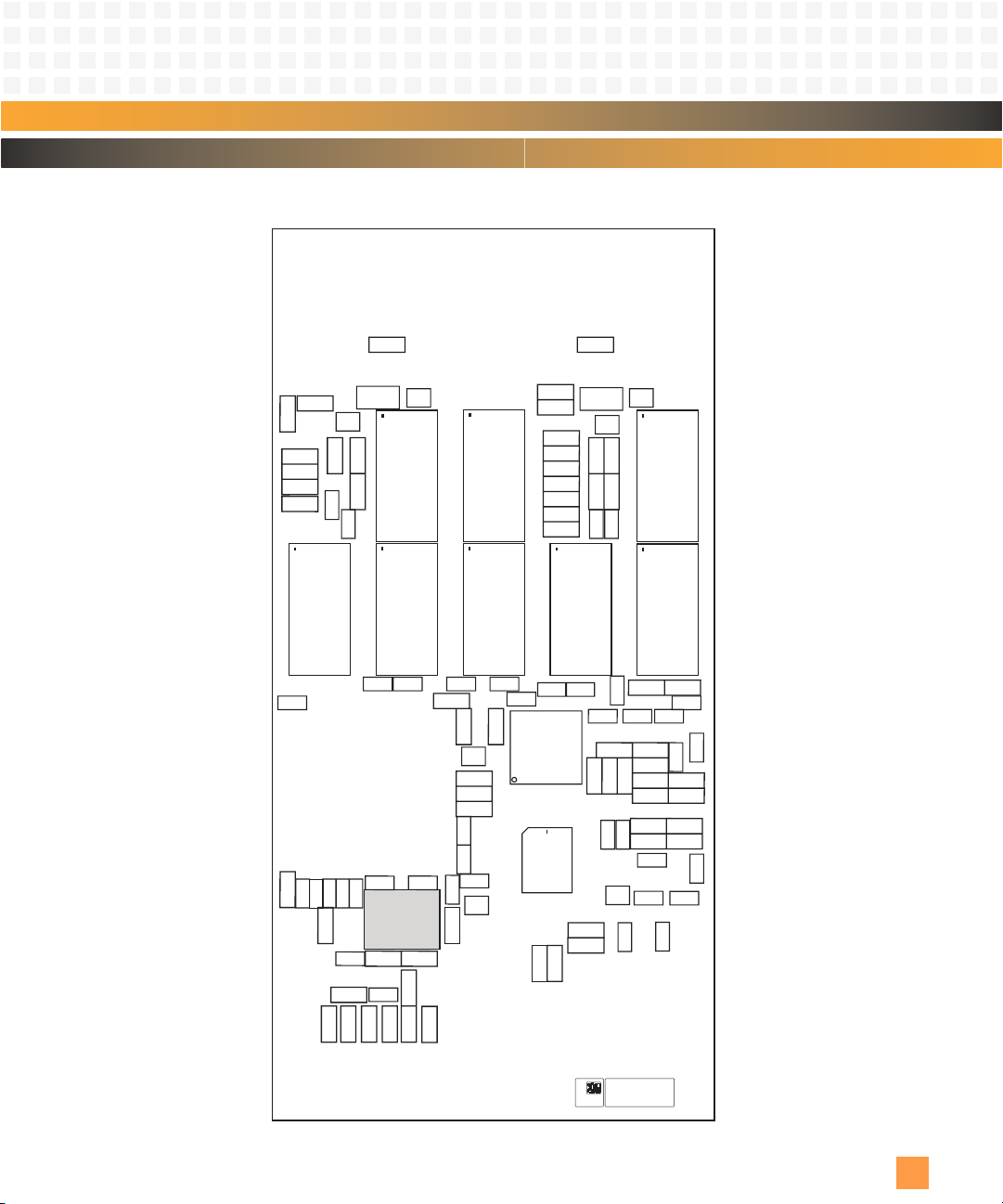

Figure 2-2: Component Map, Top (rev. 33) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-3: Component Map, Bottom (rev. 33) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

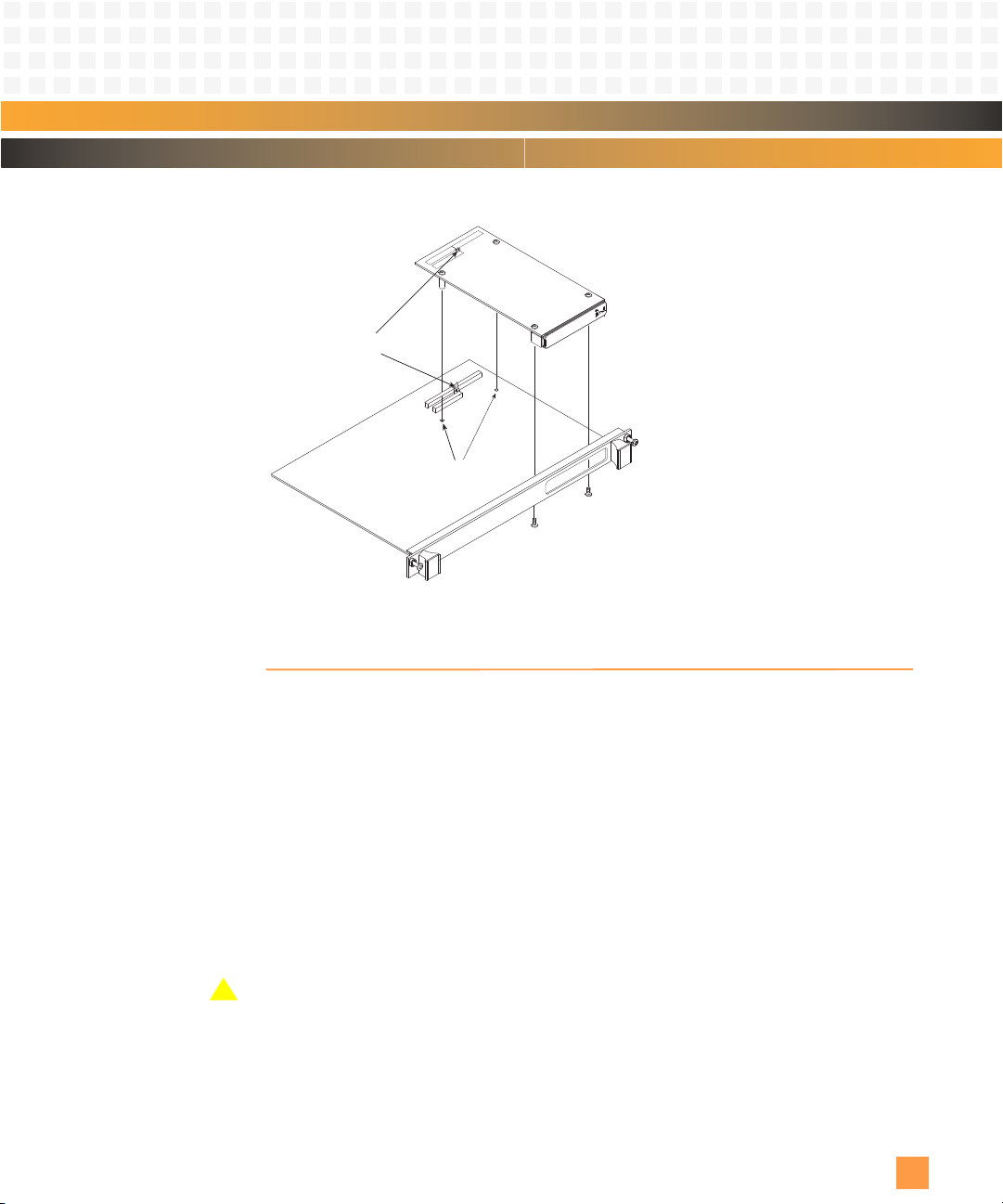

Figure 2-4: PmT1 and PmE1 Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

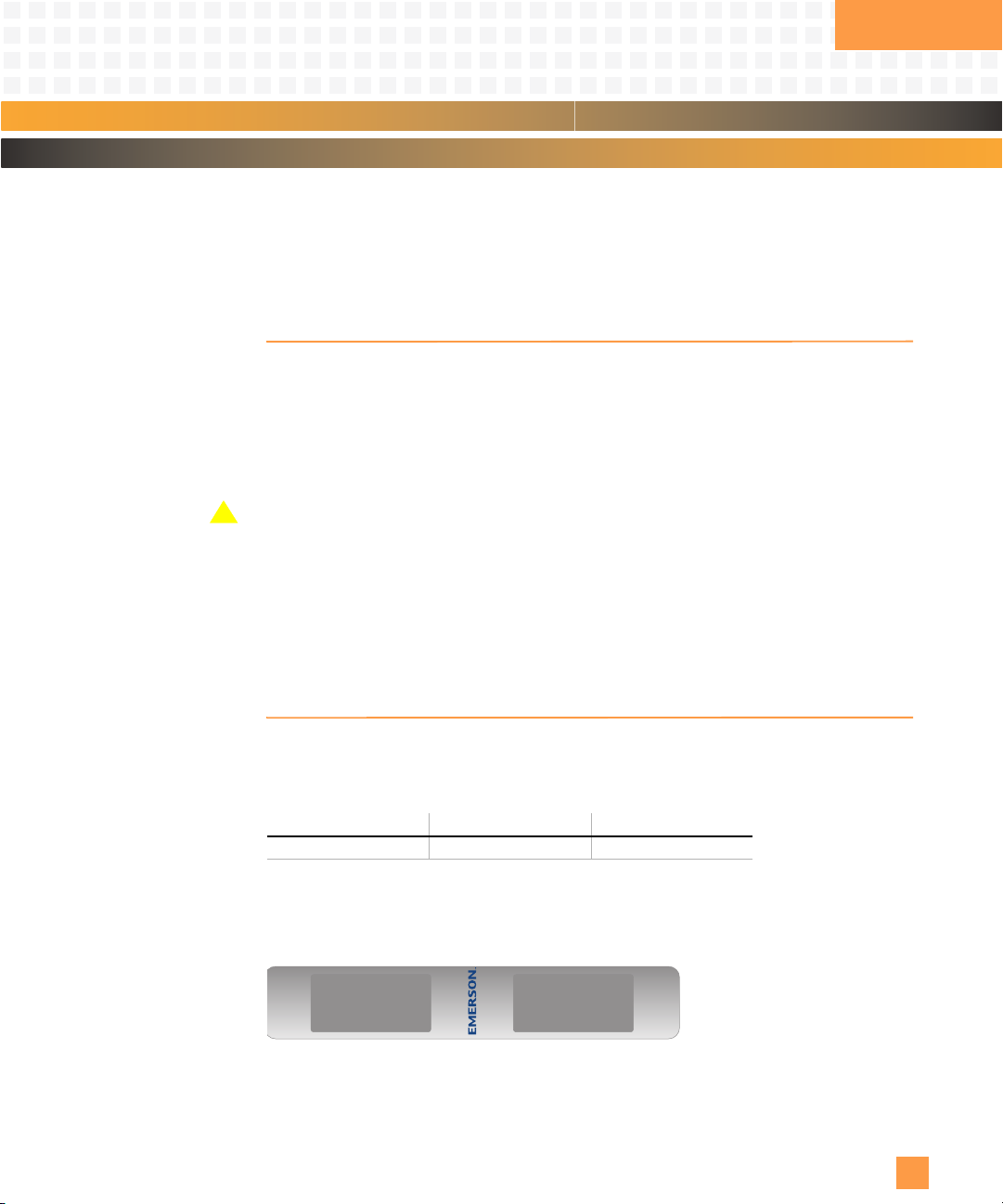

Figure 2-5: Serial Number and Product ID on Bottom Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 3-1: Processor BDM Header. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Figure 6-1: TDM and FDL Connectivity Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Figure 6-2: MDI Interface Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

Figure 6-3: Front Panel I/O Connectors, P1 and P2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

Figure 6-4: Front Panel I/O Cable Assembly (C308A009-05). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

Figure 7-1: PMC Interface Connectors (P11, P12, P14). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Figure 8-1: Monitor Start-up Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

1000236 7-02 PmT1 and PmE 1 User’s Manua l

ix

Page 12

(blank page)

x

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 13

Tab les

Table 1-1: Address Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Table 1-2: MTBF Hours . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Table 1-3: Regulatory Agency Compliance — T1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Table 1-4: Regulatory Agency Compliance — E1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Table 1-5: Technical References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Table 2-1: Circuit Board Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Table 2-2: Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Table 2-3: Environmental Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Table 3-1: MPC860P Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Table 3-2: MPC860P Special Purpose Register Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table 3-3: MPC860P Internal Register Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table 3-4: MPC860P Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Table 3-5: MPC860P SIU Register Block Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Table 3-6: MPC860P Ports A and C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Table 3-7: Processor BDM Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Table 4-1: I2C EEPROM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-2: I2C EEPROM Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Table 4-3: RAM Acess Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Table 5-1: MPC860P CPM Register Block Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Table 5-2: CPM Initialization Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-3: RISC Controller Processing Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-4: Asynchronous Baud Rates (16X oversample). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Table 5-5: Synchronous Baud Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Table 5-6: P14, P0, P2 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Table 6-1: TDM to T1E1 Port Connections for TDMB (P1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

Table 6-2: T1E1 Signals from Transceiver, P1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Table 6-3: TDM to T1E1 Port Connections for TDMA (P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Table 6-4: T1E1 Signals from Transceiver, P2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Table 6-5: FDL QUICC Port Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

Table 6-6: MDI Port Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

Table 6-7: MDI Bit Field Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

Table 6-8: Compu-Shield to RJ45 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

Table 7-1: PCI Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Table 7-2: Local Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Table 7-3: Shared Runtime Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Table 7-4: PCI9060ES PCI Configuration Register Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 7-5: PCI9060ES Local Configuration Register Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 7-6: PCI9060ES Shared Runtime Register Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Table 7-7: PCI9060ES Bus Priority Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Table 7-8: PCI-to-Local Slave Access Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

1000236 7-02 PmT1 and PmE 1 User’s Manua l

xi

Page 14

Table 7-9: Connector P11 and P12 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Table 8-1: NVRAM Configuration Groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

Table 8-2: Device Download Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

Table 8-3: NVRAM Power-up Diagnostic PASS/FAIL Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-17

Table 8-4: PLX Mailbox 0 Sequence and Fail Mask Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-17

Table 8-5: Error and Screen Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-28

Table 8-6: Assigned Exception Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-34

Table 8-7: IsLegal Function Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-39

Table 8-8: NVOp Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-41

Table 8-9: NVOP Error Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-42

xii

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 15

Registers

Register 4-1: Board Configuration 0 (BCR), 0x010 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

1000236 7-02 PmT1 and PmE 1 User’s Manua l

i

Page 16

(blank page)

ii

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 17

Overview

CPU: The CPU for the PmT1 and PmE1 is the Freescale MPC860P PowerQUICC 32-bit micropro-

RAM: The PmT1 and PmE1 module is populated with 16 megabytes of 32-bit wide DRAM.

Flash: The PmT1 and PmE1 module has a 32-pin PLCC flash socket with a 512-kilobyte flash capac-

Section 1

The PmT1 and PmE1 is a single width PMC module designed to provide high-speed T1 and

E1 interfaces for PMC-compatible baseboards. The design is based on the Freescale™

MPC860P PowerQUICC™ microprocessor and the PLX Technology PCI9060ES bus interface

controller. The PmT1 has two standard landed T1 channels, and the PmE1 has two standard

landed E1 channels. An optional EIA-422 port is available.

COMPONENTS AND FEATURES

The following is a brief summary of the PmT1 and PmE1 hardware components and features:

cessor chip running at 80MHz. See Chapter 3 for processor features.

ity.

Serial I/O: The PmT1 and PmE1 module has two EIA-232 I/O ports implemented with two serial man-

agement controllers (SMCs). If the second E1 channel is not required, the PmE1 can be factory configured to additionally provide a single EIA-422 serial port.

T1E1: The PmT1 is factory configured to support the T1 channel using the Dallas Semiconductor

DS2151Q controller. The PmE1 is factory configured to support the E1 channel using the

Dallas Semiconductor DS2153Q controller.

PCI Bus: The PLX Technology PCI9060ES controls the Peripheral Component Interconnect (PCI) bus.

The PmT1 and PmE1 modules appear as peripheral cards to PCI.

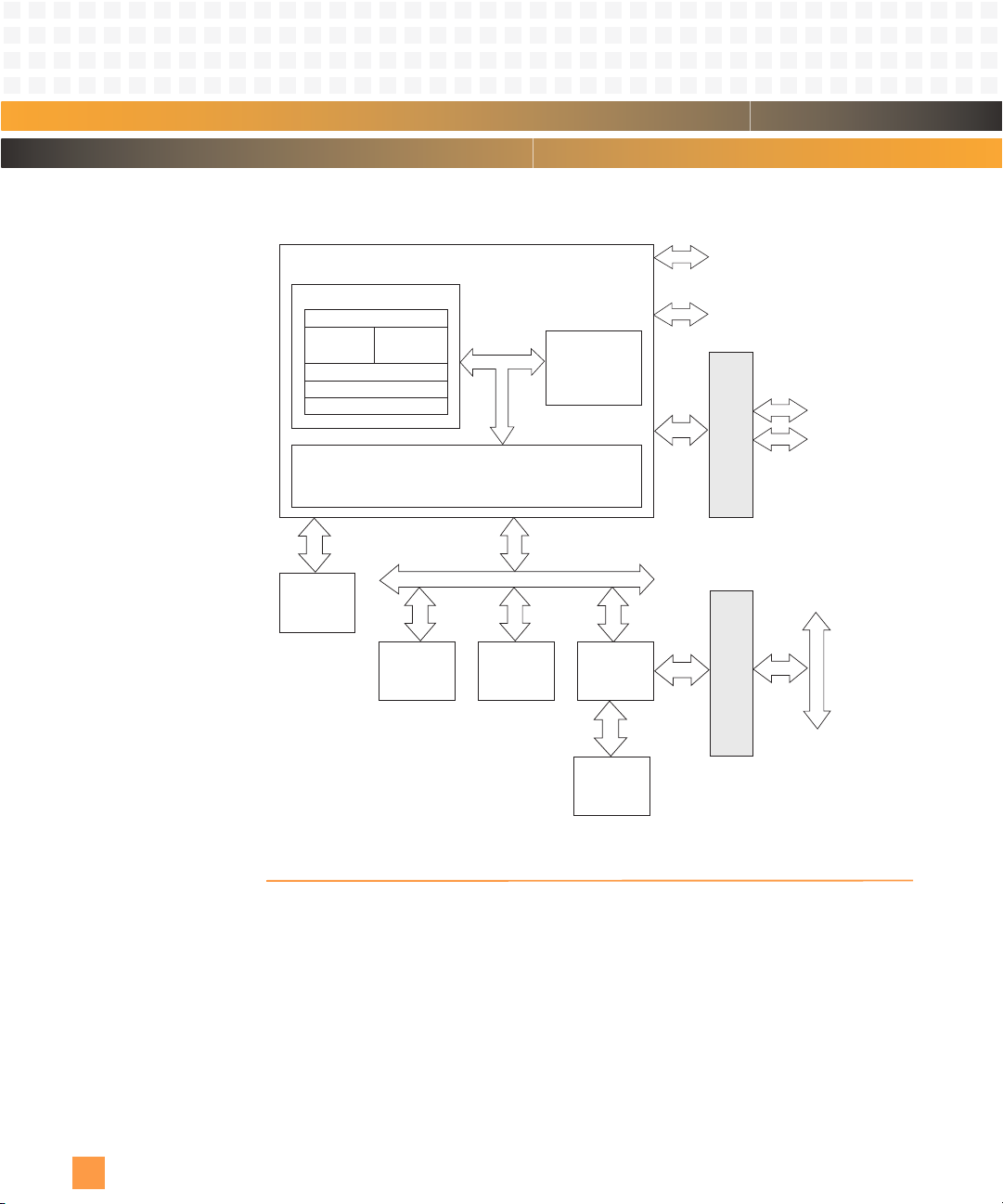

FUNCTIONAL OVERVIEW

The following block diagram provides a functional overview for the PmT1 and PmE1:

1000236 7-02 PmT1 and PmE 1 User’s Manua l

1-1

Page 18

Overview: Physical Memory Map

EIA232 Console

and Download

Serial Ports

CPU

MPC860P

PMC Connectors

P14

System Interface Unit (SIU)

Memory Controller

Internal

Bus Interface

Unit

External

Bus Interface

Unit

PCMCIA-ATA Interface

System Functions

Real-Time Clock

Power PC

Processor Core

32-Bit Bus

Communcations

Processor Module (CPM)

PMC Connectors

P11, P12

PCI Controller

PCI90x0

Serial

EEPROM

128 bytes

EEPROM

2 kilobytes

I C

2

1

A21/D32

A20/D8

A32/D32

32

PmT1 or PmE1

Channel 1

PmT1 or PmE1

Channel 2 or EIA422 Port

DRAM

16 megabytes

PCI

PCI

Flash/ROM

Socket

512 kilobytes

Figure 1-1: General System Block Diagram

1-2

PHYSICAL MEMORY MAP

The physical memory map of the PmT1 and PmE1 is depicted in Fig. 1-2. Information on particular portions of the memory map can be found in later sections of this manual. See

Tab l e 1- 1 for a list of these references.

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 19

PMC/PCI Interface Registers

Board Configuration Register

Reserved

Reserved

Reserved

Reserved

CPU Registers

IDs / Interrupts

PCI I/O Space

PCI Memory Space

DRAM

Hex Address

FFFF,FFFF

FFF0,0000

FF00,0000

C101,0000

C100,0000

C000,0200

C000,0180

C000,0000

8000,0000

6000,0000

4000,0000

0100,0000

0000,0000

C000,0080

Reserved

Flash/ROM Socket

Overview: Physical Memory Map

Figure 1-2: Physical Memory Map

1000236 7-02 PmT1 and PmE 1 User’s Manua l

1-3

Page 20

Overview: Additional Information

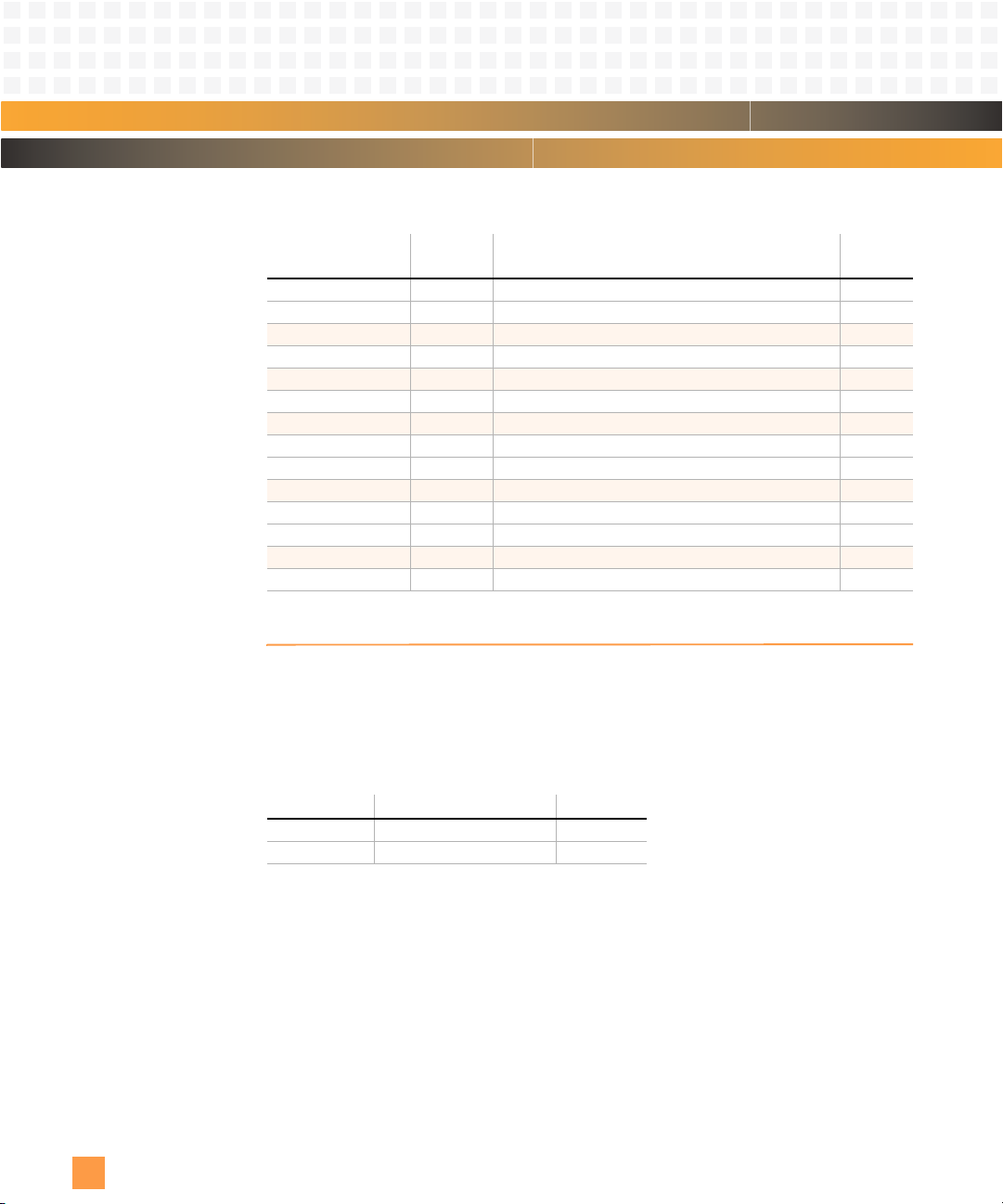

Tab le 1-1 : Address Summary

Physical Address

(hex):

FFF0,0000 R Flash/ROM Socket 4-1

FF00,0000 R/W CPU registers 3-2

C101,0 000 — reserved —

C100,0000 R/W PMC/PCI Interface registers 7-2

C000,0 200 — reserved —

C000,0180 R Board Configuration register 4-3

C000,0 080 — reserved —

C000,000C R Conventional Interrupt register 3-4

C000,0000 R Interrupt Vec tor regist er 3-4

8000,0000 — reserved —

6000,0 000 R/W PCI I/O Space 7-2

4000,0 00 R/W PCI Memor y Space 7-2

C101,0 000 — reserved —

0000,0000 R/W DRA M 4-2

ADDITIONAL INFORMATION

This section lists the PmT1 and PmE1 hardware’s regulatory certifications and briefly discusses the terminology and notation conventions used in this manual. It also lists general

technical references.

Mean time between failures (MTBF) is listed in the following table:

Tab le 1-2 : MTBF Hours

Access

Mode: Description:

See

Page:

Product Calculation Method: Hours:

PmT1 Bellcore Issue 5 344,234

PmE1 Telecordia Issue 1 1,333,573

Product Certification

The PmT1 and PmE1 hardware has been tested to comply with various safety, immunity,

and emissions requirements as specified by the Federal Communications Commission

(FCC), Underwriters Laboratories (UL), and others. The following table summarizes this

compliance:

1-4

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 21

Overview: Additional Information

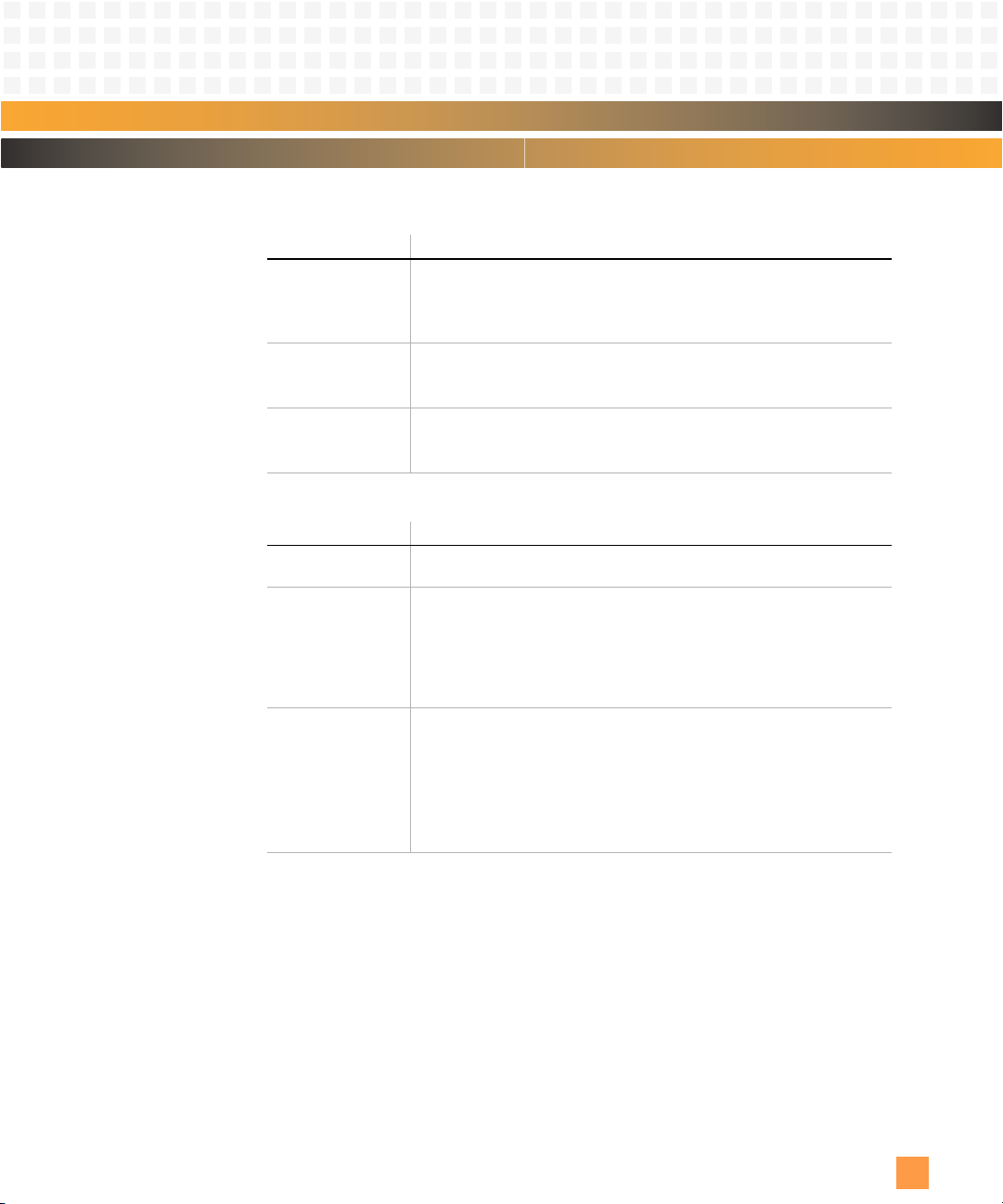

Tab le 1-3 : Regulatory Agency Compliance — T1

Type: Specification:

Safety UL60950-1, CSA C22.2 No. 60950-1-03, 1st Edition – Safety of

Information Technology Equipment, including Electrical Business

Equipment (BI-National)

Global IEC – CB Scheme Report IEC 60950, all country deviations

Telecom FCC Part 68 – Title 47, Code of Federal Regulations, Radio

Frequency Devices

IC CS03 – Radiated and Conducted Emissions, Canada

EMC FCC Part 15, Class A – Title 47, Code of Federal Regulations, Radio

Tab le 1-4 : Regulatory Agency Compliance — E1

Type: Specification:

Safety IEC60950/EN60950 – Safety of Information Technology Equipment

Telecom CTR012 – Business Telecommunications; Open Network Provision

EMC EN55022 – Information Technology Equipment, Radio Disturbance

Frequency Devices

ICES 003, Class A – Radiated and Conducted Emissions, Canada

(Western Europe)

technical requirements; 2048 kbits/s digital unstructured leased line

attachment requirements for terminal equipment.

CTR013 – Business Telecommunications Open Network Provision

technical requirement, 2048 kbits/s structured, leased line attachment

requirements for terminal equipment.

Characteristics, Limits and Methods of Measurement

EN55024 – Information Technology Equipment, Immunity

Characteristics, Limits and Methods of Measurement

ETSI EN300386 – Electromagnetic Compatibility and Radio Spectrum

Matters (ERM), Telecommunication Network Equipment,

Electromagnetic Compatibility (EMC) Requirements

Emerson maintains test reports that provide specific information regarding the methods

and equipment used in compliance testing. Unshielded external I/O cables, loose screws, or

a poorly grounded chassis may adversely affect the PmT1 and PmE1 hardware’s ability to

comply with any of the stated specifications.

The UL web site at ul.com has a list of Emerson’s UL certifications. To find the list, search in

the online certifications directory using Emerson’s UL file number, E190079. There is a list

for products distributed in the United States, as well as a list for products shipped to Canada. To find the PmT1 and PmE1, search in the list for 01439143-xx, where xx changes with

each revision of the printed circuit board.

1000236 7-02 PmT1 and PmE 1 User’s Manua l

1-5

Page 22

Overview: Additional Information

RoHS Compliance

The PmT1 and PmE1 are compliant with the European Union’s RoHS (Restriction of Use of

Hazardous Substances) directive created to limit harm to the environment and human

health by restricting the use of harmful substances in electrical and electronic equipment.

Effective July 1, 2006, RoHS restricts the use of six substances: cadmium (Cd), mercury

(Hg), hexavalent chromium (Cr (VI)), polybrominated biphenyls (PBBs), polybrominated

diphenyl ethers (PBDEs) and lead (Pb). Configurations that are 5-of-6 are built with tin-lead

solder per the lead-in-solder RoHS exemption.

To obtain a certificate of conformity (CoC) for the PmT1 and PmE1 modules, send an

e-mail to sales@artesyncp.com or call 1-800-356-9602. Have the part number(s) (e.g.,

C000####-##) for your configuration(s) available when contacting Emerson.

Terminology and Notation

Active low signals: An active low signal is indicated with an asterisk * after the signal name.

Byte, word: Throughout this manual byte refers to 8 bits, word refers to 16 bits, and long word refers to

32 bits, double long word refers to 64 bits.

PLD: This manual uses the acronym, PLD, as a generic term for programmable logic device (also

known as FPGA, CPLD, EPLD, etc.).

Radix 2 and 16: Hexadecimal numbers end with a subscript 16. Binary numbers are shown with a

subscript 2.

Technical References

Further information on basic operation and programming of the PmT1 and PmE1 components can be found in the following documents:

Tab le 1-5 : Technical References

Device / Interface: Document: 1

Controller, T1/E1 DS2153Q, E1 Single Chip Transceiver Data Sheet

(Dallas Semiconductor, REV: 01106)

DS2151Q, T1 Single Chip Transceiver Data Sheet

(Dallas Semiconductor, REV: 011706)

Application Note 342; DS2151, DS2153 Initialization and Programming

(Dallas Semiconductor, 102899)

http://www.maxim-ic.com/

CPU MPC860P PowerQUICC™ Technical Summary

(Freescale Semiconductor, 07/2004 Rev. 3)

http://www.freescale.com/

1-6

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 23

Overview: Additional Information

Device / Interface: Document: 1 (continued)

EEPROM CAT93C86 (Die Rev. C) 16-Bit Microwire Serial EEPROM

PCI PCI Local Bus Specification

PMC Draft Standard for a Common Mezzanine Card Family: CMC P1386/Draft 2.0

Serial Interface EIA Subcommittee TR-30.2 on Interface, EIA Standard RS-232-D

1. Frequently, the most current information regarding addenda/errata for specific documents may be

found on the corresponding web site.

(Catalyst l Semiconductor, Inc.., Doc. No. 1091, Rev. O, 10/13/06)

http://www.catsemi.com/

(PCI Special Interest Group, Revision 2.1 1995)

http://www.pcisig.com /

PCI9060ES PCI Bus Master Interface Chip for Adapters and Embedded

Systems–data sheet

(Mountain View, CA: PLX Technology, Inc., December1995 VERSION 1.2)

http://www.plxtech.com/

April 4, 1995

(IEEE:N ew York, NY)

Draft Standard Physical and Environmental Layers for PCI Mezzanine Cards:

PMC P1386.1/Draft 2.0 April 4, 1995

(IEEE: New York, NY)

http://www.ieee.org/

(Electronic Industries Association, August 1969)

http://www.eia.org/

1000236 7-02 PmT1 and PmE 1 User’s Manua l

1-7

Page 24

Overview: Additional Information

1-8

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 25

Setup

!

TDM B

TDM A

Section 2

This chapter describes the physical layout of the boards, the setup process, and how to

check for proper operation once the boards have been installed. This chapter also includes

troubleshooting, service, and warranty information.

ELECTROSTATIC DISCHARGE

Before you begin the setup process , please remember that electrostatic discharge ( ESD) can

easily damage the components on the PmT1 and PmE1 hardware. Electronic devices, especially those with programmable parts, are susceptible to ESD, which can result in operational failure. Unless you ground yourself properly, static charges can accumulate in your

body and cause ESD damage when you touch the board.

Caution: Use proper static protection and handle the PmT1 and PmE1 board only when absolutely

necessary. Always wear a wriststrap to ground your body before touching a board. Keep

your body grounded while handling the board. Hold the board by its edges–do not touch

any components or circuits. When the board is not in an enclosure, store it in a staticshielding bag.

To ground yourself, wear a grounding wriststrap. Simply placing the board on top of a staticshielding bag does not provide any protection–place it on a grounded dissipative mat. Do

not place the board on metal or other conductive surfaces.

PMT1 AND PME1 CIRCUIT BOARD

The PmT1 and PmE1 circuit board is a PMC module assembly. It uses an eight-layer printed

circuit board with the following dimensions:

Tab le 2-1 : Circuit Board Dimensions

Width: Depth: Height:

5.86 in. (148.8 mm) 2.913 in. (74.0 mm) .39 in. (10.0 mm)

The following figures show the front panel and component maps for the PmT1 and PmE1

circuit board.

Figure 2-1: PmT1 and PmE1 Front Panel

1000236 7-02 PmT1 and PmE 1 User’s Manua l

2-1

Page 26

Setup: PmT1 and PmE1 Circuit Board

C1

C10

C12 C13

C14

C15

C16

C17

C18

C19

C2

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C3

C30

C4

C5

C6

C7

C8

C9

L1

L2

P1

P11

P12

P14

P2

R1

R10R11

R12

R13

R14

R5

R6

R7

R8

R9

RN1

RN2

S1

S2

U1

U100

U101

U12

U14

U15

U16

U17

U18

U19

U2

U20

U21

U22

U3

U4

U5

U6

U8

U9

X5

Y4

Y5

U13

U10

U7

U11

F1

F2 F3 F4

F5

F6

F7

F8

F9

F11

F13

F15

Y1

Y2

Y7

Y3

Y6

PCI90x0

MPC860

T1/E1

T1/E1

Figure 2-2: Component Map, Top (rev. 33)

2-2

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 27

Setup: PmT1 and PmE1 Circuit Board

R19

R18

U25 U24 U23

U30 U29 U28 U27 U26

CR2/CR6

CR1/CR4

CR5

CR3

CR8

CR7

CR9

CR10

CR11

C67

U31

U32

R69 R68

R71

R16

R74

R73

R75

R72

R17

R15

R63

R66

R52

R55

R56

R59

R60

R57

R58

R48

R42

R47

R54

P3

R53

R46

R43

R64

R62

R65

R51

R50

R49

R41

R40

R39

R45

R44

R25

R29

R30

R24

R23

R36

R33

R26

R22

R31

R32

R37

R38

R20

R21

R27

R28

R34

R35

R2

R3

R4

C11

C33

C32

C31

C51

C54

C47

C43

C48

C49

C50

C52

C66

C65

C58

C61

C62

C63

C64

R61

C46

C39

C38

C37

C36

C45

C35

C34

C44

C42 C41

C40

C60

C59

C57

C53

C56 C55

C68

R67

R70

10001234-AA

D

590-

YYYYY

Figure 2-3: Component Map, Bottom (rev. 33)

1000236 7-02 PmT1 and PmE 1 User’s Manua l

2-3

Page 28

Setup: Installation

Connectors

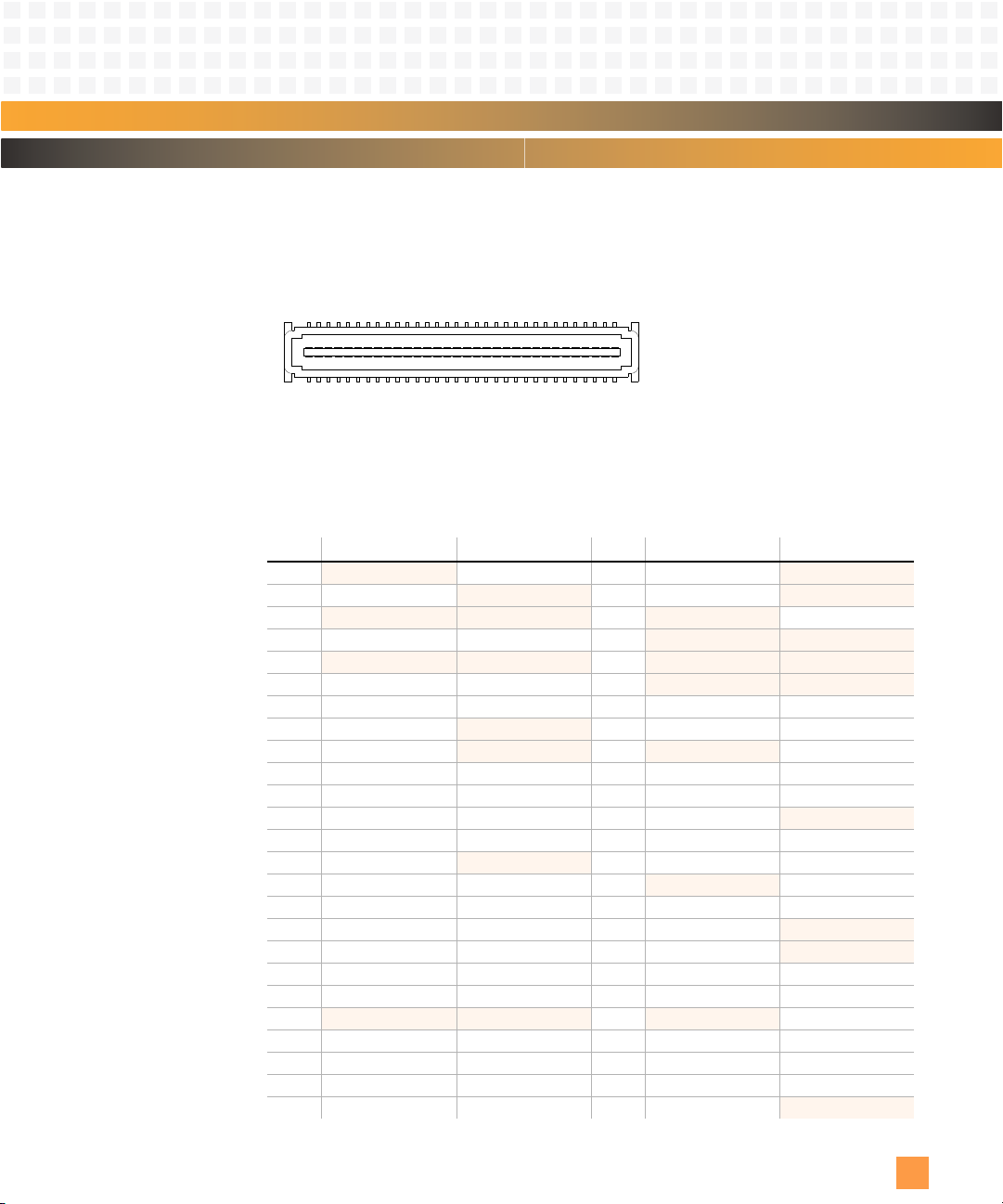

The PmT1 and PmE1 circuit board has various connectors (see the figures beginning on

page 2-2), summarized as follows:

P1/P2: These connectors are installed for the PmT1 front panel I/O configurations. See Chapter 6

for pin assignments.

P3: This is the optional 10-pin BDM JTAG header for viewing processor functions. See

for pin assignments.

P11/P12: These provide a 32-bit PCI interface between the module and the PMC baseboard. Pin

assignments are shown in Chapter 7.

P14: This is the I/O connector for the EIA-422 and EIA-232 serial ports. See Chapter 5 for pin

assignments.

Tab l e 3- 7

INSTALLATION

The PmT1 and PmE1 module may be installed in either expansion site on the baseboard. To

attach the module to your baseboard, follow these steps:

1 Remove the loosely installed screws from the standoffs on the PmT1 and PmE1 module.

2 Line up the P11, P12, and P14 connectors and the 5V keying hole with the PMC connectors

and the keying pin on the baseboard. Press the module into place, making sure that the

connectors are firmly mated and the module front panel is fully seated in the baseboard

front panel.

3 From the back of the baseboard, insert and tighten the two screws in the standoffs closest

to the PMC connectors.

2-4

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 29

Setup: PmT1 and PmE1 Setup

Tighten these two screws first.

Voltage key

!

Figure 2-4: PmT1 and PmE1 Installation

4 Insert and tighten the two remaining screws.

PMT1 AND PME1 SETUP

You need the following items to set up and check the operation of the Emerson PmT1 and

PmE1:

❐ Five-volt compatible PMC baseboard

❐ Chassis and power supply

❐ Serial interface cable for EIA-232 port, Emerson part #C0006322-xx0

❐ Two Compu-shield to RJ45 cable assemblies (Emerson part number C308A009-xx) for

front panel I/O configurations

❐ Computer terminal

Save the antistatic bag and box for future shipping or storage.

Caution: Do not install the board in a rack or remove the board from a rack while power is applied, at

risk of damage to the board.

Power Requirements

The Emerson PmT1 and PmE1 circuit board typically requires 6.7 watts maximum.

1000236 7-02 PmT1 and PmE 1 User’s Manua l

2-5

Page 30

Setup: Reset Methods

Tab le 2-2 : Power Requirements

Volts: Range (volts): Maximum Current:

+5 +/- 5% 1.16 A, typical

1. Running on-card memory test.

The exact power requirements for the PmT1 and PmE1 circuit board depend upon the specific configuration of the board, including the CPU frequency and amount of memory

installed on the board. Please contact Emerson Technical Support at 1-800-327-1251 if you

have specific questions regarding the board’s power requirements.

Environmental Considerations

As with any printed circuit board, be sure that air flow to the board is adequate. Chassis constraints and other factors greatly affect the air flow rate. The environmental requirements

are listed in

Tab le 2-3 : Environmental Requirements

Tab l e 2 -3 .

Environment: Range: Relative Humidity:

Operating Temperature 0° to +55° Centigrade, ambient

Storage Temperature —40° to 70° Centigrade Not to exceed 95%

Air Flow 50 linear feet/minute n/a

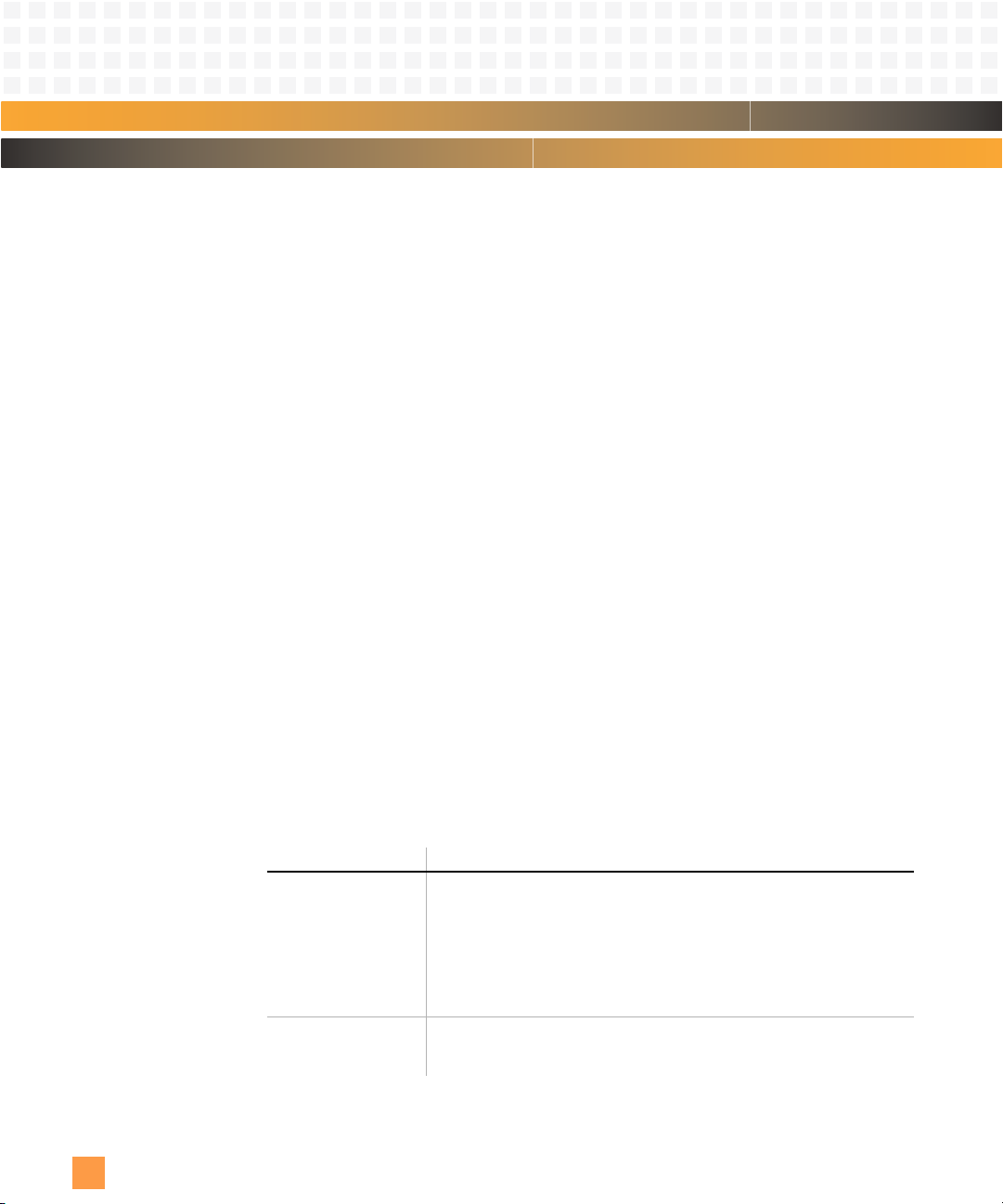

RESET METHODS

The entire board is reset on power-up. A baseboard PCI reset causes a PORESET* of the

PmT1 and PmE1. The PCI9060ES may be programmed to initiate a software controlled hard

reset from the PCI bus.

(at board)

1

Not to exceed 95% (noncondensing)

(non-condensing)

To do a hard reset of the PmT1 and PmE1 from the local bus, clear and then set bit 16 in the

PCI9060ES register at local address C100,00EC

To do a hard reset of the PmT1 and PmE1 from the PCI bus, the same bit must be cleared

and then set in software. However, the PCI bus is little endian so this bit appears as bit 8

from the (big-endian) point of view of the MPC860P. This means that bit 8 of the register at

offset 6C

from the PCI base address must be cleared and then set. After this reset, the

16

module must be reconfigured on PCI by the baseboard.

TROUBLESHOOTING

In case of difficulty, use this checklist:

2-6

PmT1 and PmE1 Us er’s Manual 1000236 7-02

16

.

Page 31

Setup: Troubleshooting

❐ Be sure the PmT1 and PmE1 circuit board is seated firmly in the baseboard and that the

baseboard is fully plugged in the chassis.

❐ Be sure the system is not overheating.

❐ Check the cables and connectors to be certain they are secure.

❐ If you are using the PmT1 and PmE1 monitor, run the power-up diagnostics and check

the results. “Power-up Diagnostic/Test Commands”, Section describes the power-up

diagnostics.

❐ Check your power supply for proper DC voltages. If possible, use an oscilloscope to look

for excessive power supply ripple or noise (over 50 mV

❐ Check that your terminal is connected to serial port A (SMC1).

❐ The PmT1 and PmE1 monitor uses values stored in on-card NVRAM (I

configure and set the baud rates for its console port. The lack of a prompt might be

caused by incorrect terminal settings, and incorrect configuration of the NVRAM, or a

malfunctioning NVRAM. Try holding down the H character during a reset to abort

autoboot using NVRAM parameters. If the prompt comes up, the NVRAM console

parameters are probably configured incorrectly. Enter the command nvopen, then the

command nvdisplay, to check the console configuration. For more information about

the way NVRAM is used to configure the console port baud rates, refer to Chapter 8.

below 10 MHz).

pp

2

C EEPROM) to

Technical Support

If you need help resolving a problem with your PmT1 and PmE1, visit

http://www.emersonembeddedcomputing.com/contact/postsalessupport.html on the

Internet or send e-mail to support@artesyncp.com. If you do not have internet access, call

Emerson for fur ther assistance:

(800) 327-1251 or (608) 826-8006 (US)

44-131-475-7070 (UK)

Have the following information available when contacting support:

• PmT1 and PmE1 serial number and product identification (see

• monitor version (see

• the baseboard serial number and product identification

• version and part number of the operating system (if applicable) This information is

labeled on the master media supplied by Emerson or another vendor.

• whether your board has been customized for options such as a higher processor speed

or additional memory

Fig. 8- 1 start-up display)

1000236 7-02 PmT1 and PmE 1 User’s Manua l

Fig. 2-5)

2-7

Page 32

Setup: Troubleshooting

10001234-AA

D

590-

YYYYY

Serial number

Product ID

10001234-AA

D

590-

YYYYY

• license agreements (if applicable)

Figure 2-5: Serial Number and Product ID on Bottom Side

Product Repair

If you plan to return the board to Emerson Network Power for service, visit

http://www.emersonembeddedcomputing.com/contact/productrepair.html on the internet or send e-mail to serviceinfo@artesyncp.com to obtain a Return Merchandise Authorization (RMA) number. We will ask you to list which items you are returning and the board

serial number, plus your purchase order number and billing information if your PmT1 and

PmE1 hardware is out of warranty. Contact our Test and Repair Services Department for

any warranty questions. If you return the board, be sure to enclose it in an antistatic bag,

such as the one in which it was originally shipped. Send it prepaid to:

Emerson Network Power, Embedded Computing

Test and Repair Services Department

8310 Excelsior Drive

Madison, WI 53717

RMA #____________

Please put the RMA number on the outside of the package so we can handle your problem

efficiently. Our service department cannot accept material received without an RMA number.

2-8

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 33

Central Processing Unit

The PmT1 and PmE1 module uses the Freescale MPC860P PowerQUICC™ microprocessor

installed as its CPU. The MPC860P combines an embedded PowerPC™ core with features of

the QUICC MC68360 communications processor module (CPM). This chapter is an overview

of the processor logic on the PmT1 and PmE1. It includes information on the CPU, exception handling, and processor reset.

Tab le 3-1 : MPC860P Features

Feature: Description:

Instruction Set 32-bit

System Clock Rate 80 MhZ

Data Bus 32-bit

Address Bus 32-bit

Cache 16K instruction, 8K data

MMU 32-entr y instruction and data Translation Look-aside Buffer (TLB)

Dual-port RAM 8K

ATM 10/100 base-T Ethernet, QMC microcode for multichannel HDLC support

Serial Channel four SCCs, two SMCs, one SPI and on I

System Interface

Unit (SIU)

DMA channels 16 virtual SDMA and 2 IDMA

Dynamic bus sizing 8-, 16-, or 32-bits

Voltages 3.3V operation with 5V TTL compatibility

Memory controller, internal and external bus interface units, real-time clock,

PCMIA-ATA interface, and JTAG TAP

2

C interface

Section 3

Beyond the usual CPU functions, the MPC860P provides:

• A DRAM controller is contained in the system interface unit (SIU). The memory

controller is described in the “On-card DRAM”, Section .

• Four high-speed SCC serial ports are supported by the CPM. The serial interface is

described in Chapter 5

MPC860P INITIALIZATION

Some of the MPC860P registers must be initialized with Emerson-specific values. The values in the following tables assume a PmT1 and PmE1 configuration of 9600 baud, 40-MHz

and CPU speed.

The relevant special purpose registers on the MPC860P are accessed with the Move to Special Registers (mtspr) and the Move from Special Registers (mfspr) instructions.

1000236 7-02 PmT1 and PmE 1 User’s Manua l

3-1

Page 34

Central Processing Unit: MPC860P Initialization

Tab le 3-2 : MPC860P Special Purpose Register Initialization

Decimal

Address: Register:

148 ICR 0000,0000 Interrupt cause

149 DER 0000,0000 Debug enable

158 ICTRL 0000,0000 Instruction support control

638 IMMR FF00,00 00 Inter nal memor y map se ts up the base add ress of

— MSR 1002 Machine State register (control)

Required

Hex Format: Notes:

The internal registers of the MPC860P are mapped to a contiguous 16-kilobyte block of

memory space on a 64-kilobyte boundary. The special purpose register IMMR specifies the

base address of this block. The following table is for the four megabyte PmT1 and PmE1,

some values may change for different configurations.

Tab le 3-3 : MPC860P Internal Register Initialization

Physical

Address (hex): Register:

General SIU

FF00,0 000 SIUMCR 7062,3900 SIU module con figuration

FF00,0004 SYPCR FFFF,FF08 System protection control

MEMC

FF00,0100 BR0 FFF0,0501 Base register bank 0

FF00,0104 OR0 FFF8,09F4 Option register bank 0

FF00,0108 BR1 0000,0081 Base register bank 1

FF00,010C OR1 FFC0,0000 Option register bank 1

FF00,0110 BR2 0040,0081 Base register bank 2

FF00,0114 OR2 0000,0000 Option register bank 2

FF00,0118 BR3 C100,0001 Base register bank 3

FF00,011C OR3 FFFF,8128 Option register bank 3

FF00,0120 BR4 — Base register bank 4

FF00,0 124 OR4 C0 00,0128 Option register bank 4

FF00,0130 BR6 C000,0401 Base register bank 6

FF00,0134 OR6 FF80,0120 Option register bank 6

FF00,0170 MAMR 4E82,1113 Machine A mode

System Integration Timers

FF00,0200 TBSCR 00C2 Timebase status and control

FF00,0240 PISCR 0082 PIT status and control

Clocks and Reset

FF00,0280 SCCR 0200,0000 System clock control

Input/Output Por

the MPC860P internal register block

Required

Hex Format: Description:

3-2

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 35

Central Processing Unit: MPC860P Exception Handling

Physical

Address (hex): Register:

FF00,0950 PADIR 000A Port A data direction register

FF00,0952 PAPAR 0000 Port A pin assignment register

FF00,0954 PADDR 0000 Port A open drain register

BRGs

FF00,09F0 BRGC1 10144 BRG1 configuration register

FF00,09F4 BRGC2 10144 BRG2 configuration register

SMC s

FF00,0A82 SMCMR1 4823 SMC1 mode register

FF00,0A92 SMCMR2 4823 SMC2 mode register

PIP

FF00,0AB8 PBDIR 0030 Port B data direction register

FF00,0ABC PBPAR 00C0 Port B pin assignment register

FF00,0AC2 PBODR 0010 Port B open drain register

SI

FF00,0AE0 SIMODE 1000,0000 SI mode register

FF00,0AEC SICR 0000,0000 SI clock route

MPC860P EXCEPTION HANDLING

Each type of CPU exception transfers control to a different address in the vector table. The

vector table normally occupies the first 8-kilobytes of RAM (with a base address of

0000,0000

may be used to point to an error routine or for code or data storage.

exceptions recognized by the MPC860P in the order of their priority

Tab le 3-4 : MPC860P Exceptions

) or flash (with a base address of FFF0,000016). An unassigned vector position

16

Required

Hex Format: Description: (continued)

Tab l e 3- 4 lists the

Vec tor Ad dre ss

Exception:

Development port NMI 01F00 Highest priority

NMI reset 00100

Tr ac e 0 0D 0 0

Instruction TLB miss 01100

Instruction TLB error 01300

Machine check 00200

Instruction breakpoint 01D00

Software emulation 01000

Alignment 00600

System call 00C00

Data TLB miss 01200

Hex Offset: Notes:

1000236 7-02 PmT1 and PmE 1 User’s Manua l

3-3

Page 36

Central Processing Unit: System Interface Unit (SIU)

Vec tor Ad dre ss

Exception:

Data TLB error 01400

Data breakpoint 01C00

Peripheral breakpoint 01E00

External interrupt 00500

Decrementer Decrementer Lowest priority

CPU Interrupts

The logic on the PmT1 and PmE1 module receive external interrupts LSERR* and LINTo*

from the PCI9060ES chip. These interrupts are combined on IRQ7*, which is the only external interrupt input used on the MPC860P.

The Conventional Interrupt register and the Interrupt Vector register are available to monitor the status of the external interrupts. These registers are byte wide and read-only.

Attempts to read these registers with data sizes greater than a byte does not result in a bus

error.

Hex Offset: Notes: (continued)

The Conventional Interrupt register at C000,000C

are active. If bit 5 is one, LSERR* is active. If bit 4 is one, LINTo* is active. All other bits in this

register read as zero.

Bits (4:2) of the Interrupt Vector register (at C000,0000

priority external interrupt that is pending. The vector for LSERR* is 100

LINTo* is 011

. The vector 0002 indicates that no interrupt is pending.

2

Internal interrupt sources including the hardware bus monitor, the software watchdog

timer, the periodic interrupt timer (PIT), the real-time clock, and the CPM may each be

assigned to a particular interrupt level in software. Interrupt levels may be programmed for

logic low or negative edge assertion.

SYSTEM INTERFACE UNIT (SIU)

The SIU provides the MPC860P with system configuration and monitoring features. In particular, two system timers are described in the following subsections. The memory controller is also part of the SIU but is described in the “On-card DRAM”, Section .

Tab le 3-5 : MPC860P SIU Register Block Map

Physical Hex

Address: Acronym: Register Block Name:

FF00,0000 SIU General System Interface Unit

FF00,0 080 — reserved

FF00,0 100 MEMC Memor y controller

indicates which PCI9060ES interrupts

16

) store the vector of the highest

16

; the vector for

2

3-4

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 37

Central Processing Unit: Software Reset

Physical Hex

Address: Acronym: Register Block Name: (continued)

FF00,0200 — System integration timers

FF00,0280 — Clocks and reset

FF00,0300 — System integration timers keys

FF00,0380 — Clocks and reset keys

Timebase Counter

This 64-bit counter provides a timebase reference for software. The counter generates a

maskable interrupt when it reaches the value programmed into one of four reference registers. On the PmT1 and PmE1, the timebase clock source is the system clock divided by 16.

Decrementer Counter

This 32-bit counter provides a decrementer interrupt. It is clocked by the same source as the

timebase counter (system clock divided by 16).

SOFTWARE RESET

The MPC860P may be reset in software via the PCI9060ES PCI interface chip. Writing a one

to bit 30 at local address C100,00EC holds the local bus logic in the PCI9060ES reset and

LRESETO* asserted. The contents of the PCI configuration registers and Shared Runtime

registers are not reset. The PCI adapter software reset can only be cleared from the PCI bus.

To do a hard reset of the PmT1 and PmE1 from the local bus, clear and then set bit 16 in the

PCI9060ES register at local address C100,00EC

16

.

To do a hard reset of the PmT1 and PmE1 from the PCI9060ES device, the same bit must be

cleared and then set in software. However, the PCI is little endian so this bit appears as bit 8

from the (big-endian) point of view of the MPC860P. This means that bit 8 of the register at

offset 6C

from the PCI base address must be cleared and then set. After this reset, the

16

module must be reconfigured on PCI by the baseboard.

MPC860 PARALLEL PORT CONFIGURATION

The following values set up the MPC860 parallel ports to receive RCLK from the incoming

T1/E1 stream, route the clock to the respective Baud Rate Generator (TDMA: BRGO2,

TDMB: BRGO4), then output the clock from the Baud Rate Generator as TCLK.

padir 0 x44F0

papr 0xEFFF

pcdir 0x0002

pcpar 0x0F00

1000236 7-02 PmT1 and PmE 1 User’s Manua l

3-5

Page 38

Central Processing Unit: Optional BDM Header

Tab l e 3- 6 lists the implementation of the MPC860 Port A and C signals used on the PmT1

and PmE1 module.

Tab le 3-6 : MPC860P Ports A and C

MPC860 Pin: MPC860 Signal: Use:

PA15 RXD1 Facility Data Link (FDL A)

PA1 4 TX D1 F DL( A)

PA13 RXD2 FDL(B)

PA12 TXD2 FDL(B)

PA1 1 L1 TXD B T DMB

PA1 0 L1 RXD B TD MB

PA9 L1 TXDA TDM A

PA8 L1 RXDA TDM A

PA7 CLK1/L1 RCLK A TDMA

PA6 CL K2 TDMA

PA5 BR GO2 TDM A

PA4 CL K4 FDL

PA3

PA2 CLK6/L1 RCLK B TDM B

PA1 BR GO4 TDM B

PA0 CLK8/L1 TCLKB TDMB

PC15 — Management Data Interface (MDI)

PC14 — MDI

PC13 — MDI

PC12

PC11

PC10

PC9

PC8

PC7 L1TSYNCB TDMB

PC6 L1RSYNCB TDMB

PC5 L1TSYNCA TDMA

PC4 L1RSYNCA TDMA

PC3

reser ved —

reser ved —

reser ved —

reser ved —

reser ved —

reser ved —

reser ved —

OPTIONAL BDM HEADER

An optional 10-pin header (P3) is available for examining processor functions. The recommended mating connector is AMP part number 746288-1. The standard pin assignment is

shown in

3-6

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Tab l e 3 -7 .

Page 39

Central Processing Unit: Optional BDM Header

1

2

9

10

Figure 3-1: Processor BDM Header

Tab le 3-7 : Processor BDM Pin Assignments

Pin

Number:

1 VFLSO Visible History Buffer Flushes Status 0 output line reports how

2 SRESET* Software Reset input signal may initiate a warm reset.

3GND1Ground 1

4 TCK Test Clock input scan data is latched at the rising edge of this signal

5GND2Ground 2

6 VFLS1 Visible History Buffer Flushes Status 1 output line reports how

7 HRESET* Hardware Reset input signal is used at power-up to reset the

8 TDI Test Data Input signal acts as the input port for scan instructions

93_3V +3.3 Voltage

10 TDO Test Data Output signal acts as the output port for scan (JTAG)

Signal

Name: Description:

many instructions were flushed from the history buffer in the

MPC860P internal core.

(1K ohm pull-up to +5 volts, input to board, JTAG bit clock).

many instructions were flushed from the history buffer in the

MPC860P internal core.

processor.

and data (1K ohm pull-up to +5 volts, input to board, JTAG data in).

instructions and data.

1000236 7-02 PmT1 and PmE 1 User’s Manua l

3-7

Page 40

Central Processing Unit: Optional BDM Header

3-8

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 41

On-Card Memory Configuration

!

The PmT1 and PmE1 module provides one 32-pin flash socket, an EEPROM, and one RAM

configuration. Off-card memory may be accessed via the PMC/PCI interface.

SOCKETED FLASH

The PmT1 and PmE1 modules have a 32-pin PLCC socket for a byte-wide read-only flash. Up

to 512-kilobytes of flash may be installed. The socketed flash occupies physical address

space FFF0,0000-FFFF,FFFF

Note: To avoid damage, please use the proper tool to remove the PLCC device.

The MPC860P controls the access time for flash. The default power-up timing allows flash

with speeds of 200-nanoseconds or faster. We strongly suggest that you use the default

timing because of the inherent risks of optimizing timing for a specific configuration, and

because of the fact that flash may be cached.

Caution: The monitor resides within this socketed device (ROM address: 0x0 - 0x30000) and should

not be overwritten.

16

.

Section 4

I2C EEPROM

Another memory device on the PmT1 and PmE1 is a 16-kilobit serial EEPROM. It is internally

organized as 1Kx16 and is accessed through the I

EEPROM supports a sixteen-byte page write mode and a self-timed write cycle. It provides a

minimum endurance of 100,000 cycles and a minimum data retention of 100 years.

2

C interface consists of the Serial Clock (SCL) and the Serial Data (SDA) lines, which are

The I

controlled by bits in the PBDIR and PBDAT registers, and accessible with longword

read/write.

Tab le 4-1 : I2C EEPROM Regi sters

Hex Address: Register Name: Bit: Access: Description:

FF00,0AB8 Port B Direction

FF00,0AC4 Port B Data

FF00,0AC4 PBDAT 27 W I

FF00,0AC4 PBDAT 27 R I

(PBDIR)

(PBDAT)

2

C interface pins on the MPC860P. The

27 R/W Set SDA as an input or an output.

0= Input

1= Output

2

26 R/W I

C EEPROM Clock Line (SCL)

0= Drives SCL low

1= Drives SCL high

2

C EEPROM Line Driver (SDA)

0= Drives SDA low

1= Drives SDA high

2

C EEPROM Data on D0 (SDA)

1000236 7-02 PmT1 and PmE 1 User’s Manua l

4-1

Page 42

On-Card Memory Configuration: On-card DRAM

I2C EEPROM Operation

The I2C EEPROM supports a bidirectional bus-oriented protocol. The protocol defines any

device that sends data onto the bus as a transmitter and the receiving device as the receiver.

The device controlling the transfer is the CPU, and the I

slave. The CPU always initiates data transfers and provides the clock for both transmit and

receive operations.

Initialization software for the I

lowed by a stop condition to reset EEPROM to a known state, since the chip maintains its

state even between power-ups.

Emerson Memory Map

The following memory map convention has been established by Emerson for data storage

within the I

parameters without affecting each other.

Tab le 4-2 : I2C EEPROM Memory Map

Hex Byte Offset: Description:

400—7FF User nonvolatile data storage

300—3FF Reserved for the operating system

000—2FF Reserved for the monitor

2

C EEPROM. This map allows various operating systems to store their boot

2

C EEPROM should issue a start condition immediately fol-

2

C EEPROM being controlled is the

ON-CARD DRAM

The PmT1 and PmE1 support 16-megabyte DRAM configuration four bytes wide, for data

storage. On-card RAM occupies physical addresses starting at 0000,0000

Note: All accesses to on-card DRAM must be aligned to natural boundaries. For example, byte accesses must be

aligned to byte boundaries, word accesses to word boundaries, and long-word accesses to long-word boundaries.

The DRAM is controlled by the MPC860P DRAM controller. The controller may be programmed for most memory sizes and speeds, block sizes from 32-kilobytes to 4-gigabytes,

and write protection.

In addition to the basic DRAM control functions the MPC860P chip provides several additional DRAM-related functions. Performance enhancing features include: programmable

delay insertion for controlling RAS recovery time, RAS low time, CAS setup before RAS time,

row address hold time, CAS recovery time, CAS pulse width, CAS access time, and address

access time.

4-2

PmT1 and PmE1 Us er’s Manual 1000236 7-02

16

.

Page 43

On-Card Memory Configuration: On-card DRAM

On-card Memory Sizing and Type

The Board Configuration register (C000,018016) is a byte-wide, read-only register that contains configuration information about the MPC860P and DRAM. Bit (5) is no parity. The configuration registry values are factory set.

Register 4-1: Board Configuration 0 (BCR), 0x010

7654 3 210

LBS 1 0MEMSNOBMEMSNOB

LBS: Local Bus Speed

00 Reserved

01 33.33 MHz with 66.66 MHz processor

10 40.00 MHz with 40.00 MHz processor

11 40.00 MHz with 80.00 MHz processor

Bit 4: On-card memory type valued

0 Fast page mode (FPM)

1 Synchronous DRAM (not available)

MEMS/NOB: Memory Size/Number of Banks

0000-0111 Reserved

1000 16/one bank of 16M x 32

DRAM Timing

One of the primary functions of the MPC860P is to allow flexible control of all important

DRAM timing parameters. The correct DRAM timing for any reasonable combination of

board speed and DRAM speed is handled by the user-programmable machine (UPM). The

timing parameters are stored in the UPM’s internal RAM. Reference Chapter 16 in the

MPC860 PowerQUICC™ User’s Manual (Freescale 07/2004, Revision 3) for more details about

the UPM.

Tab le 4-3 : RAM Acess Time

Cycle: Total Clocks: Wait States:

Reads 4

Writes 3

Burst Read (4

accesses)

Tab l e 4- 3 describes the wait states for the PmT1 and PmE1 module.

1

2

4

1

2

3

1

8

2

7

1000236 7-02 PmT1 and PmE 1 User’s Manua l

1

3

2

3

1

2

2

2

3-1-2-1

3-1-1-1

1

2

4-3

Page 44

On-Card Memory Configuration: On-card DRAM

Cycle: Total Clocks: Wait States: (continued)

Burst Write (4

accesses)

1. At 40 MHz local bus speed.

2. At 33 MHz local bus speed.

7

5

1

2

2-1-1-1

2-1-1-1

1

2

For non-burst cycles, the number in the “Total Clocks” column of Tab l e 4 - 3 is the total number of CPU clock cycles required to complete the transfer, and the number in the “Wait

States” column is the number of wait states per cycle.

For burst cycles, the number in the “Total Clocks” column of

Ta bl e 4 - 3 is the total number of

CPU clocks for the first access of the four long-word burst, plus the number of clocks for the

second, third, and fourth cycles. The number in the “Wait States” column is the number of

wait states for each of the four accesses.

4-4

PmT1 and PmE1 Us er’s Manual 1000236 7-02

Page 45

Serial I/O

Section 5

The PmT1 and PmE1 module has six TTL serial ports that are supplied by the MPC860P PowerQUICC™. The MPC860P supports the serial ports with the following features:

• Communications Processor Module (CPM), which includes a RISC controller, 224 buffer

descriptors, continuous mode transmission and reception on all serial channels, dualport RAM, fourteen serial DMA (SDMA) channels, and NMSI mode (each serial channel

can have its own pins)

• Four serial communication controllers (SCCs)

• Two serial management controllers (SMCs) for the console and download serial ports

• Four baud rate generators that are independent (i.e., can be connected to any SCC or

SMC), allow changes during operation, and have autobaud support

• Protocols in firmware for asynchronous/synchronous UARTs, HDLC, and SS7

For detailed descriptions of the MPC860P features and examples of how to implement

them, refer to the MPC860 PowerQUICC™ User’s Manual.

THE COMMUNICATIONS PROCESSOR MODULE

The physical base address of the MPC860P is FF00,000016. The following table shows the

register block map for the CPM portion of the MPC860P. Please refer to the MPC860 Power-

QUICC™ User’s Manual for descriptions of the registers in each register block.

Tab le 5-1 : MPC860P CPM Register Block Map

Physical Address (hex): Acronym: Register Block Name:

FF00,0930 — CPM Interrupt Control

FF00,0950 — Input/Output Por t

FF00,0980 — CPM Timers

FF00,09C0 — Communication Processor

FF00,0 9F0 BRG Baud Rate Generators

FF00,0A00 SCC1 Serial Communications Controller 1

FF00,0A20 SCC2 Serial Communications Controller 2

FF00,0A40 SCC3 Serial Communications Controller 3

FF00,0A60 SCC4 Serial Communications Controller 4

FF00,0A82 SMC1 Serial Management Controller 1

FF00,0A9 SMC2 Serial Management Controller 2

FF00,0A82 — reserved

FF00,0 AE0 SI Serial I nterface

1000236 7-02 PmT1 and PmE 1 User’s Manua l

5-1

Page 46

Serial I/O: The Communications Processor Module

CPM Register Initialization Format

Some of the CPM registers must be initialized as described in Tab le 5 - 2 .

Tab le 5-2 : CPM Initialization Values

Physical Address

(hex): Acronym:

Input/Output Port

FF00,0950 PADIR 000A Port A Data Direction register

FF00,0952 PAPAR 0000 Port A Pin Assignment register

FF00,0954 PAODR 0000 Port A Open Drain register

BRGs

FF00,09F0 BRGC1 10144 BRG1 Configuration register

FF00,09F4 BRGC2 10144 BRG2 Configuration register

FF00,0AC2 PBODR 0010 Port B Open Drain register

SMC s

FF00,0A82 SMCMR1 4823 SMC1 mode register

FF00,0A92 SMCMR2 4823 SMC2 mode register

SI

FF00,0AE0 SIMODE 1000,0000 SI Mode register

FF00,0AEC SICR 0000,0000 SI Clock route

Required

Hex Format: Description:

RISC Controller

The RISC controller manages the serial interface to the CPM. It services all I/O requests,

allowing the CPU on the PmT1 and PmE1 module to dedicate compute time to other tasks.

The RISC controller implements user-chosen protocols, manages serial DMA transfers and