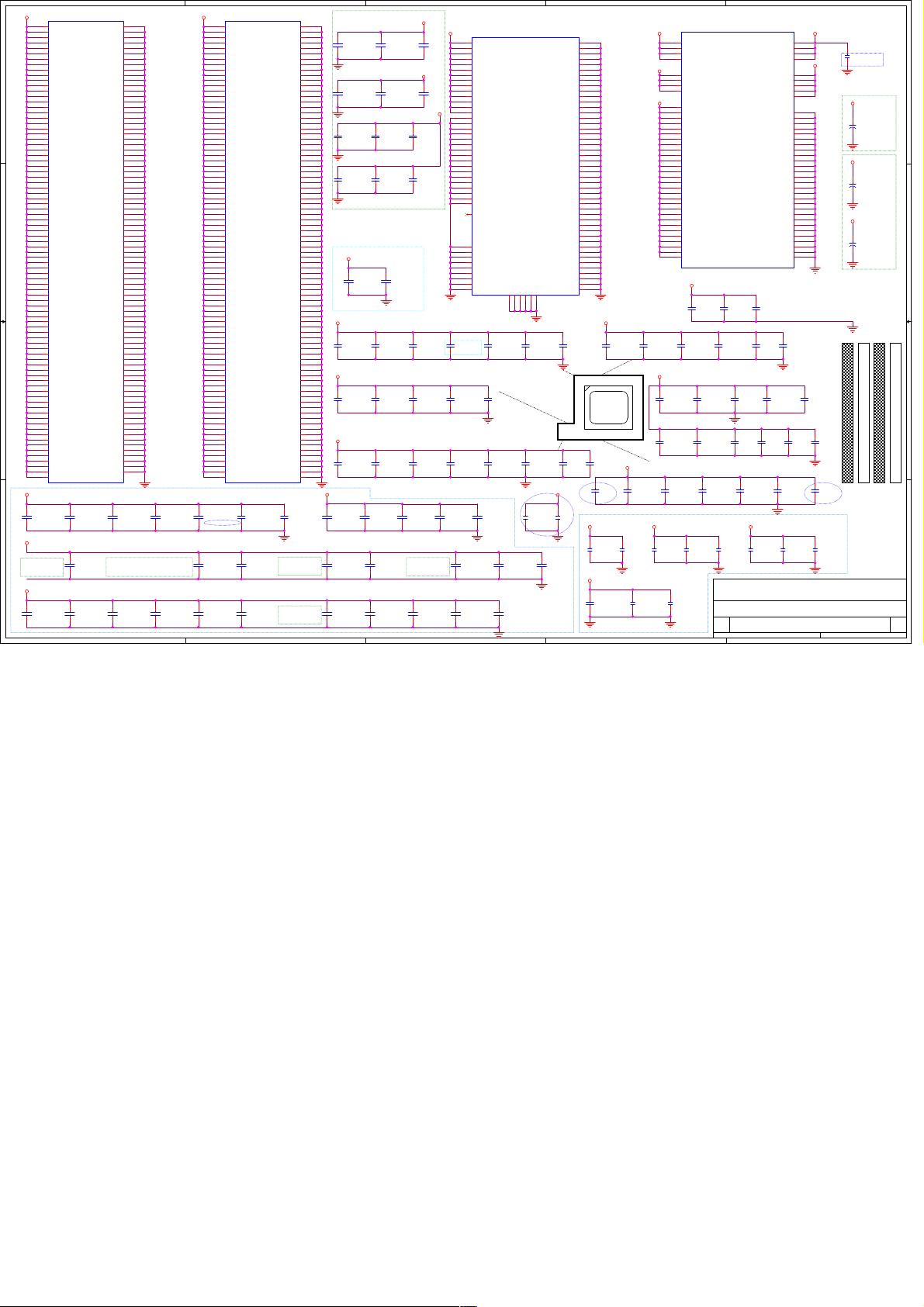

Page 1

5

4

3

2

1

D D

RS880PM-AM

VER:1.0.

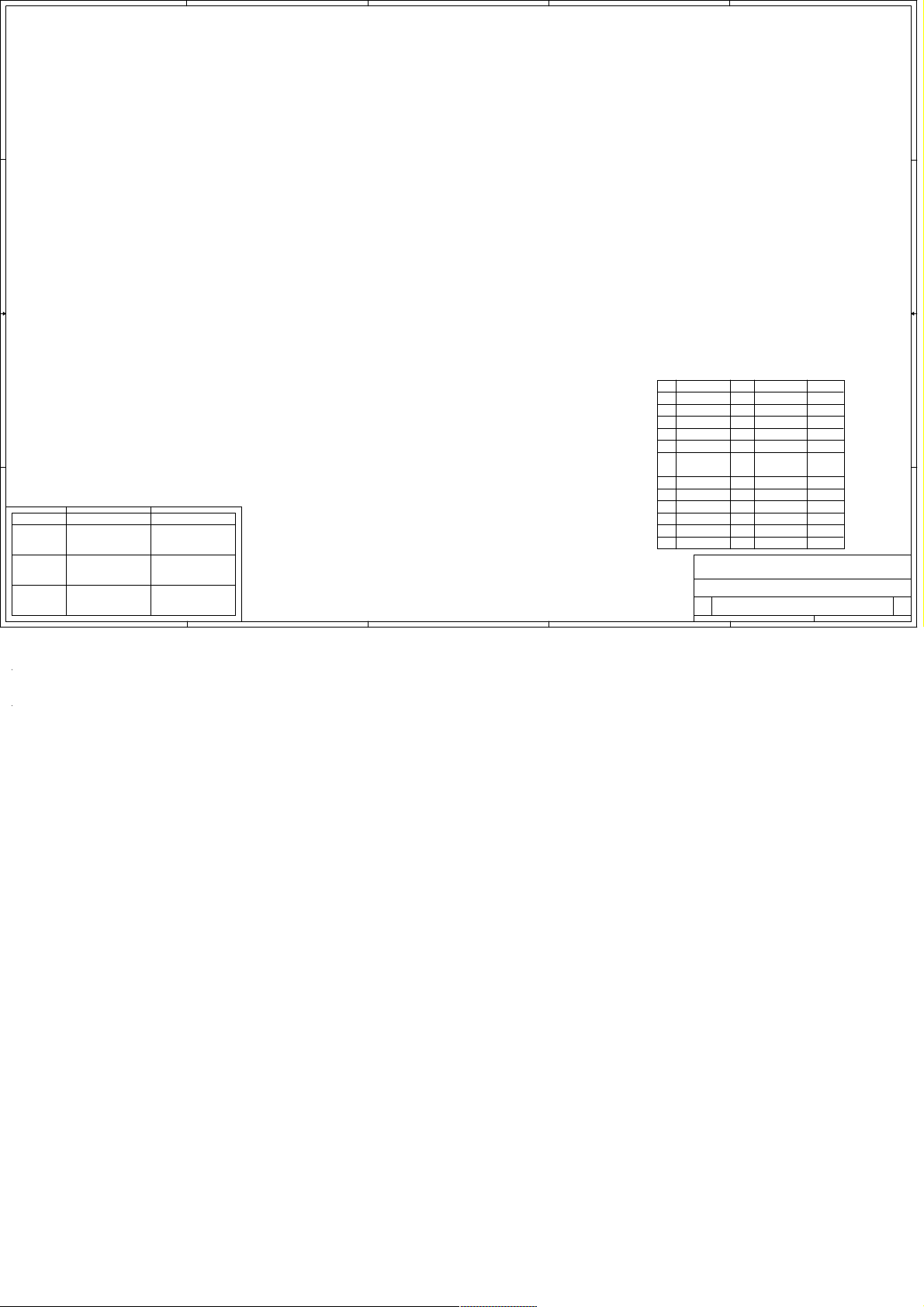

SCHEMATICS TABLE:

Page Index

------- ------------------------

1

COVER PAGE

BLOCK DIAGRAM2

3

HT,CPU MEMORY

CPU CONTROL & MISC

4

CPU PWR & GND

C C

5

CPU HDT

6

Firs Logic DDR3 DIMM

7

Second Logic DDR3 DIMM

8

RS880P-HT LINK I/F

9

RS880P-PCIE I/F

10

RS880P-SYSTEM I/F

11

RS880P-SPMEM/STRAPS

12

13

B B

Job

Schematics

A A

Designer

Layout

Approval

SB950 PCIE/PCI/CPU/LPC/CLK

14

SB950 ACPI/GPIO/USB/AZ/EC

15

SB950 SATA/FC/HWM/SPI

16

SB950 POWER & DECOUPLING

17

SB950 STRAPS

18

Signature

Dennis/Scott

5

Date

03/08/'11~

01/08/'11

03/08/'11

Page Index

------- ------------------------

VGA / HDMI

19

PCIE/16X/1X

20

USB,5VDUAL SWITCH

21

PCI SLOT

22

SIO-F71869A

23

FAN,PS2,FAN

24

LAN Realtek 8111E-VL

25

26

AUDIO ALC662-VC

27

Audio Connector(PANEL)

28

ETRON EJ168 USB3.0 HOST

29

CPU VCORE ISL6328CRZ

30

DC POWER, DDRIII POWER

NB/SB CORE POWERRS880P-POWER

31

PANEL,ATX24P

32

Attention

33

34

Misc.

35 Reset Diagram

36 Power Distribution

37 History

L1:TOPPCB STACK:

L2:PWR

L3:GND

(1)47079_2_02 AMD Family 15h Processor Electrical Data Sheet (NDA)_2010-03-xx

(2)46103_rs880_dg_nda_1.06 RS880-Series IGP Motherboard Design Guide (NDA)_2010-09-07

(3)48702_sb9xx_dg_nda_1.00 SB9xx Motherboard Design Guide (NDA)_2010-08-20

(4)Ref.Dory_D(RS880P/SB950) Dory Schematic for AM3r2 (PDF)_2010-11-29

4

L4:BOTTOM

PCB Size : 244x244x1.6mm,4L(62mil=1.57mm),1080-prepreg

3

2

AM3+ Stackup(1080 prepreg,4L)

Layer Material

Solder Mask

Plating

Cu

L1

Dielectric

(HRC)

Cu

L2

Dielectric

L3 Cu

Dielectric

(HRC)

Cu

L4

Plating 1.0 0.0356

Solder Mask 0.0254

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Hight(mm) Hight(mil)

OZ

0.0254

0.0356

1.0

0.0178

0.5

0.0686

/2.0 /0.0711

1.0

0.03555

1.1379

1.0/2.0

0.03555/0.0711

0.0686

0.0178

0.5

1.5748

Total

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Cover Page

Cover Page

Cover Page

RS880PM-AM

RS880PM-AM

RS880PM-AM

1.00

1.40

0.7

2.70

1.40/2.80

44.8

1.40/2.80

2.70

0.7

1.40

1.00

1

GECS

1.4~1.9

1.4~1.9

1

1

1

Intel-6

1.9

1.9

1.0.

1.0.

1.0.

of

37Thursday, May 26, 2011

of

37Thursday, May 26, 2011

of

37Thursday, May 26, 2011

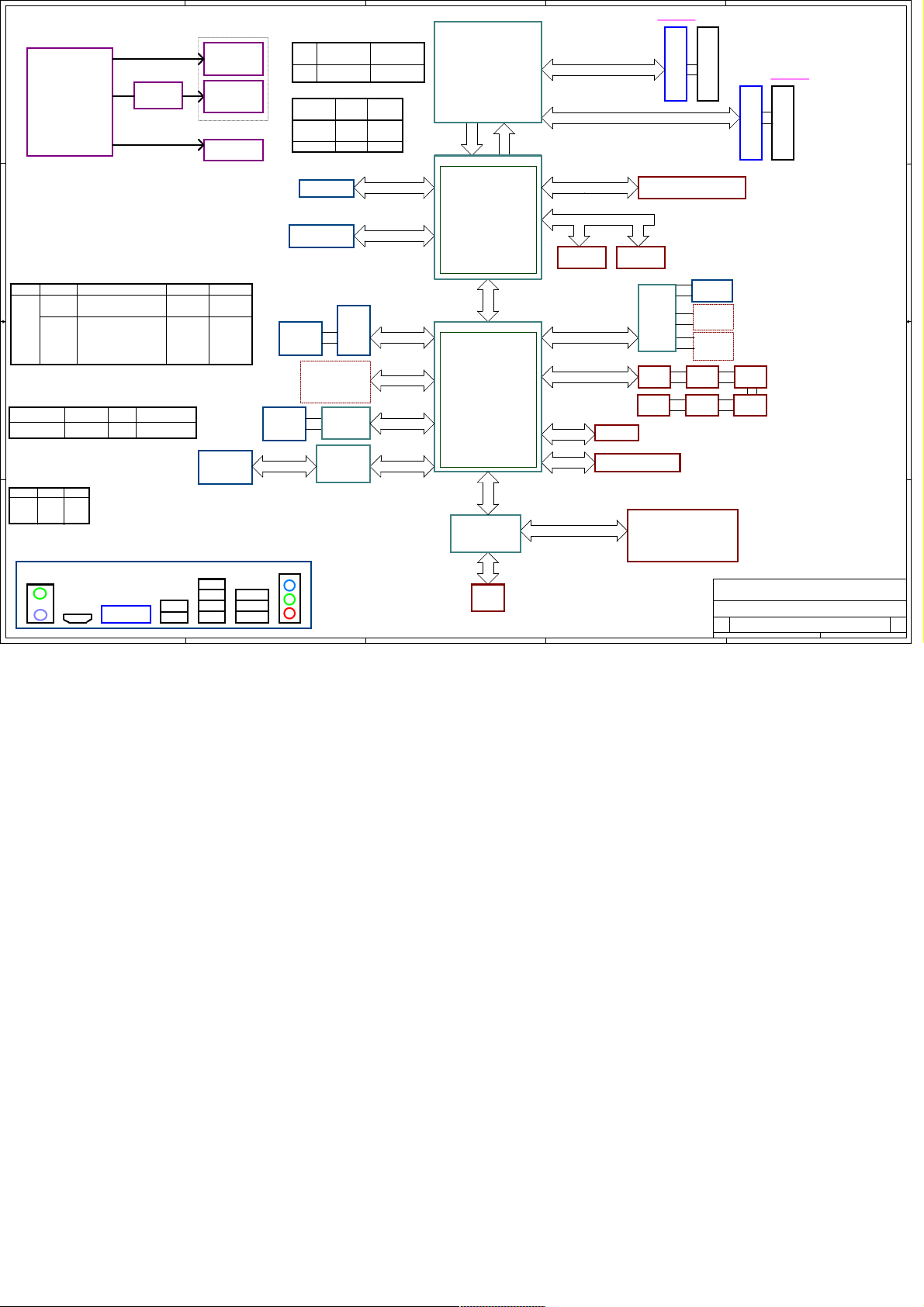

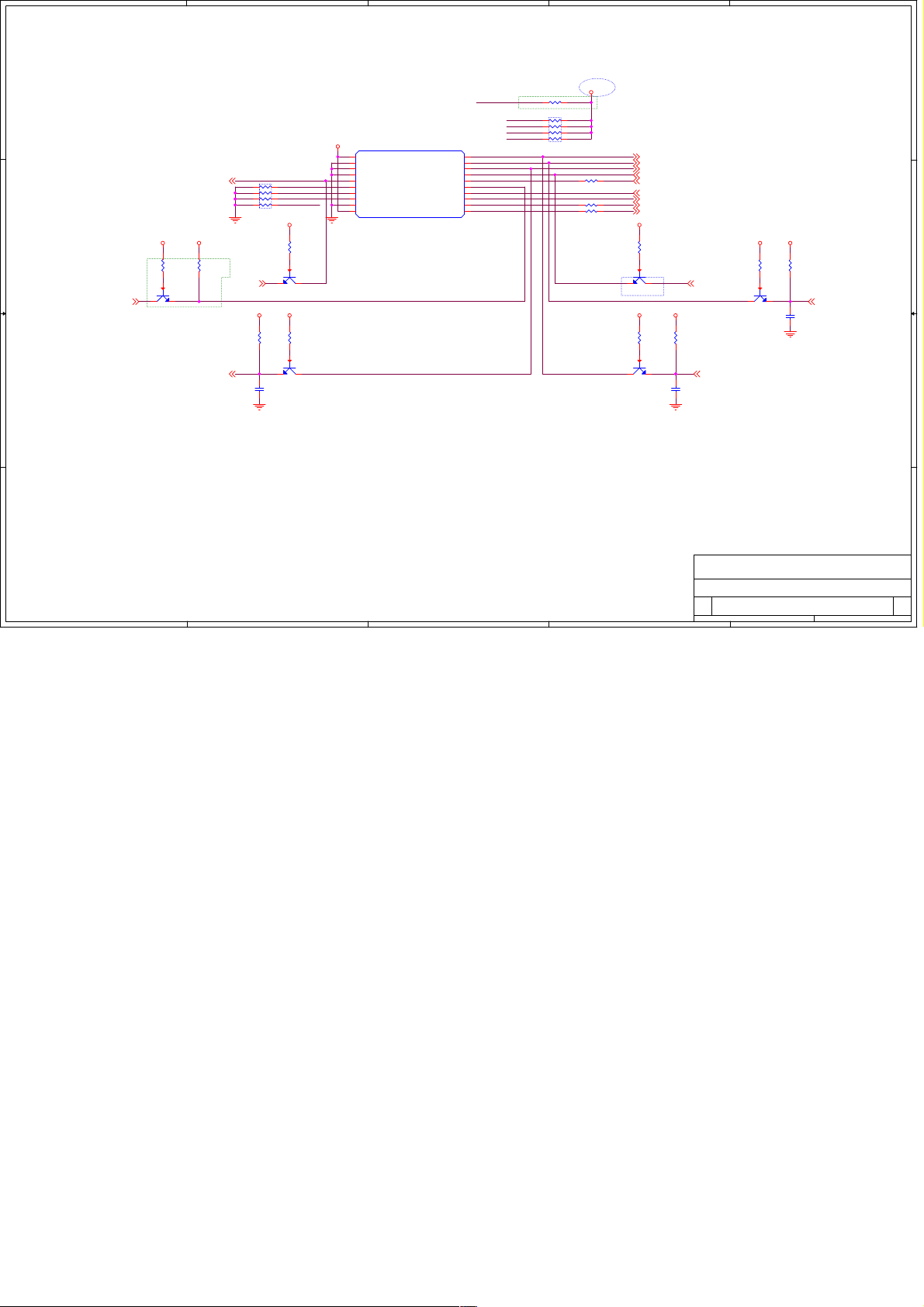

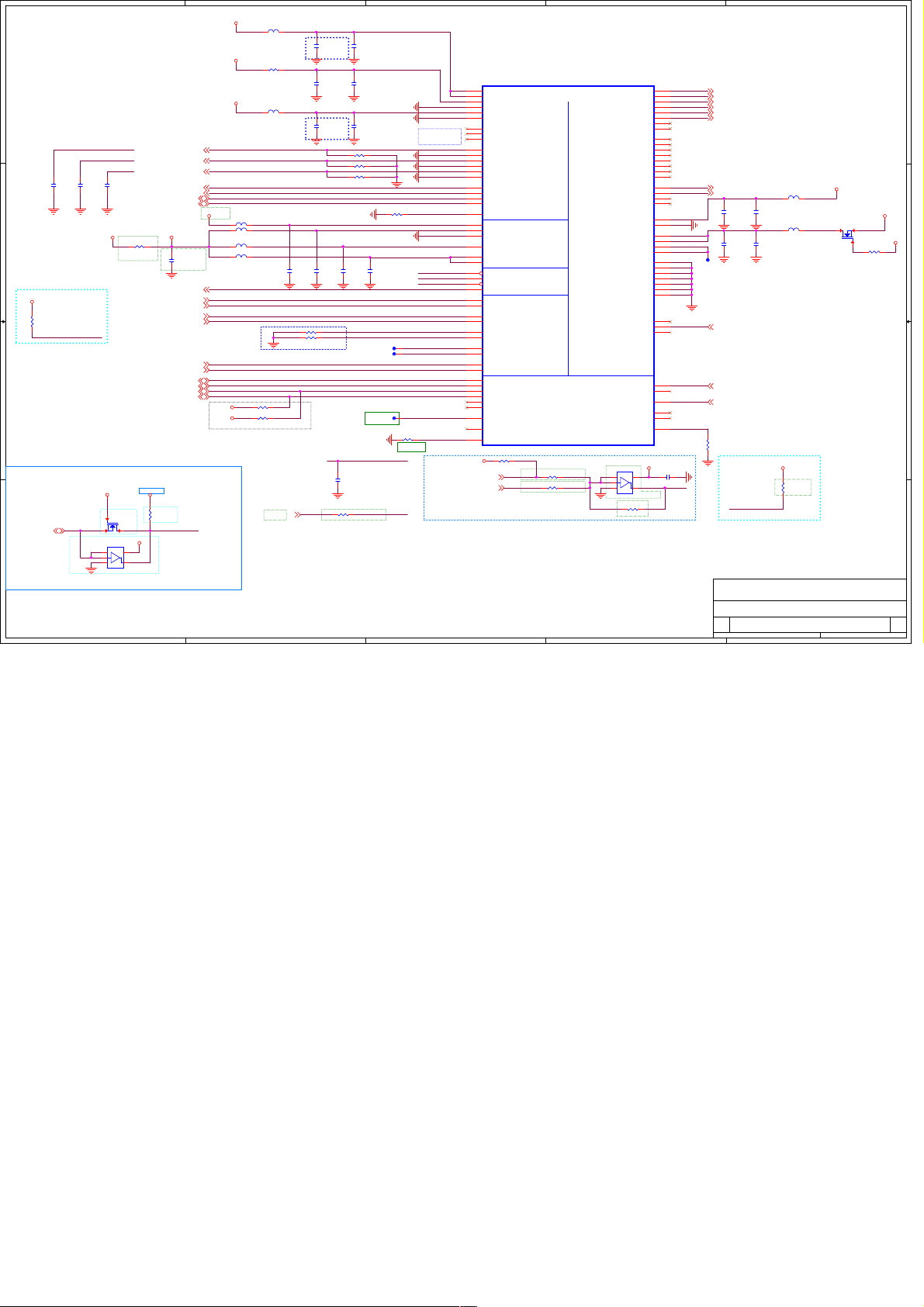

Page 2

5

CPU Vcore 4-phase

(only power pack)

29

Int driver*2

(WOL:Disable,

S0=Blink, S1=OFF)

:ON with A color:

:ON with A color:

WOL

Support

Support

Ext driver*2

Gate Driver

Intersil

(SOP-8)

6612ACBZS*2

Int driver*1

Amber1000

Commercial

Project

"After G3" required

Rear IO

CPU PWM

D D

Intersil 6328CRZ

(QFN-48)

MP:Apr '11

(reserve 125W)

TDP:95W

(1-1)AM3+/enable loadline, AM3/disable loadline

(1-2)Dual OCP(TDC/Spike)

(2)PSI_L

(3)APD(Automatic Phase Dropping)

(4)APA(Adaptive Phase Alignment)

(5)DCR current sensing

C C

SVC/D:Serial VID Clock/Data

WOL:Enable

LAN

Active-LED

(Single Color)

Rear Side

Speed-LED

(Dual Color)

B B

ErP lot 6.0

(2010, SYS<1W)

Disable

Enable(X)

PS:2013(SYS<0.5W) is better.

USB

VCC5 VCC5

S1S0VCC5

S3

5VSB

S4/S5

0V

A A

LAN LED(Rear Side)

LED S0/S1

Access:Blink

Others:OFF

Disconnected:OFF

100 Green

10 :OFF

Sleep State

S1/S3/S4/S5

S1/S3/S4

PS/2

VCC5

5VSB

0V

PS/2

HDMI

VGA

5

S3 S4/S5

Access:Blink

Others:OFF

OFF OFF

USB3.0

i) H-side 2MOS

ii) L-side 2MOS

(with heat sink

position for H-side)

i) H-side 2MOS

ii) L-side 2MOS

(with heat sink

position for H-side)

820uF*8

VDDNB 1-phase

(only power pack)

i) H-side 1MOS

ii) L-side 2MOS

820uF*3

Access:Blink

Others:OFF

Rear IO

USB3.0 CON.

(2 ports)

USB2.0

29

29

29

For card reader.

S4/S4 wo 5V_Dual

LAN+USB2.0

4

CPU

Socket

Power Pack

H-Side

L-Side 212

CPU-FAN 3-pin 4-pin

(1)Hybrid Crossfire : support

(onboard + PCIEx16)

(2)Surround view : support

Rear IO

(w/LAN)

USB 0

USB 1

USB 6/7

USB 8/9

USB 10/11

USB 12/13

Rear IO

LAN CON.

25

USB 2.0(480Mb/s)

USB 3.0(5Gb/s)

AUDIO

4

AM3(938,45nm)

Rear IO

HDMI CON.

Rear IO

VGA CON.

21

Header

USB3.0 Host

Etron

(TQFP100)

AM3(941)

*

95W 125W

3-Phase 4-Phase

19

19

Rear IO

USB 5

USB 4

USB 3

USB 2

(Black)

(H5x2,Yellow)

(Black)

(reserve)

Giga LAN

RTL8111E-VL

(QFN48)

EJ168

AM3(938,45nm)

AM3+(940,32nm)

AM3b(942)

BlackIvory

2

TMDS

VGA

21

S4/S4 wo 5V_Dual

21

S4/S4 wo 5V_Dual

PCIE X1 GEN2 I/F

SB_GPP_0

25

PCIE X1 GEN2 I/F

SB_GPP_1

2828

USB 2.0

USB 2.0

3

Consumer

Zambezi AM3+

(尚比西河)

Family 15h, 32nm

AMD AM3+ package &

AM3b Socket(black,942)

SVI only

Side Band Temp. Sensor I/F only

MT C1E/PSI_L

VDD(Vcore) loadline

Up to 8 cores SCM

TDP:95W/(125W reserve)

Ini. Production:Aug '11

ncHT3.0 5.2GT/s

Link

OUT

RS880P(AMD 880G)

HT LINK0 CPU I/F

DX10.1 IGP

TMDS/HDMI

Display Port X2

Side Port Memory

2 X8 PCIE I/F

1 X4 PCIE I/F WITH SB

6 X1 PCIE I/F

TDP:18W

Production: Feb '11

SB950

4 X 1 PCIE GEN2 I/F

USB2.0 (14)+ 1.1(2)

SATA3.0 (6 PORTS)

INT CLK GEN

GBMAC

AZALIA HD AUDIO

LPC I/F(S5)

SPI I/F

ACPI 1.1

HW Monitor

PCI/PCI BDGE

INT RTC

EC

Production: Feb '11

Super IO

Fintek F71869A

EuP,G3 to S5(RI1#,VBAT)

(LQFP128)

3

3,4,5,6

16x16

IN

(FCBGA,528)

PtoP RS780

9,,10,11,12,13

A-Link GEN 2(4X PCIE)

Not PtoP SB700

TDP:6W

(FCBGA,605)

14,15,16,17,18

LPC I/F

23

PS/2

KB&MS

24

Follow acer

EE V5.21 D.G.

Channel A

128bit

Channel B

5.0GT/s

GEN2 I/F

PCIE X1(2) GEN2 I/F

NB_GPP_0

20 20

1600, 1866

PCIE X 1 Slot 2

DDR3 1066, 1333,

DDR3 1066, 1333,1600, 1866

PCIE X16

PCIE X 1 Slot 1

HD AUDIO I/F

SATA3.0 (6Gb/s) I/F

RAID 0,1,5,10

eSATA*6 port

SPI ROM

SPI I/F

(32Mb)

PCI

PCI Slot 1

(White)

HW Monitor I/F

2

DIMM4(A0)

DIMM1(A0)

DIMM2(A1)

Blue

Black

Unbuffered

DDR3 DIMM1

Unbuffered

Layer-4 Layer-4

PCIE X 16 SLOT

(Black)

NB_GPP_1

(White)(White)

Rear IO

HD AUDIO

ALC662-VC

(LQFP48)

SATA#1

(All black)

SATA#6

(reserve)

HD AUDIO

Header

(H5x2,Purple)

HD AUDIO

Header

(H1x4,black)

26

SPDIFO

(reserve)

SATA#2

16

16

16

SATA#5

16

22

HW Monitor

(1)Internal: 3.3V/5VSB/VBAT

(2)External:CPU core/1.1V/5V/12V

(3)CPU/SYS/Vcore MOS

temperature detect.

(4)CPU(AM3/AM3+) Temperature

detect SB-TSI

2

1

DIMM1(B1)

DIMM3(B0)

DDR3 DIMM2

DIMM4(B1)

Black

Blue

Unbuffered

DDR3 DIMM3

Layer-1 Layer-1

Unbuffered

DDR3 DIMM4

20

27

27

Near PCIEX16

27

SATA#3

16

SATA#4

PS:SATA2.0 and SATA3.0

1616

has different footprint.

23

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

RS880PM-AM

RS880PM-AM

RS880PM-AM

1

2

2

2

of

37Thursday, May 26, 2011

of

37Thursday, May 26, 2011

of

37Thursday, May 26, 2011

1.0.

1.0.

1.0.

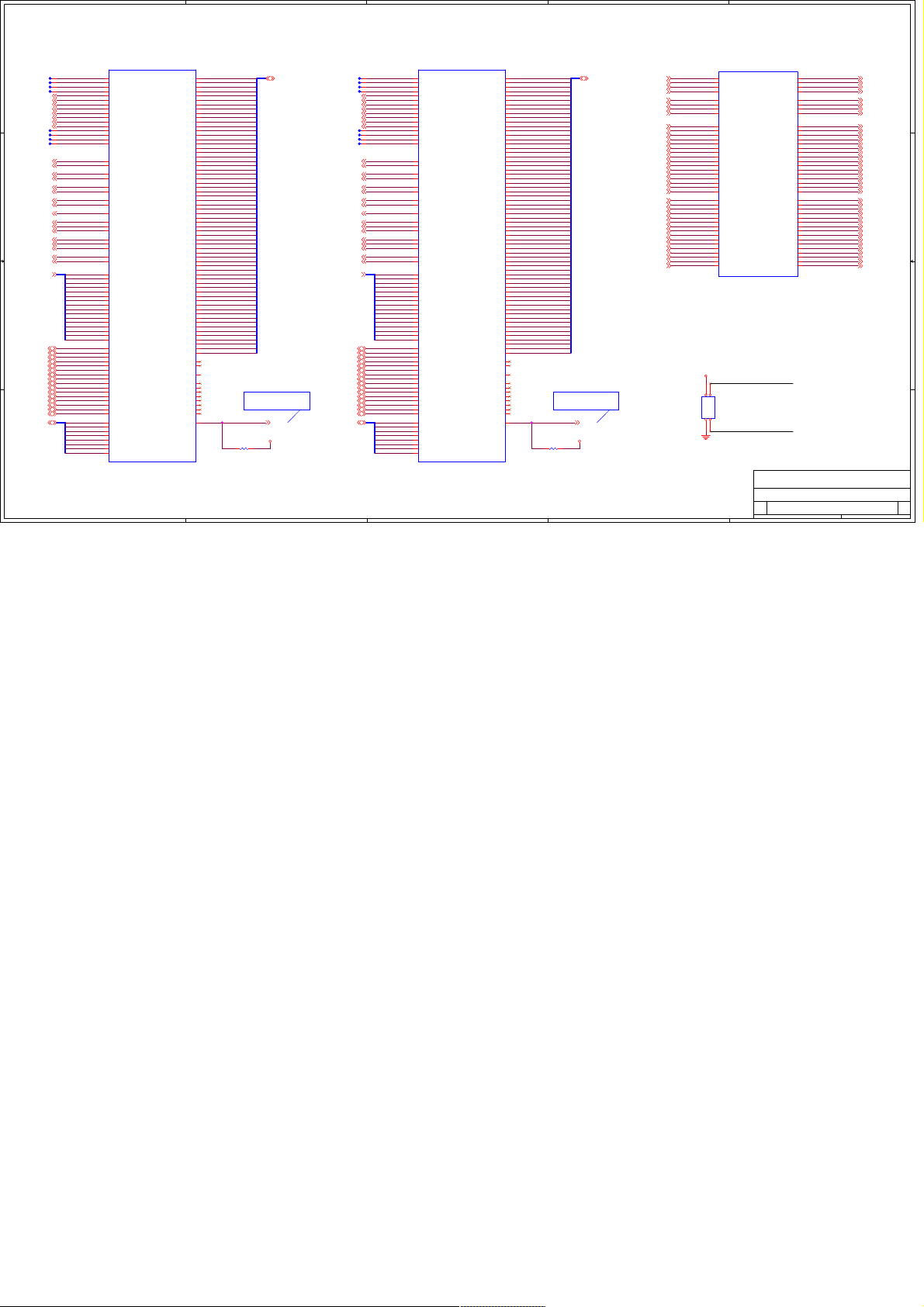

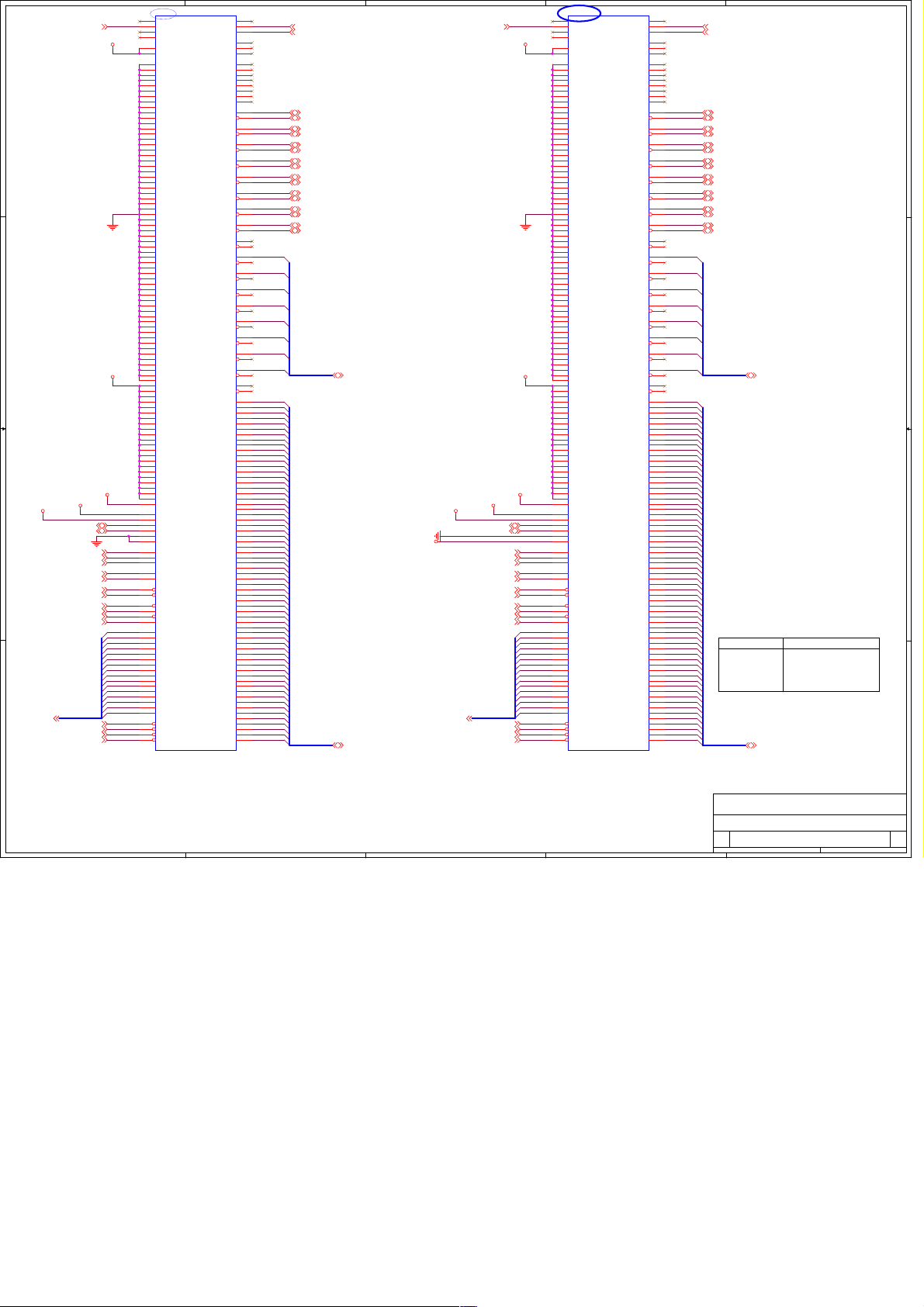

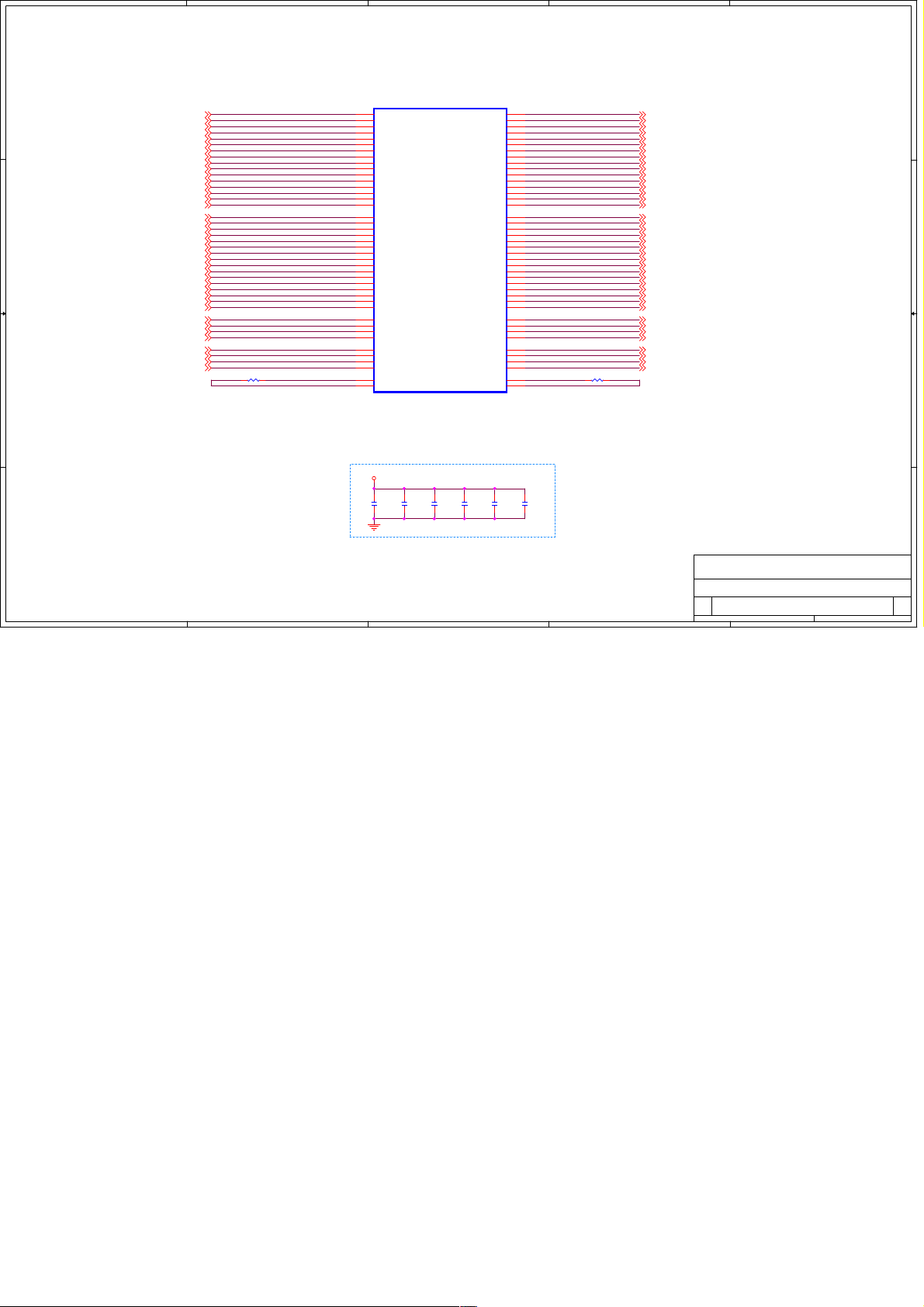

Page 3

5

4

3

2

1

CPU Memory

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

CPU1A

AG21

RSVD1

AG20

RSVD2

AE20

RSVD3

AE19

RSVD4

U27

MA_CLK_H5

U26

MA_CLK_L5

V27

MA_CLK_H4

W27

MA_CLK_L4

W26

MA_CLK_H3

W25

MA_CLK_L3

U24

MA_CLK_H2

V24

MA_CLK_L2

G19

RSVD5

H19

RSVD6

G20

RSVD7

G21

RSVD8

AC25

MA0_CS_L1

AA24

MA0_CS_L0

AE28

MA0_ODT1

AC28

MA0_ODT0

AD27

MA1_CS_L1

AA25

MA1_CS_L0

AE27

MA1_ODT1

AC27

MA1_ODT0

E20

MA_RESET_L

AB25

MA_CAS_L

AB27

MA_WE_L

AA26

MA_RAS_L

N25

MA_BANK2

Y27

MA_BANK1

AA27

MA_BANK0

L27

MA_CKE1

M25

MA_CKE0

M27

MA_ADD15

N24

MA_ADD14

AC26

MA_ADD13

N26

MA_ADD12

P25

MA_ADD11

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

F19

F15

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

5

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

ZIF-942P-S

MEM CHA

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

W30

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

R345 1K-04

MA_DATA[63..0] 7,8

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

MA_EVENT_L 7,8

+VDIMM +VDIMM

1 2

4

TP5

TP9

TP7

TP3

MB1_CLK_P18

MB1_CLK_N18

MB0_CLK_P07

MB0_CLK_N07

MB1_CLK_P08

MB1_CLK_N08

MB0_CLK_P17

MB0_CLK_N17

TP2

TP4

TP6

TP8

MB0_CS_L17

MB0_CS_L07

MB0_ODT17

MB0_ODT07

MB1_CS_L18

MB1_CS_L08

MB1_ODT18

MB1_ODT08

MB_RESET_L7,8

MB_CAS_L7,8

MB_WE_L7,8

MB_RAS_L7,8

MB_BANK27,8

MB_BANK17,8

MB_BANK07,8

MB_CKE17,8

MB_CKE07,8

MB_ADD[15..0]7,8

MB_DQS_P77,8

MB_DQS_N77,8

MB_DQS_P67,8

MB_DQS_N67,8

MB_DQS_P57,8

MB_DQS_N57,8

MB_DQS_P47,8

MB_DQS_N47,8

MB_DQS_P37,8

MB_DQS_N37,8

MB_DQS_P27,8

MB_DQS_N27,8

MB_DQS_P17,8

MB_DQS_N17,8

MB_DQS_P07,8

MB_DQS_N07,8

MB_DM[7..0]7,8

D D

C C

B B

A A

STP32

STP47

STP33

STP46

STP29

STP45

STP25

STP44

MA1_CLK_P18

MA1_CLK_N18

MA0_CLK_P07

MA0_CLK_N07

MA1_CLK_P08

MA1_CLK_N08

MA0_CLK_P17

MA0_CLK_N17

STP26

STP42

STP27

STP41

STP31

STP43

STP30

STP48

MA0_CS_L17

MA0_CS_L07

MA0_ODT17

MA0_ODT07

MA1_CS_L18

MA1_CS_L08

MA1_ODT18

MA1_ODT08

MA_RESET_L7,8

MA_CAS_L7,8

MA_WE_L7,8

MA_RAS_L7,8

MA_BANK27,8

MA_BANK17,8

MA_BANK07,8

MA_CKE17,8

MA_CKE07,8

MA_ADD[15..0]7,8

MA_DQS_P77,8

MA_DQS_N77,8

MA_DQS_P67,8

MA_DQS_N67,8

MA_DQS_P57,8

MA_DQS_N57,8

MA_DQS_P47,8

MA_DQS_N47,8

MA_DQS_P37,8

MA_DQS_N37,8

MA_DQS_P27,8

MA_DQS_N27,8

MA_DQS_P17,8

MA_DQS_N17,8

MA_DQS_P07,8

MA_DQS_N07,8

MA_DM[7..0]7,8

DDR3 Memory Interface BDDR3 Memory Interface A

CPU1B

AJ19

TP33

TP35

TP34

TP31

TP27

TP29

TP30

TP32

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

AK19

AL19

AL18

AE30

AC31

AF31

AD29

AE29

AB31

AG31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

U31

U30

W29

W28

Y31

Y30

V31

W31

A18

A19

C19

D19

B19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

RSVD9

RSVD10

RSVD11

RSVD12

MB_CLK_H5

MB_CLK_L5

MB_CLK_H4

MB_CLK_L4

MB_CLK_H3

MB_CLK_L3

MB_CLK_H2

MB_CLK_L2

RSVD13

RSVD14

RSVD15

RSVD16

MB0_CS_L1

MB0_CS_L0

MB0_ODT1

MB0_ODT0

MB1_CS_L1

MB1_CS_L0

MB1_ODT1

MB1_ODT0

MB_RESET_L

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

ZIF-942P-S

3

MEM CHB

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

V29

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

MB_EVENT_LMA_EVENT_L

1 2

R355 1K-04

MB_DATA[63..0] 7,8

MB_EVENT_L 7,8

H_CLKIN_P1

H_CLKIN_P19

H_CLKIN_N1

H_CLKIN_N19

H_CLKIN_P0

H_CLKIN_P09

H_CLKIN_N0

H_CLKIN_N09 H_CLKOUT_N0 9

H_CTLIN_P1

H_CTLIN_P19

H_CTLIN_N1

H_CTLIN_N19

H_CTLIN_P0

H_CTLIN_P09

H_CTLIN_N0

H_CTLIN_N09

H_CADIN_P15

H_CADIN_P159

H_CADIN_N15

H_CADIN_N159

H_CADIN_P14

H_CADIN_P149

H_CADIN_N14

H_CADIN_N149

H_CADIN_P13

H_CADIN_P139

H_CADIN_N13

H_CADIN_N139

H_CADIN_P12

H_CADIN_P129

H_CADIN_N12

H_CADIN_N129

H_CADIN_P11

H_CADIN_P119

H_CADIN_N11

H_CADIN_N119

H_CADIN_P10

H_CADIN_P109

H_CADIN_N10

H_CADIN_N109

H_CADIN_P9

H_CADIN_P99

H_CADIN_N9

H_CADIN_N99

H_CADIN_P8

H_CADIN_P89

H_CADIN_N8

H_CADIN_N89

H_CADIN_P7

H_CADIN_P79

H_CADIN_N7

H_CADIN_N79

H_CADIN_P6

H_CADIN_P69

H_CADIN_N6

H_CADIN_N69

H_CADIN_P5

H_CADIN_P59

H_CADIN_N5

H_CADIN_N59

H_CADIN_P4

H_CADIN_P49

H_CADIN_N4

H_CADIN_N49

H_CADIN_P3

H_CADIN_P39

H_CADIN_N3

H_CADIN_N39

H_CADIN_P2

H_CADIN_P29

H_CADIN_N2

H_CADIN_N29

H_CADIN_P1

H_CADIN_P19

H_CADIN_N1

H_CADIN_N19

H_CADIN_P0 H_CADOUT_P0

H_CADIN_P09

H_CADIN_N0

H_CADIN_N09

NOTE:

We can repair two 1X2 headers for layout design more convenience!!

2

+VCC

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

12

34

HT LINK

CPU1H

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

ZIF-942P-S

11-106-942120

(替)11-106-942020

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

HT LINK

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

Layer 1

IP1

HEADER 2X2-O

Layer 4

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Custom

Custom

Custom

HT,CPU MEMORY

HT,CPU MEMORY

HT,CPU MEMORY

RS880PM-AM

RS880PM-AM

RS880PM-AM

H_CLKOUT_P1

H_CLKOUT_N1

H_CLKOUT_P0

H_CLKOUT_N0

H_CTLOUT_P1

H_CTLOUT_N1

H_CTLOUT_P0

H_CTLOUT_N0

H_CADOUT_P15

H_CADOUT_N15

H_CADOUT_P14

H_CADOUT_N14

H_CADOUT_P13

H_CADOUT_N13

H_CADOUT_P12

H_CADOUT_N12

H_CADOUT_P11

H_CADOUT_N11

H_CADOUT_P10

H_CADOUT_N10

H_CADOUT_P9

H_CADOUT_N9

H_CADOUT_P8

H_CADOUT_N8

H_CADOUT_P7

H_CADOUT_N7

H_CADOUT_P6

H_CADOUT_N6

H_CADOUT_P5

H_CADOUT_N5

H_CADOUT_P4

H_CADOUT_N4

H_CADOUT_P3

H_CADOUT_N3

H_CADOUT_P2

H_CADOUT_N2

H_CADOUT_P1

H_CADOUT_N1

H_CADOUT_N0

1

H_CLKOUT_P1 9

H_CLKOUT_N1 9

H_CLKOUT_P0 9

H_CTLOUT_P1 9

H_CTLOUT_N1 9

H_CTLOUT_P0 9

H_CTLOUT_N0 9

H_CADOUT_P15 9

H_CADOUT_N15 9

H_CADOUT_P14 9

H_CADOUT_N14 9

H_CADOUT_P13 9

H_CADOUT_N13 9

H_CADOUT_P12 9

H_CADOUT_N12 9

H_CADOUT_P11 9

H_CADOUT_N11 9

H_CADOUT_P10 9

H_CADOUT_N10 9

H_CADOUT_P9 9

H_CADOUT_N9 9

H_CADOUT_P8 9

H_CADOUT_N8 9

H_CADOUT_P7 9

H_CADOUT_N7 9

H_CADOUT_P6 9

H_CADOUT_N6 9

H_CADOUT_P5 9

H_CADOUT_N5 9

H_CADOUT_P4 9

H_CADOUT_N4 9

H_CADOUT_P3 9

H_CADOUT_N3 9

H_CADOUT_P2 9

H_CADOUT_N2 9

H_CADOUT_P1 9

H_CADOUT_N1 9

H_CADOUT_P0 9

H_CADOUT_N0 9

3

3

3

of

of

of

1.0.

1.0.

1.0.

37Thursday, May 26, 2011

37Thursday, May 26, 2011

37Thursday, May 26, 2011

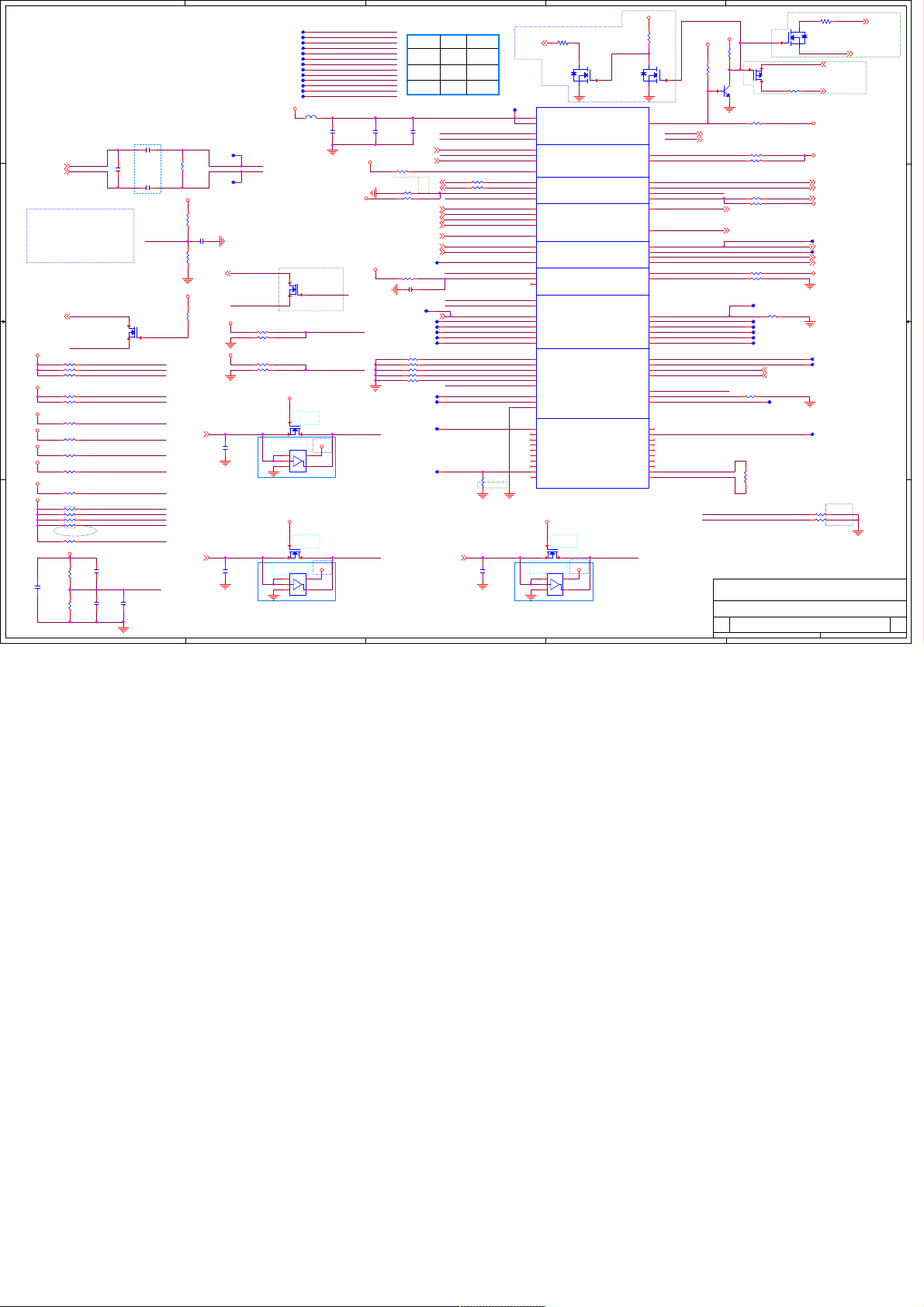

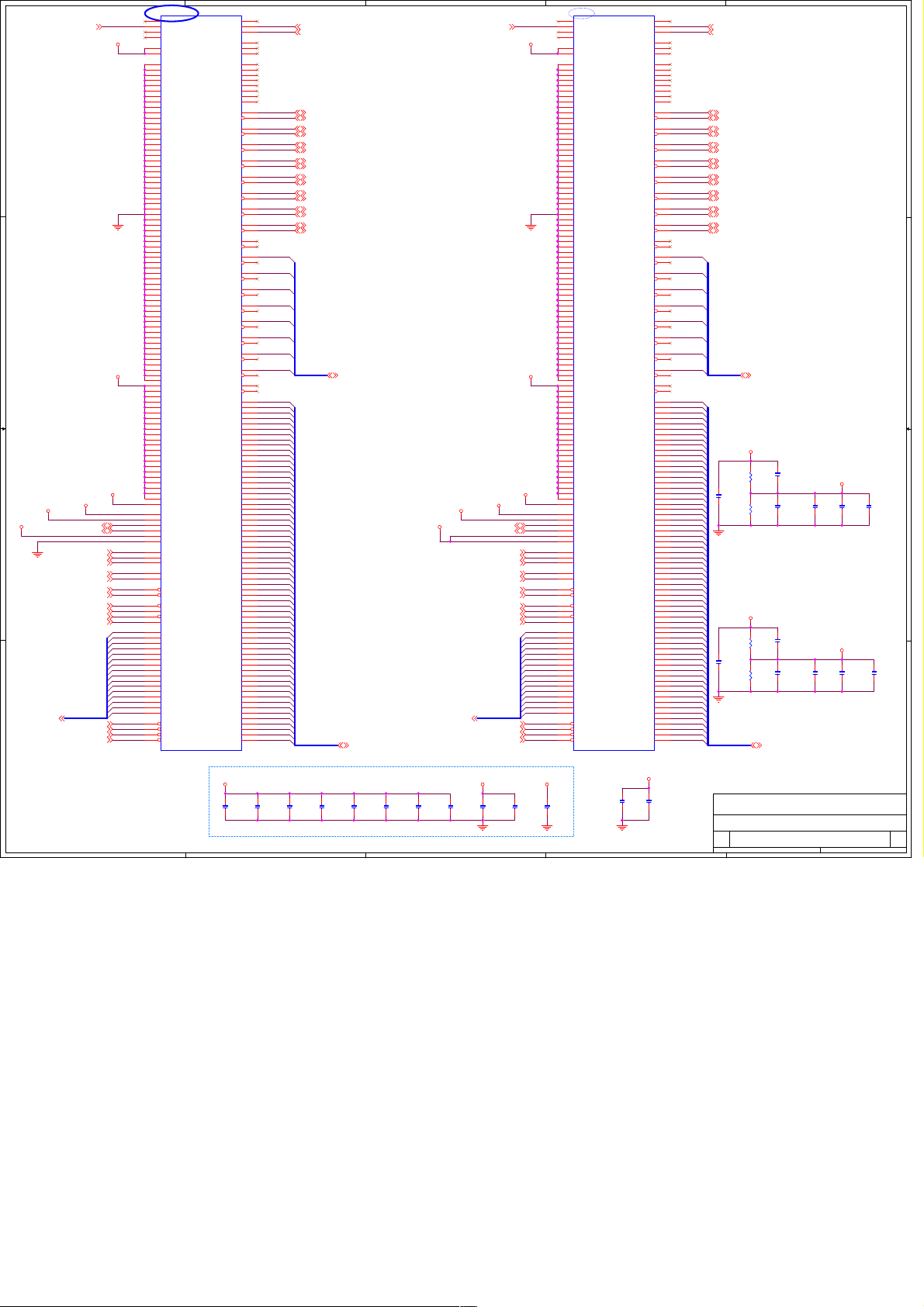

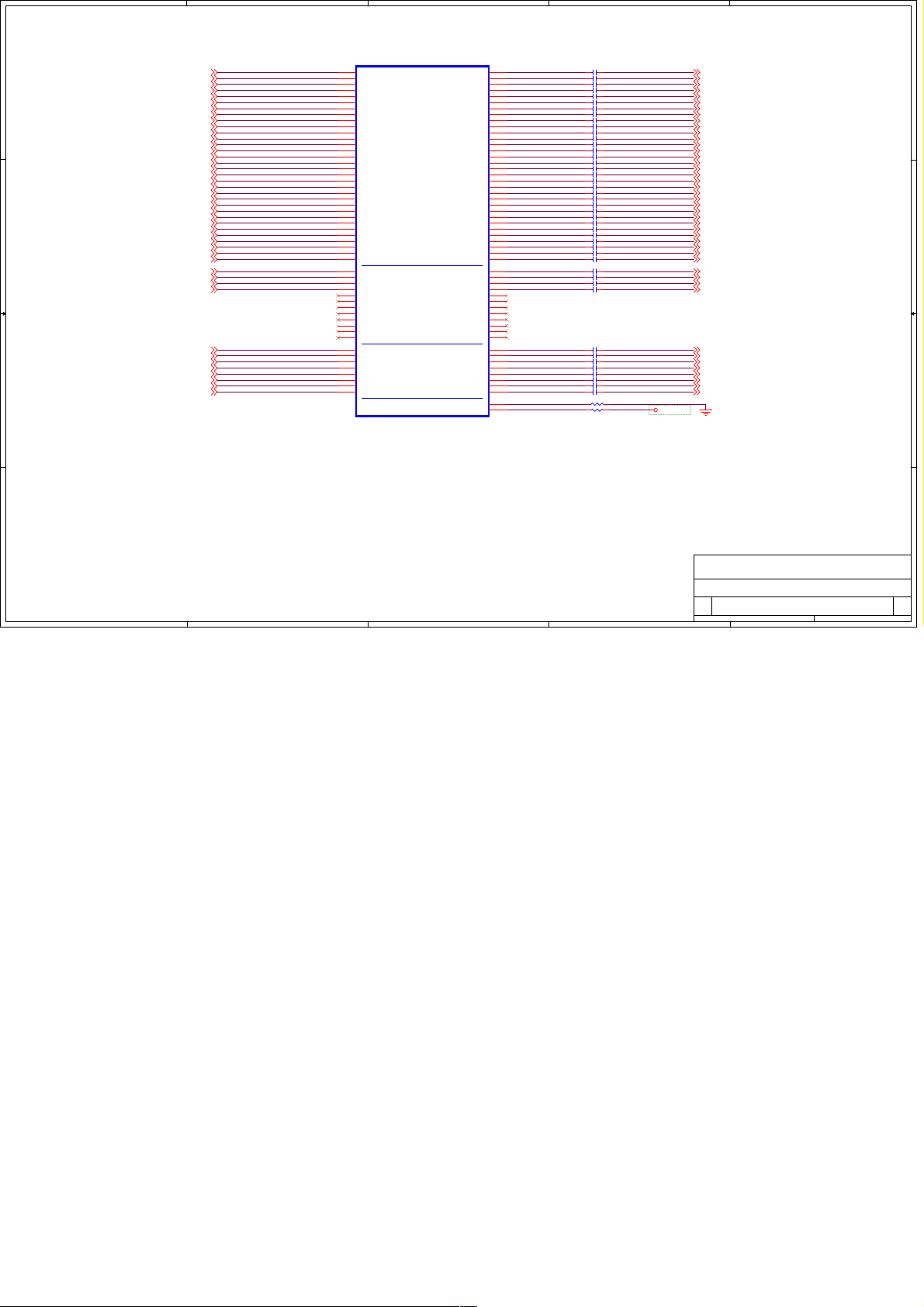

Page 4

5

D D

Note: Update with new

clock termination

scheme, if necessary.

H_CLK200_P14

H_CLK200_N14

C C

H_THERMTRIP_L15

+VDIMM

+VDIMM

B B

+VDIMM

+VDIMM

+VDIMM

+VDIMM

+VDIMM

+VDIMM

A A

H_CLK200_P

H_CLK200_N

H_THERMTRIP_L

H_THERMTRIP_L_1.5

1 2

R241 1K-04

1 2

R222 1K-04

1 2

R210 1K-04

1 2

R249 1K-04

1 2

R209 1K-04

1 2

R207 1K-04

1 2

R213 1K-04

1 2

R198 1K-04

1 2

R204 1K-04

1 2

R181 1K-04

RN11

1 2

3 4

5 6

7 8

1K-8P4R

1 2

R177 1K-04

+VDIMM

12

ER69

15-1

C329

4.7U-08

12

ER58

15-1

2 1

2 1

5

0112

C341

.1U-04-O

C325

.1U-04

21

C308 3900P-04

Cs

C305

10P-04-O

2 1

Cs

21

C303 3900P-04

H_FETGATE1

0125

FDV301N-S

03-050-530106

MN5

DS

BSS138-7-01-F-S

G

H_FETGATE

Vgs(th)=1.2v

H_PWROK

CPU_STOP_L

H_RST_L

H_TEST27_SINGLECHAIN

H_TEST26_BURNIN_L

H_THERMTRIP_L_1.5

H_SIC

H_SID

H_ALERT_L

CPU_IDLEEXIT_L

H_TEST11_BP4

H_TEST17_BP3

H_TEST16_BP2

H_TEST15_BP1

H_TEST14_BP0

Place witin 500 mils

of the CPU socket.

H_M_VREF

C337

1000P-04

2 1

STP24

12

H_CLKIN_P

ER39

Rs

H_CLKIN_N

169-1-04

STP21

+VCC3

12

R231

10K-04

C304

21

.1U-04-O

12

R215

20K-04-O

TALERT16

+VDIMM

12

R214

4.7K-04

+VDIMM

+VDIMM

LDT_PWROK14

2 1

LDT_RST_L14

2 1

4

CPU Control and Miscellaneous

+VDDA_2P5V

SIC:Sideband Temperature

Sensor I/F Clock

2011-01-24

AMD review recommend

TALERT

H_ALERT_L

1 2

ER43 510-1-04-O

1 2

ER42 510-1-04

1 2

ER49 510-1-04

1 2

ER48 510-1-04-O

03-050-530106

C360

74AUP1G07GW

180P-04-O

STP33

STP30

STP32

STP10

STP11

STP8

STP9

STP68

STP63

STP29

STP26

STP31

STP34

FB14

1 2

FB-600-08P

FDV301N-S

03-050-530106

MN7

DS

FDV301N-S-O

G

H_TEST25_BYPASSCLK

H_TEST25_BYPASSCLK_LH_TEST25_BYPASSCLK_L

+1.8V

MN9

G

BSH111-O

DS

U30

1

5

2

3 4

H_TEST24_SCANCLK1

H_TEST20_SCANCLK2

H_TEST12_SCANSHIFTENB

H_VCORE_FB

H_VCORE_FB_L

NB_VCORE_FB

NB_VCORE_FB_L

H_THERMDC

H_THERMDA

H_TEST23_TSTUPD

H_TEST25_BYPASSCLK

H_TEST25_BYPASSCLK_L

H_TEST27_SINGLECHAIN

2A

C365

4.7U-X5-08

2 1

+VDIMM

2011-03-08 VA to VB

Net rename.

+VDIMM

H_FETGATE1

2011-04-19 VB to V1.0

Del MN9

Add U30 for H_PWROK rising time.

H_PWROK

+3VSB

2011-04-27 V1.0 to V1.0(.)

+1.8V change to +3VSB for S3.

U30 change to 74AUP1G07GW

C344

.22U-16V-04

2 1

H_PWROK6

H_RST_L6

1 2

R200 1K-04

1 2

R203 1K-04

1 2

R199 1K-04-O

H_VCORE_FB29

H_VCORE_FB_L29

+VDIMM

1 2

ER62 39.2-1-04

2 1

C348 2.2U-6V3X-X-O

CPU_IDLEEXIT_L15

1 2

R235 1K-04

1 2

R232 1K-04

1 2

R238 1K-04

1 2

R239 1K-04

1 2

R225 1K-04

STP13

OD-BUFFER(NEED PULL HIGH)74AUP1G07GW (02-197-007131)

+1.8V

2011-04-19 VB to V1.0

Del MN6

MN6

G

Add U26 for H_RST_L rising time.

BSH111-O

U26

74AUP1G07GW

1

2

3 4

DS

+3VSB

5

H_RST_L

2011-04-27 V1.0 to V1.0.

+1.8V change to +3VSB for S3.

U26 change to 74AUP1G07GW

C319

180P-04-O

03-050-530106

3

CPU AM3 AM3+

Core_Type

GND

(G5-pin)

Droop

Disable

Control

(100K)

Offset

Disable

Control

H_VDDA

H_CLKIN_P

C347

H_CLKIN_N

3300P-04

2 1

H_PWROK

CPU_STOP_L

H_RST_L

H_PRESENT_L_1.5

2011-03-08 VA to VB

R202, R208 change to Short Pad

R208

SIC23

R202

SID23

H_SA0

H_ALERT_L

H_TDI

H_TDI6

H_TRST_L

H_TRST_L6

H_TCK

H_TCK6

H_TMS

H_TMS6

H_DBREQ_L

H_DBREQ_L6

H_VCORE_FB

H_VCORE_FB_L

H_VTT_SENSE

STP40

H_M_VREF

H_M_ZN

H_TEST25_BYPASSCLK

H_TEST25_BYPASSCLK_L

CPU_IDLEEXIT_L

CPU_IDLEEXIT_L

H_TEST11_BP4

STP14

H_TEST17_BP3

STP18

H_TEST16_BP2

STP12

H_TEST15_BP1

STP15

H_TEST14_BP0

STP19

H_TEST24_SCANCLK1

H_TEST20_SCANCLK2

H_TEST21_SCANEN

H_TEST22_SCANSHIFTEN

H_TEST12_SCANSHIFTENB

H_TEST27_SINGLECHAIN

H_TEST2_DRAIN0

STP28

H_TEST3_GATE0

STP23

H_TEST7_ANALOG_T

STP25

H_VID1_PVEN

STP16

2011-03-08 VA to VB

48121_1_02 AM3r2

Processor Motherboard

Schematic Checklist (NDA)_

2011-02-07.xlsx update for AM3

compatible.

H_STOP_L11,14

floating

Enable

(0 ohm)

Enable

(35 mV)

1 2

1 2

SHORT PAD-04

SHORT PAD-04

R186

300-04

C318

180P-04-O

2 1

STP37

H_SIC

H_SID

AL10

AJ10

AH10

AH11

AJ11

03-050-530106

OD-BUFFER(NEED PULL HIGH)74AUP1G07GW (02-197-007131)

4

3

OFS29

CPU1C

C10

VDDA_1

D10

VDDA_2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

AL3

CPU_PRESENT_L

AL6

SIC

AK6

SID

AK4

SA0

AL4

ALERT_L

TDI

TRST_L

TCK

AL9

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

E12

VDDR_SENSE

F12

M_VREF

M_ZVDDIO

TEST31

A10

TEST25_H

B10

TEST25_L

F3

IDLEEXIT_L/TEST36

F2

TEST11

D6

TEST17

E7

TEST16

F8

TEST15

C5

TEST14

AK8

TEST24

AJ8

TEST20

AL8

TEST21

AJ9

TEST22

AH9

TEST12

AK9

TEST27

AJ6

TEST2

AH7

TEST3

AJ7

TEST13

E5

RSVD17

C18

RSVD18

C20

RSVD19

G24

RSVD20

G25

RSVD21

H25

RSVD22

D2

RSVD23

D1

RSVD24

E2

RSVD25

E1

RSVD26

ZIF-942P-S

+1.8V

U27

74AUP1G07GW

1

2

3 4

2011-05-10 V1.0 to V1.0(.)

Offset control circuit.

ER102

13K-1-04

MN22

2N7002K-S

500mA

INT. MISC.

MN8

G

BSH111-O

DS

5

OD-BUFFER(NEED PULL HIGH)74AUP1G07GW (02-197-007131)

Offset control

D

G

2N7002K-S

S

CORE_TYPE

MISC.

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

2011-04-18 VB to V1.0

Del MN8

Add U27 for LDT_STOP# skew

CPU_STOP_L

+3VSB

2011-04-27 V1.0 to V1.0.

+1.8V change to +3VSB for S3.

U27 change to 74AUP1G07GW

R462

4.7K-04

MN21

THERMDC

THERMDA

DBRDY

HTREF1

HTREF0

TEST9

TEST10

TEST32_H

TEST32_L

TEST30_H

TEST30_L

TEST28_H

TEST28_L

TEST18

TEST19

TEST26

TEST23

TEST6

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

2

SVC

SVD

TDO

2

+VCC

12

D

S

G5

C1

E3

AG9

AG8

AK7

AL7

AK10

B6

AK11

AL11

G4

G3

V8

V7

F6

G7

L30

L31

L25

L26

J10

H9

E9

F10

AK5

AH8

AJ5

F1

D4

AD25

AE24

AE25

AJ18

AJ20

AK3

C11

D11

+VCC

+VDIMM

R363

4.7K-04

R192

1K-04

G

1 2

B

H_CORETYPE

H_SVC

H_SVC 29

H_SVD

H_SVD 29

H_SVC

H_SVD

H_THERMDC

H_THERMDA

H_THERMTRIP_L_1.5

H_PROCHOT_L_1.5

H_TDO

H_DBRDY

H_VDIMM_FB

H_VDIMM_FB_L

NB_VCORE_FB

NB_VCORE_FB_L

H_HTREF1

H_HTREF0

H_TEST9

H_TEST10_ANALOGOUT

ANATSTOUT_H

ANATSTOUT_L

ANATSTIN_H

ANATSTIN_L

H_TEST28_PLLCHRZ

H_TEST28_PLLCHRZ_L

H_TEST18_PLLTEST1

H_TEST19_PLLTEST0

H_TEST26_BURNIN_L

H_TEST23_TSTUPD

H_TEST6_DIECRACKMON

H_TEST8_DIG_T

H_TEST29_FBCLKOUT

H_TEST29_FBCLKOUT_L

R224 1K-04

H_TEST18_PLLTEST1

H_TEST19_PLLTEST0

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

G

12

G

QSW4

PA002FMG-S

D S

1 2

R364 0-04

QN19

PMBS3904-S

E C

12

R255 4.7K-04-O

1 2

R187 1K-04

1 2

R176 1K-04

2011-03-08 VA to VB

R212 change to Short Pad

1 2

R212 SHORT PAD-04

1 2

R216 300-04

H_TDO 6

H_DBRDY 6

1 2

ER21 46.4-1-04

1 2

ER20 46.4-1-04

STP17

1 2

R193 0-04-O

STP27

STP52

STP51

STP49

STP50

H_TEST18_PLLTEST1 6

H_TEST19_PLLTEST0 6

1 2

STP22

12

ER47

80.6-1-04-O

R220 1K-04

R219 1K-04

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

CPU CONTROL & MISC

CPU CONTROL & MISC

CPU CONTROL & MISC

RS880PM-AM

RS880PM-AM

RS880PM-AM

1

D

ER70 1.47K-1-04-O

MN11

2N7002K-S-O

S

Droop control

+5VSB

+VDIMM

CPU_THERMDC 23

CPU_THERMDA 23

H_PROCHOT_L 14

+VDIMM

STP39

H_VDIMM_FB 30

STP38

NB_VCORE_FB 29

NB_VCORE_FB_L 29

+HT_1P2V_B

STP36

STP35

STP20

1 2

1 2

1

Load line control

IF MN11 off , load line 1.3m

MN11 ON , load line 0.Xm

FB 29

6323_VCC 29

DRPCTRL 29

0112

4

4

4

of

of

of

VSEN 29

37Thursday, May 26, 2011

37Thursday, May 26, 2011

37Thursday, May 26, 2011

1.0.

1.0.

1.0.

Page 5

CPU1D

110A

5

A3

VSS

A7

VSS

A9

VSS

A11

VSS

B4

VSS

B9

VSS

B11

VSS

B14

VSS

B16

VSS

B18

VSS

B20

VSS

B22

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

C3

VSS

D14

VSS

D16

VSS

D18

VSS

D20

VSS

D22

VSS

D24

VSS

D26

VSS

D28

VSS

D30

VSS

E11

VSS

F4

VSS

F14

VSS

F16

VSS

F18

VSS

F20

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

G9

VSS

G11

VSS

H8

VSS

H10

VSS

H12

VSS

H14

VSS

H16

VSS

POWER/GND1

H18

VSS

H26

VSS

H28

VSS

H30

VSS

J4

VSS

J5

VSS

J7

VSS

J9

VSS

J11

VSS

J13

VSS

J15

VSS

J17

VSS

J19

VSS

J21

VSS

J23

VSS

K2

VSS

K3

VSS

K8

VSS

K10

VSS

K12

VSS

K14

VSS

K16

VSS

K18

VSS

K20

VSS

K22

VSS

K24

VSS

K26

VSS

K28

VSS

K30

VSS

L7

VSS

L9

VSS

L11

VSS

L13

VSS

L15

VSS

L17

VSS

L19

VSS

L21

VSS

L23

VSS

M8

VSS

M10

VSS

Bottom Side Decoupling

SC99

SC98

22U-6V3-08-X

SC79

22U-6V3-08-X

SC69

22U-6V3-08-X

5

SC100

22U-6V3-08-X

22U-6V3-08-X

2011-03-15

for AMD Validation Test

Not co-layout POS CAP

SC85

SC88

22U-6V3-08-X

22U-6V3-08-X

CPU1E

T15

VDD

T17

VDD

T19

VDD

T21

VDD

T23

VDD

U8

VDD

U10

VDD

U12

VDD

U14

VDD

U16

VDD

U18

VDD

U20

VDD

U22

VDD

V9

VDD

V11

VDD

V13

VDD

V15

VDD

V17

VDD

V19

VDD

V21

VDD

V23

VDD

W4

VDD

W5

VDD

W8

VDD

W10

VDD

W12

VDD

W14

VDD

W16

VDD

W18

VDD

W20

VDD

W22

VDD

Y2

VDD

Y3

VDD

Y7

VDD

Y9

VDD

Y11

VDD

Y13

VDD

Y15

VDD

Y17

VDD

Y19

VDD

Y21

VDD

Y23

VDD

AA8

VDD

AA10

VDD

AA12

VDD

AA14

VDD

AA16

VDD

AA18

VDD

AA20

VDD

AA22

VDD

AB7

VDD

AB9

VDD

AB11

VDD

AB13

VDD

AB15

VDD

AB17

VDD

AB19

VDD

AB21

VDD

AB23

VDD

AC4

VDD

AC5

VDD

AC8

VDD

AC10

VDD

AC12

VDD

AC14

VDD

AC16

VDD

AC18

VDD

AC20

VDD

AC22

VDD

AD2

VDD

AD3

VDD

AD7

VDD

AD9

VDD

AD11

VDD

AD23

VDD

AE10

VDD

AE12

VDD

AF7

VDD

AF9

VDD

AF11

VDD

AG4

VDD

AG5

VDD

AG7

VDD

AH2

VDD

AH3

VDD

ZIF-942P-S

SC101

22U-6V3-08-X-O

0112

SC72

22U-6V3-08-X

SC86

22U-6V3-08-X

+VCORE +VCORE

B3

VDD

C2

VDD

C4

VDD

D3

VDD

D5

VDD

E4

VDD

E6

VDD

F5

VDD

F7

VDD

G6

VDD

G8

VDD

H7

H11

H23

J8

J12

J14

J16

J18

J20

J22

J24

K7

K9

K11

K13

K15

K17

K19

K21

K23

L4

L5

L8

L10

L12

L14

L16

L18

L20

L22

M2

M3

M7

M9

M11

M13

M15

M17

M19

M21

M23

N8

N10

N12

N14

N16

N18

N20

N22

P7

P9

P11

P13

P15

P17

P19

P21

P23

R4

R5

R8

R10

R12

R14

R16

R18

R20

R22

T2

T3

T7

T9

T11

T13

+VDIMM

CRB:22uF*5,10uF*2

SC97

22U-6V3-08-X

+VCORE

CRB:22uF*25

2011-03-15

+VCORE

for AMD Validation Test

Not co-layout POS CAP

SC81

22U-6V3-08-X

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

ZIF-942P-S

D D

C C

B B

A A

4

POWER/GND2

12

SC102

10U-X5-08-X

SC73

22U-6V3-08-X

2011-03-15

for AMD Validation Test

Not co-layout POS CAP

SC89

22U-6V3-08-X

4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

12

SC103

10U-X5-08-X

M12

M14

M16

M18

M20

SC152

M22

22U-6V3-08-X-O

N4

N5

N7

N9

N11

N13

N15

N17

SC149

N19

22U-6V3-08-X-O

N21

N23

P2

P3

P8

12

P10

P12

C586

P14

10U-X5-08-O

P16

P18

P20

P22

R7

12

R9

R11

C589

R13

10U-X5-08-O

R15

2011-03-11

R17

for AMD Validation Test.

R19

R21

R23

T8

T10

T12

2011-04-20 VB to V1.0

T14

Add C584, C585, C242 for

T16

AMD 95W Validation Test.

T18

T20

+NB_VCORE

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

+NB_VCORE

V2

V3

CRB:22uF*3,4.7uF*1,0.22uF*2,0.01uF*1

V10

V12

12

V14

V16

C243

V18

22U-6V3-08

V20

V22

H20

+VCORE

W9

W11

CRB:4.7uF*3,0.22uF*2

W13

W15

12

W17

W19

SC71

W21

4.7U-X5-08-X

W23

Y8

Y10

Y12

Y14

+HT_1P2V

Y16

Y18

CRB:10uF*2,4.7uF*2,0.22uF*2,180pF*2

Y20

Y22

12

AA4

AA5

C277

AA7

10U-X5-08

AA9

+NB_VCORE

CRB:22uF*5

SC65

22U-6V3-08-X

SC84

22U-6V3-08-X

SC90

22U-6V3-08-X

C584

22U-6V3-08

12

C587

10U-X5-08-O

12

C590

10U-X5-08-O

12

C244

22U-6V3-08

12

SC83

4.7U-X5-08-X

12

C276

10U-X5-08

C292

22U-6V3-08

SC82

22U-6V3-08-X

SC62

22U-6V3-08-X

SC151

22U-6V3-08-X-O

SC150

22U-6V3-08-X-O

C585

22U-6V3-08

+VCORE

+NB_VCORE

SC153

22U-6V3-08-X-O

+VCORE

SC154

22U-6V3-08-X-O

+VCORE

12

C588

10U-X5-08-O

12

C591

10U-X5-08-O

12

12

C241

22U-6V3-08

12

12

SC78

4.7U-X5-08-X

12

12

C279

4.7U-X5-08

C295

SC58

22U-6V3-08

22U-6V3-08-X

2011-03-15

for AMD Validation Test

Not co-layout POS CAP

SC75

22U-6V3-08-X

3

CPU1F

A4

VDDNB

A6

VDDNB

B5

VDDNB

B7

VDDNB

C6

VDDNB

C8

VDDNB

D7

VDDNB

D9

VDDNB

E8

VDDNB

E10

VDDNB

F9

VDDNB

F11

VDDNB

G10

VDDNB

G12

VDDNB

1

MT1

2

MT2

3

MT3

4

MT4

5

MT5

6

MT6

7

MT7

8

MT8

9

MT9

10

MT10

11

MT11

12

MT12

13

MT13

14

MT14

15

MT15

16

MT16

17

MT17

B2

NP/RSVD

18

MT18

19

MT19

20

MT20

21

MT21

22

MT22

23

MT23

24

MT24

25

MT25

26

MT26

ZIF-942P-S

C242

22U-6V3-08

SC76

.22U-16V-04-X

C278

4.7U-X5-08

SC80

22U-6V3-08-X

SC91

22U-6V3-08-X

3

2

Processor Power and Ground

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA21

VSS

AA23

VSS

AB2

VSS

AB3

VSS

AB8

VSS

AB10

VSS

AB12

VSS

AB14

VSS

AB16

VSS

AB18

VSS

AB20

VSS

AB22

VSS

AC7

VSS

AC9

VSS

AC11

VSS

AC13

VSS

AC15

VSS

AC17

VSS

AC19

VSS

AC21

VSS

AC23

VSS

AD8

VSS

AD10

VSS

AD12

VSS

AD14

VSS

AD16

VSS

AD20

VSS

AD22

VSS

AD24

VSS

AE4

VSS

AE5

VSS

AE7

VSS

AE11

VSS

AF2

VSS

AF3

VSS

W7

VSS

AF10

VSS

AF12

VSS

AF14

VSS

AF16

VSS

H24

VSS

AF8

VSS

+HT_1P2V_C

12

C293

.01U-04

A1 A31

AM3

Top View

AL1 AL31

12

12

C383

C386

180P-04

180P-04

12

+VDIMM

SC74

22U-6V3-08-X

C273

.22U-16V-04

0112

0112

C491

+VDIMM +VCORE +NB_VCORE

180P-04

2 1

SC96

.01U-04-X

2 1

+HT_1P2V

12

C274

.1U-10VX-04

12

C239

.22U-16V-04

12

SC77

.22U-16V-04-X

12

C390

.22U-16V-04

C296

22U-6V3-08

20A

POWER/GND3

MT2728MT2829MT2930MT3031MT3132MT32

27

12

C240

.22U-16V-04

12

C353

.22U-16V-04

C490

180P-04

2 1

SC87

22U-6V3-08-X

SC92

22U-6V3-08-X

+HT_1P2V

CPU1G

AJ1

VLDT_A_1

AJ2

VLDT_A_2

AJ3

VLDT_A_3

AJ4

VLDT_A_4

+HT_1P2V_C

A12

VDDR

B12

VDDR

C12

VDDR

D12

VDDR

+VDIMM

M24

VDDIO_1

M26

VDDIO_2

M28

VDDIO_3

M30

VDDIO_4

P24

VDDIO_5

P26

VDDIO_6

P28

VDDIO_7

P30

VDDIO_8

T24

VDDIO_9

T26

VDDIO_10

T28

VDDIO_11

T30

VDDIO_12

V25

VDDIO_13

V26

VDDIO_14

V28

VDDIO_15

V30

VDDIO_16

Y24

VDDIO_17

Y26

VDDIO_18

Y28

VDDIO_19

Y29

VDDIO_20

AB24

VDDIO_21

AB26

VDDIO_22

AB28

VDDIO_23

AB30

VDDIO_24

AC24

VDDIO_25

AD26

VDDIO_26

AD28

VDDIO_27

AD30

VDDIO_28

AF30

VDDIO_29

ZIF-942P-S

+VCORE

CRB:10uF*1,4.7uF*2,0.22uF*1,0.01uF*2

12

12

C359

10U-X5-08

+HT_1P2V

CRB:22uF*1,4.7uF*2,0.22uF*2

12

C379

22U-6V3-08

12

C358

C357

4.7U-X5-08

4.7U-X5-08

+VDIMM

CRB:4.7uF*3,0.22uF*4,180pF*4

12

C428

4.7U-X5-08

12

C486

.22U-16V-04

12

C376

4.7U-X5-08

EMC

SC95

SC104

.01U-04-X

2 1

.01U-04-X

2 1

2

SC64

.01U-04-X

2 1

2 1

C284

.22U-16V-04

2 1

1

+HT_1P2V_B

H1

H2

H5

H6

+HT_1P2V

AG12

VDDR

AH12

VDDR

AJ12

VDDR

AK12

VDDR

AL12

VDDR

AF18

VSS

AF20

VSS

AF22

VSS

AF24

VSS

AF26

VSS

AF28

VSS

AG10

VSS

AG11

VSS

AH14

VSS

AH16

VSS

AH18

VSS

AH20

VSS

AH22

VSS

AH24

VSS

AH26

VSS

AH28

VSS

AH30

VSS

AK2

VSS

AK14

VSS

AK16

VSS

AK18

VSS

AK20

VSS

AK22

VSS

AK24

VSS

AK26

VSS

AK28

VSS

AK30

VSS

AL5

VSS

12

C354

.01U-04

12

C420

C430

.22U-16V-04

.22U-16V-04

12

12

C488

180P-04

12

12

C285

.22U-16V-04

C294

.01U-04

2 1

2 1

RS880PM-AM

RS880PM-AM

RS880PM-AM

HT_1P2V_B

2011-03-15

Stuff SC33 POS CAP for

AMD Validation Test.

2011-03-15

Reserve SC155, SC156

POS CAP for

AMD Validation Test.

C485

180P-04

0112

C351

4.7U-X5-08

SC70

180P-04-X

1

VLDT_B_1

2.5A

VLDT_B_2

VLDT_B_3

VLDT_B_4

4A

POWER/GND4

5A

Place caps about three inches apart along

+VCORE entire trace EMI Caps

12

C224

.01U-04-O

12

C417

4.7U-X5-08

12

C489

.22U-16V-04

12

C380

4.7U-X5-08

SC93

.01U-04-X

12

12

C219

C561

.01U-04-O

.01U-04-O

12

12

C355

C356

.22U-16V-04

.01U-04

Place across each

VDIMM-GND plane split.

12

12

C421

4.7U-X5-08

12

12

C487

C484

180P-04

180P-04

12

C352

.22U-16V-04

SC94

SC63

180P-04-X

.01U-04-X

2 1

2 1

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

AM3+ CPU PWR & GND

AM3+ CPU PWR & GND

AM3+ CPU PWR & GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Place as close

as possible to

CPU socket.

C255

10U-X5-08

2 1

+VCORE

12

SC33

330U-2V-9M-X

+VCORE

12

SC155

330U-2V-9M-X-O

+VCORE

12

SC156

330U-2V-9M-X-O

DIMMs

of

of

of

5 37Thursday, May 26, 2011

5 37Thursday, May 26, 2011

5 37Thursday, May 26, 2011

1.0.

1.0.

1.0.

Page 6

5

4

3

2

1

2

4

6

8

18

H_DBREQ_L

CPU_RST_L

CPU_PLLTEST0

CPU_PLLTEST1

2011-03-08 VA to VB

48121_1_02 AM3r2

Processor Motherboard

Schematic Checklist (NDA)_

2011-02-07.xlsx update.

R248 1K-04

H_TCK

H_TMS

H_TDI

H_TRST_L

HDT_10

+VDIMM

1 2

RN12

1 2

3 4

5 6

7 8

1K-8P4R-O

1 2

R254 0-04-O

1 2

ER61 15-1-04-O

1 2

ER53 15-1-04-O

0112

QN7

PMBS3904-S-O

E C

H_TCK 4

H_TMS 4

H_TDI 4

H_TDO 4

H_PWROK 4

H_DBRDY 4

H_DBREQ_L 4

H_TEST19_PLLTEST0 4

H_TEST18_PLLTEST1 4

+1.8V

12

R258

10K-04-O

HDT_8G

B

0127

12

R267

10K-04-O

HDT_2G

B

QN8

PMBS3904-S-O

EC

+VCC3+1.8V

12

12

IMC_TDI 15

R262

10K-04-O

IMC_TCK 15

C372

33P-04-O

12

R268

10K-04-O

HDT_4G

B

QN5

PMBS3904-S-O

EC

+VCC3+1.8V+VDIMM

12

12

R260

10K-04-O

C366

33P-04-O

IMC_TMS 15

HDT:Hardware Debug Tool

D D

H_TRST_L4

C C

H_RST_L4

B B

+VDIMM

2011-03-22 VA to VB

If HDT not use, can be un-populated.

12

R230

10K-04-O

HDT_12G

B

QN2

PMBS3904-S-O

EC

12

R228

300-04-O

IMC_TDO15

1 2

RN13 10K-8P4R-O

3 4

5 6

7 8

H_DBRDY

+1.8V

12

HDT_9G

B

E C

IMC_TRST-15

+VCC3 +1.8V

12

12

R237

10K-04-O

HDT_6G

B

E C

12

C343

33P-04-O

R257

10K-04-O

QN6

PMBS3904-S-O

R236

10K-04-O

QN3

PMBS3904-S-O

11-106-942120

(替)11-106-942020

CPU HDT+ Connector

+VDIMM

HDT

1

CPU_VDDIO

3

GND

5

GND

7

GND

9

CPU_TRST_L10CPU_PWROK_BUF

11

HDT_11

CPU_DBRDY312CPU_RST_L_BUF

13

HDT_13

CPU_DBRDY214CPU_DBRDY0

15

HDT_15

CPU_DBRDY116CPU_DBREQ_L

17

GND

19

CPU_VDDIO20CPU_PLLTEST1

HDTHEADER-O

2011-04-08 VB to V1.0

If HDT not use, can be un-populated

RN12, R248, RN13, R257, QN6, R228, R230, QN2,

R237, R236, C343, QN3, R258, QN7, R268, R260,

QN5, C366, R267, R262, QN8, C372,R254,ER53,ER61

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TDO

CPU_PLLTEST0

A A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

HDT

HDT

HDT

RS880PM-AM

RS880PM-AM

RS880PM-AM

1

1.0.

1.0.

6

6

6

1.0.

of

37Thursday, May 26, 2011

of

37Thursday, May 26, 2011

of

37Thursday, May 26, 2011

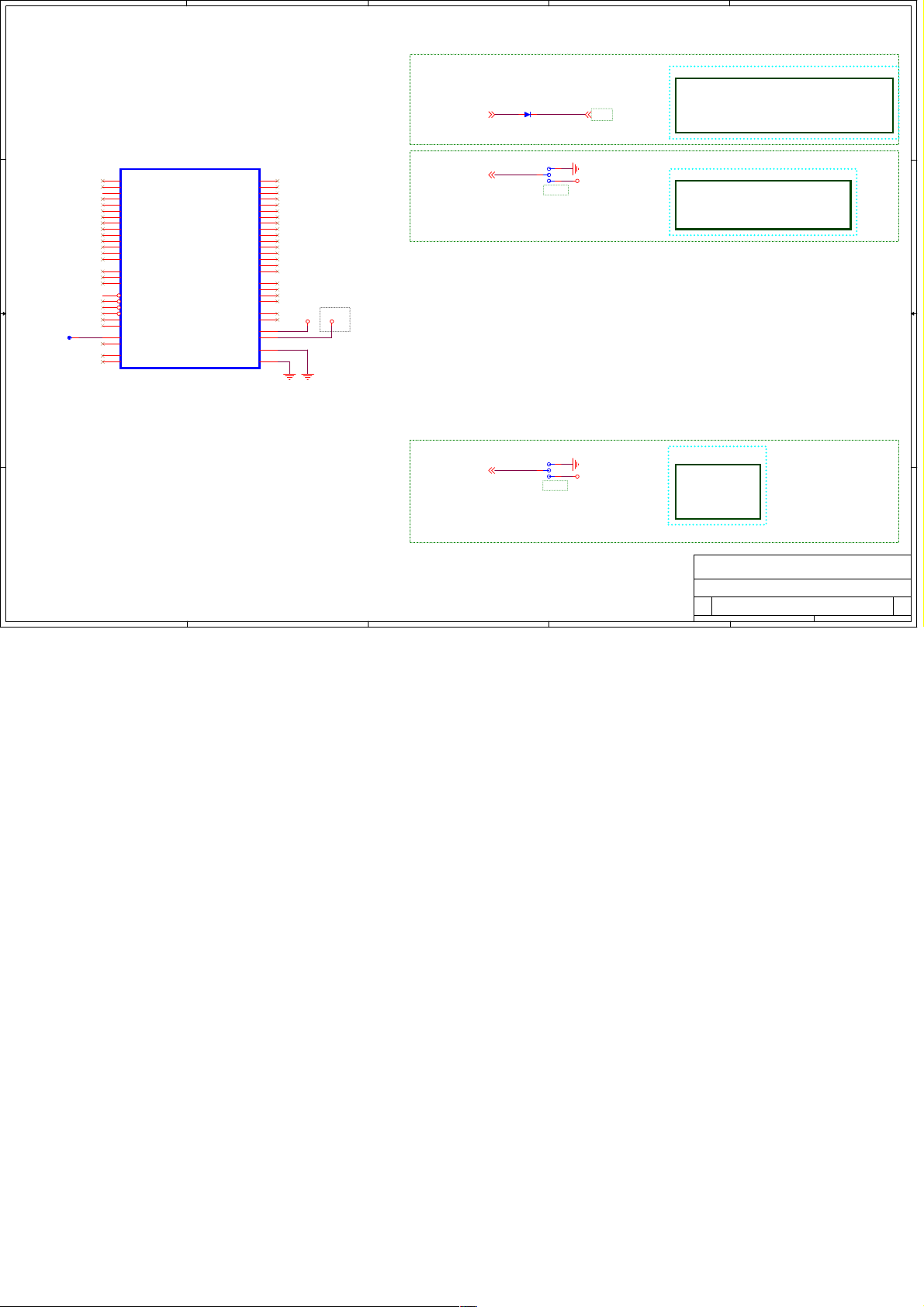

Page 7

5

2011-05-13 V1.0 to V1.0(.)

DIMM1 rename to DIMM4 for meet Acer spec.

D D

C C

+MEM_VREFDQ

B B

MA_ADD[15..0]

MA_ADD[15..0]3,8

A A

MA_EVENT_L3,8

+MEM_VREFCA

SCLK08,15

SDATA08,15

MA_BANK23,8

MA_BANK13,8

MA_BANK03,8

MA_CKE13,8

MA_CKE03,8

MA0_CS_L13

MA0_CS_L03

MA0_CLK_N13

MA0_CLK_P13

MA0_CLK_N03

MA0_CLK_P03

MA_RESET_L3,8

MA_CAS_L3,8

MA_RAS_L3,8

MA_WE_L3,8

MA_EVENT_L

+DDR_VTTR

+VDIMM

+VCC3

SCLK0

SDATA0

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA0_CS_L1

MA0_CS_L0

MA0_CLK_N1

MA0_CLK_P1

MA0_CLK_N0

MA0_CLK_P0

MA_RESET_L

MA_CAS_L

MA_RAS_L

MA_WE_L

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

198

187

49

48

240

120

239

235

232

229

226

223

220

217

214

211

208

205

202

199

166

163

160

157

154

151

148

145

142

139

136

133

130

127

124

121

119

116

113

110

107

104

101

98

95

92

89

86

83

80

47

44

41

38

35

32

29

26

23

20

17

14

11

8

5

2

197

194

191

189

186

183

182

179

176

173

170

78

75

72

69

66

65

62

60

57

54

51

236

67

1

118

238

237

117

52

190

71

169

50

76

193

64

63

185

184

188

181

61

180

59

58

178

56

177

175

70

55

174

196

172

171

168

74

192

73

DIMM4

FREE

FREE

FREE

FREE

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDSPD

VREFCA

VREFDQ

SCL

SDA

SA1

SA0

BA2

BA1

BA0

CKE1

CKE0

S1*

S0*

CK1/NU*

CK1/NU

CK0*

CK0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

RESET*

CAS*

RAS*

WE*

DDR3-240P-BL

RSVD

ODT1

ODT0

NC/PAR IN

NC/ERR OUT

NC/TEST4

CB(0)

CB(1)

CB(2)

CB(3)

CB(4)

CB(5)

CB(6)

CB(7)

DQS(0)

DQS*(0)

DSQ(1)

DSQ*(1)

DSQ(2)

DSQ*(2)

DSQ(3)

DSQ*(3)

DQS(4)

DQS*(4)

DQS(5)

DQS*(5)

DSQ(6)

DSQ*(6)

DQS(7)

DQS*(7)

DQS(8)

DQS*(8)

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ(0)

DQ(1)

DQ(2)

DQ(3)

DQ(4)

DQ(5)

DQ(6)

DQ(7)

DQ(8)

DQ(9)

DQ(10)

DQ(11)

DQ(12)

DQ(13)

DQ(14)

DQ(15)

DQ(16)

DQ(17)

DQ(18)

DQ(19)

DQ(20)

DQ(21)

DQ(22)

DQ(23)

DQ(24)

DQ(25)

DQ(26)

DQ(27)

DQ(28)

DQ(29)

DQ(30)

DQ(31)

DQ(32)

DQ(33)

DQ(34)

DQ(35)

DQ(36)

DQ(37)

DQ(38)

DQ(39)

DQ(40)

DQ(41)

DQ(42)

DQ(43)

DQ(44)

DQ(45)

DQ(46)

DQ(47)

DQ(48)

DQ(49)

DQ(50)

DQ(51)

DQ(52)

DQ(53)

DQ(54)

DQ(55)

DQ(56)

DQ(57)

DQ(58)

DQ(59)

DQ(60)

DQ(61)

DQ(62)

DQ(63)

79

77

195

68

53

167

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

MA0_ODT1

MA0_ODT0

MA_DQS_P0

MA_DQS_N0

MA_DQS_P1

MA_DQS_N1

MA_DQS_P2

MA_DQS_N2

MA_DQS_P3

MA_DQS_N3

MA_DQS_P4

MA_DQS_N4

MA_DQS_P5

MA_DQS_N5

MA_DQS_P6

MA_DQS_N6

MA_DQS_P7

MA_DQS_N7

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

4

MA0_ODT1 3

MA0_ODT0 3

MA_DQS_P0 3,8

MA_DQS_N0 3,8

MA_DQS_P1 3,8

MA_DQS_N1 3,8

MA_DQS_P2 3,8

MA_DQS_N2 3,8

MA_DQS_P3 3,8

MA_DQS_N3 3,8

MA_DQS_P4 3,8

MA_DQS_N4 3,8

MA_DQS_P5 3,8

MA_DQS_N5 3,8

MA_DQS_P6 3,8

MA_DQS_N6 3,8

MA_DQS_P7 3,8

MA_DQS_N7 3,8

MA_DM[7..0]

MA_DATA[63..0]

MA_DM[7..0] 3,8

MA_DATA[63..0] 3,8

+VCC3

+MEM_VREFDQ

MB_ADD[15..0]3,8

3

MB_EVENT_L3,8

+MEM_VREFCA

SCLK08,15

SDATA08,15

MB_BANK23,8

MB_BANK13,8

MB_BANK03,8

MB_CKE13,8

MB_CKE03,8

MB0_CS_L13

MB0_CS_L03

MB0_CLK_N13

MB0_CLK_P13

MB0_CLK_N03

MB0_CLK_P03

MB_ADD[15..0]

MB_RESET_L3,8

MB_CAS_L3,8

MB_RAS_L3,8

MB_WE_L3,8

0113 follow Dory

MB_EVENT_L

+DDR_VTTR

+VDIMM

+VCC3

SCLK0

SDATA0

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB0_CS_L1

MB0_CS_L0

MB0_CLK_N1

MB0_CLK_P1

MB0_CLK_N0

MB0_CLK_P0

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_RESET_L

MB_CAS_L

MB_RAS_L

MB_WE_L

198

187

49

48

240

120

239

235

232

229

226

223

220

217

214

211

208

205

202

199

166

163

160

157

154

151

148

145

142

139

136

133

130

127

124

121

119

116

113

110

107

104

101

98

95

92

89

86

83

80

47

44

41

38

35

32

29

26

23

20

17

14

11

8

5

2

197

194

191

189

186

183

182

179

176

173

170

78

75

72

69

66

65

62

60

57

54

51

236

67

1

118

238

237

117

52

190

71

169

50

76

193

64

63

185

184

188

181

61

180

59

58

178

56

177

175

70

55

174

196

172

171

168

74

192

73

DIMM3

FREE

FREE

FREE

FREE

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDSPD

VREFCA

VREFDQ

SCL

SDA

SA1

SA0

BA2

BA1

BA0

CKE1

CKE0

S1*

S0*

CK1/NU*

CK1/NU

CK0*

CK0

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

RESET*

CAS*

RAS*

WE*

DDR3-240P-BL

RSVD

ODT1

ODT0

NC/PAR IN

NC/ERR OUT

NC/TEST4

CB(0)

CB(1)

CB(2)

CB(3)

CB(4)

CB(5)

CB(6)

CB(7)

DQS(0)

DQS*(0)

DSQ(1)

DSQ*(1)

DSQ(2)

DSQ*(2)

DSQ(3)

DSQ*(3)

DQS(4)

DQS*(4)

DQS(5)

DQS*(5)

DSQ(6)

DSQ*(6)

DQS(7)

DQS*(7)

DQS(8)

DQS*(8)

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ(0)

DQ(1)

DQ(2)

DQ(3)

DQ(4)

DQ(5)

DQ(6)

DQ(7)

DQ(8)

DQ(9)

DQ(10)

DQ(11)

DQ(12)

DQ(13)

DQ(14)

DQ(15)

DQ(16)

DQ(17)

DQ(18)

DQ(19)

DQ(20)

DQ(21)

DQ(22)

DQ(23)

DQ(24)

DQ(25)

DQ(26)

DQ(27)

DQ(28)

DQ(29)

DQ(30)

DQ(31)

DQ(32)

DQ(33)

DQ(34)

DQ(35)

DQ(36)

DQ(37)

DQ(38)

DQ(39)

DQ(40)

DQ(41)

DQ(42)

DQ(43)

DQ(44)

DQ(45)

DQ(46)

DQ(47)

DQ(48)

DQ(49)

DQ(50)

DQ(51)

DQ(52)

DQ(53)

DQ(54)

DQ(55)

DQ(56)

DQ(57)

DQ(58)

DQ(59)

DQ(60)

DQ(61)

DQ(62)

DQ(63)

2

79

77

MB0_ODT1

MB0_ODT0

MB_DQS_P0

MB_DQS_N0

MB_DQS_P1

MB_DQS_N1

MB_DQS_P2

MB_DQS_N2

MB_DQS_P3

MB_DQS_N3

MB_DQS_P4

MB_DQS_N4

MB_DQS_P5

MB_DQS_N5

MB_DQS_P6

MB_DQS_N6

MB_DQS_P7

MB_DQS_N7

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB0_ODT1 3

MB0_ODT0 3

MB_DQS_P0 3,8

MB_DQS_N0 3,8

MB_DQS_P1 3,8

MB_DQS_N1 3,8

MB_DQS_P2 3,8

MB_DQS_N2 3,8

MB_DQS_P3 3,8

MB_DQS_N3 3,8

MB_DQS_P4 3,8

MB_DQS_N4 3,8

MB_DQS_P5 3,8

MB_DQS_N5 3,8

MB_DQS_P6 3,8

MB_DQS_N6 3,8

MB_DQS_P7 3,8

MB_DQS_N7 3,8

MB_DM[7..0]

silkscreen

DIMM1

DIMM2

DIMM3

DIMM4

MB_DATA[63..0]

MB_DM[7..0] 3,8

MB_DATA[63..0] 3,8

195

68

53

167

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93