Page 1

5

4

3

2

1

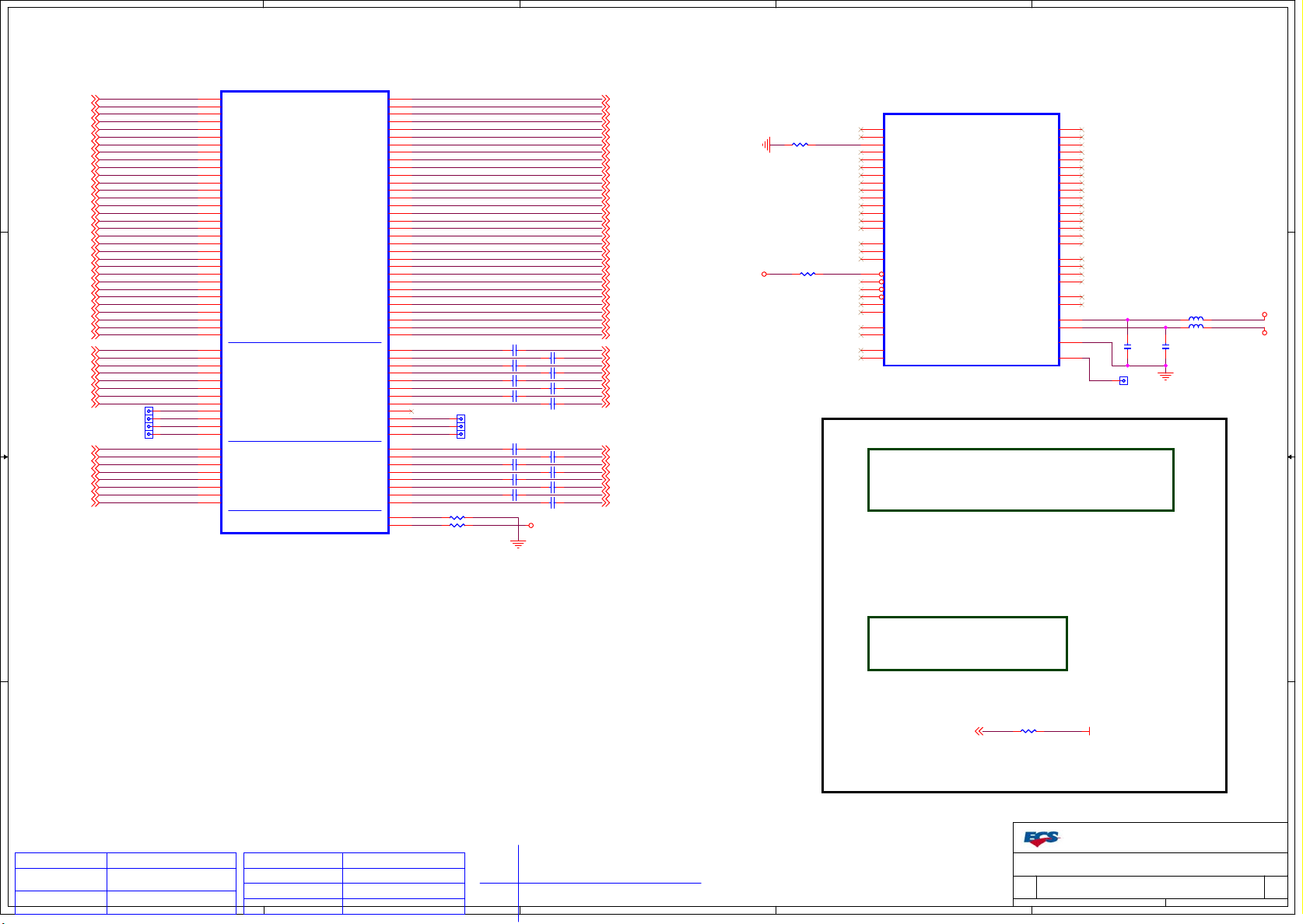

RS780M-A2

D D

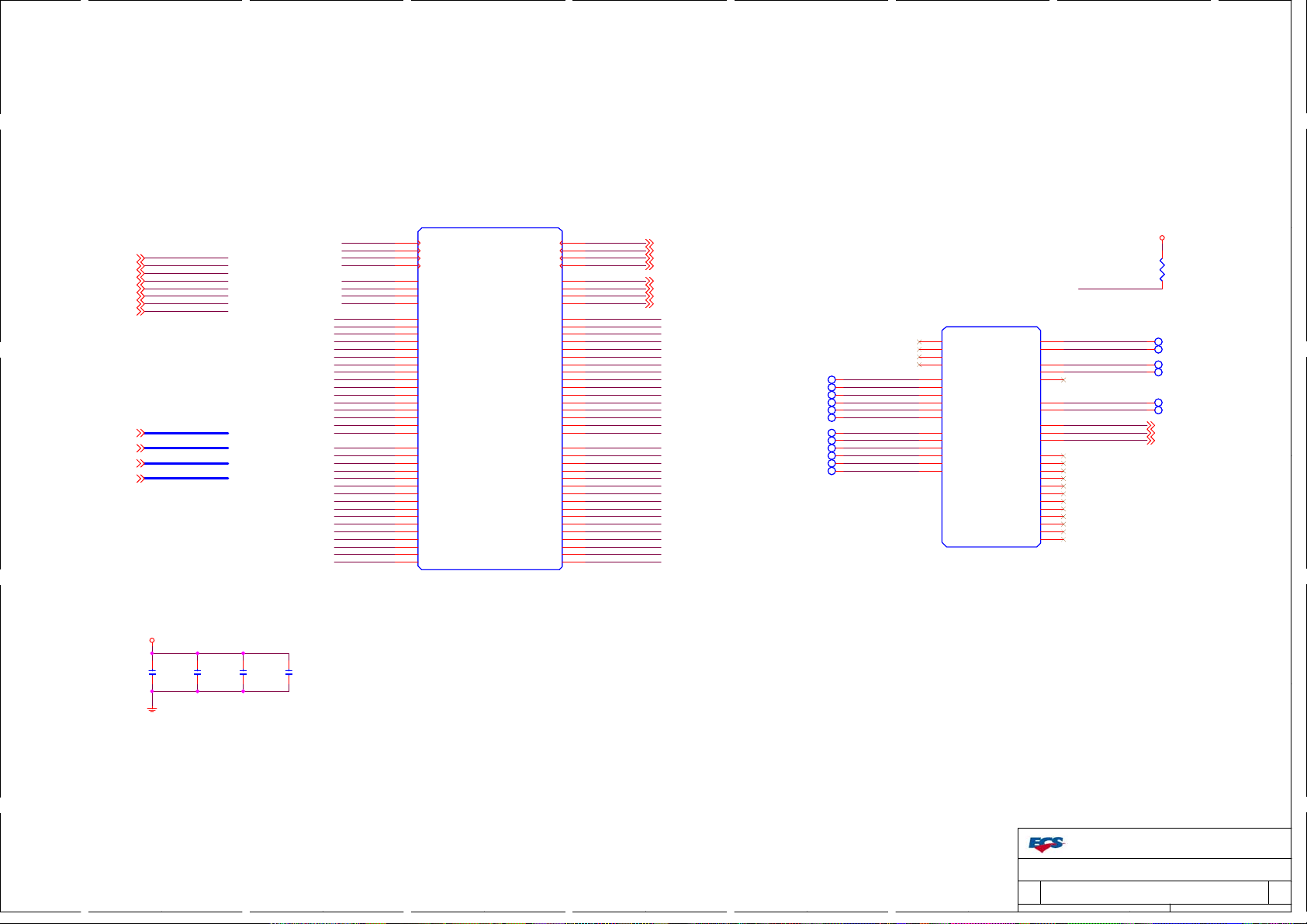

SCHEMATICS TABLE:

Page Index

------- ------------------------

1

COVER PAGE

BLOCK DIADRAM

2

3

CPU M2-1 HyperTransport

CPU M2-2 DDR2

4

5

CPU M2-3 Miscellany

6

C C

10

11

12

13

14

15

B B

16

17

18

19

CPU M2-4 Power and Ground

7

First Logic DDR2 DIMM

8

Second Logic DDR2 DIMM

9

DDR2 Termination

CLOCK GEN ICS9LPRS471

RS780 HT LINK I/F

RS780 PCIE I/F

RS780 SYSTEM I/F

RS780 POWER 33

PCI-E X16 CONN&PCI-E X8CONN

VGA/HDMI

SB700 STRAP/PWR/DECOUPLING

SB700 PCIE/PCI/CPU/LPC

SB700 ACPI/GPIO//USB/AUDIO

Page Index

------- ------------------------

20

SB700 SATA/IDE/HWM/SPI

21 SB700 STRAPS

22

PCI1&2

23

USB/IDE

24

PCI-E x1(2 SLOTS) & PCI3

25

PCIE LAN RTL8111C/8101E-1

26

Audio Codec ALC888S

27

Audio Interface

28

JMB361 ESATA+USB

29

IT8726

30

FAN CTAL

FRONT PANEL

31

32

OVER CLOCK / PS2

CPU VCORE ISL6323

NB POWER

34

DC-DC

35

36

POWER SEQUENCE

37

CLOCK DISTRIBUTION

38

POWER DELIVERY CHART

Attention&104&IMPENDANCE

39

REVISION HISTORY:

Rev Date Notes

VA 2008/08/12

V1.0 2008/09/18

Modify RS780D

DEL ADD

1. SP

2. PCIE SW

3. -1 PCIE x16

4. -1 LAN 8112

5. 1394

6. 4PIN POWER

V : 1.0

1. JMB361(ESATA)

2. +1 PCI

3. POWER LED

L1:TOPPCB STACK:

L2:PWR

L3:GND

L4:BOTTON

IMPORTANT NOTES ABOUT

THIS SCHEMATIC

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

DESIGN NOTE: Example

A A

text for the design note to

show the note inside the

colored box.

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

1) DESIGN NOTES in

grey are information

notes.

2) DESIGN NOTES in

yellow are notes of

caution.

3) DESIGN NOTES in

red are critical, and

must be understood and

followed.

5

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Cover Page

Cover Page

Cover Page

RS780M-A2

139Tuesday, October 21, 2008

139Tuesday, October 21, 2008

139Tuesday, October 21, 2008

of

of

1

of

1.0

1.0

1.0

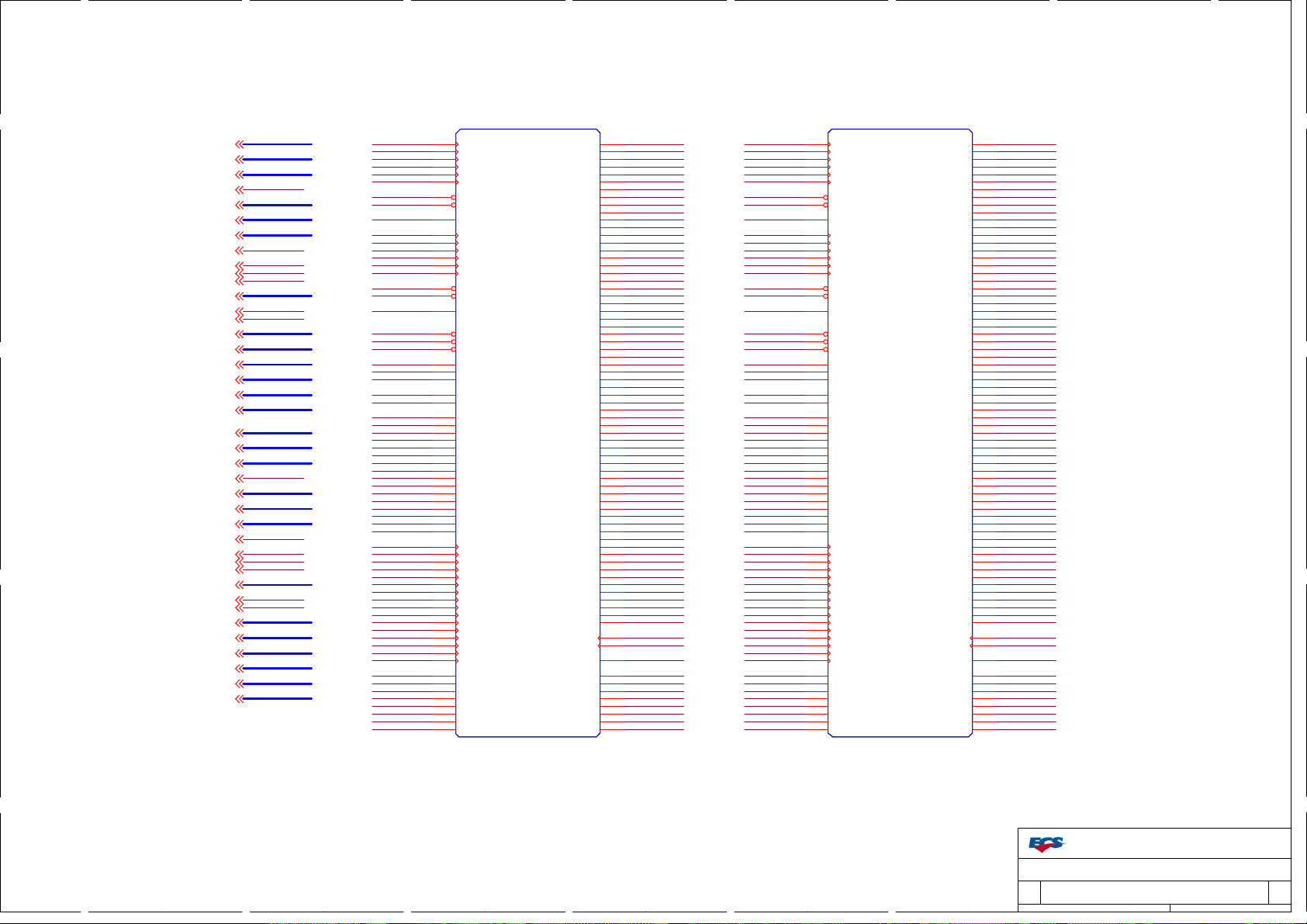

Page 2

5

4

3

2

1

DDRII 400,533,667,800,1066

note:1066 for AM2g2

128bit

DDRII 400,533,667,800,1066

LINK

AMD

AM2/AM2g2

AM2 SOCKET

OUT

IN

3,4,5,6

16x16

D D

OVER Clock

35

Clock

Generator

ICS9LPR471

10

HyperTransport

UNBUFFERED

DDRII DIMM1

UNBUFFERED

DDRII DIMM2

DDRII FIRST LOGICAL DIMM

7,9

7,9 8,9

UNBUFFERED

DDRII DIMM3

UNBUFFERED

DDRII DIMM4

DDRII SECOND LOGICAL DIMM

8,9

RX780/RS780/RS780D

HyperTransport LINK0 CPU I/F

DX10 IGP( RS780)

VGA CON

HDMI /DVI CON

C C

USB-7

24

USB-8

B B

USB-9

24

24 24 30

USB-11USB-10

USB-12

17

18

USB-2USB-6 USB-3USB-4USB-5

USB-1

2724242424

USB 2.0

27

30

PCI BUS

PCI BUS

LVDS/TVOUT/TMDS(RS780/740)

DISPLAY PORT X2 (RS780)

Side Port Memory(RS780/740)

1 X16 PCIE I/F

1 X4 PCIE I/F WITH SB

6 X1 PCIE I/F (4 X1 for RS740)

11,12,13,14,15

4X

PCIE

SB750

USB2.0 (12)+ 1.1(2)

SATA II (6 PORTS)

AZALIA HD AUDIO

ATA 66/100/133

SPI I/F

LPC I/F(S5)

ACPI 1.1

INT RTC

HW MONITOR

PCI/PCI BDGE

19,20, 21, 22, 23,

16X

PCIE GPP[1:0]

X1

26

HD AUDIO I/F

SATA II I/F

ATA 66/100/133 I/F

ATA 66/100/133 I/F

6 1X PCIE INTERFACE

PCIE GPP2

GIGABIT

27

RTL8111C

PCIE GPP3

JMB361

30

HD AUDIO HDR

28

SATA#0 SATA#1

IDE CON

FLASH

BIOS

24

23

16X or 8X

2323

HD AUDIO

REAR CON

SATA#2

PCIE

16X

SLOT

ESATA

30

29

SATA#3

23 23

16

SATA#4

SATA#5

23

23

PCI SLOT

#1

DESKTOP AM2/AM2g2

POWER

A A

5

DDR2

MEMORY

POWER

36

38

25

PCI SLOT

#2

RS780

CORE & PCIE

POWER

SB700

CORE & PCIE

POWER

4

PCI SLOT

25

#3

26

ITE LPC SIO

IT8726

31

37

37

COM1

KBD

MOUSE

34

34

3

2

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

BLOCK DIAGRAM

RS780M-A2

RS780M-A2

RS780M-A2

2

2

2

of

of

1

of

1.0

1.0

1.0

39Tuesday, October 21, 2008

39Tuesday, October 21, 2008

39Tuesday, October 21, 2008

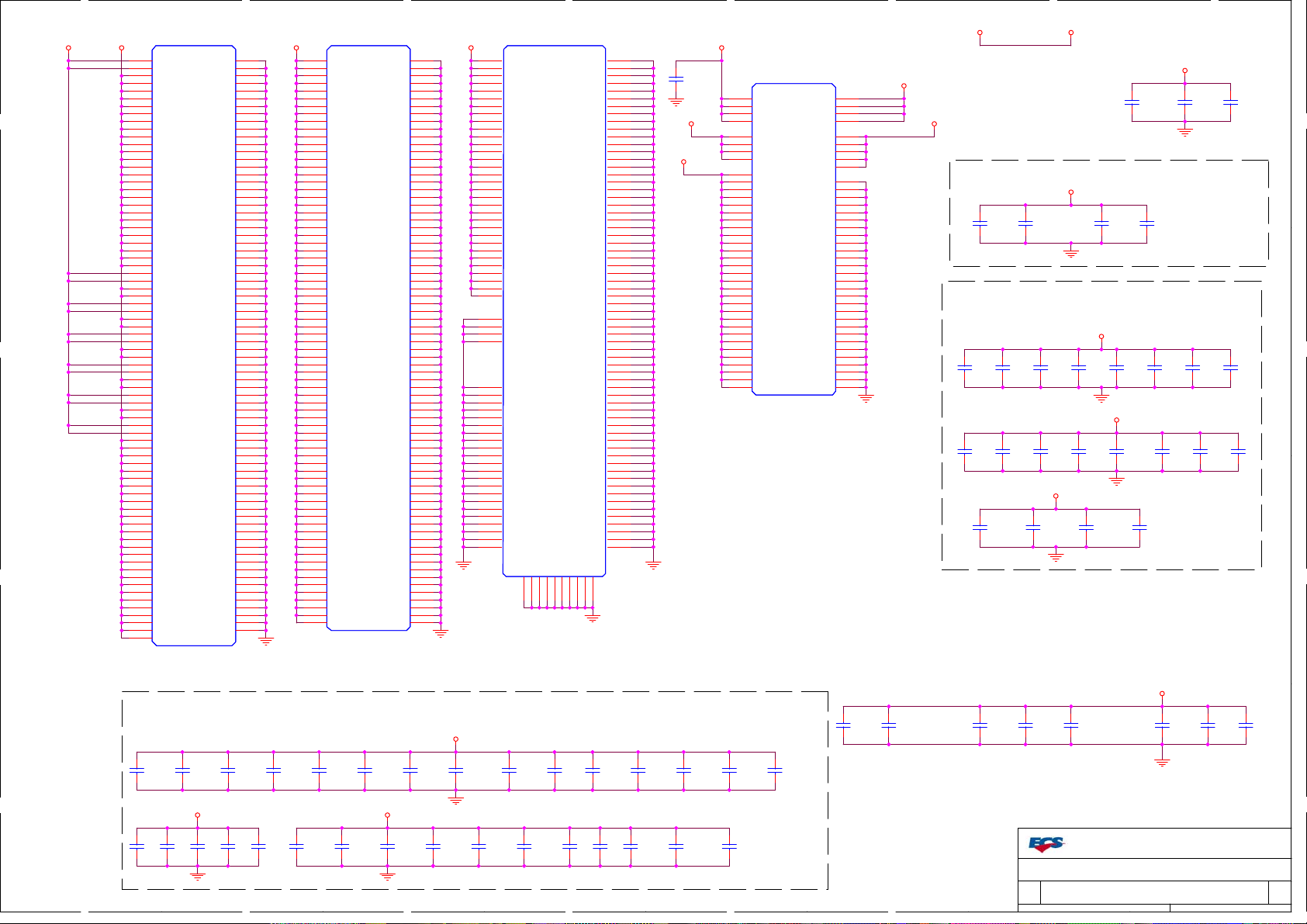

Page 3

8

A

7

6

5

4

3

2

1

D D

CPU1A

CPU1A

HYPERTRANSPORT

L0_CLKIN_H1

L0_CLKIN_H111

L0_CLKIN_L111

L0_CLKIN_H011

L0_CLKIN_L011

L0_CTLIN_H011

L0_CTLIN_L011

L0_CTLIN_H111

L0_CTLIN_L111

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

C C

L0_CADIN_L[0..15]11

L0_CADIN_H[0..15]11

L0_CADOUT_H[0..15]11

L0_CADOUT_L[0..15]11

L0_CADIN_L[0..15]

L0_CADIN_H[0..15]

L0_CADOUT_H[0..15]

L0_CADOUT_L[0..15]

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1 11

L0_CLKOUT_L1 11

L0_CLKOUT_H0 11

L0_CLKOUT_L0 11

L0_CTLOUT_H1 11

L0_CTLOUT_L1 11

L0_CTLOUT_H0 11

L0_CTLOUT_L0 11

STP24STP24

STP20STP20

STP23STP23

STP22STP22

STP21STP21

STP25STP25

STP31STP31

STP29STP29

STP30STP30

STP26STP26

STP27STP27

STP28STP28

MA1_CLK_H3

1

MA1_CLK_L3

1

MA1_ODT1

1

MA0_CLK_H3

1

MA0_CLK_L3

1

MA0_ODT1

1

MB1_CLK_H3

1

MB1_CLK_L3

1

MB1_ODT1

1

MB0_CLK_H3

1

MB0_CLK_L3

1

MB0_ODT1

1

W26

W25

AE27

U24

V24

AE28

Y31

Y30

AG31

V31

W31

AF31

CPU_CORE_TYPE

CPU1E

CPU1E

INTERNAL MISC E

INTERNAL MISC E

L25

RSVD1

L26

RSVD2

L31

RSVD3

L30

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

CPU_MA_RESET

E20

CPU_MB_RESET

B19

CPU_ALERT_L

AL4

CPU_SA0

AK4

AK3

CPU_RSVD_VIDSTRB1

F2

CPU_RSVD_VIDSTRB0

F3

CPU_VDDNB_FB

G4

CPU_VDDNB_FB-

G3

CPU_CORE_TYPE

G5

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

V_DIMM

R190

R190

300-04

300-04

1 2

STP19STP19

1

STP18STP18

1

STP14STP14

1

STP13STP13

1

STP11STP11

1

STP12STP12

1

CPU_VDDNB_FB 33

CPU_VDDNB_FB- 33

CPU_CORE_TYPE 33

B B

VCC_CORE

BC26

BC26

.1U-04-O

.1U-04-O

2 1

2 1

BC30

BC30

.1U-04-O

.1U-04-O

2 1

BC27

BC27

.1U-04-O

.1U-04-O

BC25

BC25

.1U-04-O

.1U-04-O

2 1

A

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

CPU M2-1 HyperTransport

CPU M2-1 HyperTransport

CPU M2-1 HyperTransport

RS780M-A2

RS780M-A2

RS780M-A2

3

3

3

of

of

of

1.0

1.0

1.0

39Tuesday, October 21, 2008

39Tuesday, October 21, 2008

39Tuesday, October 21, 2008

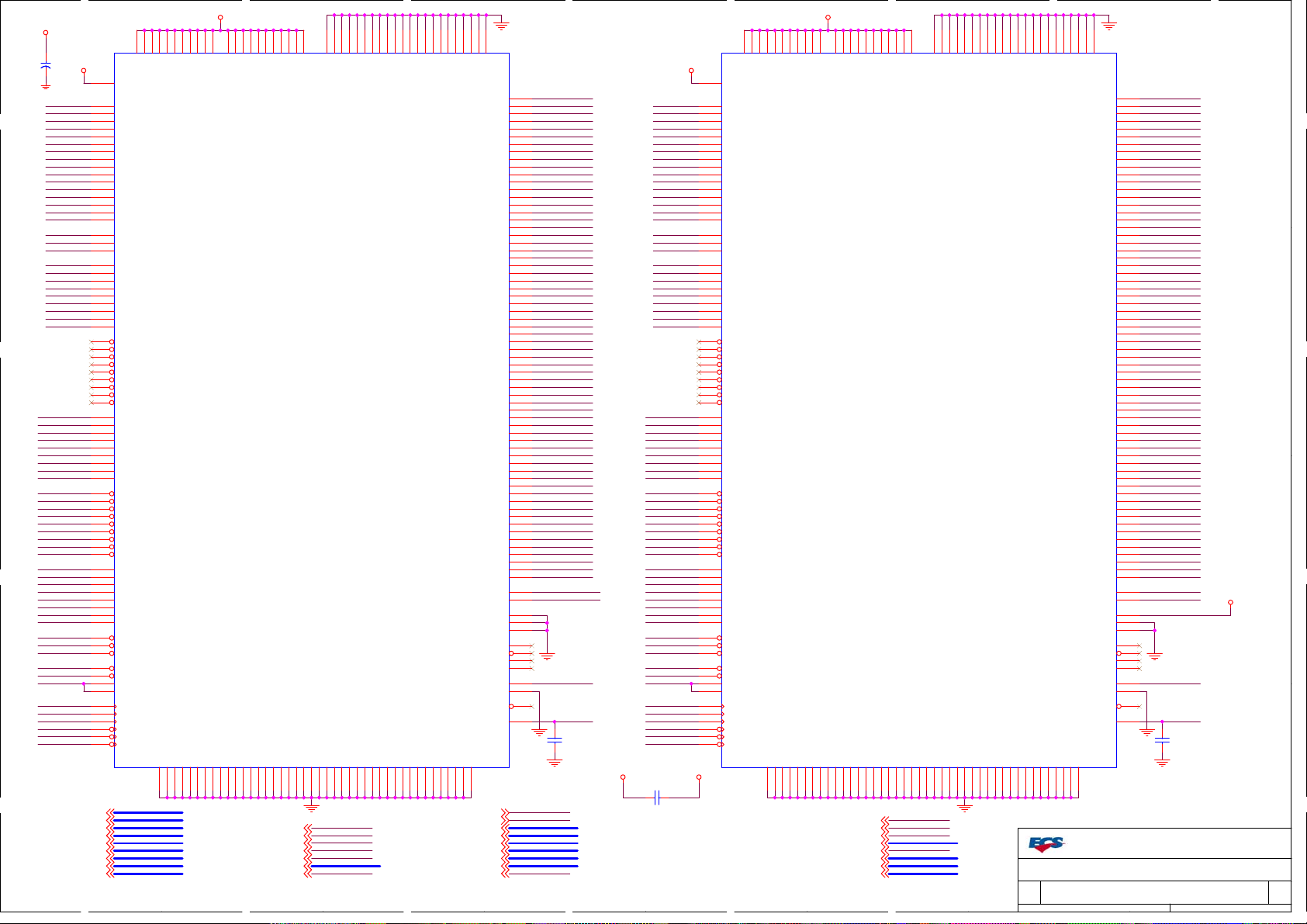

Page 4

8

A

D D

MA0_CLK_H[2..0]7,9

MA0_CLK_L[2..0]7,9

MA0_CS_L[1..0]7,9

MA1_CLK_H[2..0]8,9

MA1_CLK_L[2..0]8,9

MA1_CS_L[1..0]8,9

MA_BANK[2..0]7,8,9

MA_ADD[15..0]7,8,9

C C

B B

MA_DQS_H[8..0]7,8

MA_DQS_L[8..0]7,8

MA_DM[8..0]7,8

MA_DATA[63..0]7,8

MA_CHECK[7..0]7,8

MB0_CLK_H[2..0]7,9

MB0_CLK_L[2..0]7,9

MB0_CS_L[1..0]7,9

MB1_CLK_H[2..0]8,9

MB1_CLK_L[2..0]8,9

MB1_CS_L[1..0]8,9

MB_BANK[2..0]7,8,9

MB_ADD[15..0]7,8,9

MB_DQS_H[8..0]7,8

MB_DQS_L[8..0]7,8

MB_DM[8..0]7,8

MB_DATA[63..0]7,8

MB_CHECK[7..0]7,8

7

MA0_CLK_H[2..0]

MA0_CLK_L[2..0]

MA0_CS_L[1..0]

MA0_ODT07,9

MA1_ODT08,9

MA_CAS_L7,8,9

MA_WE_L7,8,9

MA_RAS_L7,8,9

MA_CKE18,9

MA_CKE07,9

MB0_ODT07,9

MB1_ODT08,9

MB_CAS_L7,8,9

MB_WE_L7,8,9

MB_RAS_L7,8,9

MB_CKE18,9

MB_CKE07,9

MA0_ODT0

MA1_CLK_H[2..0]

MA1_CLK_L[2..0]

MA1_CS_L[1..0]

MA1_ODT0

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK[2..0]

MA_CKE1

MA_CKE0

MA_ADD[15..0]

MA_DQS_H[8..0]

MA_DQS_L[8..0]

MA_DM[8..0]

MA_DATA[63..0]

MA_CHECK[7..0]

MB0_CLK_H[2..0]

MB0_CLK_L[2..0]

MB0_CS_L[1..0]

MB0_ODT0

MB1_CLK_H[2..0]

MB1_CLK_L[2..0]

MB1_CS_L[1..0]

MB1_ODT0

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK[2..0]

MB_CKE1

MB_CKE0

MB_ADD[15..0]

MB_DQS_H[8..0]

MB_DQS_L[8..0]

MB_DM[8..0]

MB_DATA[63..0]

MB_CHECK[7..0]

6

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA0_CLK_H0

MA0_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT0

MA1_CLK_H2

MA1_CLK_L2

MA1_CLK_H1

MA1_CLK_L1

MA1_CLK_H0

MA1_CLK_L0

MA1_CS_L1

MA1_CS_L0

MA1_ODT0

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

AG21

AG20

G19

H19

U27

U26

AC25

AA24

AC28

AE20

AE19

G20

G21

V27

W27

AD27

AA25

AC27

AB25

AB27

AA26

N25

Y27

AA27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

L27

T25

T27

F19

F15

MEMORY INTERFACE A

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

CPU1B

CPU1B

5

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

4

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_CLK_H0

MB0_CLK_L0

MB0_CS_L1

MB0_CS_L0

MB0_ODT0

MB1_CLK_H2

MB1_CLK_L2

MB1_CLK_H1

MB1_CLK_L1

MB1_CLK_H0

MB1_CLK_L0

MB1_CS_L1

MB1_CS_L0

MB1_ODT0

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

AJ19

AK19

U31

U30

AE30

AC31

AD29

AL19

AL18

C19

D19

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

N31

AA31

AA28

M31

M29

N28

N29

AE31

N30

AA29

R29

R28

R31

R30

U29

U28

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AH17

AJ23

AK29

C30

A18

A19

P29

P31

T31

T29

A23

B17

B13

MEMORY INTERFACE B

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

3

CPU1C

CPU1C

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

2

1

A

Elitegroup Computer Systems

Elitegroup Computer Systems

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

CPU M2-2 DDR2

CPU M2-2 DDR2

CPU M2-2 DDR2

RS780M-A2

RS780M-A2

RS780M-A2

439Tuesday, October 21, 2008

439Tuesday, October 21, 2008

439Tuesday, October 21, 2008

of

of

of

1.0

1.0

1.0

Page 5

8

A

7

6

5

4

3

2

1

AK6

AJ10

AJ11

AH9

AG9

AG8

AH7

C10

D10

AL3

AL6

AL9

E12

F12

A10

B10

F10

AJ7

AJ5

AJ6

A8

B8

C9

D8

C7

A5

G2

G1

E9

F6

D6

E7

F8

C5

E5

SB_CPUPWRGD_CPU

LDT_STOP_CPU-

LDT_RST_CPU-

12

C246

C246

.1U-04-O

.1U-04-O

CPU1D

CPU1D

MISC

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

THERMTRIP_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

VRD_VID5

D2

VRD_VID4

D1

VRD_VID3

C1

VRD_VID2

E3

VRD_VID1

E2

VRD_VID0

E1

THERMTRIP_L

AK7

PROCHOT_L

AL7

CPU_TDO

AK10

CPU_DBRDY

B6

CPU_VDDIO_FB_H

AK11

CPU_VDDIO_FB_L

AL11

CPU_PSI_L

F1

CPU_HTREF1

V8

CPU_HTREF0

V7

CPU_TEST29_H

C11

CPU_TEST29_L

D11

differential pair

shorter than 1.5 inches.

CPU_SC1

AK8

CPU_TEST23

AH8

CPU_SSEN_A

AJ9

CPU_SCAN_EN

AL8

CPU_SC2

AJ8

J10

H9

CPU_TEST27

AK9

CPU_TEST26

AK5

G7

D4

V_DIMM

R192

R192

1K-04

1K-04

1 2

1 2

CPU_TDO 32

CPU_DBRDY 32

TP10TP10

1

1

TP12TP12

1

TP6TP6

ER28 44.2-1-04ER28 44.2-1-04

1 2

ER27 44.2-1-04ER27 44.2-1-04

1 2

1

STP16STP16

1

STP17STP17

R191

R191

1K-04

1K-04

CPU_THERMTRIP- 19

PROCHOT_L 18

VLDT_B

ER36 80.6-1-04ER36 80.6-1-04

12

R202 300-04R202 300-04

1 2

VRD_VID[5..0]

CPU_SC2

CPU_SC1

CPU_SSEN_B

CPU_SSEN_A

VRD_VID[5..0] 33

2

4

6

8

RN11

RN11

1K-8P4R

1K-8P4R

1

3

5

7

+2.5V_VDDA for CPU PLL

U12A

U12A

G

1

OP358-S

OP358-S

12

12

CPU_M_VREFCPU_M_VREF

VCC3

DS

Q19

Q19

2N7002-S

2N7002-S

+2.5V_VDDA

12

EC41

EC41

100U-16L-OS-J

100U-16L-OS-J

12

ER31

ER31

169-1-04

169-1-04

+2.5V_VDDA@105mA

V_DIMM

CLKIN_H

CLKIN_L

2

4

6

8

2

4

6

8

RN10

RN10

300-8P4R

300-8P4R

RN7

RN7

300-8P4R

300-8P4R

+2.5V_VDDA

PROCHOT_L

1

THERMTRIP_L

3

CPU_TEST26

5

7

SB_CPUPWRGD_CPU

1

LDT_STOP_CPU-

3

LDT_RST_CPU-

5

CPU_PLLTEST1

7

3.R194 to CPU <600mil

4.C113,C117 to CPU <1250mil

L15

L15

1 2

FB120-08

FB120-08

Width:50mil and Long:500mil

12

MC34

MC34

10U-08

10U-08

12

V_DIMM

12

C235

C235

3300P-04-O

3300P-04-O

CPU_TDI32

CPU_TRST_32

CPU_TCK32

CPU_TMS32

CPU_DBREQ_32

CPU_CORE_FB33

CPU_CORE_FB-33

TP11TP11

ER32 39.2-1-04ER32 39.2-1-04

1 2

ER33 39.2-1-04ER33 39.2-1-04

1 2

R206 300-04R206 300-04

1 2

TP9TP9

TP8TP8

STP15STP15

TP7TP7

CPU_THERMDC29

CPU_THERMDA29

D D

EN_VDDA29

VCCNS_REF

R121

R121

1 2

10K-04

10K-04

+12V

84

3

+

+

2

-

-

C C

C230 3900P-04C230 3900P-04

CPU_CLKIN_H10

CPU_CLKIN_L10

B B

12

MC37

MC37

22U-6V3X-08-O

22U-6V3X-08-O

CPU_CLKIN_H

CPU_CLKIN_L

V_DIMM

12

ER35

ER35

16.9-1

16.9-1

12

ER34

ER34

16.9-1

16.9-1

12

C243

C243

.1U-04

.1U-04

C232 3900P-04C232 3900P-04

12

C244

C244

1000P-04-O

1000P-04-O

SB_CPUPWRGD18,33

CPU_VDDA

C233

C233

CLKIN_H

CLKIN_L

.22U-06

.22U-06

SB_CPUPWRGD_CPU

LDT_STOP_CPULDT_RST_CPU-

CPU_SIC

CPU_SID

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

CPU_CORE_FB

CPU_CORE_FB-

CPU_VTT_SENSE

1

CPU_M_VREF

CPU_M_ZN

CPU_M_ZP

CPU_TEST25_H

CPU_TEST25_L

CPU_PLLTEST0

CPU_PLLTEST1

CPU_BP3

1

CPU_BP2

1

CPU_BP1

1

CPU_BP0

1

CPU_SSEN_B

LDT_STOP-13,18

LDT_RST-13,18,32

AL10

AH10

AH11

V_DIMM

R193 1K-04R193 1K-04

1 2

R200 1K-04-OR200 1K-04-O

1 2

R205 510-04R205 510-04

1 2

R204 510-04R204 510-04

1 2

CPU_SIC

CPU_SID

CPU_TEST25_H

CPU_TEST25_L

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

CPU M2-3 Miscellany

CPU M2-3 Miscellany

CPU M2-3 Miscellany

RS780M-A2

RS780M-A2

RS780M-A2

5

5

5

of

of

of

39Tuesday, October 21, 2008

39Tuesday, October 21, 2008

39Tuesday, October 21, 2008

1.0

1.0

1.0

A

Page 6

8

A

CPU1F

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

AC8

AC10

AD2

AD3

AD7

AD9

AE10

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

G10

G12

H11

H23

K11

K13

K15

K17

K19

K21

K23

Y17

Y19

CPU1F

VDD1

VDD1

A4

VDD1

A6

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

VDD49

VDD50

H7

VDD51

VDD52

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

VDD150

VDD151

CPU_VDDNB

VCC_CORE VCC_CORE VCC_CORE

D D

C C

B B

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

7

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

R10

R12

R14

R16

R18

R20

U10

U12

U14

U16

U18

U20

W10

W12

W14

W16

W18

W20

6

CPU1G

CPU1G

VDD2

L14

L16

L18

M2

M3

M7

M9

N8

P11

P13

P15

P17

P19

R4

R5

R8

T11

T13

T15

T17

T19

T21

U8

V11

V13

V15

V17

V19

V21

W4

W5

W8

Y11

Y13

Y15

Y21

VDD2

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

P7

VDD19

P9

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

V9

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

VDD72

VDD73

VDD74

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

M21

M23

N20

N22

R22

U22

W22

DHOLE1

DHOLE2

DHOLE3

DHOLE4

MT1

MT2

MT3

MT4

MT5

MT6

MT7

MT8

MT9

MT10

MT11

MT12

MT13

MT14

MT15

MT16

MT17

MT18

MT19

MT20

MT21

MT22

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

VDD21

VDD22

VDD23

VDD24

P21

VDD25

P23

VDD26

VDD27

T23

VDD28

VDD29

V23

VDD30

VDD31

Y23

VDD32

DHOLE1

DHOLE2

DHOLE3

DHOLE4

MT1

MT2

MT3

MT4

MT5

MT6

MT7

MT8

MT9

MT10

MT11

MT12

MT13

MT14

MT15

MT16

MT17

MT18

MT19

MT20

MT21

MT22

5

CPU1H

CPU1H

VDD3

VDD3

MT23

MT24

MT25

MT26

MT27

MT28

MT23

MT24

MT25

MT26

MT27

MT28

N17

VSS1

N19

VSS2

N21

VSS3

N23

VSS4

P2

VSS5

P3

VSS6

P8

VSS7

P10

VSS8

P12

VSS9

P14

VSS10

P16

VSS11

P18

VSS12

P20

VSS13

P22

VSS14

R7

VSS15

R9

VSS16

R11

VSS17

R13

VSS18

R15

VSS19

R17

VSS20

R19

VSS21

R21

VSS22

R23

VSS23

T8

VSS24

T10

VSS25

T12

VSS26

T14

VSS27

T16

VSS28

T18

VSS29

T20

VSS30

T22

VSS31

U4

VSS32

U5

VSS33

U7

VSS34

U9

VSS35

U11

VSS36

U13

VSS37

U15

VSS38

U17

VSS39

U19

VSS40

U21

VSS41

U23

VSS42

V2

VSS43

V3

VSS44

V10

VSS45

V12

VSS46

V14

VSS47

V16

VSS48

V18

VSS49

V20

VSS50

V22

VSS51

W9

VSS52

W11

VSS53

W13

VSS54

W15

VSS55

W17

VSS56

W19

VSS57

W21

VSS58

W23

VSS59

Y8

VSS60

Y10

VSS61

Y12

VSS62

W7

VSS63

Y20

VSS64

Y22

VSS65

MT29

MT30

MT31

MT32

MT29

MT30

MT31

MT32

12

DDR_VTT DDR_VTT

V_DIMM

MC38

MC38

4.7U-08

4.7U-08

4

+1.2V_HT

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

CPU1I

CPU1I

VDDIO

VDDIO

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

VLDT_B

3

VLDT_B

2

VCC1.2+1.2V_HT

1

VLDT_B

VLDT_B

12

MC25

MC25

4.7U-08-O

4.7U-08-O

Place near Socket M2

12

MC30

MC30

4.7U-08

4.7U-08

12

MC29

MC29

4.7U-08-O

4.7U-08-O

+1.2V_HT

12

C227

C227

.22U-06

.22U-06

12

C228

C228

180P-04

180P-04

12

C209

C209

.22U-06

.22U-06

12

Decoupling between Socket M2 and DIMMs

Place as Close to Socket M2 as Possible

DDR_VTT

12

MC57

MC57

4.7U-08-O

4.7U-08-O

12

MC68

MC68

4.7U-08

4.7U-08

12

MC59

MC59

4.7U-08

4.7U-08

12

MC58

MC58

4.7U-08

4.7U-08

12

MC69

MC69

4.7U-08-O

4.7U-08-O

12

C309

C309

.22U-06-O

.22U-06-O

12

C396

C396

.22U-06-O

.22U-06-O

V_DIMM

12

C338

C338

.22U-06

.22U-06

12

C310

C310

.22U-06-O

.22U-06-O

12

C438

C438

.22U-06-O

.22U-06-O

12

MC56

MC56

4.7U-08-O

4.7U-08-O

12

C245

C245

1000P-04

1000P-04

DDR_VTT

12

C249

C249

1000P-04-O

1000P-04-O

12

C324

C324

.22U-06-O

.22U-06-O

12

C251

C251

1000P-04-O

1000P-04-O

12

C248

C248

1000P-04

1000P-04

12

C247

C247

180P-04-O

180P-04-O

12

C250

C250

180P-04-O

180P-04-O

12

C242

C242

180P-04

180P-04

C218

C218

180P-04

180P-04

12

C253

C253

180P-04-O

180P-04-O

CHANGE TOP LAYER

Place Decoupling Capacitors on Bottom Side underneath Socket M2

FOR AMD validation / EMI

12

SC48

SC48

10U-X5-08-X

10U-X5-08-X

12

SC44

SC44

.22U-06-X

.22U-06-X

12

SC47

SC47

10U-08-X

10U-08-X

12

SC53

SC53

180P-04-X-O

180P-04-X-O

12

12

SC45

SC45

.01U-04-X

.01U-04-X

SC46

SC46

10U-X5-08-X

10U-X5-08-X

12

SC73

SC73

10U-X5-08-X

10U-X5-08-X

12

SC52

SC52

10U-08-X

10U-08-X

12

SC72

SC72

10U-08-X

10U-08-X

12

SC51

SC51

10U-X5-08-X

10U-X5-08-X

12

SC49

SC49

10U-08-X

10U-08-X

VCC_CORE V_DIMM

12

12

SC59

SC59

SC54

SC54

.22U-06-X

.22U-06-X

.22U-06-X-O

.22U-06-X-O

12

SC71

SC71

4.7U-08-X-O

4.7U-08-X-O

12

SC50

SC50

10U-08-X

10U-08-X

VCC_CORE

12

12

SC70

SC70

4.7U-08-X

4.7U-08-X

SC58

SC58

10U-X5-08-X

10U-X5-08-X

12

SC69

SC69

4.7U-08-X-O

4.7U-08-X-O

12

SC57

SC57

10U-08-X

10U-08-X

12

SC64

SC64

4.7U-08-X

4.7U-08-X

12

SC56

SC56

10U-X5-08-X

10U-X5-08-X

12

.22U-06-X-O

.22U-06-X-O

SC68

SC68

12

SC55

SC55

10U-08-X

10U-08-X

12

SC67

SC67

.01U-04-X

.01U-04-X

12

SC62

SC62

10U-X5-08-X

10U-X5-08-X

12

SC74

SC74

180P-04-X-O

180P-04-X-O

12

12

SC66

SC66

.22U-06-X

.22U-06-X

SC61

SC61

10U-08-X

10U-08-X

12

SC60

SC60

10U-X5-08-X

10U-X5-08-X

12

SC65

SC65

.22U-06-X-O

.22U-06-X-O

12

SC63

SC63

10U-08-X

10U-08-X

12

MC32

MC32

10U-08

10U-08

12

MC33

MC33

10U-08

10U-08

12

MC35

MC35

10U-08

10U-08

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

12

12

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Custom

Custom

Custom

MC27

MC27

MC36

MC36

10U-08-O

10U-08-O

10U-08

10U-08

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

CPU M2-4 Power and Ground

CPU M2-4 Power and Ground

CPU M2-4 Power and Ground

CPU_VDDNB

12

MC26

MC26

.22U-06

.22U-06

RS780M-A2

RS780M-A2

RS780M-A2

12

6

6

6

MC31

MC31

.01U-04

.01U-04

12

MC28

MC28

.01U-04

.01U-04

A

1.0

1.0

1.0

of

39Tuesday, October 21, 2008

of

39Tuesday, October 21, 2008

of

39Tuesday, October 21, 2008

Page 7

8

A

V_DIMM

184

187

189

238

188

183

63

182

61

60

180

58

179

177

70

57

176

196

174

173

71

190

54

125

134

146

155

202

211

223

232

164

126

135

147

156

203

212

224

233

165

7

16

28

37

84

93

105

114

46

6

15

27

36

83

92

104

113

45

42

43

48

49

161

162

167

168

192

74

73

193

76

52

171

185

137

220

186

138

221

197

VDD69VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

NC(DQS9#)

NC(DQS10#)

NC(DQS11#)

NC(DQS12#)

NC(DQS13#)

NC(DQS14#)

NC(DQS15#)

NC(DQS16#)

NC(DQS17#)

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS8#

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

RAS#

CAS#

WE#

S0#

S1#

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

MA0_CLK_H[2..0]

MA0_CLK_L[2..0]

MA_CHECK[7..0]

MA_DQS_H[8..0]

MA_DQS_L[8..0]

MA_DM[8..0]

MA_BANK[2..0]

MA_ADD[15..0]

MA_DATA[63..0]

VDD59VDD64VDD

VDD67VDD

VSS

VSS

VSS

VSS

VSS

225

228

231

234

237

12

VCC3 VCC3

EC59

EC59

560U-6.3D-OS

560U-6.3D-OS

MA_ADD0

MA_ADD1

D D

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DM8

C C

MA_DQS_H0

MA_DQS_H1

MA_DQS_H2

MA_DQS_H3

MA_DQS_H4

MA_DQS_H5

MA_DQS_H6

MA_DQS_H7

MA_DQS_H8

MA_DQS_L0

MA_DQS_L1

MA_DQS_L2

MA_DQS_L3

MA_DQS_L4

MA_DQS_L5

MA_DQS_L6

MA_DQS_L7

MA_DQS_L8

MA_CHECK0

B B

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

MA_RAS_L

MA_CAS_L

MA_WE_L

MA0_CS_L0

MA0_CS_L1

MA_CKE0

MA0_CLK_H0

MA0_CLK_H1

MA0_CLK_H2

MA0_CLK_L0

MA0_CLK_L1

MA0_CLK_L2

MA0_CLK_H[2..0]4,9

MA0_CLK_L[2..0]4,9

MA_CHECK[7..0]4,8

MA_DQS_H[8..0]4,8

MA_DQS_L[8..0]4,8

MA_DM[8..0]4,8

MA_BANK[2..0]4,8,9

MA_ADD[15..0]4,8,9

MA_DATA[63..0]4,8

7

V_DIMM V_DIMM

172

178

VDD

VDD53VDD

VSS

VSS

VSS

VSS

213

216

219

222

181

191

194

78

VDDQ62VDDQ

VDDQ72VDDQ

VDDQ75VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

166

169

198

201

204

207

210

MA0_ODT04,9

MA_CKE04,9

MA_CAS_L4,8,9

MA_WE_L4,8,9

MA_RAS_L4,8,9

MA0_CS_L[1..0]4,9

MEM_VREF8,9

2

170

175

VDDQ

VDDQ51VDDQ

VDDQ56VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

136

139

142

145

148

151

154

157

160

163

MA0_ODT0

MA_CKE0

MA_CAS_L

MA_WE_L

MA_RAS_L

MA0_CS_L[1..0]

MEM_VREF

6

DDR2_1

DDR2_1

VSS85VSS82VSS79VSS66VSS65VSS50VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96

DQ43

208

DQ44

209

DQ45

214

DQ46

215

DQ47

98

DQ48

99

DQ49

107

DQ50

108

DQ51

217

DQ52

218

DQ53

226

DQ54

227

DQ55

110

DQ56

111

DQ57

116

DQ58

117

DQ59

229

DQ60

230

DQ61

235

DQ62

236

DQ63

120

SCL

119

SDA

239

SA0

240

SA1

101

SA2

102

NC(TEST)

NC(Par_In)

NC

ODT0

ODT1

RESET#

VREF

VSS88VSS91VSS94VSS97VSS

DDR2-240P-OR

DDR2-240P-OR

SMBCK8,10,15,19,22,24,34

SMBDT8,10,15,19,22,24,34

55

68

19

195

77

18

1

SMB_MEM_SCL

SMB_MEM_SDA

MB_ADD[15..0]

MB_BANK[2..0]

MB_DM[8..0]

MB_DQS_H[8..0]

MB_DQS_L[8..0]

MB_CHECK[7..0]

MB_RAS_L

NC(Err_Out#)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

118

121

124

127

130

133

MB_ADD[15..0]4,8,9

MB_BANK[2..0]4,8,9

MB_DM[8..0]4,8

MB_DQS_H[8..0]4,8

MB_DQS_L[8..0]4,8

MB_CHECK[7..0]4,8

MB_RAS_L4,8,9

5

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

SMB_MEM_SCL

SMB_MEM_SDA

MA0_ODT0

MEM_VREF

12

C372

C372

.1U-04-O

.1U-04-O

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DM8

MB_DQS_H0

MB_DQS_H1

MB_DQS_H2

MB_DQS_H3

MB_DQS_H4

MB_DQS_H5

MB_DQS_H6

MB_DQS_H7

MB_DQS_H8

MB_DQS_L0

MB_DQS_L1

MB_DQS_L2

MB_DQS_L3

MB_DQS_L4

MB_DQS_L5

MB_DQS_L6

MB_DQS_L7

MB_DQS_L8

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

MB_RAS_L

MB_CAS_L

MB_WE_L

MB0_CS_L0

MB0_CS_L1

MB_CKE0

MB0_CLK_H0

MB0_CLK_H1

MB0_CLK_H2

MB0_CLK_L0

MB0_CLK_L1

MB0_CLK_L2

V_DIMM VCC3

C366

C366

1 2

.1U-04-O

.1U-04-O

238

188

183

63

182

61

60

180

58

179

177

70

57

176

196

174

173

71

190

54

125

134

146

155

202

211

223

232

164

126

135

147

156

203

212

224

233

165

16

28

37

84

93

105

114

46

15

27

36

83

92

104

113

45

42

43

48

49

161

162

167

168

192

74

73

193

76

52

171

185

137

220

186

138

221

4

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

NC(DQS9#)

NC(DQS10#)

NC(DQS11#)

NC(DQS12#)

NC(DQS13#)

NC(DQS14#)

NC(DQS15#)

NC(DQS16#)

NC(DQS17#)

7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

6

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS8#

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

RAS#

CAS#

WE#

S0#

S1#

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

184

187

189

197

VDD67VDD

VDD69VDD

VDD

VSS

VSS

VSS

VSS

228

231

234

237

3

172

178

VDD

VDD53VDD

VDD59VDD64VDD

VSS

VSS

VSS

VSS

VSS

213

216

219

222

225

MB0_CS_L[1..0]4,9

MB0_CLK_H[2..0]4,9

MB0_CLK_L[2..0]4,9

MB_DATA[63..0]4,8

181

191

194

78

VDDQ62VDDQ

VDDQ72VDDQ

VDDQ75VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

166

169

198

201

204

207

210

MB0_ODT04,9

MB_CAS_L4,8,9

MB_WE_L4,8,9

MB_CKE04,9

170

175

VDDQ

VDDQ51VDDQ

VDDQ56VDDQ

VSS

VSS

VSS

VSS

151

154

157

160

163

MB0_ODT0

MB_CAS_L

MB_WE_L

MB0_CS_L[1..0]

MB_CKE0

MB0_CLK_H[2..0]

MB0_CLK_L[2..0]

MB_DATA[63..0]

VSS

2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

121

124

127

130

133

136

139

142

145

148

2

DDR2_2

DDR2_2

VSS85VSS82VSS79VSS66VSS65VSS50VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS

MB_DATA0

3

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

SCL

SDA

SA0

SA1

SA2

NC(TEST)

NC(Err_Out#)

NC(Par_In)

ODT0

ODT1

RESET#

VREF

VSS88VSS91VSS94VSS97VSS

VSS

VSS

VSS

VSS

VSS

VSS

106

109

112

115

118

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

DDR2-240P-OR

DDR2-240P-OR

100

103

Elitegroup Computer Systems

Elitegroup Computer Systems

Elitegroup Computer Systems

DDR2 DIMM

DDR2 DIMM

DDR2 DIMM

NC

MB_DATA1

4

MB_DATA2

9

MB_DATA3

10

MB_DATA4

122

MB_DATA5

123

MB_DATA6

128

MB_DATA7

129

MB_DATA8

12

MB_DATA9

13

MB_DATA10

21

MB_DATA11

22

MB_DATA12

131

MB_DATA13

132

MB_DATA14

140

MB_DATA15

141

MB_DATA16

24

MB_DATA17

25

MB_DATA18

30

MB_DATA19

31

MB_DATA20

143

MB_DATA21

144

MB_DATA22

149

MB_DATA23

150

MB_DATA24

33

MB_DATA25

34

MB_DATA26

39

MB_DATA27

40

MB_DATA28

152

MB_DATA29

153

MB_DATA30

158

MB_DATA31

159

MB_DATA32

80

MB_DATA33

81

MB_DATA34

86

MB_DATA35

87

MB_DATA36

199

MB_DATA37

200

MB_DATA38

205

MB_DATA39

206

MB_DATA40

89

MB_DATA41

90

MB_DATA42

95

MB_DATA43

96

MB_DATA44

208

MB_DATA45

209

MB_DATA46

214

MB_DATA47

215

MB_DATA48

98

MB_DATA49

99

MB_DATA50

107

MB_DATA51

108

MB_DATA52

217

MB_DATA53

218

MB_DATA54

226

MB_DATA55

227

MB_DATA56

110

MB_DATA57

111

MB_DATA58

116

MB_DATA59

117

MB_DATA60

229

MB_DATA61

230

MB_DATA62

235

MB_DATA63

236

SMB_MEM_SCL

120

SMB_MEM_SDA

119

239

240

101

102

55

68

19

195

77

18

1

RS780M-A2

RS780M-A2

RS780M-A2

MB0_ODT0

MEM_VREF

12

C371

C371

.1U-04-O

.1U-04-O

1

VCC3

739Tuesday, October 21, 2008

739Tuesday, October 21, 2008

739Tuesday, October 21, 2008

of

of

of

1.0

1.0

1.0

A

Page 8

8

A

7

V_DIMM V_DIMM

6

5

4

3

2

1

197

VCC3 VCC3

238

MA_ADD0

188

MA_ADD1

183

MA_ADD2

D D

C C

MA_DQS_H0

MA_DQS_H1

MA_DQS_H2

MA_DQS_H3

MA_DQS_H4

MA_DQS_H5

MA_DQS_H6

MA_DQS_H7

MA_DQS_H8

MA_DQS_L0

MA_DQS_L1

MA_DQS_L2

MA_DQS_L3

MA_DQS_L4

MA_DQS_L5

MA_DQS_L6

MA_DQS_L7

MA_DQS_L8

MA_CHECK0

B B

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

MA_RAS_L

MA_CAS_L

MA_WE_L

MA1_CS_L0

MA1_CS_L1

MA_CKE1

MA1_CLK_H0

MA1_CLK_H1

MA1_CLK_H2

MA1_CLK_L0

MA1_CLK_L1

MA1_CLK_L2

MA1_CLK_H[2..0]4,9

MA1_CLK_L[2..0]4,9

MA_CHECK[7..0]4,7

MA_DQS_H[8..0]4,7

MA_DQS_L[8..0]4,7

MA_DATA[63..0]4,7

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DM8

MA_DM[8..0]4,7

MA_BANK[2..0]4,7,9

MA_ADD[15..0]4,7,9

63

182

61

60

180

58

179

177

70

57

176

196

174

173

71

190

54

125

134

146

155

202

211

223

232

164

126

135

147

156

203

212

224

233

165

7

16

28

37

84

93

105

114

46

6

15

27

36

83

92

104

113

45

42

43

48

49

161

162

167

168

192

74

73

193

76

52

171

185

137

220

186

138

221

VDD69VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

NC(DQS9#)

NC(DQS10#)

NC(DQS11#)

NC(DQS12#)

NC(DQS13#)

NC(DQS14#)

NC(DQS15#)

NC(DQS16#)

NC(DQS17#)

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS8#

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

RAS#

CAS#

WE#

S0#

S1#

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

MA1_CLK_H[2..0]

MA1_CLK_L[2..0]

MA_CHECK[7..0]

MA_DQS_H[8..0]

MA_DQS_L[8..0]

MA_DM[8..0]

MA_BANK[2..0]

MA_ADD[15..0]

MA_DATA[63..0]

VSS

234

237

VDD67VDD

VSS

VDD

VDD53VDD

VDD59VDD64VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

213

216

219

222

225

228

231

181

191

194

78

VDDQ62VDDQ

VDDQ72VDDQ

VDDQ75VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

166

169

198

201

204

207

210

MA1_ODT04,9

MA_CKE14,9

MA_CAS_L4,7,9

MA_WE_L4,7,9

MA_RAS_L4,7,9

MA1_CS_L[1..0]4,9

MEM_VREF7,9

172

178

184

187

189

2

170

175

VDDQ

VDDQ51VDDQ

VDDQ56VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

118

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

MA1_ODT0

MA_CKE1

MA_CAS_L

MA_WE_L

MA_RAS_L

MA1_CS_L[1..0]

MEM_VREF

MB_DQS_H[8..0]4,7

MB_DQS_L[8..0]4,7

MB_CHECK[7..0]4,7

NC(Err_Out#)

MB_ADD[15..0]4,7,9

MB_BANK[2..0]4,7,9

MB_DM[8..0]4,7

MB_RAS_L4,7,9

VSS85VSS82VSS79VSS66VSS65VSS50VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

SCL

SDA

SA0

SA1

SA2

NC(TEST)

NC(Par_In)

ODT0

ODT1

RESET#

VREF

VSS88VSS91VSS94VSS97VSS

DDR2-240P-Y

DDR2-240P-Y

SMBCK7,10,15,19,22,24,34

SMBDT7,10,15,19,22,24,34

DDR2_3

DDR2_3

NC

MA_DATA0

3

MA_DATA1

4

MA_DATA2

9

MA_DATA3

10

MA_DATA4

122

MA_DATA5

123

MA_DATA6

128

MA_DATA7

129

MA_DATA8

12

MA_DATA9

13

MA_DATA10

21

MA_DATA11

22

MA_DATA12

131

MA_DATA13

132

MA_DATA14

140

MA_DATA15

141

MA_DATA16

24

MA_DATA17

25

MA_DATA18

30

MA_DATA19

31

MA_DATA20

143

MA_DATA21

144

MA_DATA22

149

MA_DATA23

150

MA_DATA24

33

MA_DATA25

34

MA_DATA26

39

MA_DATA27

40

MA_DATA28

152

MA_DATA29

153

MA_DATA30

158

MA_DATA31

159

MA_DATA32

80

MA_DATA33

81

MA_DATA34

86

MA_DATA35

87

MA_DATA36

199

MA_DATA37

200

MA_DATA38

205

MA_DATA39

206

MA_DATA40

89

MA_DATA41

90

MA_DATA42

95

MA_DATA43

96

MA_DATA44

208

MA_DATA45

209

MA_DATA46

214

MA_DATA47

215

MA_DATA48

98

MA_DATA49

99

MA_DATA50

107

MA_DATA51

108

MA_DATA52

217

MA_DATA53

218

MA_DATA54

226

MA_DATA55

227

MA_DATA56

110

MA_DATA57

111

MA_DATA58

116

MA_DATA59

117

MA_DATA60

229

MA_DATA61

230

MA_DATA62

235

MA_DATA63

236

SMB_MEM_SCL

120

SMB_MEM_SDA

119

239

240

101

102

55

68

19

MA1_ODT0

195

77

18

MEM_VREF

1

SMB_MEM_SCL

SMB_MEM_SDA

MB_ADD[15..0]

MB_BANK[2..0]

MB_DM[8..0]

MB_DQS_H[8..0]

MB_DQS_L[8..0]

MB_CHECK[7..0]

MB_RAS_L

12

C373

C373

.1U-04-O

.1U-04-O

VCC3

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3